сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Цифровой одноканальный инфранизкочастотный фазометр | 1987 |

|

SU1472831A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1439619A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1348828A1 |

Изобретение относится к цифровой электроизмерительной технике и может быть использовано прм создании универсальных цифровых приборов для измерения характеристик синусоидальных сигналов. Цель изобретения - повышение точности и быстродействия измерений. Она достигается тем, что в устройство введены второй счетчик 9 адреса, второе оперативное запоминающее устройство 7, три селектора- мультиплексора 3. 4, 14, три селектора-демультиплексора 2, 10, 11, цифровой рекурсивный фильтр 15, сумматор 12 и вычитатель 13. Устройство также содержит аналого-цифровой преобразователь 1, счетчик 9 адреса, оперативное запоминающее устройство 6, элемент ИЛИ 5, блок 16 вычислений и блок 17 индикации. 3 ил.

Ш)

VJ сл

00

сл

4 СЛ

Изобретение относится к цифровой электроизмерительной технике, а именно к измерению амплитуды, фазы и частоты синусоидальных сигналов.

Цель изобретения - повышение точности и быстродействия измерений.

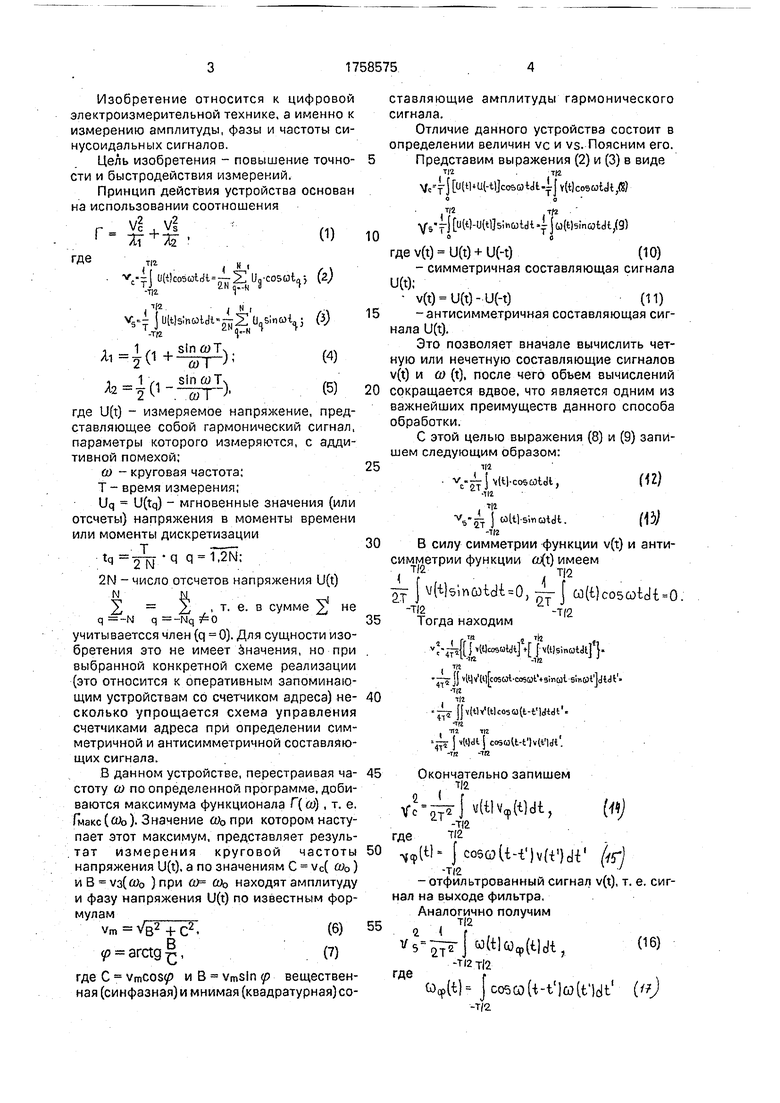

Принцип действия устройства основан на использовании соотношения

Г

V3.V

Ъ+-%

(D

TI2.ц ,

u(ticcautdi-j S Uj-cosot,} (г)

-Т12 t1

JU

V5.i j UMsincotdfj-IE U.sino)i. i (З)

Vrz2VN H

slnwTx

Ai(1 +

i 1 /, slnftTTv &-20аГГ

где U(t) - измеряемое напряжение, представляющее собой гармонический сигнал, параметры которого измеряются, с аддитивной помехой;

(О - круговая частота;

Т - время измерения;

Uq U(tq) - мгновенные значения (или отсчеты) напряжения в моменты времени или моменты дискретизации Т

tq

2N

q q 1,2N;

2N - число отсчетов напряжения U(t) 2) 2) , т. е. в сумме не

q -N q -Nq

учитываетсся член (q 0). Для сущности изобретения это не имеет значения, но при выбранной конкретной схеме реализации (это относится к оперативным запоминающим устройствам со счетчиком адреса) несколько упрощается схема управления счетчиками адреса при определении симметричной и антисимметричной составляющих сигнала.

В данном устройстве, перестраивая частоту (а поопределенней программе, добиваются максимума функционала Г( о), т. е. (макс (%). Значение котором наступает этот максимум, представляет результат измерения круговой частоты напряжения U(t), а по значениям С vc( Ш0) и В УЗ( ) при и С0о находят амплитуду и фазу напряжения U(t) по известным формулам

(6)

vm Ve2 +с2.

р

р arctg -,

(7)

где С Vmcosp и В VmSin (p вещественная (синфазная) и мнимая (квадратурная) составляющие амплитуды гармонического сигнала.

Отличие данного устройства состоит в определении величин vc и vs. Поясним его. 5Представим выражения (2) и (3) в виде

Т|2ТК

VC4 j U{tl U(-t|Jco&c3 У t -ij у (t) cosutdi $

Т|2

,т/г

Y5-fi uW-uWbihwtdt4J((:)sinwtdt,

оо

W3v(t) U(t) + U(-t)(10)

- симметричная составляющая сигнала U(t);

- v(t) U(t)-U(-t)(11)

-антисимметричная составляющая сигнала U(t).

Это позволяет вначале вычислить четную или нечетную составляющие сигналов v(t) и (о (t), после чего объем вычислений сокращается вдвое, что является одним из важнейших преимуществ данного способа обработки.

С этой целью выражения (8) и (9) запишем следующим образом: да

vc-5fJxW-cosfi)Wl,(2)

112 Т|2

j colt sin tatdt.

-TI2

(13

В силу симметрии функции v(t) и антисимметрии функции ft)(t) имеем

Т4 Т 2

- v(%;nwtdbO, J co(t)co50).

-TI2

Тогда находим

-Т (2

- jh-WcwByiftf vftlemotJl }.

414

j{ vlljv Wfcosurt-cosut +ainal s muJt jdtdt 0

-T|Z

111

T J Hb Wcosult-t Widt1т«

tilTI2

j WJljtosuU-tXt Mt .

-TR-112

Окончательно запишем

TI2

4 J

Гс-21

где Т12

VC OT

I v(tlv9(t}dt,(

ny Z j Op

-TI2

1 ч1-.

(tl- co5oU-t )v(i )di У

-Т/2. У

- отфильтрованный сигнал v(t), т. е. сигнал на выходе фильтра, Аналогично получим

,

й

i/ .

V5 2T2

где

jwfclWqMdt,(16)

-Т 12 т|2

(t) JcWQ -t lwlt ldt (I) -Т/2

- отфильтрованный сигнал w(t) В формулах (14), (15), (16), (17) перейдем к дискретному представлению (от интегралов к суммам), предполагая, что полное чис- ло отсчетов сигналов на интервале

измерения (--п , -у) равно 2N, что соответствует шагу дискретизации At T/2N. Для формул (14), (15) имеем

Ч. V с

it 2Т

S ),

rN а

(18)

tt)Z co5 cOU%k| v(kutUt. (19)

Обозначим

v(q At) vq Уф(дД t) A -t УФЧ Тогда выражения (18), (19) принимают вид Ч ( N г.,

-u)

V с

N i чг

vjoo cosfa-kUoilv LJ

к)

гЛ

где Да

Как известно, величина УФЧ представляет собой выходной сигнал цифрового фильтра с импульсной характеристикой hn cosqAcr на вход которого подана последовательность КОДОВ Vk (v-N-q V-N-2 ... 0).

Аналогично для формул (16), (17) имеем

v,ft (

S°V (}

N ,

«n(p-2cos(. (гз)

Отсчеты vq, (tiq симметричного v(t) и антисимметричного oi(t) сигналов образуются по отсчетам входного сигнала Uq согласно формулам (10) и (11):

Vq v(q At) Uq + U-q(24)

fflq 0) (q At) Uq - U-q, (25)

где Uq Ufa At), U-q U(-q At).

Найдем структуру цифрового фильтра для получения сигналов и для этого вычислим передаточную функцию

H(z)| (26)

q 0

где hq cosq Act ; q 0, hq 0 при q 0 (условие реализуемости фильтра). Получим

н(2.|:г о5Я4о(,- (1:г л+Јгл-1Ч 1.

1-о2V° о/

д ьг созлоб

2 i-z-V4 + -2- е-5Н 1-2г- со5л«, + г-г

(27)

Известно, что такой вид имеет передаточная функция рекурсивного фильтра второго порядка. Соответствующее разностное уравнение, связывающее входную xq (vq или

ftAq) И ВЫХОДНУЮ Уд(Уфд ИЛИ fttyq ) ПОСЛедОВЗ5 тельности кодов и определяющее структуру

цифрового рекурсивного фильтра имеет вид

yq - 2cosAcr yq-i xq - cosAa xq-i (28)

Отметим, что такой фильтр находится на

границе устойчивости, так как знаменатель

выражения (27) имеет корни zi,2 е так что zi,2 1. Однако поскольку фильтр работает только 2N тактов, то его неустойчивость не проявляется. Она может сказаться в накоплении погрешностей, что можно устранить выбором разрядности счетчиков или регистров фильтра.

Аналоговый вариант такого фильтра нереализуем.

Таким образом, в основу работы устрой- ства положены формулы (1), (4), (5), (6), (7), (8), (19), (20), (21), (24), (25), причем соотношения (19) и (21) реализуются цифровым рекурсивным фильтром второго порядка.

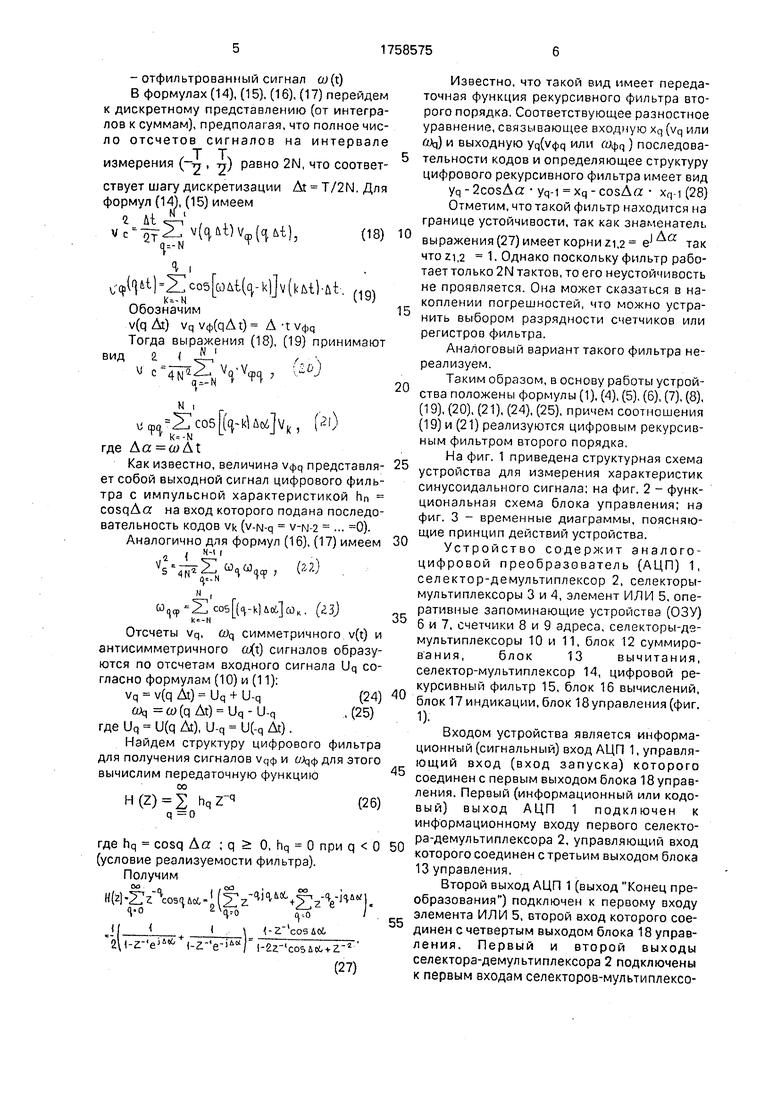

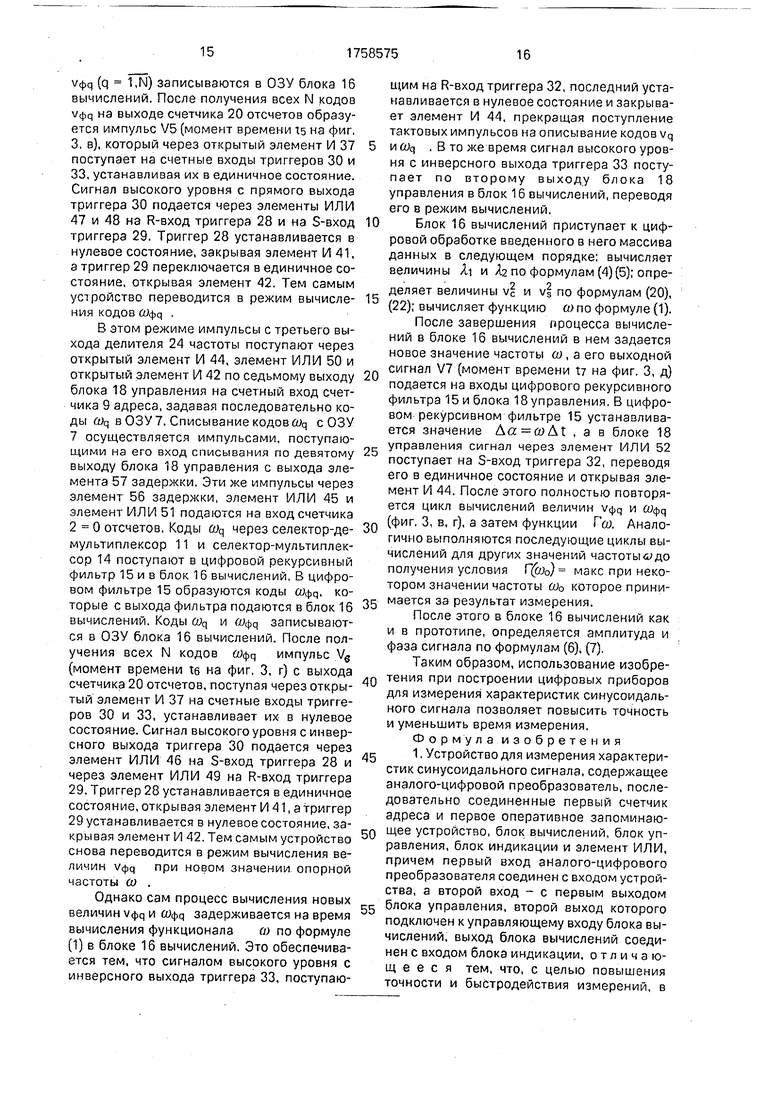

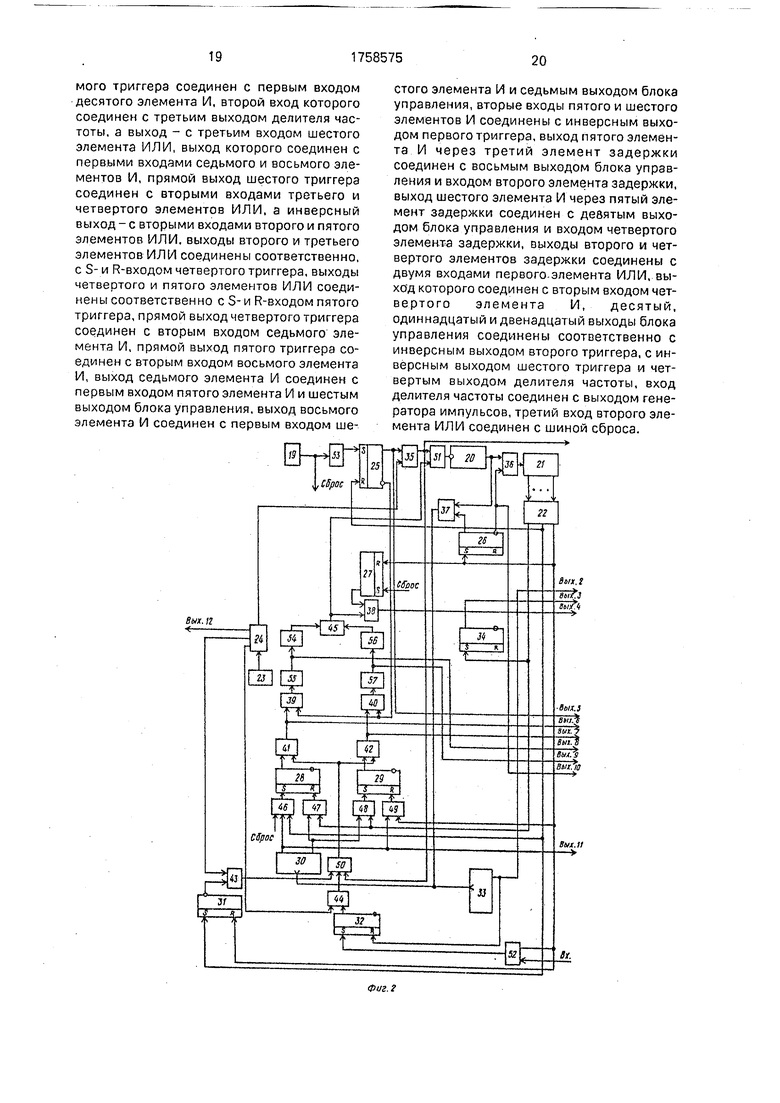

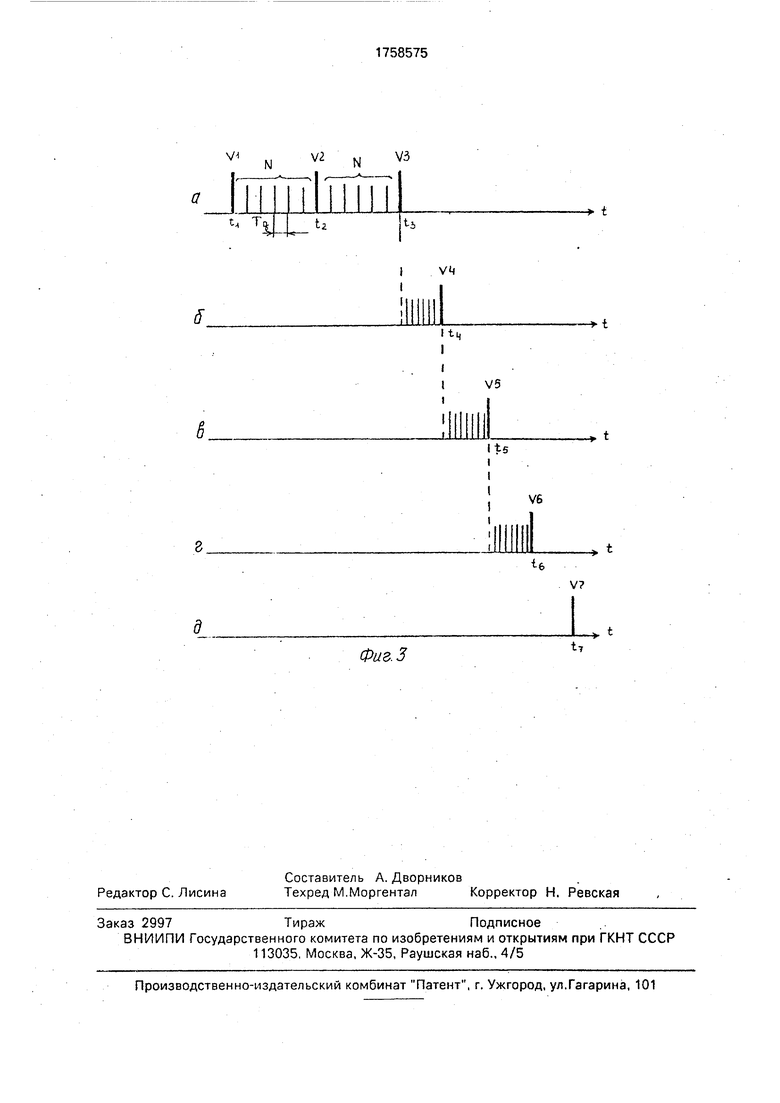

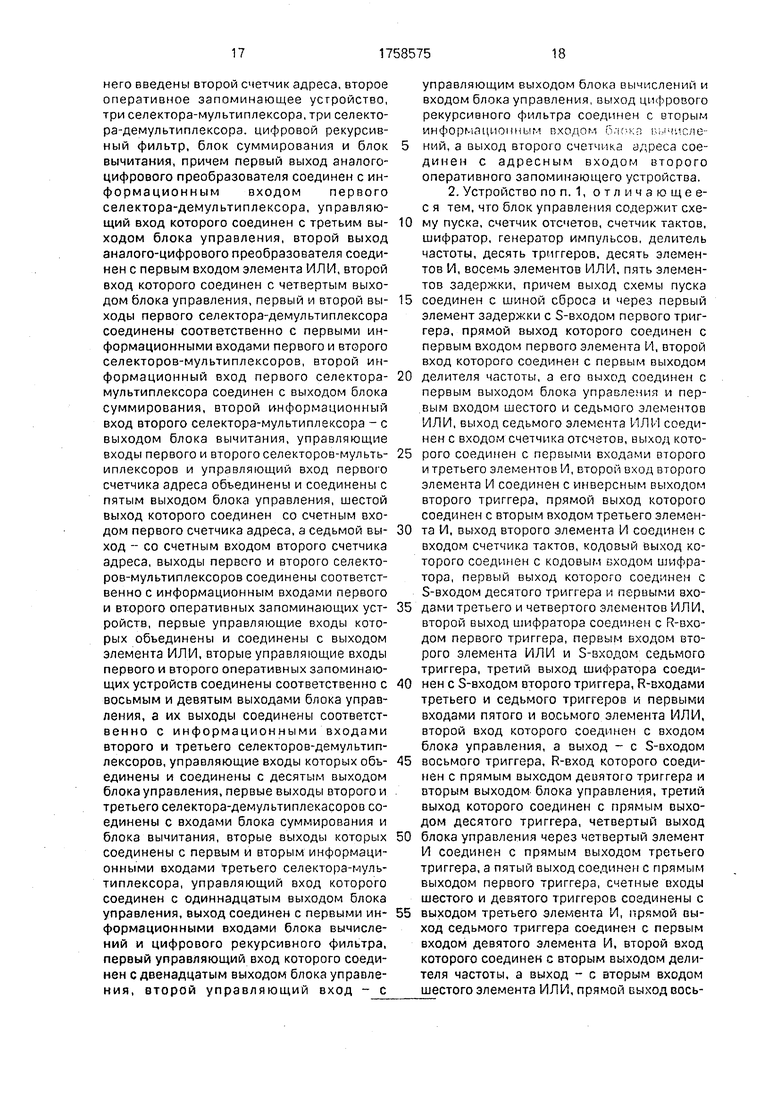

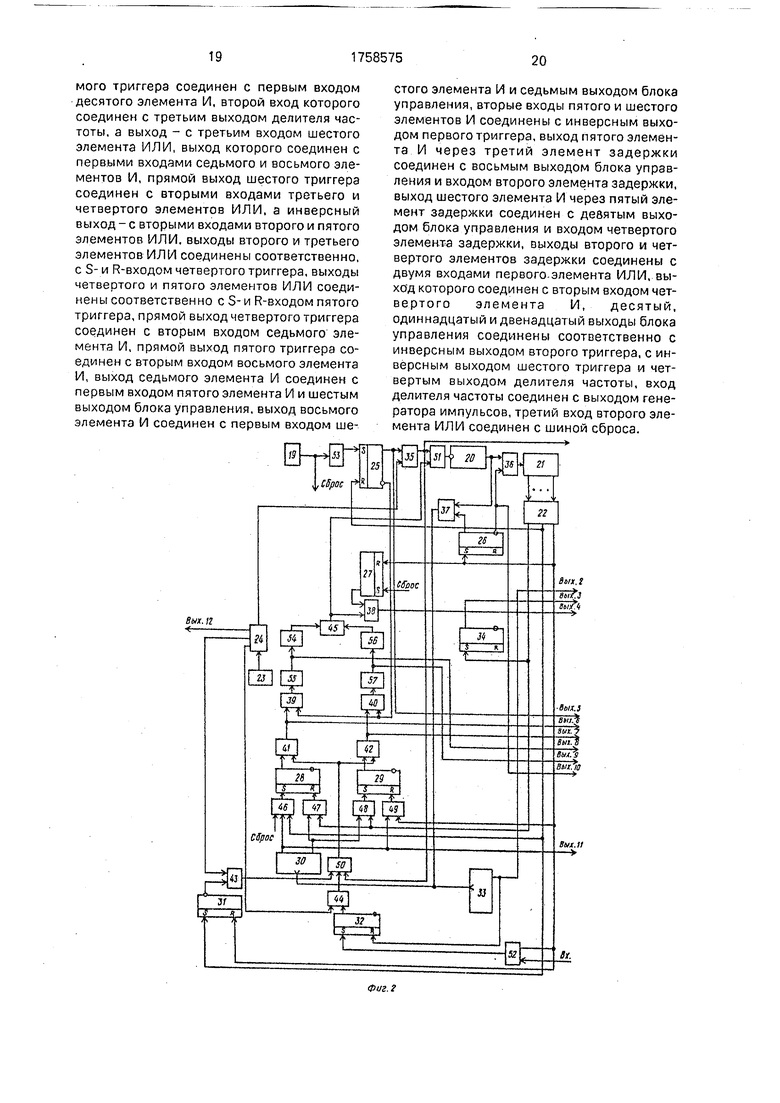

На фиг. 1 приведена структурная схема устройства для измерения характеристик синусоидального сигнала; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - временные диаграммы, поясняющие принцип действий устройства.

Устройство содержит аналого- цифровой преобразователь (АЦП) 1, селектор-демультиплексор 2, селекторы- мультиплексоры 3 и 4, элемент ИЛИ 5, оперативные запоминающие устройства (ОЗУ) 6 и 7, счетчики 8 и 9 адреса, селекторы-дз- мультиплексоры 10 и 11, блок 12 суммирования, блок13 вычитания, селектор-мультиплексор 14, цифровой рекурсивный фильтр 15, блок 16 вычислений, блок 17 индикации, блок 18управления (фиг.

1).

Входом устройства является информационный (сигнальный) вход АЦП 1, управляющий вход (вход запуска) которого соединен с первым выходом блока 18 управления. Первый (информационный или кодовый) выход АЦП 1 подключен к информационному входу первого селекто- ра-демультиплексора 2, управляющий вход которого соединен с третьим выходом блока 13 управления.

Второй выход АЦП 1 (выход Конец преобразования) подключен к первому входу элемента ИЛИ 5, второй вход которого сое55

динен с четвертым выходом блока 18 управления. Первый и второй выходы селектора-демультиплексора 2 подключены к первым входам селекторов-мультиплексоров 3 и 4 соответственно. Второй вход селектора-мультиплексора 3 соединен с выходом блока 12 суммирования, а второй вход селектора-мультиплексора 4 - с выходом блока 13 вычитания.

Управляющие входы селекторов-мультиплексоров 3 и 4 и управляющий вход (вход реверса) счетчика 8 адреса объединены и подключены к пятому выходу блока 18 управления, Счетный вход счетчика 8 адреса соединен с шестым выходом блока 18 управления, а счетный вход счетчика 9 адреса - с седьмым выходом блока 18 управления. Кодовые выходы счетчиков 8 и 9 адреса подключены к адресным входам ОЗУ 6 и 7 соответственно, информационные входы которых соединены с выходами селекторов- мультиплексоров 3 и 4, первые управляющие входы (входы записи) объединены между собой v. соединены с выходом элемента ИЛИ 5, а вторые управляющие входы (входы списывания) подключены соответственно к восьмому и девятому выходам блока 18 управления.

Выходы ОЗУ 6 и 7 соединены с информационными входами селекторов-демуль- типлексоров 10 и 11, управляющие входы которых объединены между собой и подключены к десятому выходу блока 18 управления.Первыевыходы селекторов-демультиплексоров 10, 11 соединены с входами блока 12 суммирования и блока 13 вычитания, а вторые выходы - с первым и вторым информационными входа ми селектора-мультиплексора 14. управляющий аход которого подключен к одиннадцатому выходу блока 18 управления, а его выход соединен с первым информационным входом блока 16 вычислений и входом цифрового рекурсивного фильтра 15, выход которого подключен к второму информационному входу блока 16 вычислений. Первый управляющий вход цифрового рекурсивного фильтра 15 соединен с двенадцатым выходом блока 18 управления, а второй управляющий вход, объединен с входом блока 18 управления и соединен с управляющим выходом блока 16 вычислений. Управляющий вход блока 16 вычислений подключен к второму выходу блока 18 управления, а информационный выход - к блоку 17 индикации.

Блок управления содержит схему 19 пуска, счетчик 20 отсчетов, счетчик 21 тактов, шифратор 22, генератор 23 импульсов, делитель 24 частоты, триггеры 25 - 34, элементы И 35 - 44, элементы ИЛИ 45 - 52, элементы 53 - 57 задержки.

Выход схемы 19 пуска соединен с шиной сброса (на схеме не показана) и через

элемент 53 задержки с S-входом триггера

25,прямой выход которого подключен к пятому выходу блока 18 управления и к первому входу элемента И 35. Второй вход

элемента И 35 соединен с первым выходом

делителя 24 частоты, а его выход подключен

к первому выходу блока 18 управления и

первым входам элементов ИЛИ 50 и 51.

Вход делителя 24 частоты соединен с

0 выходом генератора 23 импульсов. Выход элемента ИЛИ 51 подключен к входу счетчика 20 отсчетов, выход которого соединен с первыми входами элементов И 36 и 37. Второй вход элемента И 36 объединен с деся5 тым выходом блока 18 управления и подключен к инверсному выходу триггера

26,прямой выход которого соединен с вторым входом элемента И 37.

Выход элемента И 36 подключен к входу

0 счетчика 21 тактов, кодовый выход которого соединен с шифратором 22. Первый выход шифратора 22 подключен к S-входу триггера 34 и первым входом элементов ИЛИ 47 и 48. Прямой выход триггера 34 является третьим

5 выходом блока 18 управления.

Второй выход шифратора 22 срединен с R-входом триггера 25, первым входом элемента ИЛИ 46 и S-входом триггера 31. Третий выход шифратора 22 подключен к

0 S-входу триггера 26, R-входу триггера 27, R-входу триггера 31, первому входу элемента ИЛИ 49 и первому входу элемента ИЛИ 52, второй вход которого подключен к входу блока 18 управления, а выход соединен с

5 S-входом триггера 32, подключенного своим R-входом к второму выходу блока 18 управления и инверсному выходу триггера 33. Счетные входы триггеров 30 и 33 объединены между собой и подключены к выходу

0 элемента И 37, Прямой выход триггера 31 соединен с первым входом элемента И 43, второй вход которого подключен к второму выходу делителя 24 частоты, а выход - к второму входу элемента ИЛИ 50.

5 Прямой выход триггера 32 соединен с первым входом элемента И 44, второй вход которого подключен к третьему выходу делителя 24 частоты, а выход - к третьему входу элемента ИЛИ 50, выход которого со0 единен с первыми входами элементов И 41 и 42. Инверсный выход триггера 30 соединен с вторыми входами элементов ИЛИ 46 и 49 и одиннадцатым выходом блока 18 управления, а прямой выход - с вторыми входами

5 элементов 47 и 48. Выходы элементов ИЛИ 46, 47 подключены к S- и R-входам триггера 28, а выходы элементов ИЛИ 48, 49 - к S- и R-входам триггера 29.

Прямой выход триггера 28 соединен с вторым входом элемента И 41, а прямой

выход триггера 29 - с вторым входом элемента И 42, Выход элемента И 41 подключен к шестому выходу блока 18 управления и первому входу элемента И 39. Выход элемента И 42 подключен к седьмому выходу блока 18 управления и первому входу элемента И 40, Вторые входы элементов И 39 и 40 объединены между собой и подключены к инвпрсному выходу триггера 25. Выход элемента И 39 через элемент 55 задержки соединен с восьмым входом блока 18 управления и входом элемента 54 задержки. Выход элемента И 40 через элемент 57 задержки соединен с девятым выходом блока 18 управления и входом элемента 56 задержки. Выходы элементов 54 и 56 задержки подключены к двум входам элемента ИЛИ 45, выход которого соединен с первым входом элемента И 38, подключенного своим вторым входом к прямому выходу триггера 27, а его выход служит четвертым выходом блока 18 управления, двенадцатый выход которого соединен с четвертым выходом делителя 24 частоты.

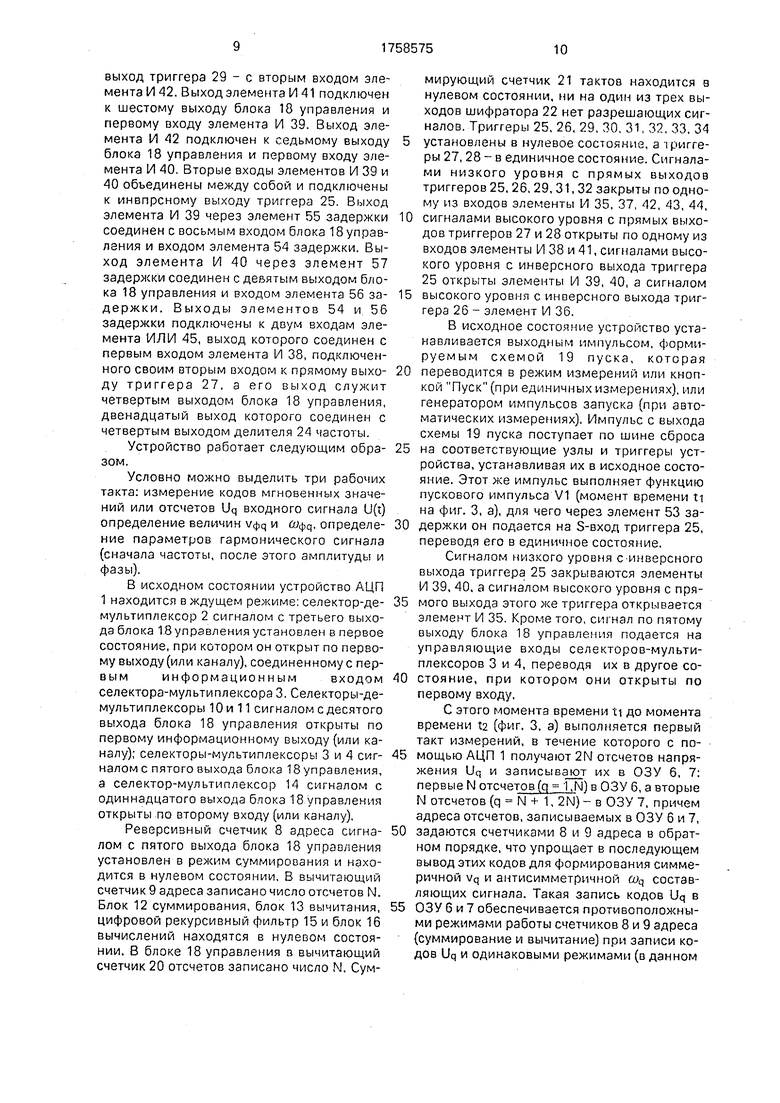

Устройство работает следующим образом.

Условно можно выделить три рабочих такта: измерение кодов мгновенных значений или отсчетов Uq входного сигнала U(t) определение величин ,q и otyq, определение параметров гармонического сигнала (сначала частоты, после этого амплитуды и фазы).

В исходном состоянии устройство АЦП 1 находится в ждущем режиме: селектор-де- мультиплексор 2 сигналом с третьего выхода блока 18 управления установлен в первое состояние, при котором он открыт по первому выходу (или каналу), соединенному с пер- вым информационным входом селектора-мультиплексора 3. Селекторы-де- мультиплексоры 10 и 11 сигналом с десятого выхода блока 18 управления открыты по первому информационному выходу (или каналу); селекторы-мультиплексоры 3 и 4 сигналом с пятого выхода блока 18 управления, а селектор-мультиплексор 14 сигналом с одиннадцатого выхода блока 18 управления открыты по второму входу (или каналу).

Реверсивный счетчик 8 адреса сигналом с пятого выхода блока 18 управления установлен в режим суммирования и находится в нулевом состоянии. В вычитающий счетчик 9 адреса записано число отсчетов N. Блок 12 суммирования, блок 13 вычитания, цифровой рекурсивный фильтр 15 и блок 16 вычислений находятся в нулевом состоянии. В блоке 18 управления в вычитающий счетчик 20 отсчетов записано число N. Суммирующий счетчик 21 тактов находится а нулевом состоянии, ни на один из трех выходов шифратора 22 нет разрешающих сигналов. Триггеры 25, 26, 29, 30, 31, 32, 33, 34 установлены в нулевое состояние, а триггеры 27, 28 - в единичное состояние. Сигналами низкого уровня с прямых выходов триггеров 25. 26, 29, 31, 32 закрыты по одному из входов элементы И 35, 37, 42, 43, 44,

сигналами высокого уровня с прямых выходов триггеров 27 и 28 открыты по одному из входов элементы И 38 и 41, сигналами высокого уровня с инверсного выхода триггера 25 открыты элементы И 39, 40, а сигналом

высокого уровня с инверсного выхода триггера 26 - элемент И 36.

В исходное состояние устройство устанавливается выходным импульсом, формируемым схемой 19 пуска, которая

переводится в режим измерений или кнопкой Пуск (при единичных измерениях), или генератором импульсов запуска (при автоматических измерениях). Импульс с выхода схемы 19 пуска поступает по шине сброса

на соответствующие узлы и триггеры устройства, устанавливая их в исходное состояние. Этот же импульс выполняет функцию пускового импульса V1 (момент времени tt на фиг. 3, а), для чего через элемент 53 задержки он подается на S-вход триггера 25, переводя его в единичное состояние.

Сигналом низкого уровня с инверсного выхода триггера 25 закрываются элементы И 39, 40. а сигналом высокого уровня с прямого выхода этого же триггера открывается элемент И 35. Кроме того, сигнал по пятому выходу блока 18 управления подается на управляющие входы селекторов-мультиплексоров 3 и 4, переводя их в другое состояние, при котором они открыты по первому входу,

С этого момента времени ti до момента времени t2 (фиг, 3, а) выполняется первый такт измерений, в течение которого с помощью АЦП 1 получают 2N отсчетов напряжения Uq и записывают их в ОЗУ 6, 7: первые N отсчетов (q 1.N) в ОЗУ 6, а вторые N отсчетов (q N + 1, 2N)- в ОЗУ 7, причем адреса отсчетов, записываемых в ОЗУ 6 и 7,

задаются счетчиками 8 и 9 адреса в обратном порядке, что упрощает в последующем вывод этих кодов для формирования симме- ричной Vq и антисимметричной щ составляющих сигнала. Такая запись кодов Uq в

ОЗУ 6 и 7 обеспечивается противоположными режимами работы счетчиков 8 и 9 адреса (суммирование и вычитание) при записи кодов Uq и одинаковыми режимами (в данном

случае вычитание, но можно и суммирование) при списывании кодов Uq с ОЗУ 6 и 7,

Импульсы с первого выхода делителя 24 частоты, следующие с заданным интервалом (или периодом) дискрнетизации Тд (фиг. 3, а) входного сигнала и U(t) через открытый элемент И 35 и элемент ИЛИ 51 поступают на счетчик 20 отсчетов, по первому выходу блока 18 управления на вход запуска АЦП 1, на сигнальный (или информационный) вход которого подается измеряемый сигнал U(t), и через элемент ИЛИ 50 на первые входы элементов И 41, 42. Поскольку элемент И 42 закрыт сигналом низкого уровня с прямого выхода триггера 29, то импульсы с выхода элемента И 35 через него не проходят. В то же время эти импульсы поступают через открытый элемент И 41 по шестому выходу блока 18 управления на счетный вход счетчика 8 адреса и на первый вход элемента 1/1 39, через который они не проходят, так как он закрыт по второму входу сигналом низкого уровня с инверсного выхода триггера 25.

Импульсы, поступающие с первого выхода блока 18 управления на вход запуска АЦП 1, переводят его в рабочее состояние, и на информационном (или кодовом) выходе АЦП 1 образуются коды мгновенных значений (или отсчеты) Uq сигнала U(t) в моменты дискретизации tq. Эти коды через селектор- демультиплексор 2 и селектор-мультиплексор 3 поступают на информационные входы ОЗУ 6, адреса ячеек памяти которого задаются кодом счетчика 8 адреса, подаваемым на адресный вход ОЗУ 6. Состояние счетчика 8 адреса последовательно увеличивается на единицу импульсами, поступающими на его счетный входе шестого выхода блока 18 управления синхронно с импульсами запуска АЦП 1. Запись кодов Uq с АЦП 1 в ОЗУ б осуществляется импульсами Конец преобразования, которые подаются с одноименного выхода АЦП 1 через элемент ИЛИ 5 на входы записи ОЗУ 6, 7. Так устройство работает до получения N отсчетов Uq (q 1,N), т. е. в течение импульсов запуска, подсчитываемых счетчиком 20 отсчетов. После этого счетчик 20 обнуляется и на его выходе образуется импульс V2 (момент времени 12 на фиг. 3, а), который восстанавливает исходное состояние счетчика 20 и через открытый элемент И 36 подается на счетчик 21 тактов, записывая в него единицу. На первом выходе шифратора 22 формируется высокий уровень сигнала, который поступает на S-вход триггера 34, через элемент ИЛИ 47 на R-вход триггера 28 и через элемент ИЛИ 48 на S-вход триггера 29. Триггер 34 устанавливается в единичное состояние, сигнал высокого уровня с его прямого выхода поступает по третьему выходу блока 18 управления на управляющий вход селек- тора-демультиплексора 2 и переводит его в

другое состояние, при котором он закрывается по первому выходу и открывается по второму выходу. Триггер 28 возвращается в исходное состояние, закрывая элемент И 41, а триеггер 29 переключается в единичное состояние, открывая элемент И 42.

После этого с момента времени t2 до момента времени ts (фиг. 3,а) импульсы с выхода элемента И 35 продолжают поступать на запуск АЦП 1 по первому выходу

блока 18 управления, а также через элемент ИЛИ 50 и элемент И 42 по седьмому выходу блока 18 управления на счетный вход счетчика 9 адреса. Коды с выхода АЦП 1 через селектор-демультиплексор 2 и селектормультиплексор 4 податюся на информационный вход ОЗУ 7, адреса которого задаются кодом вычитающего счетчика 9 адреса, С получением очередных N отсчетов Uq (q N + 1, 2N) на выходе счетчика 20

образуется импульс V3 (момент времени хз на фиг. 3, а), который через элемент И 36 записывается в счетчик 21 тактов. На втором выходе шифратора 22 образуется сигнал высокого уровня, который поступает на

R-вход триггера 25, на S-вход триггера 31 и через элемент ИЛИ 46 на S-вход триггера 28. Триггер 25 возвращается в исходное состояние, закрывая элемент И 35 и открывая элементы И 39, 40, а также сигналом по

пятому выходу блока 18 управления переключает селекторы-мультиплексоры 3 и 4, открывая их по второму входу, и устанавливает счетчик 8 адреса по его управляющему входу (входу реверса) в режим вычитания, К

этому моменту в счетчик 8 адреса будет записано число N и оно сохраняется, В счетчике 9 адреса также восстанавливается число N его выходным импульсом после того, как в предыдущем такте на него поступило N

импульсов с седьмого выхода блока 18 управления,

С момента времени ta до момента времени t4 (фиг. 3, б) выполняется второй такт измерений, при котором осуществляется

вычисление кодов симметричной vq и антисимметричной составляющих сигнала по отсчетам Uq, записанным в ОЗУ 6 и 7. Причем в этом, вычислительном такте списывания кодов Uq может производиться с

высокой частотой, ограничиваемой только быстродействием выполнения операций в блоке 12 суммирования и в блоке 13 вычитания. Эти импульсы подаются с второго выхода делителя 24 частоты через открытый

элемент И 43, через элемент ИЛИ 50 и через элементы И 41 и 42 по шестому и седьмому выходам блока 18 управления на счетные входы счетчиков 8 и 9 адреса. Оба счетчика работают в одном направлении, а следовательно, адреса кодов Uq в ОЗУ 6 и 7 изменяются симметрично относительно границы, р азделяющей их на две половины Uq (q -1,N) и U-q (q N+1, 2N) (момент времени t на фиг, 3, а), что достигается, как указывалось, противоположным изменением адресов кодов Uq в одном из ОЗУ, в данном случае в ОЗУ б, при их записи и списывании. С некоторой задержкой по отношению к входным импульсам счетчиков 8, 9 адреса на выходах элементов 55 и 57 задержки формируются импульсы, поступающие по восьмому и девятому выходам блока 18 управления на входы списывания ОЗУ 6, 7. Коды Uq с ОЗУ 6 через селектор-демультип- лексор 10, открытый по первому входу, подаются на первые входы блока 12 суммирования и бпока 13 вычитания, а коды U-q с ОЗУ 7 через селектор-демультиплек- сор 11, также открытый по первому входу, поступают на вторые входы бтока 12 суммирования сумматора и блока 13 вычитания.

В блоке 12 суммирования и блоке 13 вычитания согласно соотношениям (24) и (25), коды Vq и Wq которые через селекторы- мультиплексоры 3 и 4, открытые по вторым входам, подаются на информационные входы ОЗУ 6 и 7, т. е, для хранения кодов vq и Wq используются те же ОЗУ 6 и 7, для чего они записываются в ячейки памяти списанных кодов Uq и U-q. Поскольку число кодов vq и Wq равно N(q 1, N), то объем каждого ОЗУ 6 и 7 позволяет записать раздельно все

КОДЫ Vq И (Уд .

Запись кодов vq, atq осуществляется импульсами, поступающими по четвертому выходу блока 18 управления через элемент ИЛИ 5 на объединенные входы записи ОЗУ 6 и 7. Эти импульсы образуются на выходе элемента ИЛИ 45 с некоторой задержкой, задаваемой элементами 54 и 56 задержки по отношению к импульсам списывания на выходах элементов 55 и 57, задержки. Выходные импульсы элемента ИЛИ 45 подаются через открытый элемент И 38 на четвертый выход блока 18 управления и через элмент ИЛИ 51 на счетчик 20 отсчетов. С поступлением N импульсов списывания (и записи) 6, 7 будут записаны коды vq, щ (q 1 ,IM) и в этот момент в очередной раз обнулится счетчик 20 отсчетов. Его третий выходной импульс V4 (момент времени t4 на фиг. 3, 6) через открытый элемент И 36 поступит в счетчик 21 тактов и на третьем

0

5

0

5

0

5

0

5

0

5

выход шифратора 22 образуется сигнал, который подается на S-вход триггера 26, на R-вход триггера 27, через элемент ИЛИ 49 на R-вход трш гера 29. на -г.м ,r -пгггра 3 1 и через элемент ИЛИ 52 па S-вход rpni i ера 32.

Триггер 26 устанавливается в единичное состояние, закрывая элемент И 36 и открывая элемент И 37. Кроме того, сигнал с инверсного выхода триггера 26 поступает по десятому выходу блока 18 управления на управляющие входы селекторов-демультип- лексоров 10, 11, открывая из по второму выходу. Триггеры 27, 29 и 31 возвращаются в исходное состояние, закрывая элементы И 38, 42 и 43 соответственно. Триггер 32 устанавливается в единичное состояние,открывая элемент И 44 для прохождения импульсов с третьего выхода делителя 24 частоты.

На этом завершаетсся второй такт измерений и начинается третий такт измерений, в течение которого производится определение частоты, в соответствии с известным, как и в прототипе, критерием (1),

но величины v и vs в отличие от прототипа, находят с применением цифрового рекурсивного фильтра 15 согласно выражениям (20), (22), 8 свою очередь третий такт работы устройства выполняется за несколько одинаковых циклов вычислений. Рассмотрим первый цикл вычислений. Импульсы с третьего выхода делителя 24 частоты поступают через открытый элемент И 44, элемент ИЛИ 50 и открытый элемент И 41 по шестому выходу блока 18 управления на счетный вход счетчика 8 адреса, задавая последовательно адреса кодов в ОЗУ 6. Списывание кодов vq осуществляется теми же импульсами с выхода элемента И 41, которые подаются через открытый элемент И 39 и элемент 55 задержки по восьмому выходу блока 18 управления на вход списывания ОЗУ 6. Кеды vq с выхода ОЗУ 6 через селектор-демультиплек- сор 10 и селектор-мультиплексор 14 поступают на вход цифрового рекурсивного фильтра 15 и на первый информационный вход блока 16 вычислений. Работа цифрового рекурсивного фильтра 15 синхронизируется импульсами, поступающими на него по двенадцатому выходу блока 18 управления с четвертого выхода делителя 24 частоты. Частота этих импульсов выбирается исходя из быстродействия цифрового рекурсивного фильтра 15. После завершения вычисления кода V( этот код с выхода фильтра 15 вводится в блок 16 вычислений по его второму информационному входу. Коды vq и

(q 1,N) записываются в ОЗУ блока 16 вычислений. После получения всех N кодов V( на выходе счетчика 20 отсчетов образуется импульс V5 (момент времени ts на фиг. 3, в), который через открытый элемент И 37 поступает на счетные входы триггеров 30 и 33, устанавливая их в единичное состояние. Сигнал высокого уровня с прямого выхода триггера 30 подается через элементы ИЛИ 47 и 48 на R-вход триггера 28 и на S-вход триггера 29. Триггер 28 устанавливается в нулевое состояние, закрывая элемент И 41, з триггер 29 переключается в единичное состояние, открывая элемент 42. Тем самым устройство переводится в режим вычисления КОДОВ СОфд .

В этом режиме импульсы с третьего выхода делителя 24 частоты поступают через открытый элемент И 44, элемент ИЛИ 50 и открытый элемент И 42 по седьмому выходу блока 18 управления на счетный вход счетчика 9 адреса, задавая последовательно коды fUq в ОЗУ 7, Списывание кодов с ОЗУ 7 осуществляется импульсами, поступающими на его вход списывания по девятому выходу блока 18 управления с выхода элемента 57 задержки. Эти же импульсы через элемент 56 задержки, элемент ИЛИ 45 и элемент ИЛИ 51 подаются на вход счетчика 2 0 отсчетов. Коды через селектор-де- мультиплексор 11 и селектор-мультиплексор 14 поступают в цифровой рекурсивный фильтр 15 и в блок 16 вычислений. В цифровом фильтре 15 образуются коды софд, которые с выхода фильтра подаются в блок 16 вычислений. Коды (Dq и utyq записывают- ся в ОЗУ блока 16 вычислений. После получения всех N кодов Щц импульс Vs (момент времени te на фиг. 3, г) с выхода счетчика 20 отсчетов, поступая через открытый элемент И 37 на счетные входы триггеров 30 и 33, устанавливает их в нулевое состояние. Сигнал высокого уровня с инверсного выхода триггера 30 подается через элемент ИЛИ 46 на S-вход триггера 28 и через элемент ИЛИ 49 на R-вход триггера 29. Триггер 28 устанавливается в единичное состояние, открывая элемент И 41, а триггер 29 устанавливается в нулевое состояние, закрывая элемент И 42. Тем самым устройство снова переводится в режим вычисления величин уфр при новом значении опорной частоты ш .

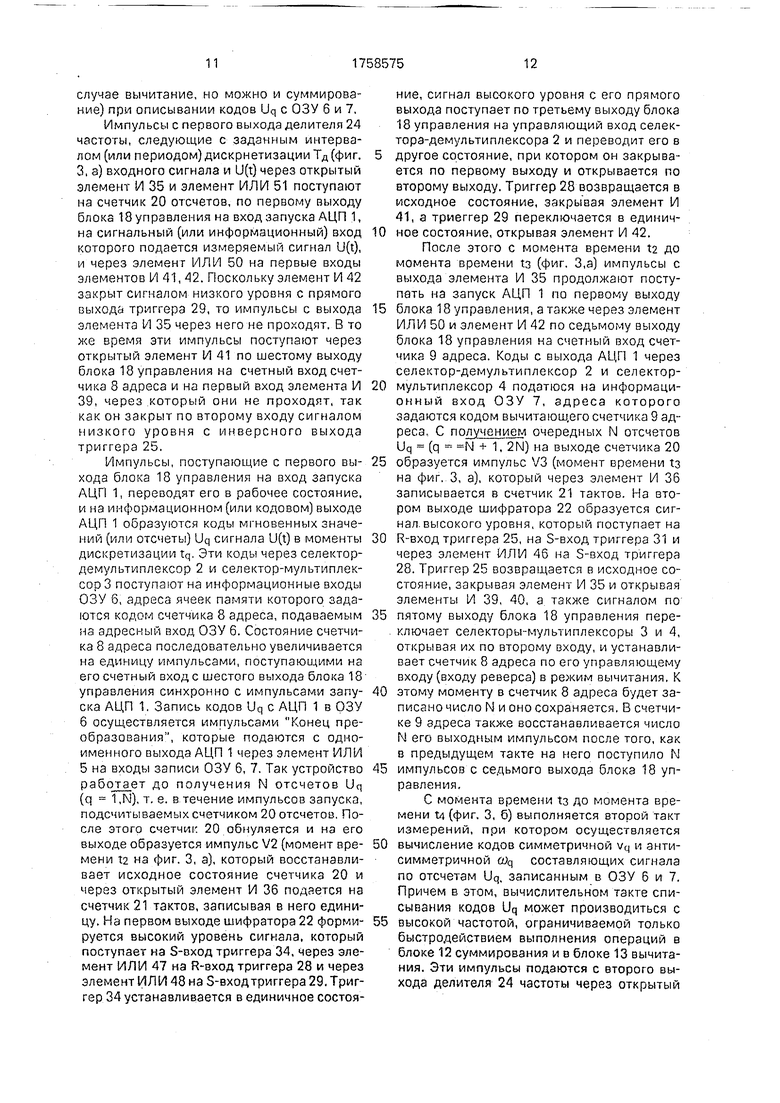

Однако сам процесс вычисления новых величин УФЧ и (УфЧ задерживается на время вычисления функционала а по формуле (1) в блоке 16 вычислений. Это обеспечивается тем, что сигналом высокого уровня с инверсного выхода триггера 33, поступаю0

5

0

5

0

5

0

5

0

5

щим на R-вход триггера 32, последний устанавливается в нулевое состояние и закрывает элемент И 44, прекращая поступление тактовых импульсов на списывание кодов vq . В то же время сигнал высокого уровня с инверсного выхода триггера 33 поступает по второму выходу блока 18 управления в блок 16 вычислений, переводя его в режим вычислений.

Блок 16 вычислений приступает к цифровой обработке введенного в него массива данных в следующем порядке: вычисляет величины /li и Я2 по формулам (4)(5); опреОО

деляет величины vЈ и vf по формулам (20), (22); вычисляет функцию т по формуле (1).

После завершения процесса вычислений в блоке 16 вычислений в нем задается новое значение частоты сл, а его выходной сигнал V7 (момент времени п на фиг. 3, д) подается на входы цифрового рекурсивного фильтра 15 и блока 18 управления, В цифровом рекурсивном фильтре 15 устанавливается значение Aa , а в блоке 18 управления сигнал через элемент ИЛИ 52 поступает на S-вход триггера 32, переводя его в единичное состояние и открывая элемент И 44. После этого полностью повторяется цикл вычислений величин уфд и шфц (фиг, 3, в, г), а затем функции . Аналогично выполняются последующие циклы вычислений для других значений частотьшдо получения условия Г(со0) макс при некотором значении частоты (Do которое принимается за результат измерения.

После этого в блоке 16 вычислений как и в прототипе, определяется амплитуда и фаза сигнала по формулам (6), (7),

Таким образом, использование изобретения при построении цифровых приборов для измерения характеристик синусоидального сигнала позволяет повысить точность и уменьшить время измерения.

Формула изобретения

1, Устройство для измерения характеристик синусоидального сигнала, содержащее аналого-цифровой преобразователь, последовательно соединенные первый счетчик адреса и первое оперативное запоминающее устройство, блок вычислений, блок управления, блок индикации и элемент ИЛИ, причем первый вход аналого-цифрового преобразователя соединен с входом устройства, а второй вход - с первым выходом блока управления, второй выход которого подключен к управляющему входу блока вычислений, выход блока вычислений соединен с входом блока индикации, отличающееся тем, что, с целью повышения точности и быстродействия измерений, в

него введены второй счетчик адреса, второе оперативное запоминающее устройство, три селектора-мультиплексора, три селекто- ра-демультиплексора. цифровой рекурсивный фильтр, блок суммирования и блок вычитания, причем первый выход аналого- цифрового преобразователя соединен с ин- формационным входом первого селектора-демультиплексора, управляющий вход которого соединен с третьим вы- ходом блока управления, второй выход аналого-цифрового преобразователя соединен с первым входом элемента ИЛИ, второй вход которого соединен с четвертым выходом блока управления, первый и второй вы- ходы первого селектора-демультиплексора соединены соответственно с первыми информационными входами первого и второго селекторов-мультиплексоров, второй информационный вход первого селектора- мультиплексора соединен с выходом блока суммирования, второй информационный вход второго селектора-мультиплексора - с выходом блока вычитания, управляющие входы первого и второго селекторов-мульть- иплексоров и управляющий вход первою счетчика адреса объединены и соединены с пятым выходом блока управления, шестой выход которого соединен со счетным входом первого счетчика адреса, а седьмой вы- ход - со счетным входом второго счетчика адреса, выходы первого и второго селекторов-мультиплексоров соединены соответственно с информационным входами первого и второго оперативных запоминающих уст- ройств, первые управляющие входы которых объединены и соединены с выходом элемента ИЛИ, вторые управляющие входы первого и второго оперативных запоминающих устройств соединены соответственно с восьмым и девятым выходами блока управления, а их выходы соединены соответственно с информационными входами второго и третьего селекторов-демультип- лексоров, управляющие входы которых объ- единены и соединены с десятым выходом блока управления, первые выходы второго и третьего селектора-демультиплекасоров соединены с входами блока суммирования и блока вычитания, вторые выходы которых соединены с первым и вторым информационными входами третьего селектора-мультиплексора, управляющий вход которого соединен с одиннадцатым выходом блока управления, выход соединен с первыми ин- формационными входами блока вычислений и цифрового рекурсивного фильтра, первый управляющий вход которого соединен с двенадцатым выходом блока управле- ния, второй управляющий вход - с

управляющим выходом блока вычислений и входом блока управления выход цифрового рекурсивного фильтра соединен с вторым информационным вхолом i .числе кий, а выход второю счетчика адреса соединен с адресным входом второго оперативного запоминающего устройства. 2. Устройство по п. 1, отличающее- с я тем, что блок управления содержит схему пуска, счетчик отсчетов, счетчик тактов, шифратор, генератор импульсов, делитель частоты, десять триггеров, десять элементов И, восемь элементов ИЛИ. пять элементов задержки, причем выход схемы пуска соединен с шиной сброса и через первый элемент задержки с S-входом первого триггера, прямой выход которого соединен с первым входом первого элемента И, второй вход которого соединен с первым выходом делителя частоты, а его выход соединен с первым выходом блока управления и первым входом шестого и седьмого элементов ИЛИ, выход седьмого элемента ИЛИ соединен с входом счетчика отсчетов, выход которого соединен с первыми входами второго и третьего элементов И, второй второго элемента И соединен с инверсным выходом второго триггера, прямой выход которого соединен с вторым входом третьего элемента И, выход второго элемента И соединен с входом счетчика тактов, кодовый выход которого соединен с кодовым входом шифратора, первый выход которого соединен с S-входом десятого триггера и первыми входами третьего и четвертого элементов ИЛИ, второй выход шифратора соединен с R-вхо- дом первого триггера, первым входом второго элемента ИЛИ и S-входом седьмого триггера, третий выход шифратора соединен с S-входом второго триггера, R-входами третьего и седьмого триггеров и первыми входами пятого и восьмого элемента ИЛИ, второй вход которого соединен с входом блока управления, а выход - с S-входом восьмого триггера, R-вход которого соединен с прямым выходом девятого триггера и вторым выходом блока управления, третий выход которого соединен с прямым выходом десятого триггера, четвертый выход блока управления через четвертый элемент И соединен с прямым выходом третьего триггера, а пятый выход соединен с прямым выходом первого триггера, счетные входы шестого и девятого триггеров соединены с выходом третьего элемента И, прямой выход седьмого триггера соединен с первым входом девятого элемента И, второй вход которого соединен с вторым выходом делителя частоты, а выход - с вторым входом шестого элемента ИЛИ, прямой выход восьмого триггера соединен с первым входом десятого элемента И, второй вход которого соединен с третьим выходом делителя частоты, а выход - с третьим входом шестого элемента ИЛИ, выход которого соединен с первыми входами седьмого и восьмого элементов И, прямой выход шестого триггера соединен с вторыми входами третьего и четвертого элементов ИЛИ, а инверсный выход - с вторыми входами второго и пятого элементов ИЛИ, выходы второго и третьего элементов ИЛИ соединены соответственно, с S- и R-входом четвертого триггера, выходы четвертого и пятого элементов ИЛИ соединен ы соответствен но с S- и R-входом пятого триггера, прямой выход четвертого триггера соединен с вторым входом седьмого элемента И, прямой выход пятого триггера соединен с вторым входом восьмого элемента И, выход седьмого элемента И соединен с первым входом пятого элемента И и шестым выходом блока управления, выход восьмого элемента И соединен с первым входом шестого элемента И и седьмым выходом блока управления, вторые входы пятого и шестого элементов И соединены с инверсным выходом первого триггера, выход пятого элемента И через третий элемент задержки соединен с восьмым выходом блока управления и входом второго элемента задержки, выход шестого элемента И через пятый элемент задержки соединен с девятым выходом блока управления и входом четвертого элемента задержки, выходы второго и четвертого элементов задержки соединены с двумя входами первого.элемента ИЛИ, выход которого соединен с вторым входом чет- вертого элемента И, десятый, одиннадцатый и двенадцатый выходы блока управления соединены соответственно с инверсным выходом второго триггера, с инверсным выходом шестого триггера и четвертым выходом делителя частоты, вход делителя частоты соединен с выходом генератора импульсов, третий вход второго элемента ИЛИ соединен с шиной сброса.

..

Jj-111 . ...

35

V NV2 N V3

J

t4

ФигЗ

t7

| Патент США Ns 4523289, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения характеристик синусоидального сигнала | 1985 |

|

SU1307366A1 |

| кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-08-30—Публикация

1990-04-23—Подача