Область техники, к которой относится изобретение

Многие компьютерные системы образуются из отдельных компонентов, например, интегральных схем (ИС), связанных с материнской платой или другой печатной платой системы. С увеличением производительности обработки и количества блоков обработки, которые могут входить в состав одной ИС, система, образованная из одной ИС, такой как однокристальная система (SoC), может быть включена в различные устройства, такие как мобильные устройства, встроенные системы и т.д.

Для соединения компонентов друг с другом используется некоторый тип схемы межсоединений, и могут быть также предусмотрены один или более маршрутизаторов. В настоящее время многочисленные маршрутизаторы системы являются весьма однородными: различные порты маршрутизатора работают с одной и той же скоростью, как и различные виртуальные каналы (ВК) или другие независимые магистрали порта. В этом состоит несоответствие с фактическими применениями в SoC, где сбалансированный трафик по всем портам и одинаковая критичность по всем виртуальным каналам действительно являются редкими случаями. Однородное построение по всем портам и ВК неизбежно приводит к неоптимальному энергопотреблению в компонентах, где приемлема более низкая скорость, и потерям производительности в компонентах, где критические сообщения имели бы выигрыш от более высокой скорости обработки.

Краткое описание чертежей

Фиг.1 - блок-схема системы, согласно варианту осуществления настоящего изобретения.

Фиг.2 - блок-схема маршрутизатора, согласно варианту осуществления настоящего изобретения.

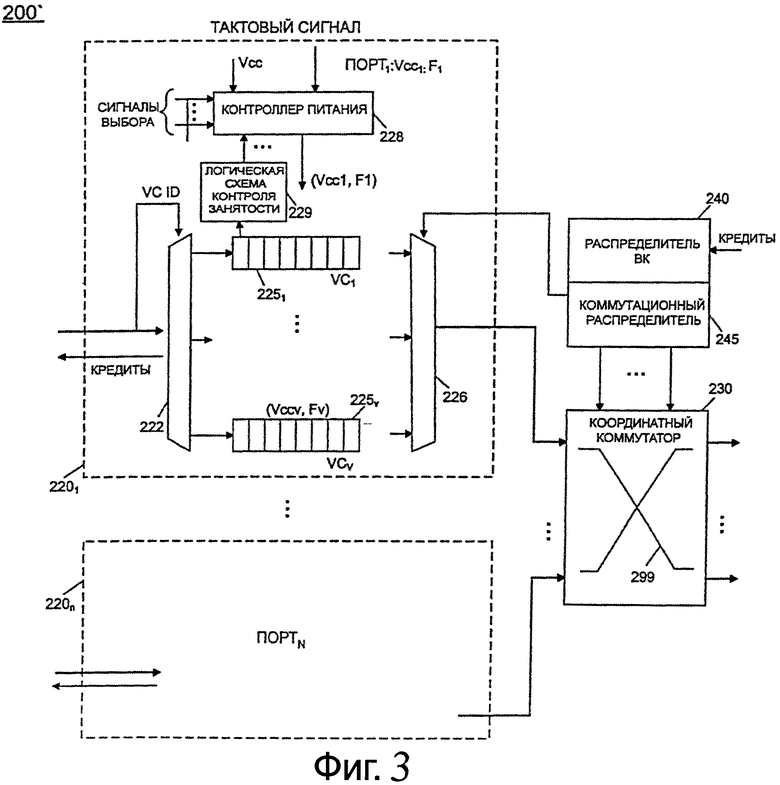

Фиг.3 - блок-схема маршрутизации, согласно другому варианту осуществления настоящего изобретения.

Фиг.4 - блок-схема буфера, использующего управление на пакетной основе, согласно одному варианту осуществления настоящего изобретения.

Подробное описание изобретения

В различных вариантах осуществления можно выполнить гетерогенную микроархитектуру маршрутизатора. На высоком уровне, различные порты маршрутизатора, различные виртуальные каналы порта и/или даже различные пакеты, совместно использующие один виртуальный канал, могут работать при различных тактовых частотах и напряжениях для согласования присущей гетерогенности при обработке элементов и семантике программного обеспечения пакетов. Для реализации гетерогенного управления можно использовать один или более контроллеров питания маршрутизатора с целью обеспечения отдельных пар частота-напряжение для более лучшего использования производительности/питания в каждом порту, канале или пакете.

Варианты осуществления можно использовать в связи с многочисленными различными типами систем. В некоторых реализациях, однокристальная система (SoC), такая как сеть, на кристалле (NoC), могут включать в себя многочисленные ядра, которые связаны через систему межсоединений типа сети. На фиг.1 показана блок-схема системы, согласно варианту осуществления настоящего изобретения. Как показано на фиг.1, система 100 может быть однокристальной системой, включающей в себя множество механизмов обработки 1100.0-110n,m. В различных вариантах осуществления, эти механизмы обработки могут представлять собой ядра, такие как ядра общего назначения с относительно простой очередной микроархитектурой многоядерного процессора. Механизмы обработки могут быть гомогенными (однородными) или гетерогенными (неоднородными) механизмами обработки, имеющими некоторые специализированные функциональные возможности, такие как декодирование, пакетная обработка или другие такие функциональные возможности. Как видно, механизмы 110 обработки связаны с сетевым межсоединением, в котором каждый процессор связан с соответствующим маршрутизатором из множества маршрутизаторов 1200,0-120n,m.

Каждый такой маршрутизатор может включать в себя множество портов, каждый из которых имеет многочисленные виртуальные каналы, которые будут обсуждены в дальнейшем ниже. Этими различными маршрутизаторами можно управлять для того, чтобы иметь различные рабочие параметры, например, разные уровни напряжения и частоты, для реализации различий при связи через маршрутизаторы. Как дополнительно видно на фиг.1, может также присутствовать контроллер 130 памяти.

Как показано в варианте осуществления на фиг.1, благодаря различным типам трафика, перемещающимся в различных направлениях через маршрутизатор, индивидуальными портами маршрутизатора можно управлять независимо для того, чтобы реализовать необходимую производительность обработки в противовес потребляемой мощности. Например, трафик из контроллера 130 памяти в процессор Р1 находится преимущественно в одном направлении, показанном жирными линиями. Этот сценарий представляет собой случай для иерархии памяти с кэш-памятями с обратной записью, где трафик, считанный из оперативной памяти, обычно в несколько раз выше, чем трафик записи в памяти. Например, на маршрутизаторе Р1 порт ввода из контроллера памяти имел бы выигрыш от гораздо более высокой тактовой частоты, чем ввод из маршрутизатора 1202,1.

К тому же определенные типы пакетов в кэш-когерентной системе можно категоризировать для изменения уровней критичностей. Когда пакеты отображаются в виртуальные каналы с использованием их критичностей, может быть квазиоптимальным построением “один тактовый импульс для всех пакетов”. В представленной ниже таблице 1, показаны три уровня критичности для пакетов в одном протоколе связи. Как видно, типы сообщения в кэш-когерентных микропроцессорах имеют различные свойства критичности по отношению к производительности приложения. В примере, представленном в таблице 1, три уровня критичности пакета могут быть основаны на содержании пакетов. В общем, большинство критических пакетов представляют собой такие пакеты, которые относятся к типам сообщений о когерентности кэш-памятей, включающим в себя различные ответы (Rsp), пакеты слежения (Snp) и подтверждение конфликта (AckCnflt). В свою очередь, пакеты со средней критичностью относятся к другим ответам, которые направляют данные, определенный запрос считывания (Rd) и сообщения о недействительности данных (Inv). Наконец, сообщения о типах запросов на обратную запись (Wb) могут иметь самый низкий приоритет. Например, задержка пакета RspI обычно увеличивает время ожидания удачного обращения к кэш-памяти, хотя задержка WbMtoI является часто вредной.

На фиг.2 показана блок-схема маршрутизатора, согласно варианту осуществления настоящего изобретения. Как показано на фиг.2, маршрутизатор 200 может соответствовать одному из маршрутизаторов SoC, которые показаны на фиг.1.

Маршрутизатор 200 включает в себя множество портов 2201-220n, каждый из которых может включать в себя многочисленные независимые буферы. Управление тем, в какой порт подается входящий пакет, может осуществляться через координатный коммутатор или другую логическую схему коммутации другого маршрутизатора или другого агента, связанного с маршрутизатором. В частности, как показано на фиг.2, каждый порт 220 может включать в себя множество буферов 225 (например, буферы обратного магазинного типа (FIFO)), каждый из которых связан с различным виртуальным каналом. Следует отметить, что хотя порты, показанные на фиг.2, расположены в одном направлении, то есть слева направо, маршрутизатор может включать в себя многочисленные порты, имеющие различные направления.

Как видно, поступающие данные вводятся в буфер через входной мультиплексор 222 порта, в котором маршрутизируется поступающий пакет. Входной мультиплексор 222 может выбрать из своих входных сигналов выходной сигнал, который будет подаваться в соответствующий буфер, на основании идентификатора виртуального канала поступающего пакета. Подобным образом, выходы буферов 225 связаны с выходным мультиплексором 226, которым можно управлять с помощью распределителя 240 виртуальных каналов. Как видно, поступающие кредиты подаются в распределитель 240 виртуальных каналов, например, из других маршрутизаторов, с которыми связан маршрутизатор 200. Затем, данный буфер виртуального канала может иметь свои выходные сигналы, выбираемые в случае, когда он имеет доступный кредит. Коммутационный распределитель 245 может выбирать из своих различных входных сигналов пакет для передачи в заданный порт другого маршрутизатора. В некоторых вариантах осуществления эти распределители можно объединить в одну логическую схему или контроллер. Различные алгоритмы маршрутизатора можно использовать при создании этого определения. Например, в случае маршрутизации источника, источник пакета специфицирует весь маршрут таким образом, чтобы коммутационный распределитель мог анализировать информацию о маршруте, включенную в пакет. Другой тип алгоритма маршрутизации может представлять собой динамическую маршрутизацию, в которой пакет не имеет полного маршрута, но вместо этого включает в себя только идентификатор (ID) узла назначения. В этом случае, коммутационный распределитель может получить доступ к таблице маршрутизации для определения маршрутизации. Подобным образом, маршрутизатор 200 может предоставить кредиты обратно поставщику пакетов. То есть, так как пакет выводится из данного буфера виртуального канала, кредит, соответствующий этому виртуальному каналу, можно доставить обратно в объект, который предоставил пакет маршрутизатору. Выходные сигналы из различных портов можно подать через координатный коммутатор 230 в выбранный объект, с которым связан маршрутизатор, например, другой такой маршрутизатор или механизм обработки, через двунаправленные связи 299 от узла к узлу.

Для независимой регулировки частоты, на которой работают различные порты, можно предусмотреть контроллер 210 питания. Как видно, контроллер 210 питания связан с приемом глобальной тактовой частоты, который может представлять собой сигнал глобальной тактовой частоты, соответствующий рабочей частоте. К тому же, контроллер 210 питания может принимать множество коэффициентов деления, которые можно устанавливать статическим или динамическим образом, как будет описано ниже. В некоторых вариантах осуществления, каждый порт имеет свой собственный коэффициент деления. Контроллер 210 питания дополнительно связан с приемом глобального напряжения, который может представлять собой сигнал глобального напряжения, соответствующий рабочему напряжению для SoC. Соответственно, на основании принятых коэффициентов деления и глобальной тактовой частоты и напряжения, контроллер 210 питания может вырабатывать пары сигналов тактовой частоты-напряжения, которые можно подать в каждый из портов. Хотя в варианте осуществления, показанном на фиг.2, используется один контроллер питания из расчета на один маршрутизатор, объем настоящего изобретения не ограничивается этим, и в некоторых вариантах осуществления каждый порт может иметь отдельный контроллер питания.

Таким образом, в варианте осуществления (фиг.2) показан гетерогенный маршрутизатор, в котором можно реализовать управление тактовой частотой - напряжением из расчета на один порт. Выбором пар частота-напряжение для реализации, показанной на фиг.2, можно управлять статическим образом или динамическим образом на основании занятости буферов. В некоторых реализациях, одним или более портами можно управлять статическим образом, хотя одним или более другими портами можно управлять динамическим образом. Статическая реализация может быть основана на априорном знании относительно того, как трафик будет вероятно протекать через маршрутизатор. Например, когда известно, что будет вероятно большой трафик, выходящий из контроллера памяти, по сравнению с входящим в контроллер памяти, портами, которые выводят данные из контроллера памяти, можно управлять так, чтобы работать на более высокой частоте по сравнению с портами, направленными на входы в контроллер памяти.

В одном варианте осуществления, контроллер 210 памяти может выбирать соответствующую пару частота-напряжение для каждого порта на основании информации, полученной из логической схемы 250 контроля занятости буфера. В одной реализации, логическая схема 250 контроля занятости обеспечивает сигналы коэффициентов деления для динамического управления коэффициентом. В другой реализации, программное обеспечение системы устанавливает коэффициент деления, например, на основании априорного знания относительно ожидаемых картин трафика через порт. Более конкретно, в одном варианте осуществления, логическая схема может выполнять сравнение числа входов буфера порта с пороговым значением. Следует отметить, что это сравнение может быть основано на занятости всех буферов порта или только одного или более предопределенных буферов. В данном случае, тактовая частота/ напряжение порта увеличивается в случае, когда число входов буферов, находящихся в использовании, превышает определенный пороговый уровень в порте. И, наоборот, пустой буфер FIFO в течение длительного периода времени может показывать состояние ожидания (обнаруженное с помощью логической схемы контроля занятости), и тактовую частоту/ напряжение можно уменьшать до состояния самой низкой потребляемой мощности в режиме ожидания, что приводит к существенной экономии потребляемой мощности. Управление рабочим периодом позволяет постоянно настраивать маршрутизатор на изменяющиеся запросы трафика, достигая наилучшего компромисса между производительностью и потребляемой мощностью. В статической реализации, следует отметить, что логическая схема 250 может отсутствовать, и сигналами коэффициентов можно управлять статическим образом. В некоторых реализациях, можно использовать комбинацию статического и динамического управления, например, на основании из расчета на порт или из расчета на буфер.

В варианте осуществления фиг.2, степень детализации адаптации тактовой частоты и напряжения представлены из расчета на порт. Таким образом, контроллер питания (и логическую схему контроля занятости) можно сконфигурировать на основании из расчета на порт, или каждый порт можно сконфигурировать для того, чтобы поддерживать связь с единственной конкретизацией этих компонентов. Понятно, что помимо управления питанием на основе порта подобным образом можно управлять связями между портами для осуществления экономии потребляемой мощности. В еще одних вариантах осуществления, гетерогенные маршрутизаторы можно выполнить с управлением из расчета на приоритет напряжения/частоты. То есть в некоторых приложениях вместо управления из расчета на порт может быть управление каждым отдельным буфером порта, например, на основании из расчета приоритета или виртуального канала для чрезвычайно тонкого управления питанием. На фиг.3 показана блок-схема маршрутизатора, согласно другому варианту осуществления настоящего изобретения. Как показано на фиг.3, маршрутизатор 200' можно сконфигурировать подобным образом, как и маршрутизатор, показанный на фиг.2. Однако вместо управления из расчета на порт, каждый отдельный буфер 225 маршрутизатора 200' может иметь свою пару частота-напряжение с отдельным управлением. Чтобы осуществить такое управление, контроллер 228 питания и логическая схема 229 контроля занятостью можно предусмотреть из расчета на один порт и можно подать отдельные сигналы управления тактовой частотой-напряжением в каждый буфер 225 виртуального канала, например, на основании поступающих выбранных сигналов, которые можно подать из статического источника (на фиг.3 не показан) или логической схемы 229 контроля занятостью.

В одной реализации систему можно сконфигурировать таким образом, чтобы каждый виртуальный канал выделялся на основании критичности сообщения, такой как статическое выделение, в котором первый виртуальный канал связан с большинством критических пакетов, второй виртуальный канал связан со следующими критическими пакетами и т.д. В таких реализациях, первый буфер виртуального канала может работать на более высоких скоростях, чем другие буферы виртуальных каналов. В еще одной реализации, включающей в себя виртуальные каналы на основе критичности, можно реализовать динамическое управление путем управления набором буферов порта таким образом, чтобы, когда поток данных проходит через виртуальный канал с самым высоким приоритетом (который связан с одним буфером) в другие каналы (и их связанные буферы), можно было отключить или перевести в состояние ожидания с низкой потребляемой мощностью, делая возможным управление с учетом рабочей нагрузки. Чтобы осуществить это управление, каждый пакет может включать в себя рекомендацию относительно качества обслуживания (QoS), такую как битовое поле, для того, чтобы показать приоритет пакета. Буфером можно управлять таким образом, чтобы после приема пакета с самым высоким приоритетом использовалась высокая частота для управления пакетом через буфер, и после приема пакета с низким приоритетом, управление ресурсами буфера выполнялось с более низкой частотой. Предполагается, что система, в которой первый виртуальный канал (ВК0) активно вводят/выводят флиты пакетов с самым высоким приоритетом, оставшиеся каналы/буферы, например, BK1-BKV, можно переводить в состояния с низкой потребляемой мощностью. Таким образом, в этом варианте осуществления, основанием для адаптации тактового сигнала и напряжения является приоритет сообщения.

Адаптацию тактовой частоты и напряжения можно выполнить различными способами. Для высокопроизводительной многоядерной архитектуры можно использовать решение относительно периода проектирования, которое является прозрачным с точки зрения программного обеспечения. Для SoC, которые содержат многочисленные блоки интеллектуальной собственности (IP) с требованиями к QoS, можно использовать механизм динамического управления периодом работы, основанный на рекомендациях, предусмотренных программным обеспечением. Например, транзакцию прямого доступа к памяти (DMA) с низким приоритетом можно использовать по низковольтному, с малым электропотреблением пути по всем маршрутизаторам между модулями памяти.

В еще одних вариантах осуществления, можно реализовать даже еще более тонкое управление. Как показано на фиг.4, управление можно выполнить на пакетной основе, например, согласно приоритету самого пакета. Этот приоритет может отличаться от приоритета, приписываемого виртуальному каналу, или от других таких идентификаторов. В различных вариантах осуществления, каждый блок управления потоком (например, так называемый флит) может иметь в заголовке (например, в заголовке пакета) блока индикатор своего приоритета. На основании этой информации, пакеты, которые совместно используют буфер, можно обрабатывать с различными скоростями. В частности, как показано в варианте осуществления на фиг.4, буфер 320 включает в себя первый участок 320а и второй участок 320b, каждым из которых можно управлять с различной скоростью на основании сигналов управления, полученных, например, через контроллер 310 питания. Как видно, контроллер 310 питания может принимать сигналы глобальной тактовой частоты и напряжения и коэффициенты деления, которые можно установить посредством информации, которая присутствует в поле заголовка пакета. На основании этой информации, контроллер 310 питания может выработать тактовые сигналы записи и тактовые сигналы считывания для записи данных в конкретный участок буфера 320 и считывания данных из него. Хотя в варианте осуществления на фиг.4 показана конкретная реализация, понятно, что можно реализовать другие реализации для обеспечения тонкого управления напряжением/частотой. В качестве одного примера можно реализовать управление мощностью в маршрутизаторе, который работает при синхронизации с известными состояниями питания процессора (например, так называемые состояния Р или С спецификации усовершенствованного интерфейса управления конфигурированием и энергопотреблением (ACPI)). В данном случае, локальный маршрутизатор и буферы (на этом порту), подсоединенные к процессору, могут также находиться в режиме пониженного энергопотребления (или переводиться в режим номинального электропотребления) на основании режима(ов) питания процессора. Кроме того, другие реализации можно применять в маршрутизаторах, подсоединяемых к контроллеру памяти с состояниями, учитывающими особенности питания.

Варианты осуществления можно реализовать в виде кода и можно сохранить на носителе информации, имеющем сохраненные на нем инструкции, которые можно использовать для программирования системы для того, чтобы выполнить эти инструкции. Носитель информации может включать в себя, но не ограничивается, любой тип диска, включающий в себя гибкие диски, оптические диски, твердотельные диски (SSD), компактные оптические диски (CD-ROM), перезаписываемые компакт-диски (CD-RW) и магнитооптические диски, полупроводниковые устройства, такие как постоянные запоминающие устройства (ПЗУ), оперативные запоминающие устройства (ОЗУ), такие как динамические ОЗУ (DRAM), статические ОЗУ, такие как (SRAM), стираемые перепрограммируемые ПЗУ (EPROM), флэш-памяти, электрически-стираемые программируемые ПЗУ (EEPROM), магнитные или оптические карты или любой другой тип носителя, подходящий для хранения электронных инструкций.

Хотя настоящее изобретение было описано по отношению к ограниченному числу вариантов осуществления, специалистам в данной области техники будут очевидны многочисленные модификации и их изменения. Подразумевается, что прилагаемая формула изобретения охватывает все такие модификации и изменения, которые подпадают под истинные сущность и объем этого настоящего изобретения.

Изобретение относится к устройствам обработки информации. Технический результат заключается в оптимизации производительности и питания в каждом порту маршрутизатора. Технический результат достигается тем, что сравнивают уровень занятости буфера порта маршрутизатора с пороговым значением, и управляют портом так, чтобы он функционировал при первом напряжении и частоте, на основании, по меньшей мере частично, указанного сравнения, и управляют по меньшей мере одним другим портом маршрутизатора так, чтобы он функционировал при втором напряжении и частоте. 3 н. и 16 з.п. ф-лы, 1 табл., 4 ил.

1. Способ управления маршрутизатором, содержащий этапы, на которых:

определяют уровень занятости первого буфера, причем указанный первый буфер первого порта маршрутизатора связан с множеством маршрутизаторов и по меньшей мере с одним процессором, причем первый порт включает в себя множество буферов, включающих в себя первый буфер, а маршрутизатор включает в себя множество портов, каждый из которых включает в себя множество буферов;

сравнивают уровень занятости первого буфера с первым пороговым значением; и

управляют первым портом так, чтобы он функционировал при первом напряжении и частоте, на основании, по меньшей мере частично, указанного сравнения, при этом управляют по меньшей мере одним другим портом из указанного множества портов маршрутизатора так, чтобы он функционировал при втором напряжении и частоте, причем каждый из множества портов обладает отдельным управлением напряжением и частотой.

2. Способ по п.1, дополнительно содержащий этап, на котором динамически управляют первым портом так, чтобы он функционировал при другом напряжении и частоте, на основании изменения уровня занятости.

3. Способ по п.1, дополнительно содержащий этап, на котором статически управляют вторым портом маршрутизатора так, чтобы он функционировал при втором напряжении и частоте, причем указанное статическое управление основано на априорном знании характера трафика, ожидаемого через маршрутизатор.

4. Способ по п.1, дополнительно содержащий этап, на котором маршрутизируют первый пакет в первый буфер на основании идентификатора виртуального канала первого пакета.

5. Способ по п.4, дополнительно содержащий этап, на котором выбирают первый пакет из выходного мультиплексора, связанного с выходом первого буфера, когда доступен кредит, соответствующий первому буферу, и маршрутизируют первый пакет в заданный порт второго маршрутизатора.

6. Способ по п.1, дополнительно содержащий этап, на котором переводят по меньшей мере, один другой буфер и входные/выходные линии связи первого порта в состояние с низким энергопотреблением, когда первый буфер содержит по меньшей мере один пакет данных.

7. Способ по п.1, дополнительно содержащий этапы, на которых:

сравнивают уровень занятости множества буферов первого порта с указанным первым пороговым значением; и

управляют множеством буферов так, чтобы они функционировали при первом напряжении и частоте, на основании по меньшей мере частично указанного сравнения.

8. Способ по п.1, дополнительно содержащий этап, на котором управляют каждым из множества буферов первого порта так, чтобы они функционировали при независимом напряжении и частоте, на основании критичности сообщения, связанной с каждым из множества буферов.

9. Устройство управления маршрутизатором, содержащее:

маршрутизатор, имеющий множество портов, каждый из которых включает в себя множество буферов виртуальных каналов, связанных параллельно, между входным мультиплексором и выходным мультиплексором, при этом каждый из множества портов подлежит управлению по отдельности так, чтобы они функционировали при выбранной паре частота-напряжение, на основе, по меньшей мере частично, сравнения уровня занятости первого из множества буферов виртуальных каналов соответствующего порта с пороговым значением, при этом управление по меньшей мере одним другим портом из указанного множества портов осуществляется так, чтобы он функционировал при другом напряжении и частоте.

10. Устройство по п. 9, в котором каждый из множества буферов виртуальных каналов порта подлежит управлению по отдельности так, чтобы функционировать при другой паре частота-напряжение, на попакетной основе.

11. Устройство по п.9, в котором, когда буфер виртуального канала с самым высоким приоритетом первого порта из множества портов содержит по меньшей мере один пакет, другие буферы виртуальных каналов первого порта помещены в состояние с низким энергопотреблением, при этом каждый из буферов виртуальных каналов связан с уровнем приоритета пакетов, подлежащих хранению в соответствующем буфере виртуального канала.

12. Устройство по п.9, дополнительно содержащее логическую схему контроля занятости, связанную с первым портом из множества портов, для определения уровня занятости первого порта и для сравнения уровня занятости с пороговым значением, при этом указанная выбранная пара частота-напряжение первого порта основана, по меньшей мере частично, на указанном сравнении.

13. Устройство по п.12, дополнительно содержащее контроллер, включающий в себя контроллер тактовой частоты, для приема глобального тактового сигнала и для обеспечения различного тактового сигнала отношения для каждого из множества портов на основании сигнала отношения для каждого из множества портов и глобального тактового сигнала и регулятор напряжения для приема сигнала напряжения и для вывода различного отрегулированного напряжения в каждый из множества портов на основании сигнала отношения и сигнала напряжения.

14. Устройство по п. 13, в котором контроллер выполнен с возможностью приема первого сигнала отношения из первого входного пакета и выработки тактового сигнала записи для сохранения первого входного пакета в первом буфере виртуального канала первого порта, причем тактовый сигнал записи соответствует первому сигналу отношения, принимаемому в заголовке первого входного пакета.

15. Устройство по п. 14, характеризующееся тем, что выполнено с возможностью обработки первого входного пакета и второго входного пакета, содержащихся в первом буфере виртуального канала, с различными скоростями согласно соответствующим сигналам отношения.

16. Устройство по п.9, характеризующееся тем, что выполнено с возможностью статического управления по отдельности множеством портов на основании априорного знания об ожидаемом характере трафика через маршрутизатор.

17. Система управления маршрутизатором, содержащая:

множество механизмов обработки;

по меньшей мере один контроллер памяти; и

множество маршрутизаторов для обеспечения связи механизмов обработки и указанного по меньшей мере одного контроллера памяти через сеть межсоединений, при этом каждый маршрутизатор включает в себя множество портов, каждый из которых имеет множество параллельно связанных буферов между входным мультиплексором и выходным мультиплексором, координатный коммутатор, связанный с выходным мультиплексором, выходную логическую схему выбора, связанную с выходным мультиплексором и координатным коммутатором, для выбора пакета из выходного мультиплексора и порта другого из множества маршрутизаторов для приема пакета, логическую схему контроля занятости, связанную с множеством параллельных буферов, для определения уровня занятости каждого из множества параллельных буферов и для сравнения соответствующего уровня занятости с пороговым значением для выработки результата, и контроллер для приема указанного результата, глобального тактового сигнала и сигнала напряжения и для обеспечения пары частота-напряжение для каждого из множества параллельных буферов на основании, по меньшей мере частично, указанного результата, при этом каждый параллельный буфер выполнен с возможностью функционирования при гетерогенной паре частота-напряжение, а множество механизмов обработки, указанный по меньшей мере один контроллер памяти и множество маршрутизаторов выполнены на одном полупроводниковом кристалле.

18. Система по п.17, характеризующаяся тем, что выполнена с возможностью управлять каждым маршрутизатором так, чтобы он функционировал при гетерогенных парах частота-напряжение, дополнительно на попакетной основе.

19. Система по п. 17, в которой по меньшей мере один порт одного из множества маршрутизаторов выполнен с возможностью функционирования при статических напряжении и частоте, причем статические напряжение и частота основаны на априорном знании характера трафика, ожидаемого через указанный по меньшей мере один порт.

| Колосоуборка | 1923 |

|

SU2009A1 |

| US 7343433 B2, 11.03.2008 | |||

| Колосоуборка | 1923 |

|

SU2009A1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| ОГРАНИЧЕНИЕ ТРАФИКА ДЛЯ СЕТИ С ПЕРЕДАЧЕЙ С УРОВНЯМИ КАЧЕСТВА ОБСЛУЖИВАНИЯ | 2002 |

|

RU2299516C2 |

Авторы

Даты

2015-10-20—Публикация

2011-03-29—Подача