ПРЕДПОСЫЛКИ СОЗДАНИЯ ИЗОБРЕТЕНИЯ

Область техники, к которой относится изобретение

Это изобретение относится к области техники цифровых систем и, в частности, к взаимосвязи различных компонентов при помощи связной инфраструктуры.

Описание известного уровня техники

Цифровые системы обычно включают в себя множество компонентов, которые связаны друг с другом связной инфраструктурой. Эта инфраструктура позволяет обеспечивать связь компонентов друг с другом для осуществления работы цифровой системы. Приведенными в качестве примера цифровыми системами являются, в том числе, компьютеры (например, портативные компьютеры, настольные компьютеры, серверы, рабочие станции и т.д.), мобильные устройства (персональные цифровые информационные устройства, сотовые телефоны, смартфоны и т.д.), специализированные устройства (устройства Глобальной системы определения местоположения (GPS), аудиоплееры и т.д.), устройства, встроенные в другие изделия (например, системы в автомобилях) и т.д.

Сложные системы часто включают в себя множественные связанные друг с другом компоненты с различными требованиями, предъявляемыми к связи, и с потенциально множественными уровнями межсоединений в связной инфраструктуре. Проектирование инфраструктуры для обеспечения поддержки всех компонентов и для достижения заданного уровня функционирования в таких средах является сложным и подверженным ошибкам. Должны приниматься решения, например, в отношении полосы пропускания и скорости различных интерфейсов в инфраструктуре, ширины полосы частот, доступной для различных компонентов, структуры инфраструктуры, буферизации в инфраструктуре и т.д. Часто эти решения должны приниматься при наличии неполной информации о том, какие именно решения являются правильными. В результате, во многих случаях связная инфраструктура либо является спроектированной с чрезмерным запасом (непроизводительное расходование ресурсов), либо спроектированной с недостаточным запасом (невозможность достижения желательных рабочих параметров или даже невозможность реализации функциональных возможностей). В некоторых системах для реализации связной инфраструктуры могут использоваться спроектированные заранее схемы инфраструктуры. Ограничения, обусловленные спроектированными заранее схемами, также могут влиять на способность достижения целевых рабочих параметров всей системы.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

В одном из вариантов осуществления изобретения в связной инфраструктуре могут быть встроены одна или большее количество схем управления инфраструктурой для управления различными аспектами связи, осуществляемой компонентами в системе. В некоторых вариантах осуществления изобретения схемы управления инфраструктурой могут быть включены в состав интерфейса, обеспечивающего сопряжение компонентов со связной инфраструктурой. В альтернативном варианте или в дополнение к этому, в других вариантах осуществления изобретения, которые включают в себя связную инфраструктуру с иерархической структурой, схемы управления инфраструктурой могут быть включены в состав различных уровней иерархии. Схемы управления инфраструктурой могут быть программируемыми и, следовательно, могут обеспечивать возможность настройки параметров связной инфраструктуры так, чтобы она удовлетворяла целевым рабочим параметрам и/или функциональным возможностям.

В различных вариантах осуществления изобретения может использоваться множество схем управления инфраструктурой. Например, могут использоваться схемы управления инфраструктурой, реализующие ограничение по транзакциям. Ограничители инфраструктуры могут ограничивать количество транзакций, ожидающих выполнения, из конкретного источника, или могут ограничивать ширину полосы частот, используемую этим источником, во времени. В некоторых вариантах осуществления изобретения настройка ограничителей внутри связной инфраструктуры может обеспечивать возможность лучшего совместного использования доступной ширины полосы частот связи.

Другим примером являются формирователи трафика записей. В некоторых вариантах осуществления изобретения, когда записи подаются из более узкополосного/более медленного интерфейса в более широкополосный/более быстрый интерфейс, то формирователи трафика могут накапливать данные перед передачей записей через более широкополосный/более быстрый интерфейс во избежание непроизводительного расходования ширины полосы частот в более широкополосном/более быстром интерфейсе. Другим типом формирователя потока трафика записей, который может использоваться в некоторых вариантах осуществления изобретения, является формирователь, предотвращающий передачу одной или большего количества дополнительных записей из источника до тех пор, пока не будут полностью переданы данные из одной или большего количества предыдущих записей. В некоторых вариантах осуществления изобретения такой формирователь может предотвращать захват источником слишком большой полосы частот в течение заданного промежутка времени путем ограничения количества записей, которые были инициированы источником и ожидают поступления данных в инфраструктуре.

В некоторых вариантах осуществления изобретения система может обеспечивать поддержку качества обслуживания (QoS). Может быть предусмотрено наличие различных схем управления инфраструктурой, которые, например, присваивают параметры качества обслуживания (QoS) тем транзакциям, которые не содержат их; переопределяют параметры качества обслуживания (QoS) для определенных транзакций; модифицируют ограничители транзакций на основании более высоких параметров качества обслуживания (QoS) для транзакций из конкретного источника и т.д. В некоторых вариантах осуществления изобретения такие схемы управления инфраструктурой могут улучшать способность системы удовлетворять требованиям, предъявляемым к качеству обслуживания (QoS).

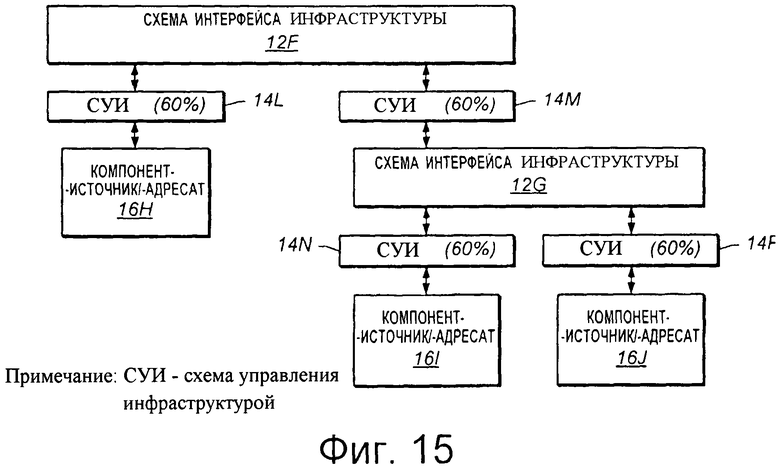

Некоторые варианты осуществления изобретения могут включать в себя связную инфраструктуру с иерархической структурой, в которой транзакции из двух или больше источников объединяются на более высоком уровне в инфраструктуре. На разных уровнях иерархии схемы управления инфраструктурой могут использоваться для управления трафиком на конкретном уровне. Например, схемы управления инфраструктурой могут использоваться с двумя или более компонентами, которые связаны с первой схемой инфраструктуры, которая сама может быть связана со второй схемой инфраструктуры на втором уровне. Могут использоваться дополнительные схемы управления инфраструктурой между схемами инфраструктуры первого и второго уровней. Множество уровней управления инфраструктурой может обеспечивать дополнительную гибкость при настройке связной инфраструктуры.

В различных вариантах осуществления изобретения может быть реализована любая желательная комбинация или субкомбинация вышеописанных признаков.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

В изложенном ниже подробном описании приведены ссылки на сопроводительные чертежи, а здесь приведено их краткое описание.

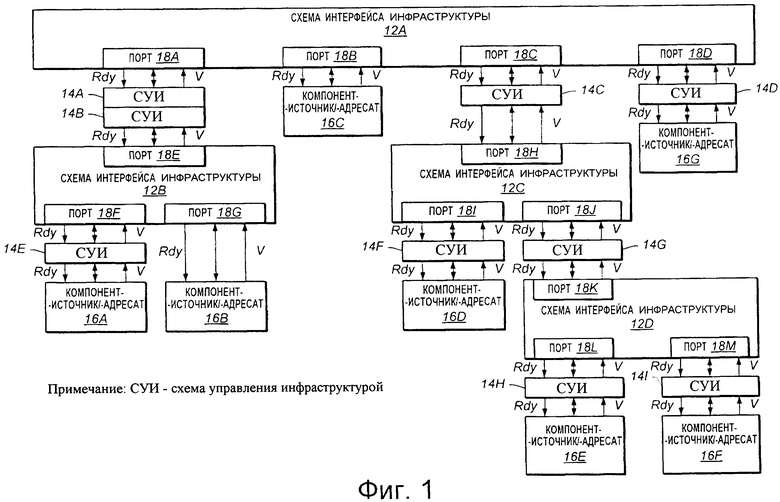

На Фиг. 1 изображена высокоуровневая блок-схема системы, включающей в себя схемы инфраструктуры и схемы управления инфраструктурой.

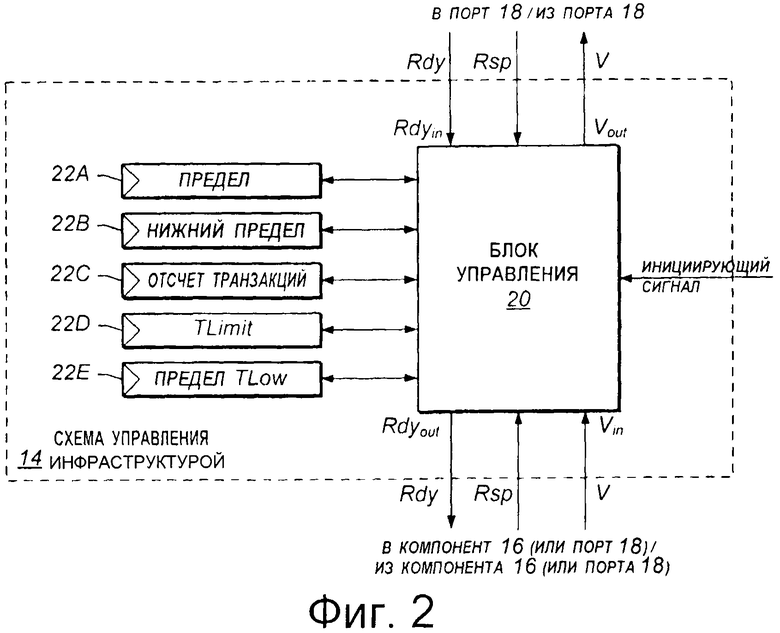

На Фиг. 2 изображена блок-схема одного из вариантов осуществления схемы ограничителя инфраструктуры.

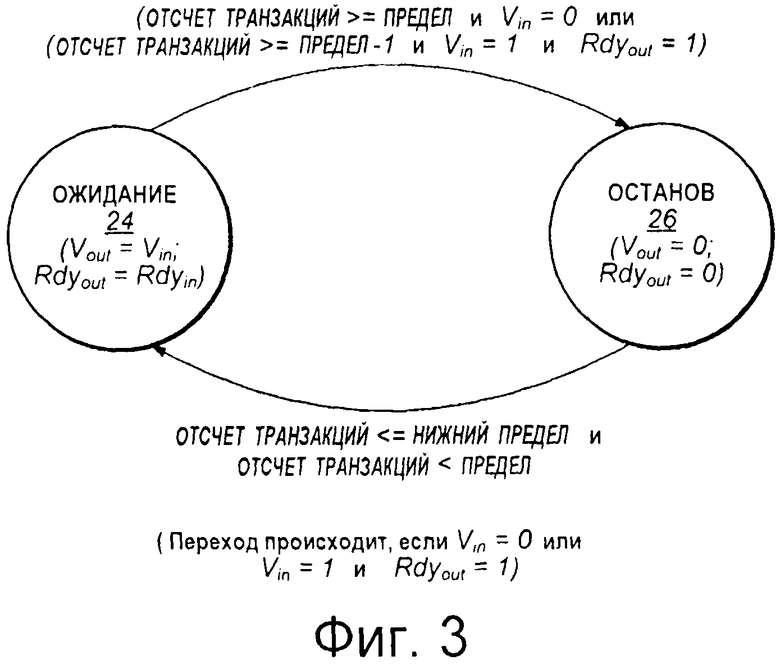

На Фиг. 3 изображен конечный автомат, иллюстрирующий функционирование одного из вариантов осуществления схемы ограничителя инфраструктуры, показанного на чертеже Фиг. 2.

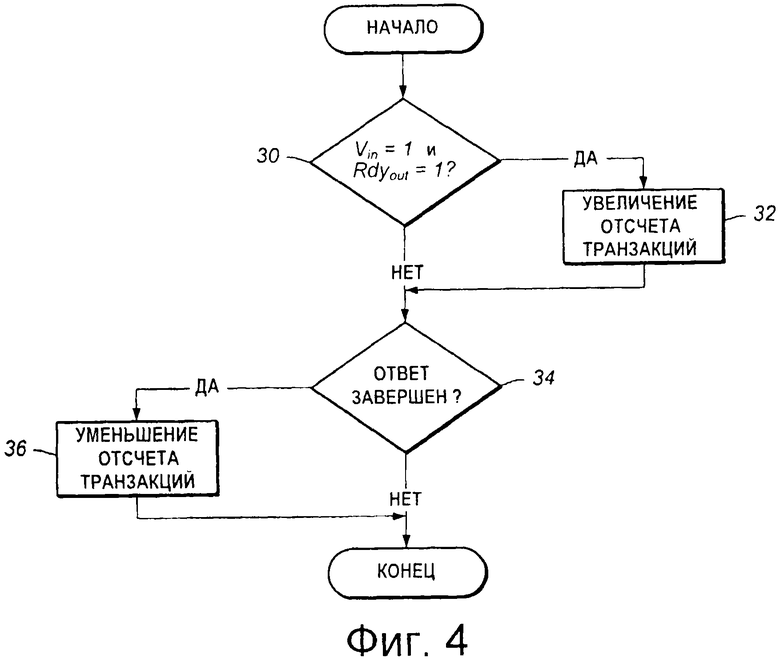

На Фиг. 4 изображена схема последовательности операций, на которой проиллюстрированы дополнительные операции, выполняемые в одном из вариантов осуществления схемы ограничителя инфраструктуры, показанном на чертеже Фиг. 2.

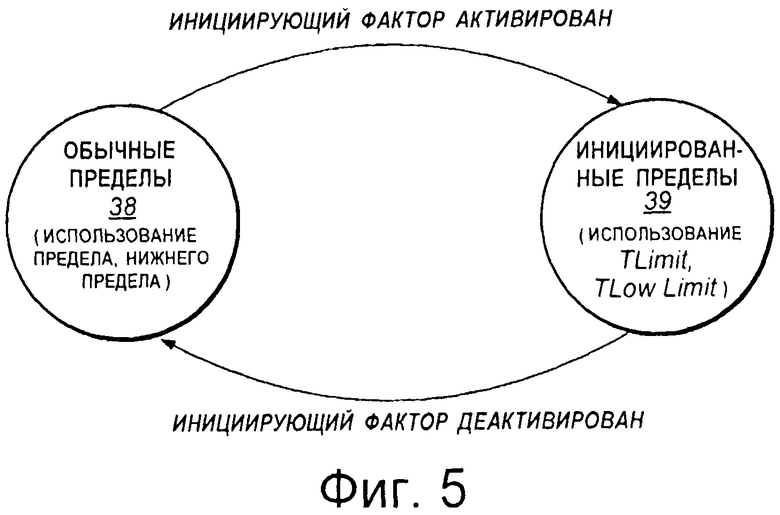

На Фиг. 5 изображен конечный автомат, иллюстрирующий динамическое модифицирование ограничений в одном из вариантов осуществления схемы ограничителя инфраструктуры, показанном на чертеже Фиг. 2.

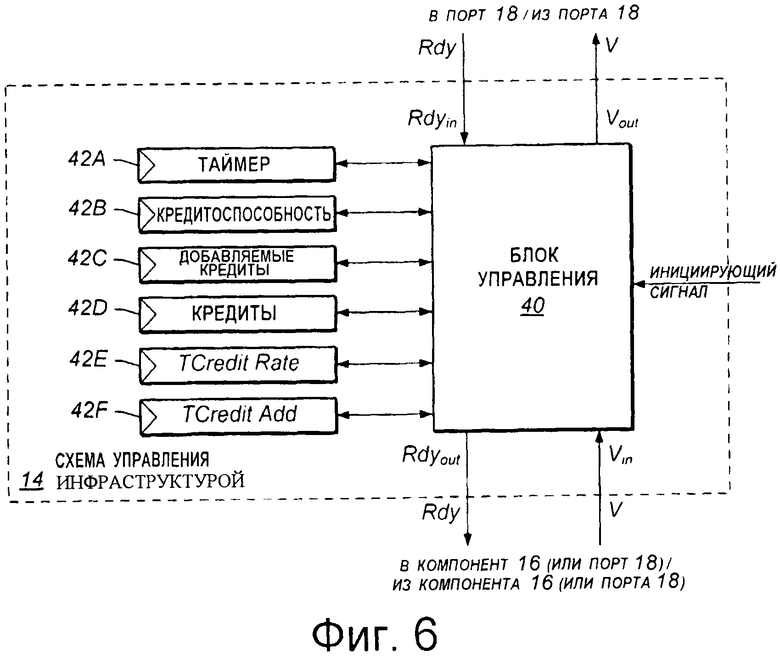

На Фиг. 6 изображена блок-схема другого варианта осуществления схемы ограничителя инфраструктуры.

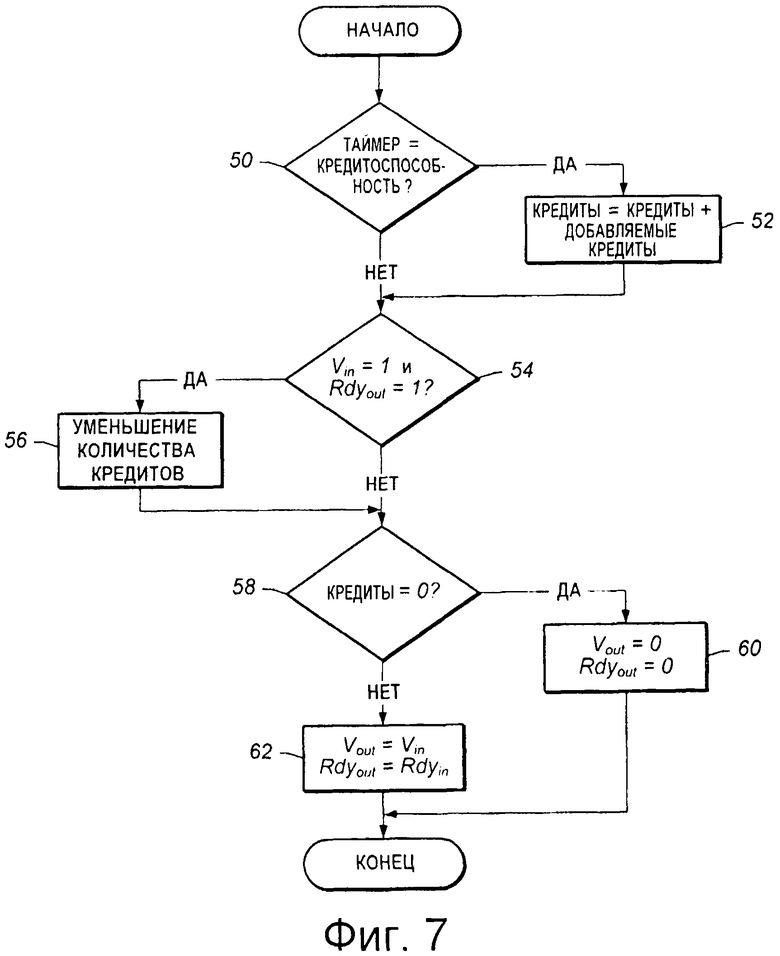

На Фиг. 7 изображена схема последовательности операций, на которой проиллюстрировано функционирование одного из вариантов осуществления схемы ограничителя инфраструктуры, показанного на чертеже Фиг. 6.

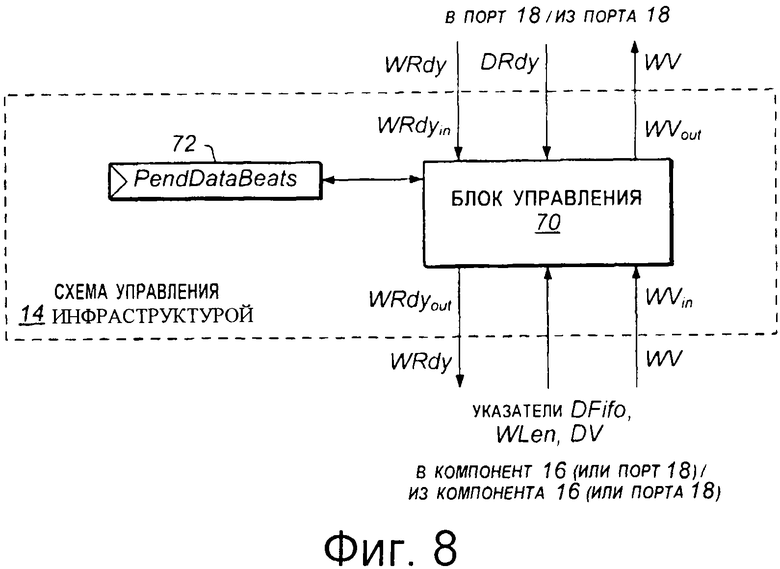

На Фиг. 8 изображена блок-схема одного из вариантов осуществления схемы формирователя трафика записей.

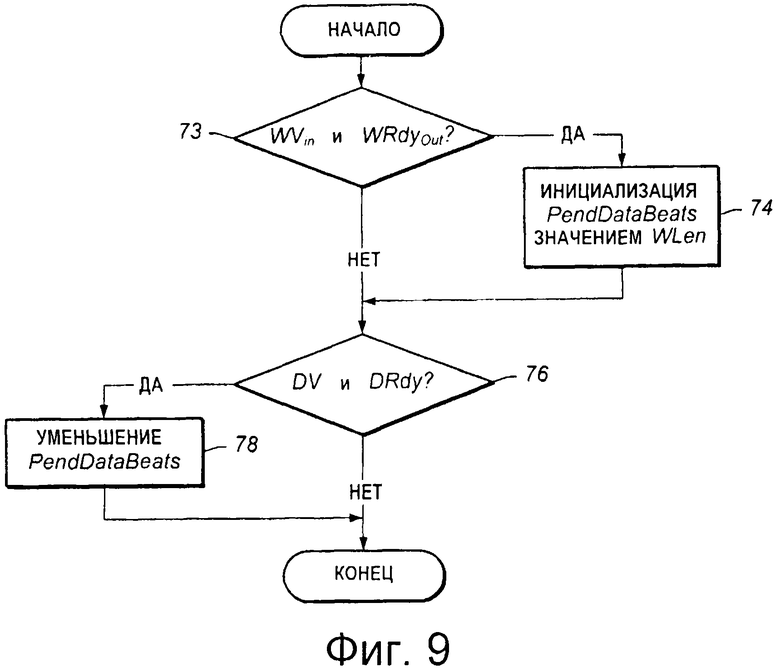

На Фиг. 9 изображена схема последовательности операций, на которой проиллюстрировано функционирование одного из вариантов осуществления схемы формирователя трафика записей, показанного на чертеже Фиг. 8.

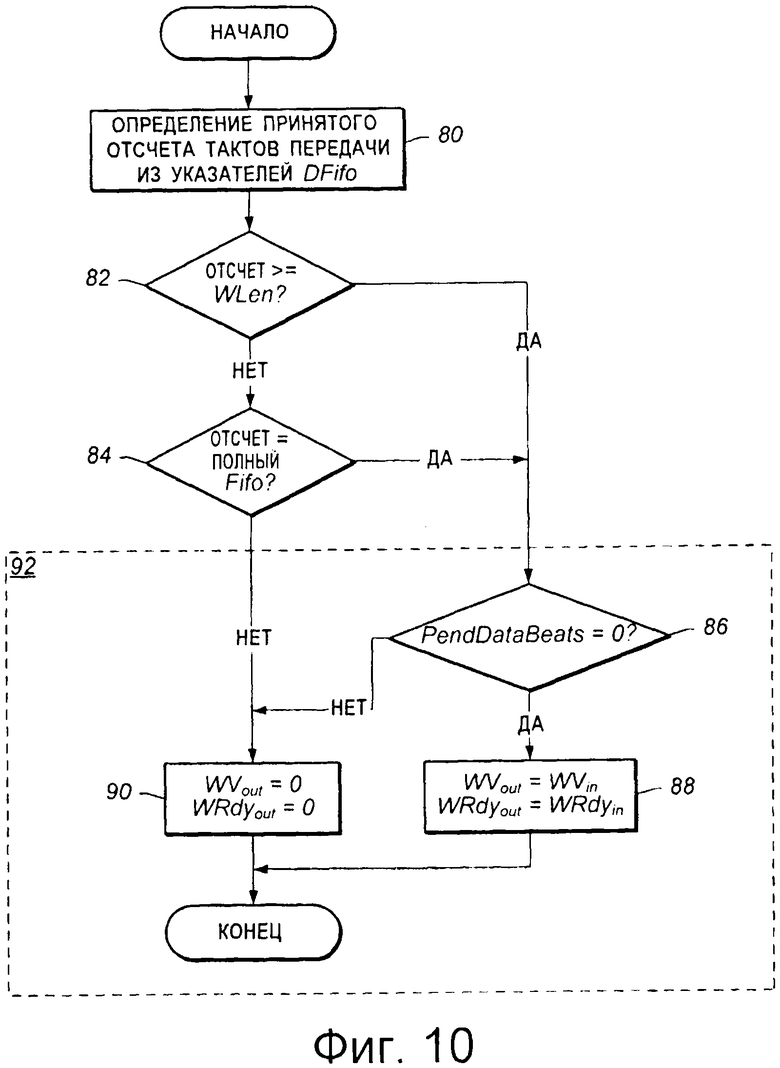

На Фиг. 10 изображена схема последовательности операций, на которой проиллюстрированы дополнительные операции, выполняемые в одном из вариантов осуществления схемы формирователя трафика записей, показанном на чертеже Фиг. 8.

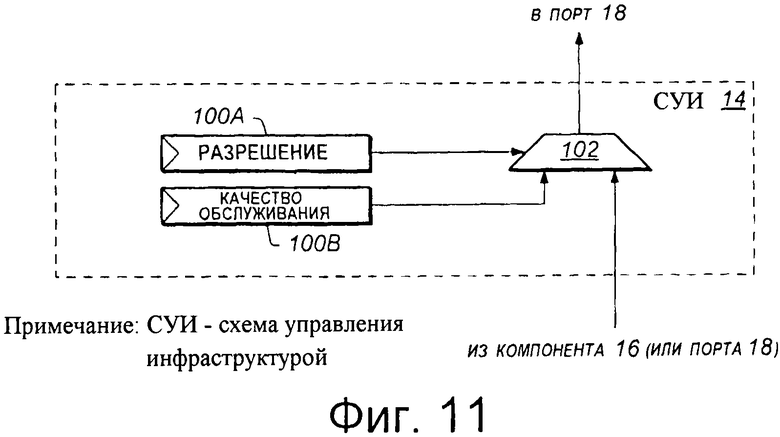

На Фиг. 11 изображена блок-схема одного из вариантов осуществления программируемой схемы управления качеством обслуживания (QoS) в инфраструктуре.

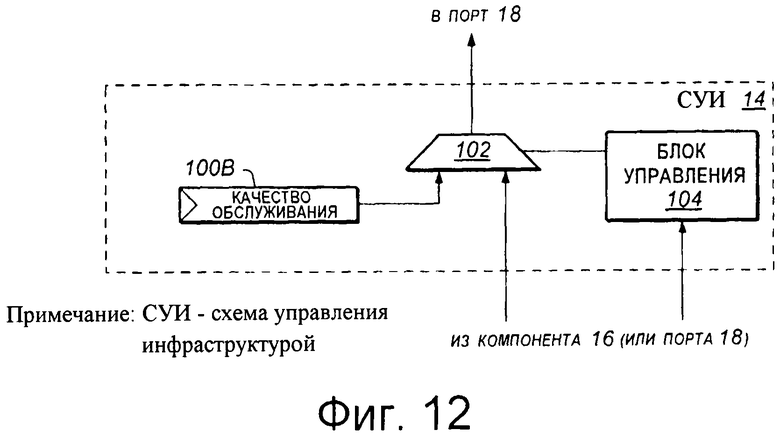

На Фиг. 12 изображена блок-схема одного из вариантов осуществления схемы управления переопределением качества обслуживания (QoS) в инфраструктуре.

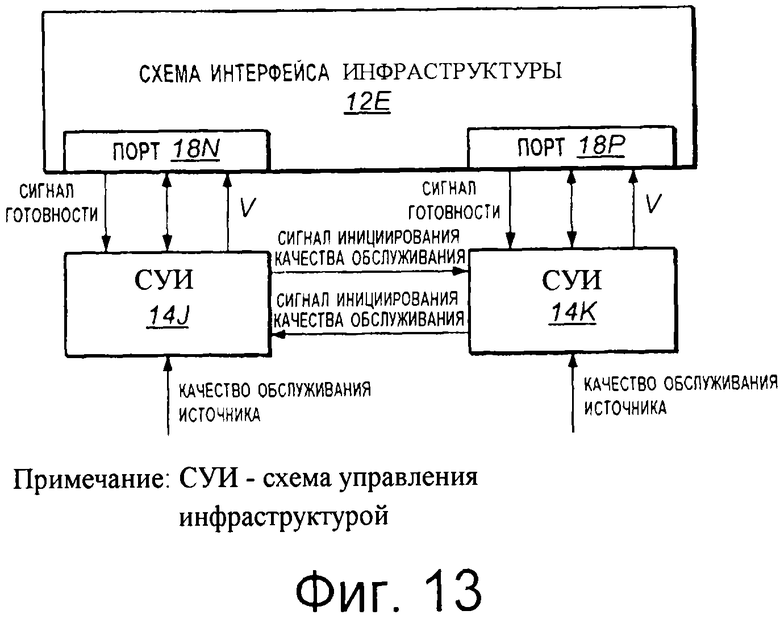

На Фиг. 13 изображена блок-схема, на которой проиллюстрирован один из вариантов осуществления динамического модифицирования параметров схемы управления инфраструктурой в ответ на параметры качества обслуживания (QoS).

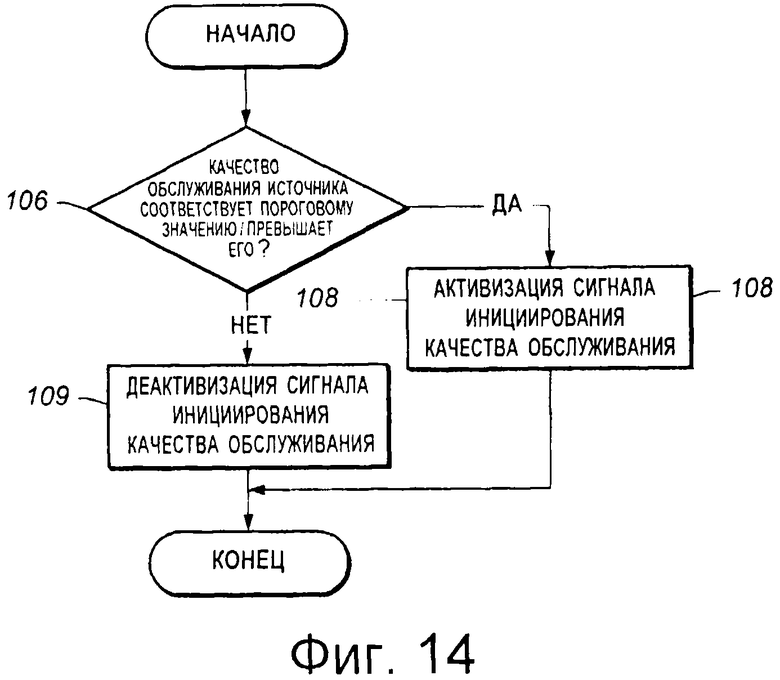

На Фиг. 14 изображена схема последовательности операций, на которой проиллюстрировано функционирование одного из вариантов осуществления схем управления инфраструктурой, показанного на чертеже Фиг. 13.

На Фиг. 15 изображена блок-схема одного из вариантов осуществления схем управления инфраструктурой с иерархической структурой.

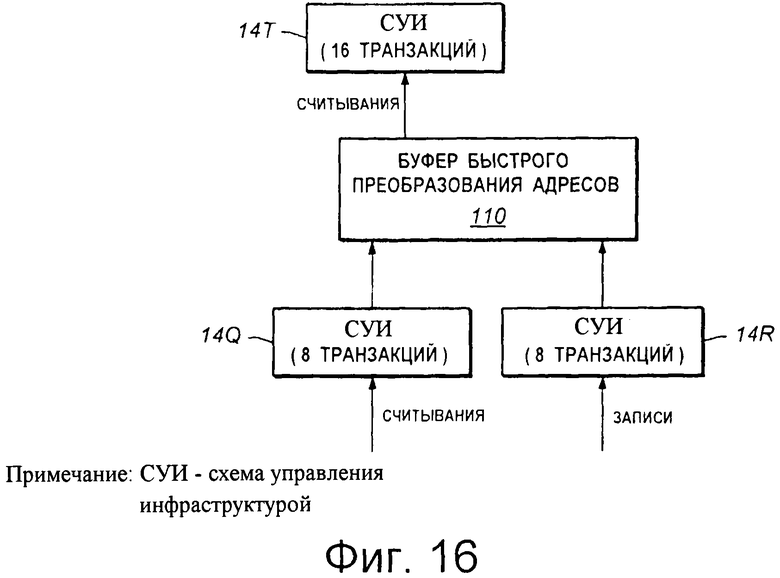

На Фиг. 16 изображена блок-схема одного из вариантов осуществления схем управления инфраструктурой с иерархической структурой для решения проблемы "узких мест".

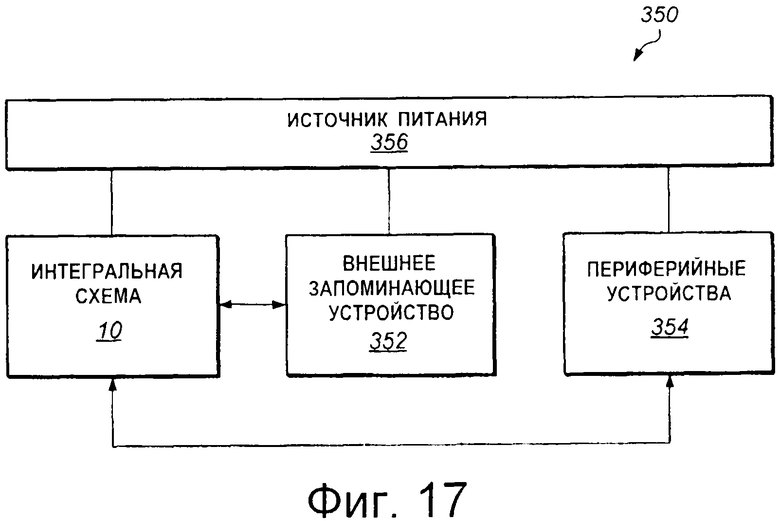

На чертеже Фиг. 17 изображена блок-схема одного из вариантов осуществления системы.

На Фиг. 18 изображена блок-схема одного из вариантов осуществления запоминающей среды, доступ к которой может осуществляться при помощи компьютера.

Несмотря на то, что возможны различные видоизмененные и альтернативные варианты настоящего изобретения, в качестве примера на чертежах показаны конкретные варианты его осуществления, и здесь приведено их подробное описание. Однако, следует понимать следующее: подразумевают, что чертежи и их подробное описание не ограничивают изобретение его конкретным раскрытым вариантом, а, наоборот, подразумевают, что оно охватывает собой все модификации, эквиваленты и альтернативные варианты, не выходящие за пределы сущности и объема настоящего изобретения, определяемого прилагаемой формулой изобретения. Используемые здесь заголовки предназначены только лишь для организационных целей и подразумевают, что они не используются для ограничения объема описания. Используемое во всей этой заявке слово "может" используется в разрешающем смысле (то есть, оно означает "имеющий потенциальную возможность"), а не в обязательном смысле (то есть, когда оно означает "должен"). Аналогичным образом, слова "включать в себя", "включающий в себя" и "включает в себя" означают "включающий в себя что-либо, но не только это".

Различные блоки, схемы или иные компоненты могут быть описаны как "сконфигурированные для" выполнения задачи или задач. В таких контекстах фраза "сконфигурированный для" представляет собой расширенное перечисление структуры, которое обычно означает "имеющий схему, которая" выполняет задачу или задачи во время работы. По существу, блок/схема/компонент могут быть сконфигурированы для выполнения задачи даже тогда, когда блок/схема/компонент не являются включенными в текущий момент времени. В общем, схемы, которые образуют структуру, соответствующую словосочетанию "сконфигурированный для", могут включать в себя аппаратные схемы. Аналогичным образом, для удобства описания различные блоки/схемы/компоненты могут быть описаны как выполняющие задачу или задачи. Такие описания следует интерпретировать как включающие в себя фразу "сконфигурированный для". Подразумевают, что перечисление в явном виде блока/схемы/компонента как сконфигурированного для выполнения одной или большего количества задач не требует применения толкования шестого абзаца § 112 раздела 35 Кодекса законов США для этого блока/схемы/компонента.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Теперь переходя к рассмотрению чертежа Фиг. 1, на нем показана блок-схема одного из вариантов осуществления системы 10. В проиллюстрированном варианте осуществления изобретения система 10 включает в себя множество схем 12A-12D интерфейсов инфраструктуры, множество схем 14A-14I управления инфраструктурой и множество компонентов-источников и/или компонентов-адресатов (src/dest) 16A-16G. Схемы 12A-12D интерфейсов инфраструктуры могут образовывать связную инфраструктуру (или участок связной инфраструктуры) в системе 10, обеспечивая для компонентов 16A-16G возможность связи друг с другом и/или с другими компонентами системы (не показаны). Например, связная инфраструктура может обеспечивать доступ компонентов 16A-16G к запоминающей системе (на чертеже Фиг. 1 не показана). В частности, каждая схема 12A-12D интерфейса инфраструктуры может включать в себя множество портов (например, порты 18A-18M). Могут быть созданы соединения между этими портами и другими портами, и портами и компонентами, для формирования связной инфраструктуры. Схемы 14A-14I управления инфраструктурой могут быть сконфигурированы для управления одним или большим количеством аспектов передачи по связной инфраструктуре. Количество схем 12A-12D интерфейсов инфраструктуры, схем 14A-14I управления инфраструктурой и компонентов 16A-16G может быть различным в различных вариантах осуществления изобретения и может быть большим или меньшим, чем их количество, показанное на чертеже Фиг. 1. Кроме того, компоновка различных схем и компонентов может быть иной, чем показанная на чертеже Фиг. 1.

В проиллюстрированном варианте осуществления изобретения компонент 16A связан со схемой 14E управления инфраструктурой, которая связана с портом 18F схемы 12B интерфейса инфраструктуры. Несмотря на то, что схема 14E управления инфраструктурой показана как связанная со всем интерфейсом компонента 16A и со всем интерфейсом порта 18F, эта связь не обязательно должна быть такой же самой в различных вариантах осуществления изобретения. Например, в некоторых вариантах осуществления схемы 14E управления инфраструктурой она может быть связана с участком интерфейса с компонентом 16A (и с соответствующим участком интерфейса с портом 18F), а остальным участком интерфейса может являться непосредственная связь между компонентом 16A и портом 18F. То есть поток через остальной участок может не проходить через схему 14E управления инфраструктурой. То же самое утверждение также может быть справедливым и для других схем управления инфраструктурой, компонентов и портов в различных вариантах осуществления изобретения. Таким образом, компонент или порт могут быть связаны со схемой управления инфраструктурой и с портом даже несмотря на то, что для удобства схема управления инфраструктурой может быть показана на чертеже как связанная со всем интерфейсом. В одном из вариантов осуществления изобретения участок интерфейса, с которым связаны схемы управления инфраструктурой, может включать в себя один или большее количество управляющих сигналов в интерфейсе. Этот участок может включать в себя вплоть до всех управляющих сигналов в интерфейсе или любое желательное подмножество управляющих сигналов. В этих вариантах осуществления изобретения передачи адресов и данных, теги транзакций и т.д. могут являться частью остального участка интерфейса. Управление участком интерфейса, с которым связана схема управления инфраструктурой, может осуществлять схема управления инфраструктурой. То есть схема управления инфраструктурой может быть сконфигурирована для модифицирования сигналов, вводимых в схему управления инфраструктурой, для генерации соответствующего выходного сигнала из схемы управления инфраструктурой, подаваемого в принимающий порт/компонент. Схема управления инфраструктурой также может быть соединена для приема дополнительного участка интерфейса только лишь для осуществления текущего контроля (то есть схема управления инфраструктурой может не модифицировать дополнительный участок интерфейса). Таким образом, схема управления инфраструктурой может быть сконфигурирована для генерации управляющих сигналов от имени порта/компонента для управления работой интерфейса. То есть схема управления инфраструктурой может перехватывать сигналы и модифицировать их для подачи в приемник.

Некоторые компоненты-источники могут не иметь соответствующих схем управления инфраструктурой. Например, компонент 16B на чертеже Фиг. 1 связан с портом 18G без каких-либо схем управления инфраструктурой. Такие компоненты могут не требовать наличия схем управления инфраструктурой (например, их скорость генерации транзакции может быть достаточно низкой, вследствие чего схемы управления инфраструктурой не являются необходимыми, или компонент может быть выполнен так, что сам ограничивает генерацию его транзакции, вследствие чего внешнее управление не нужно). В альтернативном варианте, в вариантах осуществления изобретения с иерархической структурой, например, в варианте осуществления изобретения, показанном на чертеже Фиг. 1, достаточное управление транзакциями могут обеспечивать схемы управления инфраструктурой на ином уровне иерархии, например, схемы 14A-14B управления инфраструктурой на чертеже Фиг. 1 для компонента 16B.

Схема 12B интерфейса инфраструктуры может быть сконфигурирована так, что направляет транзакции, принятые в портах 18F и 18G, наружу через порт 18E, который может быть связан с интерфейсом, с которым связаны схемы 14A-14B управления инфраструктурой. Схемы 14A-14B управления инфраструктурой дополнительно связаны с портом 18A. Как упомянуто выше, в альтернативном варианте порты 18A и 18E могут быть непосредственно соединенными для остального участка интерфейса, за исключением того участка, с которым могут быть связаны схемы 14A-14B управления инфраструктурой для осуществления желательного управления транзакциями. Аналогичным образом, если один из компонентов 16A-16B или оба эти компонента могут являться адресатом транзакции (или подчиненным устройством), то схема интерфейса инфраструктуры может быть сконфигурирована для направления транзакций, принятых в порту 18E, в один из портов 18F-18G или в оба этих порта.

Аналогичным образом, на чертеже по Фиг. 1: компонент 16C связан с портом 18B, показанным на чертеже Фиг 1; порт 18C связан со схемой 14C управления инфраструктурой и с портом 18H; порт 18D связан со схемой 14D управления инфраструктурой и с компонентом 16G, порт 18H связан со схемой 14F управления инфраструктурой и с компонентом 16D, порт 18I связан со схемой 14G управления инфраструктурой и с портом 18K, порт 18L связан со схемой 14H управления инфраструктурой и с компонентом 16E, а порт 18M связан со схемой 14I управления инфраструктурой и с компонентом 16F.

Как правило, схемы 14A-14I управления инфраструктурой могут быть сконфигурированы для управления одним или большим количеством аспектов передачи транзакции по связной инфраструктуре посредством компонентов 16A-16G и/или портов 18A-18M, с которыми они связаны. Таким образом, схемы 14A-14I управления инфраструктурой могут модифицировать характер поведения трафика в связной инфраструктуре и могут обеспечивать возможность регулирования производительности системы в целом. Ниже приведено более подробное описание различных схем управления инфраструктурой. Кроме того, как проиллюстрировано, например, схемами 14A-14B управления инфраструктурой, в конкретном интерфейсе могут использоваться две или более схем управления инфраструктурой, и они могут функционировать совместно для управления связной инфраструктурой. В тех случаях, когда используются две или более схем управления инфраструктурой, может потребоваться, чтобы конкретная транзакция удовлетворяла условиям, предъявляемым средствами управления для каждой схемы управления инфраструктурой до продвижения этой транзакции. Например, одна схема управления инфраструктурой может ограничивать количество транзакций, ожидающих выполнения, а другая схема управления инфраструктурой может предотвращать выполнение новой операции записи до тех пор, пока не будут переданы данные предыдущей операции записи. Выполнение новой операции записи может предотвращать любая из схем управления инфраструктурой.

Схемы управления инфраструктурой могут быть программируемыми (например, посредством программного обеспечения, выполняющегося в системе 10, или посредством внешнего управляющего сигнала, подаваемого на вход схем управления инфраструктурой). Возможность программирования схем управления инфраструктурой может позволять производить настройку системы. В некоторых вариантах осуществления изобретения схемы управления инфраструктурой могут быть динамически программируемыми во время использования. Таким образом, функционирование схем управления инфраструктурой может быть изменено как рабочая нагрузка при системных изменениях. Другие варианты осуществления изобретения могут быть статически программируемыми (например, во время инициализации или "начальной загрузки" системы).

В одном из вариантов осуществления изобретения управляющие сигналы в интерфейсе включают в себя сигнал достоверности (V на чертеже Фиг. 1) из главного устройства, желающего выдать транзакцию в связную инфраструктуру, и сигнал готовности (Rdy на чертеже Фиг. 1) из подчиненного устройства в интерфейсе. Транзакция может быть инициирована при наличии обоих сигналов: сигнала достоверности и сигнала готовности. Соответственно, в одном из вариантов осуществления изобретения схемы 14A-14I управления инфраструктурой могут быть сконфигурированы для управления выдачей транзакции путем стробирования сигналов достоверности и/или сигналов готовности в интерфейсе. То есть схемы управления инфраструктурой могут модифицировать сигналы достоверности и/или сигналы готовности (например, гарантируя, что эти сигналы деактивированы) для управления выдачей транзакции. Аналогичным образом, сигналы достоверности и сигналы готовности могут быть связаны с интерфейсом передачи данных, и в каждом периоде тактовых импульсов, в котором имеются оба сигнала: сигнал готовности данных и сигнал достоверности данных, может быть передан такт передачи данных. Соответственно, в одном из вариантов осуществления изобретения схемы 14A-14I управления инфраструктурой могут быть сконфигурированы для управления передачей тактов данных в интерфейсе путем стробирования/модифицирования сигналов достоверности данных и/или сигналов готовности данных. Интерфейсы могут быть двунаправленными, где компонент или порт может функционировать как главное устройство для некоторых транзакций и как подчиненное устройство для других транзакций. В одном из вариантов осуществления изобретения в инфраструктуре связи могут иметься отдельные интерфейсы считывания и записи. Схемы 14A-14I управления инфраструктурой могут включать в себя оба варианта: интерфейсы считывания и интерфейсы записи, или некоторые из них могут применяться только для интерфейса считывания или только для интерфейса записи. Некоторые схемы 14A-14I управления инфраструктурой могут функционировать независимо в интерфейсах считывания и записи или могут функционировать совместно в этих интерфейсах.

В других вариантах осуществления изобретения схемы 14A-14I управления инфраструктурой могут быть сконфигурированы для модифицирования одного или большего количества атрибутов транзакции в транзакции. Например, в некоторых вариантах осуществления системы может обеспечиваться поддержка параметров качества обслуживания (QoS) для транзакций. Параметр качества обслуживания (QoS) может задавать уровень качества обслуживания (QoS), который может быть запрошен для транзакции, и уровни качества обслуживания (QoS) могут использоваться в системе для назначения приоритетов для трафика в попытке удовлетворения требованиям к качеству обслуживания (QoS) в системе в целом. Некоторые компоненты не могут быть спроектированы обеспечивающими параметры качества обслуживания (QoS) и могут быть предусмотрены схемы управления инфраструктурой, которые вводят запрограммированный параметр качества обслуживания (QoS) для таких компонентов. Другие схемы управления инфраструктурой могут быть сконфигурированы для переопределения параметров качества обслуживания (QoS), предоставленных компонентами, для определенных транзакций. Другие атрибуты транзакций могут быть модифицированы или вставлены аналогичным образом (например, способность кэширования, когерентность и т.д.).

Как упомянуто выше, схемы 12A-12D интерфейсов связной инфраструктуры могут включать в себя схемы, связывающие интерфейсы в каждом из портов друг с другом для создания связной инфраструктуры. Таким образом, схемы интерфейсов инфраструктуры могут включать в себя, например, буферизацию в каждом порту для приема транзакций, данных транзакций и т.д. и их буферизацию для передачи через другой порт. Схемы интерфейсов инфраструктуры могут дополнительно включать в себя межсоединение между портами, схему для управления межсоединением (например, схему арбитража). В одном из вариантов осуществления изобретения схемы 12A-12D интерфейсов инфраструктуры могут представлять собой заранее спроектированные схемы, купленные разработчиком системы 10 для включения их в состав системы 10. Схема 12A-12D интерфейса инфраструктуры может представлять собой физическую схему или может представлять собой блок, составляющий "интеллектуальную собственность" (IP), который может быть куплен у третьей стороны и включен в состав конструкции интегральной схемы, которая может быть изготовлена так, что включает в себя схемы интерфейсов инфраструктуры наряду с другими схемами. Поскольку схемы интерфейсов инфраструктуры предоставлены третьей стороной, то индивидуальная настройка и модифицирование могут быть ограниченными. Соответственно, схемы 14A-14I управления инфраструктурой могут обеспечивать дополнительную гибкость для настройки рабочих характеристик системы.

Как правило, порт может представлять собой пункт связи в схемах 12A-12D интерфейсов инфраструктуры. То есть порт может включать в себя схемы для связи по одному интерфейсу с одним или с большим количеством источников или адресатов транзакций (например, с компонентами или с другими портами). То есть интерфейс в одном порту может включать в себя полный механизм связи для передачи транзакций. Интерфейсом может являться шина, интерфейс пакетной связи, интерфейс двухточечной связи и т.д.

Транзакцией может являться одна передача через интерфейс. Транзакция может включать в себя адрес, идентифицирующий данные, на которые воздействует транзакция, и может дополнительно включать в себя передаваемые данные. Транзакцией считывания может являться передача данных от адресата транзакции к источнику, а транзакцией записи может являться передача данных из источника адресату. Транзакция может быть выдана источником (например, компонентом-источником) и принята компонентом-адресатом. Транзакция может считаться ожидающей выполнения с того момента времени, когда источником выдана транзакция, до того момента времени, когда переданы соответствующие данные. Транзакция может быть завершена в ответ на передачу данных. Транзакция может иметь различные атрибуты помимо адреса и данных, которые дополнительно описывают транзакцию. Приведенными в качестве примера атрибутами могут являться, в том числе один или большее количество из следующих атрибутов, например: размер (например, измеренный в байтах и/или описанный сигналами разрешения байтов), способность кэширования, когерентность, рассмотренные выше параметры качества обслуживания (QoS) и т.д. В вариантах осуществления изобретения, основанных на пакетной передаче, транзакция может включать в себя один или большее количество пакетов. Например, в транзакции считывания могут содержаться пакет запроса на считывание и ответный пакет данных. В когерентных вариантах осуществления изобретения в транзакции считывания могут содержаться дополнительные пакеты для обеспечения когерентности (например, тестовые пакеты и ответные тестовые пакеты).

Компонент может включать в себя любое устройство или комбинацию устройств, сконфигурированных для выполнения заданного набора операций в системе. Приведенными в качестве примера компонентами могут являться, в том числе, процессоры, контроллеры памяти (и соответствующие запоминающие устройства), устройства кэш-памяти, периферийные устройства, такие как, например, графические устройства, устройства обработки видеоинформации, звуковые устройства, сетевые устройства, устройства ввода-вывода, запоминающие устройства большой емкости и т.д. Компоненты, которые могут инициировать транзакции (главные устройства), могут именоваться компонентами-источниками. Компоненты, которые могут являться целями транзакций (подчиненные устройства), могут именоваться компонентами-адресатами. Компоненты, которые могут являться как главными устройствами, так и подчиненными устройствами, могут именоваться как компонентами-источниками, так и компонентами-адресатами. В различных вариантах осуществления изобретения может использоваться любая комбинация компонентов-источников и компонентов-адресатов.

В одном из вариантов осуществления изобретения система 10 может быть объединена в одной интегральной микросхеме как конфигурация "система на микросхеме" (SOC). В других вариантах осуществления изобретения может быть реализована любая желательная степень интеграции и/или дискретная схема.

Ниже приведено более подробное описание различных вариантов осуществления схем управления инфраструктурой. В различных вариантах реализации систем могут использоваться комбинации различных вариантов осуществления изобретения, и/или в других вариантах реализации систем варианты осуществления изобретения могут использоваться поодиночке. В описанных ниже вариантах осуществления изобретения используются те же самые номера позиций, которые были использованы на чертеже Фиг. 1, но без буквенных индексов, поскольку в любой точке в системе 10 может использоваться любой желательный вариант осуществления схемы управления инфраструктурой. То есть упомянутые ниже схемы управления инфраструктурой именуют схемами 14 управления инфраструктурой, понимая, что ими являются любые из схем 14A-14I управления инфраструктурой. Аналогичным образом, может быть приведена ссылка на компонент 16, понимая, что может быть упомянут любой компонент 16A-16G в зависимости от того, на какую именно схему 14A-14I управления инфраструктурой приведена ссылка; и может быть приведена ссылка на порт 18, понимая, что может быть упомянут любой порт 18A-18M в зависимости от того, на какую именно схему 14A-14I управления инфраструктурой приведена ссылка.

Ограничители инфраструктуры

В наборе схем управления инфраструктурой могут содержаться схемы ограничителей инфраструктуры одного или большего количества типов. Ограничители инфраструктуры обычно могут быть сконфигурированы для ограничения выдачи транзакций на основании одного или большего количества программируемых факторов. Например, ограничители инфраструктуры могут включать в себя ограничители транзакций (которые могут ограничивать количество транзакций, ожидающих выполнения в конкретный момент времени) и ограничители ширины полосы частот (которые могут ограничивать ширину полосы частот, используемой транзакциями за заданную единицу времени).

На чертеже по Фиг. 2 изображена блок-схема одного из вариантов осуществления схемы 14 управления инфраструктурой, которая реализует ограничитель транзакций. В проиллюстрированном варианте осуществления изобретения схема 14 управления инфраструктурой включает в себя блок 20 управления и набор регистров 22A-22E. Блок 20 управления связан с регистрами 22A-22E. Некоторые из регистров 22A-22E могут быть программируемыми для установления ограничений, реализуемых ограничителем транзакций. Другие регистры 22A-22E могут быть предусмотрены для сохранения состояния для блока 20 управления.

Как проиллюстрировано на чертеже Фиг. 2, ограничитель транзакций сконфигурирован для ограничения количества транзакций, ожидающих выполнения, из компонента 16 или порта 18, связанного с "нижней частью" блока управления, показанной на чертеже Фиг. 2. В этом варианте осуществления изобретения ограничитель транзакций может реализовывать ограничение по транзакциям путем управления сигналами достоверности и сигналами готовности для предотвращения выдачи новых транзакций управляемым компонентом 16/портом 18. Соответственно, сигнал достоверности из управляемого компонента 16/порта 18 может быть принят управляемым компонентом 16/портом 18 в качестве входного сигнала (Vin), и сигнал (Rdyout) готовности может быть выведен в управляемый компонент 16/порт 18. Может быть выведен сигнал (Vout) достоверности, подаваемый в порт 18, и сигнал (Rdyin) готовности, подаваемый в порт 18, который показан в "верхней части" чертежа Фиг. 2, может быть принят блоком 20 управления. Также с обеих сторон могут быть приняты ответные сигналы (Rsp), связанные с интерфейсом передачи данных. Например, для транзакций считывания может иметься сигнал готовности данных и сигнал достоверности данных, а для транзакций записи может иметься другая пара сигналов: сигнал готовности данных/сигнал достоверности данных, аналогичных сигналам готовности и достоверности для инициирования транзакции. Для транзакции считывания сигнал достоверности данных может быть предоставлен портом 18, а сигнал готовности данных может быть предоставлен управляемым компонентом 16/портом 18. Для транзакции записи сигнал достоверности данных может быть предоставлен управляемым компонентом 16/портом 18, а сигнал готовности данных может быть предоставлен портом 18. Следует отметить следующее: несмотря на то, что в этом примере ограничитель транзакций обеспечивает ограничение транзакций в одном направлении, в других вариантах осуществления изобретения может быть реализовано ограничение транзакций в обоих направлениях (или могут использоваться два ограничителя, по одному для каждого направления).

Предел по транзакциям, применяемый схемой 14 управления инфраструктурой, может быть запрограммирован в регистре 22A "предел". Как только количество транзакций, ожидающих выполнения, из управляемого компонента 16/порта 18 достигает или превышает этот предел, блок 20 управления может осуществлять стробирование выходных сигналов достоверности и готовности для предотвращения инициирования дополнительных транзакций. Когда одна или большее количество транзакций, ожидающих выполнения, завершены, блок 20 управления может обнаружить, что количество транзакций, ожидающих выполнения, уменьшилось, и может прекратить стробирование выходных сигналов. После этого управляемый компонент 16/порт 18 могут инициировать дополнительные транзакции. В проиллюстрированном варианте осуществления изобретения блок 20 управления может отслеживать количество транзакций, ожидающих выполнения, в регистре 22C "подсчет транзакций".

В некоторых случаях, например, в случае широкополосного управляемого компонента, количество транзакций, ожидающих выполнения, может быстро увеличиться до предельного значения, а затем дополнительные транзакции могут быть ограничены инициированием на взаимно-однозначном основании с завершением транзакций. Для предотвращения или ослабления этого эффекта в ограничителе транзакций может содержаться гистерезис. В частности, блок управления может быть сконфигурирован так, что после того, как блок 20 управления начинает стробирование сигналов достоверности и сигналов готовности вследствие того, что количество транзакций, ожидающих выполнения, достигло предела, запрограммированного в регистре 22A, или превышает его, он продолжает стробирование сигналов достоверности и готовности до тех пор, пока количество транзакций, ожидающих выполнения, не уменьшится до величины, равной второму пределу ("нижнему пределу"), запрограммированному в регистре 22B, или меньшей, чем этот предел. Нижний предел может быть запрограммирован меньшим, чем предел во время использования. Гистерезис также может приводить к более "пульсирующим" транзакциям из такого компонента, что может быть эффективным для контроллеров памяти. То есть транзакции широкополосного компонента могут происходить в пакетах вместо их выдачи во взаимно-однозначном соответствии с завершением транзакций. Количество транзакций в пакете может быть равным, например, разности между пределом и нижним пределом.

В некоторых вариантах осуществления изобретения схема 14 управления инфраструктурой может обеспечивать поддержку динамических изменений пределов. Динамические изменения могут быть сделаны программно (например, путем перепрограммирования регистров 22A-22B), и схема 15 управления инфраструктурой может быть сконфигурирована так, что изменения, произведенные программно, гарантированно происходят без сбоев сигналов достоверности и сигналов готовности во время перехода (например, вследствие мгновенных изменений стробирования сигналов достоверности и сигналов готовности) и без входа в неопределенное состояние, которое может вызвать неожиданное действие. В альтернативном варианте или в дополнение к этому схема 14 управления инфраструктурой может обеспечивать поддержку динамических изменений пределов аппаратными средствами. Например, второй набор пределов (TLimit и нижний предел TLow в регистрах 22D-22E на чертеже Фиг. 2) может быть запрограммирован в схеме 14 управления инфраструктурой. Инициирующий входной сигнал может инициировать изменение пределов от пары предел/нижний предел в регистрах 22A-22B до инициированной пары предел/нижний предел, хранящейся в регистрах 22D-22E. Инициирующий фактор может быть сгенерирован извне вследствие условия, обнаруженного в системе. Например, инициирующим фактором может являться обнаружение того, что требования к качеству обслуживания (QoS), предъявляемые другим компонентом, увеличиваются до более высоких уровней качества обслуживания (QoS). В одном из вариантов осуществления изобретения триггер может оставаться действующим до тех пор, пока не будет желательным возврат к обычным пределам. В другом варианте осуществления изобретения пределы могут быть инициированы фронтом, и можно утверждать, что триггер переключается туда и обратно между пределами и пределами TLimits.

Пределы TLimits могут быть запрограммированы равными любым значениям. Например, если условием инициирования является условие, которое использует преимущество нижних пределов в схеме 14 управления инфраструктурой, то пределы TLimits могут быть запрограммированы более низкими, чем обычные пределы. Примерами такого инициирующего фактора могут являться, в том числе, упомянутое выше повышение требований к качеству обслуживания (QoS), обнаружение того, что другой компонент увеличивает свои требования, предъявляемые к ширине полосы частот, и т.д. С другой стороны, если условием инициирования является условие, которое использует преимущество более высоких пределов, то пределы TLimits могут быть запрограммированы более высокими, чем обычные пределы. Примерами такого инициирующего фактора могут являться, в том числе, перевод другого компонента в режим ожидания или его выключение, обнаружение более низких требований, предъявляемых к ширине полосы частот, в другом компоненте и т.д.

На чертеже по Фиг. 3 изображен конечный автомат, иллюстрирующий один из вариантов осуществления схемы ограничителя транзакций. В состоянии 24 ожидания схема ограничителя транзакций не осуществляет стробирование сигналов достоверности и сигналов готовности. Соответственно, сигнал Vout из блока 20 управления равен сигналу Vin на входе блока 20 управления, и сигнал Rdyout из блока 20 управления равен сигналу Rdyin на входе блока 20 управления. Рассматривая это другим образом, сигналы достоверности и сигналы готовности могут проходить через схему ограничителя транзакций, пока ограничитель находится в состоянии 24 ожидания. С другой стороны, в состоянии 26 останова оба сигнала Vout и Rdyout являются стробированными (установленными равными нулю).

Переход из состояния 24 ожидания в состояние 26 останова может происходить тогда, когда подсчет транзакции в регистре 22C является большим или равным пределу. Для безопасного совершения перехода в состояние 26 останова в те моменты времени, когда программное обеспечение может изменять программируемый предел, может использоваться уравнение, показанное на чертеже Фиг. 3. То есть, если подсчет транзакции является большим или равным пределу, и управляемый компонент/порт не предпринимает попытку передачи транзакции (Vin=0), то этот переход может происходить. Если подсчет транзакции является большим или равным значению, меньшему чем предел, то управляемый компонент/порт предпринимает попытку передачи транзакции (Vin=1), и транзакция разрешена (Rdyout), то этот переход также может происходить.

Переход из состояния 26 останова в состояние 24 ожидания может происходить тогда, когда подсчет транзакций является меньшим или равным нижнему пределу, и подсчет транзакций является меньшим чем предел. Для того случая, когда гистерезис не используется, и нижний предел не запрограммирован ниже предела, может быть выполнено сравнение подсчета транзакций с пределом. Для варианта осуществления изобретения, в котором реализован гистерезис, может применяться проиллюстрированное уравнение. Если гистерезис не реализован, то переход из состояния 26 останова в состояние 24 ожидания может быть выполнен в том случае, если подсчет транзакций является меньшим, чем предел. И вновь, для разрешения программного динамического модифицирования пределов переход из состояния 26 останова в состояние 24 ожидания может произойти, если управляемый компонент/порт (Vin=0) не предпринимает попытку транзакции, или если управляемый компонент/порт предпринимает попытку передачи транзакции (Vin=1), и транзакцию разрешают (Rdyout).

Теперь переходим к рассмотрению чертежа по Фиг. 4, на нем показана схема последовательности операций, иллюстрирующая функционирование одного из вариантов осуществления схемы 14 управления инфраструктурой, показанной на чертеже Фиг. 2 (и, в частности, блока 20 управления) для сохранения подсчета транзакций в регистре 22C. Несмотря на то, что для простоты понимания блоки показаны в конкретном порядке следования, могут использоваться другие порядки следования. В схеме 14 управления инфраструктурой/блоке 20 управления эти блоки могут выполняться параллельно в комбинаторной логике. Блоки, комбинации блоков и/или схема последовательности операций в целом могут быть реализованы в виде конвейерной схемы по множеству периодов тактовых импульсов. Схема 14 управления инфраструктурой/блок 20 управления могут быть сконфигурированы для реализации функционирования, показанного на чертеже Фиг. 4.

Если управляемый компонент/порт выдает запрос на транзакцию (Vin=1) и блок 20 управления не стробирует сигнал готовности (Rdyout =1), то управляемый компонент/порт передает транзакцию (блок 30 принятия решения, ветвь "ДА"). Соответственно, блок 20 управления может быть сконфигурирован для приращения подсчета транзакций в регистре 22C на единицу (блок 32). Если ответ (передача данных) по транзакции, ожидающей выполнения, завершен (блок 34 принятия решения, ветвь "ДА"), то транзакция завершена, и блок 20 управления может быть сконфигурирован для уменьшения подсчета транзакций на единицу (блок 36). В зависимости от типа транзакции, ответ для отслеживания завершения транзакции может быть различным. Например, операции записи могут быть завершены управляемым компонентом/портом, тогда как операции считывания могут быть завершены возвратом данных из порта. Поскольку выполняют обновление подсчета (вместо попытки отслеживания конкретной транзакции), то может оказаться достаточным выполнение логической операции ИЛИ для всех вместе ответов. В альтернативном варианте, как упомянуто выше, в некоторых вариантах осуществления изобретения могут быть реализованы отдельные интерфейсы считывания и записи, и схема 14 управления инфраструктурой может только наблюдать ответы для транзакции соответствующего типа.

Переходим к рассмотрению следующего чертежа Фиг. 5, на нем показан конечный автомат, иллюстрирующий функционирование одного из вариантов осуществления схемы 14 управления инфраструктурой/блока 20 управления для реализации динамического инициирования различных пределов. Конечный автомат включает в себя состояние 38 с обычными пределами и состояние 39 с инициированными пределами. В состоянии 38 с обычными пределами могут использоваться предел и нижний предел из регистров 22A-22B. В состоянии с инициированными пределами могут использоваться пределы TLimit и TLow из регистров 22D-22E. Переход из состояния 38 в состояние 39 может происходить в ответ на наличие инициирующего фактора, а переход из состояния 39 в состояние 38 может происходить в ответ на отсутствие инициирующего фактора. В альтернативном варианте инициирующие импульсы могут вызвать переход в любом направлении.

Аналогично обсуждению конечного автомата, показанного на чертеже Фиг. 3, переходы на чертеже Фиг. 5 могут происходить, если управляемый компонент/порт не предпринимает попытку транзакции (Vin=0) или если управляемый компонент/порт предпринимает попытку передачи транзакции (Vin=1), и транзакцию разрешают (Rdyout).

Теперь переходим к рассмотрению чертежа Фиг. 6, на нем показана блок-схема одного из вариантов осуществления схемы 14 управления инфраструктурой, в которой реализован ограничитель ширины полосы частот. В проиллюстрированном варианте осуществления изобретения схема 14 управления инфраструктурой включает в себя блок 40 управления и набор регистров 42A-42F. Блок 40 управления связан с регистрами 42A-42F. Некоторые из регистров 42A-42F могут быть программируемыми для установления пределов, реализуемых ограничителем транзакций. Другие регистры 42A-42F могут быть предусмотрены для сохранения состояния для блока 40 управления.

Как проиллюстрировано на чертеже по Фиг. 6, ограничитель ширины полосы частот сконфигурирован для ограничения ширины полосы частот из компонента 16 или порта 18, который связан с "нижней частью" блока управления, показанного на чертеже по Фиг. 6. В этом варианте осуществления изобретения ограничитель ширины полосы частот может осуществлять это ограничение путем управления сигналами достоверности и сигналами готовности, предотвращая выдачу новых транзакций управляемым компонентом 16/портом 18, когда выделенная ширина полосы частот является израсходованной в течение заданной единицы времени (пока эта единица времени не истечет). Соответственно, сигнал достоверности из управляемого компонента 16/порта 18 может быть принят управляемым компонентом 16/портом 18 в качестве входного сигнала (Vin), и сигнал (Rdyout) готовности может быть выведен в управляемый компонент 16/порт 18. Может быть выведен сигнал (Vout) достоверности, подаваемый в порт 18, и сигнал (Rdyin) готовности, подаваемый в порт 18, который показан в "верхней части" чертежа по Фиг. 6, может быть принят блоком 40 управления. Как изложено выше, в других вариантах осуществления изобретения могут быть реализованы ограничения в обоих направлениях, или ограничители могут использоваться для каждого желательного направления.

В этом варианте осуществления изобретения управление шириной полосы частот может осуществляться путем предоставления нескольких кредитов, где для каждой выданной транзакции используют один кредит. В других вариантах осуществления изобретения может использоваться иное количество кредитов за каждую транзакцию (например, на основании размера транзакции). Количество кредитов, предоставляемых в каждую единицу времени, может быть запрограммировано в регистре 42C "добавляемые кредиты", и промежуток времени, соответствующий кредитам, может быть запрограммирован в регистре 42B "кредитоспособность". Этот промежуток времени может быть измерен в единицах периодов тактовых импульсов, в реальном масштабе времени или любой иной желательной мерой времени.

Блок 40 управления может быть сконфигурирован для сохранения показаний таймера в регистре 42A для измерения течения времени. Каждый раз, когда истекает количество времени "кредитоспособность", к оставшимся кредитам для использования могут быть добавлены кредиты из "добавляемых кредитов". Оставшиеся кредиты могут быть сохранены в регистре 42D "кредиты". По мере выдачи транзакций количество кредитов в регистре "кредиты" может уменьшаться. Если количество кредитов доходит до нуля, то блок 40 управления может предотвращать выдачу дополнительных транзакций до тех пор, пока количество кредитов снова не станет не равным нулю (по истечении интервала "кредитоспособность" путем добавления кредитов из "добавляемых кредитов"). Если промежуток времени истекает до использования всех имеющихся кредитов, то кредиты могут быть перенесены на следующий промежуток времени. То есть срок действия кредитов может не истекать. В других вариантах осуществления изобретения срок действия кредитов может истечь, и блок 40 управления может инициализировать регистр 42D "кредиты" при помощи значения "добавляемые кредиты" из регистра 42C по истечении каждого промежутка времени. Количество кредитов также может иметь насыщение по максимальному значению. Это максимальное значение может быть программируемым или постоянным.

В одном из вариантов осуществления изобретения ограничитель ширины полосы частот может обеспечивать поддержку инициирующего входного сигнала и изменения пределов TLimits аналогично приведенному выше обсуждению применительно к чертежу Фиг. 5. TLimits могут включать в себя TCredit rate в регистре 42E и TCredit add в регистре 42F. Как изложено выше, TLimits могут быть большими или меньшими, чем обычные пределы.

Теперь переходим к рассмотрению чертежа по Фиг. 7, на нем показана схема последовательности операций, иллюстрирующая функционирование одного из вариантов осуществления схемы 14 управления инфраструктурой, показанного на чертеже Фиг. 6 (и, в частности, блока 40 управления). Несмотря на то, что для простоты понимания блоки показаны в конкретном порядке следования, могут использоваться другие порядки следования. В схеме 14 управления инфраструктурой/блоке 40 управления эти блоки могут выполняться параллельно в комбинаторной логике. Блоки, комбинации блоков и/или схема последовательности операций в целом могут быть реализованы в виде конвейерной схемы по множеству периодов тактовых импульсов. Схема 14 управления инфраструктурой/блок 40 управления может быть сконфигурирована для реализации функционирования, показанного на чертеже по Фиг. 7.

Блок 40 управления может обновлять показание таймера в регистре 42A согласно результату измерения времени, реализованного в схеме 14 управления инфраструктурой (например, путем однократного приращения на единицу через каждый период тактовых импульсов). Показание таймера может быть сравнено с количеством кредитов, запрограммированным в регистре 42B, и если показание таймера равно количеству кредитов, то промежуток времени истек (блок 50 принятия решения, ветвь "ДА"). Блок 40 управления может быть сконфигурирован для добавления значения "добавляемые кредиты" из регистра 42C в регистр 42D " кредиты" (блок 52).

Если транзакцию разрешают (Vin=1 и Rdyout=1 - блок 54 принятия решения, ветвь "ДА"), то блок 40 управления может постепенно уменьшать количество кредитов в регистре 42D "кредиты" (блок 56). Если количество кредитов в регистре 42D "кредиты" уменьшилось до нуля (блок 58 принятия решения, ветвь "ДА"), то блок 40 управления может осуществить стробирование сигналов достоверности и сигналов готовности (Vout=0 и Rdyout=0) (блок 60). В противном случае (блок 58 принятия решения, ветвь "НЕТ") блок 40 управления может передать входные сигналы на выходы (Vout=Vin и Rdyout=Rdyin) (блок 62).

Формирователи трафика записей

Другим вариантом осуществления схемы 14 управления инфраструктурой могут являться схемы формирователей трафика записей одного или большего количества типов. Схема формирователя трафика записей первого типа может использоваться в интерфейсах, в которых более узкополосный интерфейс от компонента или порта соединен с более широкополосным портом. Эта схема формирователя трафика записей может именоваться схемой сбора записываемых данных. Порт может быть более широкополосным, если ширина данных (то есть данных, передаваемых в одном такте передачи данных в порту) является более широкой, чем в более узкополосном компоненте/порте. В таких случаях для передачи данных в порт может использоваться увеличитель размера (не показанный). Увеличитель размера может захватывать данные с более узкой шины и передавать данные по надлежащему участку более широкой шины данных. Например, увеличитель размера с узкой шины данных до более широкой шины данных, которая является вдвое более широкой, чем узкая шина данных, может поочередно передавать данные в верхней половине или в нижней половине более широкой шины данных, поскольку данные принимает более узкая шина данных. Однако, увеличитель размера не предназначен для накопления тактов передачи данных для передачи, если шина данных не занята какой-либо другой передачей. Если для передачи данных доступна более широкая шина данных, то увеличитель размера передает узкие данные и использует разрешения для байтов или иные указатели достоверности для идентификации того, по какой части более широкой шины данных производят передачу данных. Схема сбора записываемых данных может быть сконфигурирована для задержки инициирования транзакции записи до тех пор, пока не будут собраны данные из более узкополосного интерфейса. Таким образом, может иметь место более эффективное использование более широкополосного интерфейса. В других случаях порт может быть более широкополосным, поскольку его синхронизацию осуществляют с более высокой тактовой частотой, чем более узкополосного компонента/порта. В этом случае задержка инициирования транзакции записи может уменьшить количество периодов тактовых импульсов или позволить обойтись без них в более широкополосном интерфейсе, в котором какие-либо данные не передают, поскольку следующие данные для операции записи по-прежнему принимают с более низкой шириной полосы частот. И вновь, в некоторых вариантах осуществления изобретения может быть достигнута более высокая эффективность более широкополосного порта.

Формирователь трафика записей другого типа может использоваться для предотвращения инициирования конкретным компонентом или портом слишком большого количества транзакций записи до завершения самой ранней из транзакций записи. Формирователь трафика записей этого типа может именоваться схемой расширителя запроса на запись. В узкополосном интерфейсе или в интерфейсе с более медленной синхронизацией выдача слишком большого количества транзакций записи из одного компонента/порта может препятствовать выдаче транзакций записи другими компонентами/портами до тех пор, пока не будет передан, по меньшей мере, первый такт передачи данных для каждой транзакции записи, ожидающей выполнения (для сохранения упорядоченности). Если компонент/порт, выдающий транзакцию, медленно предоставляет данные, то могут иметь место длинные задержки в других компонентах/портах. В некоторых вариантах осуществления изобретения схема расширителя запроса на запись может использоваться вместе со схемой сбора записей. Например, если порт связан с мультиплексором между узкой шиной данных со схемой сбора записей и входом, имеющим ту же самую ширину, что и порт, более широкополосный вход может иметь преобладающее влияние на ширину полосы частот, предотвращая получение достаточной ширины полосы частот более узкополосным входом. В альтернативном варианте более узкополосный вход может выдавать слишком большое количество запросов, уменьшая имеющуюся ширину полосы частот для более широкополосного входа. Схема расширителя запроса на запись может разрешать выдачу одной или большего количества транзакций записи (до заданного предела), но затем может предотвращать дополнительные транзакции записи из того же самого порта/компонента до тех пор, пока не будут завершены выданные транзакции записи (например, до тех пор, пока не будут переданы все такты передачи данных). В рассмотренном ниже варианте осуществления схемы расширителя запроса на запись выдачу транзакций записи ограничивают одной на каждый компонент-источник/порт. В других вариантах осуществления изобретения может быть разрешено более одной выдачи транзакций записи, или разрешенное количество может быть программируемым.

На чертеже по Фиг. 8 изображена блок-схема одного из вариантов осуществления схемы 14 управления инфраструктурой, которая может реализовать схему сбора записываемых данных или схему расширителя запроса на запись. В варианте осуществления изобретения, показанном на чертеже Фиг. 8, схема управления инфраструктурой включает в себя блок 70 управления и регистр 72 "незавершенные такты передачи данных". Блок 70 управления связан с регистром 72 "незавершенные такты передачи данных". Блок 70 управления также может быть связан с сигналами достоверности и сигналами готовности из более узкополосного компонента/порта (показанного в нижней части чертежа по Фиг. 8) и более широкополосного порта (показанного в верхней части чертежа по Фиг. 8). В этом варианте осуществления изобретения порт может обеспечивать поддержку отдельных интерфейсов считывания и записи, и таким образом сигналы достоверности и сигналы готовности являются частью интерфейса записи (WV и WRdy на чертеже Фиг. 8). Блок 70 управления также может осуществлять текущий контроль сигналов достоверности данных и готовности данных (соответственно, DV и DRdy). Записываемые данные могут быть буферизованы в буфере обратного магазинного типа (FIFO) (например, в увеличителе размера, в компоненте-источнике или в порте), и блок 70 управления может осуществлять текущий контроль указателей FIFO (DFifo Ptrs на чертеже по Фиг. 8). В дополнение к этому, атрибутом транзакции, передаваемым вместе с адресом транзакции, текущий контроль которого также может осуществляться блоком 70 управления, может являться длина записи (WLen).

На чертеже по Фиг. 9 изображена схема последовательности операций, на которой проиллюстрировано функционирование одного из вариантов осуществления схемы 14 управления инфраструктурой, показанного на чертеже Фиг. 8, и, в частности, блока 70 управления для сохранения незавершенных тактов передачи данных (PendDataBeats) в регистре 72. Несмотря на то, что для простоты понимания блоки показаны в конкретном порядке следования, могут использоваться другие порядки следования. В схеме 14 управления инфраструктурой/блоке 70 управления эти блоки могут выполняться параллельно в комбинаторной логике. Блоки, комбинации блоков и/или схема последовательности операций в целом могут быть реализованы в виде конвейерной схемы по множеству периодов тактовых импульсов. Схема 14 управления инфраструктурой/блок 70 управления может быть сконфигурирована для реализации функционирования, показанного на чертеже Фиг. 9.

Если блок 70 управления разрешает инициирование транзакции записи (оба WVin и WRdyout=1 - ветвь "ДА" в блоке 73 принятия решения), то блок 70 управления может инициализировать регистр 72 "незавершенные такты передачи данных" посредством количества тактов передачи, указанных атрибутом WLen транзакции (блок 74). В альтернативном варианте регистр 72 может быть инициализирован посредством количества байтов, указанных регистром WLen. В тех случаях, когда более чем одна транзакция записи могут одновременно являться ожидающими выполнения, блок 70 управления может добавить значение WLen к текущему значению регистра. Таким образом, в этих вариантах осуществления изобретения значение в регистре 72 может отображать остающийся для передачи объем данных (такты передачи или байты) для транзакций записи, ожидающих выполнения.

Если происходит передача данных (оба DV и DRdy = 1 - ветвь "ДА" в блоке 76 принятия решения), то блок 72 управления может постепенно уменьшить содержимое регистра 72 "незавершенные такты передачи данных" (блок 78). Это уменьшение может являться уменьшением на единицу, если значение в регистре 72 представляет собой такты передачи данных. Если это значение представляет собой байты данных, то уменьшение может быть произведено на объем передачи (например, в более широкополосном порте).

Теперь переходим к рассмотрению чертежа по Фиг. 10, на нем показана схема последовательности операций, иллюстрирующая функционирование одного из вариантов осуществления схемы 14 управления инфраструктурой, показанного на чертеже Фиг. 8 (и, в частности, блока 70 управления), для реализации схемы сбора записываемых данных. Несмотря на то, что для простоты понимания блоки показаны в конкретном порядке следования, могут использоваться другие порядки следования. В схеме 14 управления инфраструктурой/блоке 70 управления эти блоки могут выполняться параллельно в комбинаторной логике. Блоки, комбинации блоков и/или схема последовательности операций в целом могут быть реализованы в виде конвейерной схемы по множеству периодов тактовых импульсов. Схема 14 управления инфраструктурой/блок 70 управления может быть сконфигурирована для реализации функционирования, показанного на чертеже по Фиг. 10.

Блок 70 управления может быть сконфигурирован для определения подсчета тактов передачи для данных, хранящихся в DFifo, в ответ на указатели DFifo (блок 80). В альтернативном варианте вместо приема указателей DFifo блок 70 управления может просто принять подсчет тактов передачи. Если этот подсчет является большим, чем длина транзакции записи (WLen), или равным ей (блок 82 принятия решения, ветвь "ДА"), то данные для транзакции записи готовы в DFifo для передачи. С другой стороны, если DFifo заполнен целиком (блок 84 принятия решения, ветвь "ДА"), то, возможно, понадобится инициирование транзакции записи, поскольку передаваемые данные для транзакции записи не могут быть полностью сохранены в DFifo. В любом случае, в этом варианте осуществления изобретения блок 70 управления может предотвратить инициирование транзакции записи, которая во всем остальном является готовой, если предыдущая транзакция записи не завершена (количество незавершенных тактов передачи данных не равно нулю - блок 86 принятия решения). Если предыдущая транзакция записи завершена (блок 86 принятия решения, ветвь "ДА"), то блок 70 управления может пропустить сигналы WVin и WRdyin в качестве сигналов WVout и WRdyout (блок 88). В противном случае (ветви "НЕТ" в блоках 82 и 84 принятия решения или ветвь "НЕТ" в блоке 86 принятия решения) блок 70 управления может осуществить стробирование сигналов WVout и WRdyout, предотвращая выдачу транзакции записи (блок 90).

Вариант осуществления изобретения, в котором реализована схема расширителя запроса на запись, может быть аналогичным, но в нем может быть реализована только лишь проверка того, равно ли количество незавершенных тактов передачи данных нулю. То есть схема расширителя запроса на запись может реализовывать часть схемы последовательности операций, показанной на чертеже Фиг. 10, окруженную пунктирной линией 92 (блок 86 принятия решения и блоки 88 и 90). Однако, схема сбора записываемых данных может предотвращать выдачу конкретной транзакции записи до тех пор, пока не будут приняты такты передачи данных для этой конкретной транзакции записи, тогда как схема расширителя запроса на запись может предотвращать выдачу конкретной транзакции записи до тех пор, пока не будут приняты такты передачи данных из предыдущей транзакции записи.

Следует отметить, что в некоторых вариантах осуществления схемы сбора записываемых данных и/или схемы расширителя запроса на запись могут быть реализованы дополнительные признаки в попытке сделать использование исходной ширины полосы частот интерфейса более эффективным. Например, проверка подсчета незавершенных тактов передачи данных может производиться для одного оставшегося такта передачи, а не для 0, ожидая, что последний такт передачи вскоре может быть передан, и может быть начата следующая запись (с некоторым наложением на операцию записи). Другой пример может быть основан на соотношении ширины полос частот, когда шины работают на одной и той же частоте. На основании этого соотношения схема сбора записываемых данных может проверять меньшее количество тактов передачи данных. Например, когда это соотношение равно двум, то схема сбора записываемых данных может проверять половину тактов передачи данных.

Управление инфраструктурой, связанное с качеством обслуживания (QoS)

В вариантах осуществления изобретения могут содержаться различные схемы управления инфраструктурой, связанной с качеством обслуживания (QoS). Как правило, по меньшей мере, некоторые компоненты 16 в системе 10 могут быть сконфигурированы для назначения выдаваемым им транзакциям параметров качества обслуживания (QoS). Параметры качества обслуживания (QoS) для транзакций могут использоваться для уравновешивания требований, предъявляемых к производительности компонентов. Однако, в некоторых случаях один или большее количество компонентов могут быть разработаны так, что предоставляют параметры качества обслуживания (QoS). В других случаях параметры качества обслуживания (QoS), назначенные одним или большим количеством компонентов, могут не являться столь же желательными, как другие назначенные параметры качества обслуживания (QoS), с учетом общей производительности системы. Может быть предусмотрено, что в таких случаях схемы управления инфраструктурой предоставляют и/или изменяют параметры качества обслуживания (QoS). Кроме того, параметры качества обслуживания (QoS) могут использоваться для инициирования измененных ограничений в других схемах управления инфраструктурой, что более подробно рассмотрено ниже.

Как правило, параметром качества обслуживания (QoS) может являться атрибут транзакции, который может идентифицировать запрошенный уровень обслуживания для транзакции. Транзакциям со значениями параметра качества обслуживания (QoS), которые запрашивают более высокие уровни обслуживания, может быть отдано предпочтение по сравнению с транзакциями, которые запрашивают более низкие уровни обслуживания. Это предпочтение может быть применено в различных схемах 12 интерфейсов инфраструктуры или в компоненте-адресате 16, являющемся адресатом транзакций, или в обоих из них. Таким образом, конкретный компонент-источник может быть сконфигурирован для использования параметров качества обслуживания (QoS) для идентификации того, какие транзакции являются более важными для компонента-источника (и таким образом, что их, например, следует обслуживать до других транзакций из того же самого компонента-источника), специально для тех источников, которые обеспечивают поддержку неупорядоченных передач данных относительно передач адреса из компонента-источника. Кроме того, параметры качества обслуживания (QoS) могут позволять источникам запрашивать более высокие уровни обслуживания, чем уровни обслуживания других источников в том же самом порте и/или компонентов-источников в других портах.

В некоторых вариантах осуществления изобретения различные типы трафика могут иметь различные определения параметров качества обслуживания (QoS). То есть различные типы трафика могут иметь различные наборы параметров качества обслуживания (QoS). Например, для транзакций в реальном масштабе времени может быть задан набор параметров качества обслуживания (QoS) в реальном масштабе времени, а для транзакций не в реальном масштабе времени может быть задан набор параметров качества обслуживания (QoS) не в реальном масштабе времени. Схемы 12 интерфейсов инфраструктуры и/или компоненты-адресаты 16 могут быть сконфигурированы для обработки параметров качества обслуживания (QoS) и могут быть сконфигурированы для использования относительных значений параметров качества обслуживания (QoS) для установления графика очередности обслуживания транзакций.

В качестве примера, параметры качества обслуживания (QoS) в реальном масштабе времени могут включать в себя зеленый, желтый и красный уровни, указывающие возрастающие потребности в данных с низкой задержкой на каждом уровне. Таким образом, зеленый уровень может отображать самый низкий приоритет параметров качества обслуживания (QoS) в реальном масштабе времени, желтый уровень может отображать средний приоритет, а красный уровень может отображать самый высокий приоритет. Параметры качества обслуживания (QoS) не в реальном масштабе времени могут включать в себя уровень максимальных усилий и уровень с низкой задержкой, рассматриваемый как более высокий, чем уровень максимальных усилий. Уровень максимальных усилий может рассматриваться как более низкий, чем каждый из уровней в реальном масштабе времени. В некоторых вариантах осуществления изобретения уровень с низкой задержкой может динамически изменяться между уровнем, равным зеленому уровню или желтому уровню, на основании общего состояния системы. В других вариантах осуществления изобретения может быть реализован любой желательный набор или могут быть реализованы любые желательные наборы параметров качества обслуживания (QoS).

В некоторых вариантах осуществления изобретения параметры качества обслуживания (QoS) могут быть обновлены для незавершенных транзакций. Может быть обеспечена поддержка различных механизмов обновления. Например, параметры качества обслуживания (QoS) для незавершенных транзакций из компонента-источника 16 могут быть обновлены в том случае, если последующая транзакция из этого компонента-источника 16 выдана с более высоким параметром качества обслуживания (QoS). В одном из вариантов осуществления изобретения транзакции, имеющие более низкий уровень качества обслуживания (QoS), могут быть вытеснены транзакциями, имеющими более высокий уровень качества обслуживания (QoS)). В качестве другого примера, может быть обеспечена поддержка интерфейса боковой полосы от одного или большего количества компонентов-источников для обновления параметров качества обслуживания (QoS) путем передачи запроса на обновление через интерфейс боковой полосы. В другом примере для обновления параметров качества обслуживания (QoS) может использоваться относительный срок незавершенных транзакций.

Переходим к рассмотрению чертежа по Фиг. 11, на нем показан вариант осуществления схемы 14 управления инфраструктурой, которая может использоваться для предоставления параметра качества обслуживания (QoS) для транзакции. В проиллюстрированном варианте осуществления изобретения блок 14 управления инфраструктурой включает в себя регистр 100A "разрешение", регистр 100B "качество обслуживания (QoS)" и мультиплексор (mux) 102, связанный с регистрами 100A-100B. В частности, регистр 100A "разрешения" может быть связан со средством управления выбором в мультиплексоре 102, а регистр 100B качества обслуживания (QoS) может быть связан с мультиплексором 102 в качестве его входа. Другой вход мультиплексора 102 может быть связан с участком интерфейса с управляемым компонентом 16/портом 18 (в нижней части чертежа Фиг. 11), который передает параметр качества обслуживания (QoS), а выход мультиплексора 102 может быть связан с соответствующим участком интерфейса с портом 18 в нижней части чертежа Фиг. 11.

Схема 14 управления качеством обслуживания (QoS) в инфраструктуре, показанная на чертеже по Фиг. 11, может использоваться для предоставления программируемого параметра качества обслуживания (QoS) для компонента-источника 16, который сам по себе не выполнен с возможностью предоставления параметра качества обслуживания (QoS). Схема 14 управления качеством обслуживания (QoS) в инфраструктуре также может использоваться в порту 18, который сконфигурирован для передачи транзакций из одного или большего количества компонентов-источников, все из которых не выполнены с возможностью предоставления параметров качества обслуживания (QoS). Если регистр 100A "разрешение" запрограммирован так, что разрешает работу схемы 14 управления инфраструктурой, мультиплексор 102 может быть сконфигурирован для выбора параметра качества обслуживания (QoS), запрограммированного в регистре 100B "качество обслуживания (QoS)". В противном случае параметр качества обслуживания (QoS), принятый из управляемого компонента 16/порта 18, может быть выбран мультиплексором 102.

На чертеже по Фиг. 12 изображена блок-схема другого варианта осуществления схемы 14 управления инфраструктурой, которая может переопределять параметр качества обслуживания (QoS) из компонента-источника 16 или порта 18 на основании одного или большего количества других атрибутов транзакции. В проиллюстрированном варианте осуществления изобретения схема 14 управления инфраструктурой может включить в себя регистр 100B "качество обслуживания (QoS)" и мультиплексор 102 аналогично варианту осуществления изобретения, показанному на чертеже Фиг. 11, и блок 104 управления. Аналогично варианту осуществления изобретения, показанному на чертеже Фиг. 11, регистр 100B "качество обслуживания (QoS)" связан с входом мультиплексора 102, другой вход мультиплексора 102 связан с участком интерфейса из управляемого компонента 16/порта 18, передающим параметр качества обслуживания (QoS), а выход мультиплексора 102 связан с участком интерфейса с портом 18, передающим параметр качества обслуживания (QoS). Средство управления выбором мультиплексора 102 связано с блоком управления 104, который соединен для приема одного или большего количество атрибутов транзакции из управляемого компонента 16/порта 18. В некоторых вариантах осуществления изобретения атрибуты транзакции, принятые блоком 104 управления, могут также включать в себя параметр качества обслуживания (QoS).

Вариант осуществления изобретения, показанный на чертеже Фиг. 12, может переопределять параметр качества обслуживания (QoS), присвоенный компонентом-источником 16, параметром качества обслуживания (QoS), запрограммированным в регистре 100B "качество обслуживания (QoS)". Запрограммированный параметр качества обслуживания (QoS) может указывать более высокий желательный уровень качества обслуживания (QoS) или более низкий желательный уровень качества обслуживания (QoS), чем переопределяемое качество обслуживания (QoS). Например, более высокий уровень качества обслуживания (QoS) может быть выбран для определенных транзакций для повышения общей производительности. В одном из вариантов реализации пропуск преобразования адреса транзакции может приводить к считыванию таблиц преобразований для отсутствующих данных преобразования в одной или в большем количестве транзакций считывания. Поскольку после этого это преобразование может использоваться для многих транзакций, может оказаться целесообразным передавать эти транзакции считывания с более высоким уровнем качества обслуживания (QoS), чем другие транзакции. Атрибуты транзакции, декодированные блоком 104 управления для обнаружения переопределения, могут включать в себя тип транзакции "считывание" и другие атрибуты, идентифицирующие считывание как считывание с преобразованием. В качестве другого примера, транзакции, выданные управляемым портом, могут включать в себя транзакции, источниками которых являются компоненты, назначающие параметры качества обслуживания (QoS), и другие транзакции, источниками которых являются компоненты, не назначающие параметры качества обслуживания (QoS). Идентификатор транзакции может идентифицировать источник и может являться атрибутом транзакции, который может быть использован для определения того, используется ли переопределение или нет. В общем, в различных вариантах осуществления изобретения могут быть проанализированы любые атрибуты транзакции.

Переходим к рассмотрению чертежа по Фиг. 13, на нем показана блок-схема согласно одному из вариантов осуществления схемы 12E интерфейса инфраструктуры, имеющая порты 18N и 18P, связанные, соответственно, со схемами 14J и 14K управления инфраструктурой. Схема 14J управления инфраструктурой связана со схемой 14K управления инфраструктурой для предоставления сигнала инициирования качества обслуживания (QoS), которая, в свою очередь, сконфигурирована для предоставления сигнала инициирования качества обслуживания (QoS) в схему 14K управления инфраструктурой. Каждая схема 14J-14K управления инфраструктурой подключена для приема параметра качества обслуживания (QoS) источника вместе с транзакцией из источника (компонента или порта), который подключен так, что поддерживает связь с соответствующим портом 18N или 18P.

Схемами 14J-14K управления инфраструктурой могут являться ограничители инфраструктуры различных типов, такие как, например, ограничители транзакций или ограничители ширины полосы частот. Каждая схема 14J-I4K управления инфраструктурой может быть сконфигурирована для подачи сигнала в другую схему управления инфраструктурой в том случае, если параметр качества обслуживания (QoS) принятой транзакции из источника соответствует пороговому значению качества обслуживания (QoS)/превышает его. В ответ на активный инициирующий фактор схема 14J-14K управления инфраструктурой, принимающая активный инициирующий фактор, может переключиться с использованием TLimits. Путем программирования TLimits так, чтобы они были более низкими, чем обычные пределы, схема 14J-14K управления инфраструктурой приема может уменьшать свои пределы в ответ на активный инициирующий фактор, и, таким образом, повышенные требования к качеству обслуживания (QoS) в активной схеме 14J-14K управления инфраструктурой могут позволять компоненту 16/порту 18, предъявляющему повышенные требования к качеству обслуживания (QoS), фактически получать большую ширину полосы частот посредством схемы 12E интерфейса инфраструктуры, поскольку другой компонент/порт может использовать меньшую ширину полосы частот. В некоторых вариантах осуществления изобретения может быть обеспечена поддержка множества пороговых значений и множества наборов TLimits, что позволяет реализовать даже еще меньшие пределы при достижении/превышении пороговых значений качества обслуживания (QoS). Например, в варианте осуществления изобретения, в котором реализованы зеленый, желтый и красный уровни в реальном масштабе времени, может иметь оба уровня: желтый и красный уровни в качестве пороговых значений, и TLimits для красного порогового значения могут являться более низкими, чем TLimits для желтого порогового значения. Пороговые значения для уровней качества обслуживания (QoS) могут быть программируемыми в схеме 14J-14K управления инфраструктурой или могут быть неизменными. В еще одном варианте осуществления изобретения пороговые значения качества обслуживания (QoS) могут использоваться в масштабе всей системы для управления шириной полосы частот. Например, таблица TLimits может быть запрограммирована на основании количества компонентов-источников, перешедших через одно или большее количество пороговых значений качества обслуживания (QoS). При увеличении количества компонентов-источников, производящих передачи (например) на желтом или красном уровнях качества обслуживания (QoS), TLimits в различных ограничителях могут быть обновлены на основании значений из таблицы.

На чертеже по Фиг. 14 изображена схема последовательности операций, на которой проиллюстрировано функционирование одного из вариантов осуществления схем 14J-14K управления инфраструктурой для генерации сигнала инициирования качества обслуживания (QoS). Ответ на сигнал активного инициирующего фактора может быть аналогичным показанному на чертеже Фиг. 5. Несмотря на то, что для простоты понимания блоки показаны в конкретном порядке следования, могут использоваться другие порядки следования. В схеме управления 14J-14K инфраструктурой эти блоки могут выполняться параллельно в комбинаторной логике. Блоки, комбинации блоков и/или схема последовательности операций в целом могут быть реализованы в виде конвейерной схемы по множеству периодов тактовых импульсов. Схема 14J-14K управления инфраструктурой может быть сконфигурирована для реализации функционирования, показанного на чертеже по Фиг. 14.