Изобретение относится к электроизмерительной и вычислительной технике и может быть использовано для высокоточного преобразования быстроизменяющихся электрических сигналов в цифровой код.

Известен параллельный аналого-цифровой преобразователь динамического типа [Патент 2389133 РФ, H03M 1/12 С1. - №2008150663/09 от 23.12.2008 г.; опубл. 10.05.2010 г.], принцип работы которого основан на одновременном сравнении напряжения входного аналогового сигнала с N опорными уровнями, формируемыми динамическим квантованием. Количество компараторов, составляющих параллельный аналого-цифровой преобразователь динамического типа, равно разрядности выходного двоичного кода, а напряжение опорного уровня для каждого компаратора создается привязанным к нему цифроаналоговым преобразователем. Аналого-цифровой преобразователь с такой архитектурой использует одноразрядные каскады, а следовательно, требует значительных энергетических затрат и занимает большую площадь, так как требуется компенсировать погрешности множества каскадов. Архитектура с многоразрядными каскадами позволяет уменьшить влияние последующих каскадов на линейность преобразования и соотношение сигнал/шум.

Известно устройство конвейерного аналого-цифрового преобразования [Применение высокоскоростных систем/Под редакцией Уолта Кестера. - Москва: Техносфера, 2009. - 368 с. ISBN978-5-94836-199-4], взятое за прототип, содержащее по меньшей мере три блока выборки/хранения далее по тексту БВХ, где первый вход первого БВХ является входом устройства, блок управления, по меньшей мере три линейки компараторов с (N+2) входами и N выходами каждая, где N - количество компараторов в одной линейке, формирователь опорных напряжений, имеющий N выходов, соединенных со всеми линейками компараторов соответственно, по меньшей мере два цифроаналоговых преобразователя и два разностных усилителя, а также формирователь выходного двоичного кода, имеющего (s·N+1) входов и n выходов, являющихся выходом устройства, где s - количество линеек компараторов; n - разрядность выходного двоичного кода, причем выход блока управления соединен со вторым входом всех БВХ и первым входом формирователя выходного двоичного кода, первый вход первой линейки компараторов соединен с выходом первого БВХ, а первый вход второй и последующей линейки компараторов соединен с выходом БВХ текущего этапа преобразования, выход разностного усилителя текущего этапа преобразования соединен с первым входом БВХ последующего этапа преобразования, N выходов каждой линейки компараторов соединены с N входами цифроаналогового преобразователя текущего этапа преобразования, а также с N входами формирователя выходного двоичного кода, выход каждого цифроаналогового преобразователя соединен со вторым входом разностного усилителя текущего этапа преобразования, первый вход которого соединен с выходом БВХ текущего этапа преобразования.

Недостаток данного устройства, принятого за прототип, заключается в возможности пропуска кодов и, следовательно, уменьшении точности аналого-цифрового преобразования, обусловленного наличием нелинейности и импульсных помех цифроаналогового преобразователя.

Предлагаемое устройство направлено на достижение технического результата, заключающегося в исключении пропуска кодов и, соответственно, повышении точности аналого-цифрового преобразования, связанного с нелинейностью и импульсными помехами цифроаналогового преобразователя при определении остаточного напряжения на каждом этапе преобразования.

Указанный технический результат достигается тем, что в устройстве конвейерного аналого-цифрового преобразования, содержащем по меньшей мере три БВХ, где первый вход первого БВХ является входом устройства, блок управления, по меньшей мере три линейки компараторов с (N+2) входами и N выходами каждая, формирователь опорных напряжений, имеющий N выходов, соединенных со всеми линейками компараторов соответственно, по меньшей мере два разностных усилителя, первый вход которых соединен с БВХ текущего этапа преобразования, а также формирователь выходного двоичного кода, имеющий (s·N+1) входов и n выходов, являющихся выходом устройства, причем выход блока управления соединен со вторым входом всех БВХ и первым входом формирователя выходного двоичного кода, первый вход первой линейки компараторов соединен с выходом первого БВХ, а первый вход второй и последующей линейки компараторов соединен с выходом БВХ текущего этапа преобразования, выход разностного усилителя текущего этапа преобразования соединен с первым входом БВХ последующего этапа преобразования, N выходов каждой линейки компараторов соединены с соответствующими входами формирователя выходного двоичного кода, согласно изобретению введены аналоговые мультиплексоры по числу разностных усилителей, имеющие (2·N) входов и один выход каждый, причем N входов каждого аналогового мультиплексора соединены с N выходами формирователя опорных напряжений, а оставшиеся N входов у каждого аналогового мультиплексора соединены с N выходами линейки компараторов текущего этапа преобразования, выход каждого аналогового мультиплексора соединен со вторым входом разностного усилителя текущего этапа преобразования.

В процессе работы устройства аналоговые мультиплексоры будут коммутировать опорное напряжение, значение которого определяется "единичным" кодом на выходе линейки компараторов текущего этапа преобразования, на второй вход разностного усилителя.

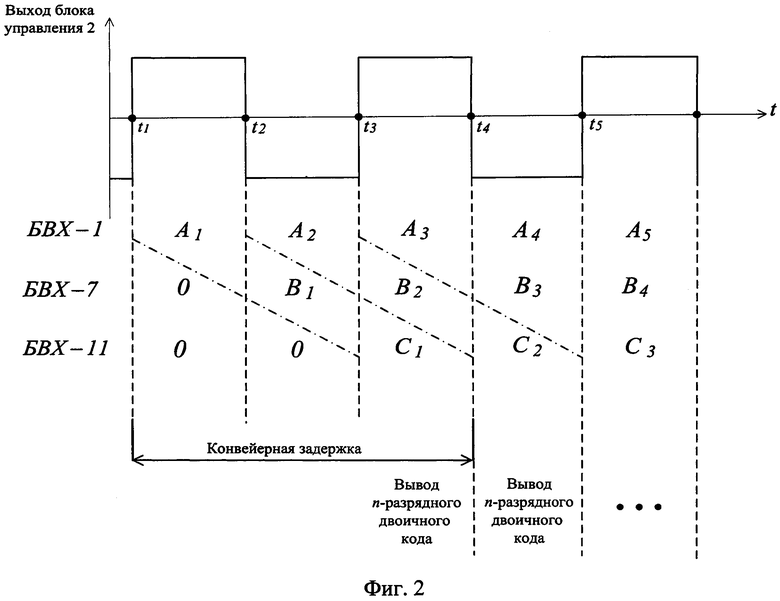

На фиг. 1 показана структурная схема устройства конвейерного аналого-цифрового преобразования.

Устройство состоит из блоков выборки/хранения (БВХ) 1, 7 и 11, блока управления 2, формирователя опорных напряжений 3, линеек компараторов 4, 8 и 12, аналоговых мультиплексоров 5 и 9, разностных усилителей 6 и 10 и формирователя выходного двоичного кода 13.

Принцип работы устройства конвейерного аналого-цифрового преобразования основан на поэтапном сравнении входного аналогового сигнала с N опорными уровнями квантования, и объединении результатов сравнения в выходной двоичный код. При этом на первом этапе преобразования в БВХ-1 сохраняется значение входного аналогового сигнала, а на втором и последующем этапе преобразования в БВХ 7 и 11 сохраняется значение усиленного в N раз остаточного напряжения с выхода разностных усилителей 6 и 10 соответственно. Сохраненные значения выборок аналогового сигнала БВХ 1 и 7 подаются на первый вход линеек компараторов 4 и 8 соответственно, а также на первый вход разностных усилителей 6 и 10, соответственно. Сохраненное значение выборки аналогового сигнала БВХ 11 подается только на линейку компараторов 12 оконечного этапа преобразования. На остальные входы (0-1…0-N) линеек компараторов 4, 8 и 12 подаются значения уровней квантования (Uon,1, …, Uon,N) с формирователя опорных напряжений 3 соответственно. Линейки компараторов 4, 8 и 12 осуществляют сравнение сохраненных значений БВХ 1, 7 и 11 соответственно, с формируемыми уровнями квантования (Uon,1, …, Uon,N) формирователем опорных напряжений. По результатам сравнения на выходе линеек компараторов 4 и 8 формируется N-разрядный "единичный" код, который используется как для формирования выходного n-разрядного двоичного кода в 13, так и в качестве адреса определяемого значения, коммутируемого аналоговыми мультиплексорами 5 и 9 соответственно, опорных напряжений Uon,x и Uon,y, где x=1 … N, y=1 … N, на второй вход разностных усилителей 6 и 10 соответственно. На выходе линейки компараторов 12 формируется N-разрядный "единичный" код, который используется только для формирования выходного n-разрядного двоичного кода в 13. На выходе разностного усилителя 6 формируется усиленное в N раз остаточное напряжение U1, пропорциональное разности сохраненного БВХ 1 значения входного аналогового сигнала Uвх и коммутируемого аналоговым мультиплексором 5 опорного напряжения Uon,x, а на выходе разностного усилителя 10 формируется усиленное в N раз остаточное напряжение Uk, пропорциональное разности остаточного напряжения сохраненного БВХ 7 Ul и коммутируемого аналоговым мультиплексором 9 опорного напряжения Uon,y. Количество компараторов в одной линейке равно количеству формируемых опорных напряжений N.

Разрядность выходного двоичного кода Uвых определяется по формуле

n=(k+1)·log2N,

где k - количество этапов преобразования, на которых осуществлялось формирование усиленного остаточного напряжения.

БВХ 1, 7 и 11 осуществляют выборку аналогового сигнала в момент динамики тактирующего импульса, поступающего с блока управления 2.

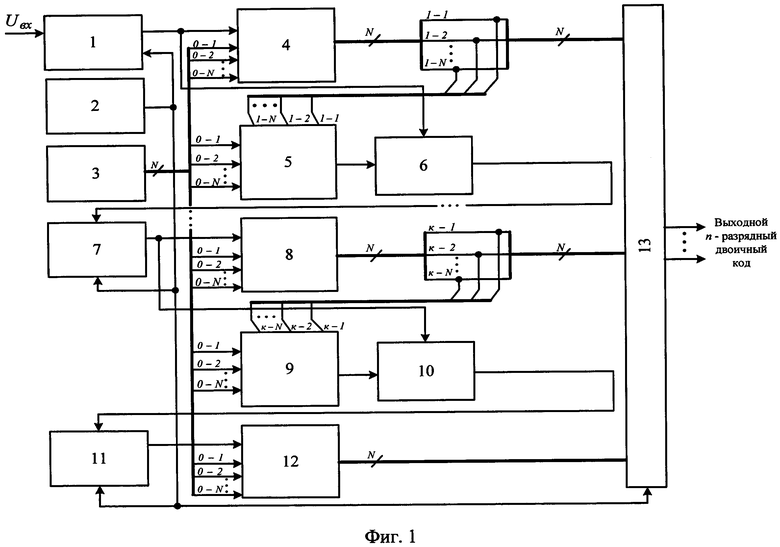

На фиг. 2 показаны временные диаграммы работы устройства конвейерного аналого-цифрового преобразования, где A1, A2, … - выборка, хранение и преобразование отсчетов входного аналогового сигнала на входе устройства; B1, B2, … - выборка, хранение и преобразование отсчетов аналогового сигнала, формируемого разностным усилителем 6; C1, C2, … - выборка, хранение и преобразование отсчетов аналогового сигнала, формируемого разностным усилителем 10.

В момент времени t1 БВХ-1 сохраняет значение отсчета входного аналогового сигнала A1, которое поступает на первый вход линейки компараторов 4, на выходе которой формируется N-разрядный "единичный" код X(XN-1 … X1X0), поступающий в формирователь выходного двоичного кода 13, где он преобразуется в двоичный, а также на адресный вход аналогового мультиплексора 5, определяя тем самым значение опорного напряжения Uon,x, которое коммутируется на второй вход разностного усилителя 6. На выходе разностного усилителя 6 формируется усиленное в N раз остаточное напряжение, определяемое как разность сохраненного в момент времени t1 значения входного аналогового сигнала и коммутированного аналоговым мультиплексором 5 опорного напряжения Uon,x.

В момент времени t2 БВХ-1 сохраняет последующее значение входного аналогового сигнала A2, а БВХ-7 сохраняет значение усиленного остаточного напряжения с предыдущего этапа преобразования B1, которое далее поступает на первый вход линейки компараторов 8, на выходе которой формируется N-разрядный "единичный" код Y(YN-1 … Y1Y0), поступающий в формирователь выходного двоичного кода 13, где он преобразуется в двоичный, а также на адресный вход аналогового мультиплексора 9, определяя тем самым значение опорного напряжения Uon,y. Данное напряжение коммутируется на второй вход разностного усилителя 10, где формируется усиленное в N раз остаточное напряжение, определяемое как разность сохраненного в момент времени t2 блоком БВХ-7 значения усиленного остаточного напряжения с предыдущего этапа преобразования и коммутированного аналоговым мультиплексором 9 опорного напряжения Uon,y.

В момент времени t3 БВХ-1 сохраняет последующее значение входного аналогового сигнала A3, БВХ-7 сохраняет значение усиленного остаточного напряжения с предыдущего этапа преобразования B2, а БВХ-11 сохраняет значение усиленного остаточного напряжения с предыдущего этапа преобразования C1. Данное напряжение поступает на первый вход линейки компараторов 12 оконечного этапа, на выходе которой формируется N-разрядный "единичный" код Z(ZN-1 … Z1Z0), поступающий в формирователь выходного двоичного кода 13, где он преобразуется в двоичный, и объединяется с преобразованными в двоичный код X(XN-1 … X1X0) и Y(YN-1 … Y1Y0) в выходной n-разрядный двоичный код.

Известно [Цифровые устройства и микропроцессоры/Д.А. Безуглов, И.В. Калиенко. - Изд. 2-е - Ростов н/Д: Феникс, 2008. - 468 с.: ил.], что цифроаналоговые преобразователи характеризуются нелинейностью, т.е. разностью реального напряжения, соответствующего входному значению двоичного кода, и напряжения которое должно соответствовать коду в идеальном случае, а также импульсными помехами, т.е. крутыми всплесками или провалами в выходном напряжении, возникающие во время смены значений входного кода. Например, при переходе значения кода 011…1111 к значению 100…0000, ключ самого старшего разряда цифроаналогового преобразователя с суммированием весовых токов откроется позже, чем закроются ключи младших разрядов, то на выходе цифроаналогового преобразователя некоторое время будет существовать сигнал, соответствующий коду 000…0000. Одновременно с усилением полезного сигнала в разностном усилителе будет усиливаться и шум, вносимый цифроаналоговым преобразователем. Использование аналоговых мультиплексоров позволяет исключить эти импульсные помехи и нелинейность, так как опорное напряжение, определяемое "единичным" N-разрядным кодом на выходе линейки компараторов, будет прямо проходить на второй вход разностного усилителя. При переходе значения кода от 011…1111 к значению 100…0000 откроется только один ключ, соответствующий номеру опорного напряжения 100…0000. Аналоговый мультиплексор представляет собой набор аналоговых ключей с повышенным быстродействием (порядка 1 нс), количество которых равно количеству уровней квантования N, и дешифратор, декодирующий адрес, который включает только адресованный ключ, блокируя остальные. В качестве аналоговых ключей могут быть использованы МДП - транзисторы, имеющие малое сопротивление в проводящем состоянии, крайне высокое сопротивление в состоянии отсечки (до сотен ГОм), малые токи утечки и малую емкость.

Применение предложенного устройства конвейерного аналого-цифрового преобразования позволяет исключить пропуски кодов, обусловленные наличием нелинейности и импульсными помехами цифроаналогового преобразователя, и, следовательно, увеличить точность аналого-цифрового преобразования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1720160A1 |

| СПОСОБ КАСКАДНО-КОНВЕЙЕРНОГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2014 |

|

RU2571916C2 |

| ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 2006 |

|

RU2308148C1 |

| Цифровое устройство для анализа сигналов | 1985 |

|

SU1545227A1 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2002 |

|

RU2240649C2 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1988 |

|

SU1594692A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 2006 |

|

RU2308802C1 |

Изобретение относится к электроизмерительной и вычислительной технике и может быть использовано для высокоточного преобразования быстроизменяющихся электрических сигналов в цифровой код. Техническим результатом является повышение точности аналого-цифрового преобразования, связанного с нелинейностью и импульсными помехами цифроаналогового преобразователя при определении остаточного напряжения на каждом этапе преобразования. Устройство содержит блоки выборки/хранения, блок управления, линейки компараторов, формирователь опорных напряжений, разностные усилители, аналоговые мультиплексоры, формирователь выходного двоичного кода. 2 ил.

Устройство конвейерного аналого-цифрового преобразования, содержащее по меньшей мере три блока выборки/хранения (БВХ), где первый вход первого БВХ является входом устройства, блок управления, по меньшей мере три линейки компараторов с (N+2) входами и N выходами каждая, где N - количество компараторов в одной линейке, формирователь опорных напряжений, имеющий N выходов, соединенных со всеми линейками компараторов соответственно, по меньшей мере два разностных усилителя, первый вход которых соединен с выходом БВХ текущего этапа преобразования, а также формирователь выходного двоичного кода, имеющий (s·N+1) входов, где s - количество линеек компараторов и n выходов, где n - разрядность выходного двоичного кода, являющиеся выходом устройства, причем выход блока управления соединен со вторым входом всех БВХ и первым входом формирователя выходного двоичного кода, первый вход первой линейки компараторов соединен с выходом первого БВХ, а первый вход второй и последующей линейки компараторов соединен с выходом БВХ текущего этапа преобразования, выход разностного усилителя текущего этапа преобразования соединен с первым входом БВХ последующего этапа преобразования, N выходов каждой линейки компараторов соединены с соответствующими входами формирователя выходного двоичного кода, отличающееся тем, что оно снабжено аналоговыми мультиплексорами по числу разностных усилителей, имеющими (2·N) входов и один выход каждый, причем N входов каждого аналогового мультиплексора соединены с N выходами формирователя опорных напряжений, а оставшиеся N входов у каждого аналогового мультиплексора соединены с N выходами линейки компараторов текущего этапа преобразования, выход каждого аналогового мультиплексора соединен со вторым входом разностного усилителя текущего этапа преобразования.

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Конвейерный аналого-цифровой преобразователь | 1986 |

|

SU1381706A1 |

| US 2010182182 A1, 22.07.2010 | |||

| US 2010295714 A1, 25.11.2010 | |||

| US 7283083 B1, 16.10.2007. | |||

Авторы

Даты

2015-11-27—Публикация

2014-12-08—Подача