регистра и счетному входу счетчика, информационный выход которого подключен к входу блока сравнения, выход которого подключен к тактовому входу блока сравнения, вход квадратора, первый вход элемента И второй вход элемента И являются соответственно

первым, вторым и третьим входами Формирователя опорного сигнала, выходом которого является выход масштабирую- , щего усилителя, выходы обнуления - счетчика и первого регистра объединены и являются четвертым входом формирователя опорного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинированный аналого-циффровой преобразователь | 1986 |

|

SU1363468A1 |

| Система связи с дельта-модуляцией | 1983 |

|

SU1163476A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ УДАРНОГО ИМПУЛЬСА | 2006 |

|

RU2325660C1 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

| Система индивидуального радиовызова | 1992 |

|

SU1838881A3 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Адаптивное устройство анализа | 1986 |

|

SU1386938A1 |

| Генератор гармонических сигналов | 1989 |

|

SU1626379A1 |

| Устройство для кодирования звуковых сигналов | 1978 |

|

SU681552A2 |

Цель изобретения - повышение точности. Устройство содержит цифровой фильтр, первый аналого-цифровой преобразователь, блок дискретного преобразования Фурье, синхронизатор. Дополнительно введены коммутатор, цифроаналоговый преобразователь, второй аналого-цифровой преобразователь и формирователь опорного сигнала. 1 ил.

Изобретение относится к вычислительной технике и может использоваться для анализа данных в различных цифровых системах обработки информа- ции.

Целью изобретения является повышение точности обработки информации (за счет дополнительного аналого-ииф- рового преобразования данных на выходе цифрового фильтра с учетом сжатия динамического диапазона входного сигнала) .

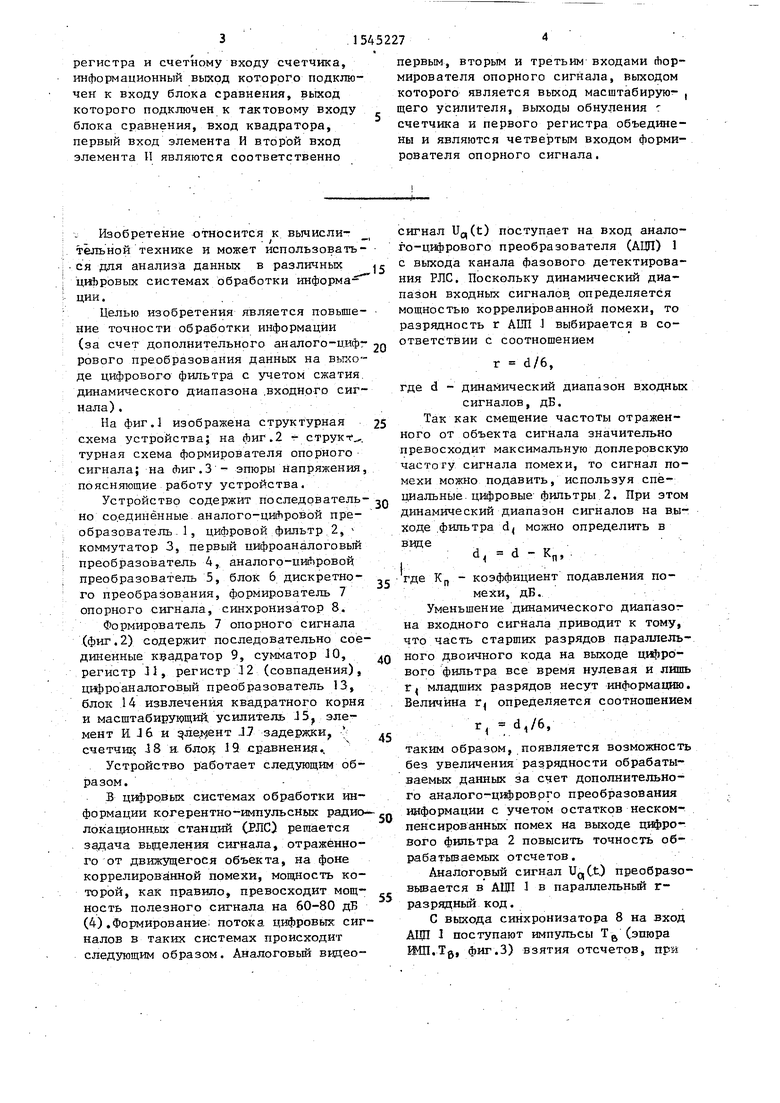

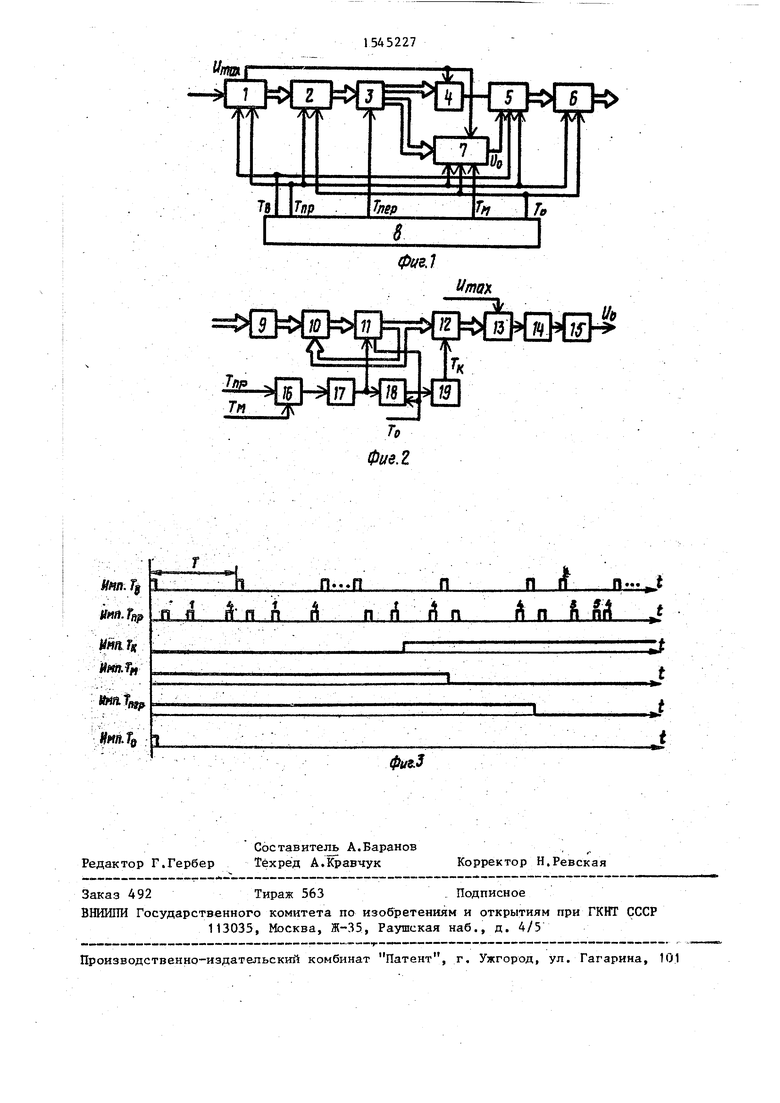

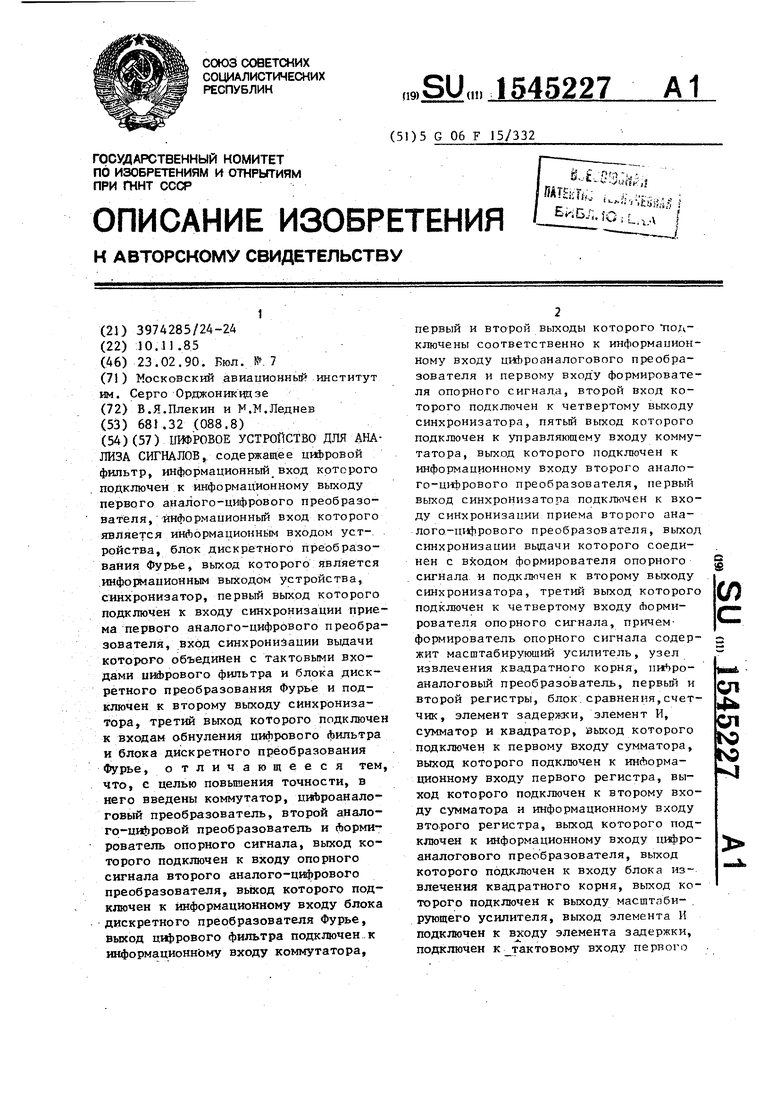

На фиг.1 изображена структурная схема устройства; на Лиг.2 - структ турная схема формирователя опорного сигнала; на Фиг.З - эпюры напряжения, поясняющие работу устройства.

Устройство содержит последователь- но соединенные аналого-цифровой преобразователь 1, цифровой фильтр 2, коммутатор 3, первый цифроаналоговый преобразователь 4, аналого-цифровой преобразователь 5, блок 6 дискретного преобразования, формирователь 7 опорного сигнала, синхронизатор 8.

Формирователь 7 опорного сигнала (фиг.2) содержит последовательно соединенные квадратор 9, сумматор 10, регистр II, регистр J2 (совпадения), цифроаналоговый преобразователь 13, блок 14 извлечения квадратного корня и масштабирующий усилитель 15f элемент И J6 и длелент -П задержки, счетчик J8 и блок, 19 сравнения..

Устройство работает следующим образом.

В цифровых системах обработки информации когерентно-импульсных радиолокационных станций СРЛС) решается задача выделения сигнала, отраженного от движущегося объекта, на фоне коррелированной помехи, мощность которой, как правило, превосходит мощ- ность полезного сигнала на 60-80 дБ (4).Формирование потока цифровых сигналов в таких системах происходит следующим образом. Аналоговый видео

5

с

п

5

п

Q .,

0

сигнал U о, (О поступает на вход аналого-цифрового преобразователя (АЦП) 1 с выхода канала фазового детектирования РЛС. Поскольку динамический диапазон входных сигналов определяется мощностью коррелированной помехи, то разрядность г ALII 1 выбирается в соответствии с соотношением

г d/6,

где d - динамический диапазон входных

сигналов, дБ.

Так как смещение частоты отраженного от объекта сигнала значительно превосходит максимальную доплеровскую частоту сигнала помехи, то сигнал помехи можно подавить, используя специальные цифровые фильтры 2. При этом динамический диапазон сигналов на выходе фильтра d можно определить в виде

d d - Кп,

где Кп - коэффициент подавления помехи, дБ.

Уменьшение динамического диапазона входного сигнала приводит к тому, что часть старших разрядов параллельного двоичного кода на выходе цифрового фильтра все время нулевая и лишь tj младших разрядов несут информацию. Величина г определяется соотношением

г, d,/6,

таким образом, появляется возможность без увеличения разрядности обрабатываемых данных за счет дополнительного аналого-цифроврго преобразования информации с учетом остатков нескомпенсированных помех на выходе цифрового фильтра 2 повысить точность обрабатываемых отсчетов.

Аналоговый сигнал Ua(t) преобразовывается в АЦП 1 в параллельный г- разрядный код.

С выхода синхронизатора 8 на вход А1Щ 1 поступают импульсы Т6 (эпюра ШП.ТВ, фиг.З) взятия отсчетов, при

этом на выходах компараторов АЦП I устанавливается параллельный единичный m-разрядный код (г loj.m), который затем преобразовывается в двоичный код, для чего на его вход поступают . импульсы преобразования Thp (эпюра ИМП.ТПр, фиг.З). Величина опорного сигнала UWaKC в АШ 1 выбирается, исходя из максимального значения динамического диапазона входных сигналов.

С выхода АЦП I двоичный код поступает в цифровой Фильтр 2, который осуществляет сжатие динамического диапазона.

С выхода цифрового Фильтра 2 цифровой поток сигналов поступает в коммутатор 3 (фиг.1), на управляющий вход которого с третьего выхода синхронизатора поступает сигнал Тпрр переключения, показанный на соответствующей эпюре (фиг.З). В силу этого цифровые отсчеты поступают в формирователь 7 опорного сигнала, который определяет опорный сигнал Uon дополнительного АЦП 5 путем усреднения остатков нескомпенсированной помехи на выходе блока 2 за М периодов.

На вход элемента И 16 поступает сигнал Т (эпюра ШП.Т фиг.З) с вьтхода синхронизатора 8, в силу этого И импульсов ТПр проходят через элемент И 16 и поступают на вход элемента 17 задержки. Информация со второго выхода коммутатора 3 через квадратор 9 поступает на вход сумматора 10, в котором суммируется с предыдущим накопленным значением квадрата огибающей выходного сигнала сЬильтра, а затем импульсом Т„р (импульс I, эпюра ИМП.ТПр, фиг.З), поступающим с выхода элемента 17 задержки, записывается в регистр 11, который в начале работы обнуляется импульсом Т . При этом величина Ј4 задержки сигнала элементом 17 определяется соотношением

- f о. - о

деЈ

Ф

л f t °ке

+ ° кь

+ Ј

Ј

/ч

О ьа. Ч

- времена задержек сигнала соответственно в блоках 2, 9 и 10.

В процессе накопления сигнала перый счетчик 18, предварительно обну

45227

ленный импульсом Т0, считает импульсы ТПр, а выходной код L, счетчика 18 поступает в блок 19 сравнения, в котором сравнивается с цифровым кодом М. В момент равенства L,, М на выходе блока 19 формируется сигнал Тк (эпюра ИМП.ТК, Фиг.З), поступающий на вход регистра 12 совпадения. С выхода регистра 11 через регистр J 2 на вход второго цифроаналогового преобразователя (ПАП) 13 поступит усредненное значение не скомпенсированных остатков помехи Z, которое определяется с помощью соотношения

10

15

Z ZL

м г и п,

где п 1,М - текущий номер отсчета; - - отсчеты сигналов -на выходе фильтра 2.

На выходе масштабирующего усилителя 15 устанавливается опорный сиг

нал U

U

on

ОП

в соответствии с алгоритмом - КлПГ,

0

5

0

где К - коэффициент масштабирующего

усилителя 15/

После формирования опорного сигнала Uon информация с первого выхода коммутатора 3 начинает поступать в ЦАП 4, в котором преобразовывается в аналоговую форму, причем цифроанало- говое преобразование производится относительно UWQ)tc. Далее аналоговый 5 сигнал поступает в АШ1 5, в котором производится аналого-цифровое преобразование с использованием опорного сигнала Uon . С выхода А1ЛТ 5 информация поступает в блок 6 дискретного преобразования урье (ДПФ), который осуществляет спектральный анализ входного сигнала в соответствии со следующим алгоритмом И- nl

х(к) 2Lx(n)wH,

где К О, N-1

текущий номер частотной гармоники; N - объем анализируемой

выборки;

х(п) - входной сигнал блока 6 ДПФ;

пг

WM eexp

j-j |-пК весовые коэффициенты преобразования.

Авторы

Даты

1990-02-23—Публикация

1985-11-10—Подача