Изобретение относится к области обработки видеосигналов, а именно к устройствам и способам приведения к единому формату различных цифровых видеосигналов, и может применяться в устройствах цифровой обработки изображений, входящих в состав систем видеонаблюдения и видеоаналитики.

В настоящее время в связи с развитием технологий происходит улучшение качества видеоизображения и появление новых форматов видеосигнала: увеличивается разрешение и частота кадров видеоизображения, создаются новые высокоскоростные интерфейсы передачи видеоизображений. Тем не менее, до сих пор остаются актуальными видеоизображения с небольшим разрешением и устоявшиеся форматы видеосигнала. Следовательно, к современным устройствам обработки изображений предъявляются требования умения обработки как новых, так и старых форматов видеосигнала. Для обработки каждого из существующих форматов видеоизображения требуются различные аппаратные модули, что усложняет конструкции устройств и способов обработки видеоизображения. Удобней и выгодней производить обработку над одним единым видом видеосигнала, поэтому для сокращения количества оборудования разные сигналы приводят к единому виду.

Наиболее близкими к заявленному изобретению являются устройство и способ приведения к единому формату различных цифровых видеосигналов (заявка US 2005206784), содержащие процессор для ввода видео, включающий в себя преобразователь форматов и конвертер цветового пространства для систем сжатия видео. Конвертер преимущественно преобразует сигналы Bayer в видеосигналы GBR 4:1:1. Он так же преобразует YCbCb 4:2:2 с прогрессивной и чересстрочной разверткой в YCbCb 4:1:1 и обеспечивает преобразование цветового пространства между RGB и YCbCr. Процессор выполняет прием видеосигнала с низкой пиксельной частотой, например 27 МГц, и работает только с параллельными интерфейсами, такими как Raw, имеющим пиксельную частоту, сигналы горизонтальной и вертикальной синхронизации, и синхросигнал четного и нечетного полукадров, и форматами SDTV - ВТ.601 и ВТ.656. Поддерживаемые размеры изображения могут варьироваться от 352*288 до 720*480 (30 кадров в секунду) или 720*576 (25 кадров в секунду). Данные устройство и способ выбраны в качестве прототипов заявленного изобретения.

Недостатком устройства и способа прототипов является то, что они не поддерживают прием изображений высокой четкости (разрешения HD, Full HD, Ultra HD) и высокоскоростных видеосигналов в последовательных интерфейсах, а также то, что преобразованные с целью дальнейшего кодирования видеосигналы в GBR или YCbCr 4:1:1 не удобны для последующей обработки кадров видеоизображения.

Задачей заявленного изобретения является создание устройства и способа приведения к единому формату различных цифровых видеосигналов, универсальных по обрабатываемым видеосигналам, которые позволяют принимать от одного до одиннадцати видеосигналов одновременно по различным параллельным и последовательным интерфейсам, причем видеоизображения, передаваемые посредством видеосигналов, могут иметь различное разрешение и количество кадров в секунду, разное цветовое пространство (RGB, YcbCr, Bayer, Mono и др.), разную пиксельную субдискретизацию (4:4:4, 4:2:2, 4:2:0 и т.д.), различные стандартизированные форматы (ВТ.656, ВТ.1120, HiSPi, MIPI CSI 2, MIPI CSI 3).

Поставленная задача решена путем создания устройства приведения к единому формату различных цифровых видеосигналов, содержащего параллельный, последовательный, MIPI CSI 2 и MIPI CSI 3 порты ввода видео, выходы которых соединены со входами мультиплексора, выход которого соединен со входом модуля обрезки и децимации кадров, а также массив управляющих регистров, выходы которого соединены с портами ввода видео, мультиплексором и модулем обрезки и децимации кадров, при этом массив управляющих регистров выполнен с возможностью управления и задания конфигураций параллельного, последовательного, MIPI CSI 2 и MIPI CSI 3 портов ввода видео, мультиплексора и модуля обрезки и децимации кадров; параллельный, последовательный, MIPI CSI 2 и MIPI CSI 3 порты ввода видео выполнены с возможностью приема входных видеосигналов, при этом приема синхросигналов и данных в зависимости от конфигурации порта по различным фронтам входного тактового сигнала, с возможностью пересинхронизации входных видеосигналов на внутреннюю частоту, приведения их к унифицированному пиксельному формату (УПФ) и направления в мультиплексор, выполненный с возможностью осуществления выбора нескольких потоков видеосигналов и направления их в модуль обрезки и децимации кадров, выполненный с возможностью уменьшения размеров кадра по вертикали и по горизонтали и осуществления децимации потоков видеосигналов по кадрам.

В предпочтительном варианте осуществления устройства параллельный порт выполнен с возможностью инвертирования входных управляющих синхросигналов, а также с возможностью создания из входного видеосигнала на основе горизонтальной и вертикальной синхронизации синхросигнала четного и нечетно полукадров, если входной видеосигнал поступает в чересстрочной развертке без этого сигнала.

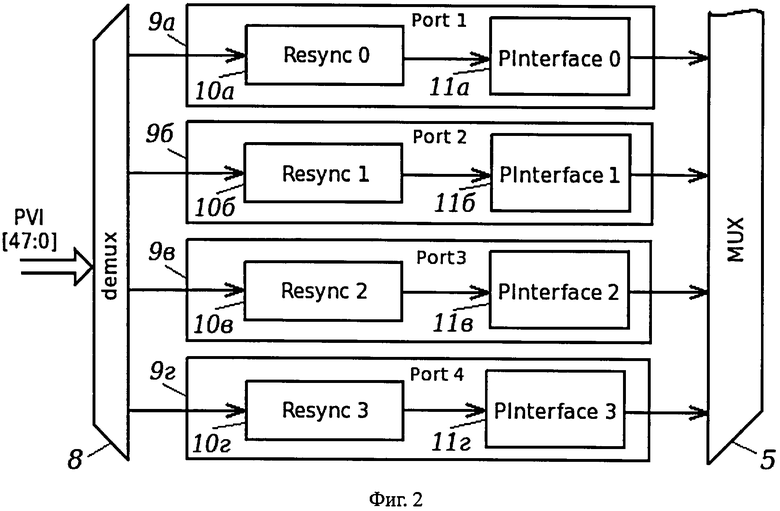

В предпочтительном варианте осуществления устройства параллельный порт содержит внешние выводы, распределенные по входам демультиплексора, выходы которого соединены со входами модулей пересинхронизации, выходы которых связаны со входами модулей преобразования, выходы которых связаны со входами мультиплексора, при этом демультиплексор выполнен с возможностью разделения объединенного потока входных видеосигналов и направления разделенных потоков входных видеосигналов на модули пересинхронизации, выполненные с возможностью пересинхронизации потока входных видеосигналов на внутреннюю частоту устройства и передачи пересинхронизованного потока входных видеосигналов в модули преобразования, выполненные с возможностью преобразования сигналов синхронизации, перемещения цветовых компонент на шине данных и передачи преобразованного потока входных видеосигналов в мультиплексор.

В предпочтительном варианте осуществления устройства параллельный порт выполнен с возможностью приема входных видеосигналов с пиксельной частотой до 150 МГц по меньшей мере от одного источника видеосигнала, который имеет параллельный интерфейс.

В предпочтительном варианте осуществления устройства параллельный порт выполнен с возможностью преобразования по меньшей мере в семь конфигураций, причем в каждой конфигурации параллельный порт выполнен с возможностью приема от 1-го до 4-х потоков входных видеосигналов одновременно.

В предпочтительном варианте осуществления устройства параллельный порт выполнен с возможностью приема от 1-го до 4-х потоков входных видеосигналов одновременно с помощью 4-х групп выводов LVTTL, выполненных с возможностью приема синхросигналов от источника входного видеосигнала, в каждую из которых входят: пиксельная частота, горизонтальная и вертикальная синхронизации и синхросигнал четного и нечетного полукадров; а также с помощью 40-битной шины данных, выполненной с возможностью распределения между группами выводов LVTTL, в зависимости от конфигурации параллельного порта.

В предпочтительном варианте осуществления устройства каждый модуль пересинхронизации предназначен для своего потока входных видеосигналов и независим от другого модуля пересинхронизации.

В предпочтительном варианте осуществления устройства модуль пересинхронизации выполнен с возможностью приема по переднему, по заднему или по обоим фронтам пиксельной частоты входных видеосигналов, а после осуществления пересинхронизации, модуль пересинхронизации выполнен с возможностью формирования нового тактового сигнала, по переднему фронту которого передают данные внутри устройства.

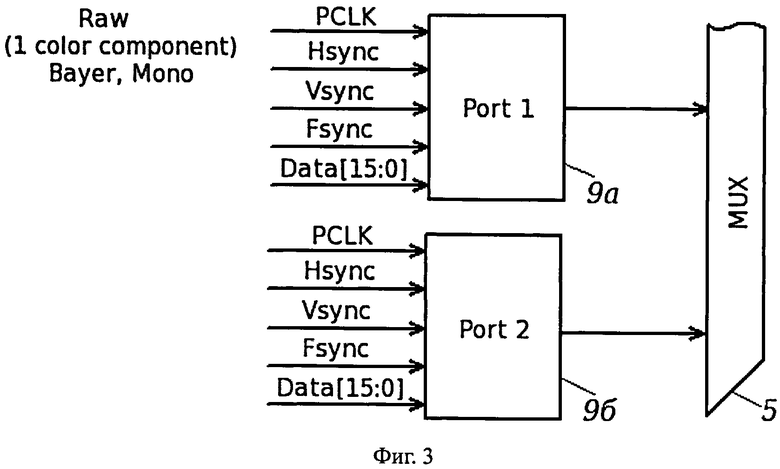

В предпочтительном варианте осуществления устройства в первой конфигурации параллельный порт разделен на два одинаковых порта, каждый из которых выполнен с возможностью приема видеосигналов в raw формате с одной цветовой компонентой за такт и содержит выводы для приема сигналов пиксельной частоты, горизонтальной и вертикальной синхронизации, синхросигнала четного и нечетного полей кадра, а также содержит 16-битную шину данных.

В предпочтительном варианте осуществления устройства во второй конфигурации параллельный порт настроен на прием одного raw потока входных видеосигналов с тремя цветовыми компонентами за такт и содержит выводы для приема сигналов пиксельной частоты, горизонтальной и вертикальная синхронизации, синхросигнала четного и нечетного полукадра, а также содержит 36-битную шину данных, по 12 бит для каждой из трех цветовых компонент.

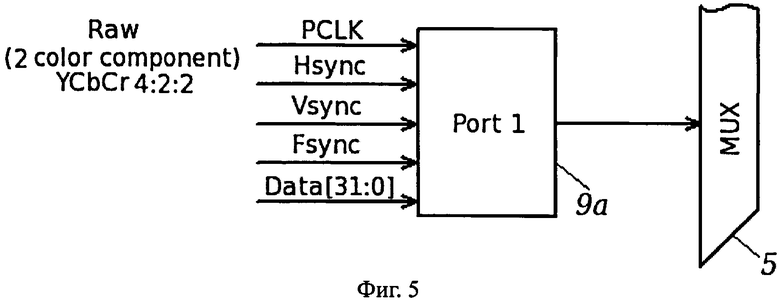

В предпочтительном варианте осуществления устройства в третьей конфигурации параллельный порт настроен на прием одного raw потока входных видеосигналов с двумя цветовыми компонентами за такт и содержит выводы для приема сигналов пиксельной частоты, горизонтальной и вертикальной синхронизации, синхросигнала четного и нечетного полукадра, а также содержит 32-битную шину данных, по 16 бит для каждой из двух цветовых компонент.

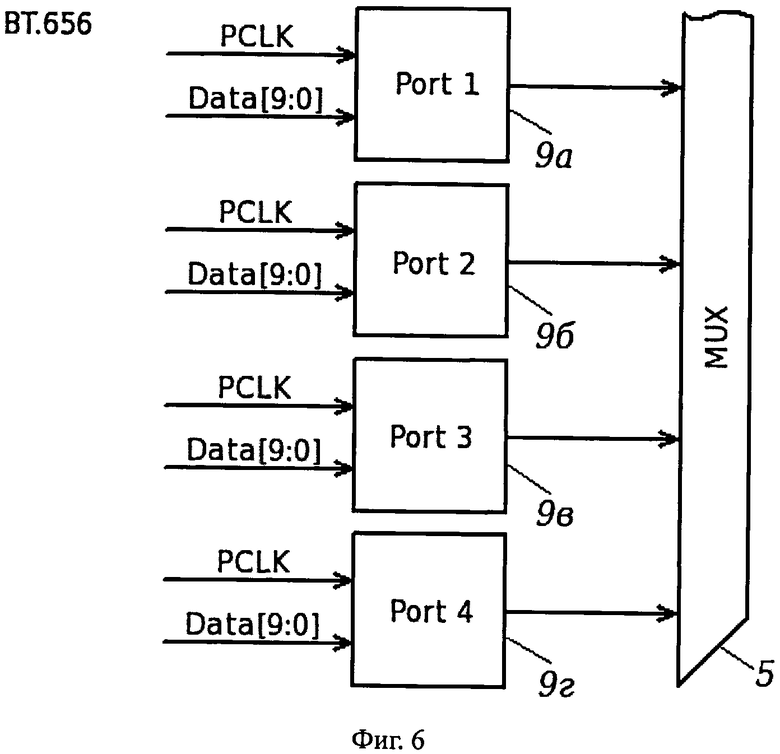

В предпочтительном варианте осуществления устройства в четвертой конфигурации параллельный порт разделен на четыре одинаковых порта, каждый из которых выполнен с возможностью приема видеосигналов в формате ВТ.656 10 и 8 бит.

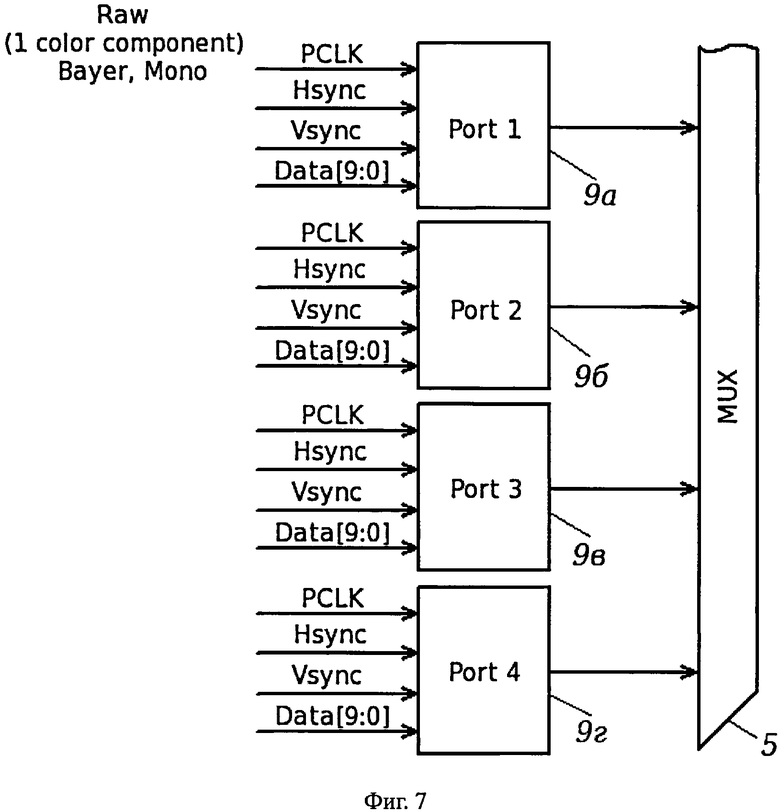

В предпочтительном варианте осуществления устройства в пятой конфигурации параллельный порт разделен на четыре одинаковых порта, каждый из которых содержит 10-битную шину данных и выводы для приема сигналов пиксельной частоты и горизонтальной и вертикальной синхронизации.

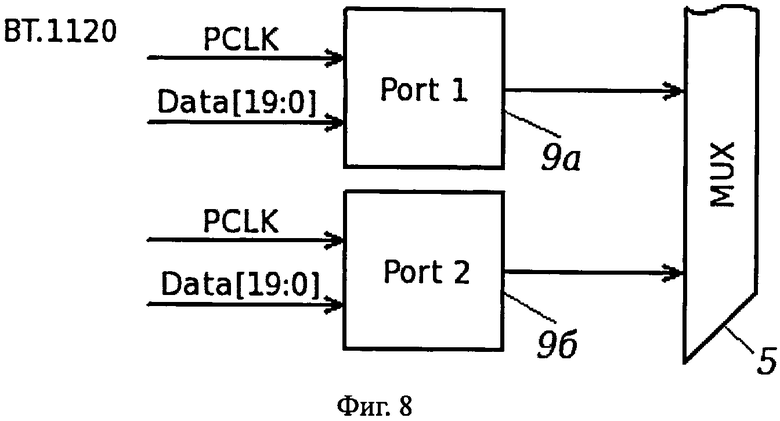

В предпочтительном варианте осуществления устройства в шестой конфигурации параллельный порт разделен на два одинаковых порта, каждый из которых выполнен с возможностью приема видеосигналов в формате ВТ.1120 и содержит 20-битную шину данных.

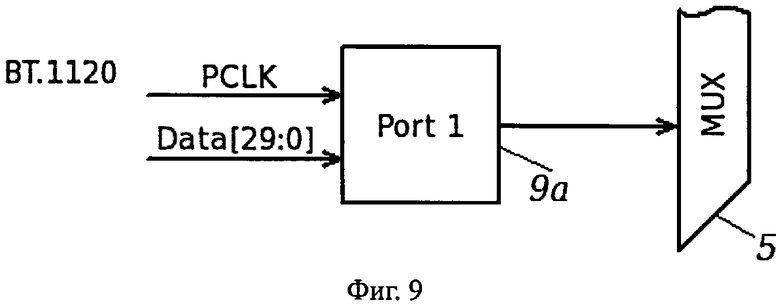

В предпочтительном варианте осуществления устройства в седьмой конфигурации параллельный порт настроен на прием видеосигналов в формате ВТ.1120 и содержит 30-битную шину данных.

В предпочтительном варианте осуществления устройства модуль преобразования содержит на входе мультиплексор, первый выход которого соединен с первым входом модуля перемещения цветовых компонент, а второй выход соединен со входом модуля выделения синхросигналов, выход которого соединен со вторым входом модуля перемещения цветовых компонент, выход которого соединен со входом модуля преобразования сигналов, при этом модуль выделения синхросигналов выполнен с возможностью выделения синхросигналов из потока видеосигналов форматов ВТ.656 и ВТ.1120, модуль перемещения цветовых компонент выполнен с возможностью изменения порядка следования компонент и изменения размещения цветовой компоненты в разрядах шины данных путем программирования модуля, модуль преобразования сигналов выполнен с возможностью преобразования сигналов строчной и кадровой синхронизации, а также синхросигнала четного и нечетного полукадров, а мультиплексор выполнен с возможностью направления потока входных видеосигналов в модуль выделения синхросигналов и затем в модуль перемещения цветовых компонент, если поток входных видеосигналов представлен в формате ВТ.1120 или ВТ.656, а также с возможностью направления потока входных видеосигналов сразу в модуль перемещения цветовых компонент, минуя модуль выделения синхросигналов, если поток входных видеосигналов представлен в других поддерживаемых видеоформатах.

В предпочтительном варианте осуществления устройства последовательный порт содержит четыре входных секции, выходы которых соединены со входами десериалайзеров, выходы которых соединены со входами модулей сборки битов, выходы которых соединены со входами блока преобразования входного видеосигнала в УПФ, причем входные секции выполнены с возможностью приема входных видеосигналов, преобразования уровней напряжения дифференциальных сигналов и передачи видеосигналов в десериалайзеры, выполненные с возможностью приема данных видеосигналов по переднему, заднему или обоим фронтам пиксельной частоты в форматах Bayer или Mono с разрядностью 8, 10, 12, 14 или 16 и с возможностью автоматической подстройки для приема данных видеосигнала в середине "полки" принимаемого синхросигнала или ближе к переднему или заднему фронту путем выбора одного из выходов DLL, соединенных с десериалайзерами, при этом разрядность данных на выходе десериалайзеров составляет 32 бита, по 8 бит на каждую линию, а также с возможностью передачи данных видеосигналов на модули сборки битов, выполненные с возможностью сборки битов пикселя в 16-битный формат, в каждой линии, причем, если разрядность принимаемого пикселя менее 16 бит, то принятые биты размещают в старших битах 16-разрядного слова, а младшие заполняют нулями, а также с возможностью передачи сформированных пикселей в заданной очереди в блок преобразования входного видеосигнала в УПФ, выполненный с возможностью упорядочивания пикселей, поступающих с разных секций, в один поток и создания синхросигналов, при этом формирования на выходе УПФ.

В предпочтительном варианте осуществления устройства каждая входная секция имеет четыре дифференциальных вывода для подключения линий передач данных и дифференциальный вывод для пиксельной частоты.

В предпочтительном варианте осуществления устройства входная секция имеет на входах преобразователи уровней дифференциальных сигналов, выполненные с возможностью приема по LVDS, subLVDS, SLVS-400 и SLVS-200, при этом данные с выходов преобразователей уровней дифференциальных сигналов поступают на десериалайзеры.

В предпочтительном варианте осуществления устройства последовательный порт выполнен с возможностью приема входных видеосигналов, имеющих последовательные интерфейсы с частотой передачи данных до 800 Мбит в секунду на одну линию передачи, и поддерживает прием входных видеосигналов высокой и сверхвысокой четкости.

В предпочтительном варианте осуществления устройства порт MIPI CSI 2 выполнен с возможностью конфигурирования для приема данных по восьми, четырем, двум или одной линиям данных, при этом каждая линия данных обеспечивает прием на скорости до 1500 Мбит в секунду.

В предпочтительном варианте осуществления устройства порт MIPI CSI 2 содержит по меньшей мере один модуль CSI RX DPHY, соединенный с приемником видеосигнала по протоколу MIPI CSI 2, который соединен по меньшей мере с одним декодером, который соединен по меньшей мере с одним модулем преобразования в УПФ, а приемник видеосигнала содержит по меньшей мере один порт данных, при этом модуль CSI RX DPHY выполнен с возможностью реализации физического уровня протокола MIPI CSI 2 и состоит из одного блока Clock Lane и по меньшей мере одного блока Data Lane, причем блок Data Lane содержит десериалайзер, выполненный с возможностью преобразования последовательных данных в многоразрядный код, а блок Clock Lane содержит делитель частоты, выполненный с возможностью формирования синхросигнала для многоразрядных данных; приемник видеосигнала выполнен с возможностью приема многоразрядных данных от блока Data Lane и компоновки их в один поток, с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, а также с возможностью передачи данных и управляющих сигналов с порта данных по меньшей мере в один декодер, выполненный с возможностью анализа формата данных и формирования сигналов управления для модуля преобразования в УПФ, а также с возможностью передачи данных на многоразрядные входы модуля преобразования в УПФ, выполненного с возможностью преобразования потока видеоданных в унифицированный пиксельный формат (УПФ).

В предпочтительном варианте осуществления устройства модуль CSI RX DPHY выполнен с возможностью реализации физического уровня протокола MIPI CSI 2 и состоит из одного блока Clock Lane и четырех блоков Data Lane, причем блок Data Lane содержит десериалайзер, выполненный с возможностью преобразования последовательных данных в 8-разрядный код, а блок Clock Lane содержит делитель частоты, выполненный с возможностью формирования синхросигнала для 8-разрядных данных, при этом для приема по восьми блокам Data Lane используют конфигурацию порта MIPI CSI 2 с двумя модулями CSI RX DPHY; приемник видеосигнала выполнен с возможностью приема 8-разрядных данных от блока Data Lane и компоновки их в один поток, с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, а также с возможностью передачи данных и управляющих сигналов с порта данных в два декодера, выполненные с возможностью анализа формата данных и формирования сигналов управления для модуля преобразования в УПФ, с возможностью преобразования данных в 16-разрядный формат, при этом передачи 5, 6, 7, 8, 10, 12, 14-разрядных данных в старшие разряды 16-разрядных выходов и заполнения младших разрядов нулями, а также с возможностью передачи данных на 16-разрядные входы двух модулей преобразования в УПФ, выполненных с возможностью преобразования потока видеоданных в унифицированный пиксельный формат (УПФ).

В предпочтительном варианте осуществления устройства приемник видеосигнала выполнен с возможностью приема 8-разрядных данных от блока Data Lane и компоновки их в один поток, а также с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, при этом цветовые компоненты пикселя могут выдаваться в различной последовательности, в зависимости от формата, по меньшей мере через один 24-разрядный порт данных, при этом, если порт MIPI CSI 2 сконфигурирован как один порт, то данные и сигналы синхронизации выдают на нулевой порт данных.

В предпочтительном варианте осуществления устройства порт MIPI CSI 3 содержит модуль CSI3 RX DPHY, соединенный с приемником видеосигнала по протоколу MIPI CSI 3, который соединен с декодером, который соединен с модулем преобразования в УПФ, а приемник видеосигнала содержит по меньшей мере один порт данных, при этом модуль CSI RX DPHY выполнен с возможностью реализации физического уровня протокола MIPI CSI 3 и состоит из выделенного канала управления, выполненного с возможностью передачи управляющей информации для источника видеосигнала, и по меньшей мере одного блока Data Lane, причем блок Data Lane содержит десериалайзер, выполненный с возможностью преобразования последовательных данных в многоразрядный код; приемник видеосигнала выполнен с возможностью приема многоразрядных данных от блока Data Lane и компоновки их в один поток, с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, а также с возможностью передачи данных и управляющих сигналов с порта данных в декодер, выполненный с возможностью анализа формата данных и формирования сигналов управления для модуля преобразования в УПФ, а также с возможностью передачи данных на многоразрядные входы модуля преобразования в УПФ, выполненного с возможностью преобразования потока видеоданных в унифицированный пиксельный формат (УПФ).

В предпочтительном варианте осуществления устройства модуль CSI RX DPHY выполнен с возможностью реализации физического уровня протокола MIPI CSI 3 и состоит из выделенного канала управления, выполненного с возможностью передачи управляющей информации для источника видеосигнала, и четырех блоков Data Lane, причем блок Data Lane содержит десериалайзер, выполненный с возможностью преобразования последовательных данных в 8-разрядный код, а для приема по восьми блокам Data Lane используют конфигурацию порта MIPI CSI 3 с двумя модулями CSI RX DPHY; приемник видеосигнала выполнен с возможностью приема 8-разрядных данных от блока Data Lane и компоновки их в один поток, с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, а также с возможностью передачи данных и управляющих сигналов с порта данных в декодер, выполненный с возможностью анализа формата данных и формирования сигналов управления для модуля преобразования в УПФ, с возможностью преобразования данных в 16-разрядный формат, при этом передачи 5, 6, 7, 8, 10, 12, 14-разрядных данных в старшие разряды 16-разрядных выходов и заполнения младших разрядов нулями, а также с возможностью передачи данных на 16-разрядные входы модуля преобразования в УПФ, выполненного с возможностью преобразования потока видеоданных в унифицированный пиксельный формат (УПФ).

В предпочтительном варианте осуществления устройства приемник видеосигнала выполнен с возможностью приема 8-разрядных данных от блока Data Lane и компоновки их в один поток, а также с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, при этом цветовые компоненты пикселя могут выдаваться в различной последовательности, в зависимости от формата, через по меньшей мере один 24-разрядный порт данных, при этом, если порт MIPI CSI 3 сконфигурирован как один порт, то данные и сигналы синхронизации выдают на нулевой порт данных.

В предпочтительном варианте осуществления устройства модуль обрезки и децимации кадров выполнен с возможностью приведения сигналов, пришедших от портов ввода видео, к УПФ в случае, если при некоторых условиях и конфигурациях портов ввода видео приведение сигналов к УПФ не было выполнено раннее с помощью портов ввода видео.

Поставленная задача решена также путем создания способа приведения к единому формату различных цифровых видеосигналов, в котором с помощью массива управляющих регистров управляют и задают конфигурацию параллельного, последовательного, MIPI CSI 2 и MIPI CSI 3 портов ввода видео, мультиплексора и модуля обрезки и децимации кадров, с помощью параллельного, последовательного, MIPI CSI 2 и MIPI CSI 3 портов ввода видео принимают входные видеосигналы, при этом синхросигналы и данные в зависимости от конфигурации порта принимают по различным фронтам входного тактового сигнала, пересинхронизируют входные видеосигналы на внутреннюю частоту, приводят к унифицированному пиксельному формату (УПФ) и направляют в мультиплексор, с помощью которого выбирают несколько потоков видеосигналов и направляют их в модуль обрезки и децимации кадров, с помощью которого уменьшают размеры кадра по вертикали и по горизонтали и выполняют децимацию потоков видеосигналов по кадрам.

В предпочтительном варианте осуществления способа с помощью модуля выделения синхросигналов, входящего в состав модуля преобразования параллельного порта, выделяют управляющие синхросигналы из потока данных, если входные видеосигналы поступают в формате ВТ.656 или ВТ.1120, если же входные видеосигналы поступают в других поддерживаемых форматах, то их без изменений передают на следующий по тракту модуль перемещения цветовых компонент, входящий в состав модуля преобразования параллельного порта.

В предпочтительном варианте осуществления способа с помощью параллельного порта выполняют программируемую перестановку цветовых компонент на шине видеоданных, при этом упорядочивают цветовые компоненты на шине видеоданных к нужному формату.

В предпочтительном варианте осуществления способа с помощью параллельного порта инвертируют входные управляющие синхросигналы, а также на основе горизонтальной и вертикальной синхронизации создают из входного видеосигнала синхросигнал четного и нечетного полукадров, если входной видеосигнал поступает в чересстрочной развертке без этого сигнала.

В предпочтительном варианте осуществления способа с помощью последовательного порта принимают входные дифференциальные видеосигналы различных уровней напряжения, выбранные из набора сигналов, содержащего сигналы LVDS, subLVDS, SLVS-400 и SLVS-200.

В предпочтительном варианте осуществления способа с помощью последовательного порта принимают входные видеосигналы сверхвысокой четкости Ultra HD 4K со скоростью до 60 кадров в секунду, а также Full HD со скоростью до 120 кадров в секунду.

В предпочтительном варианте осуществления способа с помощью портов MIPI CSI 2 и MIPI CSI 3 в зависимости от формата входного видеосигнала, поступающего с приемников видеосигналов этих портов, автоматически программируют блоки преобразования видеосигналов, входящие в состав портов MIPI CSI 2 и MIPI CSI 3.

В предпочтительном варианте осуществления способа программируют модуль обрезки и децимации кадров, при этом задают разрешение изображения, выдаваемого этим модулем, а также прорежают видеосигнал по кадрам.

В предпочтительном варианте осуществления способа с помощью модуля обрезки и децимации кадров приводят сигналы, пришедшие от портов ввода видео, к УПФ в случае, если при некоторых условиях и конфигурациях портов ввода видео приведение сигналов к УПФ не было выполнено раннее с помощью портов ввода видео.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

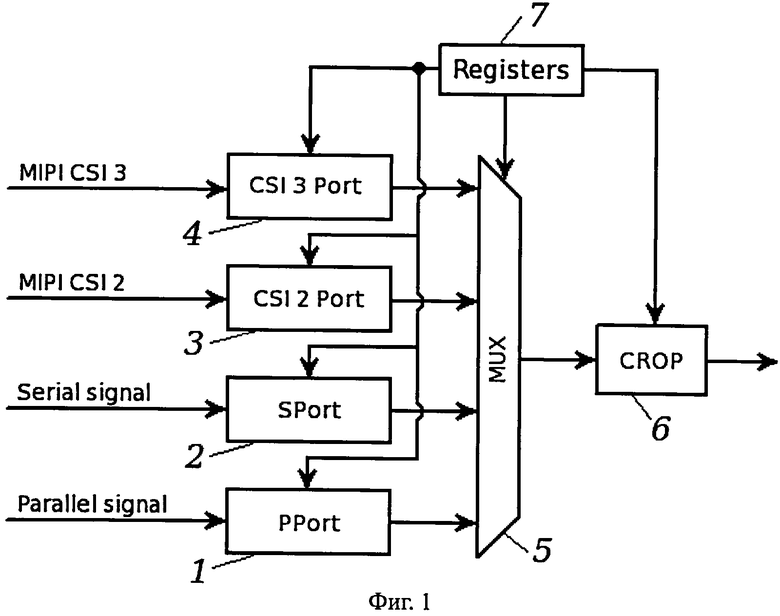

Фиг. 1. Общая схема устройства приведения к единому формату различных цифровых видеосигналов, выполненная согласно изобретению.

Фиг. 2. Схема параллельного порта, выполненная согласно изобретению.

Фиг. 3. Схема параллельного порта в первой конфигурации, выполненная согласно изобретению.

Фиг. 4. Схема параллельного порта во второй конфигурации, выполненная согласно изобретению.

Фиг. 5. Схема параллельного порта в третьей конфигурации, выполненная согласно изобретению.

Фиг. 6. Схема параллельного порта в четвертой конфигурации, выполненная согласно изобретению.

Фиг. 7. Схема параллельного порта в пятой конфигурации, выполненная согласно изобретению.

Фиг. 8. Схема параллельного порта в шестой конфигурации, выполненная согласно изобретению.

Фиг. 9. Схема параллельного порта в седьмой конфигурации, выполненная согласно изобретению.

Фиг. 10. Структурная схема модуля преобразования PInterface, выполненная согласно изобретению.

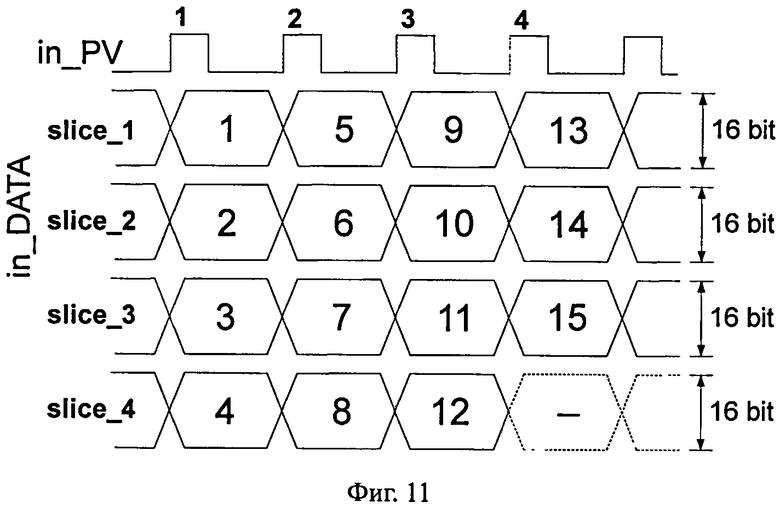

Фиг. 11. Схема принципа нумерации цветовых компонент потока входного видеоизображения при работе модуля перемещения цветовых компонент CCMoving, выполненная согласно изобретению.

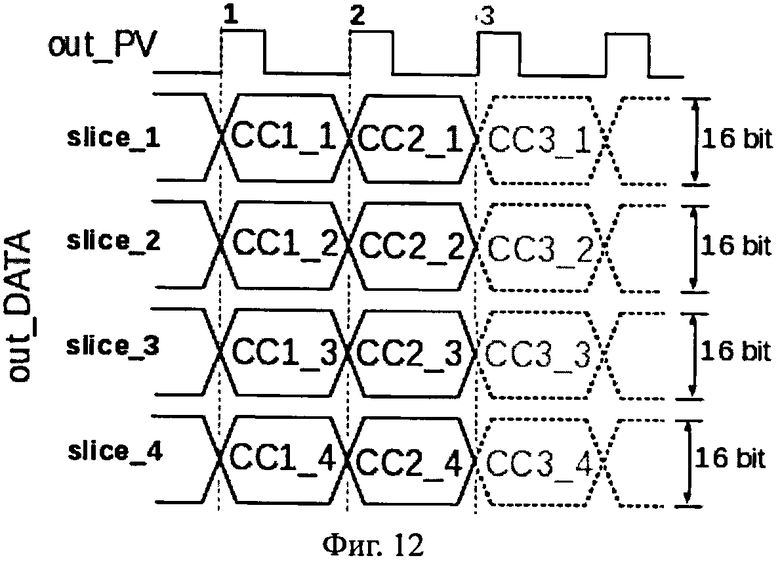

Фиг. 12. Схема соответствия параметров и цветовых компонент в потоке выходного видеоизображения модуля перемещения цветовых компонент CCMoving, выполненная согласно изобретению.

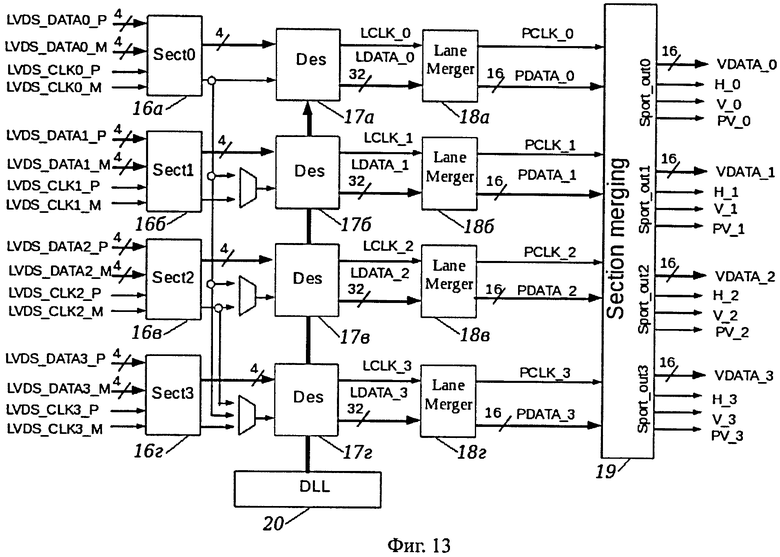

Фиг. 13. Структурная схема последовательного порта, выполненная согласно изобретению.

Фиг. 14. Структурная схема порта MIPI CSI 2, выполненная согласно изобретению.

Фиг. 15. Структурная схема порта MIPI CSI 3, выполненная согласно изобретению.

Рассмотрим кратко функционирование заявленных устройства и способа приведения к единому формату различных цифровых видеосигналов (Фиг. 1-15). Заявленное устройство приведения к единому формату различных цифровых видеосигналов (Фиг. 1) состоит из портов ввода видео: параллельного порта (1), последовательного порта (2), портов MIPI CSI 2 (3) и MIPI CSI 3 (4), а также модуля (6) обрезки и децимации кадров, которые преобразуют различные видеосигналы в формат удобный для обработки, называемый унифицированным пиксельным форматом (УПФ), а также массива управляющих регистров (7).

Параллельный порт (1) рассчитан на источники видеосигнала, имеющие параллельный интерфейс, с пиксельной частотой до 150 МГц. Параллельный порт (1) включает в себя модули Resync (10а-г) пересинхронизации входного видеопотока на внутреннюю частоту устройства и модули PInterface (11а-г), которые выполняют преобразование сигналов синхронизации и перемещение цветовых компонент на шине данных. Параллельный порт (1) доступен в одной из семи возможных конфигураций (Фиг. 3-9), в зависимости от которых может принимать от 1-го до 4-х потоков одновременно. Это обеспечивают 4 группы выводов LVTTL для приема синхросигналов от источника входного видеосигнала, в каждую из которых входят: пиксельная частота, горизонтальная и вертикальная синхронизации и синхросигнал четного и нечетного полукадров; и 40-битная шина данных, которая распределяется между этими группами выводов, в зависимости от выбранной конфигурации.

Последовательный порт (2) предназначен для источников видеосигнала, имеющих последовательные интерфейсы с частотой передачи данных до 800 Мбит в секунду на одну линию передачи, и поддерживает прием сигналов высокой и сверхвысокой четкости. Последовательный порт (2) состоит из преобразователей уровня входных дифференциальных сигналов, десериалайзеров (17а-г) и блоков (18а-г) преобразования видеосигнала в УПФ и имеет 4 входных секции (16а-г), каждая из которых включает в себя 4 дифференциальных вывода для подключения линий передач данных и дифференциальный вывод для пиксельной частоты.

Порт (3) с интерфейсом MIPI CSI-2 может быть сконфигурирован как один порт с 8, 4, 2 или 1 линиями данных или 2 порта с 4, 2 или 1-ой линиями данных. Каждая линия данных обеспечивает прием на скорости до 1500 Мбит в секунду. Порт состоит из приемника (22) видеосигнала по протоколу MIPI CSI 2, декодера (23а-б), который анализирует формат данных и формирует сигналы управления для модуля (24а-б), преобразующего поток видеоданных в унифицированный пиксельный формат.

Порт (4) с интерфейсом MIPI CSI-3 может быть сконфигурирован как один порт с 4, 2, или 1-ой линиями данных для приемника и одной линией данных для передатчика. Передача данных может осуществляться на скорости до 2500 Мбит в секунду на каждую линию передачи данных. В остальном данный порт схож с портом MIPI CSI-2.

Потоки со всех портов поступают на мультиплексор (5), который может выбрать от 1 до 4 потоков и направляет их на модуль (6) обрезки и децимации кадров.

Рассмотрим более подробно вариант выполнения заявленных устройства и способа приведения к единому формату различных цифровых видеосигналов, представленный на Фиг. 1-15. На фиг. 1 изображена структура заявленного устройства приведения к единому формату различных цифровых видеосигналов. Устройство содержит четыре различных порта (параллельный порт (1), последовательный порт (2), порт MIPI CSI 2(3), порт MIPI CSI 3 (4)), которые обеспечивают прием потоков видео независимо друг от друга. С портов (1)-(4) от 1 до 11-ти видеопотоков (до 4-х с параллельного, до 4-х с последовательного, до 2-х с MIPI CSI 2 и 1 с MIPI CSI 3) поступают в мультиплексор (5). В нем отбирают от 1 до 4-х видеопотоков, которые направляют в модуль (6) обрезки и децимации кадров. Все управление и выбор конфигурации заявленного устройства осуществляют с помощью массива регистров (7), из которого на все модули поступают команды и настройки.

Параллельный порт (1) (фиг. 2) имеет 48 внешних выводов, которые распределяют по входам демультиплексора demux (8) в зависимости от выбранной конфигурации. Допускается семь различных конфигураций. В первой конфигурации (фиг. 3) параллельный порт (1) разделяют на 2 одинаковых порта (9а-б) для приема видеосигнала в raw формате с одной цветовой компонентой за такт, каждый из которых включает в себя выводы для подключения пиксельной частоты, горизонтальной и вертикальной синхронизации, синхросигнала четного и нечетного полей кадра, а также 16-битную шину данных. Во второй конфигурации (фиг. 4) параллельный порт (1) настраивают на прием одного raw потока с тремя цветовыми компонентами, который состоит и следующих сигналов: пиксельная частота, горизонтальная и вертикальная синхронизации, синхросигнал четного и нечетного полукадра и 36-разрядная шина данных, по 12 бит для каждой из трех цветовых компонент. Третья конфигурация (фиг. 5) параллельного порта (1) отличается от второй только шиной данных, которая представляет собой 32-разрядную шину для двух цветовых компонент, по 16 бит на каждую. В четвертой конфигурации (фиг. 6) параллельный порт (1) разделяют на четыре одинаковых порта (9а-г) для приема видеосигналов в формате ВТ.656 10 и 8 бит. Пятая конфигурация (фиг. 7) параллельного порта (1) предусматривает четыре порта (9а-г), каждый из которых имеет 10-битовую шину данных и выводы для пиксельной частоты и горизонтальной и вертикальной синхронизации. В шестой конфигурации (фиг. 8) параллельный порт (1) разделяют на два одинаковых порта (9а-б) для приема видеопотоков в формате ВТ.1120 с 20-битной шиной в каждом. Последняя, седьмая, конфигурация (фиг. 9) параллельного порта (1) представляет собой порт с 30-битной шиной данных для приема ВТ.1120.

Во всех конфигурациях параллельного порта (1) каждый содержащийся в нем порт состоит из модуля Resync (10а-г) пересинхронизации видеопотока на внутреннюю частоту устройства и модуля PInterface (11а-г) преобразования сигналов (фиг. 2). В параллельном порте (1) каждый из четырех модулей Resync (10а-г) предназначен для своего потока и независим друг от другого модуля Resync (10а-г). Модули Resync (10а-г) могут осуществлять прием по переднему, по заднему или по обоим фронтам входной пиксельной частоты, а затем, после пересинхронизации, создают новый тактовый сигнал, и внутри заявленного устройства данные передают только по переднему фронту этого нового тактового сигнала. Также параллельный порт (1) включает в себя 4 модуля PInterface (11а-г), каждый из которых состоит из модуля BT_to_Raw (13) выделения синхросигналов из потока данных форматов ВТ.656 и ВТ.1120, модуля CCMoving (14) перемещения цветовых компонент (СС - color component) по шине данных и модуля HVF_mod (15) преобразования сигналов строчной (Н), кадровой (V) синхронизации, синхросигнала четного и нечетного полукадров (F) (фиг. 10). На входе модуля PInterface (11a-г) стоит мультиплексор mux (12), который в случае, если поток в формате ВТ.1120 или ВТ.656, направляет его в модуль BT_to_Raw (13), где происходит выделение синхросигналов из видеоданных, и затем направляет его в модуль CCMoving (14), а в случае, если поток в других поддерживаемых видеоформатах, то мультиплексор mux (12) направляет поток сразу в модуль CCMoving (14), в обход модуля BT_to_Raw (13). Модуль CCMoving (14) предназначен для изменения порядка следования компонент и изменения размещения цветовой компоненты в разрядах шины данных. Это достигается программированием модуля CCMoving (14), который имеет несколько параметров. Входной поток видеосигналов параметризируется количеством тактов пиксельной частоты (in_PV) от одного до четырех, называемым циклом сборки для четных и нечетных строк, а также нумерацией компонент, в зависимости от того, в каком такте и в каких разрядах она передается (фиг. 11). Выходной поток также имеет параметр количества тактов пиксельной частоты (out_PV) для четных и нечетных строк, но ограничен значениями 1, 2 или 3 и называется количеством выдаваемых пикселей. Вместе с этим в выходном потоке каждой цветовой компоненте поставлен в соответствие параметр, в который нужно вписать номер цветовой компоненты из входного потока, чтобы разместить ее в нужном такте и на нужных разрядах (фиг. 12). Далее в модуле HVF_mod (15), в случае необходимости, инвертируют сигналы Н, V и F. Так же модуль HVF_mod (15) позволяет создать сигнал F, используя входные сигналы H и V, если при чересстрочной развертке, по каким-то причинам, от источника такой сигнал отсутствует или в конфигурации не хватило внешних выводов для этого сигнала (например, 4 конфигурация). Далее предварительно преобразованный видеосигнал поступает на мультиплексор (5), а затем в модуль (6) обрезки и децимации кадров.

Таким образом, параллельный порт включает в себя модули, с помощью которых выделяют управляющие синхросигналы из потока данных, в случае приема видеосигнала в форматах ВТ.656 или ВТ.1120, модули, с помощью которых выполняют перестановку цветовых компонент по шине данных, и модули преобразования управляющих синхросигналов.

Последовательный порт SPort (2) имеет четыре дифференциальных вывода для подключения пиксельных (LVDS_CLK) частот источников и шестнадцать дифференциальных выводов для данных (LVDS_DATA), которые разбиты на четыре одинаковые группы (секции - Sect (16а-г)) по четыре линии данных и одну пиксельную частоту (фиг. 13). По количеству принимаемых источников доступны следующие конфигурации:

1 источник - 1 общий порт, тогда все линии данных относятся к одному порту и возможен прием данных по одной пиксельной частоте для всех линий данных;

2 источника - 2 порта, тогда линии данных распределяются по 8 линий для каждого порта и на каждый порт имеется в распоряжении по 2 линии пиксельных частот;

4 источника - 4 порта, тогда каждый порт имеет по секции сигналов.

На входах каждой секции имеются преобразователи уровней дифференциальных сигналов, которые обеспечивают прием по LVDS, subLVDS, SLVS-400 и SLVS-200. Данные с выхода преобразователей уровней дифференциальных сигналов поступают на десериалайзеры Des (17а-г), которые принимают данные по переднему, заднему или обоим фронтам пиксельной частоты в форматах Bayer или Mono с разрядностью 8, 10, 12, 14 или 16. Путем выбора одного из выходов DLL (20) может осуществляться автоматическая подстройка для приема данных в середине "полки" принимаемого синхросигнала, или ближе к переднему или заднему фронту. Разрядность данных на выходе десериалайзера составляет 32 бита, по 8 бит на каждую линию. С блоков Des (17а-г) данные поступают на модули Lane Merger (18а-г), в которых происходит сборка битов пикселя в 16-битный формат, в каждой линии. Если разрядность принимаемого пикселя менее 16 бит, то принятые биты размещают в старших битах 16-разрядного слова, а младшие заполняют нулями. Далее сформированные пиксели, в заданной очередности, посылают на блок Section Merger (19), где происходит упорядочивание пикселей, поступающих с разных секций, в один поток и создание синхросигналов, получая на выходе УПФ.

В порте MIPI CSI 2 (3) модуль CSI RX DPHY (21а-б), реализующий физический уровень протокола MIPI CSI 2, состоит из одного Clock Lane и четырех Data Lane (фиг.14). Каждый Data Lane содержит десериалайзер, который преобразует последовательные данные в 8-разрядный код. Clock Lane содержит делитель частоты, который формирует синхросигнал для 8-разрядных данных. Для приема по 8 Data Lane используют два модуля CSIRXDPHY (21a-6).

Приемник видеосигнала, модуль CSI RX (22), принимает 8-разрядные данные от каждого Data Lane и компонует их в один поток, сортирует данные в зависимости от кадра и строки, осуществляет преобразование в формат, определенный в заголовке пакета. Цветовые компоненты пикселя могут выдаваться в различной последовательности, в зависимости от формата, через 24-разрядный порт данных Data Port. Если порт MIPI CSI 2 (3) сконфигурирован как один порт, то данные и сигналы синхронизации выдают на нулевой Data Port 0, если как два порта, то используют нулевой порт данных Data Port 0 и первый порт данных Data Port 1. Данные и управляющие сигналы с порта данных Data Port поступают в декодеры CSI Decoder (23а-б), который анализирует формат данных и формирует сигналы управления для модулей преобразования в УПФ Sinterface (24а-б), а также осуществляет преобразование данных в 16-разрядный формат. 5, 6, 7, 8, 10, 12, 14-разрядные данные поступают в старшие разряды 16-разрядных выходов, а младшие заполняются нулями. Данные с выхода CSI Decoder (23а-б) поступают на 16-разрядные входы модуля Sinterface (24а-б) и преобразуют с помощью него в УПФ.

Порт MIPI CSI 3 (4) в целом схож по принципу работы и по структуре с портом MIPI CSI 2 (3) (фиг. 15), но в отличие от модуля CSI RX DPHY (21а-б) порта MIPI CSI 2 (3) модуль CSI3 RX DPHY (25) не содержит Clock Lane, а данные синхронизируют синхросигналом, выделяемым из потока данных, поступающих на Data lane0-3. Имеется выделенный канал управления Ctrl Lane, по которому передают управляющую информацию для источника видеосигнала. Порт MIPI CSI 3 (4) поддерживает только один источник видеосигнала, поэтому в его состав входит по одному модулю CSI3 Decoder (27) и Sinterface (24в). Приемник Unipro/Host Controller (26) отвечает протоколу MIPI CSI 3, а по выдаваемым форматам аналогичен CSI RX(22).

Модуль CROP (6) обрезки и децимации кадров (фиг. 1) приводит пришедшие сигналы к формату УПФ, если при некоторых условиях и конфигурациях это не было достигнуто раннее. Также он позволяет уменьшить размеры кадра по вертикали и по горизонтали и выполнить децимацию по кадрам.

Хотя описанный выше вариант выполнения изобретения был изложен с целью иллюстрации заявленного изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла заявленного изобретения, раскрытого в прилагаемой формуле изобретения.

Изобретение относится к области обработки видеосигналов. Технический результат заключается в приведении к единому формату различных цифровых видеосигналов. Устройство и способ приведения к единому формату различных цифровых видеосигналов, универсальных по обрабатываемым видеосигналам, которые позволяют принимать от одного до одиннадцати видеосигналов одновременно по различным параллельным и последовательным интерфейсам, причем видеоизображения, передаваемые посредством видеосигналов, могут иметь различное разрешение и количество кадров в секунду, разное цветовое пространство (RGB, YcbCr, Bayer, Mono и др.), разную пиксельную субдискретизацию (4:4:4, 4:2:2, 4:2:0 и т.д.), различные стандартизированные форматы (ВТ.656, ВТ.1120, HiSPi, MIPI CSI 2, MIPI CSI 3). 2 н. и 35 з.п. ф-лы, 15 ил.

1. Устройство приведения к единому формату различных цифровых видеосигналов, содержащее параллельный, последовательный, MIPI CSI 2 и MIPI CSI 3 порты ввода видео, выходы которых соединены со входами мультиплексора, выход которого соединен со входом модуля обрезки и децимации кадров, а также массив управляющих регистров, выходы которого соединены с портами ввода видео, мультиплексором и модулем обрезки и децимации кадров, при этом массив управляющих регистров выполнен с возможностью управления и задания конфигураций параллельного, последовательного, MIPI CSI 2 и MIPI CSI 3 портов ввода видео, мультиплексора и модуля обрезки и децимации кадров; параллельный, последовательный, MIPI CSI 2 и MIPI CSI 3 порты ввода видео выполнены с возможностью приема входных видеосигналов, при этом приема синхросигналов и данных в зависимости от конфигурации порта по различным фронтам входного тактового сигнала, с возможностью пересинхронизации входных видеосигналов на внутреннюю частоту, приведения их к унифицированному пиксельному формату (УПФ) и направления в мультиплексор, выполненный с возможностью осуществления выбора нескольких потоков видеосигналов и направления их в модуль обрезки и децимации кадров, выполненный с возможностью уменьшения размеров кадра по вертикали и по горизонтали и осуществления децимации потоков видеосигналов по кадрам.

2. Устройство по п. 1, отличающееся тем, что параллельный порт выполнен с возможностью инвертирования входных управляющих синхросигналов, а также с возможностью создания из входного видеосигнала на основе горизонтальной и вертикальной синхронизации синхросигнала четного и нечетно полукадров, если входной видеосигнал поступает в чересстрочной развертке без этого сигнала.

3. Устройство по п. 1, отличающееся тем, что параллельный порт содержит внешние выводы, распределенные по входам демультиплексора, выходы которого соединены со входами модулей пересинхронизации, выходы которых связаны со входами модулей преобразования, выходы которых связаны со входами мультиплексора, при этом демультиплексор выполнен с возможностью разделения объединенного потока входных видеосигналов и направления разделенных потоков входных видеосигналов на модули пересинхронизации, выполненные с возможностью пересинхронизации потока входных видеосигналов на внутреннюю частоту устройства и передачи пересинхронизованного потока входных видеосигналов в модули преобразования, выполненные с возможностью преобразования сигналов синхронизации, перемещения цветовых компонент на шине данных и передачи преобразованного потока входных видеосигналов в мультиплексор.

4. Устройство по п. 1, отличающееся тем, что параллельный порт выполнен с возможностью приема входных видеосигналов с пиксельной частотой до 150 МГц по меньшей мере от одного источника видеосигнала, который имеет параллельный интерфейс.

5. Устройство по п. 1, отличающееся тем, что параллельный порт выполнен с возможностью преобразования по меньшей мере в семь конфигураций, причем в каждой конфигурации параллельный порт выполнен с возможностью приема от 1-го до 4-х потоков входных видеосигналов одновременно.

6. Устройство по п. 5, отличающееся тем, что параллельный порт выполнен с возможностью приема от 1-го до 4-х потоков входных видеосигналов одновременно с помощью 4-х групп выводов LVTTL, выполненных с возможностью приема синхросигналов от источника входного видеосигнала, в каждую из которых входят: пиксельная частота, горизонтальная и вертикальная синхронизации и синхросигнал четного и нечетного полукадров; а также с помощью 40-битной шины данных, выполненной с возможностью распределения между группами выводов LVTTL, в зависимости от конфигурации параллельного порта.

7. Устройство по п. 3, отличающееся тем, что каждый модуль пересинхронизации предназначен для своего потока входных видеосигналов и независим от другого модуля пересинхронизации.

8. Устройство по п. 3, отличающееся тем, что модуль пересинхронизации выполнен с возможностью приема по переднему, по заднему или по обоим фронтам пиксельной частоты входных видеосигналов, а после осуществления пересинхронизации модуль пересинхронизации выполнен с возможностью формирования нового тактового сигнала, по переднему фронту которого передают данные внутри устройства.

9. Устройство по п. 5, отличающееся тем, что в первой конфигурации параллельный порт разделен на два одинаковых порта, каждый из которых выполнен с возможностью приема видеосигналов в raw формате с одной цветовой компонентой за такт и содержит выводы для приема сигналов пиксельной частоты, горизонтальной и вертикальной синхронизации, синхросигнала четного и нечетного полей кадра, а также содержит 16-битную шину данных.

10. Устройство по п. 5, отличающееся тем, что во второй конфигурации параллельный порт настроен на прием одного raw потока входных видеосигналов с тремя цветовыми компонентами за такт и содержит выводы для приема сигналов пиксельной частоты, горизонтальной и вертикальная синхронизации, синхросигнала четного и нечетного полукадра, а также содержит 36-битную шину данных, по 12 бит для каждой из трех цветовых компонент.

11. Устройство по п. 5, отличающееся тем, что в третьей конфигурации параллельный порт настроен на прием одного raw потока входных видеосигналов с двумя цветовыми компонентами за такт и содержит выводы для приема сигналов пиксельной частоты, горизонтальной и вертикальной синхронизации, синхросигнала четного и нечетного полукадра, а также содержит 32-битную шину данных, по 16 бит для каждой из двух цветовых компонент.

12. Устройство по п. 5, отличающееся тем, что в четвертой конфигурации параллельный порт разделен на четыре одинаковых порта, каждый из которых выполнен с возможностью приема видеосигналов в формате ВТ.656 10 и 8 бит.

13. Устройство по п. 5, отличающееся тем, что в пятой конфигурации параллельный порт разделен на четыре одинаковых порта, каждый из которых содержит 10-битную шину данных и выводы для приема сигналов пиксельной частоты и горизонтальной и вертикальной синхронизации.

14. Устройство по п. 5, отличающееся тем, что в шестой конфигурации параллельный порт разделен на два одинаковых порта, каждый из которых выполнен с возможностью приема видеосигналов в формате ВТ.1120 и содержит 20-битную шину данных.

15. Устройство по п. 5, отличающееся тем, что в седьмой конфигурации параллельный порт настроен на прием видеосигналов в формате ВТ.1120 и содержит 30-битную шину данных.

16. Устройство по п. 1, отличающееся тем, что модуль преобразования содержит на входе мультиплексор, первый выход которого соединен с первым входом модуля перемещения цветовых компонент, а второй выход соединен со входом модуля выделения синхросигналов, выход которого соединен со вторым входом модуля перемещения цветовых компонент, выход которого соединен со входом модуля преобразования сигналов, при этом модуль выделения синхросигналов выполнен с возможностью выделения синхросигналов из потока видеосигналов форматов ВТ.656 и ВТ.1120, модуль перемещения цветовых компонент выполнен с возможностью изменения порядка следования компонент и изменения размещения цветовой компоненты в разрядах шины данных путем программирования модуля, модуль преобразования сигналов выполнен с возможностью преобразования сигналов строчной и кадровой синхронизации, а также синхросигнала четного и нечетного полукадров, а мультиплексор выполнен с возможностью направления потока входных видеосигналов в модуль выделения синхросигналов и затем в модуль перемещения цветовых компонент, если поток входных видеосигналов представлен в формате ВТ.1120 или ВТ.656, а также с возможностью направления потока входных видеосигналов сразу в модуль перемещения цветовых компонент минуя модуль выделения синхросигналов, если поток входных видеосигналов представлен в других поддерживаемых видеоформатах.

17. Устройство по п. 1, отличающееся тем, что последовательный порт содержит четыре входных секции, выходы которых соединены со входами десериалайзеров, выходы которых соединены со входами модулей сборки битов, выходы которых соединены со входами блока преобразования входного видеосигнала в УПФ, причем входные секции выполнены с возможностью приема входных видеосигналов, преобразования уровней напряжения дифференциальных сигналов и передачи видеосигналов в десериалайзеры, выполненные с возможностью приема данных видеосигналов по переднему, заднему или обоим фронтам пиксельной частоты в форматах Bayer или Mono с разрядностью 8, 10, 12, 14 или 16 и с возможностью автоматической подстройки для приема данных видеосигнала в середине "полки" принимаемого синхросигнала или ближе к переднему или заднему фронту путем выбора одного из выходов DLL, соединенных с десериалайзерами, при этом разрядность данных на выходе десериалайзеров составляет 32 бита, по 8 бит на каждую линию, а также с возможностью передачи данных видеосигналов на модули сборки битов, выполненные с возможностью сборки битов пикселя в 16-битный формат, в каждой линии, причем, если разрядность принимаемого пикселя менее 16 бит, то принятые биты размещают в старших битах 16-разрядного слова, а младшие заполняют нулями, а также с возможностью передачи сформированных пикселей в заданной очереди в блок преобразования входного видеосигнала в УПФ, выполненный с возможностью упорядочивания пикселей, поступающих с разных секций, в один поток и создания синхросигналов, при этом формирования на выходе УПФ.

18. Устройство по п. 17, отличающееся тем, что каждая входная секция имеет четыре дифференциальных вывода для подключения линий передач данных и дифференциальный вывод для пиксельной частоты.

19. Устройство по п. 17, отличающееся тем, что каждая входная секция имеет на входах преобразователи уровней дифференциальных сигналов, выполненные с возможностью приема по LVDS, subLVDS, SLVS-400 и SLVS-200, при этом данные с выходов преобразователей уровней дифференциальных сигналов поступают на десериалайзеры.

20. Устройство по п. 17, отличающееся тем, что последовательный порт выполнен с возможностью приема входных видеосигналов, имеющих последовательные интерфейсы с частотой передачи данных до 800 Мбит в секунду на одну линию передачи, и поддерживает прием входных видеосигналов высокой и сверхвысокой четкости.

21. Устройство по п. 1, отличающееся тем, что порт MIPI CSI 2 выполнен с возможностью конфигурирования для приема данных по восьми, четырем, двум или одной линиям данных, при этом каждая линия данных обеспечивает прием на скорости до 1500 Мбит в секунду.

22. Устройство по п. 1, отличающееся тем, что порт MIPI CSI 2 содержит по меньшей мере один модуль CSI RX DPHY, соединенный с приемником видеосигнала по протоколу MIPI CSI 2, который соединен по меньшей мере с одним декодером, который соединен по меньшей мере с одним модулем преобразования в УПФ, а приемник видеосигнала содержит по меньшей мере один порт данных, при этом модуль CSI RX DPHY выполнен с возможностью реализации физического уровня протокола MIPI CSI 2 и состоит из одного блока Clock Lane и по меньшей мере одного блока Data Lane, причем блок Data Lane содержит десериалайзер, выполненный с возможностью преобразования последовательных данных в многоразрядный код, а блок Clock Lane содержит делитель частоты, выполненный с возможностью формирования синхросигнала для многоразрядных данных; приемник видеосигнала выполнен с возможностью приема многоразрядных данных от блока Data Lane и компоновки их в один поток, с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, а также с возможностью передачи данных и управляющих сигналов с порта данных по меньшей мере в один декодер, выполненный с возможностью анализа формата данных и формирования сигналов управления для модуля преобразования в УПФ, а также с возможностью передачи данных на многоразрядные входы модуля преобразования в УПФ, выполненного с возможностью преобразования потока видеоданных в унифицированный пиксельный формат (УПФ).

23. Устройство по п. 22, отличающееся тем, что модуль CSI RX DPHY выполнен с возможностью реализации физического уровня протокола MIPI CSI 2 и состоит из одного блока Clock Lane и четырех блоков Data Lane, причем блок Data Lane содержит десериалайзер, выполненный с возможностью преобразования последовательных данных в 8-разрядный код, а блок Clock Lane содержит делитель частоты, выполненный с возможностью формирования синхросигнала для 8-разрядных данных, при этом для приема по восьми блокам Data Lane используют конфигурацию порта MIPI CSI 2 с двумя модулями CSI RX DPHY; приемник видеосигнала выполнен с возможностью приема 8-разрядных данных от блока Data Lane и компоновки их в один поток, с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, а также с возможностью передачи данных и управляющих сигналов с порта данных в два декодера, выполненные с возможностью анализа формата данных и формирования сигналов управления для модуля преобразования в УПФ, с возможностью преобразования данных в 16-разрядный формат, при этом передачи 5, 6, 7, 8, 10, 12, 14-разрядных данных в старшие разряды 16-разрядных выходов и заполнения младших разрядов нулями, а также с возможностью передачи данных на 16-разрядные входы двух модулей преобразования в УПФ, выполненных с возможностью преобразования потока видеоданных в унифицированный пиксельный формат (УПФ).

24. Устройство по п. 23, отличающееся тем, что приемник видеосигнала выполнен с возможностью приема 8-разрядных данных от блока Data Lane и компоновки их в один поток, а также с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, при этом цветовые компоненты пикселя могут выдаваться в различной последовательности, в зависимости от формата, по меньшей мере через один 24-разрядный порт данных при этом, если порт MIPI CSI 2 сконфигурирован как один порт, то данные и сигналы синхронизации выдают на нулевой порт данных.

25. Устройство по п. 9, отличающееся тем, что порт MIPI CSI 3 содержит модуль CSI3 RX DPHY, соединенный с приемником видеосигнала по протоколу MIPI CSI 3, который соединен с декодером, который соединен с модулем преобразования в УПФ, а приемник видеосигнала содержит по меньшей мере один порт данных, при этом модуль CSI RX DPHY выполнен с возможностью реализации физического уровня протокола MIPI CSI 3 и состоит из выделенного канала управления, выполненного с возможностью передачи управляющей информации для источника видеосигнала, и по меньшей мере одного блока Data Lane, причем блок Data Lane содержит десериалайзер, выполненный с возможностью преобразования последовательных данных в многоразрядный код; приемник видеосигнала выполнен с возможностью приема многоразрядных данных от блока Data Lane и компоновки их в один поток, с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, а также с возможностью передачи данных и управляющих сигналов с порта данных в декодер, выполненный с возможностью анализа формата данных и формирования сигналов управления для модуля преобразования в УПФ, а также с возможностью передачи данных на многоразрядные входы модуля преобразования в УПФ, выполненного с возможностью преобразования потока видеоданных в унифицированный пиксельный формат (УПФ).

26. Устройство по п. 25, отличающееся тем, что модуль CSI RX DPHY выполнен с возможностью реализации физического уровня протокола MIPI CSI 3 и состоит из выделенного канала управления, выполненного с возможностью передачи управляющей информации для источника видеосигнала, и четырех блоков Data Lane, причем блок Data Lane содержит десериалайзер, выполненный с возможностью преобразования последовательных данных в 8-разрядный код, а для приема по восьми блокам Data Lane используют конфигурацию порта MIPI CSI 3 с двумя модулями CSI RX DPHY; приемник видеосигнала выполнен с возможностью приема 8-разрядных данных от блока Data Lane и компоновки их в один поток, с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, а также с возможностью передачи данных и управляющих сигналов с порта данных в декодер, выполненный с возможностью анализа формата данных и формирования сигналов управления для модуля преобразования в УПФ, с возможностью преобразования данных в 16-разрядный формат, при этом передачи 5, 6, 7, 8, 10, 12, 14-разрядных данных в старшие разряды 16-разрядных выходов и заполнения младших разрядов нулями, а также с возможностью передачи данных на 16-разрядные входы модуля преобразования в УПФ, выполненного с возможностью преобразования потока видеоданных в унифицированный пиксельный формат (УПФ).

27. Устройство по п. 26, отличающееся тем, что приемник видеосигнала выполнен с возможностью приема 8-разрядных данных от блока Data Lane и компоновки их в один поток, а также с возможностью сортировки данных в зависимости от кадра и строки и преобразования их в формат, определенный в заголовке пакета данных, при этом цветовые компоненты пикселя могут выдаваться в различной последовательности, в зависимости от формата, через по меньшей мере один 24-разрядный порт данных при этом, если порт MIPI CSI 3 сконфигурирован как один порт, то данные и сигналы синхронизации выдают на нулевой порт данных.

28. Устройство по п. 1, отличающееся тем, что модуль обрезки и децимации кадров выполнен с возможностью приведения сигналов, пришедших от портов ввода видео, к УПФ в случае, если при некоторых условиях и конфигурациях портов ввода видео приведение сигналов к УПФ не было выполнено раннее с помощью портов ввода видео.

29. Способ приведения к единому формату различных цифровых видеосигналов, в котором с помощью массива управляющих регистров управляют и задают конфигурацию параллельного, последовательного, MIPI CSI 2 и MIPI CSI 3 портов ввода видео, мультиплексора и модуля обрезки и децимации кадров, с помощью параллельного, последовательного, MIPI CSI 2 и MIPI CSI 3 портов ввода видео принимают входные видеосигналы, при этом синхросигналы и данные в зависимости от конфигурации порта принимают по различным фронтам входного тактового сигнала, пересинхронизируют входные видеосигналы на внутреннюю частоту, приводят к унифицированному пиксельному формату (УПФ) и направляют в мультиплексор, с помощью которого выбирают несколько потоков видеосигналов и направляет их в модуль обрезки и децимации кадров, с помощью которого уменьшают размеры кадра по вертикали и по горизонтали и выполняют децимацию потоков видеосигналов по кадрам.

30. Способ по п. 29, отличающийся тем, что с помощью модуля выделения синхросигналов, входящего в состав модуля преобразования параллельного порта, выделяют управляющие синхросигналы из потока данных, если входные видеосигналы поступают в формате ВТ.656 или ВТ.1120, если же входные видеосигналы поступают в других поддерживаемых форматах, то их без изменений передают на следующий по тракту модуль перемещения цветовых компонент, входящий в состав модуля преобразования параллельного порта.

31. Способ по п. 29, отличающийся тем, что с помощью параллельного порта выполняют программируемую перестановку цветовых компонент на шине видеоданных, при этом упорядочивают цветовые компоненты на шине видеоданных к нужному формату.

32. Способ по п. 29, отличающийся тем, что с помощью параллельного порта инвертируют входные управляющие синхросигналы, а также на основе горизонтальной и вертикальной синхронизации создают из входного видеосигнала синхросигнал четного и нечетно полукадров, если входной видеосигнал поступает в чересстрочной развертке без этого сигнала.

33. Способ по п. 29, отличающийся тем, что с помощью последовательного порта принимают входные дифференциальные видеосигналы различных уровней напряжения, выбранные из набора сигналов, содержащего сигналы LVDS, subLVDS, SLVS-400 и SLVS-200.

34. Способ по п. 29, отличающийся тем, что с помощью последовательного порта принимают входные видеосигналы сверхвысокой четкости Ultra HD 4К со скоростью до 60 кадров в секунду, а также Full HD со скоростью до 120 кадров в секунду.

35. Способ по п. 29, отличающийся тем, что с помощью портов MIPI CSI 2 и MIPI CSI 3 в зависимости от формата входного видеосигнала, поступающего с приемников видеосигналов этих портов, автоматически программируют блоки преобразования видеосигналов, входящие в состав портов MIPI CSI 2 и MIPI CSI 3.

36. Способ по п. 29, отличающийся тем, что программируют модуль обрезки и децимации кадров, при этом задают разрешение изображения, выдаваемого этим модулем, а также прорежают видеосигнал по кадрам.

37. Способ по п. 29, отличающийся тем, что с помощью модуля обрезки и децимации кадров приводят сигналы, пришедшие от портов ввода видео, к УПФ в случае, если при некоторых условиях и конфигурациях портов ввода видео приведение сигналов к УПФ не было выполнено раннее с помощью портов ввода видео.

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Способ отварки промасленного тряпья | 1933 |

|

SU37057A1 |

| Устройство для сжатия цифровых телевизионных сигналов цветного изображения | 1988 |

|

SU1529471A1 |

| МНОГОВИДОВОЕ ВИДЕО КОДИРОВАНИЕ В СИСТЕМАХ МРЕG-2 | 2010 |

|

RU2509440C2 |

Авторы

Даты

2015-12-20—Публикация

2014-04-22—Подача