СП

кэ

со

пичение коэффициента сжатия. Устр-во содержит АЦП 1, блок установки 2 опорного уровня, регистры 3, 4 и 12, блок задержки 5 и 13, блоки сравнения 6 и 15, счетчики 7, 10и11,эл-т- ИЛИ 8, эл-т И 9, коммутатор; 14, блоки памяти 16 и 17, блок эл-тов ИЛИ 18, формирователь 19 кода синхронизации, преобразователь 20 кода и блок управления (БУ) 21. В устр-ве информация о кадре изображения записывается в виде последовательности кодированных инструкций, каждая из которых содержит информацию о цветности 3 и длине DJ полосы. Цель

достигается за счет использования построчно-весового кодирования.Для реализации процесса построчно-весового кодирования в устр-ве код цветности текущего зл-та отображения сравнивается с кодом цветности пре- дьщущего. В случае их совпадения значение кода длины полосы D. увеличивается на единицу, а в случае несовпадения шш превышения длиной полосы заданнор величины 2 (где 6 п 8 записывается новая инструкция (3., Вч). Устро-во по п, 2 ф-лы

отличается выполнением БУ 21. 1 з.п. ф-лы,2 ил,

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1631752A1 |

| Устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1607080A1 |

| Устройство для сжатия цветовых сигналов телевизионных изображений | 1987 |

|

SU1515400A1 |

| Устройство для сжатия телевизионных сигналов цветного изображения | 1989 |

|

SU1633523A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1462408A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

Изобретение относится к технике телевидения. Цель изобретения - увеличение коэффициента сжатия. Устройство содержит АЦП 1, блок установки 2 опорного уровня, регистры 3, 4 и 12, блоки задержки 5 и 13, блоки сравнения 6 и 15, счетчики 7, 10 и 11, эл-т ИЛИ 8, эл-т И 9, коммутатор 14, блоки памяти 16 и 17, блок эл-тов ИЛИ 18, формирователь 19 кода синхронизации, преобразователь 20 кода и блок управления (БУ) 21. В устройстве информация о кадре изображения записывается в виде последовательности кодированных инструкций, каждая из которых содержит информацию о цветности JI и длине DI полосы. Цель достигается за счет использования построчно-весового кодирования. Для реализации процесса построчно-весового кодирования в устройстве код цветности текущего эл-та отображения сравнивается с кодом цветности предыдущего. В случае их совпадения значение кода длины полосы DI увеличивается на единицу, а в случае несовпадения или превышения длиной полосы заданной величины 2N (где 6≤N≤8) записывается новая инструкция (JI, DI). Устройство по п. 2 ф-лы отличается выполнением БУ 21. 1 з.п. ф-лы, 2 ил.

Изобретение относится к технике передачи и хранения цветных изображений в системах с применением телевзионных дисплеев и видеотерминалов, может быть использовано в автоматизированных системах отображения, об- работки данных и управления.

Целью изобретения является увеличение коэффициента сжатия.

Сущность изображения состоит в том, 40 увеличение коэффициента сжатия достигнуто благодаря применению построчно-весового кодирования

Кадр изображения в направлении сканирования разбивается на участки (полосы), в состав которых входят элементы отображения одной цветности Информация о кадре изображения записывается в виде последовательности кодированных инструкций, каждая из которых содержит информацию о цвет- ности (J,)H длине (D;) полосы. Разрядность кода J.(т) выбирается исходя из требований, предъявленных к системе. Так, при m 8, число отображенных оттенков составит 2 256

Разрядность кода D . (п) фиксирова.нана и лежит в пределах: 1 4 /1ор, где К - число элементов отображения в кадре. В реальных изображениях длины примерно 50% полос не превьппает 64 и более 93% - 256. Таким образом целесообразно выбирать п в пределах 6 п 8.

Полосы дпинон более чем 2 разбиваются на части, длины которых не превышают 2 и информация о них записывается в виде нескольких инструкций, имеющих одинаковые коды цветности ( 3 ;) .

5

5

О

,

В общем случае число инстт кций О, D.) для каждого кадра изображений различно и зависит от сложности (детальности) изображения

Для реализации процесса построчно- весового кодирования необходимо код цветности текущего элемента отображения сравнить с кодом цветности предыдущего. В случае их совпадения значение кода длины полосы D; увеличивается на единицу, в случае несовпадения t-ши превышения длиной полосы величины 2 записывается новая (Инструкция (J., D.).

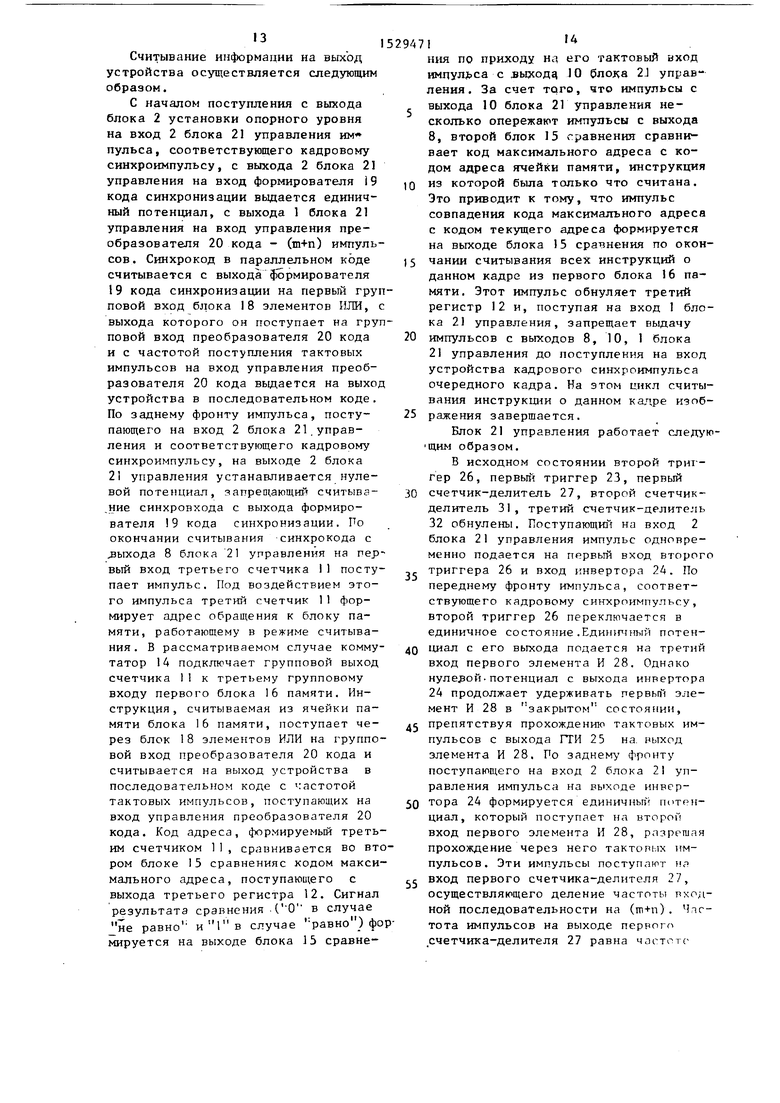

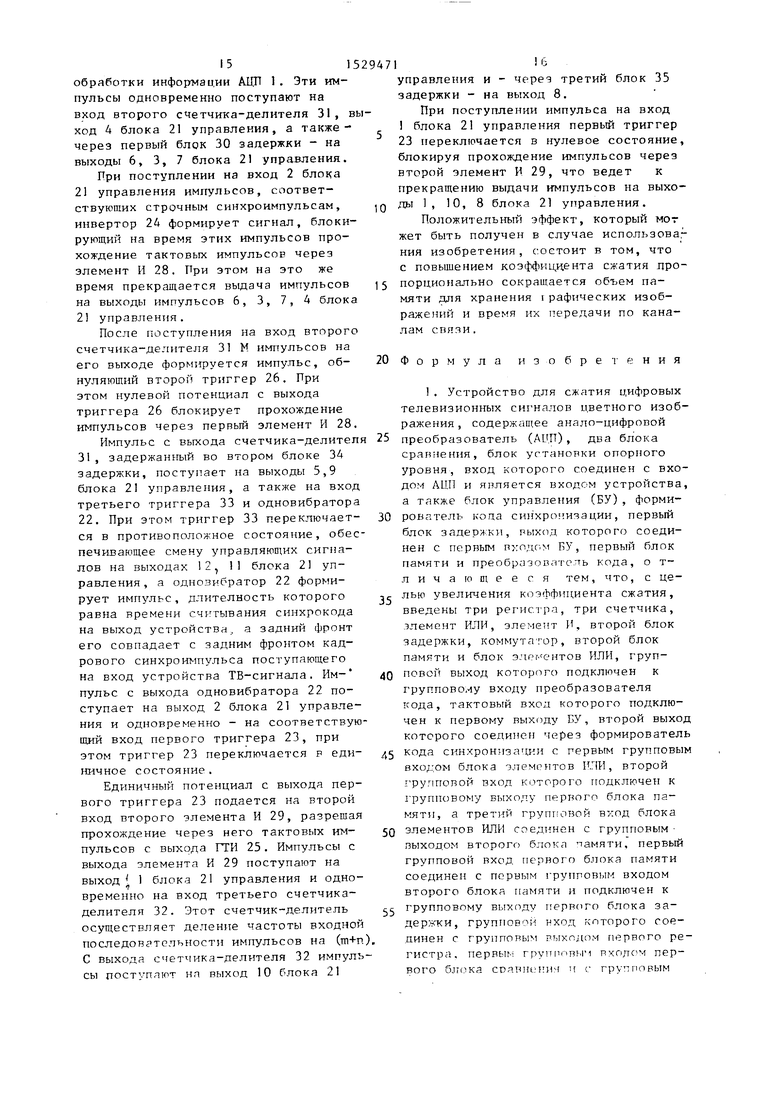

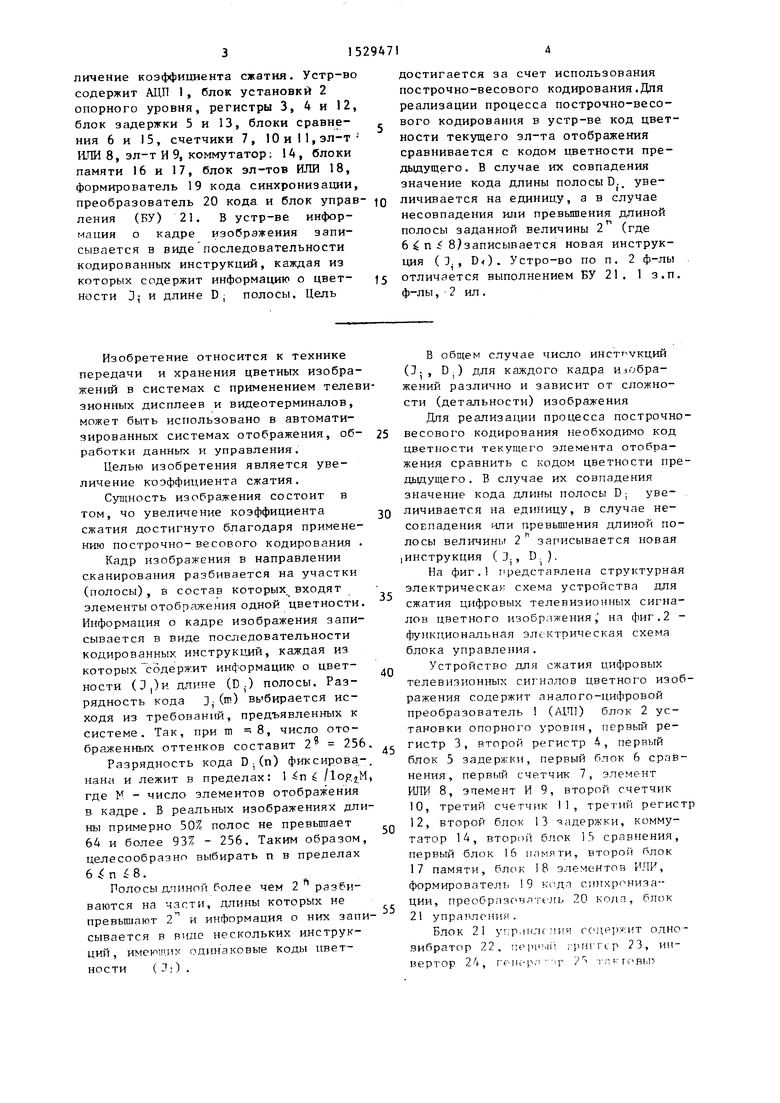

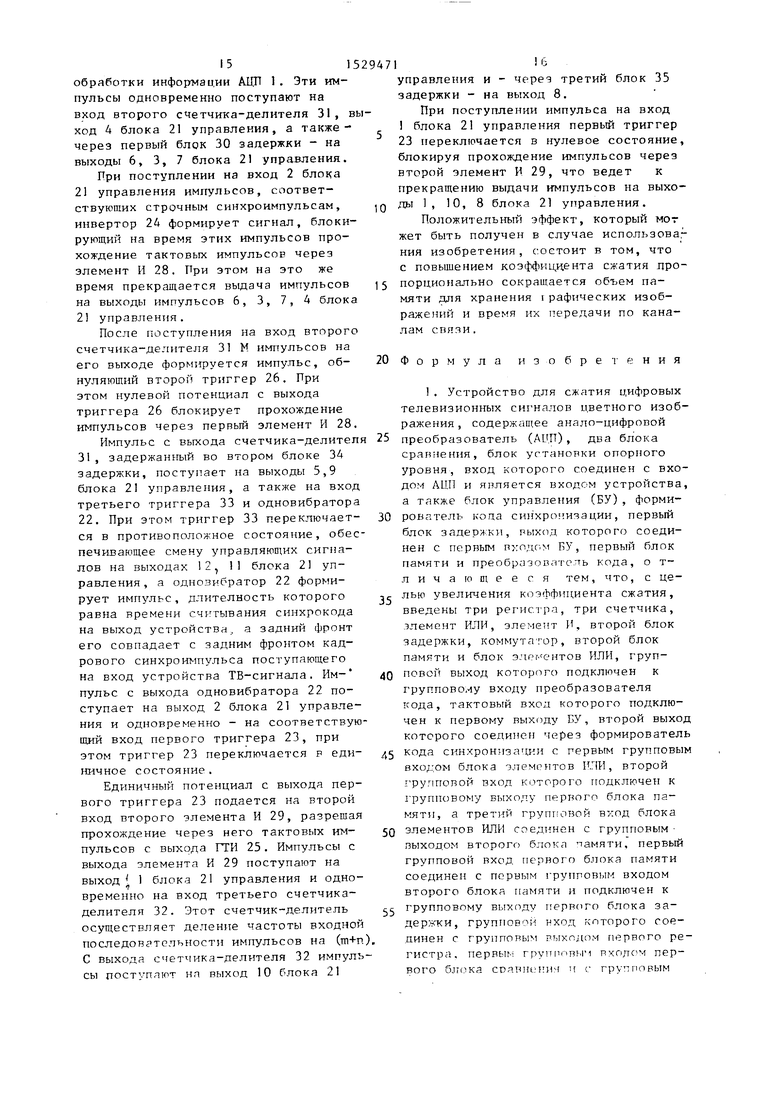

На фиг.1 гфедстарлена структурная электрическая схема устройства для сжатия цифровых телевизионных сигналов цветного изображения, на фиг.2 - функциональная электрическая схема блока управления.

Устройство для сжатия цифровых телевизионных сигналов цветного изображения содержит аналого-цифровой преобразователь 1 (А1П1) блок 2 установки опорного уровня, первый регистр 3, второй регистр 4, первый блок 5 задержки, первый блок 6 сравнения, первый счетчик 7, элемент ИЛИ 8, эпемент И 9, второй счетчик 10, третий счетчик II, третий регистр 12, второй блок 13 задержки, коммутатор 14, второй блок 15 сравнения, первый блок 16 1ГЛМЯТИ, второй блок 17 памяти, блок 18 элементов ИЛИ, формирователь 19 К(дл ситгхрониза- ции, преобрпзс вгтгель 20 кода, блок 21 управления.

Блок 21 ynp.uf. K мия сс 11,ержит одно - вибратор 22. iiein Mi rprirrtp 23, инвертор 24, rpiit i -i Г г,-и-г о БЫТимпульсов, второй триггер 26, первый счетчик-делитель 27, первый элемент И 28, второй элемент И 29, первьи блок 30 задержки, второй счет чш -деяитель 31, третий счетчик-делитель 32, третий триггер 33, второй блок 34 задержки, третий блок 35 задержки.

АЦП 1 преобразует аналоговый те- левиэионный сигнал в цифровой, где каждому элементу отображения соответствует т-разрядный код цветности. Вход аналого-цифрового преобразователя 1 объединен с входом блока 2 установки опорного уровня и является входом устройства.

Блок 2 установки опорного уровня предназначен для формирования импульсов, соответствующих кадровым и строчным синхроимпульсам аналогового телевизионного сигнала.

Первый регистр 3 предназначен для записи, хранения и выдачи кода цветности текущего элемента отобра- жения.

Второй регистр 4 предназначен для записи, хранения и выдачи кода цветности предыдущего элемента отображения .

Первый блок 5 задержки предназначен для задержки кода цветности, поступающего на входы блоков памяти (16, 17), на время, требуемое для переключения второго счетчика 10.

Первый блок 6 сравнения предназначен для поразрядного сравнения га- разрядных кодов цветности текущего и предыдущего элементов отображения и формирования на своем выходе единичного импульса в случае их несовпадения. Первый блок 6 сравнения содержит та элементов ИСКЛЮЧАЮЦЩЕ ИЛИ, выходы которых подключены к входам элемента ИЛИ, выход которого подключен к первому входу элемента И, второй вход которого является третьим входом первого блока 6 сравнения, первым входом которого служат первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых образуют второй вход блока 6 сравнения, выходом которого служит выход элемента И.

Первый счетчик 7 предназначен для формирования п-разрядного кода длины полосы (D ,.) , причем численно код D. выражет количество элементов отображения, цветность которых совпадает

с цветностью предшествующего каждому из них элемента отображения.

Элемент ИЛИ 8 предназначен для объединения выходов первого блока 6 сравнения и элемента И 9.

Элемент И 9 предназначен для формирования импульса переполнения первого счетчика 7.

Второй счетчик 10 предназначен для формирования кода адреса обращения к блоку памяти (16 или 17), работающему в режиме записи-в данном цикле обработки информации.

Третий счетчик J предназначен для формирования кода адреса обращения к блоку памяти (16 или 17), работающему в данном цикле обработки в режиме считывания.

Третий регистр 12 предназначен для записи, хранения и выдачи на второй групповой вход второго блока 15 сравнения кода максимального адреса (то есть адреса ячейки памяти блока 16 или 17 памяти в которую записана инструкция о последней полосе предыдущего кадра). Этот код необходим для формирования сигнала окончания считывания инструкций на выход устройства.

Второй блок 13 задержки предназначен для задержки кода длины полосы, поступающего одновременно на соответствующие групповые входы первого и второго блоков (16 и 17) памя- ти, на время, требуемое для переключения второго счетчика 10.

Коммутатор 14 предназначен для поочередного подключения выходов второго, третьего счетчиков 10, П и соответствующим групповым вхопям первого и второго блоков 16 и 17 памяти.Выбор блока памяти (16 или 17), к которому осуществляется подключение выхода того или иного счетчика (10 или 11), определяется комбинацией сигналов, поступаюо их на первый, второй входы (входы управления) коммутатора 14. Коммутатор 14 содержит четыре блока элементов И, два блока элементов ИЛИ, выходы которых являются групповыми выходами коммутатора 14, первьи групповой вход которого образован первыми входами первого и второго блоков элементов И. Второй групповой вход коммутатора 14 образован первыми входами третьего и четвертого блоков элементов И.

Второй блок 15 сравнения предназначен для сравнения кода максимального адреса и кода текущего адреса (т.е. адреса ячейки памяти, из кото- рой осуществляется считывание инструкций) , а также для формирования единичного импульса при совпадении этих кодов.

Первый блрк 16 памяти предназна- чен для записи, хранения и вьщачи инструкций (J,Dj) о коде изображения .

Назначение второго блока 17 памят аналогично назначению первого блока 16 памяти.

Блок 18 элементов ИЛИ. предназначен для объединения выходов первого блока 16 памяти, второго блока 17 памяти, формирователя 19 кода синхро- низации.

Формирователь 19 кода синхронизации предназначен для хранения и выдачи синхронизирующей кодовой ком- бинаци перед началом считыва-

Тшя инструкций (-Э,- ; ° кадре изображения.

Преобразователь 20 кода предназначен для преобразования считываемых в параллельном коде инструк- ций О., D.) в последовательный код. Преобразователь 20 кода содержит счетчик и мультиплексор, выход которого является выходом преобразователя 20 кода, первый вход которого подключен к информационным входам мультиплексора, адресные входы которого подключены к выходам счетчика, счетный вход которого является входом управления преобразователя 20 кода.

Блок 21 управления предназначен дпя обеспечения согласованной работы блоков устройства путем формирования и выдачи управляющих сигналов и так- товых импульсов на соответствующие входы блоков устройства.

Одновибратор 22 (фиг. 2) предназначен для формирования импульса заданной длительности при поступле- НИИ на его вход единичного импульса

Первый триггер 23 предназначен для управления прохождением тактовых импульсов через второй элемент

И 29.

Инвертор 24 предназначен для формирования сигнала, запрещающего на время поступления на вход устройства кадровых и строчных синхроимпульсов формирование и выдачу тактовых импульсов на выкоды, подключенные к входам блоков устройства, которые обеспечивают обработку поступающей информации.

Генератор 25 тактовых импульсов предназначен для формирования тактовых импульсов с частотой в (та+п) раз больщей, чем частота обработки информации АЦП 1. Такая частота необходима для обеспечения считывания информации о кадре за время, не превьшающее время поступления кадра на вход устройства. В самом неблагоприятном случае (для изображения, в котором цветность каждого последующего элемента отображения отличается от цветности предьщущего) для описания одного элемента отображения требуется (m+n) бит, поэтому требуемая скорость считывания информации должна быть минимум в (т+п) раз выше скорости обработки информации АЦП 1 .

Второй триггер 26 предназначен дпя управления прохождением тактовых импульсов через первый элемент И 28.

Первый счетчик-делитель 27 имеет коэффициент деления, равный (т+п), и предназначен для формирования импульсов с частотой, равной частоте обработки информации А1Щ.

Первый элемент И 28 предназначен для управления выдачей тактовых импульсов на вход первого счетчика-делителя 27.

Второй элемент И 29 предназначен для управления выдачей тактовых импульсов одновременно на выход 1 блок 21 управления и вход третьего счетчика-делителя 32.

Второй блок ЗА задержки предназначен для задержки импульсов, поступающих на его вход, на некоторое время 1,1 , причем г 7 1 7 Гз(где 1, , -Г, tj - время задержки импульса соответственно на первом, втором, третьем выходах второго блока 34 задержки

Второй счетчик-делитель 31 имеет коэффициент цепелшя, равный числу элементов изображения в кадре (И),и предназначен для формирования импульса, свидетельств тощего о saBepmeiniii обработки кадра.

Третий счетчик-делитель 32 имеет коэффипиент деления, равный (т+п), и предназначен для формирования импульсов , каждый из которых формируется

no окончании считыиаиия (ш+n)-разряд- нон инструкции г;1 выход устройства.

Третий TpifD ep 33 имеет счетный вход (Т-григгер) н предназначен для формирования управляющих сигналов (потенциалов) .

Первый блок 30 задержки предназначен для задержки импульсов, поступаю- цщх на его вход, на различное время

причем

t , 7 , 7 (.

(где

1 7

Lj- время задержки соответственно н первом, втором, третьем выходах первого блока 30 задержки).

Третий блок 35 задержки предназначен для разнесения во времени сов, поступающих на соответству-юшие выходы блока 21 управления.

Устройство работает следующим образом.

Поступающий на вход устройства ТВ сигнал преобразуется АЦП 1 в форму, где каждому элементу отображения соответствует т-разрядный код цветности, и подвергается построчно-весовому кодированию. В результате кодирования информация о кадре представляется списком кодированных инструкций (J;, D|), который записывается в первь й или второй блок (16, 17) памяти. Выбор блока памяти осуществляется сигналами с вь ходов блока 21 управления. При этом, если информация о J-TOM кадре бьта записана в первый блок 16 памяти, то информация о (j+l)-M кадре запишется во второй блок 17 памяти. Одновременно с лро- цессом записи сжатой информации о (j+l)-кaдpe во второй блок 17 памяти из первого блока 16 памяти будет осуществляться считывание инструкций о j-том кадре на выход устройства. Информация о следующем (j+2)-M кадре запишется в освободившийся первый блок 16 памяти. Таким образом запись информации о каждом новом кадре будет осуществляться в освободившийся блок памяти.

Работу устройства рассмотрим по структурной схеме (фиг.1).

В исходном состоянии первый регистр 3, второй регистр 4, второй счетчик 10, третий счетчик 11 обнулены. В третий регистр 12 записан код максимального адреса предыдущего кадра или, если на вход устройства поступает первый кадр, - нулевая комбинация. В один из блоков памяти (16 и-пи 17) записаны кодирован-

5

0

5

0

5

0

5

0

5

ные инструкции (J. , Г).) о прс. и.щун рм кадре (в случае, когда пя нхсмт устройства поступает первый ка.чр, иба блока памяти пбнулсЧ)ьО Для удобства рассмотрения рлбпты AOiiycTiiM, что сжатая информация о предьщушем кадре записана во второй блок 17 памяти.

С поступлением на вход устройства аналогового ТВ-сигнала блок 2 установки опорного уровня формирует им- цульс, соответствующий кадровому синхроимпульсу, и выдает его на вход 2 блока 21 управления, разрешая цикл работы, АЦП 1 преобразует аналоговый сигнал в т-разрядный код цветности, который поступает на групповой вход первого регистра 3. Этот код соответствует текущему элеие:1гу отображения С приходом тактового импульса с блока 21 управления на нервьй вход первого регистра 3 код записывается в регистр. По приходу тактового импульса с блока 21 управления на первый вход второго регистра 4 в этот регистр записывается код, поступающий с группового выхода первого регистра 3. За счет того, что импульс на выходе 4 блока 21 управления опережает импульс на выходе 3, во второй регистр 4 запишется код цветности предыдущего элемента отображения (или, если начиняется обработка нового кадрп, - нулевой комбинации). Коды цветности текущего и предыдущего элементов отобГ Чжения, поступающие с групповых выходов соответственно первого, второго регистров 3, 4 на групповые входы первого, блока 6 сравнения, поразрядно сравниваются. С приходом тактового импульса с выхода 6 блока 21 управления на вход управления первого блока 6 сравнения на его выходе формируется сигнал результата сравнения. Этот сигнал одновременно поступает на первый вход первого счетчика 7 и - через элемент ИЛИ 8 - на первый вход второго счетчика 10.

В случае различия кодов цветности соседних элементов изображения на выходе первого блока 6 сравнения формируется единичный импульс, обнуляющий первый счетчик 7 и увеличивающий состояние второго счетчика 10 нл единицу. Если коды цветности соседних элементов совпадют, то под воздействием нулевого потенциала, поступлю- щего с выхода блока б сравнения, ятп111

рой счетчкк 10 сохранит свое состояние неизменным, а первый счетчик 7 под воздействием импульсов с выхода блока 21 управления увеличит свое сотояние на единицу. Параллельный код цветности элемента (J.) с выхода первого регистра 3 через первый блок 5 задержки одновременно поступает на первые групповые входы блоков памяти (16, I7).Параллельный код длины полосы (D,-) с группового выхода первого счетчика 7 одновременно поступает на групповой вход первого элемента И 9 и - через второй блок 13 задержки - на вторые групповые входы блоков памяти (16,17).

Коммутатор 14 осуществляет подключение группового выхода второго счет ,чика 10 к третьему групповому входу блока памяти,работающего в режиме записи (в рассматриваемом случае - первого блока 16 памяти). Таким образом, по адресу формируемому вторым счетчиком 10, в первый блок 16 па- мяти производится запись кодированной инструкции (J, D), Если коды цветности текущего и предыдущего элементов отображения совпадают, то запись новой инструкции (с измененным D;) производится ПО старому адресу. Если коды цветности текущего и предыдущего элементов изображения не совпадают, то запись новой инструкции производится- по новому адресу. Так как запись в блок памяти производится асинхронно, то смена адреса на третьем групповом входе блока памяти должна опережать смену кодов (J , D.} соответственно на первом, втором групповых входах того же блока памяти. Для вьтолнения этого условия используются первый, второй блоки 5, 13 задержки. Если длина полосы превышает 2 элементов изображения, то кодирование происхбдит следующим образом.

При полном заполнении первого счетчика 7 (т.е. когда на его выходах установится п единиц ) на вь1- ходе элемента И 9 формируется единичный потенциал, который проходя через элемент ИЛИ 8, воздействует на первый вход второго счетчика 10, при этом состояние счетчика 10 не меняется и инструкция (D-, D.) за-, письшается в блок 16 памяти по старому адресу. С приходом следующего тактового импульса на второй вход

5 0

0 5

5

0

5

7112

первого счетчика 7 чтот счетчик обнуляется, при этом ча выходе элемента И 9 формируется нулевой потенциал, образуя задний фронт импульса. По этому заднему фронту второй счетчик 10 увеличивает свое состояние на единицу, и новая инструкция (с прежним Э| и D; 0) записывается в блок 16 памяти по новому адресу.

При поступлении на вход устройства строчного синхроимпульса блок 2 установки опорного уровня выдает на вход 2 блока 21 управления импульс, синхронный строчному синхроимпульсу, при этом на время длительности этого импульса блок 21 управления пере- ,стает выдавать тактовые импульсы на )выходы 3, 4, 6, 7. Это приводит к тому, что процедуре построчи -весе- вого кодирования будут подвергаться только те части полного ТВ-сигнала, которые несут информацию о цветности.

После обработки последнего элемента кадра с выхода 9 блока 21 управления на первый вход третьего регистра 12 поступит импульс, под воздействием которого в регистр 12 запишется код максимального адреса, поступающий с группового выхода второго счетчика 10. По окончания записи кода максимального адреса в регистр 12 на выходе 5 блока 21 управления формируется импульс, обнуляющий первый регистр 3, второй регистр 4, второй счетчик 10, третий счетчик I1. Одновременно с этим на выходе 11 блока 21 управле П1Я устанавливается нулевой потенциал, а на выходе 12 блока 21 управления - единичный потенциал, чем достигается смена режимов работы первого и второго блоков (16, 17)памяти. На этом цикл кодирования текущего кадра изображения завершается .

С поступлением кадрового синхроимпульса следующего кадра на вход устройства начинается цикл считыва- ния.из первого блока 16 памяти инструкций о предыдущем кадре и коди- рования следующего кадра. Кодирование следующего кадра изображения осуществляется аналогично рассмотренному, с той разницей, что запись инструкций производится во второй блок 17 памяти.

Считывание информации на выход устройства осуществляется следующим образом.

С началом поступления с выхода блока 2 установки опорного уровня на вход 2 блока 21 управления им пульса, соответствующего кадровому синхроимпульсу, с выхода 2 блока 21 управления на вход формирователя 19 кода синхронизации вьщается единичный потенциал, с выхода 1 блока 21 управления на вход управления преобразователя 20 кода - (т+п) импульсов. Синхрокод в параллельном коде считывается с выхода формирователя 19 кода синхронизации на первый групповой вход блока 18 элементов ИЛИ, с выхода которого он поступает на групповой вход преобразователя 20 кода и с частотой поступления тактовых импульсов на вход управления преобразователя 20 кода выдается на выход устройства в последовательном коде, По заднему фронту импульса, посту- пающего на вход 2 блока 21,управления и соответствующего кадровому синхроимпульсу, на выходе 2 блока 21 управления устанавливается нулевой потенциал, зaпpeD aющий считыва- ,ние синхровхода с выхода формирователя 9 кода синхронизации. По окончании считывания синхрокода с выхода 8 блока 21 управления на первый вход третьего счетчика I1 поступает импульс. Под воздействием этого импульса третий счетчик 11 формирует адрес обращения к блоку памяти, работающему в режиме считывания. В рассматриваемом случае комму- татор 14 подключает групповой выход счетчика 1I к третьему групповому входу первого блока 16 памяти. Инструкция , считываемая из ячейки памяти блока 16 памяти, поступает че- рез блок 1В элементов ИЛИ на групповой вход преобразователя 20 кода и считывается на выход устройства в последовательном коде с частотой тактовых импульсов, поступающих на вход управления преобразователя 20 кода. Код адреса, формируемый третьим счетчиком 11, сравнивается во втором блоке 15 сравненияс кодом максимального адреса, поступающего с выхода третьего регистра 12. Сигнал

результата сравнения С О в случае не равно случае равно) ф

равно

мируется на выходе блока 15 сравнефо

14

5

JQ )5 2025 ЗОQдQг

35

рния по приходу на его тактовый вход импульса с льрсодч Ю блока 2J управления . За счет того, что импульсы с выхода 10 блока 21 управления несколько опережают импульсы с выхода 8, второй блок 15 сравнения сравни вает код максимального адреса с кодом адреса ячейки памяти, инструкция из которой была только что считана. Это приводит к тому, что импульс совпадения кода максимального адреса с кодом текущего адреса формируется на выходе блока 15 сравнения по окончании считывания всех инструкций о данном кадре из первого блока 16 памяти. Этот импульс обнуляет третий регистр 12 и, поступая на вход 1 блока 21 управления, запрещает выдачу импульсов с выходов 8, 10, 1 блока 21 управления до поступления на вход устройства кадрового синхроимпульса очередного кадра. На этом цикл считывания инструкции о данном кадре изображения завершается.

Блок 21 управления работает следующим образом.

В исходном состоянии второй триггер 26, первьй триггер 23, первый счетчик-делитель 27, второй счетчик- делитель 31, третий с четчик-делитель 32 обнулены. Поступающий на вход 2 блока 21 управления импульс одновременно подается на первый вход второго триггера 26 и вход инвертора 24. По переднему фронту кмпульса, соответствующего кадровому синхроимпульсу, второй триггер 26 переключается в единичное состояние.Едишгчпый потенциал с его выхода подается на третий вход первого элемента И 28. Однако нулевой.потенциал с выхода инвертора 24 продолжает удерживать первьш элемент И 28 в закрытом состоянии, препятствуя прохождению тактовых импульсов с выхода ГТИ 25 на. НЫХРД элемента И 28. По заднему Фронту поступающего на вход 2 блока 21 управления импульса на вь ходе инвертора 24 формируется единичньпЧ пс тен- циал, который поступает па второй вход первого элемента И 28, разрешая прохождение через него тактопых импульсов. Эти импульсы поступают на вход первого счетчика-делителя 27, осуществляющего деление частоты входной последовательности на (т+п). Чпг- тота импульсов на выходе первого счетчика-делителя 27 равна частотг

1515

обработки информации АЦП 1. Эти импульсы одновременно поступают на вход второго счетчика-делителя 31, вход 4 блока 21 управления, а также- через первый блок 30 задержки - на выходы 6, 3, 7 блока 21 управления.

При поступлении на вход 2 21 управления импульсов, соответствующих строчным синхроимпульсам, инвертор 24 формирует сигнал, блокирующий на время этих импульсов прохождение тактовых импульсов через элемент И 28. При этом на это же время прекращается вьщача импульсов на выходы импульсов 6, 3, 7, 4 блока 21 управления.

После поступления на вход второго счетчика-делителя 31 М импульсов на его выходе формируется импульс, об- нуляющий второй триггер 26. При этом нулевой потенциал с выхода триггера 26 блокирует прохождение импульсов через первый элемент И 28.

Импульс с выхода счетчика-делител 31 , задержанный во втором блоке 34 задержки, поступает на выходы 5,9 блока 21 управления, а также на вход третьего триггера 33 и одновибратора 22. При этом триггер 33 переключает- ся в противоположное состояние, обеспечивающее смену управляющих сигналов на выходах 12, 11 блока 21 управления, а одновибратор 22 формирует импульс, длителность которого равна времени считывания синхрокода на выход устройства, а задний фронт его совпадает с задним фронтом кадрового синхроимпульса поступающего на вход устройства ТВ-сигнала. Им- пульс с выхода одновибратора 22 поступает на выход 2 блока 21 управления и одновременно - на соответствующий вход первого триггера 23, при этом триггер 23 переключается р еди- ничное состояние.

Единичный потенциал с выхода первого триггера 23 подается на второй вход второго элемента И 29, разрешая прохождение через него тактовых им- пульсов с выхода ГТИ 25. Импульсы с выхода элемента И 29 поступают на выход { 1 блока 21 управления и одновременно на вход третьего счетчика- делителя 32. Этот счетчик-делитель осуществляет деление частоты входной последовательности импульсов на (m+n С выхода счетчика-делителя 32 импульсы поступают на выход 10 блока 21

управления и - через третий блок 35

задержки - на выход 8.

При поступлении импульса на вход 1 блока 21 управления первый триггер 23 переключается в нулевое состояние блокируя прохождение импульсов через второй элемент И 29, что ведет к прекращению выдачи импульсов на выходы 1, 10, 8 блока 21 управления.

Положительный эффект, который мог жет быть получен в случае использова ния изобретения, состоит в том, что с повьшением коэффициента сжатия дро порционально сокращается объем памяти для хранения iрафических изображений и время их передачи по каналам связи.

Формула изобретения

1

входом.второго регистра, групповой вход первого регистра подключен к групповому Бьгходу АЩТ, первый вход первого регистра подключен к третьему выходу БУ, четвертый выход которого соединен с первым входом второго регистра, групповой выход которог подключен к второму групповому входу первого блока сравнения, пятый выход БУ подключен к второму входу первого регистра и второму входу первого регистра, шестой выход БУ соединен с входом управления первого блока сран нения, выход которого подключен к первому входу элемента ИЛИ и к первому входу первого счетчика, второй вход которого подключен к седьмому выходу БУ, групповой выход первого счетчика соединен через элемент И с вторым входом элемента {ШИ, з через второй блок задержки соединен с вторы ми rpynnoBbLMH входами первого и второго блоков памяти, выход элемента ИЛИ соединен с первым входом второго счетчика, восьмой выход БУ подключен к первому входу третьего счетчика, второй вход которого соединен с вторым входом второго счетчика и пятым выходом БУ, групповой выход второго счетчика подключен к групповому входу третьего регистра и к первому групповому входу коммутатора, второй групповой вход которого подключен к групповому выходу третьего счетчика, и первому групповому входу второго блока сравнения, девятый выход БУ соединен с первым входом третьего регистра, десятый выход БУ подключен к тактовому входу второго блока сравне ния, выход которого соединен с вторы входом третьего регистра, групповой выход которого подключен к второт-г/ групповому входу второго блока сравнения, первый вход коммутатора сое- дивен с первым входом первого блока памяти и первым входом второго блока памяти и подключен к одиннадцатому выходу БУ, двенадцатый выход которог подключен к второму входу коммутатора второму входу первого блока памяти и второму входу второго блока памяти, третий групповой вход первого блока памяти соединен с первым-групповым выходом коммутатора, второй группо- вой выход которого подключен к третьему групповому входу второго блока памяти, второй вход блока управления

I18

подключен к выходу блока установки опорного уровня,а выход преобразователя кода является выходом устройства.

Составитель О. Канатчикова Редактор А. Маковская Техред А.Кравчук Корректор Э.Лончаксша

Заказ 7763/57

Тираж 626

ВНИИПИ Государстпеиного комитета по и-эобретениям и открытиям при ГКПТ CCCF 113035, Москва, Ж-35, Раушская наб., д. ч/З

Фиг. 2

Подписное

| Способ приготовления катализатора для дегидрирования этилового спирта в ацетальдегид | 1960 |

|

SU136325A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-12-15—Публикация

1988-02-02—Подача