Предлагаемое изобретение относится к области радиотехники и связи и может использоваться в быстродействующих цифроаналоговых преобразователях, системах передачи информации, различных вычислительных и измерительных устройствах.

В современных системах передачи и обработки сигналов широкое распространение получили цифроаналоговые преобразователи (ЦАП) с коммутацией весовых токов [1-9], которая обеспечивается специальным драйвером, осуществляющим переключение весовых токов [10-22]. Динамические параметры таких драйверов определяют быстродействие ЦАП, характеризующееся допустимой частотой схемы входного кода.

Ближайшим прототипом заявляемого устройства является драйвер, представленный в патенте фирмы Analog Devices US 6.031.477 fig. 1. Кроме этого, данная архитектура драйвера, выполненная на транзисторах с другим типом канала, присутствует в патенте US 6.559.784 fig. 2. Он содержит первый 1 и второй 2 выходные полевые транзисторы, стоки которых соединены с соответствующими противофазными первым 3 и вторым 4 токовыми выходами устройства, истоки объединены и соединены с источником коммутируемого разрядного тока 5, первый 6 коммутирующий полевой транзистор, затвор которого связан с первым 7 логическим входом устройства, исток подключен к шине источника питания 8, а сток соединен с затвором первого 1 выходного полевого транзистора и истоком второго 9 коммутирующего полевого транзистора, причем затвор второго 9 коммутирующего полевого транзистора связан со вторым 10 противофазным логическим входом устройства, третий 11 коммутирующий полевой транзистор, затвор которого связан со вторым 10 противофазным логическим входом устройства, исток подключен к шине источника питания 8, а сток соединен с затвором второго 2 выходного полевого транзистора и истоком четвертого 12 коммутирующего полевого транзистора, причем затвор четвертого 12 коммутирующего полевого транзистора связан с первым 7 логическим входом устройства.

Существенный недостаток известного устройства (независимо от типа канала применяемых в нем полевых транзисторов) состоит в том, что время установления переходного процесса при переключении разрядного тока сравнительно велико, что отрицательно сказывается на частоте смены входного кода ЦАП на его основе. Данный недостаток проявляется, прежде всего, в том случае, когда быстродействие драйвера меньше быстродействия входного триггера, формирующего сигналы для первого 7 и второго 10 противофазных логических входов устройства (на чертеже фиг. 1 триггер не показан). Кроме этого в качестве недостатков следует назвать проблемы, связанные с необходимостью реализации цепи задания логического нуля, соответствующие издержки потребляемой мощности, а также площади на кристалле. Если эта цепь задания - общая для нескольких коммутаторов весовых токов, то на нее накладываются переходные процессы от переключения всех разрядов, что создает дополнительный кодозависимый источник искажений спектра выходного сигнала ЦАП. Если же эти цепи для развязки делаются индивидуальными для каждого разряда, то это еще больше усложняет общую схему ЦАП и приводит к увеличению общей потребляемой мощности.

Основная задача предлагаемого изобретения состоит в повышении быстродействия драйвера.

Введение новых связей в схему фиг. 1 позволяет не только повысить быстродействие, но и решить другие вышеназванные проблемы драйвера-прототипа. В структуре многоразрядного ЦАП предлагаемые драйверы получают индивидуальные источники задания логического нуля, но при этом не требуется дополнительных затрат площади на кристалле, не увеличивается потребляемая мощность, а общая схема устройства при этом упрощается. Уменьшение времени нарастания выходного сигнала драйвера (с 185 пс до 106 пс) уменьшает также влияние рассогласования параметров транзисторов и других эффектов, создающих паразитные составляющие в спектре выходного сигнала ЦАП.

Поставленные задачи достигаются тем, что в драйвере коммутатора разрядного тока фиг. 1, содержащем первый 1 и второй 2 выходные полевые транзисторы, стоки которых соединены с соответствующими противофазными первым 3 и вторым 4 токовыми выходами устройства, истоки объединены и соединены с источником коммутируемого разрядного тока 5, первый 6 коммутирующий полевой транзистор, затвор которого связан с первым 7 логическим входом устройства, исток подключен к шине источника питания 8, а сток соединен с затвором первого 1 выходного полевого транзистора и истоком второго 9 коммутирующего полевого транзистора, причем затвор второго 9 коммутирующего полевого транзистора связан со вторым 10 противофазным логическим входом устройства, третий 11 коммутирующий полевой транзистор, затвор которого связан со вторым 10 противофазным логическим входом устройства, исток подключен к шине источника питания 8, а сток соединен с затвором второго 2 выходного полевого транзистора и истоком четвертого 12 коммутирующего полевого транзистора, причем затвор четвертого 12 коммутирующего полевого транзистора связан с первым 7 логическим входом устройства, предусмотрены новые элементы и связи - стоки второго 9 и четвертого 12 коммутирующих транзисторов связаны с объединенными истоками первого 1 и второго 2 выходных транзисторов.

На чертеже фиг. 1 представлена схема усилителя-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с формулой изобретения.

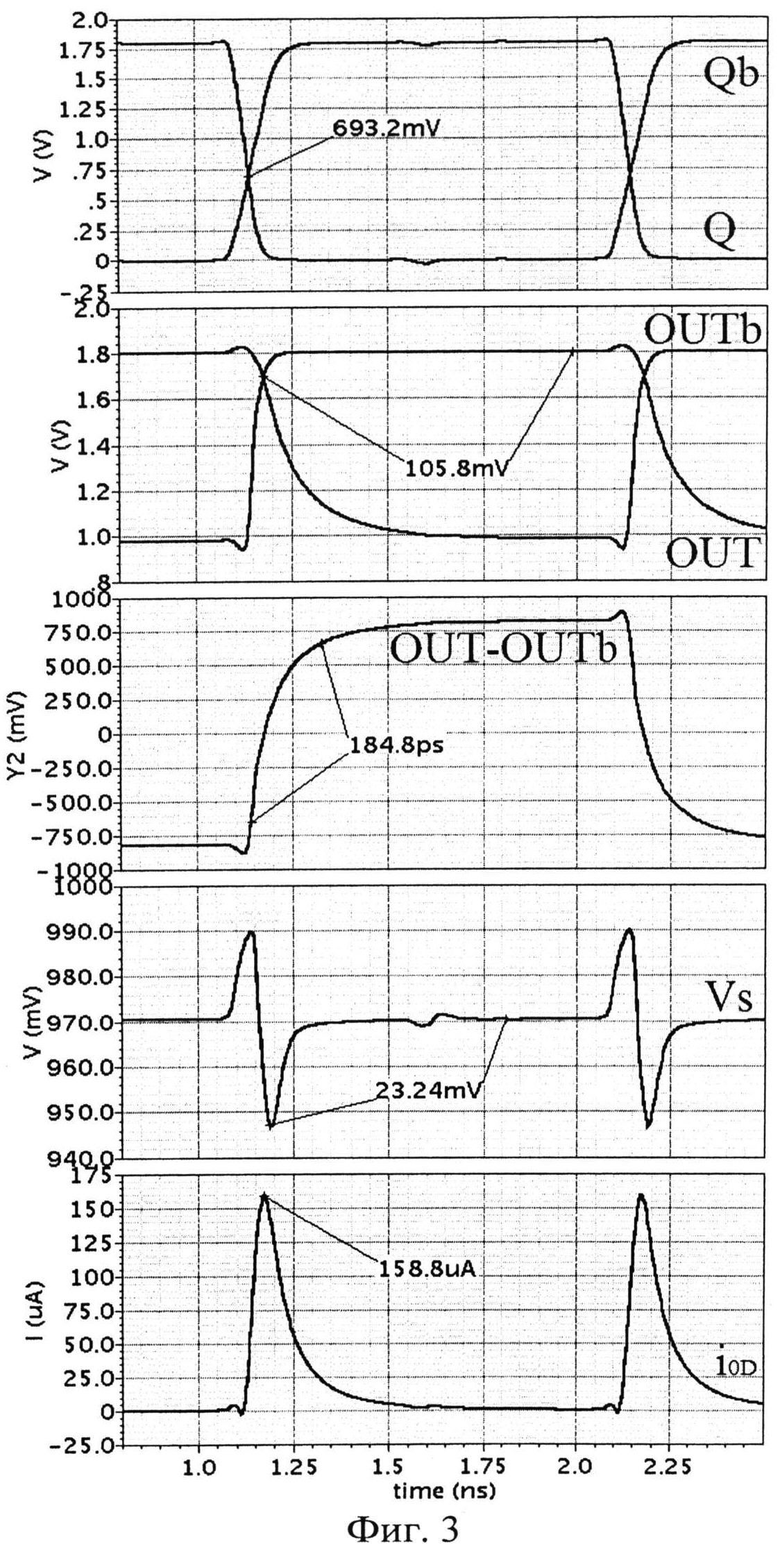

На чертеже фиг. 3 представлена временная диаграмма сигналов в схеме-прототипе фиг. 1.

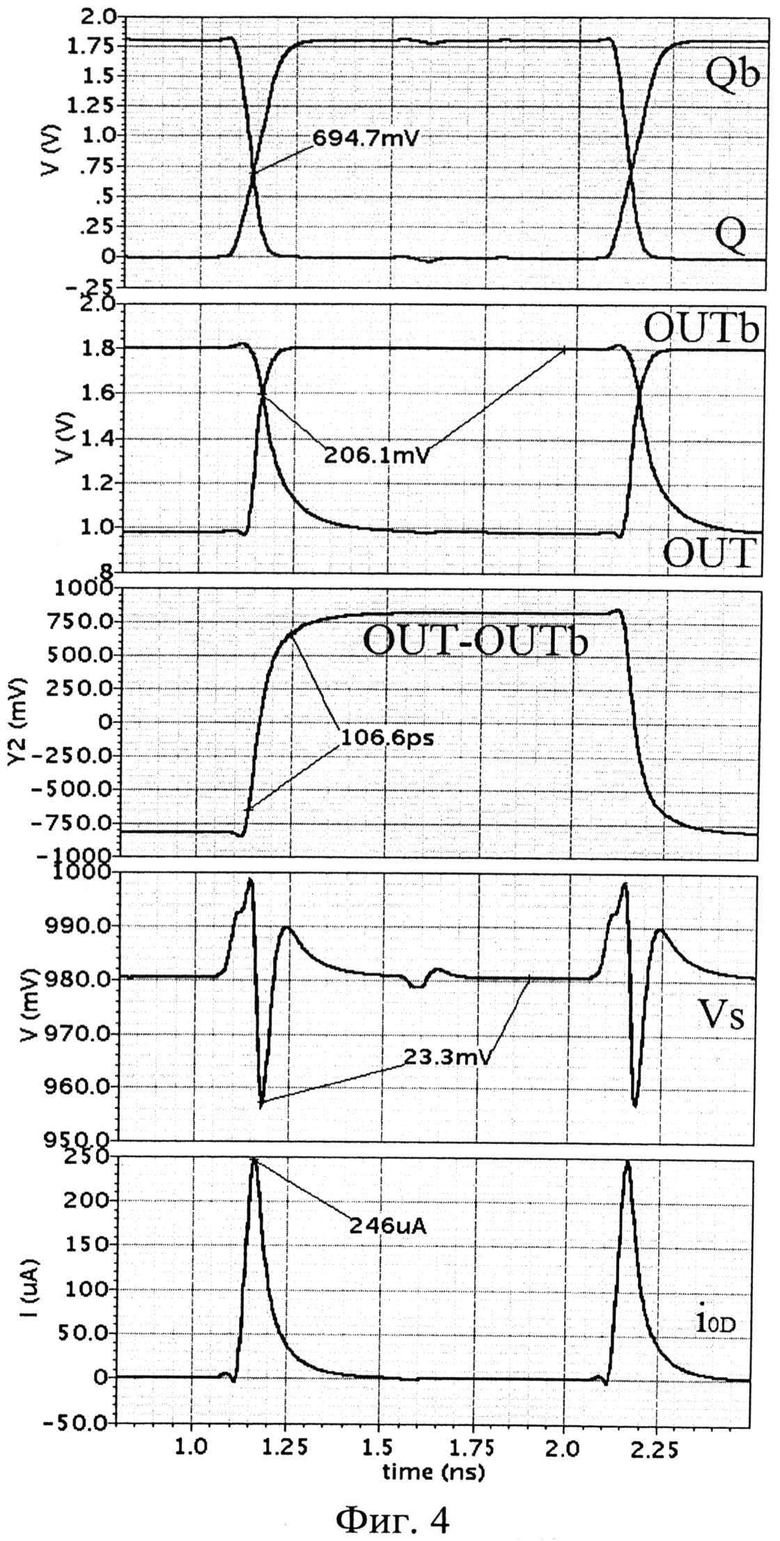

На чертеже фиг. 4 представлена временная диаграмма сигналов в заявляемой схеме (фиг. 2).

Драйвер коммутатора разрядного тока цифроаналогового преобразователя на полевых транзисторах фиг. 2 содержит первый 1 и второй 2 выходные полевые транзисторы, стоки которых соединены с соответствующими противофазными первым 3 и вторым 4 токовыми выходами устройства, истоки объединены и соединены с источником коммутируемого разрядного тока 5, первый 6 коммутирующий полевой транзистор, затвор которого связан с первым 7 логическим входом устройства, исток подключен к шине источника питания 8, а сток соединен с затвором первого 1 выходного полевого транзистора и истоком второго 9 коммутирующего полевого транзистора, причем затвор второго 9 коммутирующего полевого транзистора связан со вторым 10 противофазным логическим входом устройства, третий 11 коммутирующий полевой транзистор, затвор которого связан со вторым 10 противофазным логическим входом устройства, исток подключен к шине источника питания 8, а сток соединен с затвором второго 2 выходного полевого транзистора и истоком четвертого 12 коммутирующего полевого транзистора, причем затвор четвертого 12 коммутирующего полевого транзистора связан с первым 7 логическим входом устройства. Стоки второго 9 и четвертого 12 коммутирующих транзисторов связаны с объединенными истоками первого 1 и второго 2 выходных транзисторов. Конденсаторы 13, 14 моделируют емкости затвор-исток первого 1 и второго 2 выходных полевых транзисторов, конденсатор 15 моделирует выходную емкость источника коммутируемого разрядного тока 5.

Дополнительные напряжения смещения +Ec18 (узел 18) и +Ec19 (узел 19) обеспечивают статический режим транзисторов 16 и 17, которые образуют источник коммутирующего разрядного тока 5.

Рассмотрим работу схемы фиг.2.

В зависимости от сигналов Q и Qb на логических входах 7 и 10 ток источника коммутируемого разрядного тока 5 протекает через первый 1 или второй 2 выходной полевой транзистор на первый 3 или второй 4 токовый выход, соответственно (фиг. 2).

Например, при Q равном логической единице и, соответственно, Qb, равном логическому нулю, первый 6 коммутирующий полевой транзистор находится в режиме отсечки, а второй 9 коммутирующий полевой транзистор находится в режиме линейного сопротивления, за счет чего напряжение затвор-исток первого 1 выходного полевого транзистора равно нулю (фиг. 2). В то же время третий 11 коммутирующий полевой транзистор находится в режиме линейного сопротивления, а четвертый 12 коммутирующий полевой транзистор находится в режиме отсечки, за счет чего напряжение на затворе второго 2 выходного полевого транзистора равно напряжению V1D на шине источника питания 8. При этом ток источника коммутируемого разрядного тока 5 протекает через второй 2 выходной полевой транзистор на второй 4 токовый выход.

При переключении сигнала Q в состояние логического нуля и, соответственно, Qb - в состояние логической единицы первый 6 и четвертый 12 коммутирующие полевые транзисторы переходят в режим линейного сопротивления, а второй 9 и третий 11 коммутирующие полевые транзисторы переходят в режим отсечки (фиг. 2). При этом первый 1 выходной полевой транзистор открывается, а второй 2 выходной полевой транзистор закрывается, в результате чего происходит перекоммутация тока источника коммутируемого разрядного тока 5 со второго 4 токового выхода на первый 3 токовый выход.

В зависимости от характеристик (фиг. 3 и фиг. 4) выходных сигналов OUT и OUTb драйверов фиг. 1 и фиг. 2, а также из-за нелинейности характеристик транзисторов при переключении разрядного тока возникают нежелательные возмущения напряжения VS в истоках коммутаторов. Особенно нежелательна ситуация, когда при значительном уменьшении Vs транзистор 16 (и, возможно, 17) коммутируемого разрядного источника тока 5 уходит из режима насыщения, что значительно уменьшает выходной импеданс в его стоке и ухудшает переходный процесс коммутации тока. Уменьшение влияния описанного эффекта достигается главным образом за счет настройки пересечения фронтов сигналов OUT и OUTb таким образом, чтобы сначала открывался выключенный выходной полевой транзистор, а потом закрывался включенный выходной полевой транзистор. Оптимальным можно считать такое пересечение фронтов сигналов OUT и OUTb, при котором возмущения VS примерно симметричны относительно установившегося значения. Однако после такой оптимизации пересечение фронтов сигналов OUT и OUTb находится достаточно близко к уровню логической единицы. При этом фронты сигналов OUT и OUTb формируются не одновременно, а практически последовательно, что увеличивает время смены логического состояния сигналов OUT и OUTb на выходах драйвера-прототипа.

Применение заявляемого драйвера позволяет упростить по сравнению с прототипом общую схему устройства, уменьшить площадь кристалла и уменьшить потребляемую мощность за счет исключения дополнительной цепи задания напряжения логического нуля V0D, так как роль этой цепи выполняет уже существующий в схеме узел - узел подключения истоков выходных 1 и 2 полевых транзисторов. Важно отметить, что при этом в каждом разряде ЦАП такой драйвер имеет индивидуальную цепь задания логического нуля.

Кроме того, в заявляемом драйвере при переключении разрядов возникают два механизма поддержания выходного тока источника коммутируемого разрядного тока 5. В конечном итоге это повышает быстродействие драйвера.

Первый механизм связан с тем, что в отличие от прототипа паразитная емкость затвора выключаемого выходного полевого транзистора разряжается (i14 на фиг. 2) не в дополнительную цепь задания V0D, а в выход источника коммутируемого разрядного тока 5.

Второй механизм возникает при пересечении фронтов сигналов Q и Qb достаточно близко к уровню логического нуля, когда существует промежуток времени, на котором закрытые коммутирующие полевые транзисторы драйвера уже открылись, а открытые еще не успели закрыться. В результате возникает «временный путь» протекания тока (i9+i11 на фиг. 2) от выхода источника коммутируемого разрядного тока 5 к цепи задания V1D (шине источника питания 8).

Описанные механизмы поддержания разрядного тока приводят к тому, что по сравнению с прототипом в заявляемом драйвере оптимальное пересечение фронтов сигналов OUT и OUTb смещается ближе к «середине» между V0D и V1D, что позволяет ускорить переключение драйвера. Отметим, что повышение быстродействия драйвера уменьшает влияние рассогласования транзисторов и некоторых других факторов, ухудшающих динамическую линейность ЦАП на его основе.

Для оценки эффективности предложенного решения проведено сравнительное схемотехническое моделирование прототипа и заявляемого драйвера, реализованных в КМОП-технологии с топологической нормой 0,18 мкм. В обеих схемах использовался один и тот же триггер, формирующий сигналы на первом 7 и втором 10 логических входах устройства. Как видно из временной диаграммы на фиг. 3 и фиг. 4, данный триггер был оптимизирован по критерию быстродействия, что обуславливает пересечение фронтов его выходных сигналов Q и Qb достаточно близко (примерно 0,7 В) к середине (0,9 В) между логическими уровнями (0 и 1,8 В). Оптимизация пересечения фронтов сигналов OUT и OUTb драйвера обеспечивается за счет настройки геометрических размеров коммутирующих полевых транзисторов 6, 9, 11 и 12.

В случае прототипа (фиг. 1) оптимальное пересечение фронтов сигналов OUT и OUTb оказалось примерно на уровне V1D - 106 мВ. Как видно из временной диаграммы на фиг.3, при этом возмущения VS практически симметричны и имеют амплитуду около 23 мВ. Отметим, что в качестве цепи задания V0D для схемы прототипа использовался идеальный источник ЭДС, в то время как на реальной цепи задания логического нуля V0D возникающий при переключении импульс тока i0D=i9+i12 (фиг. 1) с амплитудой 158,8 мкА (фиг. 3) вызвал бы соответствующий переходный процесс напряжения V0D. Время нарастания фронта выходного дифференциального сигнала OUT-OUTb драйвера-прототипа составило 184,8 пс.

В случае заявляемого драйвера оптимальное пересечение фронтов сигналов OUT и OUTb сместилось из-за описанных механизмов поддержания разрядного тока и оказалось примерно на уровне V1D - 206 мВ (фиг. 4). При этом, возмущения VS (аналогично прототипу) имеют амплитуду около 23 мВ, однако время нарастания фронта выходного дифференциального сигнала OUT-OUTb драйвера значительно уменьшилось (106,6 пс). Отметим, что в отличие от схемы прототипа возникающий при переключении импульс тока i0D=i9+i12 (фиг. 2) с амплитудой 246 мкА (фиг. 4) выполняет положительную роль поддержания разрядного тока, который в рассматриваемом опыте равен 400 мкА.

В некоторых параметрических случаях, если время переключения драйвера прототипа ощутимо превышает время переключения входного триггера, формирующего сигналы на первом 7 и втором 10 логических входах устройства, применение заявляемого драйвера повышает частоту выборки ЦАП.

Таким образом, заявляемое устройство характеризуется более высоким потенциальным быстродействием, а также имеет другие (указанные в тексте заявки) преимущества в сравнении с прототипом при его применении в составе многоразрядных ЦАП с переключением весовых токов.

Библиографический список

1. Патент US 6.281.825 fig. 2

2. Патент US 7.042.379 fig. 2а

3. Патент US 5.361.068 fig. 1

4. Патент US 6.445.221

5. Патент US 5.396131 fig. 10

6. Патент US 6.246.351 fig. 2

7. Патент US 6.992.609 fig. 5

8. Патент US 5.859.606 fig. 1

9. Патент US 6.362.765 fig. 3

10. Патент US 6.559.784 fig. 2

11. Патент US 6.031.477 fig. 1

12. Патент US 5.148.164 fig. 9

13. Патент US 4.721.866

14. Патент US 5.612.697 fig. 3

15. Патент US 5.689.257 fig. 2A

16. Патент US 5.703.519 fig. 5

17. Патент US 5.917.360 fig. 2

18. Патент US 5.638.001 fig. 2

19. Патент US 5.450.084 fig. 3

20. Патент US 5.038.011 fig. 1В

21. Патент US 4.761.636 fig. 8

22. Патент US 5.790.060 fig. 3, fig. 3

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ИСТОКОВЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2013 |

|

RU2536671C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ИСТОКОВЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2013 |

|

RU2530263C1 |

| УСТРОЙСТВО КОРРЕКЦИИ СКВАЖНОСТИ ВХОДНОГО СИГНАЛА | 2011 |

|

RU2467473C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2736412C1 |

| Быстродействующий операционный усилитель с повышенной скоростью нарастания выходного напряжения | 2018 |

|

RU2683160C1 |

| УСТРОЙСТВО РЕГУЛИРОВАНИЯ ТЕМПЕРАТУРЫ ЭЛЕКТРОНАГРЕВА | 2016 |

|

RU2612311C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ ДВУХКАСКАДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2721942C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ ДЛЯ АКТИВНЫХ RC-ФИЛЬТРОВ, РАБОТАЮЩИХ В УСЛОВИЯХ ВОЗДЕЙСТВИЯ ПОТОКА НЕЙТРОНОВ И НИЗКИХ ТЕМПЕРАТУР | 2020 |

|

RU2724921C1 |

| Быстродействующий выходной каскад аналоговых микросхем на комплементарных полевых транзисторах с управляющим p-n переходом для работы при низких температурах | 2019 |

|

RU2711725C1 |

Изобретение относится к области радиотехники и может использоваться в быстродействующих цифроаналоговых преобразователях (ЦАП), в том числе системах передачи информации. Технический результат заключается в повышении быстродействия и уменьшении искажения спектра выходного сигнала ЦАП. Устройство содержит первый (1) и второй (2) выходные полевые транзисторы, стоки которых соединены с соответствующими противофазными первым (3) и вторым (4) токовыми выходами устройства, истоки объединены и соединены с источником коммутируемого разрядного тока (5), первый (6) коммутирующий полевой транзистор, затвор которого связан с первым (7) логическим входом устройства, исток подключен к шине источника питания (8), а сток соединен с затвором первого (1) выходного полевого транзистора и истоком второго (9) коммутирующего полевого транзистора, причем затвор второго (9) коммутирующего полевого транзистора связан со вторым (10) противофазным логическим входом устройства, третий (11) коммутирующий полевой транзистор, затвор которого связан со вторым (10) противофазным логическим входом устройства, исток подключен к шине источника питания (8), а сток соединен с затвором второго (2) выходного полевого транзистора и истоком четвертого (12) коммутирующего полевого транзистора, причем затвор четвертого (12) коммутирующего полевого транзистора связан с первым (7) логическим входом устройства. Стоки второго (9) и четвертого (12) коммутирующих транзисторов связаны с объединенными истоками первого (1) и второго (2) выходных транзисторов. 4 ил.

Быстродействующий драйвер коммутатора разрядного тока цифроаналогового преобразователя на полевых транзисторах, содержащий первый (1) и второй (2) выходные полевые транзисторы, стоки которых соединены с соответствующими противофазными первым (3) и вторым (4) токовыми выходами устройства, истоки объединены и соединены с источником коммутируемого разрядного тока (5), первый (6) коммутирующий полевой транзистор, затвор которого связан с первым (7) логическим входом устройства, исток подключен к шине источника питания (8), а сток соединен с затвором первого (1) выходного полевого транзистора и истоком второго (9) коммутирующего полевого транзистора, причем затвор второго (9) коммутирующего полевого транзистора связан со вторым (10) противофазным логическим входом устройства, третий (11) коммутирующий полевой транзистор, затвор которого связан со вторым (10) противофазным логическим входом устройства, исток подключен к шине источника питания (8), а сток соединен с затвором второго (2) выходного полевого транзистора и истоком четвертого (12) коммутирующего полевого транзистора, причем затвор четвертого (12) коммутирующего полевого транзистора связан с первым (7) логическим входом устройства, отличающийся тем, что стоки второго (9) и четвертого (12) коммутирующих транзисторов связаны с объединенными истоками первого (1) и второго (2) выходных транзисторов.

| US 6031477A, 29.02.2000 | |||

| US 5917360A, 29.06.1999 | |||

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2510979C1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

Авторы

Даты

2016-01-10—Публикация

2014-08-26—Подача