Изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в быстродействующих аналоговых и аналого-цифровых интерфейсах для обработки сигналов датчиков.

В современной радиоэлектронной аппаратуре, приборостроении и измерительной технике находят применение КМОП операционные усилители (ОУ), которые определяют динамические параметры многих аналоговых интерфейсов, АЦП, драйверов линий связи, ограничителей спектра и т.п. Широкое распространение получили КМОП ОУ с трехкаскадной архитектурой, которая включает комплементарный входной дифференциальный каскад (ДК) класса dual-input stage [1-31], два токовых зеркала и буферный усилитель. Предполагаемое изобретение относится к данному классу устройств.

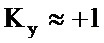

Ближайшим прототипом (фиг. 1) заявляемого устройства является ОУ по патенту США № 6.268.769, fig.3. Он содержит (фиг. 1) первый 1 и второй 2 входные полевые транзисторы разного типа проводимости, объединенные затворы которых подключены к инвертирующему входу 3 устройства, третий 4 и четвертый 5 входные полевые транзисторы разного типа проводимости, затворы которых объединены и подключены к неинвертирующему входу 6 устройства, первый 7 токостабилизирующий двухполюсник, включенный между первой 8 шиной источника питания и объеденными истоками первого 1 и четвертого 5 входных полевых транзисторов, сток второго 2 входного полевого транзистора связан с первой 8 шиной источника питания, второй 9 токостабилизирующий двухполюсник, включенный между второй 10 шиной источника питания и объеденными истоками второго 2 и третьего 4 входных полевых транзисторов, сток первого 1 входного полевого транзистора связан со второй 10 шиной источника питания, первое 11 токовое зеркало, согласованное с первой 8 шиной источника питания, вход которого подключен к стоку третьего 4 входного полевого транзистора, а выход соединен со входом буферного усилителя 12 и первым 13 корректирующим конденсатором, второе 14 токовое зеркало, согласованное со второй 10 шиной источника питания, вход которого соединен со стоком четвертого 5 входного полевого транзистора, а выход подключен ко входу буферного усилителя 12, выход которого является выходом устройства 15.

Существенный недостаток известного ОУ состоит в том, что в режиме повторителя напряжения, когда выход устройства 15 связан с инвертирующим входом 3 (фиг. 2б) он имеет невысокую максимальную скорость нарастания выходного напряжения в режиме большого сигнала (SR). Это обусловлено малыми значениями токов перезаряда первого 13 корректирующего конденсатора ОУ, которые жестко связаны с током первого 7 и второго 9 токостабилизирующих двухполюсников. Эти токи не могут выбираться большими из-за их существенного влияния на токопотребление всей схемы ОУ.

Основная задача предполагаемого изобретения состоит в повышении SR без ухудшения энергетических параметров ОУ в статическом режиме, а также создании условий раздельного регулирования SR для переднего

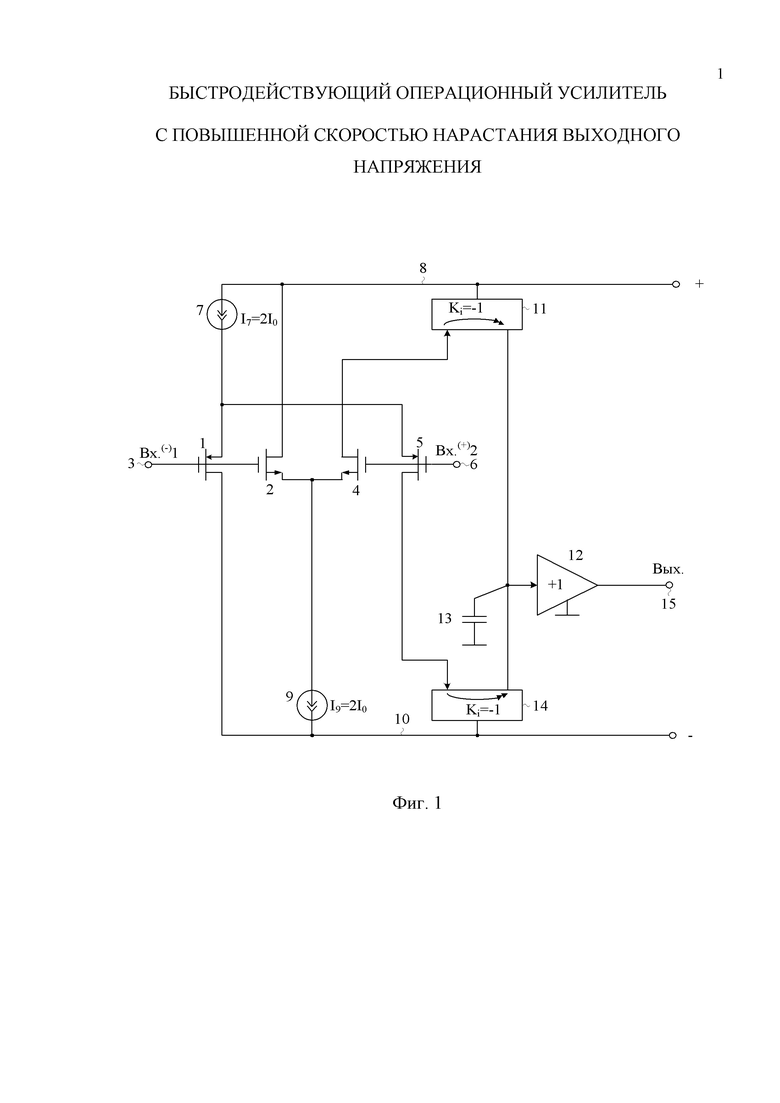

Поставленная задача достигается тем, что в операционном усилителе фиг.1, содержащем первый 1 и второй 2 входные полевые транзисторы разного типа проводимости, объединенные затворы которых подключены к инвертирующему входу 3 устройства, третий 4 и четвертый 5 входные полевые транзисторы разного типа проводимости, затворы которых объединены и подключены к неинвертирующему входу 6 устройства, первый 7 токостабилизирующий двухполюсник, включенный между первой 8 шиной источника питания и объеденными истоками первого 1 и четвертого 5 входных полевых транзисторов, сток второго 2 входного полевого транзистора связан с первой 8 шиной источника питания, второй 9 токостабилизирующий двухполюсник, включенный между второй 10 шиной источника питания и объеденными истоками второго 2 и третьего 4 входных полевых транзисторов, сток первого 1 входного полевого транзистора связан со второй 10 шиной источника питания, первое 11 токовое зеркало, согласованное с первой 8 шиной источника питания, вход которого подключен к стоку третьего 4 входного полевого транзистора, а выход соединен со входом буферного усилителя 12 и первым 13 корректирующим конденсатором, второе 14 токовое зеркало, согласованное со второй 10 шиной источника питания, вход которого соединен со стоком четвертого 5 входного полевого транзистора, а выход подключен ко входу буферного усилителя 12, выход которого является выходом устройства 15, предусмотрены новые элементы и связи – между объединенными истоками первого 1 и четвертого 5 входных полевых транзисторов и объединенными истоками второго 2 и третьего 4 входных полевых транзисторов последовательно включены второй 16 и третий 17 корректирующие конденсаторы, общий узел которых подключен к выходу устройства 15, через первый 18 дополнительный резистор.

На чертеже фиг. 1 показана схема ОУ-прототипа. На чертеже фиг. 2а представлена схема заявляемого устройства в соответствии с п. 1 формулы изобретения, а на чертеже фиг. 2б – типовая схема неинвертирующего включения заявляемого устройства фиг. 2а.

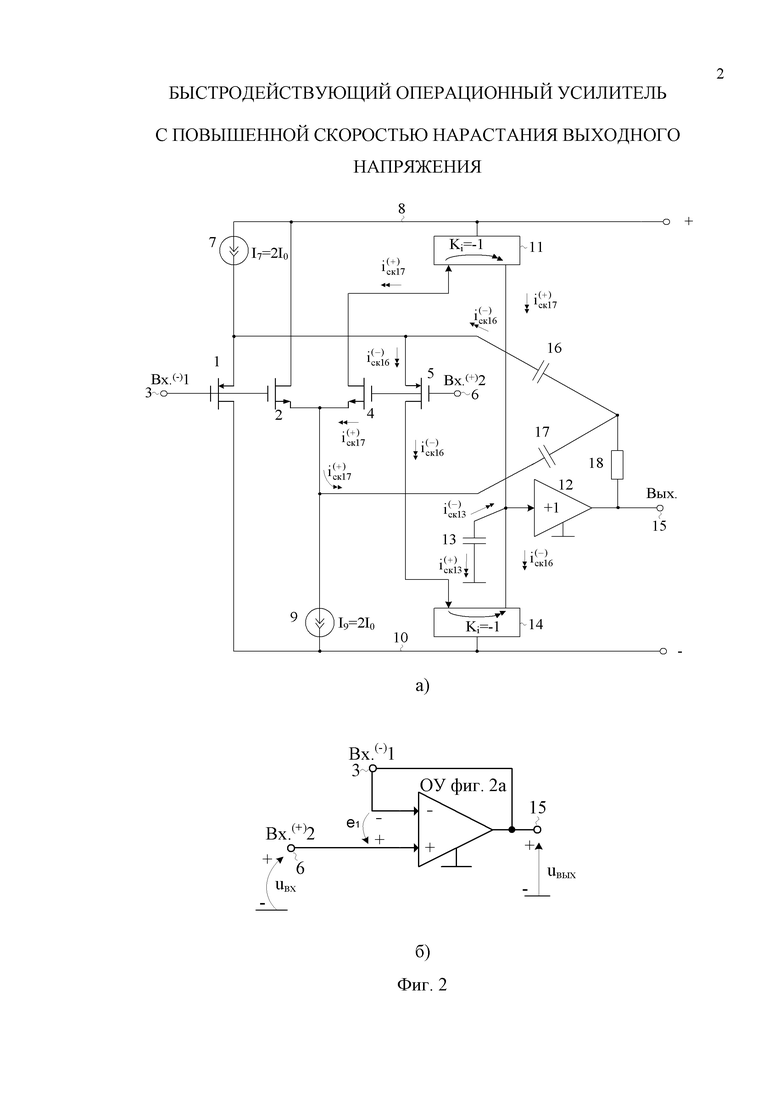

На чертеже фиг. 3 изображена схема заявляемого устройства в соответствии с п. 2 формулы изобретения. ОУ фиг. 3 имеет типовую схему включения фиг. 2б.

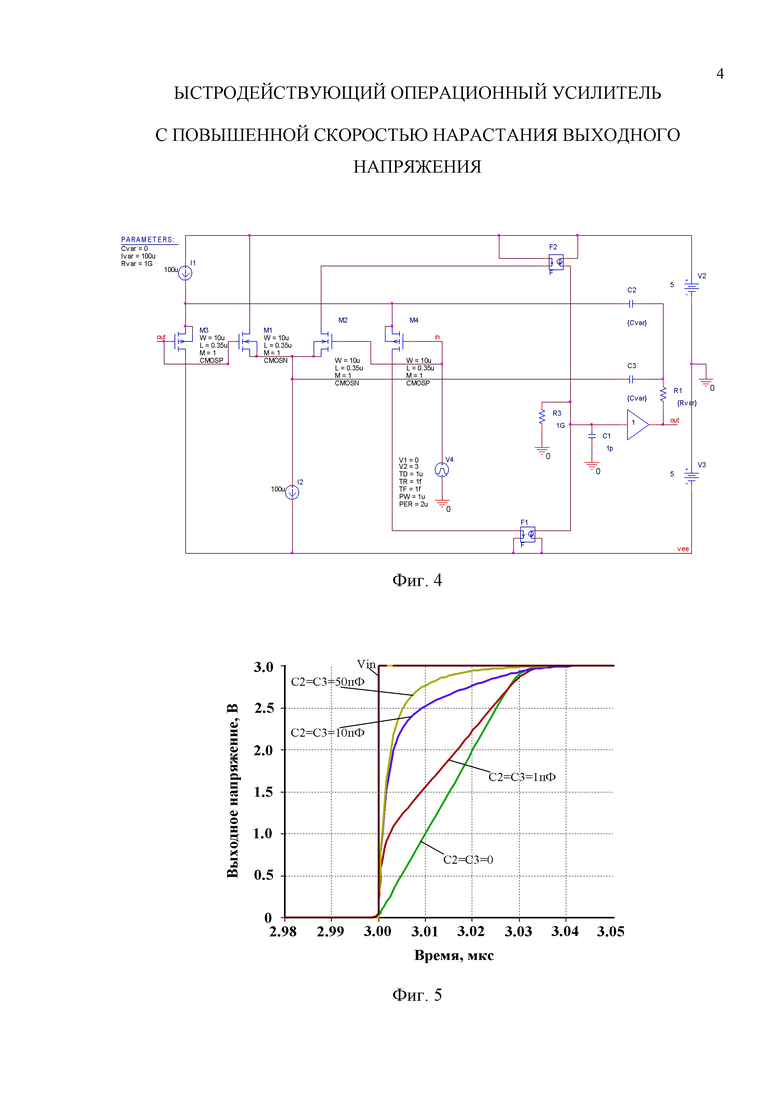

На чертеже фиг. 4 приведена схема заявляемого ОУ фиг. 2а при 100% отрицательной обратной связи (фиг. 2б) в среде PSpice на моделях SiGe интегральных полевых транзисторов техпроцесса TSMC 0.35 um при токах первого 7 и второго 9 токостабилизирующих двухполюсников I1(I7)=I2(I9)=100мкА, а также большом сопротивлении дополнительного резистора 18. При этом эквивалентное сопротивление R3, включенное параллельно корректирующему конденсатору С1, характеризующее выходные сопротивления токовых зеркал F1 и F2 и входное сопротивление буферного усилителя 12, соответствовало 1 ГОм.

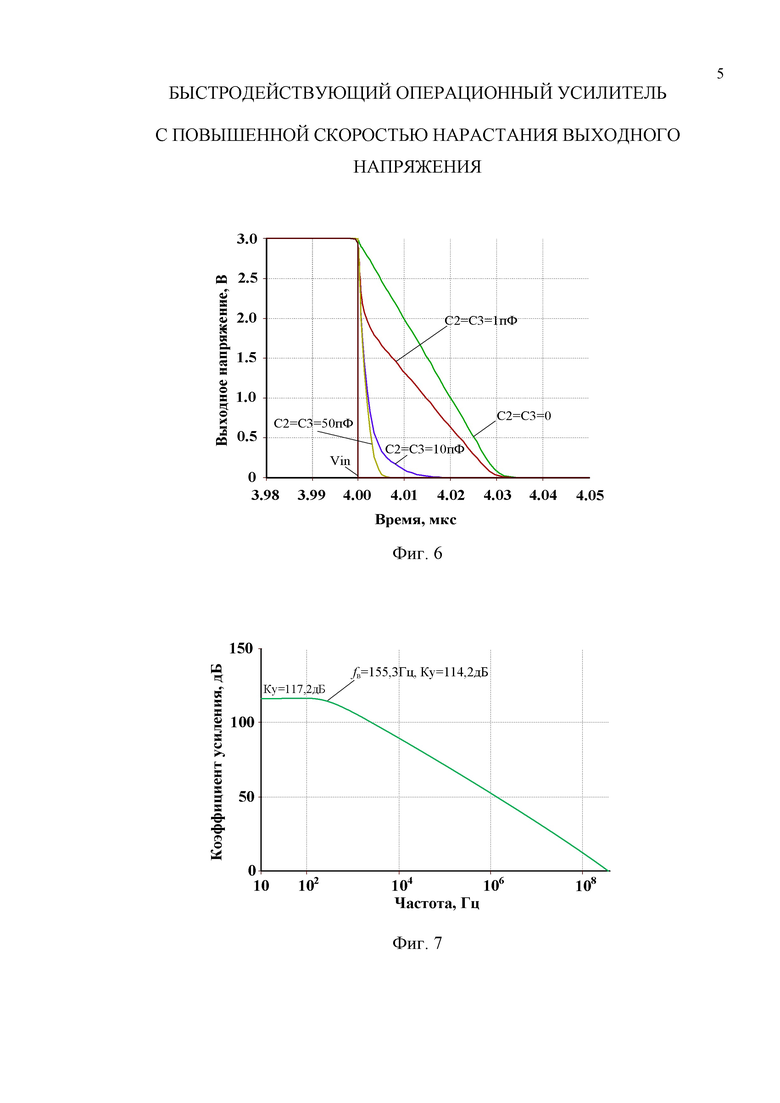

На чертеже фиг. 5 представлен передний фронт переходного процесса ОУ фиг. 4 при емкости первого 13 корректирующего конденсатора Сk1(С13)=1пФ, амплитуде входного напряжения Uвх(+)=3В и различных значениях емкостей второго 16 и третьего 17 корректирующих конденсаторов Сk2(С16)=Сk3(С17)=Сvar=0;1;10;50пФ при большом сопротивлении дополнительного резистора 18 и токах I1(I7)=I2(I9)=100мкА.

На чертеже фиг. 6 показан задний фронт переходного процесса ОУ фиг. 4 при емкости первого 13 корректирующего конденсатора Сk1(С13)=1пФ, амплитуде входного напряжения Uвх(+)=3В и различных значениях емкостей второго 16 и третьего 17 корректирующих конденсаторов Сk2(С16)=Сk3(С17)=Сvar=0;1;10;50пФ при большом сопротивлении дополнительного резистора 18 и токах I1(I7)=I2(I9)=100мкА.

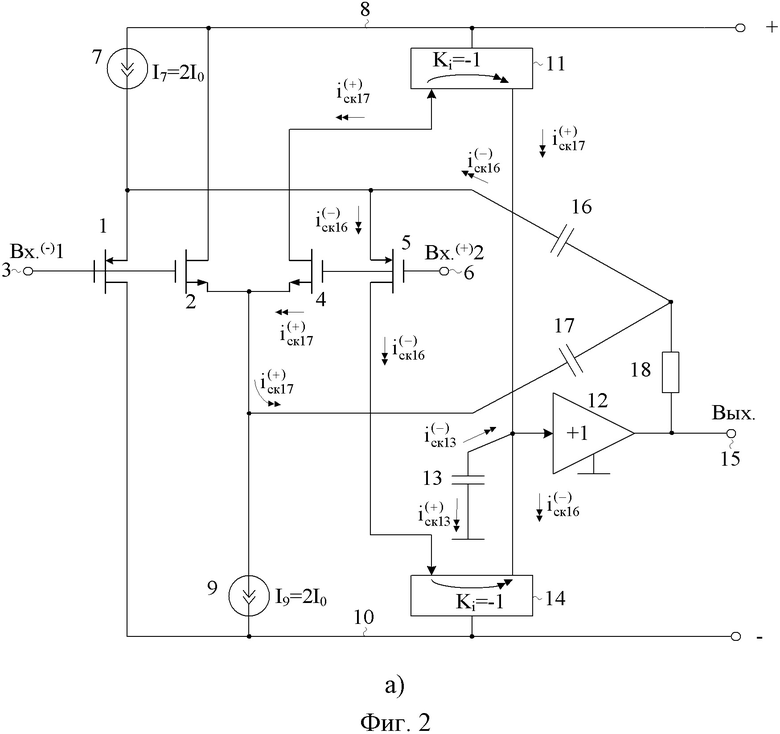

На чертеже фиг. 7 приведена амплитудно-частотная характеристика (АЧХ) разомкнутого ОУ фиг. 4 при емкости первого 13 корректирующего конденсатора Сk1(С13)=1пФ, при большом сопротивлении дополнительного резистора 18, токах I1(I7)=I2(I9)=100мкА и малых емкостях Сk2(С16)=Сk3(С17)=1фФ.

Быстродействующий операционный усилитель фиг. 2а содержит первый 1 и второй 2 входные полевые транзисторы разного типа проводимости, объединенные затворы которых подключены к инвертирующему входу 3 устройства, третий 4 и четвертый 5 входные полевые транзисторы разного типа проводимости, затворы которых объединены и подключены к неинвертирующему входу 6 устройства, первый 7 токостабилизирующий двухполюсник, включенный между первой 8 шиной источника питания и объеденными истоками первого 1 и четвертого 5 входных полевых транзисторов, сток второго 2 входного полевого транзистора связан с первой 8 шиной источника питания, второй 9 токостабилизирующий двухполюсник, включенный между второй 10 шиной источника питания и объеденными истоками второго 2 и третьего 4 входных полевых транзисторов, сток первого 1 входного полевого транзистора связан со второй 10 шиной источника питания, первое 11 токовое зеркало, согласованное с первой 8 шиной источника питания, вход которого подключен к стоку третьего 4 входного полевого транзистора, а выход соединен со входом буферного усилителя 12 и первым 13 корректирующим конденсатором, второе 14 токовое зеркало, согласованное со второй 10 шиной источника питания, вход которого соединен со стоком четвертого 5 входного полевого транзистора, а выход подключен ко входу буферного усилителя 12, выход которого является выходом устройства 15. В схему введены - между объединенными истоками первого 1 и четвертого 5 входных полевых транзисторов и объединенными истоками второго 2 и третьего 4 входных полевых транзисторов последовательно включены второй 16 и третий 17 корректирующие конденсаторы, общий узел которых подключен к выходу устройства 15, через первый 18 дополнительный резистор.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, последовательно со вторым 16 корректирующим конденсатором включен второй 19 дополнительный резистор, а последовательно с третьим 17 корректирующим конденсатором включен третий 20 дополнительный резистор.

Рассмотрим работу предлагаемого ОУ фиг. 2а при его неинвертирующем включении в соответствии со схемой фиг. 2б.

Статический режим схемы ОУ фиг. 2а устанавливается первым 7 и вторым 9 токостабилизирующими двухполюсниками. Первый 13 корректирующий конденсатор обеспечивает устойчивость ОУ при введении общей отрицательной обратной связи на его первый 3 инвертирующий вход (фиг. 2б).

При 100% отрицательной обратной связи схема фиг. 2б является неинвертирующим повторителем входного напряжения с

Если на неинвертирующий вход 6 ОУ фиг. 2а в схеме включения фиг. 2б поступает входной сигнал большой амплитуды, то это создаёт напряжение ошибки

В результате скорость перезаряда первого 13 корректирующего конденсатора существенно увеличивается, что приводит к значительному увеличению SR ОУ (см. фиг. 5, фиг. 6, табл. 1).

Таблица 1 – Взаимосвязь SR ОУ рис. 4 и емкостей Сk2(С16)=Сk3(С17)=Сvar=0..50пФ при Uвх(+)=3В, Сk1(С13)=1пФ, большом сопротивлении R18 и токах I1(I7)=I2(I9)=100мкА.

Сk2(С16)=Сk3(С17)=Сvar, пФ

Введение резисторов 19 и 20 обеспечивает (совместно с первым 18 дополнительным резистором) возможность выравнивания параметров

Таким образом, в сравнении с ОУ-прототипом предлагаемое устройство обладает существенными преимуществами по динамическим параметрам в режиме большого сигнала. При этом, данный положительный эффект обеспечивается за счет введения в схему двух корректирующих конденсаторов 16 и 17 сравнительно небольшой емкости и не требует увлечения тока потребления ОУ в статическом режиме.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US № 6.268.769, fig.3, 2001 г.

2. Патентная заявка US 2003/0206060, 2003 г.

3. Патент US 6.794.940, 2004 г.

4. Патентная заявка US 2004/0174216, 2004 г.

5. Патентная заявка US 2006/0125522, 2006 г.

6. Патент US 6.433.637, 2002 г.

7. Патентная заявка US 2007/0159248, 2007 г.

8. Патент US 5.714.906, 1995 г.

9. Патент US 7.907.011, 2011 г.

10. Патент US 6.100.762, 2000 г.

11. Патент US 5.909.146, 1999 г.

12. Патент ЕР 1150423, 2001 г.

13. Патент JP 2004/222104, 2004 г.

14. Патент US 6.801.087, 2004 г.

15. Патент US 5.917.378, 1999 г.

16. Патентная заявка US 2008/0074405, 2008 г.

17. Патентная заявка US 2009/0206930, 2009 г.

18. Патент US 6.356.153, 2002 г.

19. Патент US 5.621.357, 1997 г.

20. Патент US 6.970.043, 2005 г.

21. Патент US 6.731.169, 2004 г.

22. Патент US 5.070.306, fig. 3, 1991 г.

23. Патент US 2010/001797, 2001 г.

24. Патент US 5.610.547, fig. 34, 1997 г.

25. Патент US 6.972.623, fig. 4, fig. 6, 2005 г.

26. Патент US 2008/0238546, fig. 2, 2008 г.

27. Патент US 2008/0252374, 2008 г.

28. Патент US 7.567.124, 2009 г.

29. Патент US 7.586.373, 2009 г.

30. Патент US 2006/0215787, 2006 г.

31. Патент US 5.291.149, fig.4, 1994г.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2676014C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ИСТОКОВЫЙ ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2013 |

|

RU2536671C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2018 |

|

RU2684489C1 |

| ИЗМЕРИТЕЛЬНЫЙ УСИЛИТЕЛЬ С РЕЗОНАНСНОЙ АМПЛИТУДНО-ЧАСТОТНОЙ ХАРАКТЕРИСТИКОЙ | 2013 |

|

RU2523953C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

| УПРАВЛЯЕМЫЙ ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2013 |

|

RU2519035C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД CJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ТОКОВЫМ ВЫХОДОМ | 2019 |

|

RU2712411C1 |

Изобретение относится к области радиотехники. Технический результат: повышение максимальной скорости нарастания выходного напряжения и уменьшение времени установления переходного процесса. Для этого предложен быстродействующий операционный усилитель, содержащий первый (1) и второй (2) входные полевые транзисторы, инвертирующий вход (3) устройства, третий (4) и четвертый (5) входные полевые транзисторы, неинвертирующей вход (6) устройства, первый (7) токостабилизирующий двухполюсник, первая (8) шина источника питания, второй (9) токостабилизирующий двухполюсник, вторая (10) шина источника питания, первое (11) токовое зеркало, буферный усилитель (12), первый (13) корректирующий конденсатор, второе (14) токовое зеркало, выход устройства (15). Между объединенными истоками первого (1) и четвертого (5) входных полевых транзисторов и объединенными истоками второго (2) и третьего (4) входных полевых транзисторов последовательно включены второй (16) и третий (17) корректирующие конденсаторы, общий узел которых подключен к выходу устройства (15) через дополнительный резистор (18). 1 з.п. ф-лы, 8 ил.

1. Быстродействующий операционный усилитель, содержащий первый (1) и второй (2) входные полевые транзисторы разного типа проводимости, объединенные затворы которых подключены к инвертирующему входу (3) устройства, третий (4) и четвертый (5) входные полевые транзисторы разного типа проводимости, затворы которых объединены и подключены к неинвертирующему входу (6) устройства, первый (7) токостабилизирующий двухполюсник, включенный между первой (8) шиной источника питания и объеденными истоками первого (1) и четвертого (5) входных полевых транзисторов, сток второго (2) входного полевого транзистора связан с первой (8) шиной источника питания, второй (9) токостабилизирующий двухполюсник, включенный между второй (10) шиной источника питания и объеденными истоками второго (2) и третьего (4) входных полевых транзисторов, сток первого (1) входного полевого транзистора связан со второй (10) шиной источника питания, первое (11) токовое зеркало, согласованное с первой (8) шиной источника питания, вход которого подключен к стоку третьего (4) входного полевого транзистора, а выход соединен со входом буферного усилителя (12) и первым (13) корректирующим конденсатором, второе (14) токовое зеркало, согласованное со второй (10) шиной источника питания, вход которого соединен со стоком четвертого (5) входного полевого транзистора, а выход подключен ко входу буферного усилителя (12), выход которого является выходом устройства (15), отличающийся тем, что между объединенными истоками первого (1) и четвертого (5) входных полевых транзисторов и объединенными истоками второго (2) и третьего (4) входных полевых транзисторов последовательно включены второй (16) и третий (17) корректирующие конденсаторы, общий узел которых подключен к выходу устройства (15) через первый (18) дополнительный резистор.

2. Быстродействующий операционный усилитель по п.1, отличающийся тем, что последовательно со вторым (16) корректирующим конденсатором включен второй (19) дополнительный резистор, а последовательно с третьим (17) корректирующим конденсатором включен третий (20) дополнительный резистор.

| US 6268769 B1, 31.07.2001 | |||

| МНОГОКАНАЛЬНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2626667C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩЕЙ ЦЕПЬЮ КОРРЕКЦИИ | 2018 |

|

RU2669075C1 |

| US 4405900 A1, 20.09.1983. | |||

Авторы

Даты

2019-03-26—Публикация

2018-06-26—Подача