Изобретение относится к вычислительной технике и предназначено для адаптивной компенсации доплеровских сдвигов фазы пассивных помех; может быть использовано в адаптивных устройствах режектирования многочастотных пассивных помех.

Известен фильтр с адаптивной компенсацией доплеровской фазы пассивных помех, содержащий блоки задержки, блок комплексного сопряжения, блоки комплексного умножения, блок оценивания фазы и функциональные преобразователи [1]. Однако это устройство имеет низкую точность измерения и компенсации текущего значения доплеровской фазы пассивных помех.

Известен также измеритель доплеровской фазы пассивных помех [2], содержащий блок оценивания фазы, блок комплексного умножения, блок задержки, блок усреднения и вычислитель фазы. Однако данное устройство обладает низкой точностью измерения текущего значения доплеровской фазы пассивных помех.

Наиболее близким к изобретению является выбранное в качестве прототипа устройство с адаптивной компенсацией доплеровской фазы пассивных помех [3], содержащее блок оценивания фазы, блок задерживания, первый и второй блоки комплексного умножения, блок комплексного сопряжения и блок задержки, при этом входы блока оценивания фазы через блок задерживания соединены с первыми входами первого блока комплексного умножения, вторые входы которого соединены с выходами блока комплексного сопряжения, выходы второго блока комплексного умножения соединены с объединенными входами блока комплексного сопряжения и блока задержки, выходы блока задержки соединены с первыми входами второго блока комплексного умножения. Однако данное устройство имеет низкую точность компенсации текущего значения доплеровской фазы пассивных помех.

Задачей, решаемой в изобретении, является повышение точности адаптивной компенсации текущего значения доплеровской фазы многочастотных пассивных помех за счет применения совместной обработки частотных компонент многочастотных пассивных помех.

Для решения поставленной задачи в адаптивный компенсатор фазы пассивных помех, содержащий блок оценивания фазы, блок задерживания, первый и второй блоки комплексного умножения, блок комплексного сопряжения, блок задержки и синхрогенератор, введены первый и второй умножители, первый, второй, третий и четвертый функциональные преобразователи, первый и второй блоки памяти, комплексный сумматор, дополнительный вычислитель фазы, дополнительный блок оценивания фазы, первый и второй дополнительные блоки комплексного умножения, дополнительный блок комплексного сопряжения, дополнительный блок задержки и дополнительный блок задерживания.

Дополнительные блоки, введенные в предлагаемое устройство, являются известными. Так, соединенные вместе в блоке оценивания фазы блок задержки, блок комплексного сопряжения, блок комплексного умножения, блок усреднения и вычислитель фазы позволяют выделить доплеровский набег фазы за интервал между соседними отсчетами пассивной помехи. Однако неизвестно совместное применение первого и второго умножителей, первого, второго, третьего и четвертого функциональных преобразователей, первого и второго блоков памяти, комплексного сумматора, дополнительного вычислителя фазы, дополнительного блока оценивания фазы, дополнительных блоков комплексного умножения, дополнительного блока задержки и дополнительного блока задерживания. Новыми являются связи первого умножителя с блоком оценивания фазы, первым функциональным преобразователем и первым блоком памяти, дополнительного блока оценивания фазы с третьим функциональным преобразователем, первого и третьего функциональных преобразователей с комплексным сумматором, комплексного сумматора с дополнительным вычислителем фазы, дополнительного вычислителя фазы со вторым умножителем и четвертым функциональным преобразователем, второго и четвертого функциональных преобразователей соответственно со вторым блоком комплексного умножения и первым дополнительным блоком комплексного умножения, что обеспечивает повышение точности измерения и компенсации текущего значения доплеровской фазы многочастотных пассивных помех. Связи между синхрогенератором и всеми блоками адаптивного компенсатора фазы пассивных помех обеспечивают согласованную обработку компонент многочастотных пассивных помех.

Сравнение с техническими характеристиками, известными из опубликованных источников информации, показывает, что заявляемое решение обладает новизной и имеет изобретательский уровень.

Заявляемое решение носит технический характер, осуществимо, воспроизводимо и, следовательно, является промышленно применимым.

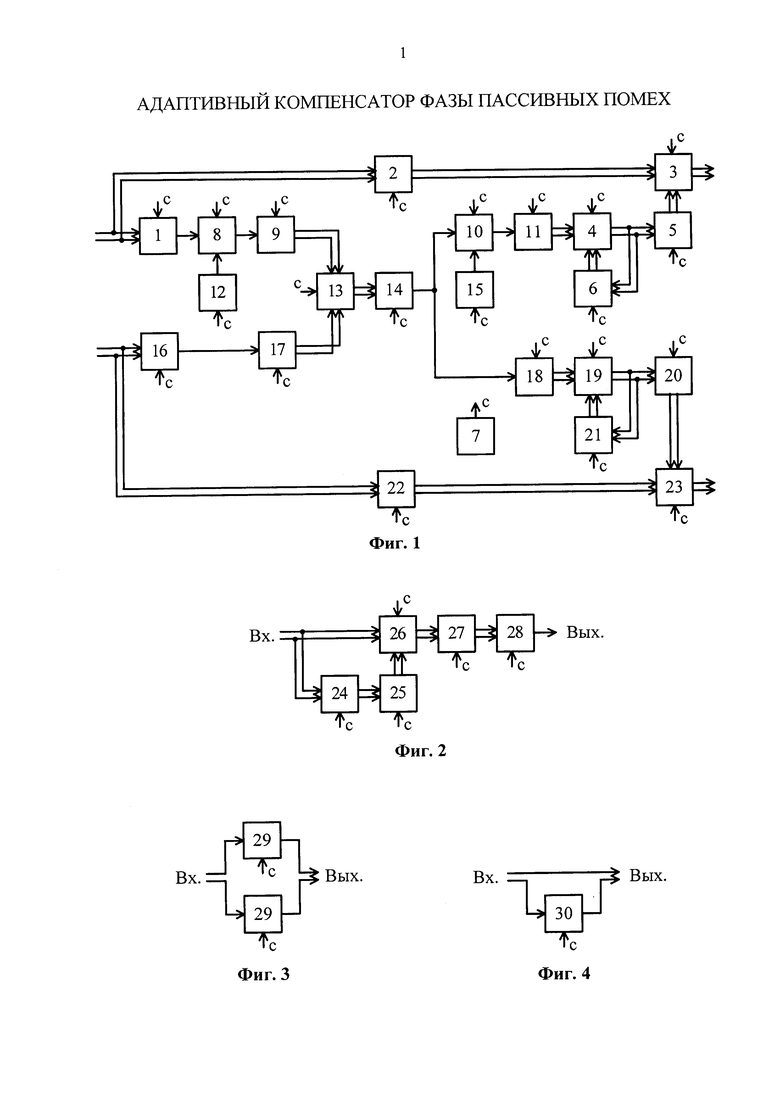

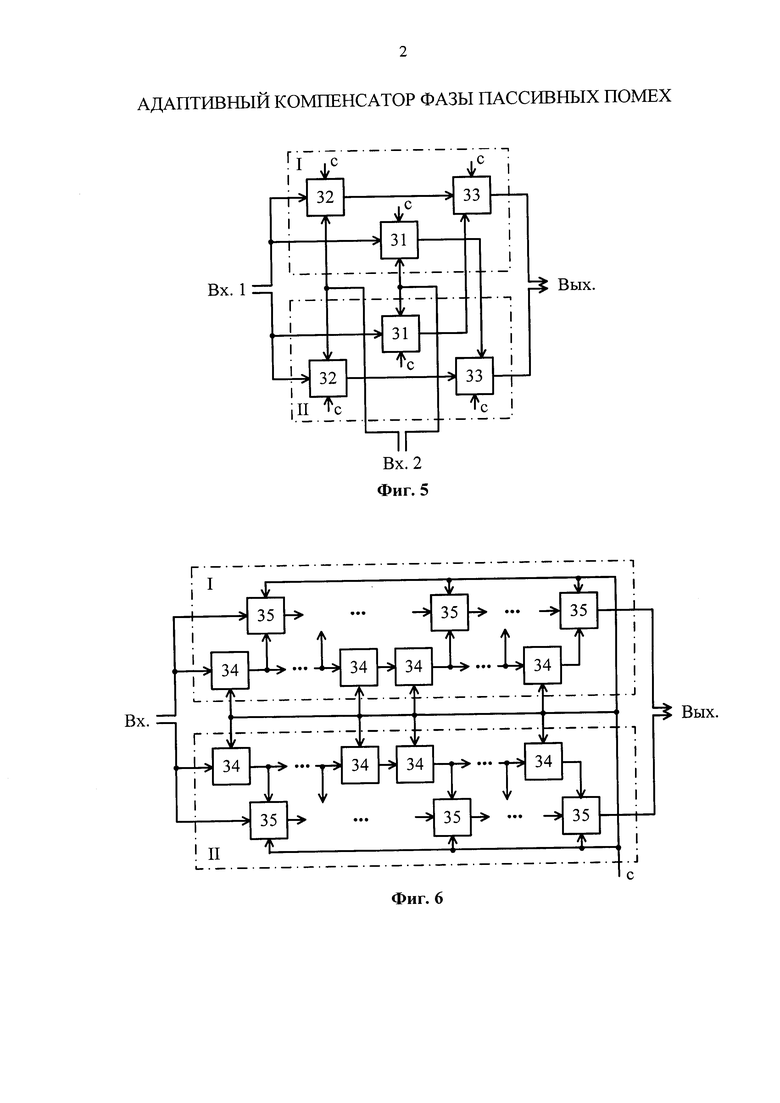

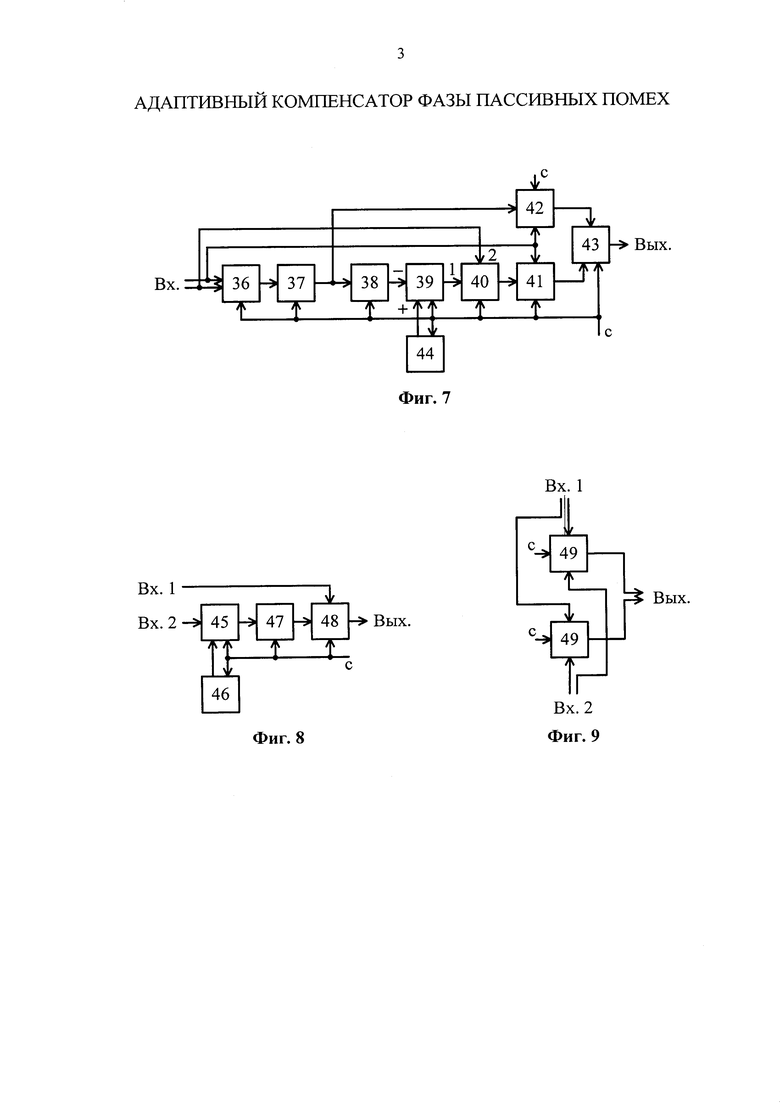

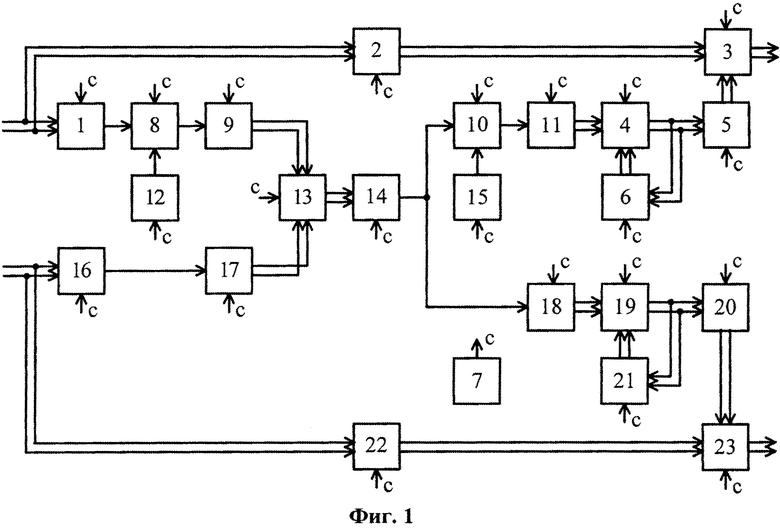

На фиг. 1 представлена структурная электрическая схема адаптивного компенсатора фазы пассивных помех; на фиг. 2 - блока оценивания фазы; на фиг. 3 - блока задерживания и блока задержки; на фиг. 4 - блока комплексного сопряжения; на фиг. 5 - блока комплексного умножения; на фиг. 6 - блока усреднения; на фиг. 7 - вычислителя фазы; на фиг. 8 - блока присвоения знака; на фиг. 9 - комплексного сумматора.

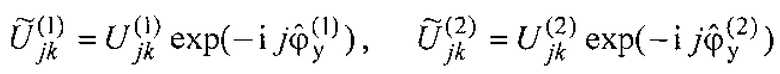

Адаптивный компенсатор фазы пассивных помех (фиг. 1) содержит блок 1 оценивания фазы, блок 2 задерживания, первый блок 3 комплексного умножения, второй блок 4 комплексного умножения, блок 5 комплексного сопряжения, блок 6 задержки, синхрогенератор 7, первый умножитель 8, первый функциональный преобразователь 9, второй умножитель 10, второй функциональный преобразователь 11, первый блок памяти 12, комплексный сумматор 13, дополнительный вычислитель фазы 14, второй блок памяти 15, дополнительный блок оценивания фазы 16, третий 17 и четвертый 18 функциональные преобразователи, первый дополнительный блок 19 комплексного умножения, дополнительный блок 20 комплексного сопряжения, дополнительный блок 21 задержки, дополнительный блок 22 задерживания и второй дополнительный блок 23 комплексного умножения, при этом входы блока 1 оценивания фазы через блок 2 задерживания соединены с первыми входами первого блока 3 комплексного умножения, вторые входы которого соединены с выходами блока 5 комплексного сопряжения, выходы второго блока 4 комплексного умножения соединены с объединенными входами блока 5 комплексного сопряжения и блока 6 задержки, выходы блока 6 задержки соединены с первыми входами второго блока 4 комплексного умножения, выход блока 1 оценивания фазы соединен с первым входом первого умножителя 8, второй вход которого соединен с выходом первого блока 12 памяти, выход первого умножителя 8 соединен с входом первого функционального преобразователя 9, выходы которого соединены с первыми входами комплексного сумматора 13, выходы комплексного сумматора 13 соединены с входами дополнительного вычислителя фазы 14, выход которого соединен с объединенными первым входом второго умножителя 10 и входом четвертого функционального преобразователя 18, второй вход второго умножителя 10 соединен с выходом второго блока 15 памяти, выход второго умножителя 10 соединен с входом второго функционального преобразователя 11, выходы которого соединены со вторыми входами второго блока 4 комплексного умножения, выход дополнительного блока 16 оценивания фазы соединен с входом третьего функционального преобразователя 17, выходы которого соединены со вторыми входами комплексного сумматора 13, выходы первого дополнительного блока 19 комплексного умножения соединены с объединенными входами дополнительного блока 20 комплексного сопряжения и дополнительного блока 21 задержки, выходы дополнительного блока 21 задержки соединены с первыми входами первого дополнительного блока 19 комплексного умножения, вторые входы которого соединены с выходами четвертого функционального преобразователя 18, входы дополнительного блока 16 оценивания фазы через дополнительный блок 22 задерживания соединены с первыми входами второго дополнительного блока 23 комплексного умножения, вторые входы которого соединены с выходами дополнительного блока 20 комплексного сопряжения, выход синхрогенератора соединен с синхровходами блока 1 оценивания фазы, блока 2 задерживания, первого 3 и второго 4 блоков комплексного умножения, блока 5 комплексного сопряжения, блока 6 задержки, первого 8 и второго 10 умножителей, первого 9, второго 11, третьего 17 и четвертого 18 функциональных преобразователей, первого 12 и второго 15 блоков памяти, комплексного сумматора 13, дополнительного вычислителя фазы 14, дополнительного блока 16 оценивания фазы, первого 19 и второго 23 дополнительных блоков комплексного умножения, дополнительного блока 20 комплексного сопряжения, дополнительного блока 21 задержки и дополнительного блока 22 задерживания, причем первыми и вторыми входами адаптивного компенсатора фазы пассивных помех являются соответственно входы блока 1 оценивания фазы и дополнительного блока 16 оценивания фазы, а первыми и вторыми выходами - соответственно выходы первого блока 3 комплексного умножения и второго дополнительного блока 23 комплексного умножения.

Блок 1 оценивания фазы и дополнительный блок 16 оценивания фазы (фиг. 2) содержат последовательно соединенные блок 24 задержки, блок 25 комплексного сопряжения, блок 26 комплексного умножения, блок 27 усреднения и вычислитель фазы 28, вторые входы блока 26 комплексного умножения объединены с входами блока 24 задержки и являются входами блоков оценивания фазы, выходами которых являются выходы вычислителя фазы 28.

Блок 2 задерживания и дополнительный блок 22 задерживания (фиг. 3) содержат две цифровые линии задерживания 29 на временнóй интервал tз, входом блоков задерживания являются входы цифровых линий задерживания 29, выходы которых являются выходами блоков задерживания.

Блоки 6 и 24 задержки и дополнительный блок 21 задержки выполняются аналогично блокам 2 и 22 задерживания (фиг. 3) и содержат две цифровые линии задержки 29 на временной интервал T, входом блоков задержки являются входы цифровых линий задержки 29, выходы которых являются выходами блоков задержки.

Блоки 5 и 25 комплексного сопряжения и дополнительный блок 20 комплексного сопряжения (фиг. 4) содержат инвертор 30, первый вход блоков комплексного сопряжения является его первым выходом, вторым входом является вход инвертора 30, выход которого является вторым выходом блоков комплексного сопряжения.

Блоки 3 и 4 комплексного умножения и дополнительные блоки 19 и 23 комплексного умножения (фиг. 5) содержат два канала (I, II), каждый из которых включает первый перемножитель 31, последовательно включенные второй перемножитель 32 и сумматор 33, выход первого перемножителя 31 одного канала соединен со вторым входом сумматора 33 другого канала, а первыми и вторыми входами блока комплексного умножения соответственно являются объединенные между собой первые входы первого и второго перемножителей 31 и 32 каждого из каналов, объединенные вторые входы вторых перемножителей 32 и объединенные вторые входы первых перемножителей 31, а выходами блока комплексного умножения являются выходы сумматоров 33 каждого из каналов.

Блок 27 усреднения (фиг. 6) содержит два канала (I, II), каждый из которых состоит из n последовательно включенных цифровых элементов 34 задержки на интервал временнóй дискретизации tд и n-1 последовательно включенных сумматоров 35, входами блока усреднения являются объединенные входы первого элемента задержки 34 и первого сумматора 35 каждого канала (I, II), выход k-го (k=1…n) элемента задержки 34, кроме (n/2)-го, соединен со вторым входом k-го (k=1…n-1) сумматора 35 каждого канала (I, II), выходами блока усреднения служат выходы (n-1)-x сумматоров.

Вычислитель фазы 28 и дополнительный вычислитель фазы 14 (фиг. 7) состоят из последовательно включенных делителя 36, функционального преобразователя 37, модульного блока 38, сумматора 39, блока 40 присвоения знака и первого ключа 41, выход функционального преобразователя 37 соединен с входом второго ключа 42, второй вход сумматора 39 соединен с выходом блока 44 памяти, управляющие входы первого и второго ключей 41 и 42 соединены с входом делителя 36, соответствующим входу действительной части комплексного числа, второй вход блока 40 присвоения знака соединен с входом делителя 36, соответствующим входу мнимой части комплексного числа, выходы первого и второго ключей 41 и 42 соединены с входами сумматора 43, выход которого является выходом вычислителя фазы, входами вычислителя фазы являются входы делителя 36.

Блок 40 присвоения знака (фиг. 8) содержит блоки 45 и 48 умножения, блок 46 памяти и ограничитель 47, причем второй вход блока присвоения знака является первым входом блока 45 умножения, второй вход которого соединен с выходом блока 46 памяти, выход блока 45 умножения соединен с входом ограничителя 47, выход которого соединен с первым входом блока 48 умножения, второй вход которого является первым входом блока присвоения знака, выходом блока присвоения знака служит выход блока 48 умножения.

Комплексный сумматор 13 (фиг. 9) содержит два сумматора 49, первые входы которых являются первыми входами комплексного сумматора, а вторые входы - вторыми входами комплексного сумматора, выходы сумматоров 49 являются выходами комплексного сумматора.

Адаптивный компенсатор фазы пассивных помех работает следующим образом.

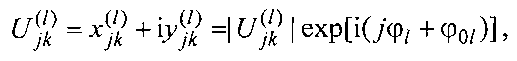

Два частотных компонента многочастотной пассивной помехи, значительно превышающих сигнал от цели, раздельно поступают на входы приемников каждого частотного канала, в которых усиливаются, в квадратурных фазовых детекторах переносятся на видеочастоту, а затем подвергаются аналого-цифровому преобразованию (соответствующие блоки на фиг. 1 не показаны). На первые и вторые входы адаптивного компенсатора фазы пассивных помех в каждом элементе разрешения по дальности каждого периода повторения поступают цифровые отсчеты комплексных огибающих соответствующих частотных компонент пассивной помехи

где  ,

,  - цифровые коды действительной и мнимой частей отсчетов

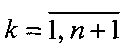

- цифровые коды действительной и мнимой частей отсчетов  ; j и k - текущие номера соответственно периода повторения и элемента разрешения по дальности, причем

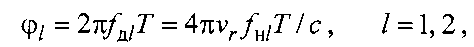

; j и k - текущие номера соответственно периода повторения и элемента разрешения по дальности, причем  ; l - номер частотного компонента, причем l=1, 2; φ0l - начальная фаза l-го частотного компонента; φl - доплеровский сдвиг фазы 1-го частотного компонента помехи, равный

; l - номер частотного компонента, причем l=1, 2; φ0l - начальная фаза l-го частотного компонента; φl - доплеровский сдвиг фазы 1-го частотного компонента помехи, равный

где fдl=2vrfн1/с - доплеровская частота помехи; Т - период повторения зондирующих импульсов; vr - радиальная скорость источника мешающих отражений (пассивной помехи); fнl - несущая частота l-го частотного компонента, причем fн2=rfн1, r<1; с - скорость распространения радиоволн.

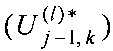

В адаптивном компенсаторе фазы пассивных помех (фиг. 1) отсчеты  и

и  поступают соответственно на входы блока 1 оценивания фазы и дополнительного блока 16 оценивания фазы (фиг. 2), где в блоках 24 задержки (фиг. 3) задерживаются на период повторения Т. После этого в блоках 25 комплексного сопряжения (фиг. 4) путем инвертирования с помощью инвертора 30 знаков мнимых проекций осуществляется комплексное сопряжение задержанных отсчетов

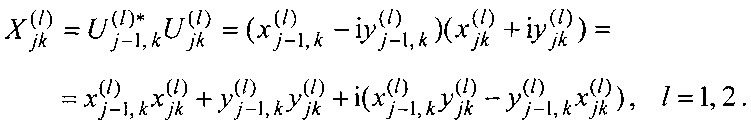

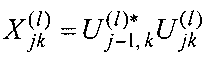

поступают соответственно на входы блока 1 оценивания фазы и дополнительного блока 16 оценивания фазы (фиг. 2), где в блоках 24 задержки (фиг. 3) задерживаются на период повторения Т. После этого в блоках 25 комплексного сопряжения (фиг. 4) путем инвертирования с помощью инвертора 30 знаков мнимых проекций осуществляется комплексное сопряжение задержанных отсчетов  . Далее в блоках 26 комплексного умножения (фиг. 5) в каждом элементе разрешения по дальности реализуется попарное умножение отсчетов в соответствии с алгоритмом

. Далее в блоках 26 комплексного умножения (фиг. 5) в каждом элементе разрешения по дальности реализуется попарное умножение отсчетов в соответствии с алгоритмом

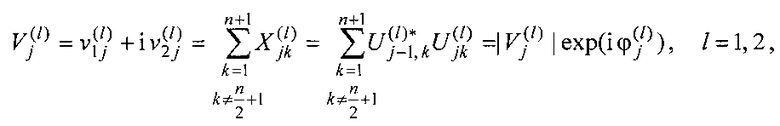

С выходов блоков 26 комплексного умножения полученные произведения  поступают в блоки 27 усреднения (фиг. 6), осуществляющие с помощью элементов 34 задержки и сумматоров 35 скользящее вдоль дальности в каждом периоде повторения суммирование величин

поступают в блоки 27 усреднения (фиг. 6), осуществляющие с помощью элементов 34 задержки и сумматоров 35 скользящее вдоль дальности в каждом периоде повторения суммирование величин  с n+1 смежных элементов разрешения по дальности временного строба, кроме элемента с номером n/2+1, для чего выходные величины элемента 34 задержки с номером n/2 поступают только на последующий элемент 34 задержки (фиг. 6). При этом на выходах блоков 27 усреднения образуются величины

с n+1 смежных элементов разрешения по дальности временного строба, кроме элемента с номером n/2+1, для чего выходные величины элемента 34 задержки с номером n/2 поступают только на последующий элемент 34 задержки (фиг. 6). При этом на выходах блоков 27 усреднения образуются величины

аргументами которых являются межпериодные доплеровские сдвиги фазы помехи  в j-м периоде повторения l-го частотного компонента (l=1, 2).

в j-м периоде повторения l-го частотного компонента (l=1, 2).

Величины  и

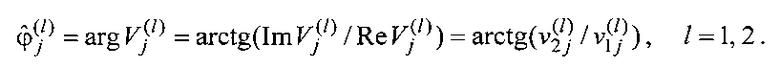

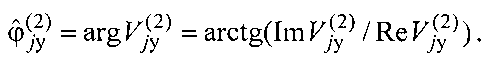

и  в блоках 1 и 16 поступают на соответствующие входы вычислителей фазы 28 (фиг. 7), где на основе блоков 36 деления и арктангенсных функциональных преобразователей 37 вычисляются оценки

в блоках 1 и 16 поступают на соответствующие входы вычислителей фазы 28 (фиг. 7), где на основе блоков 36 деления и арктангенсных функциональных преобразователей 37 вычисляются оценки

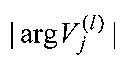

Последующие преобразования оценок  зависят от знака величины

зависят от знака величины  . При

. При  открыт второй ключ 42, и оценка

открыт второй ключ 42, и оценка  через сумматор 43 непосредственно поступает на выход вычислителя фазы 28. При

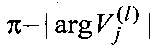

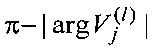

через сумматор 43 непосредственно поступает на выход вычислителя фазы 28. При  открыт первый ключ 41, а второй ключ 42 закрыт. При этом в модульном блоке 38 образуется

открыт первый ключ 41, а второй ключ 42 закрыт. При этом в модульном блоке 38 образуется  , вычитаемый в сумматоре 39 из величины %, поступающей от блока 44 памяти. Полученной разности

, вычитаемый в сумматоре 39 из величины %, поступающей от блока 44 памяти. Полученной разности  в блоке 40 присваивается знак величины

в блоке 40 присваивается знак величины  .

.

Блок 40 присвоения знака (фиг. 8) работает следующим образом. На второй вход блока 40 присвоения знака поступает величина  , где в блоке 45 умножения производится ее умножение на постоянный множитель из блока 46 памяти с целью масштабирования и дальнейшего ограничения в ограничителе 47 по уровню ±1. Таким образом, после ограничения величина на выходе ограничителя 47 имеет смысл знака величины

, где в блоке 45 умножения производится ее умножение на постоянный множитель из блока 46 памяти с целью масштабирования и дальнейшего ограничения в ограничителе 47 по уровню ±1. Таким образом, после ограничения величина на выходе ограничителя 47 имеет смысл знака величины  , который, поступая на первый вход блока 48 умножения, присваивается разности

, который, поступая на первый вход блока 48 умножения, присваивается разности  , поступающей с выхода сумматора 39 на первый вход блока 40 присвоения знака, т.е. на второй вход блока 48 умножения.

, поступающей с выхода сумматора 39 на первый вход блока 40 присвоения знака, т.е. на второй вход блока 48 умножения.

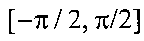

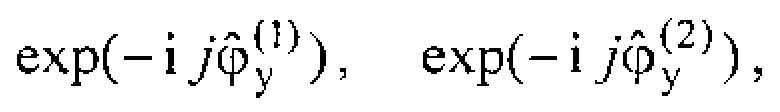

Рассмотренные операции позволяют в вычислителе фазы 28 сначала найти оценку доплеровского сдвига фазы помехи, находящуюся в интервале  , а затем при помощи последующих логических преобразований в блоках 38, 39 и 40 расширить пределы ее однозначного измерения до интервала

, а затем при помощи последующих логических преобразований в блоках 38, 39 и 40 расширить пределы ее однозначного измерения до интервала  в соответствии с алгоритмом

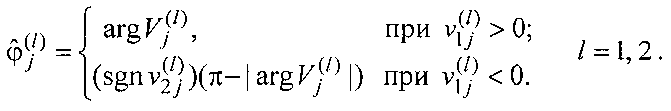

в соответствии с алгоритмом

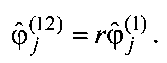

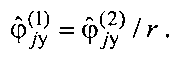

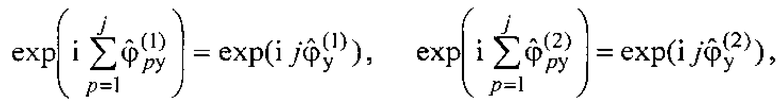

Первый умножитель 8 (фиг. 1) осуществляет умножение найденной в блоке 1 оценивания фазы l-го частотного канала оценки  на коэффициент r, хранящийся в первом блоке 12 памяти, что приводит к получению пересчитанной по отношению ко 2-му частотному каналу оценки

на коэффициент r, хранящийся в первом блоке 12 памяти, что приводит к получению пересчитанной по отношению ко 2-му частотному каналу оценки

Данная пересчитанная оценка  и найденная в дополнительном блоке 16 оценивания фазы 2-го частотного канала оценка

и найденная в дополнительном блоке 16 оценивания фазы 2-го частотного канала оценка  подвергаются межканальному усреднению. Так как непосредственное усреднение оценок

подвергаются межканальному усреднению. Так как непосредственное усреднение оценок  и

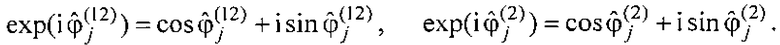

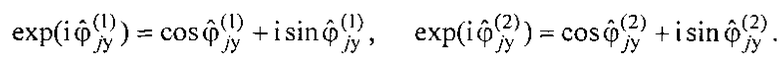

и  вследствие цикличности фазовых сдвигов приводит к существенным ошибкам, то усреднению подлежат тригонометрические функции этих оценок. Для этого в первом 9 и третьем 17 косинусно-синусных функциональных преобразователях определяются соответственно величины

вследствие цикличности фазовых сдвигов приводит к существенным ошибкам, то усреднению подлежат тригонометрические функции этих оценок. Для этого в первом 9 и третьем 17 косинусно-синусных функциональных преобразователях определяются соответственно величины

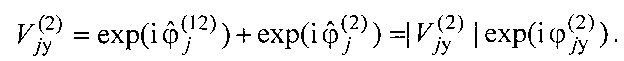

Межканальное усреднение осуществляется в комплексном сумматоре 13 (фиг. 9) путем раздельного суммирования действительных и мнимых проекций входных величин, приводящего к вычислению выходной величины

В дополнительном вычислителе фазы 14 (фиг. 7) определяется усредненная оценка для 2-го частотного канала:

Во втором умножителе 10 данная оценка умножается на хранящийся во втором блоке 15 памяти коэффициент 1/r, что приводит к получению усредненной оценки для 1-го частотного канала:

Во втором 11 и четвертом 18 косинусно-синусных функциональных преобразователях определяются соответственно величины

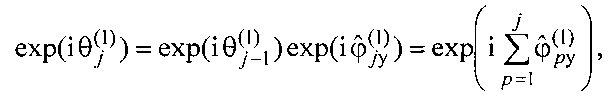

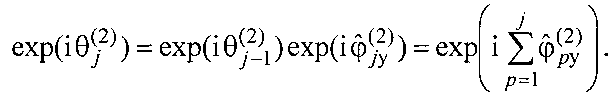

Второй блок 4 комплексного умножения совместно с блоком 6 задержки и первый дополнительный блок 19 комплексного умножения совместно с дополнительным блоком 21 задержки в каждом элементе разрешения по дальности осуществляют рекуррентное накопление оценок межпериодного доплеровского сдвига фазы помехи соответственно для 1-го и 2-го частотных каналов:

Ввиду однородности помехи по доплеровской скорости в пределах каждого элемента разрешения по дальности и равноточности оценок  и

и

что соответствует с точностью до начальной фазы текущей фазе помехи.

В блоке 5 комплексного сопряжения и в дополнительном блоке 20 комплексного сопряжения с помощью инвертора 30 знаков мнимых проекций происходит инвертирование знака текущей фазы, приводя к величинам

что позволяет в первом блоке 3 комплексного умножения и втором дополнительном блоке 23 комплексного умножения путем двумерного поворота поступающих в каждом частотном канале отсчетов  и

и  в соответствии с выражениями

в соответствии с выражениями

,

,

скомпенсировать доплеровские сдвиги фазы помехи.

Задерживание исходных отсчетов  и

и  на временной интервал tз=ntд/2+tв (где fд - интервал временной дискретизации, tв - интервал задерживания при вычислениях), реализуемое в блоке 2 задерживания и в дополнительном блоке 22 задерживания, обеспечивает временное совмещение компенсации с исключенным из обучающей выборки средним элементом с номером n/2+1 в стробе скользящего суммирования, реализуемого блоком 27 усреднения. Тогда в случае сигнала, соизмеримого по величине с помехой, или разрывной помехи при последующем режектировании отсчетов помехи с элемента разрешения, содержащего сигнал, исключается возможность ослабления или подавления сигнала за счет его влияния на используемые оценки.

на временной интервал tз=ntд/2+tв (где fд - интервал временной дискретизации, tв - интервал задерживания при вычислениях), реализуемое в блоке 2 задерживания и в дополнительном блоке 22 задерживания, обеспечивает временное совмещение компенсации с исключенным из обучающей выборки средним элементом с номером n/2+1 в стробе скользящего суммирования, реализуемого блоком 27 усреднения. Тогда в случае сигнала, соизмеримого по величине с помехой, или разрывной помехи при последующем режектировании отсчетов помехи с элемента разрешения, содержащего сигнал, исключается возможность ослабления или подавления сигнала за счет его влияния на используемые оценки.

Синхронизация адаптивного компенсатора фазы пассивных помех осуществляется подачей на все блоки заявляемого устройства последовательности синхронизирующих импульсов, вырабатываемых синхронизатором 7 (фиг. 1) с периодом повторения, равным интервалу временной дискретизации tд, выбираемому из условия требуемой разрешающей способности по дальности.

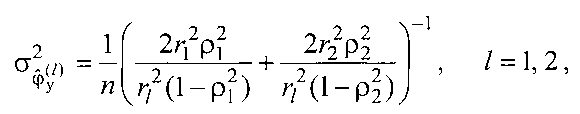

Достижение технического результата объясняется следующим образом. Погрешность усредненной оценки  в предложенном адаптивном компенсаторе фазы пассивных помех характеризуется дисперсией

в предложенном адаптивном компенсаторе фазы пассивных помех характеризуется дисперсией

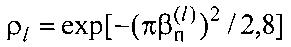

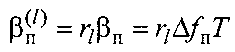

где r1=1, r2=r;  - коэффициент межпериодной корреляции помехи в l-м частотном канале (l=1, 2);

- коэффициент межпериодной корреляции помехи в l-м частотном канале (l=1, 2);  - нормированная ширина спектра помехи в l-м частотном канале (l=1, 2). Дисперсия оценки

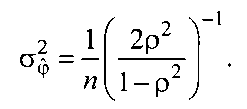

- нормированная ширина спектра помехи в l-м частотном канале (l=1, 2). Дисперсия оценки  для известного устройства (прототипа)

для известного устройства (прототипа)

Как видим, дисперсия усредненной оценки  в предложенном адаптивном компенсаторе фазы пассивных помех меньше дисперсии в известном устройстве, что соответствует повышению точности измерения и компенсации доплеровской фазы помехи, зависящей от номера частотного канала. Расчеты показывают, что при r=0,95 и βп=ΔfпT=0,1 для l-го частотного канала (l=1) точность измерения и компенсации повышается в 2 раза, а для 2-го частотного канала (l=2) - в 2,2 раза.

в предложенном адаптивном компенсаторе фазы пассивных помех меньше дисперсии в известном устройстве, что соответствует повышению точности измерения и компенсации доплеровской фазы помехи, зависящей от номера частотного канала. Расчеты показывают, что при r=0,95 и βп=ΔfпT=0,1 для l-го частотного канала (l=1) точность измерения и компенсации повышается в 2 раза, а для 2-го частотного канала (l=2) - в 2,2 раза.

Таким образом, адаптивный компенсатор фазы пассивных помех позволяет повысить точность измерения и компенсации текущего значения доплеровского сдвига фазы многочаститных пассивных помех.

Библиография

1. А.С. 934816 (СССР), МПК G01S 7/36, G01S 13/52. Режекторный фильтр / Д.И. Попов. - Опубл. 27.11.1998. - Изобретения. - 1998. - №33. - С. 407-408.

2. А.С. 1136620 (СССР), МПК G01S 7/292. Измеритель параметров пассивных помех / Д.И. Попов, В.В. Гладких. - Опубл. 27.11.1998. - Изобретения. - 1998. - №33. - С. 405.

3. А.С. 1098399 (СССР), МПК G01S 7/36. Устройство адаптивной режекции пассивных помех / Д.И. Попов. - Опубл. 20.12.1998. - Изобретения. - №35. - С. 377-378.

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОКОМПЕНСАТОР ДОПЛЕРОВСКОЙ ФАЗЫ ПАССИВНЫХ ПОМЕХ | 2015 |

|

RU2583537C1 |

| ВЫЧИСЛИТЕЛЬ ДОПЛЕРОВСКОЙ ФАЗЫ ПАССИВНЫХ ПОМЕХ | 2014 |

|

RU2559750C1 |

| ИЗМЕРИТЕЛЬ ДОПЛЕРОВСКОЙ ФАЗЫ ПАССИВНЫХ ПОМЕХ | 2014 |

|

RU2569331C1 |

| АВТОКОМПЕНСАТОР ДОПЛЕРОВСКИХ СДВИГОВ ФАЗЫ ПОМЕХ | 2016 |

|

RU2624795C1 |

| ДОПЛЕРОВСКИЙ ФАЗОМЕТР ПАССИВНЫХ ПОМЕХ | 2014 |

|

RU2550315C1 |

| АДАПТИВНЫЙ ВЫЧИСЛИТЕЛЬ ДЛЯ РЕЖЕКТИРОВАНИЯ ПОМЕХ | 2015 |

|

RU2582874C1 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ АДАПТИВНОГО РЕЖЕКТИРОВАНИЯ ПОМЕХ | 2015 |

|

RU2582871C1 |

| АДАПТИВНЫЙ РЕЖЕКТОР ПАССИВНЫХ ПОМЕХ | 2015 |

|

RU2599621C1 |

| АДАПТИВНЫЙ РЕЖЕКТОРНЫЙ ФИЛЬТР | 2015 |

|

RU2579998C1 |

| Устройство селекции движущихся целей для радиолокатора с вобуляцией периода повторения | 1984 |

|

SU1841287A1 |

Изобретение относится к вычислительной технике и может быть использовано в адаптивных устройствах режектирования многочастотных пассивных помех. Достигаемый технический результат - повышение точности адаптивной компенсации текущего значения доплеровской фазы многочастотных пассивных помех. Адаптивный компенсатор фазы пассивных помех содержит блок оценивания фазы, блок задерживания, первый и второй блоки комплексного умножения, блок комплексного сопряжения, блок задержки, синхрогенератор, первый и второй умножители, первый, второй, третий и четвертый функциональные преобразователи, первый и второй блоки памяти, комплексный сумматор, дополнительный вычислитель фазы, дополнительный блок оценивания фазы, первый и второй дополнительные блоки комплексного умножения, дополнительный блок комплексного сопряжения, дополнительный блок задержки и дополнительный блок задерживания. 9 ил.

Адаптивный компенсатор фазы пассивных помех, содержащий блок оценивания фазы, блок задерживания, первый блок комплексного умножения, второй блок комплексного умножения, блок комплексного сопряжения, блок задержки и синхрогенератор, при этом входы блока оценивания фазы через блок задерживания соединены с первыми входами первого блока комплексного умножения, вторые входы которого соединены с выходами блока комплексного сопряжения, выходы второго блока комплексного умножения соединены с объединенными входами блока комплексного сопряжения и блока задержки, выходы блока задержки соединены с первыми входами второго блока комплексного умножения, выход синхрогенератора соединен с синхровходами блока оценивания фазы, блока задерживания, первого и второго блоков комплексного умножения, блока комплексного сопряжения и блока задержки, отличающийся тем, что введены первый умножитель, первый функциональный преобразователь, второй умножитель, второй функциональный преобразователь, первый блок памяти, комплексный сумматор, дополнительный вычислитель фазы, второй блок памяти, дополнительный блок оценивания фазы, третий и четвертый функциональные преобразователи, первый дополнительный блок комплексного умножения, дополнительный блок комплексного сопряжения, дополнительный блок задержки, дополнительный блок задерживания и второй дополнительный блок комплексного умножения, при этом выход блока оценивания фазы соединен с первым входом первого умножителя, второй вход которого соединен с выходом первого блока памяти, выход первого умножителя соединен с входом первого функционального преобразователя, выходы которого соединены с первыми входами комплексного сумматора, выходы комплексного сумматора соединены с входами дополнительного вычислителя фазы, выход которого соединен с объединенными первым входом второго умножителя и входом четвертого функционального преобразователя, второй вход второго умножителя соединен с выходом второго блока памяти, выход второго умножителя соединен с входом второго функционального преобразователя, выходы которого соединены со вторыми входами второго блока комплексного умножения, выход дополнительного блока оценивания фазы соединен с входом третьего функционального преобразователя, выходы которого соединены со вторыми входами комплексного сумматора, выходы первого дополнительного блока комплексного умножения соединены с объединенными входами дополнительного блока комплексного сопряжения и дополнительного блока задержки, выходы дополнительного блока задержки соединены с первыми входами первого дополнительного блока комплексного умножения, вторые входы которого соединены с выходами четвертого функционального преобразователя, входы дополнительного блока оценивания фазы через дополнительный блок задерживания соединены с первыми входами второго дополнительного блока комплексного умножения, вторые входы которого соединены с выходами дополнительного блока комплексного сопряжения, выход синхрогенератора соединен с синхровходами первого и второго умножителей, первого, второго, третьего и четвертого функциональных преобразователей, первого и второго блоков памяти, комплексного сумматора, дополнительного вычислителя фазы, дополнительного блока оценивания фазы, первого и второго дополнительных блоков комплексного умножения, дополнительного блока комплексного сопряжения, дополнительного блока задержки и дополнительного блока задерживания, причем первыми и вторыми входами адаптивного компенсатора фазы пассивных помех являются соответственно входы блока оценивания фазы и дополнительного блока оценивания фазы, а первыми и вторыми выходами - соответственно выходы первого блока комплексного умножения и второго дополнительного блока комплексного умножения.

| RU 2064190 C1, 20.07.1996 | |||

| УСТРОЙСТВО АДАПТИВНОЙ РЕЖЕКЦИИ ПАССИВНЫХ ПОМЕХ | 1981 |

|

SU1098399A1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ШИРОКОПОЛОСНЫХ ПОМЕХ | 2000 |

|

RU2190297C2 |

| US 4395776 A, 26.07.1983. | |||

Авторы

Даты

2016-04-27—Публикация

2015-04-27—Подача