Область техники, к которой относится изобретение

Описанные в данном документе варианты осуществления относятся в основном к усовершенствованным технологиям пропуска блокировок.

Уровень техники

Традиционно, синхронизация между потоками, обращающихся к общей памяти, была реализована с помощью блокировок для защиты совместно используемых данных от параллельного доступа. Тем не менее, блокировки часто сериализируют доступ к совместно используемым данным, которые не всегда могут быть необходимы во время выполнения, но часто сомнительны, или иногда невозможно определить, когда код записан. Например, блокировка может защитить доступ ко всей хеш-таблице, но потоки могут получить доступ к определенным сегментам в хэш-таблице во время выполнения. Таким образом, в данном случае, блокировка излишне ограничивает параллелизм, что потенциально может привести к снижению производительности программы. Более эффективное использование параллельных ресурсов позволяет всем потокам, обращающихся к определенным данным, работать параллельно. Таким образом, для повышения производительности программы может использоваться блокировка с высокой степенью детализации, но часто программист при разработке и проверке сталкивается с трудностями.

Была предложена транзакционная память в качестве альтернативного решения, что позволяет потокам гипотетически входить и выходить из критических секций, называемые "транзакциями", параллельно. Если возникает конфликт во время выполнения, то потоки останавливают или отменяют транзакции и выполняют их снова для разрешения конфликта. Хотя многие эксперты считают, что единственным правильным решением является использование программной транзакционной памяти (STM), где транзакции реализованы полностью на программном обеспечении для синхронизации общей памяти в многопоточных программах, однако это влечет за собой рост накладных расходов при использовании в качестве общего решения.

Кроме того, транзакционная память требует от программиста переписать приложение с помощью анататоров транзакций для обозначения начала и окончания транзакций и, в некоторых случаях, также доступа к общей памяти. Эти усилия не могут быть значительными при разработке нового программного обеспечения, но для унаследованных приложений с потенциально тысячами строк кода (или более), это может быть существенным.

Пропуск спекулятивных блокировок (SLE) предоставляет способ выполнения критических секций параллельно в качестве спекулятивных транзакций для кода, который был записан для использования блокировок. Программист должен добавлять префикс установки блокировки и снятия блокировки с конкретными префиксами для указания начала и окончания критической секции. Если транзакция прерывается, оборудование не выполняет операцию и возвращает в начало критической секции, устанавливает блокировку и обработка продолжается в не спекулятивном режиме. К сожалению, данный вариант реализации ограничивает выполнение только одной не спекулятивной критической секции одновременно: только поток, который захватил блокировку, может выполняться не спекулятивно. Кроме того, чтобы обеспечить корректность, никакая другая спекулятивная критическая секция не может выполняться параллельно с не спекулятивной секцией.

Краткое описание чертежей

Настоящее изобретение иллюстрируется в качестве примера и не ограничивается описанием на прилагаемых чертежах, на которых одинаковые ссылочные позиции обозначают одинаковые элементы и на которых:

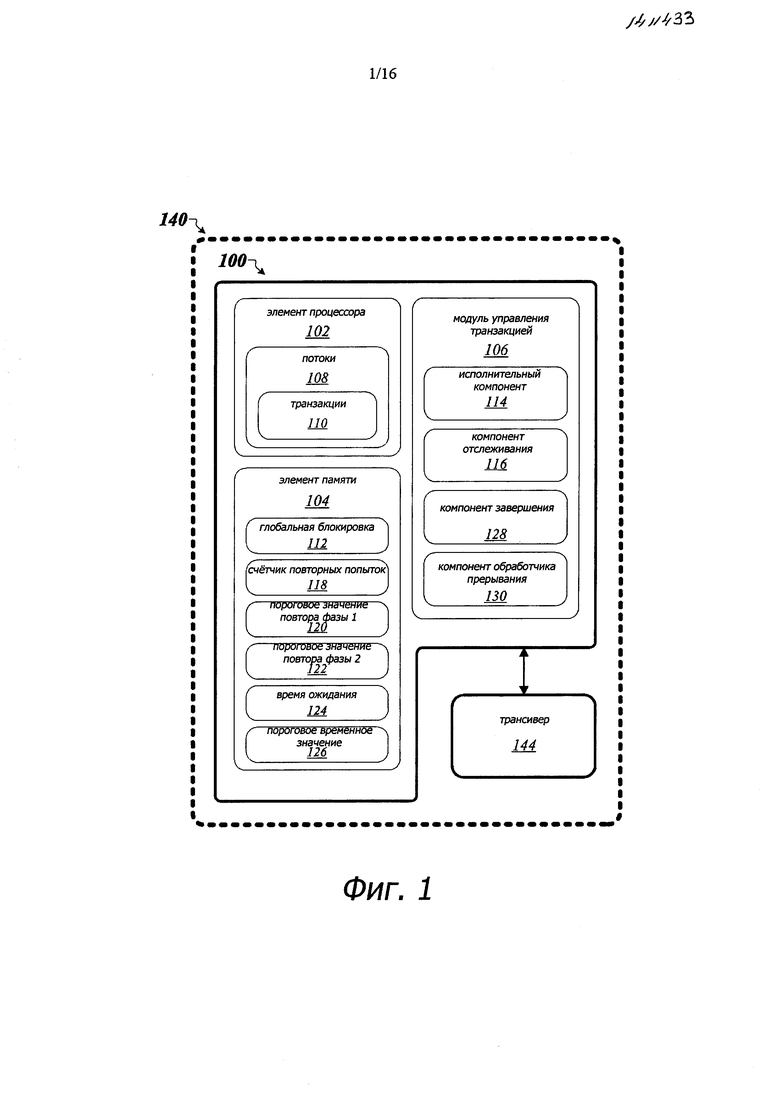

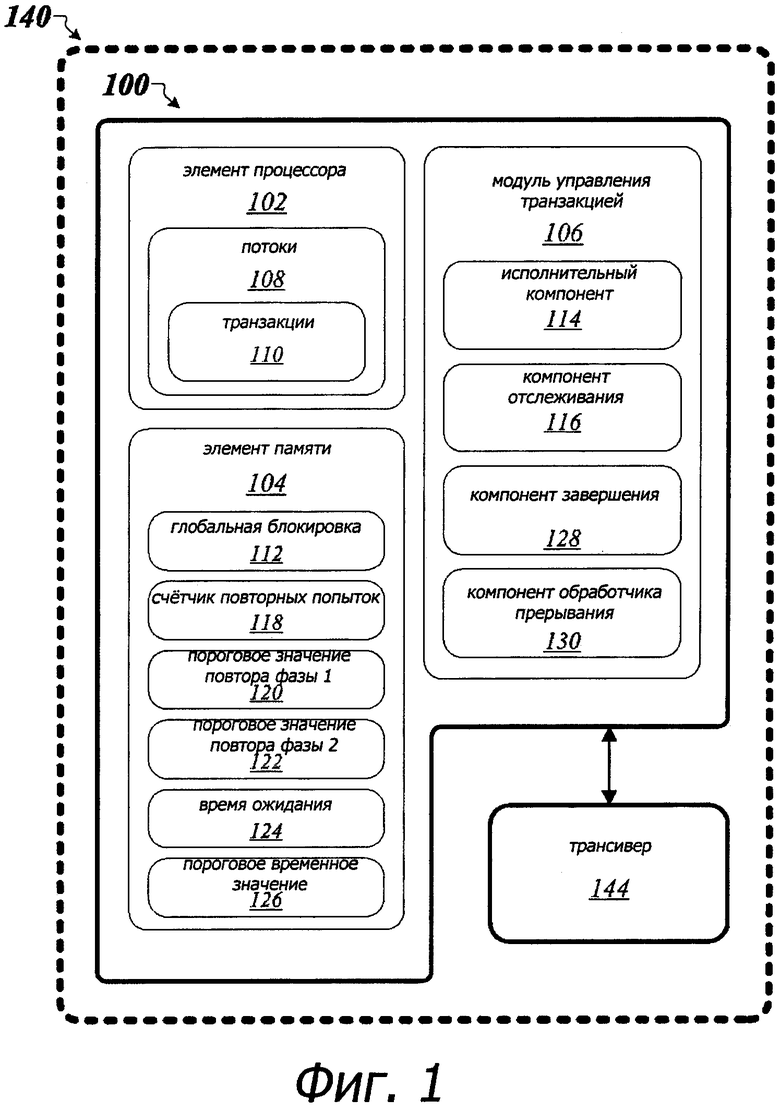

фиг. 1 иллюстрирует один вариант осуществления устройства и один вариант осуществления первой системы;

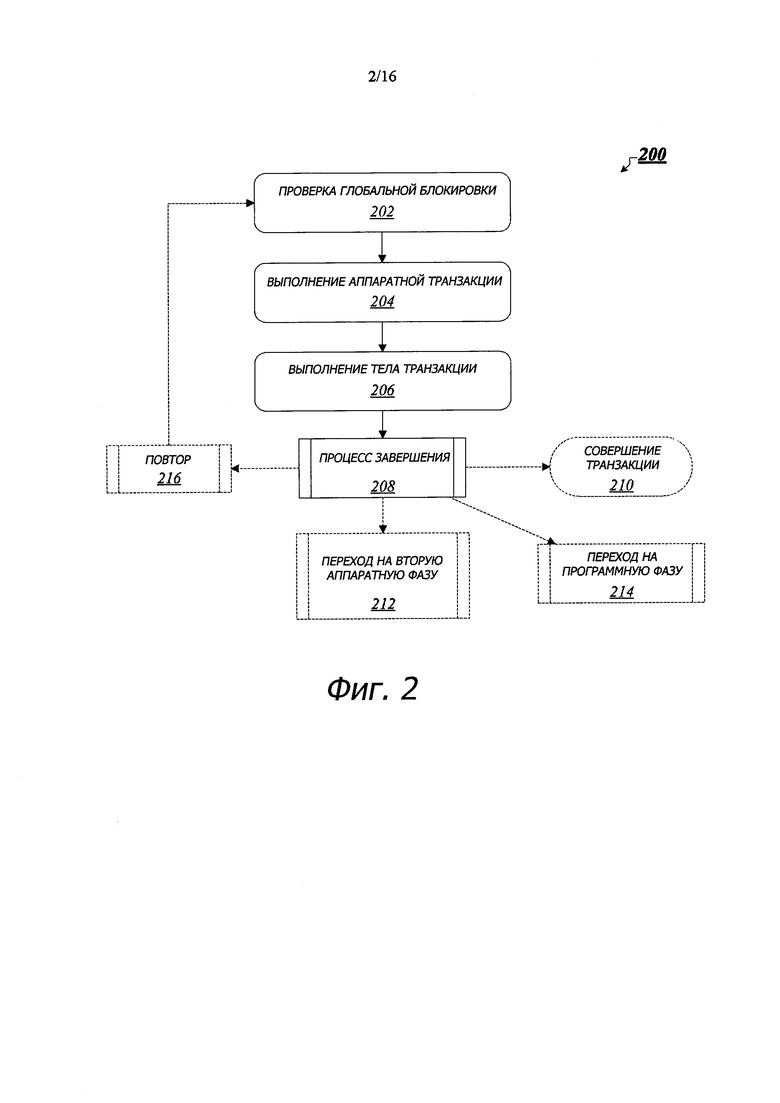

фиг. 2 иллюстрирует один вариант осуществления первого логического потока;

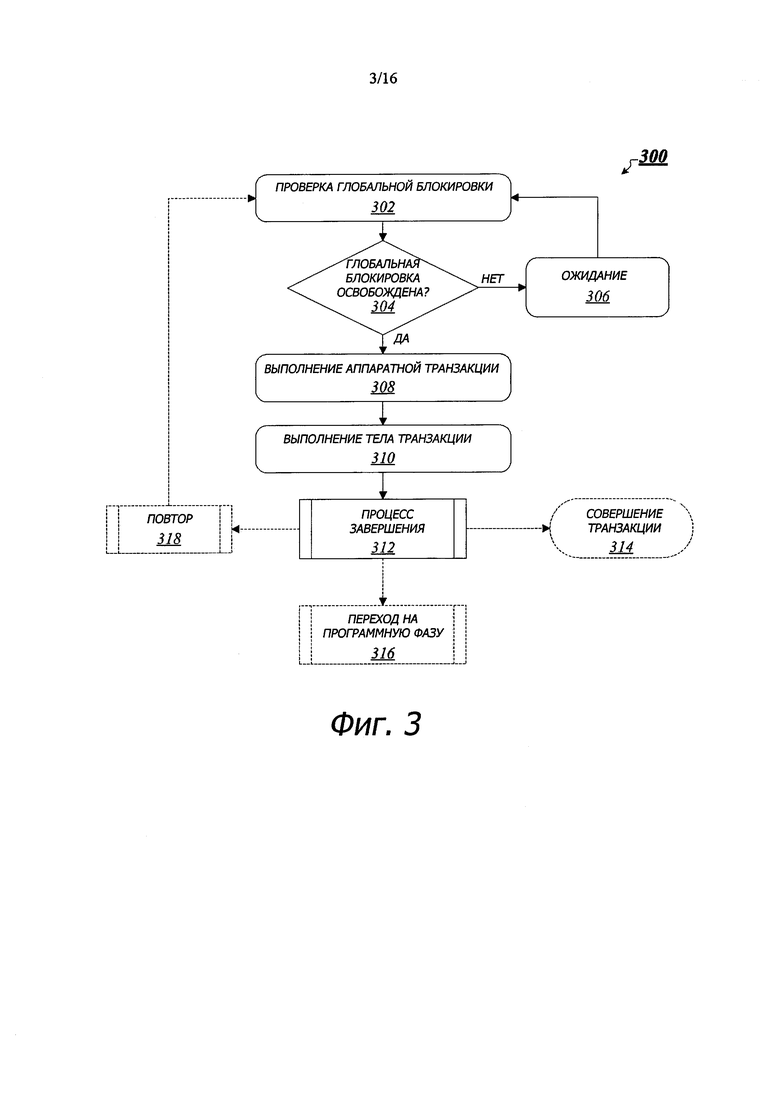

фиг. 3 иллюстрирует один вариант осуществления второго логического потока;

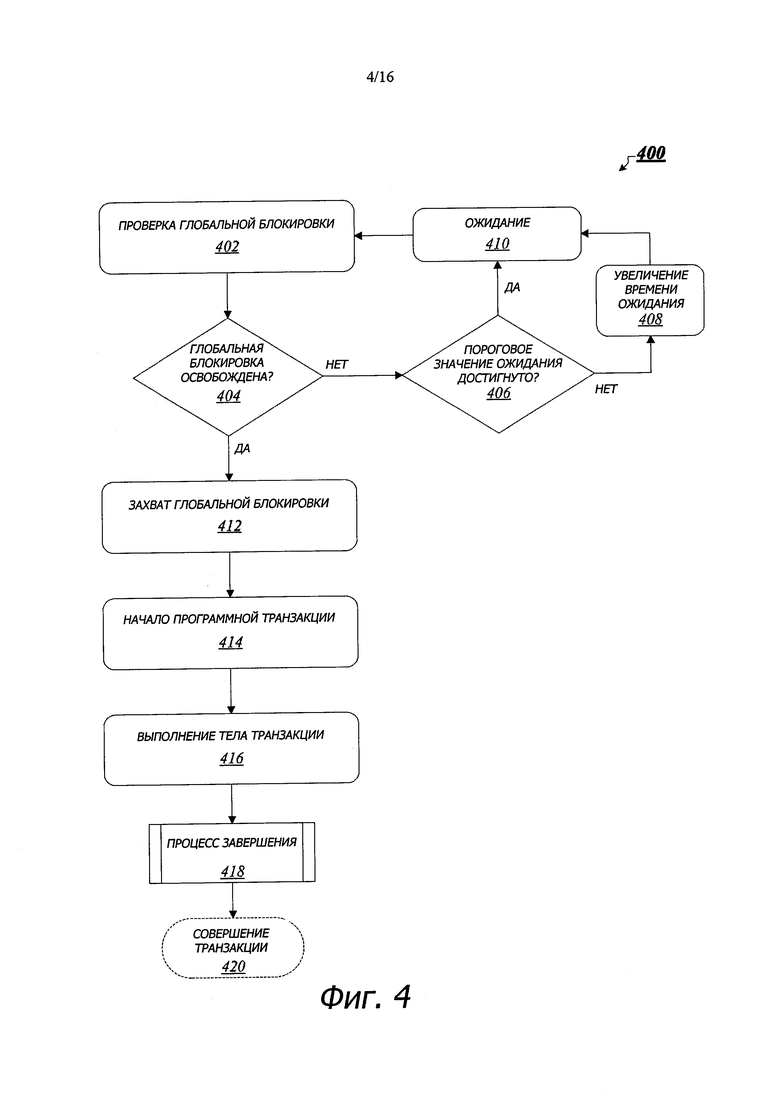

фиг. 4 иллюстрирует один вариант осуществления третьего логического потока;

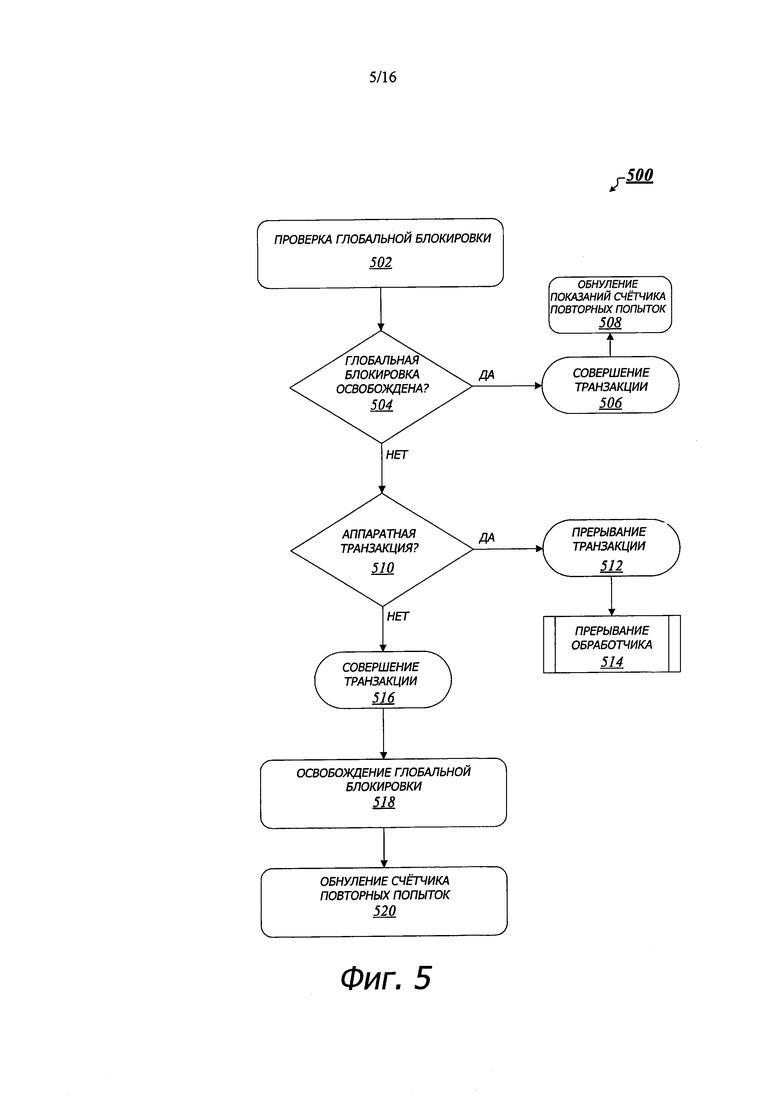

фиг. 5 иллюстрирует один вариант осуществления четвертого логического потока;

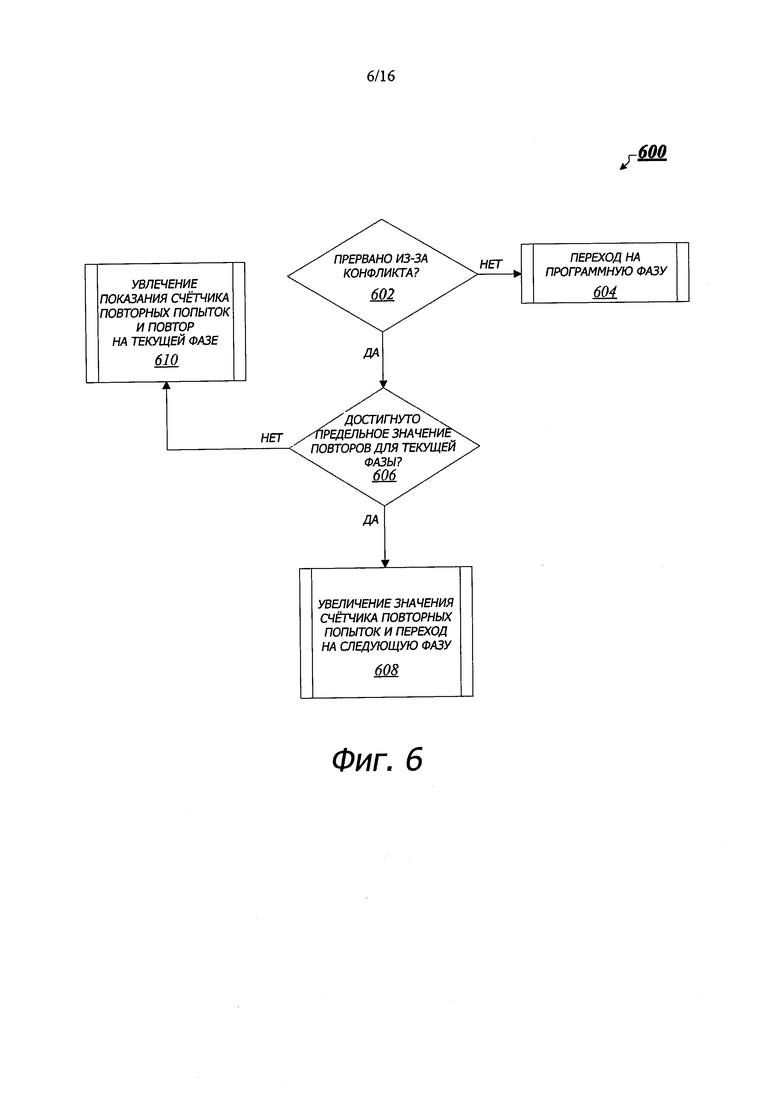

фиг. 6 иллюстрирует один вариант осуществления пятого логического потока;

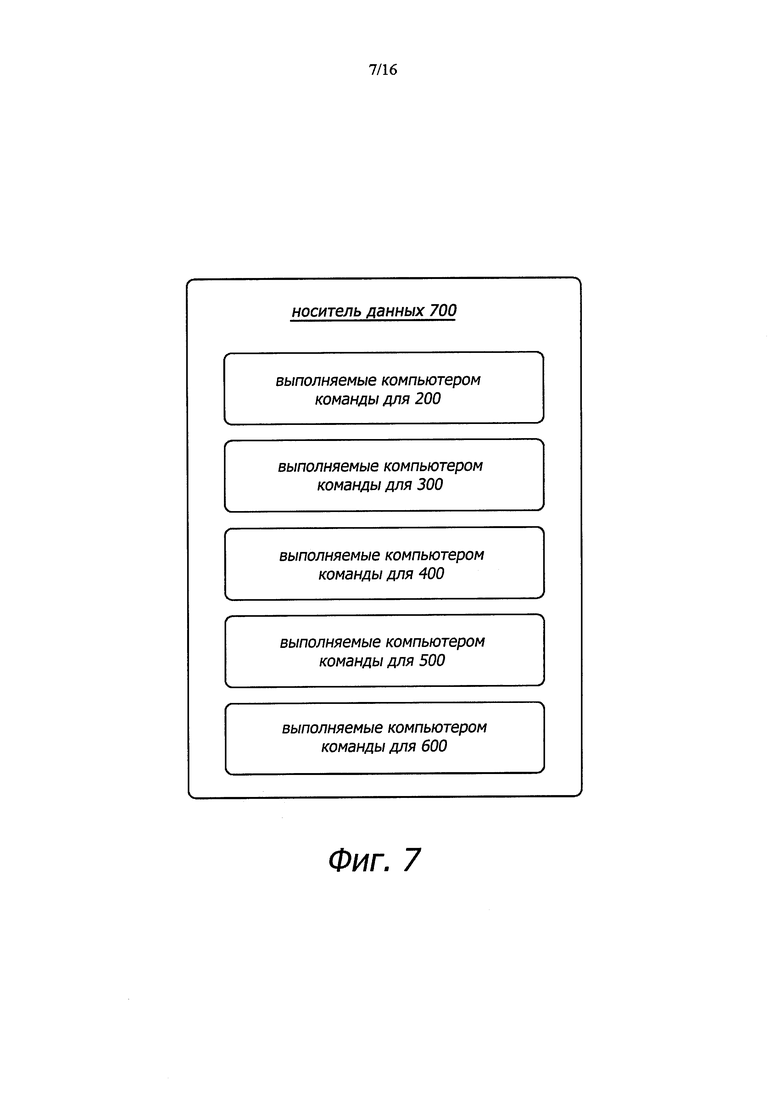

фиг. 7 иллюстрирует один вариант осуществления носителя информации;

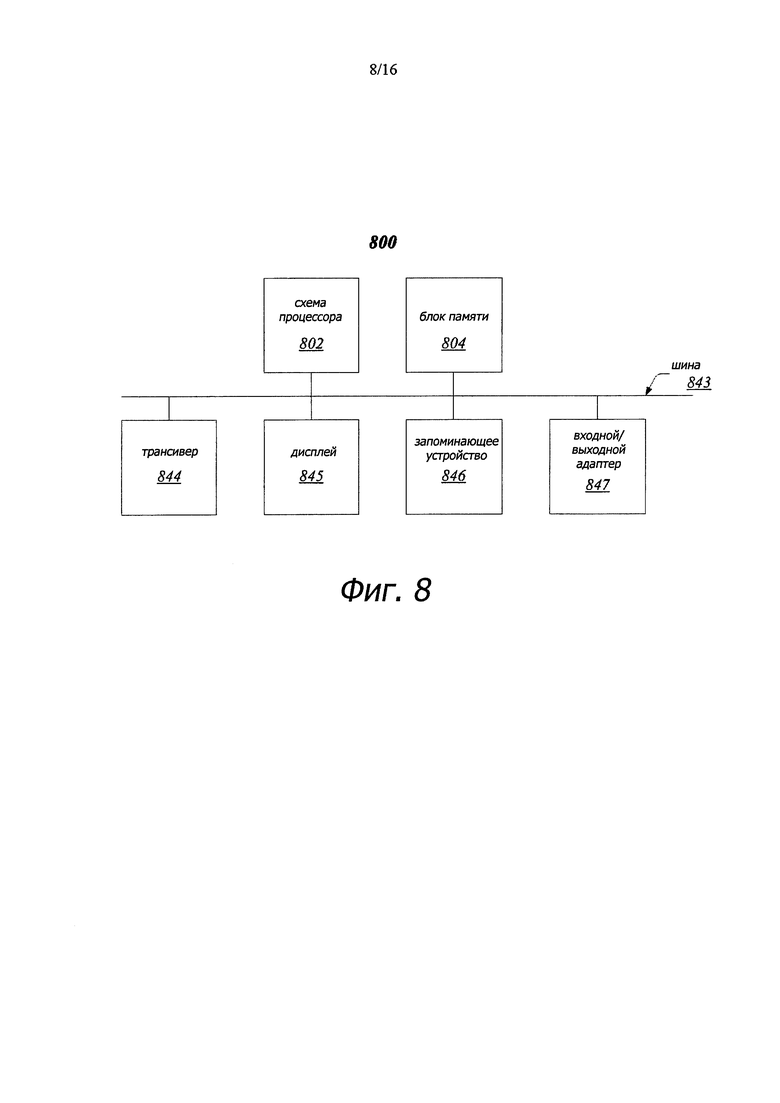

фиг. 8 иллюстрирует один вариант осуществления второй системы;

фиг. 9 иллюстрирует один вариант осуществления третьей системы;

фиг. 10 иллюстрирует один вариант осуществления устройства;

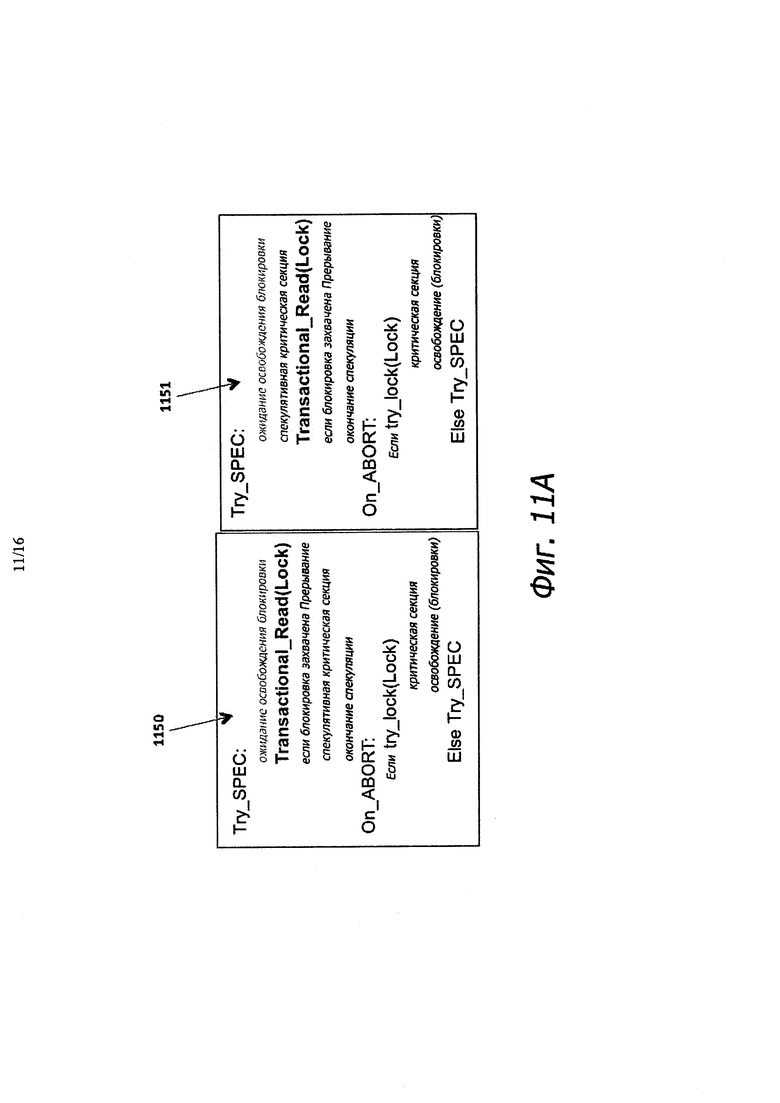

фиг. 11А иллюстрирует примерный псевдокод, иллюстрирующий работу одного варианта осуществления настоящего изобретения;

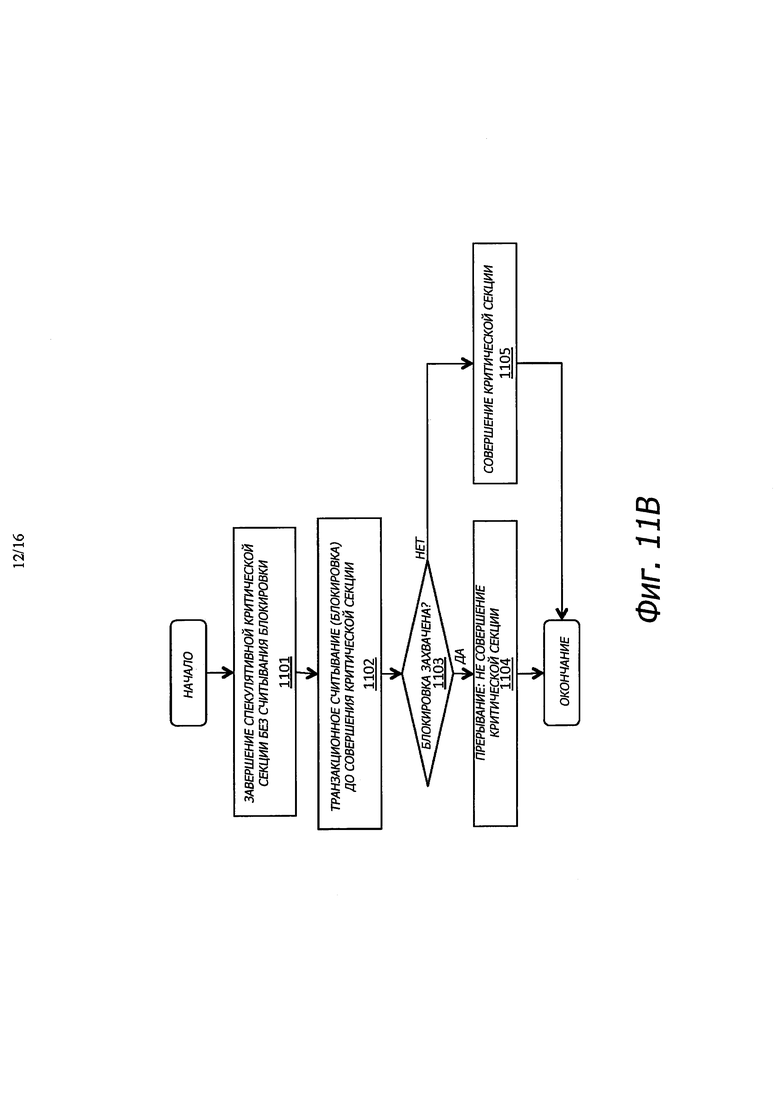

фиг. 11В иллюстрирует способ в соответствии с одним вариантом осуществления настоящего изобретения;

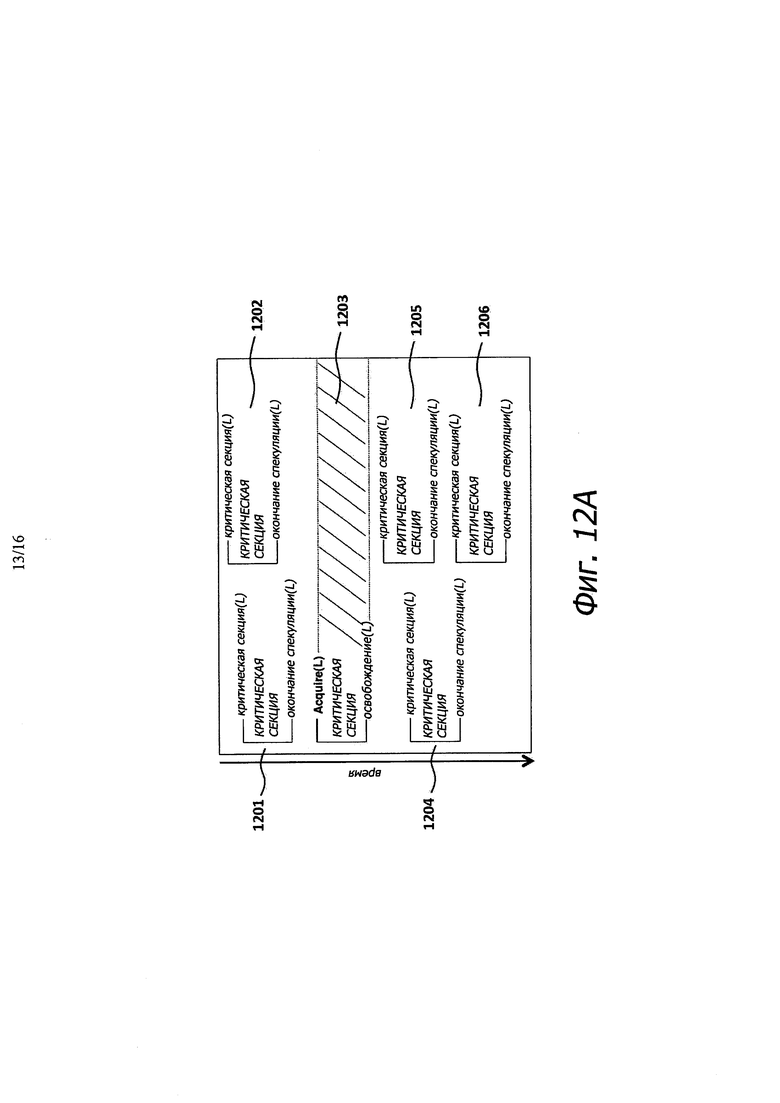

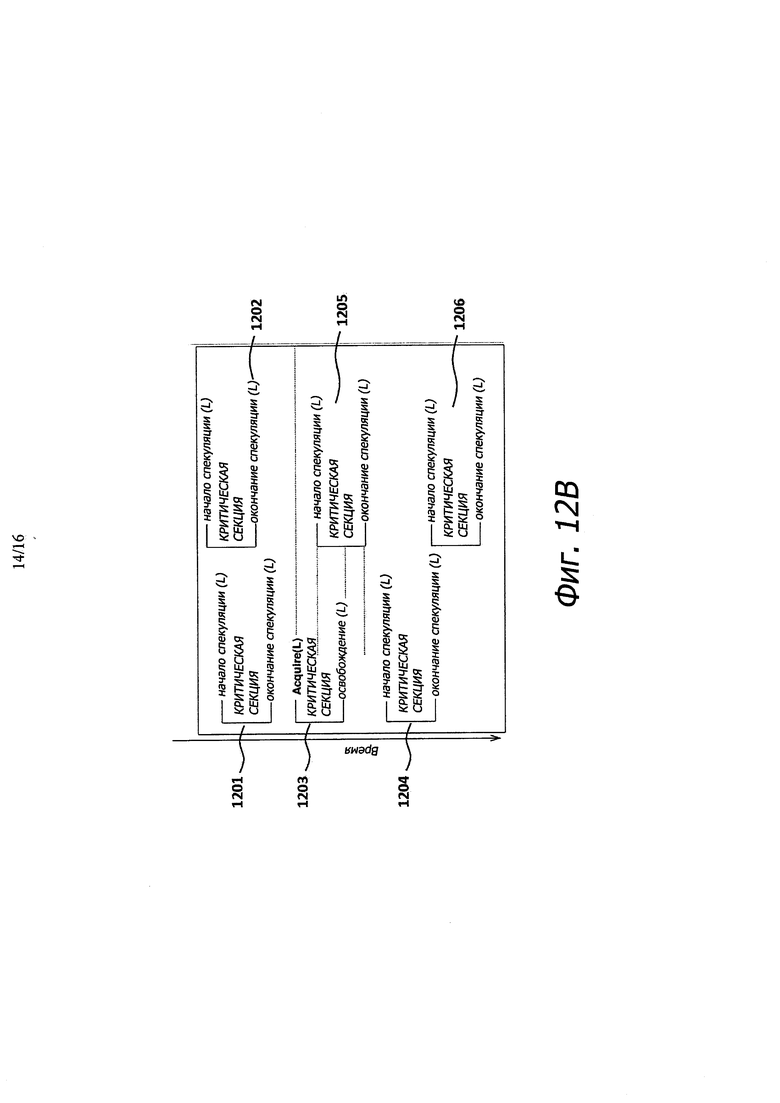

фиг. 12А-В иллюстрируют выполнение не спекулятивных критических секций и спекулятивных критических секций в разных вариантах осуществления;

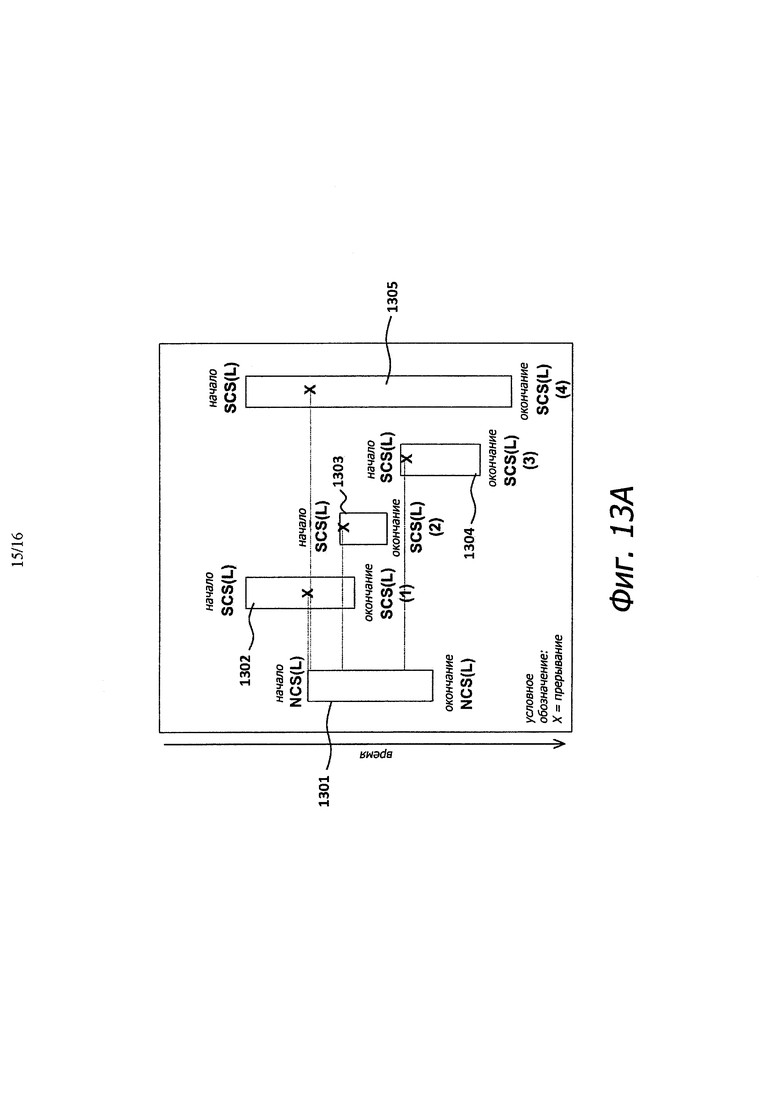

фиг. 13А-В иллюстрируют временные характеристики не спекулятивных критических секций и спекулятивных критических секций в разных вариантах осуществления.

Подробное описание вариантов осуществления

Варианты осуществления изобретения, описанные ниже, включают в себя усовершенствование предшествующих схем SLE, позволяя спекулятивным критическим секциям работать параллельно, по меньшей мере, с одной не спекулятивной критической секцией, сохраняя при этом корректность.

Согласно парадигме транзакционной памяти в среде параллельного программирования, транзакции обрабатываются с помощью подхода выполнено - не выполнено, в котором транзакции спекулятивно выполняется без изменения контента областей общей памяти до тех пор, пока те транзакции впоследствии выполняются. Таким образом, операции выполняются атомарно так, что они появляются в остальной части системы и происходят мгновенно, во время, когда они выполнены. Эти свойства позволяют обеспечить реализацию последовательности и изоляцию по отношению к операциям, которые осуществляются параллельно.

Использование программной транзакционной памяти является традиционным подходом реализации парадигмы транзакционной памяти и может включать в себя использование библиотеки времени выполнения и/или языка программирования семантики транзакционной памяти. Способы использования программной транзакционной памяти могут вызывать возникновение значительных накладных расходов, тем не менее. Аппаратная транзакционная память является другим традиционным подходом в реализации парадигмы транзакционной памяти и может включать в себя использование процессоров, кэш, протоколов шины и/или другие элементы, поддерживающие транзакции. Способы аппаратной транзакционной памяти, как правило, обеспечивают более быстрое выполнение транзакций с менее высокими ассоциированными накладными расходами, но обычно существует ограничение по размеру. Кроме того, обычные способы аппаратной транзакционной памяти обычно используют принцип выбора наилучшего возможного в соответствии с которым, не может произойти продвижение вперед. Конкретная транзакция в системе аппаратной транзакционной памяти может сколь угодно долго повторять цикл обнаружения той же ошибки, прерывание, сбоя при завершении и повторного выполнения, в связи с отсутствием механизма, для того, чтобы транзакция обрабатывалась по-разному так, чтобы цикл прерывался.

Может применяться подход гибридной транзакционной памяти в целях реализации более быстрого выполнения транзакций и снижения накладных расходов, ассоциированных с аппаратной транзакционной памятью, и в тоже время, обеспечивая прогресс при обработке транзакций. В соответствии с подходом использования гибридной транзакционной памяти, каждая транзакция первоначально обрабатывается в аппаратных средствах и впоследствии обрабатывается в программном обеспечении, если продвижение вперед не может быть достигнуто в аппаратных средствах. Одним из недостатков некоторых обычных подходов использования гибридной транзакционной памяти может быть то, что они не позволяют осуществить параллельное выполнение программных и аппаратных транзакций. В других обычных подходах использования гибридной транзакционной памяти параллельное выполнение программных и аппаратных транзакций может быть возможно, но может потребовать использования конкретного оборудования, которое поддерживает экранирующие действия и/или может потребоваться поддержка компилятора для аннотаций исходного кода транзакций. Для устранения данных недостатков, различные варианты осуществления описывают системы гибридной транзакционной памяти, в которых используется глобальная блокировка для параллельного выполнения программной транзакции и одной или более аппаратных транзакций. Некоторые варианты осуществления могут обеспечить параллельное выполнение программной транзакции и одной или более аппаратных транзакций, не требуя использования, в частности, аппаратных средств, без экранирующего действия и/или без необходимости поддержки компилятором.

Различные варианты осуществления изобретения могут быть, в основном, направлены на использование улучшенных способов управления транзакционной памятью. В одном варианте осуществления, например, устройство может содержать элемент процессора, компонент выполнения для выполнения элементом процессора параллельного выполнения программной транзакции и аппаратной транзакции в соответствии с процессом транзакционной памяти, компонент отслеживая для активации элементом процессора глобальной блокировки, указывая на выполнение программной транзакции, и компонент завершения для исполнения элементом процессора процесса завершения программной транзакции и деактивации глобальной блокировки при завершении программной транзакции, компонент завершения прерывает аппаратную транзакцию, когда глобальная блокировка активна при завершении аппаратной транзакции. Другие варианты осуществления могут быть описаны и заявлены.

Различные варианты осуществления могут включать в себя один или несколько элементов. Элемент может содержать любую упорядоченную структуру, выполненную с возможностью выполнять определенные операции. Каждый элемент может быть реализован в виде аппаратных средств, программных средств или любой их комбинации, как требуется для заданного набора конструктивных параметров или характеристик. Хотя вариант осуществления может быть описан с помощью ограниченного числа элементов в определенной топологии в качестве примера, вариант осуществления может включать в себя больше или меньше элементов в альтернативных топологиях, как требуется для данной реализации. Стоит отметить, что любая ссылка на "один вариант осуществления" или на "вариант осуществления" означает, что конкретный признак, структура или характеристика, описанные в связи с вариантом воплощения, включены в состав, по меньшей мере, одного варианта осуществления. Употребление фраз "в одном варианте осуществления", "в некоторых вариантах осуществления" и "в различных вариантах осуществления" в различных местах в описании не обязательно относятся к тому же самому варианту осуществления изобретения.

Фиг. 1 показывает блок-схема устройства 100. Как показано на фиг. 1, устройство 100 содержит множество элементов, такие как элемент 102 процессора, элемент 104 памяти и модуль 106 управления транзакцией. Варианты осуществления, однако, не ограничиваются типом, количеством или расположением элементов, показанных на этом чертеже.

В различных вариантах осуществления устройство 100 может включать в себя элемент 102 процессора. Элемент 102 процессора может быть реализован с использованием любого устройства процессора или логического устройства, способного реализовать параллелизм. В некоторых вариантах осуществления, например, элемент 102 процессора может содержать многоядерный процессор. В другом примерном варианте осуществления, элемент 102 процессора может содержать несколько процессоров, предназначенные для выполнения задач параллельно. Варианты осуществления не ограничивается этими примерами.

В различных вариантах осуществления устройство 100 может содержать или иметь возможность коммуникативно взаимодействовать с элементом 104 памяти. Элемент 104 памяти может быть реализован с помощью любых машиночитаемых носителей, способных хранить данные, как энергозависимую, так и энергонезависимую память. В некоторых вариантах осуществления, элемент 104 памяти может содержать кэш для элемента 102 процессора. В различных вариантах осуществления, элемент 104 памяти может дополнительно или альтернативно содержать другие типы носителей данных, такие как постоянное запоминающее устройство (ROM), оперативное запоминающее устройство (RAM), динамическую RAM (DRAM), DRAM с удвоенной скоростью передачи данных (DDRAM), синхронное DRAM (SDRAM), статическое RAM (SRAM), программируемое ROM (PROM), стираемую программируемую ROM (EPROM), электрически стираемую программируемую ROM (EEPROM), флэш-памяти, запоминающее устройство на полимере, такое как память на ферроэлектрическом полимере, запоминающее устройство на элементах Овшинского, память на фазовых переходах или память на сегнетоэлектриках, память со структурой металл-нитрид кремния-оксид (SONOS), магнитные или оптические карты или любой другой тип носителя, пригодный для хранения информация. Стоит отметить, что некоторая часть или весь элемент 104 памяти может быть включен в ту же интегральную схему в качестве элемента 102 процессора, или альтернативно, некоторая часть или весь элемент 104 памяти может быть расположен на интегральной схеме или на другом носителе, например, жесткий диск, который является внешним по отношению к интегральной схеме элемента 102 процессора. Хотя элемент 104 памяти установлен в устройстве 100, как показано на фиг. 1, элемент 104 памяти может быть внешним по отношению к устройству 100 в некоторых вариантах осуществления. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления, устройство 100 может включать в себя модуль 106 управления транзакциями. Модуль 106 управления транзакциями может содержать схему, логический блок и/или команды, при помощи которых осуществляется управление функционированием устройства 100 в соответствии с парадигмой транзакционной памяти. В различных вариантах осуществления модуль 106 управления транзакциями может быть выполнен с возможностью вызывать выполнение обоих транзакций, как аппаратных, так и программных транзакций в устройстве 100. Аппаратные транзакции могут содержать транзакции, выполняемые непосредственно логическим устройством в элементе 102 процессора. Программные транзакции могут содержать транзакции, выполняемые опосредовано посредством логического программирования, осуществляемого на элементе 102 процессора. Стоит отметить, что в соответствии с парадигмой транзакционной памяти, потоки могут спекулятивно выполнять транзакции без изменения контента в ячейках общей памяти до тех пор, пока транзакции будут выполнены последовательно. Если определяется конфликт или потенциальный конфликт после выполнения транзакции, то выполнение транзакции может быть прервано, вместо того, чтобы разрешить завершения процесса. Таким образом, транзакции могут быть прерваны после того, как они выполнены. Кроме того, любая конкретная транзакция может быть повторно выполнена один или несколько раз в случае, если она не была завершена после первоначального исполнения. Таким образом, при некоторых обстоятельствах, конкретная транзакция может многократно выполняется и прерывается прежде чем, в конечном счете, будет получено разрешение на ее совершение. Варианты осуществления не ограничены в этом контексте.

Фиг. 1 также иллюстрирует блок-схему системы 140. Система 140 может содержать любые из вышеупомянутых элементов устройства 100. Система 140 может дополнительно включать в себя трансивер 144. Трансивер 144 может включать в себя одну или несколько радиостанций, способных передавать и принимать сигналы с помощью различных подходящих способов беспроводной связи. Такие способы могут включать установление связи посредством одной или более беспроводных сетей. Примерные беспроводные сети включают в себя (но не ограничиваются) беспроводные локальные сети (WLANs), беспроводные персональные сети (WPANs), беспроводные городские сети (WMANs), сотовые сети и спутниковые сети. При осуществлении коммуникации посредством таких сетей, трансивер 144 может работать в соответствии с одним или более соответствующим стандартам любой версии. Варианты осуществления не ограничены в этом контексте.

Обычно, устройство 100 и/или система 140 может быть выполнена с возможностью осуществлять транзакции в соответствии с алгоритмом транзакционной памяти. Более конкретно, устройство 100 и/или система 140 может быть выполнена с возможностью выполнять алгоритм гибридной транзакционной памяти, в соответствии с которым транзакции могут быть выполнены как аппаратные, так и программные. В некоторых вариантах осуществления, в соответствии с алгоритмом гибридной транзакционной памятью, любая конкретная транзакция может быть первой, выполненной аппаратной, и затем может быть выполнена программная, если попытки совершить с помощью аппаратной были неудачны. В различных вариантах осуществления, алгоритм гибридной транзакционной памяти может обеспечить реализацию быстрого выполнения транзакции и тем самым снизить накладные расходы, связанные с аппаратной транзакционной памятью, обеспечивая дальнейшую обработку транзакций с помощью программной транзакционной памяти в качестве отката.

В различных вариантах осуществления, алгоритм гибридной транзакционной памяти может обеспечить параллельное выполнение программной транзакции и одной или более аппаратных транзакций без конструктивных ограничений, присущих обычным системам гибридной транзакционной памяти. Например, в отличие от некоторых обычных систем гибридной транзакционной памяти, которые требуют использования определенного оборудования, которое поддерживает экранирующее действие, различные варианты осуществления могут не требовать использования конкретного аппаратного оборудования и могут не требовать поддержки экранирующего действия. В качестве другого примера, в отличие от некоторых обычных систем гибридной транзакционной памяти, которые требуют поддержки уровня компилятора для аннотаций исходного кода уровня транзакций, различные варианты осуществления могут обеспечить параллельное выполнение программной транзакции и одной или несколько аппаратных транзакций, не требуя поддержки уровня компилятора. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления, элемент 102 процессора может обрабатывать один или несколько потоков 108. Каждый поток 108 может соответствовать приложению или программе, работающие на элементе 102 процессора, и любое конкретное приложение или программа могут иметь более, чем один ассоциированный поток 108. Приложение или программа может использовать конкретный поток 108 для запроса на выполнение одной или нескольких транзакций ПО. Транзакция ПО может содержать вычисления и другие задачи, которые будут выполняться элементом 102 процессора. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления, когда поток 108 запрашивает выполнение транзакции ПО, модуль 106 управления транзакцией может быть выполнен с возможностью управлять транзакцией ПО в соответствии с алгоритмом гибридной транзакционной памяти. В некоторых вариантах осуществления алгоритм гибридной транзакционной памяти может содержать несколько фаз выполнения, в течение которых могут быть сделаны попытки выполнить и завершить транзакцию ПО. В различных вариантах осуществления алгоритм гибридной транзакционной памяти может содержать первую аппаратный фазу, вторую аппаратную фазу и программную фазу. В некоторых вариантах осуществления модуль 106 управления транзакциями может быть выполнен с возможностью использовать вторую аппаратную фазу для транзакции ПО только после того, как первая аппаратная фаза была не выполнена, и может быть выполнен с возможностью использовать программную фазу для транзакции ПО только после невыполнения второй аппаратной фазы. В различных вариантах осуществления первая аппаратная фаза может содержать более агрессивную аппаратную фазу, вторая аппаратная фаза может содержать более консервативную аппаратную фазу и программная фаза может содержать откатную фазу, в течение которой транзакции ПО назначен наивысший приоритет, чтобы убедиться, что она будет завершена, и что дальнейший процесс обработки будет обеспечен. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления модуль 106 управления транзакцией может использовать глобальную блокировку 112 для обеспечения параллельного выполнения программной транзакции и одной или более аппаратных транзакций. В различных вариантах осуществления, модуль 106 управления транзакциями может быть выполнен с возможностью вызывать установку или активацию глобальной блокировки 112 при выполнении программной транзакции, и вызвать команду на освобождение или на перевод в состояние неактивности глобальной блокировки 112 при невыполнении программной транзакции. В некоторых вариантах осуществления, глобальная блокировка 112 может содержать спин-блокировку. В других вариантах осуществления может быть использована Mellor-Crummey-Scott (MCS) блокировка для глобальной блокировки 112, чтобы снизить конфликт блокировки на кэш-строке. В различных вариантах осуществления изобретения способы "MCS захват" и "MCS освобождение" могут быть использованы для использования преимуществ аппаратных транзакций, чтобы ускорить выполнение инструкций сравнение с обменом (CAS). Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления модуль 106 управления транзакциями может быть выполнен с возможностью обеспечивать выполнение некоторых аппаратных транзакций, но не допускать завершения аппаратных транзакций, когда глобальная блокировка 112 установлена или активна. В различных вариантах осуществления, модуль 106 управления транзакциями может быть выполнен с возможностью разрешать выполнение аппаратных транзакций на первой аппаратной фазе, когда глобальная блокировка 112 установлена, но может не разрешать выполнение аппаратной транзакции на второй аппаратной фазе, когда глобальная блокировка установлена. Таким образом, первая аппаратная фаза может содержать более агрессивную фазу выполнения, в то время, как вторая аппаратная фаза может содержать более консервативную фазу выполнения, во время которой, система ожидает неактивной глобальной блокировки 112 до выполнения транзакции 110. В некоторых вариантах осуществления программная фаза может содержать откатную фазу выполнения, в течение которой транзакции 110 присваивается высший приоритет для обеспечения того, что она будет завершена, и что прогресс обработки будет завершен. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления модуль 106 управления транзакцией может содержать исполнительный компонент 114. В некоторых вариантах осуществления, исполнительный компонент 114 может содержать логическую схему, схему и/или инструкции, выполненный с возможностью выполнять транзакцию 110. В различных вариантах осуществления, когда каждый раз поток 108 запрашивает выполнение новой транзакции 110, исполнительный компонент 114 может быть выполнен с возможностью выполнять одну или несколько транзакций 110. В некоторых вариантах осуществления, исполнительный компонент 114 может быть выполнен с возможностью сначала выполнять транзакцию 110 один или несколько раз как аппаратную транзакцию и затем впоследствии выполнить транзакцию 110 как программную транзакцию, если транзакция не завершена при выполнении аппаратно. В различных вариантах осуществления исполнительный компонент 114 может быть выполнен с возможностью выполнять транзакцию 110 один или несколько раз в первой аппаратной фазе, выполнять транзакцию 110 один или несколько раз на второй аппаратной фазе, если она не завершена во время первой аппаратной фазы, и выполнить транзакцию 110 в программной фазе, если она не завершена в ходе второй аппаратной фазы. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления, исполнительный компонент 114 может быть выполнен с возможностью проверять глобальную блокировку 112 перед каждым выполнением транзакции 110 во время первой аппаратной фазы и/или второй аппаратной фазы. В различных вариантах осуществления, в ходе первой аппаратной фазы исполнительный компонент 114 может быть выполнен с возможностью проверять глобальную блокировку 112 перед выполнением транзакции 110, но с возможностью продолжить выполнение транзакции 110 независимо от состояния глобальной блокировки 112. В некоторых вариантах осуществления, путем проверки глобальной блокировки 112 перед выполнением транзакции 110, исполнительный компонент 114 может быть выполнен с возможностью увеличивать вероятность того, что величина глобальной блокировки будет присутствовать в кэш-строке ядра процессора, выполняющего транзакцию 110, что может привести к временному локальному выигрышу в производительности, если и когда транзакция завершается на первой аппаратной фазе. В различных вариантах осуществления на второй аппаратной фазе исполнительный компонент 114 может быть выполнен с возможностью проверять глобальную блокировку 112 перед выполнением транзакции 110, и если глобальная блокировка 112 установлена, то исполнительный компонент 114 может быть выполнен с возможностью ожидать освобождения глобальной блокировки 112 перед выполнением транзакции 110. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления исполнительный компонент 114 может быть выполнен с возможностью проверять глобальную блокировку 112 перед выполнением транзакции 110 на программной фазе. В некоторых вариантах осуществления, если глобальная блокировка 112 активна, то исполнительный компонент 114 может быть выполнен с возможностью ожидать выполнения ряда «пустых операций» (NOPs) и затем, возможно, перепроверить глобальную блокировку 112. В различных вариантах осуществления, каждый последующий раз, когда исполнительный компонент 114 находит глобальную блокировку 112 для активации, исполнительный компонент 114 может ожидать более длительный период времени, прежде чем перепроверить глобальную блокировку 112. В некоторых вариантах осуществления исполнительный компонент 114 может быть выполнен с возможностью ожидать в течение периода времени, заданного временем 124 ожидания, и может быть выполнен с возможностью экспоненциально увеличить время 124 ожидания каждый раз, как было установлено, что глобальная блокировка 112 по-прежнему активна. В различных вариантах осуществления исполнительный компонент 114 может быть выполнен с возможностью постоянно увеличивать время 124 ожидания, пока величина не достигает пороговой величины 126 ожидания. В некоторых вариантах осуществления, когда время 124 ожидания достигает пороговой величины 126 ожидания, исполнительный компонент не может дополнительно увеличить время 124 ожидания. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления модуль 106 управления транзакцией может содержать компонент 116 отслеживания. В различных вариантах осуществления компонент 116 отслеживания может содержать логические схемы, схемы и/или инструкции, выполненный с возможностью управлять глобальной блокировкой 112, счетчик 118 повторных попыток, пороговое значение 120 повтора фазы 1 и пороговое значение 122 повтора фазы 2. В некоторых вариантах осуществления компонент 116 отслеживания может быть выполнен с возможностью устанавливать глобальную блокировку 112 на основе инструкции от исполнительного компонента 114. Например, исполнительный компонент 114 может быть выполнен с возможностью инструктировать компонент 116 отслеживания на установку глобальной блокировки 112, когда исполнительный компонент 114 начинается выполнение транзакции 110 в программной фазе. В различных вариантах осуществления, счетчик 118 повторных попыток может содержать общее число попыток, которые были сделаны для выполнения транзакции 110. В некоторых вариантах осуществления пороговое значение 120 повтора фазы 1 может содержать количество попыток, после которых исполнительный компонент 114 переводит из аппаратной фазы 1 в аппаратную фазу 2, и пороговое значение 122 фазы 2 может содержать количество попыток, после которых исполнительный компонент 114 переводит из аппаратной фазы 2 в программную фазу. В различных вариантах осуществления, когда принята новая транзакция ПО, компонент 116 отслеживания может быть выполнен с возможностью обнулить показания счетчика 118 повторных попыток. В некоторых вариантах осуществления, после каждого выполнения транзакции 110, компонент 116 отслеживания может быть выполнен с возможностью увеличить количество попыток в счетчике 118 повторных попыток. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления модуль 106 управления транзакцией может содержать компонент 128 завершения. В некоторых вариантах осуществления компонент 128 завершения может содержать логическую схему, схему и/или инструкции, выполненный с возможностью определять, следует ли завершить или прервать процесс выполнения транзакции 110 после того, как они выполняются исполнительным компонентом 114. В различных вариантах осуществления компонент 128 завершения может быть выполнен с возможностью определять, что любая конкретная транзакция 110 должна быть прервана, когда транзакция 110 конфликтует или потенциально конфликтует с другой транзакцией. В некоторых вариантах осуществления компонент 128 завершения может быть выполнен с возможностью определять, может ли транзакция 110 потенциально конфликтовать с конкурентной программной транзакцией посредством проверки глобальной блокировки 112. В различных вариантах осуществления, если глобальная блокировка 112 установлена и транзакция 110 является аппаратной транзакцией, то компонент 128 завершения может быть выполнен с возможностью определять, что транзакция 110 должна быть прервана. В некоторых вариантах осуществления, если глобальная блокировка 112 установлена и транзакция является программной транзакцией, то компонент 128 завершения может быть выполнен с возможностью завершать транзакцию 110 и инструктировать компонент 116 отслеживания освободить глобальную блокировку 112 и обнулить счетчик 118 повторных попыток. В различных вариантах осуществления, если глобальная блокировка 112 не установлена, то компонент 128 завершения может быть выполнен с возможностью завершать транзакцию 110 и инструктировать компонент 116 отслеживания обнулить счетчик 118 повторных попыток. Варианты осуществления не ограничены в этом контексте.

В некоторых вариантах осуществления модуль 106 управления транзакцией может содержать компонент 130 обработчика прерывания. В различных вариантах осуществления компонент 130 обработчика прерывания может содержать логические схемы, схемы и/или инструкции, выполненный с возможностью обрабатывать прерывание транзакций 110, в соответствии с указаниями компонента 128 завершения. В некоторых вариантах осуществления компонент 130 обработчика прерывания может быть выполнен с возможностью определять, является ли последующая операция попыткой прерывания транзакции 110, которая должна происходить в первой аппаратной фазе, на второй аппаратной фазе или в программной фазе. В различных вариантах осуществления компонент 130 обработчика прерывания может быть выполнен с возможностью определять, должна ли транзакция 110 быть прервана в результате конфликта или возможного конфликта с другой транзакции или по другой причине. Если транзакция 110 была прервана по другой причине, например, из-за недопустимой инструкции, переполнения емкости или переполнения ассоциативности кэш в связи со случайным характером доступа к памяти, компонент 130 обработчика прерывания может быть выполнен с возможностью определять, что исполнительный компонент 114 должен приступить непосредственно к программной фазе. Если транзакция 110 была прервана в связи с конфликтом или потенциальным конфликтом с другой транзакцией, то компонент 130 обработчика прерывания может быть выполнен с возможностью определять, следует ли повторить транзакцию 110 на данной фазе или на следующей фазе.

В различных вариантах осуществления, для определения фазы для следующей попытки выполнения прерывания транзакции 110, компонент 130 обработчика прерывания может быть выполнен с возможностью сравнивать показания счетчика 118 повторных попыток на фазе 1 с пороговым значением 120 повтора фазы 1 и/или пороговым значением 122 фазы 2. В некоторых вариантах осуществления, если показания счетчика 118 повторных попыток меньше, чем пороговое значение 120 фазы 1, компонент 130 обработчика прерывания может быть выполнен с возможностью инструктировать исполнительный компонент 114 повторить транзакцию 110 на первой аппаратной фазе. В различных вариантах осуществления, если показания счетчика 118 повторных попыток меньше порогового значения 122 фазы 2, но не менее порогового значения 120 фазы 1, компонент 130 обработчика прерывания может быть выполнен с возможностью инструктировать исполнительный компонент 114 повторить транзакцию 110 на второй аппаратной фазе. В некоторых вариантах осуществления, если показания счетчика 118 повторных попыток составляет не менее порогового значения 122 фазы 2, компонент 130 обработчика прерывания может быть выполнен с возможностью инструктировать исполнительный компонент 114 повторить транзакцию 110 на программной фазе. В различных вариантах осуществления компонент 116 отслеживания может быть выполнен с возможностью адаптивно определять значения пороговой величины 120 фазы 1 и/или пороговой величины 122 фазы 2 на основе количества успешных и/или неудачных завершений попыток совершения транзакций. Варианты осуществления не ограничены в этом контексте.

Операции для вышеописанных вариантов осуществления могут быть подробно описаны со ссылкой на следующие чертежи и соответствующих примерах. Некоторые из чертежей могут включать в себя логическую схему. Хотя такие чертежи, представленные здесь, могут включать в себя конкретную логическую схему, но следует понимать, что логическая блок-схема алгоритма является лишь только примером реализации общей функциональности, как описано здесь. Кроме того, данная логическая блок-схема алгоритма не обязательно должна быть выполнена в указанном порядке, если не указано иное. Кроме того, данный логический поток операций может быть реализован с помощью аппаратного элемента, программного элемента, выполняемого процессором, или любой их комбинации. Варианты осуществления не ограничены в этом контексте.

Фиг. 2 иллюстрирует один вариант осуществления логического алгоритма 200, который может быть примером операций, выполняемых одним или несколькими вариантами осуществления, описанными в данном документе. Более конкретно, логический алгоритм 200 может содержать пример операций, выполняемых в устройстве 100 и/или системе 140, показанной на фиг. 1, во время обработки любой конкретной транзакции на первой аппаратной фазе. Как показано на схеме логического алгоритма 200, глобальная блокировка может быть проверена на этапе 202. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью проверять глобальную блокировку 112. На этапе 204 может начаться аппаратная транзакция. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью начать обработку транзакции 110 в первой аппаратной фазе. На этапе 206 тело транзакции может быть выполнено. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью выполнять транзакцию 110 на аппаратном уровне.

На этапе 208 может быть применен алгоритм завершения обработки, как будет описано более подробно со ссылкой на фиг. 5 ниже. Одним из возможных результатов алгоритма завершения обработки может быть то, что транзакция может быть завершена на этапе 210. Например, компонент 128 завершения, показанный на фиг. 1, может быть выполнен с возможностью завершать транзакцию 100. Второй возможный результат алгоритма завершения обработки может быть то, что процесс обработки транзакции переходит ко второй аппаратной фазе на этапе 212. Например, компонент 128 завершения и компонент 130 обработчика прерывания, показанный на фиг. 1, могут быть выполнены с возможностью определять, что транзакция 110 должна быть прервана и выполнена повторно во второй аппаратной фазе. Третий возможный результат алгоритма завершения обработки может быть то, что обработка транзакции переходит непосредственно на программную фазу на этапе 214. Например, компонент 128 завершения и компонент 130 обработчика прерывания, показанные на фиг. 1, могут быть выполнены с возможностью определять, что транзакция 110 должна быть прерывна и повторно выполнена на программной фазе. Четвертым возможным результатом алгоритма завершения обработки может быть то, что транзакция повторяется в первой аппаратной фазе на этапе 216. Например, компонент 128 завершения и компонент 130 обработчика прерывания, показанные на фиг. 1, могут быть выполнены с возможностью определять, что транзакция 110 должна быть прервана и повторно выполнена на первой аппаратной фазе. Варианты осуществления не ограничиваются этими примерами.

Фиг. 3 иллюстрирует один вариант осуществления логической блок-схемы алгоритма 300, которая может быть примером операций, выполняемых одним или несколькими вариантами осуществления, описанными в данном документе. Более конкретно, логическая блок-схема алгоритма 300 может содержать пример операций, выполняемые в устройстве 100 и/или системе 140, показанные на фиг. 1, во время обработки любой конкретной транзакции на второй аппаратной фазе. Как показано на логической блок-схеме алгоритма 300, глобальная блокировка может быть проверена на этапе 302. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью проверять глобальную блокировку 112. На этапе 304 решение может быть принято на основании информации об освобождении глобальной блокировки. Если глобальная блокировка не освобождена, то поток может перейти на этап 306, где может быть выполнена операция ожидания, после чего глобальная блокировка может быть перепроверена. Например, если исполнительный компонент 114, показанный на фиг. 1, определяет, что глобальная блокировка 112 установлена, то может быть выполнена операция ожидания и затем выполняется повторная проверка глобальной блокировки 112. Если на этапе 304 определено, что глобальная блокировка не освобождена, то поток может перейти на этап 308. На этапе 308 может начаться аппаратная транзакция. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью начать обработку транзакции 110 на второй аппаратной фазе. На этапе 310 тело транзакции может быть выполнено. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью выполнять транзакцию 110 на аппаратном уровне.

На этапе 312 алгоритм завершения обработки может быть применен, как будет описано более подробно со ссылкой на фиг. 5 ниже. Одним из возможных результатов алгоритма завершения обработки может быть то, что транзакция может быть завершена на этапе 314. Например, компонент 128 завершения, показанный на фиг. 1, может быть выполнен с возможностью завершать транзакцию 110. Вторым возможным результатом алгоритма завершения обработки может быть факт того, что обработка транзакции переходит на программную фазу на этап 316. Например, компонент 128 завершения и компонент 130 обработчика прерывания, показанные на фиг. 1, могут быть выполнены с возможностью определять, что транзакция 110 должна быть прервана и повторно выполнена в программной фазе. Третий возможный результат алгоритма завершения обработки может представлять собой факт того, что транзакция повторяется во второй аппаратной фазе на этапе 318. Например, компонент 128 завершения и компонент 130 обработчика прерывания, показанные на фиг. 1, могут быть выполнены с возможностью определять, что транзакция 110 должна быть прервана и повторно выполнена во второй аппаратной фазе. Варианты осуществления не ограничивается этими примерами.

Фиг. 4 иллюстрирует один вариант осуществления логической блок-схемы алгоритма 400, которая может быть примером операций, выполняемых одним или несколькими вариантами осуществления, описанными в данном документе. Более конкретно, логическая блок-схема алгоритма 400 может содержать пример операций, выполняемые в устройстве 100 и/или системе 140, показанные на фиг. 1, во время обработки любой конкретной транзакции в программной фазе. Как показано на логической блок-схеме алгоритма 400, глобальная блокировка может быть проверена на этапе 402. Например, компонент 114 выполнения, показанный на фиг. 1, может быть выполнен с возможностью проверять глобальную блокировку 112. На этапе 404, решение может быть принято на основании информации об освобождении глобальной блокировки. Если глобальная блокировка не освобождена, то поток операций может перейти на этап 406.

На этапе 406 может быть определено, был ли достигнут порог ожидания. Например, компонент 116 отслеживания, показанный на фиг. 1, может быть выполнен с возможностью определять, что время 124 ожидания достигло порогового значения 126 ожидания. Если определено, что время ожидания не достигло порога ожидания, то поток операций может перейти на этап 408, где время ожидания может быть увеличено. Например, если компонент 116 отслеживания, показанный на фиг. 1 определяет, что время 124 ожидания не достигло порогового значения 126, то может быть увеличено время 124 ожидания. Из этапа 408 поток может перейти на этап 410, где процесс ожидания содержит период времени, равный времени ожидания, после чего глобальная блокировка может быть перепроверена. Например, исполнительный компонент 114, показанный на фиг. 1, может выполнять процесс ожидания, содержащий период времени, равный времени 124 ожидания, и затем осуществить повторную проверку глобальной блокировки 112. Если на этапе 406 определено, что пороговое значение ожидания было достигнуто, то поток может перейти непосредственно на этап 410 без увеличения времени ожидания на этапе 408.

Если на этапе 404 определено, что глобальная блокировка освобождена, то поток может перейти на этап 412. На этапе 412, глобальная блокировка может быть получена для транзакции, которая должна быть выполнена программно. Например, компонент 116 отслеживания может быть выполнен с возможностью получать глобальную блокировку 112 от транзакции 110, которая будет выполнена программно исполнительным компонентом 114. На этапе 414 программная транзакция может начаться. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью начать обработку транзакции 110 на программной фазе. На этапе 416 тело транзакции может быть выполнено. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью выполнять транзакцию 110 программно. На этапе 418 алгоритм завершения обработки может быть применен, как будет описано более подробно со ссылкой на фиг. 5 ниже. Применение алгоритма завершения обработки может привести к завершению транзакции на этапе 420. Например, компонент 128 завершения, показанный на фиг. 1, может быть выполнен с возможностью завершать транзакцию 110. Варианты осуществления не ограничивается этими примерами.

Фиг. 5 иллюстрирует один из вариантов осуществления логической блок-схемы алгоритма 500, который может быть примером операций, выполняемых одним или несколькими вариантами осуществления, описанными в данном документе. Более конкретно, логическая блок-схема алгоритма 500 может содержать пример операций, выполняемые компонентом 128 завершения, показанный на фиг. 1, в применении алгоритма завершения обработки для выполнения транзакции 110. Как показано на фиг. 5, глобальная блокировка может быть проверена на этапе 502. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью проверить глобальную блокировку 112. На этапе 504 может быть принято решение на основании информации об освобождении глобальной блокировки. Если глобальная блокировка не освобождена, то поток может пройти до этапа 506, где транзакция может быть завершена. Например, если глобальная блокировка 112, показанная на фиг. 1, освобождена, то компонент 128 завершения может быть выполнен с возможностью завершить транзакцию 110. Поток может проходить до этапа 508, где счетчик повторных попыток может быть обнулен. Например, компонент 116 отслеживания, показанный на фиг. 1, может быть выполнен с возможностью обнулить счетчик 118 повторных попыток.

Если определено на этапе 504, что глобальная блокировка захвачена, то поток может перейти на этап 510. На этапе 510 может быть определено, является ли транзакция аппаратной транзакцией. Например, компонент 116 отслеживания, показанный на фиг. 1, может быть выполнен с возможностью определять, является ли транзакция ПО аппаратной транзакцией. Если будет определено, что транзакция представляет собой аппаратную транзакцию, то поток может перейти на этап 512, где транзакция прерывается. Например, исполнительный компонент 114, показанный на фиг. 1, может быть выполнен с возможностью прерывать транзакцию 110. Из этапа 512, поток может перейти на этап 514, где может быть применен алгоритм прерывания обработки. Например, компонент 130 обработчика прерывания, показанный на фиг. 1, может быть выполнен с возможностью применять алгоритм прерывания обработки, когда транзакция 110 прерывается. Если определено на этапе 510, что транзакция является программной транзакцией, то поток может перейти на этап 516, где транзакция может быть завершена. Например, если компонент 116 отслеживания, показанный на фиг. 1, определяет, что транзакция 110 является программной транзакцией, компонент 128 завершения может быть выполнен с возможностью завершать транзакцию. На этапе 518 глобальная блокировка может быть освобождена. Например, компонент 128 завершения, показанный на фиг. 1, может быть выполнен с возможностью освободить глобальную блокировку 112. На этапе 520 счетчик повторных попыток может быть обнулен. Например, компонент 116 отслеживания, показанный на фиг. 1, может быть выполнен с возможностью обнулить счетчик 118 повторных попыток. Варианты осуществления не ограничивается этими примерами.

Фиг. 6 иллюстрирует один вариант осуществления логического потока 600, который может быть примером операций, выполняемые одним или несколькими вариантами осуществления, описанными в данном документе. В частности, логический поток 600 может содержать пример операций, выполняемых компонентом 130 обработчика прерывания, показанный на фиг. 1, в применении алгоритма прерывания обработки, если компонент 128 завершения установил, что транзакция 110 будет прервана. Как показано на фиг. 6 на этапе 602, решение может быть принято на основании того, что прерванная транзакция была прервана из-за конфликта или потенциального конфликта с другой транзакцией, а не в по другой причине, такой как недопустимая инструкция, переполнение емкости или переполнения ассоциативности кэша в связи со случайной схемой доступа к памяти. Если определено, что транзакция была прекращена по причине, отличной от конфликта или возможного конфликта с другой транзакцией, то поток может перейти на этап 604, где транзакция может перейти к программной фазе.

Например, если компонент 130 обработчика прерывания, показанный на фиг. 1, определяет, что транзакция 110 прервана в связи с недопустимой инструкцией, переполнением емкости, переполнения ассоциативности кэша или по другой причине, то компонент может быть выполнен с возможностью давать команду исполнительному компоненту 114 обработать транзакцию в программной фазе. Если определено на этапе 602, что транзакция была прервана в связи с конфликтом или потенциальным конфликтом с другой транзакцией, то поток может пройти на этап 606.

На этапе 606 может быть определено, было ли достигнуто предельное значение повторных попыток для текущей фазы. Например, компонент 116 отслеживания может быть выполнен с возможностью определять факт того, что показания счетчика 118 повторных попыток равны или больше порогового значения 120 повтора фазы 1 и/или порогового значения 122 повтора фазы 2. Если определено, что предельное значение повторных попыток для текущей фазы было достигнуто, то поток может перейти на 608. На этапе 608 показания счетчика повторных попыток могут быть увеличены, и процесс обработки транзакции может перейти к следующей фазе. Например, если компонент 116 отслеживания определяет, что ограниченное количество повторных попыток для текущей фазы было достигнуто, то это может увеличить значение счетчика повторных попыток, что позволить направить сигнал управления в исполнительный компонент 114 для начала обработки транзакции 110 на следующем этапе. Если на этапе 606 определено, что предел повторных попыток для текущей фазы не был достигнут, то поток может перейти на этап 610. На этапе 610 значение счетчика повторных попыток может быть увеличено, и транзакция может быть повторена на данном этапе. Например, если компонент 116 отслеживания определяет, что лимит повтора для текущего этапа не был достигнут, то это может увеличивать значение счетчика попыток и поручить исполнительному компоненту 114 повторить транзакцию 110 на текущем этапе. Варианты осуществления не ограничивается этими примерами.

На фиг. 7 показан вариант осуществления носителя 700 данных. Носитель 700 данных может содержать производственное изделие. В одном варианте осуществления носитель 700 данных может содержать любой непреходящий машиночитаемый носитель или машиночитаемый носитель, таком как оптическое, магнитное или полупроводниковое запоминающее устройство. Носитель данных может хранить различные типы исполняемые компьютером команды, например, команды для выполнения одного или нескольких логических потоков 200, 300, 400, 500 и 600. Примеры читаемого компьютером или машиночитаемого носителя данных могут включать в себя любые материальные носители, способные хранить электронные данные, в том числе энергонезависимая память или энергонезависимая память, съемное или несъемное запоминающее устройство, стираемая или нестираемая память, доступная для записи или имеющая возможность повторной записи память и так далее. Примеры исполняемых компьютером команд могут включать в себя любой подходящий тип кода, например, исходный код, скомпилированный код, интерпретированный код, исполняемый код, статический код, динамический код, объектно-ориентированный код, визуальный код и тому подобное. Варианты осуществления не ограничены в этом контексте.

Фиг. 8 иллюстрирует один вариант осуществления системы 800. В различных вариантах осуществления система 800 может являться примером одной системы или архитектуры, пригодной для использования с одним или несколькими вариантами осуществления, описанными в данном документе, такими как устройство 100 и/или система 140, показанные на фиг. 1, логический поток 200, показанный на фиг. 2, логическая блок-схема алгоритма 300, показанная на фиг. 3, логическая блок-схема алгоритма 400, показанная на фиг. 4, логическая блок-схема алгоритма 500, показанная на фиг. 5, логическая блок-схема алгоритма 600, показанная на фиг. 6 и/или носитель 700 данных, показанный на фиг. 7. Варианты осуществления не ограничены в этом отношении.

Как показано на фиг. 8, система 800 может включать в себя несколько элементов. Один или несколько элементов могут быть реализованы с использованием одной или нескольких цепей, компонентов, регистров, процессоров, программ, модулей или любой их комбинации, как требуется для заданного набора конструктивных ограничений или производительности. Хотя фиг. 8 показывает ограниченное количество элементов в определенной топологии в качестве примера, следует понимать, что более или менее элементов в любой подходящей топологии могут быть использованы в системе 800, как требуется для данной реализации. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления система 800 может включать в себя элемент 802 процессора. Элемент 802 процессора может быть реализован с использованием любого процессора или логического устройства и может быть таким же или аналогичным элементу 102 процессора, показанного на фиг. 1.

В одном варианте осуществления система 800 может включать в себя элемент 804 памяти с возможностью соединения с элементом 802 процессора. Элемент 804 памяти может быть соединен с элементом 802 процессора с помощью коммуникационной шины 843 или с помощью выделенной коммуникационной шины между элементом 802 процессора и элементом 804 памяти, как желательно для данной реализации. Элемент 804 памяти может быть реализован с использованием любой машиночитаемого или читаемого компьютером носителя, способного хранить данные, например, энергозависимое и энергонезависимое запоминающее устройство, и может быть таким же или аналогичным элементу 104 памяти, показанного на фиг. 1. В некоторых вариантах осуществления машиночитаемый или считываемый компьютером носитель может включать в себя непреходящий носитель данных. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления система 800 может включать в себя трансивер 844. Трансивер 844 может включать в себя одну или несколько радиостанций, способные передавать и принимать сигналы с использованием различных способов, пригодных для беспроводной связи, и может быть таким же или аналогичным трансиверу 144, показанному на фиг. 1.

В различных вариантах осуществления система 800 может включать в себя дисплей 845. Дисплей 845 может содержать любое устройство отображения, способное отображать информацию, полученную из элемента 802 процессора. Примеры дисплея 845 могут включать в себя телевизор, монитор, проектор и экран компьютера. В одном варианте осуществления, например, дисплей 845 может быть реализован с помощью жидкокристаллического дисплея (LCD), светоизлучающий диода (LED) или другого подходящего типа визуального интерфейса. Дисплей 845 может включать в себя, например, цветной сенсорный дисплей. В различных вариантах осуществления дисплей 845 может включать в себя один или несколько тонкопленочных транзисторов (TFT), встроенных в LCD. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления система 800 может включать в себя запоминающее устройство 846. Запоминающее устройство 846 может быть реализовано в виде энергонезависимого запоминающего устройства, например, но не ограничиваясь этим, магнитный диск, привод оптических дисков, ленточный накопитель, встроенное запоминающее устройство, подключаемое запоминающее устройство, флэш-память, SDRAM с батарейным питанием (синхронное DRAM) и/или запоминающее устройство с доступом через сеть. В вариантах осуществления память 846 может включать в себя технологию для увеличения производительности хранения с более надежной защитой ценной цифровой информации, в случае использования нескольких жестких дисков, например. Дополнительные примеры памяти 846 могут включать в себя жесткий диск, гибкий диск, компакт-диск для однократной записи данных (CD-ROM), компакт-диск для однократной записи (CD-R), компакт-диск с многократной записью (CD-RW), оптический диск, магнитный носитель, магнитооптические носители, съемные карты памяти или диски, различные виды DVD устройств, ленточные накопители, кассетное устройство или тому подобное. Варианты осуществления не ограничены в этом контексте.

В различных вариантах осуществления система 800 может включать в себя один или несколько входных/выходных адаптеров 847. Примеры входных/выходных адаптеров 847 могут включать в себя порты/адаптеры универсальной последовательной шины (USB), порты/адаптеры шины сверхбыстрой передачи данных IEEE 1394 и так далее. Варианты осуществления не ограничены в этом контексте.

Фиг. 9 иллюстрирует вариант осуществления системы 900. В различных вариантах осуществления система 900 может представлять систему или архитектуру, пригодную для использования с одним или несколькими вариантами осуществления, описанными в данном документе, такими как устройство 100 и/или система 140, показанная на фиг. 1, логическим потоком 200, показанного на фиг. 2, логической блок-схемой алгоритма 300, показанной на фиг. 3, логической блок-схемой алгоритма 400, показанной на фиг. 4, логической блок-схемой алгоритма 500, показанной на фиг. 5, логической блок-схемой алгоритма 600, показанной на фиг. 6 и/или носителем 700 данных, показанным на фиг. 7, и/или системы 800, показанной на фиг. 8. Варианты осуществления не ограничены в этом отношении.

Как показано на фиг. 9, система 900 может включать в себя несколько элементов. Один или несколько элементов могут быть реализованы с использованием одного или нескольких цепей, компонентов, регистров, процессоров, подпрограмм, модулей или любой их комбинации, как требуется для заданного набора конструктивных ограничений или производительности. Хотя фиг. 9 показывает ограниченное количество элементов в определенной топологии в качестве примера, очевидно, что больше или меньше элементов в любой подходящей топологии могут быть использованы в системе 900, как требуется для данной реализации. Варианты осуществления не ограничены в этом контексте.

В вариантах осуществления система 900 может быть медиа-системой, хотя система 900 не ограничивается этом контексте. Например, система 900 может быть включена в состав персонального компьютера (PC), портативного компьютера, ультра-портативного компьютера, планшета, сенсорной панели, портативного компьютера, карманного компьютера, переносного компьютера, персонального цифрового помощника (PDA), сотового телефона, комбинированного устройства сотовый телефон/PDA, телевизора, смарт-устройства (например, смартфона, смарт-планшета или смарт-телевизора), мобильного интернет-устройства (MID), устройство обмена сообщениями, устройство передачи данных и так далее.

В вариантах осуществления система 900 включает в себя платформу 901, соединенную с дисплеем 945. Платформа 901 может принимать контент из устройства обеспечения контента, такого как устройство (а) 948 предоставления услуги по передачи контента или устройство (а) 949 доставки контента или другие подобные источники контента. Навигационный контроллер 950 включает в себя один или несколько навигационных признаков, которые могут быть использованы для взаимодействия, например, с платформой 901 и/или дисплеем 945. Каждый из этих компонентов описан более подробно ниже.

В вариантах осуществления платформа 901 может включать в себя любую комбинацию элемента 902 процессора, набора 903 микросхем, элемента 904 памяти, трансивера 944, запоминающего устройства 946, приложений 951 и/или графической подсистемы 952. Набор 903 микросхем может обеспечить взаимодействие между элементом 902 процессора, элемента 904 памяти, трансивером 944, запоминающим устройством 946, приложениями 951 и/или графической подсистемой 952. Например, набор 903 микросхем может включать в себя адаптер для устройств хранения данных (не показан), способный обеспечивать взаимодействие с запоминающим устройством 946.

Элемент 902 процессора может быть реализован с использованием любого устройства или логического процессора и может быть таким же или аналогичным элементу 802 процессора, показанного на фиг. 8.

Элемент 904 памяти может быть реализован с использованием любых машиночитаемых или считываемых компьютером носителей, способные обеспечить хранение данных, и может быть таким же или похожим на элемент 804 памяти, показанный на фиг. 8.

Трансивер 944 может включать в себя одну или несколько радиостанций, способных передавать и принимать сигналы с использованием различных способов, пригодных для беспроводной связи, и может быть таким же или похожим на трансивер 844, показанный на фиг. 8.

Дисплей 945 может включать в себя любой тип телевизионного монитора или дисплея, и может быть таким же или подобным дисплею 845, показанному на фиг. 8.

Запоминающее устройство 946 может быть реализовано в виде устройства энергонезависимой памяти и может быть таким же или похожим на запоминающее устройство 846, показанное на фиг. 8.

Графическая подсистема 952 может выполнять обработку изображений, таких как неподвижных изображений и видео для их отображения. Графическая подсистема 952 может быть графическим процессором (GPU) или блоком обработки видеоданных (VPU), например. Аналоговый или цифровой интерфейс может быть использован для коммуникативного соединения графической подсистемы 952 и дисплея 945. Например, интерфейс может быть любым из следующего перечня: мультимедийный интерфейс высокой четкости, дисплейный порт, беспроводной HDMI и/или HD-совместимые способы беспроводной связи. Графическая подсистема 952 может быть интегрирована в элемент 902 процессора или набор 903 микросхем. Графическая подсистема 952 может быть отдельной картой, коммуникативно соединенной с набором 903 микросхем.

Способы обработки графики и/или видео, описанные здесь, могут быть реализованы с использованием различных аппаратных архитектур. Например, графические и/или видео функциональные возможности могут быть реализованы набором микросхем. В качестве альтернативы, можно использовать дискретный графический и/или видеопроцессор. В другом варианте осуществления графические и/или видео функции могут быть реализованы с помощью процессора общего назначения, в том числе многоядерного процессора. В другом дополнительном варианте осуществления, функции могут быть реализованы в устройстве бытовой электроники.

В вариантах осуществления устройство (а) 948 предоставления услуги по передачи контента может быть размещено любой национальной, международной и/или независимой службой и, следовательно, доступно для платформы 901 через Интернет, например. Устройство (а) 948 предоставления услуги по передачи контента может быть соединено с платформой 901 и/или дисплеем 945. Платформа 901 и/или устройство (а) 948 предоставления услуги по передачи контента могут быть соединены с сетью 953 для обеспечения обмена (например, передачи и/или приема) медиа информацией в и из сети 953. Устройство (а) 949 доставки контента также может быть соединено с платформой 901 и/или дисплеем 945.

В вариантах осуществления, устройство (а) 948 предоставления услуги по передачи контента может включать в себя телевизионную приставку кабельного телевидения, персональный компьютер, сеть, телефон, Интернет-совместимые устройства или устройства, способные доставлять цифровую информацию и/или контент, и любое подобное устройство, способное обеспечить однонаправленный или двунаправленный обмен контента между провайдерами контента и платформой 901 и/ дисплеем 945 через сеть 953 или напрямую. Следует иметь в виду, что контент может быть передан однонаправлено и/или в обоих направлениях в и из любого компонента в системе 900 и провайдер контента через сеть 953. Примеры контента могут включать в себя любую медиа информацию, включающую в себя, например, видео, музыку, медицинскую и игровую информацию и так далее.

Устройство (а) 948 предоставления услуги по передачи контента принимает контент, такой как информация программирования кабельного телевидения, включающая в себя медиа-информацию, цифровую информацию и/или другой контент. Примеры провайдеров контента могут включать в себя любые провайдеры, предоставляющие услуги кабельного или спутникового телевидения, или радио или интернет. Приведенные примеры не предназначены для ограничения вариантов осуществления раскрытого предмета изобретения.

В вариантах осуществления платформа 901 может принимать сигналы управления от навигационного контроллера 950, имеющий один или несколько навигационных признаков. Навигационные признаки навигационного контроллера 950 могут быть использованы для взаимодействия с пользовательским интерфейсом 954, например. В вариантах осуществления, навигационный контроллер 950 может представлять собой указывающее устройство, которое может быть компонентом компьютерной техники (специфическим устройством пользовательского интерфейса), что позволяет пользователю вводить пространственные (например, непрерывные и многомерные) данные в компьютер. Многие системы, такие как графический пользовательский интерфейс (GUI) и телевизоры и мониторы позволяют пользователю управлять и предоставлять данные в компьютер или телевизор, используя физические жесты.

Перемещения навигационных признаков навигационного контроллера 950 могут отображаться на дисплее (например, дисплей 945) в виде перемещения указателя, курсора, кольца фокусировки или другими визуальными индикаторами, отображаемые на дисплее. Например, под управлением программных приложений 951, навигационные признаки навигационного контроллера 950 могут быть отображены на виртуальных навигационных признаках, отображаемых на пользовательском интерфейсе 954. В вариантах осуществления навигационный контроллер 950 не может быть отдельным компонентом, но интегрированным в платформу 901 и/или дисплей 945. Варианты осуществления, однако, не ограничиваются элементами или в контекстом, показанными или описанными в данном документе.

В вариантах осуществления, драйверы (не показаны) могут включать в себя технологии, позволяющие пользователям мгновенно включать и выключать платформу 901, как телевизор, нажатием кнопки после первой загрузки при включении, например. Логика управления может позволить платформе 901 обеспечить потоковую передачу контента в медиа-адаптеры или другое устройство (а) 948 предоставления услуги по передачи контента или устройство (а) 949 доставки контента, когда платформа находится в положении "выкл". Кроме того, набор 903 микросхем может включать в себя схемы аппаратного оборудования и/или поддержки программного обеспечения для 5.1 пространственного звучания и/или высокой четкости 7.1 пространственного звучания, например. Драйверы могут включать в себя графический драйвер для интегрированных графических платформ. В вариантах осуществления, графический драйвер может включать в себя экспресс видеокарту взаимного соединения периферийных компонентов (PCI).

В различных вариантах осуществления один или более компонентов, показанных в системе 900, могут быть интегрированы. Например, платформа 901 и устройство (а) 948 предоставления услуги по передачи контента могут быть интегрированы или платформа 901 и или устройство (а) 949 доставки контента могут быть интегрированы, или платформа 901 устройство (а) 948 предоставления услуги по передачи контента и устройство (а) 949 доставки контента могут быть интегрированы, например. В различных вариантах осуществления платформа 901 и дисплей 945 может быть интегрированы. Дисплей 945 и устройство (а) 948 предоставления услуги по передачи контента могут быть интегрированы или дисплей 945 и устройство (а) 949 доставки контента могут быть интегрированы, например. Эти примеры не предназначены для ограничения раскрытого предмета изобретения.

В различных вариантах осуществления система 900 может быть реализована в виде системы беспроводной связи, проводной системы или их комбинации. При реализации в качестве беспроводной системы, система 900 может включать в себя компоненты и интерфейсы, подходящие для обмена по беспроводной связи общей медиа информацией, например, используя одну или несколько антенн, передатчиков, приемников, трансиверов, усилителей, фильтров, логических схем управления и так далее. Пример беспроводного совместно используемого носителя может включать в себя части беспроводного спектра, например, радиочастотный спектр и так далее. При реализации в виде проводной системы, система 900 может включать в себя компоненты и интерфейсы, подходящие для обеспечения связи через проводную среду связи, такие как адаптеры ввода/вывода, физические разъемы для подключения адаптера ввода/вывода с соответствующим проводным коммуникационным носителем, сетевой платой (NIC), дисковым контроллером, видеоконтроллером, аудио контроллером и так далее. Примеры проводной медиа коммуникации могут включать в себя провод, кабель, металлические провода, печатную плату (РСВ), объединительную панель, коммутационную матрицу, полупроводниковый материал, витую пару проводов, коаксиальный кабель, волоконно-оптический кабель и так далее.

Платформа 901 может установить один или несколько логических или физических каналов для передачи информации. Эта информация может включать в себя мультимедийную информацию и информацию управления. Медиа информации может относиться к любым данным, представляющие контент, предназначенный для пользователя. Примеры контента могут включать в себя, например, данные речевого разговора, видеоконференции, потоковое видео, сообщения электронной почты ("электронная почта"), сообщения голосовой почты, буквенно-цифровые символы, графику, изображения, видео, текст и так далее. Данные речевого разговора могут быть, например, речевой информацией, периодами молчания, фоновым шумом, комфортным шумом, тональным сигналом и так далее. Управляющая информация может относиться к любым данным, представляющие команды, инструкции или управляющие слова, которые предназначены для автоматизированной системы. Например, управляющая информация может быть использована для маршрутизации медиа информации по системе, или для подачи управляющей команды на узел для обработки мультимедийной информации в заданном порядке. Варианты осуществления, однако, не ограничиваются элементами или контекстом, показанными или описанными на фиг. 9.

Как описано выше, система 900 может быть воплощена в различных физических конструкциях или формах. Фиг. 10 иллюстрирует варианты осуществления конструктивного решения малоразмерного устройства 1000, в котором система 900 может быть реализована. В вариантах осуществления, например, устройство 1000 может быть реализовано в качестве мобильного вычислительного устройства, имеющее возможности осуществления беспроводной связи. Мобильное вычислительное устройство может относиться к любому устройству, имеющему систему обработки и мобильный источник питания, такой как один или несколько аккумуляторов, например.

Как описано выше, примеры мобильного устройства могут включать в себя персональный компьютер (PC), портативный компьютер, ультра-портативный компьютер, планшет, сенсорную панель портативного компьютера, портативный компьютер, карманный компьютер, персональный цифровой помощник (PDA), сотовый телефон, сочетание сотового телефона/PDA, телевизор, смарт-устройство (например, смартфон, смарт планшет или смарт-телевизор), мобильное интернет-устройство (MID), устройство управления сообщениями, устройство передачи данных и так далее.

Примеры мобильного устройства также могут включать в себя компьютеры, которые человек носит с собой, например, наручный компьютер, компьютер, находящийся на пальце пользователя, компьютер, установленный на кольце, который носит человек, компьютер, установленный в очках, компьютер, который носит пользователь на поясном ремне, компьютер, закрепленный на рукаве человека, на обуви на одежде и другие носимые компьютеры. В вариантах осуществления, например, мобильное вычислительное устройство может быть реализовано в виде смарт-телефона, способного выполнить компьютерные приложения, а также обеспечить голосовую связь и/или передачу данных. Хотя некоторые варианты осуществления изобретения могут быть описаны с помощью мобильного вычислительного устройства, реализованного в виде смарт-телефона в качестве примера, но очевидно, что другие варианты осуществления также могут быть реализованы с использованием других беспроводных мобильных вычислительных устройств. Варианты осуществления не ограничены в этом контексте.

Как показано на фиг. 10, устройство 1000 может включать в себя дисплей 1045, навигационный контроллер 1050, пользовательский интерфейс 1054, корпус 1055, устройство 1056 ввода/вывода и антенну 1057. Дисплей 1045 может включать в себя любое подходящее устройство отображения для отображения информации на мобильном вычислительном устройстве, и может быть таким же или аналогичным дисплею 945, показанному на фиг. 9. Навигационный контроллер 1050 может включать в себя один или несколько навигационных признаков, которые можно использовать для взаимодействия с пользовательским интерфейсом 1054, и может быть таким же, как или подобным навигационному контроллеру 950, показанному на фиг. 9. I/O устройство 1056 может включать в себя любое подходящее устройство ввода/вывода для ввода информации в мобильном вычислительном устройстве. Примеры устройства 1056 ввода/вывода могут включать в себя алфавитно-цифровую клавиатуру, цифровую клавиатуру, сенсорную панель, клавиши управления, кнопки, переключатели, клавишные переключатели, микрофоны, акустические системы, устройства распознавания голоса и программного обеспечения и так далее. Информация также может быть введена в устройство 1000 посредством микрофона. Такая информация может быть оцифрована с помощью устройства распознавания голоса. Варианты осуществления не ограничены в этом контексте.

Различные варианты осуществления изобретения могут быть реализованы с помощью аппаратных элементов, программных элементы или сочетанием того и другого. Примеры аппаратных элементов могут включать в себя процессоры, микропроцессоры, схемы, элементы схемы (например, транзисторы, резисторы, конденсаторы, катушки индуктивности и так далее), интегральные схемы специализированных интегральных схем (ASIC), программируемые логические устройства (PLD), процессоры цифрового сигнала (DSP), программируемую логическую матрицу (FPGA), логические шлюзы, регистры, полупроводниковые устройства, микросхемы, набор микросхем и так далее. Примеры программного обеспечения могут включать в себя программные компоненты, программы, приложения, компьютерные программы, прикладные программы, системные программы, машинные программы, программное обеспечение операционной системы, межплатформное программное обеспечения, встроенные программы, программные модули, процедуры, подпрограммы, функции, способы, процедуры, программные интерфейсы, интерфейсы прикладного программирования (API), наборы инструкций, вычислительный код, компьютерный код, сегменты кода, сегменты компьютерного кода, слова, значения, символы или любой их комбинации. Определение способа реализации варианта осуществления с помощью аппаратных элементов и/или программным элементов может различаться в соответствии с любым количеством факторов, таких как желаемая вычислительная скорость, уровень мощности, величина теплового допуска, бюджета цикла обработки, скорость входных данных, скорость передачи выходных данных, ресурса памяти, скорости передачи данных шины и другие конструктивные или функциональные ограничения.

Один или более аспектов, по меньшей мере, один вариант осуществления может быть реализован с помощью команд, сохраненных на машиночитаемом носителе, который представляет собой различные логические процессы в процессоре, который при считывании машиной вызывает машину выполнить логические процессы для выполнения способов, описанных в данном документе. Такие примеры, известные как "IP-ядра», могут храниться на материальном, машиночитаемом носителе и поставляться различным пользователям или производственным предприятиям для загрузки в машины, которые фактически выполняют логические процессы или процессор. Некоторые варианты осуществления могут быть реализованы, например, с использованием машинно-считываемого носителя или изделия, которое может хранить инструкции или набор инструкций, которые, если выполняется машиной, может вызвать машину для выполнения способа и/или действия в соответствии с вариантов осуществления. Такая машина может включать в себя, например, любую подходящую платформу обработки, вычислительную платформу, вычислительное устройство, устройство обработки данных, вычислительную систему, систему обработки данных, компьютер, процессор или тому подобное, и может быть реализована с использованием любой подходящей комбинации аппаратных средств и/или программного обеспечения. Машиночитаемый носитель или изделие может включать в себя, например, любой подходящий тип запоминающего устройства, устройство памяти, память, носитель памяти, устройства хранения данных, изделие для хранения информации, носитель данных и/или блок хранения, например, память, съемные или несъемные носители, стираемые или нестираемых носители медиа-информации, записываемые или повторно записываемые медиа, цифровые или аналоговые медиа, жесткий диск, дискету, компакт-диск только для чтения (CD-ROM), компакт-диск записываемый (CD-R), компакт-диск перезаписываемый (CD-RW), оптический диск, магнитные носители, магнитооптические носители, съемные карты памяти или диски, различные виды цифрового универсального диска (DVD), ленточные накопителя, кассеты и т.п. Команды могут включать в себя любой подходящий тип кода, например, исходный код, скомпилированный код, интерпретируемый код, исполняемый код, статический код, динамический код, зашифрованный код и т.п., которые реализуются с помощью любого подходящего высокого уровня, низкого уровня, объектно-ориентированного, визуального, согласованного и/или интерпретируемого языка программирования.

Следующие примеры относятся к дополнительным вариантам осуществления:

Пример 1 представляет собой устройство транзакций памяти, содержащее: элемент процессора; исполнительный компонент для исполнения элементом процессора параллельного выполнения программной транзакции и аппаратной транзакции в соответствии с процессом транзакционной памяти; компонент отслеживания для исполнения элементом процессора активирования глобальной блокировки для указания выполнения процесса программной транзакции; и компонент завершения для исполнения элементом процессора завершить программную транзакцию и деактивирования глобальной блокировки при завершении исполнения программной транзакции, компонент завершения прерывает аппаратную транзакцию, когда глобальная блокировка активна при завершении выполнения аппаратной транзакции.

В примере 2, исполнительный компонент, описанный в примере 1, возможно может предназначаться для исполнения элементом процессора для параллельного выполнения программной транзакции, аппаратной транзакции и второй аппаратной транзакции.

В примере 3, компонент завершения любого одного из примеров 1 или 2 возможно может быть предназначен для исполнения элементом процессора завершения аппаратной транзакции, когда глобальная блокировка неактивна, при выполнении завершения аппаратной транзакции.

В примере 4, устройство транзакционной памяти по любому из примеров 1-3 возможно может содержать компонент обработчика прерывания для выполнения элементом процессора определения фазы выполнения для повторного выполнения аппаратной транзакции, когда аппаратная транзакция прерывается.

В примере 5, компонент обработчика прерывания, описанный в примере 4, возможно может быть предназначен для исполнения элементом процессора подачи команды исполнительному компоненту повторно выполнить аппаратную транзакцию в программной фазе, когда определено, что аппаратная транзакция не была прервана из-за конфликта с другой транзакцией.

В примере 6, компонент обработчика прерывания по любому одному из примеров 4 и 5 возможно может быть предназначен для исполнения элементом процессора определения фазы выполнения для повторного выполнения аппаратной транзакции путем сравнения значения счетчика повторных попыток с одним или несколькими пороговыми значениями повторных попыток.

В примере 7, исполнительный компонент по любому из примеров 1-6 возможно может быть предназначен для исполнения элементом процессора выполнения аппаратной транзакции в первой аппаратной фазе, когда значение счетчика повторных попыток меньше порогового значения повтора для первой аппаратной фазы, и выполнения аппаратной транзакции во второй аппаратной фазе, когда значение счетчика повторных попыток больше или равно пороговому значению повтора для первой аппаратной фазы, но меньше, чем пороговое значение повторных попыток для второй аппаратной фазы.