Настоящее изобретение относится к области процессорных режимов выполнения, в частности к запросу блокировки выполнения участков кода.

УРОВЕНЬ ТЕХНИКИ

Достижения в проектировании полупроводниковых вычислителей и логических элементов позволили увеличить количество логических элементов, которое может быть размещено на интегральных схемах устройств. В результате конфигурации компьютерных систем эволюционировали от одиночных или нескольких интегральных схем к системам с несколькими ядрами и несколькими логическими процессорами, размещенными на отдельных интегральных схемах. Процессор или интегральная схема обычно содержит единственный процессорный кристалл, который может включать в себя несколько ядер или логических процессоров.

Неуклонно возрастающее количество ядер и логических процессоров на интегральных схемах позволяет выполнять большее количество потоков программ. Однако рост числа потоков программ, которые можно выполнять одновременно, создал проблемы синхронизации данных, коллективно используемых потоками программ. Одно из типичных решений доступа к коллективно используемым данным в системах с несколькими ядрами или несколькими логическими процессорами включает в себя использование блокировок для гарантирования взаимного исключения нескольких доступов к коллективно используемым данным. Однако неуклонно возрастающая способность к выполнению нескольких потоков программ приводит к ложным конфликтам и неправильной сериализации выполнения.

Например, рассмотрим хеш-таблицу, содержащую коллективно используемые данные. Используя систему блокировки, программист может заблокировать всю хеш-таблицу целиком, при этом доступ ко всей хеш-таблице позволяется осуществлять одному потоку. Однако это потенциально может сказаться неблагоприятным образом на производительности и характеристиках других потоков, поскольку они не смогут получить доступ ни к одной из записей хеш-таблицы до снятия блокировки. В качестве альтернативы может быть заблокирована каждая запись таблицы. Однако это увеличивает сложность программирования, поскольку программистам приходится принимать во внимание большее количество блокировок внутри хеш-таблицы.

Другая методика синхронизации данных включает в себя использование транзакционной памяти (TM). Часто транзакционное выполнение включает в себя интеллектуальное выполнение группы из множества микроопераций, операций или команд. В вышеприведенном примере оба потока выполняются в хеш-таблице и их доступ контролируется/отслеживается. Если оба потока осуществляют доступ к одной и той же записи/изменяют одну и ту же запись, то для разрешения конфликта одна из транзакций может быть прекращена. Однако в некоторых приложениях преимущество программирования транзакционной памяти может не использоваться, при этом для пропуска блокировок с целью извлечения преимуществ, аналогичных преимуществам использования транзакционной памяти, применяется методика синхронизации, часто называемая пропуском аппаратной блокировки (HLE).

В результате, методика HLE способна определить и предсказать критические участки кода. Однако при выполнении критического участка для транзакционной памяти или посредством HLE, в случае если предсказание HLE является неверным, при отслеживании предварительного доступа происходит переполнение памяти или встречается неотменяемое событие, то критический участок прерывается или перезапускается. Однако прерывание критического участка потенциально может приводить к потере циклов выполнения для операции, выполненной до прерывания.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Иллюстрации представленного изобретения приведены в качестве примера, при этом не предполагается, что прилагаемые чертежи ограничивают изобретение.

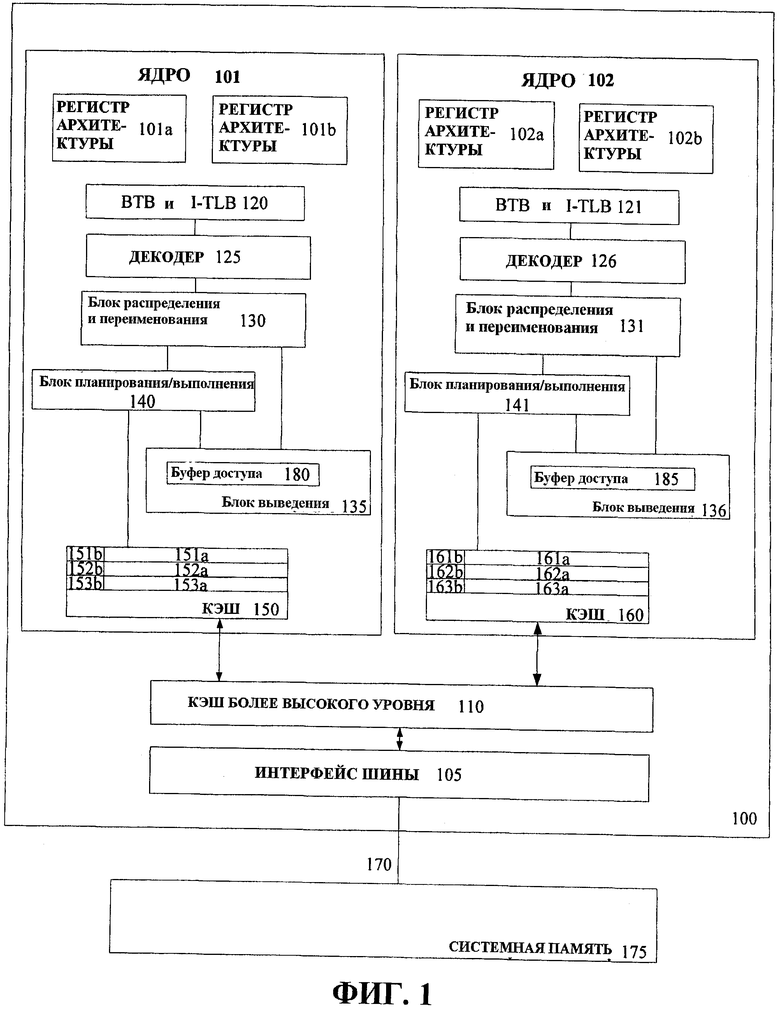

На Фигуре 1 проиллюстрирован вариант осуществления мультипроцессорного элемента, включающего в себя механизм запроса поздней блокировки.

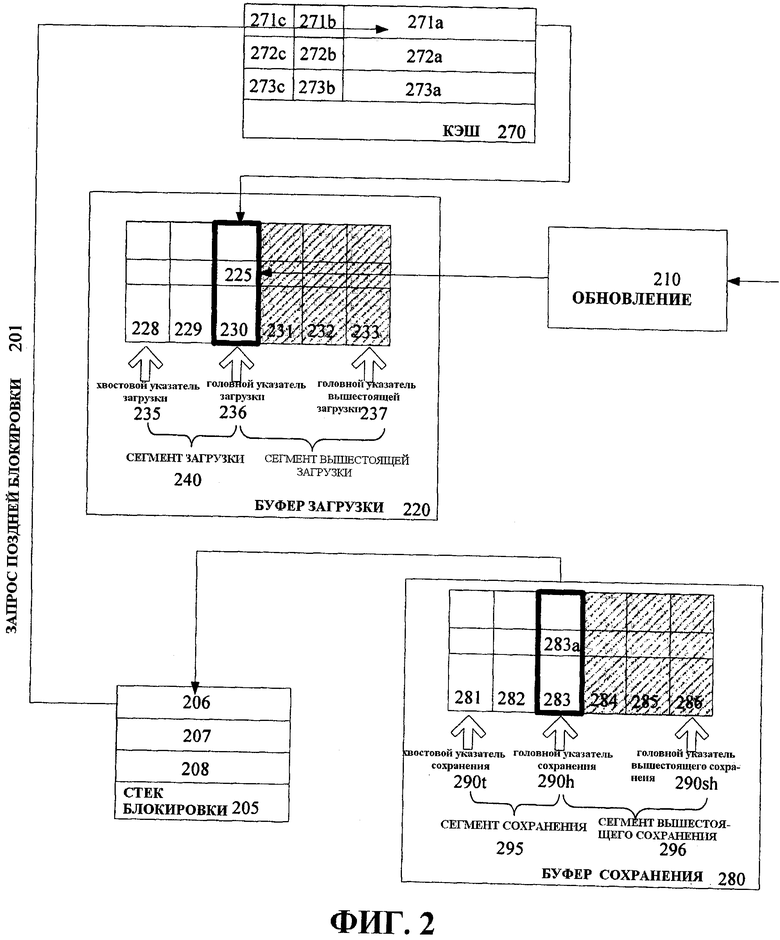

На Фигуре 2 проиллюстрирован вариант осуществления логического узла для осуществления запроса поздней блокировки для критического участка.

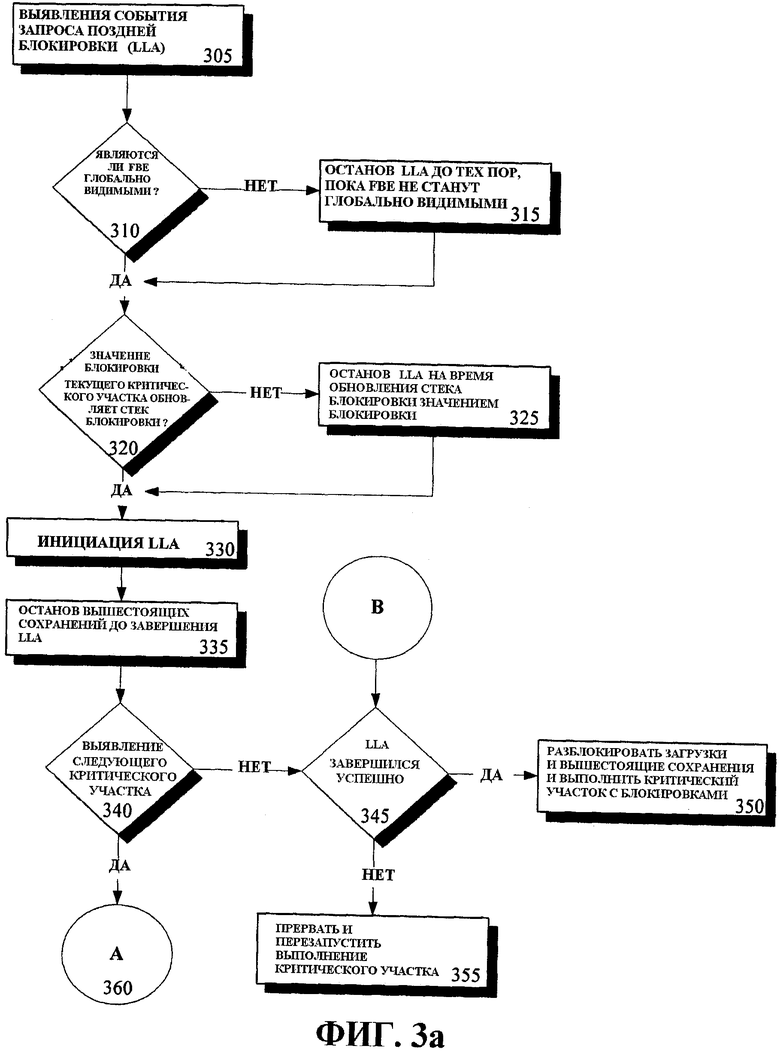

На Фигуре 3a проиллюстрирован вариант осуществления структурной схемы способа запроса поздней блокировки для текущего критического участка.

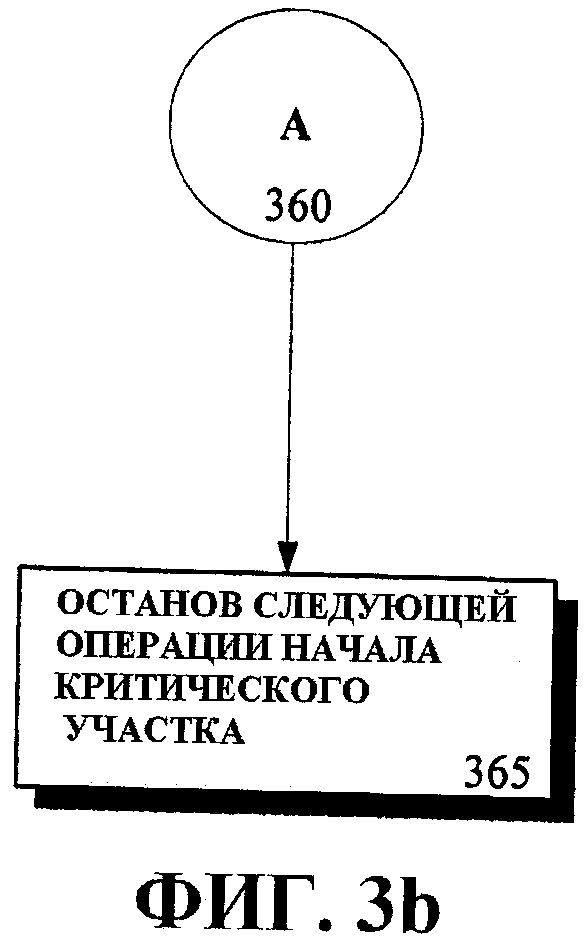

На Фигуре 3b проиллюстрирован вариант осуществления структурной схемы способа останова операций по следующему критическому участку во время запроса поздней блокировки для текущего критического участка.

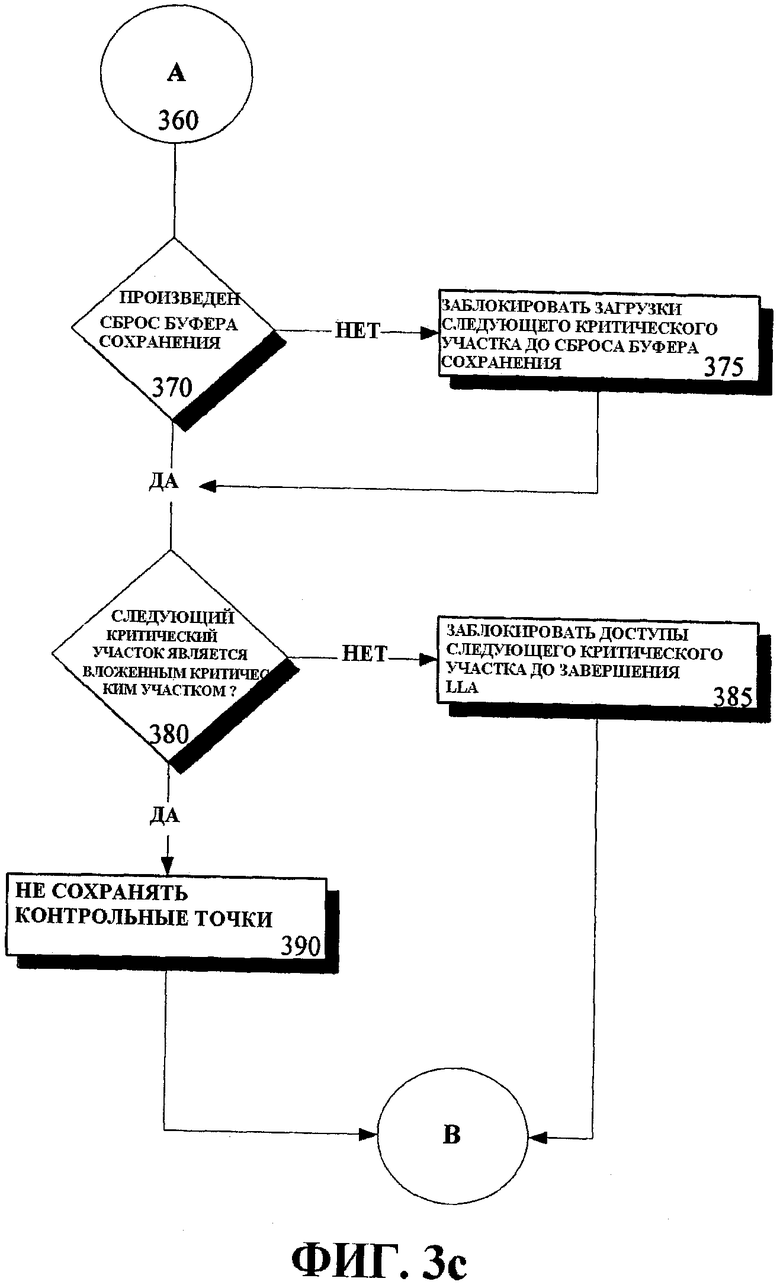

На Фигуре 3c проиллюстрирован другой вариант осуществления структурной схемы способа останова операций по следующему критическому участку во время запроса поздней блокировки для текущего критического участка.

ПОДРОБНОЕ ОПИСАНИЕ

В нижеприведенном описании изложены многочисленные характерные детали, такие как примеры аппаратной поддержки пропуска аппаратной блокировки (HLE), характерные способы разметки метаданных, характерные типы локальной памяти в процессорах, характерные типы размещения в памяти и доступа к ней и т.д. с целью обеспечения досконального понимания представленного изобретения. Однако специалисту в данной области техники будет ясно, что эти характерные детали необязательно использовать для применения представленного изобретения. В других случаях хорошо известные компоненты или способы, такие как кодирование критических участков в программном обеспечении, установление границ критических участков, характерные архитектуры многоядерных и многопоточных процессоров, генерация/обработка прерываний, организация кэша, и конкретные детали функционирования микропроцессоров не описывались подробно во избежание чрезмерного усложнения представленного изобретения.

Способ и устройство, описанные в данном документе, предназначены для схемы запроса поздней блокировки при выполнении критических участков. Конкретно схема запроса поздней блокировки в основном обсуждается в отношении компьютерных систем с многоядерным процессором. Однако способы и устройство для схемы запроса поздней блокировки не ограничиваются вышеуказанным, поскольку они могут быть реализованы на или совместно с устройством или системой с интегральной схемой, такими как сотовые телефоны, персональные цифровые органайзеры, встроенные контроллеры, мобильные платформы, платформы для настольных станций и серверные платформы, а также совместно с другими ресурсами, такими как аппаратные/программные потоки, которые выполняют критические участки. Кроме того, схема запроса поздней блокировки также в основном обсуждается в отношении выполнения критических участков во время пропуска аппаратной блокировки. Однако запрос поздней блокировки может применяться для любой схемы выполнения критических участков, например, при транзакционном выполнении.

На Фигуре 1 приведена иллюстрация варианта осуществления многоядерного процессора 100, который способен производить запрос поздней блокировки для критического участка. Как показано на фигуре, процессор 100 содержит произвольное число процессорных элементов. Процессорным элементом может являться поток, процесс, контекст, логический процессор, аппаратный поток, ядро и/или любой процессорный элемент, который, потенциально, использует коллективный доступ к ресурсам процессора, таким как элементы резервирования, элементы выполнения, каналы информации и кэш/память более высокого уровня. Физическим процессором, как правило, называется интегральная схема, которая может содержать произвольное число процессорных элементов, таких как ядра и аппаратные потоки.

Ядром часто называют логический элемент, находящийся на интегральной схеме, способный поддерживать независимое состояние архитектуры, при этом каждое независимо поддерживаемое состояние архитектуры связано с, по меньшей мере, несколькими выделенными ресурсами выполнения. В отличие от ядер, аппаратным потоком обычно называется логический элемент, расположенный на интегральной схеме, способный поддерживать независимое состояние архитектуры, при этом независимо поддерживаемое состояние архитектуры использует коллективный доступ к ресурсам выполнения. Физический процессор 100, как проиллюстрировано на Фигуре 1, содержит два ядра, ядра 101 и 102, которые имеют общий доступ к кэшу более высокого уровня 110. Кроме того, ядро 101 содержит два аппаратных потока 101a и 101b, тогда как ядро 102 содержит два аппаратных потока 102a и 102b. Следовательно, программные сущности, такие как операционная система или приложения, потенциально рассматривают процессор 100 как четыре отдельных процессора, при этом процессор 100 может выполнять четыре программных потока.

Как можно видеть, в случае, когда определенные ресурсы используются коллективно, а другие являются выделенными для состояния архитектуры, граница между терминами «аппаратный поток» и «ядро» размывается. Даже чаще ядро и аппаратный поток рассматриваются операционной системой как отдельные логические процессоры, при этом операционная система может отдельно запланировать операции для каждого логического процессора. Следовательно, процессорный элемент включает в себя любую из вышеупомянутых сущностей, способных к поддержанию контекста, например ядра, потоки, аппаратные потоки, логические процессоры, виртуальные машины или другие ресурсы обработки.

В одном из вариантов осуществления процессор 100 является многоядерным процессором, способным к параллельному выполнению нескольких потоков. Здесь первый поток связан с регистрами состояния архитектуры 101a, второй поток связан с регистрами состояния архитектуры 101b, третий поток связан с регистрами состояния архитектуры 102a, и четвертый поток связан с регистрами состояния архитектуры 102b. Упоминание процессорных элементов процессора 100 в одном из вариантов осуществления относится к ядрам 101 и 102, а также к потокам 101a, 101b, 102a и 102b. В другом варианте осуществления термин «процессорный элемент» относится к элементам одного уровня иерархии домена обработки. Например, ядра 101 и 102 находятся на одном и том же доменном уровне, потоки 101a и 101b находятся на одном и том же доменном уровне в ядре 101, и потоки 101a, 101b, 102a и 102b находятся на одном и том же доменном уровне в ядрах 101 и 102.

Хотя процессор 100 может содержать асимметричные ядра, то есть ядра с различной конфигурацией, функциональные блоки и/или логические элементы, на Фигуре 1 показаны симметричные ядра. В результате ядро 102, которое по иллюстрации является идентичным ядру 101, не будет подробно рассматриваться в целях упрощения обсуждения.

Как видно из иллюстрации, регистры состояния архитектуры 101a дублируются в регистрах состояния архитектуры 101b, таким образом, имеется возможность хранения отдельных архитектурных состояний/контекстов для процессорного элемента 101a и процессорного элемента 101b. Более мелкие ресурсы, такие как указатели команд и логический элемент переименования в логическом элементе распределения и переименования 130, также могут дублироваться для потоков 101a и 101b. Некоторые ресурсы, такие как переупорядочивающие буферы в блоке переупорядочивания/выведения 135, ILTB 120, буферы загрузки/хранения 180, и очереди могут совместно использоваться посредством разбиения на разделы. Другие ресурсы, такие как внутренние регистры общего назначения, базовый регистр таблицы страницы, низкоуровневый кэш данных и данные буфера TLB 110, блок(-и) выполнения 140 и блок внеочередного выполнения 135, потенциально могут быть совместно использованы целиком. Следует отметить, что поток может быть реализован посредством любого способа организации коллективного доступа к ресурсам ядра 101.

Модуль интерфейса шины 105 должен взаимодействовать с внешними по отношению к процессору 100 устройствами, такими как системная память 175, чипсет, северный мост, или другой интегральной схемой. Память 175 может быть выделена для процессора 100 или находиться в коллективном пользовании с другими устройствами системы. В качестве примеров памяти 175 выступает динамическая оперативная память (DRAM), статическая оперативная память (SRAM), постоянная память (ПЗУ) и долговременное хранилище.

Обычно модуль интерфейса шины 105 содержит буферы ввода/вывода (I/O) для передачи и получения сигналов шины на внутреннее соединение 170. Примеры внутреннего соединения 170 включают в себя шину приемопередатчиков (GTL), шину GTL+, шину с удвоенной скоростью передачи данных (DDR), насосную шину, дифференциальную шину, шину с кэш-когерентностью, сквозную шину, многоточечную шину или другое известное внутреннее соединение, реализующее любой известный протокол шины. Как показано, модуль интерфейса шины 105 также должен взаимодействовать с кэшем более высокого уровня 110.

Кэш более высокого уровня или более отдаленный кэш 110 предназначен для кэширования недавно вызванных и/или выполненных элементов. Следует отметить, что термины «более высокого уровня» и «более отдаленный» относятся к возрастанию или удалению уровней кэша от блока(-ов) выполнения. В одном из вариантов осуществления кэш более высокого уровня 110 является кэшем данных второго уровня. Однако кэш более высокого уровня 110 не ограничивается данным примером, поскольку он может являться кэшем команд или содержать его, при этом он также может называться кэшем трассировки. Кэш трассировки может быть вместо этого присоединен после декодера 125 с целью хранения недавно декодированных трассировок. Модуль 120 также потенциально содержит буфер адресов ветвлений для предсказания ветвлений, которые должны быть выполнены/взяты, и буфер трансляции команд (I-TLB) для хранения записей преобразования адресов для команд. В этом случае процессор, способный к интеллектуальному выполнению, потенциально осуществляет предварительную выборку и интеллектуально выполняются предсказанные ветвления.

Модуль декодирования 125 присоединяется к блоку вызова 120 с целью декодирования вызванных элементов. В одном из вариантов осуществления процессор 100 связан со структурой системы команд (ISA), которая определяет/задает команды, выполнимые на процессоре 100. Здесь команды машинного кода, распознанные ISA, часто содержат часть команды, называемую кодом операции, которая дает ссылку на/задает команду или операцию, которая должна быть выполнена.

В одном из примеров блок распределения и переименования 130 содержит распределитель для резервирования ресурсов, таких как файлы регистров, для хранения результатов обработки команд. Однако потоки 101a и 101b имеют потенциальную возможность внеочередного выполнения, при этом блок распределения и переименования 130 также резервирует другие ресурсы, такие как переупорядочивающие буферы, для трассировки результатов команд. Блок 130 также может содержать узел переименования регистров, предназначенный для переименования регистров ссылок на программу/команду в другие регистры, являющиеся внутренними по отношению к процессору 100.

Блок переупорядочивания/выведения 135 содержит такие компоненты, как вышеупомянутые переупорядочивающие буферы и буферы загрузки/хранения 180, предназначенные для поддержки внеочередного выполнения и последующего выведения команд, выполненных вне очереди. В одном из вариантов осуществления в буферах 180 могут храниться поля/значения для указания того, что связанные доступы к памяти должны быть заблокированы/остановлены до тех пор, пока не завершится запрос поздней блокировки для критического участка. Хотя показано, что буферы 180 размещены в одной области, это не является обязательным для буферов 180 и логического элемента запроса поздней блокировки. В действительности, логика трассировки 180 может быть распределена посредством процессора 100, а также может быть ассоциирована с любой частью процессорного конвейера фронтального или постпроцессора.

Блок узла(-ов) планирования и выполнения 140 в одном из вариантов осуществления содержит планировщик для распределения команд/операций по узлам выполнения. В действительности, команды/операции потенциально распределяют по узлам выполнения в соответствии с доступностью их типов. Например, команда с использованием плавающей точки распределяется на порт узла выполнения, в котором имеется доступный узел выполнения операций с плавающей точкой. Файлы регистров, связанные с узлами выполнения, также включаются для хранения результатов обработки информации команды. Приведенные в качестве примера узлы выполнения содержат узел выполнения с плавающей точкой, узел целочисленного выполнения, узел выполнения перехода, узел выполнения загрузки, узел выполнения сохранения и другие известные узлы выполнения.

Исходя из вышеописанного, следует отметить, что, как показано на иллюстрации, процессор 100 может одновременно выполнять по меньшей мере четыре программных потока. Кроме того, в одном из вариантов осуществления процессор 100 может осуществлять транзакционное выполнение. Транзакционное выполнение обычно включает в себя группирование множества команд или операций в транзакцию, элементарный участок кода или критический участок кода. В некоторых случаях слово «команда» относится к макрокоманде, составленной из множества операций. В процессоре транзакция, как правило, выполняется интеллектуально и завершается после окончания транзакции. В данном документе неопределенность транзакции относится к транзакции, выполнение которой было начато и не было завершено или прервано, то есть ожидающей обработки. Обычно во время, когда транзакция все еще ожидает обработки, производится трассировка адресов, загружаемых или записываемых в пределах памяти.

После успешной проверки этих адресов памяти, транзакция завершается, и обновления, произошедшие во время транзакции, становятся видимыми глобально. Однако, если транзакция объявлена недействительной во время ожидания обработки, то транзакция перезапускается, при этом обновления не становятся видимыми глобально. Часто для идентификации транзакции в код включается программное разграничение. Например, транзакции могут быть сгруппированы по командам, указывающим начало транзакции или окончание транзакции. Однако при транзакционном выполнении для вставки команд начала и окончания транзакции часто используются программаторы или компиляторы.

Таким образом, в одном из вариантов осуществления процессор 100 может выполнять пропуск аппаратной блокировки (HLE), при этом аппаратное обеспечение может пропускать блокировки для критических участков и выполнять их одновременно. Здесь пре-компилированные двоичные файлы без транзакционной поддержки или вновь скомпилированные двоичные файлы, для которых применяется программирование с блокировкой, могут получать преимущество от одновременного выполнения посредством поддержки HLE. Как следствие обеспечения явной совместимости, HLE часто включает в себя аппаратное обеспечение для определения критических участков и трассировки доступа к памяти. В действительности, поскольку блокировки, обеспечивающие исключение данных, пропускаются, то доступ к памяти может трассироваться таким же образом, как при выполнении транзакций. Таким образом, схема запроса поздней блокировки, обсуждаемая в данном документе, может применяться для транзакционного выполнения, HLE, другой схемы трассировки доступа к памяти, или их комбинации. Следовательно, нижеприведенное обсуждение выполнения критических участков потенциально содержит ссылку на критический участок транзакции или критический участок, определенный посредством HLE.

В одном из вариантов осуществления устройство памяти, к которому осуществляется доступ, применяется для трассировки доступа к критическому участку. Например, кэш данных низкого уровня 150 применяется для трассировки доступа к критическим участкам, связанным с транзакционным выполнением или HLE. В кэше 150 должны храниться элементы, к которым недавно осуществлялся доступ, такие как операнды, хранимые в памяти, и которые потенциально хранятся в когерентных состояниях памяти, таких как состояния изменения, исключения, коллективного доступа и неисправности (MESI). Кэш 150 может быть организован как полностью ассоциативный, модульно-ассоциативный, кэш прямого отображения или иметь другую известную организацию кэша. Хотя это не представлено на иллюстрации, D-TLB может быть ассоциирован с кэшем 150 с целью хранения последних преобразований адресов из виртуальных/линейных в физические.

Согласно иллюстрации строки 151, 152 и 153 содержат сегменты и поля, например сегмент 151a и поле 151b. В одном из вариантов осуществления поля 151b, 152b и 153b и сегменты 151a, 152a и 153a являются частью одного массива памяти, составляющего строки 151, 152 и 153. В другом варианте осуществления поля 151b, 152b и 153b являются частью отдельного массива, доступ к которому должен осуществляться через отдельные выделенные порты из строк 151a, 152a и 153a. Однако, даже когда поля 151b, 152b и 153b являются частью отдельного массива, поля 151b, 152b и 153b ассоциированы с сегментами 151a, 152a и 153a соответственно. В результате при ссылке на строку 151 кэша 150 строка 151 потенциально содержит сегмент 151a, 151b или их комбинацию. Например, при загрузке из строки 151, может осуществляться загрузка сегмента 151a. Кроме того, при задании поля трассировки для трассировки загрузки из строки 151 может осуществляться доступ к полю 151b.

В одном из вариантов осуществления строки, ячейки, сегменты или слова, например строки 151a, 152a и 153a, могут хранить несколько элементов. Элемент может являться любой командой, операндом, хранимым в памяти операндом, переменной или другой группой логических значений, обычно хранимых в памяти. В качестве примера строка 151 кэша содержит четыре элемента в сегменте 151a, например четыре операнда. Элементы, хранящиеся в строке кэша 151a, могут находиться в упакованном или сжатом состоянии, а также в несжатом состоянии. Кроме того, элементы могут храниться в кэше 150 выровненными или невыровненными относительно границ строк, множеств или маршрутов кэша 150.

Память 150 будет подробнее обсуждаться ниже со ссылкой на нижеприведенные примеры вариантов осуществления.

Кэш 150, так же как и другие элементы и узлы процессора 100, хранит и/или осуществляет операции с логическими значениями. Часто использование логических уровней и логических значений описывается единицами и нулями, представляющими состояния бинарной логики. Например, 1 относится к высокому логическому уровню, и 0 относится к низкому логическому уровню. В компьютерных системах также применялись другие представления значений, например десятичное или шестнадцатеричное представление логических значений или бинарных значений. Например, возьмем десятичное число 10, которое представляется в бинарных величинах как 1010 и в шестнадцатеричной системе как буква A.

В варианте осуществления, проиллюстрированном на Фигуре 1, доступ к строкам 151, 152 и 153 трассируется для поддержки выполнения критических участков. Доступ включает в себя операции, такие как чтение, запись, сохранение, загрузка, откачка, слежение или другие известные виды доступа к ячейкам памяти. Поля трассировки доступа, такие как поля 151b, 152b и 153b, используются для трассировки доступа к соответствующим им строкам памяти. Например, строка/сегмент памяти 151a ассоциирована с соответствующим полем трассировки 151b. Здесь поле трассировки доступа 151b ассоциировано и соответствует строке кэша 151a, поскольку поле трассировки 151b содержит биты, которые являются частью строки кэша 151. Ассоциирование может достигаться посредством физического размещения, как было проиллюстрировано, или другим способом, например соотнесением или отображением поля трассировки доступа 151b со строкой памяти 151a или 151b в аппаратной или программной поисковой таблице.

В качестве упрощенного иллюстративного примера предположим, что поля трассировки доступа 151b, 152b и 153b содержат два транзакционных бита: первый бит чтения трассировки и второй бит записи трассировки. В состоянии по умолчанию, то есть при первом логическом значении, первой и второй биты в полях трассировки доступа 151b, 152b и 153b указывают на то, что к строкам кэша 151, 152 и 153 соответственно не осуществлялся доступ при выполнении критического участка.

Предположим, что операция загрузки для загрузки из строки 151a была обнаружена в критическом участке. Первый бит чтения трассировки обновляется из состояния по умолчанию во второе состояние осуществленного доступа, соответствующее второму логическому значению. Здесь первый бит чтения трассировки, несущий второе логическое значение, показывает, что при выполнении критического участка происходило чтение/загрузка из строки кэша 151. Операция сохранения может проводиться аналогичным образом для обновления первого бита записи трассировки с целью указания того, что при выполнении критического участка происходило сохранение в ячейку памяти.

Таким образом, в случае если осуществляется проверка битов трассировки в поле 151b, связанных со строкой 151, и биты трассировки находятся в состоянии по умолчанию, то к строке кэша 151 не осуществлялся доступ во время ожидания обработки критического участка. И наоборот, если первый бит чтения трассировки имеет второе значение, то ранее при выполнении критического участка осуществлялось чтение строки кэша 151. Кроме того, если первый бит записи трассировки имеет второе значение, то во время ожидания обработки критического участка осуществлялась запись в строку 151. Поля доступа 151b, 152b и 153b потенциально используются для поддержки любого типа транзакционного выполнения или HLE. В одном из вариантов осуществления, в котором процессор 100 может осуществлять транзакционное выполнение, поля доступа 151b, 152b и 153b должны выявлять конфликты и осуществлять проверку правильности. В другом варианте осуществления, в котором аппаратная транзакционная память (HTM), программная транзакционная память (STM) или гибридная память, состоящая из вышеуказанного, применяется для транзакционного выполнения, поля трассировки доступа 151b, 152b и 153b обеспечивают выполнение аналогичных функций трассировки и проверки.

В качестве первого примера того, каким образом поля доступа и, конкретно, биты трассировки потенциально могут использоваться для способствования транзакционному выполнению, в совместно-поданной заявке на патент США, озаглавленной "Аппаратное ускорение для системы программной транзакционной памяти" с серийным номером 11/349,787 описывается использование полей доступа/транзакционных битов для ускорения STM. В качестве другого примера, расширяющая/виртуализирующая транзакционная память, включающая в себя хранение состояний полей доступа/битов трассировки транзакции во второй памяти, обсуждается в совместно-поданной заявке на патент США, озаглавленной "Способ глобального переполнения для виртуализированной транзакционной памяти" с серийным номером 11/479,902 и номером дела поверенного 042390.P23547.

На Фигуре 2 проиллюстрирован вариант осуществления логического узла для запуска запроса поздней блокировки для критического участка. Как было указано выше, транзакция часто разграничивается посредством команд начала и завершения транзакции, что позволяет легко идентифицировать критические участки. Однако HLE включает в себя определение/идентификацию и потенциальное предсказание критических участков, пропуск блокировок, разграничивающих критические участки, создание контрольных точек состояний регистров для отката после прерывания критического участка, трассировку предварительных обновлений памяти, и выявление потенциальных конфликтов данных. Одна из сложностей определения/идентификации критических участков заключается в разделении команд регулярных блокировок, которые не определяют критические участки, и команд блокировок/снятия блокировок, которые разграничивают критические участки.

В одном из вариантов осуществления для HLE критический участок определяется посредством команды блокировки, то есть командой начала критического участка и соответствующей командой снятия блокировки, то есть командой завершения критического участка. Команда блокировки может включать загрузку из ячейки адреса, то есть проверку, доступна ли блокировка, и изменения/записи в ячейку адреса, то есть обновление ячейки адреса с целью запроса блокировки. Некоторые примеры команд, которые могут использоваться в качестве команд блокировки, включают в себя команду сравнения и обмена, команду проверки и установки битов и команду обмена и добавления. В наборах команд компании Intel IA-32 и IA-64 вышеупомянутые команды включают в себя CMPXCHG, BTS и XADD в соответствии с документами по множествам команд Intel® 64 и IA-32, которые обсуждались выше.

В качестве примера, где предварительно определенные команды, такие как CMPXCHG, BTS и XADD, выявляются/распознаются, логический узел выявления и/или логический узел декодирования выявляет команды, использующие поле кода операции или другое поле команды. Приведем пример - CMPXCHG связана со следующими кодами операций: 0F B0/r, REX + 0F B0/r и REX.W+0F B1/r. В другом варианте осуществления операции, связанные с командой, используются для выявления команды блокировки. Например, в x86 для осуществления элементарного обновления памяти, указывающего на потенциальную команду блокировки, часто используются следующие три микрооперации: (1) Load_Store_Intent (L_S_I) с кодом операции 0x63; (2) STA с кодом операции 0x76; и (3) STD с кодом операции 0x7F. Здесь L_S_I получает ячейку памяти в состоянии исключительного права собственности и производит чтение ячейки памяти, тогда как операции STA и STD изменяют ячейку памяти и осуществляют запись в нее. Другими словами, логический узел выявления ищет загрузку с целью сохранения (L_S_I) для определения начала критического участка. Следует отметить, что команды блокировки могут иметь любое число других операций как с памятью, так и с не-памятью, связанных с операциями чтения, записи и изменения памяти.

Часто стек, например стек блокировок 205, используется для хранения записи, такой как запись 206, которая ассоциирована с командой блокировки. Запись команды блокировки (LIE) 206 может содержать произвольное количество полей для хранения информации, относящейся к критическим участкам, такой как физический адрес хранилища команд блокировки (LI Str PA), значение и размер загрузки команды блокировки, разблокированное значение, значение и размер хранилища команд блокировки, заблокированное значение, счетчик микроопераций, флаг снятия, флаг запроса поздней блокировки и поле указателя последней команды.

Здесь команда снятия блокировки, соответствующая команде блокировки, обозначает конец критического участка. Логический узел выявления осуществляет поиск команды снятия блокировки, соответствующей адресу, измененному командой блокировки. Следует отметить, что адрес, измененный командой блокировки, может находиться в LIE 206 в стеке блокировки 205. В результате в одном из вариантов осуществления команда снятия блокировки включает в себя любую операцию сохранения, которая устанавливает адрес, измененный соответствующей командой блокировки, обратно на незаблокированное значение. Адрес, на который ссылается команда L_S_I, хранящийся в стеке блокировки 206, сравнивается с последующими командами сохранения с целью выявления соответствующей команды снятия блокировки. Более подробную информацию о выявлении и предсказании критических участков можно найти в совместно-поданной заявке на патент США, озаглавленной "Механизм выявления и предсказания критических участков для пропуска аппаратной блокировки", серийный номер заявки 11/599,009.

Другими словами, при использовании HLE, в одном из вариантов осуществления критический участок разграничивается командой L_S_I и соответствующей командой сохранения снятия блокировки. Аналогично, критический участок транзакции определяется командой начала транзакции и командой окончания транзакции. Таким образом, ссылка на команду/операцию начала критического участка включает в себя любую команду, запускающую HLE, транзакционную память, или другой критический участок, тогда как ссылка на команду/операцию окончания критического участка включает в себя запуск HLE, транзакционную память или другие команды окончания критического участка.

В одном из вариантов осуществления буфер доступа, например буфер загрузки 220 и/или буфер хранения 280, используется для хранения записей доступа, связанных с операциями доступа к памяти. Каждая запись буфера доступа содержит поле/сегмент кода блока. По умолчанию поле кода блока предназначено для хранения первого значения, например незаблокированного значения, для указания, что соответствующая операция доступа к памяти является свободной для размещения. Однако, когда инициируется запрос поздней блокировки для текущего критического участка, поля кода блока для записей буфера, связанных со следующим критическим участком, обновляются и получают второе значение или заблокированное значение для указания того, что связанные операции доступа к памяти должны быть заблокированы/остановлены.

Как показано на иллюстрации, буфер загрузки 220 содержит множество записей буфера загрузки, такие как записи 228-233. Когда встречается операция загрузки, в буфере загрузки 220 создается/сохраняется запись буфера загрузки. В одном из вариантов осуществления буфер загрузки 220 хранит записи буфера загрузки в программном порядке, то есть в том порядке, в каком команды или операции упорядочены в коде программы. Здесь на самую раннюю запись буфера загрузки 228, то есть на самую последнюю сохраненную запись буфера загрузки, ссылается хвостовой указатель загрузки 235. В отличие от этого на самую старую запись буфера загрузки 230, которая не является вышестоящей загрузкой, ссылается головной указатель загрузки 236.

В элементе упорядоченной обработки операции загрузки выполняются в порядке, задаваемом программой, хранящимся в буфере загрузки. В результате самые старые записи буфера выполняются первыми, и головной указатель загрузки 236 перемещается на следующую самую старую запись, которой является запись 229. В отличие от этого в неупорядоченной машине операции выполняются в произвольном порядке. Однако обычно записи удаляются из буфера загрузки, то есть освобождают память, в программном порядке. В результате головной указатель загрузки 236 и хвостовой указатель загрузки 235 функционируют одинаковым образом для двух типов выполнения.

Запись буфера загрузки 230 может содержать информацию любого типа, например значение обновления памяти, значение указателя, ссылку на связанную операцию загрузки, ссылку на адрес, ассоциированный с операцией загрузки, значение, загруженное из адреса, и другие соответствующие значения, флаги или ссылки буфера загрузки. Следует отметить, что буфер хранения 280 может функционировать аналогичным буферу загрузки 220 образом, так как буфер хранения 280 изображен как содержащий записи 281-286 и поле кода блока 283a для записи 283. Кроме того, как буфер загрузки 220, так и буфер хранения 280 содержат вышестоящие сегменты загрузки 250 и 280 соответственно. В результате, во время транзакционного выполнения или HLE, доступы предварительной пересортировки, доступы после пересортировки или их комбинация можгут применяться для обновления битов трассировки доступа 271-273a-b. В совместно-поданной заявке на патент США, озаглавленной "Пост-пересортировочная схема для трассировки предварительного доступа при транзакционном выполнении" и имеющей серийный номер 11/517,029, более подробно обсуждается использование пост-пересортировочной трассировки доступа для предварительного доступа к памяти. Кроме того, в совместно-поданной заявке на патент США, озаглавленной "Гибридная пре- и пост-пересортировочная схема пропуска аппаратной блокировки (HLE)", имеющей серийный номер 11/936,243, обсуждается гибридная схема для трассировки предварительного доступа.

В одном из вариантов осуществления каждая запись буфера загрузки, такая как запись 230, содержит поле кода блока, такое как поле кода блока 225. В качестве примера, предположим, что операция загрузки с целью сохранения (LSI), соответствующая записи загрузки 230, ссылается на адрес системной памяти. Предположим, что элемент, на который ссылается адрес системной памяти, в текущий момент находится в строке кэша 271a, при этом он может как исходно принадлежать кэшу и находиться в строке кэша 271a, так и считываться в ответ на его отсутствие в кэш 270. В этом примере строка кэша 271a содержит значение блокировки для адреса или диапазона адресов, к которым будет осуществляться доступ при выполнении критического участка. Таким образом, при загрузке строки 271a считывается значение блокировки. В этом случае определяется, содержит ли строка 271a заблокированное или незаблокированное значение.

При размещении операции загрузки поле обновления памяти 225 по умолчанию обновляется с присвоением незаблокированного значения для указания, что операция загрузки может быть выполнена. Следует отметить, что обновление бита, значения или поля не обязательно указывает на изменение бита, значения или поля. Например, если поле 225 уже установлено на логический ноль, то обновление с присвоением логического ноля потенциально включает в себя перезапись логического ноля в поле 225, а также отсутствие действия с целью сохранения в поле 225 логического ноля.

В отличие от сценария, обсуждаемого выше, предположим, что запись загрузки 230 связана со следующим критическим участком, например со следующей операцией начала критического участка. Кроме того, в текущем критическом участке встречается событие запроса поздней блокировки. Примеры события запроса поздней блокировки включают в себя истечение срока таймера, заполнение множества кэшей и обнаружение неотменяемого события. Подробнее события запроса поздней блокировки обсуждаются ниже. В ответ на обнаружение события запроса поздней блокировки, поле 225 обновляется с присвоением заблокированного значения с целью блокирования/останова операции начала следующего критического участка. Блокирование и останов операции начала следующего критического участка, а также создание блокировки контрольной точки следующего критического участка подробнее обсуждается ниже.

В одном из вариантов осуществления текущий критический участок до инициации запроса поздней блокировки определяет, выполняется ли предварительное условие. Первым примером предварительного условия является ожидание глобального упорядочивания записей буфера заполнения, ожидающих обработки. Здесь, в случае отсутствия доступа к кэшу 270, то есть если строка не присутствует в измененном или исключенном состоянии, то выделяется запись буфера заполнения для получения запрошенного элемента после его извлечения. В одном из вариантов осуществления глобальное упорядочивание включает в себя любое упорядочивание, по меньшей мере, записей, сохраненных до запроса поздней блокировки, с целью обеспечения целостности памяти, то есть отсутствия нарушений упорядочивания памяти.

Другим примером потенциального предварительного условия для запроса поздней блокировки является определение, обновила ли операция начала критического участка для текущего критического участка стек блокировки с присвоением значения блокировки. Как обсуждалось выше, операция начала критического участка может включать загрузку/чтение для определения, несет ли блокировка заблокированное или незаблокированное значение, и операцию сохранения для осуществления сохранения значения блокировки в ячейку блокировки. Однако, в HLE блокировки пропускаются, и критические участки предварительно выполняются. Следовательно, сохранение, которое может быть связано с записью сохранения 283 в буфере сохранения 280, производится не для обновления строки 271a, а для обновления стека блокировки 205. В действительности, при попытке выполнения запроса поздней блокировки, значение блокировки из записи стека блокировки 206 используется для обновления строки кэша 271a с присвоением заблокированного значения. Другими словами, при применении HLE блокировка в строке кэша 271a не запрашивается до тех пор, пока не будет осуществлена поздняя блокировка посредством обновления строки кэша 271a с присвоением заблокированного значения из записи 206.

Однако в одном из вариантов осуществления операции сохранения, например вышестоящие операции сохранения, блокируются/останавливаются в ответ на инициацию запроса поздней блокировки. Следовательно, если сохранение с целью обновления записи стека блокировки 206 с присвоением значения блокировки не было проведено и инициируется запрос поздней блокировки, то это потенциально приводит к тупиковой ситуации. В этом случае сохранение значения блокировки в стек блокировки 205 для использования в запросе поздней блокировки не было осуществлено и это сохранение остановлено на время проведения запроса поздней блокировки. Другими словами, запрос поздней блокировки ожидает сохранения в стек блокировки 205, а операция сохранения ожидает завершения запроса поздней блокировки для того, чтобы обновить стек блокировки 205. Таким образом, в одном из вариантов осуществления предварительное условие включает в себя определение, было ли произведено сохранение в стек блокировки 205 значения блокировки для текущего критического участка до инициации запроса поздней блокировки для текущего критического участка.

Как было указано выше, в одном из вариантов осуществления во время запроса поздней блокировки для текущего критического участка, в случае если встречается следующий критический участок, то осуществляется останов следующего критического участка. В одном из вариантов осуществления останов критического участка включает в себя блокирование операции начала критического участка, такой как LSI, связанной с записью загрузки 230, для создания контрольной точки. Часто контрольная точка создается после отмены операции LSI. Таким образом, во время запроса поздней блокировки для текущего критического участка, операция начала следующего критического участка, такая как LSI, связанная с записью 230, должна быть заблокирована. В этом случае логический элемент обновления 210 обновляет поле 225 с присвоением заблокированного значения. Следствием наличия в поле 225 заблокированного значения является то, что операция LSI, соответствующая записи 230, не выполняется. В качестве примера, планировщик не вносит в расписание LSI для следующего критического участка, основываясь на том, что поле 225 содержит заблокированное значение. Следует отметить, что логический элемент обновления может установить заблокированное значение для произвольного числа полей, аналогичных полю 225, с целью блокирования/останова любых других операций.

В одном из вариантов осуществления заблокированное значение содержит идентификатор (ID). В результате, когда выполняется условие разблокирования операции доступа, например загрузки, связанной с записью 230, ID передается логическим элементом обновления 210. Все поля, содержащие ID, освобождаются, то есть разблокируются. Например, в случае, когда поле 225 содержит заблокированное значение, например значение MOB_BLOCK_CODE, то в ответ на сброс буфера сохранения ID передается логическим элементом обновления 210. Все записи загрузки с соответствующим ID освобождаются, то есть разблокируются. В другом примере поле 225 может быть полем HLE_BLOCK_CODE. В этом случае в ответ на завершение запроса поздней блокировки ID передается в записи буфера загрузки 220, который освобождает/разблокирует записи загрузки с соответствующим ID.

Как было указано выше, в одном из вариантов осуществления во время запроса поздней блокировки вышестоящие операции сохранения останавливаются. В этом случае логический элемент, такой как логический элемент 225, обновляет поля, такие как 283a, присваивая им заблокированное значение с целью останова вышестоящих операций сохранения. В этом случае аннулируются условия состязания между окончанием критического участка, такие как операция снятия блокировки, и операцией запроса поздней блокировки. В качестве примера, предположим, что блокировка должна храниться в строке кэша 271a. Операция начала критического участка для запроса блокировки пропускается, и значение для получения блокировки сохраняется в записи стека блокировки 206. Затем детектируется событие запроса поздней блокировки. В этом случае сохранение снятия блокировки, ссылающееся на разблокированное значение, потенциально будет состязаться с сохранением запроса поздней блокировки для получения блокировки. В результате выполнение вышестоящих операций сохранения останавливается во избежание потенциального состязания.

Следует отметить, что стек блокировки 205, как показано на иллюстрации, содержит множество записей стека. В одном из вариантов осуществления стек блокировки 205 может поддерживать множество записей для множества критических участков, например, для вложенных критических участков. В качестве примера, в случае, когда запрос поздней блокировки должен быть выполнен для одного критического участка, являющегося вложенным в стеке 205, запрос поздней блокировки должен быть выполнен и для других критических участков, на которые есть ссылки в стеке 205. В целях иллюстрации критический участок, на который ссылается LIE 206, является самым дальним внутренним критическим участком, вложенным во второй критический участок, на который ссылается LIE 207. Кроме того, второй критический участок вложен в самый ближний внешний критический участок, связанный с записью 208.

Здесь, в случае, когда запрос поздней блокировки должен быть выполнен для самого дальнего внутреннего критического участка, запрос поздней блокировки также выполняется для второго и самого ближнего внешнего критического участка. Однако в другом варианте осуществления при обнаружении снятия блокировки для самого дальнего внутреннего критического участка и когда запрос поздней блокировки должен быть выполнен для второго критического участка, запрос поздней блокировки должен выполняться для самого ближнего внешнего критического участка и не выполняться для самого дальнего внутреннего критического участка. Другими словами, в данном варианте осуществления запрос поздней блокировки выполняется для всех критических участков, имеющих большую глубину вложения, чем текущий запрос поздней блокировки.

На Фигурах 3a-3c проиллюстрирован вариант осуществления структурной схемы способа запроса поздней блокировки во время выполнения пропуска аппаратной блокировки критического участка. Хотя структурная схема показывает сравнительно линейный поток операций, в различных вариантах осуществления выполнение операций может происходить в произвольном порядке. Например, определение того, являются ли записи буфера фильтрации глобально видимыми, может происходить после определения, было ли произведено обновление стека блокировки значением блокировки текущего критического участка.

В узле 305 детектируется запрос поздней блокировки. Здесь операция начала критического участка уже была детектирована и пропущена. Например, значение блокировки, по которому осуществляется запрос блокировки для критического участка, хранится в записи команды блокировки (LIE) стека блокировки. Примеры событий запроса поздней блокировки включают в себя истечение срока таймера, заполнение множества кэшей и обнаружение неотменяемого события.

В одном из вариантов осуществления истечение срока таймера включает в себя истечение срока контрольного таймера. Здесь контрольный таймер запускается в ответ на выявление операции загрузки с целью сохранения (LSI) и/или выделение соответствующей LIE. Если соответствующая команда снятия блокировки не была выявлена до истечения срока контрольного таймера, то должен быть выполнен запрос поздней блокировки. Другими словами, после предсказания начала критического участка и отсутствия обнаружения соответствующего окончания критического участка за некоторый период времени, должен осуществляться запрос блокировки.

В другом варианте осуществления запрос поздней блокировки включает в себя заполнение множества кэшей. Например, при выполнении критического участка, производится трассировка доступов с целью выявления конфликтов данных. Однако множество кэшей может заполниться предварительными запросами, трассировка которых проводится при выполнении критического участка. Таким образом, в результате следующего доступа осуществляется выбор строки кэша для вытеснения, при этом данная строка содержит трассировочную информацию для предыдущего предварительного доступа. В результате, в ответ на вытеснение, указывающее на заполнение множества кэшей, может инициироваться запрос поздней блокировки.

В качестве еще одного примера, событие запроса поздней блокировки может включать обнаружение неотменяемого события, то есть события, процесса или доступа, который не может быть легко отменен. Конкретный пример - доступ I/O, часто является неотменяемым, поскольку доступ к устройству I/O трудно отменить. Следовательно, в ответ на обнаружение доступа I/O должен инициироваться запрос поздней блокировки.

Далее, в узле 310 после выявления запроса поздней блокировки определяется, являются ли предыдущие записи буфера заполнения (FBE) глобально видимыми. Если предыдущие записи не являются глобально видимыми, то запрос поздней блокировки останавливается, то есть не инициируется, пока предыдущие FBE не становятся глобально видимыми/упорядоченными в узле 315. В одном из вариантов осуществления глобальная видимость включает в себя упорядочивание любым способом, например, для выполнения отправки на шину/внутреннее соединение. Также в качестве примера, останов запроса поздней блокировки включает в себя обновление записи буфера сохранения, связанного с сохранением запроса поздней блокировки, с присвоением заблокированного значения.

В качестве другого потенциального предварительного условия запроса поздней блокировки в узле 320 определяется, обновило ли стек блокировки значение блокировки текущего критического участка. Как было указано выше, команда начала критического участка для критического участка часто включает в себя команду сохранения для запроса блокировки посредством сохранения значения блокировки в ячейку блокировки. Однако при HLE сохранение в ячейку блокировки пропускается, и значение блокировки записывается в запись стека блокировки, связанную с критическим участком. В одном из вариантов осуществления вышестоящие сохранения останавливаются, например, как в узле 335. Однако, поскольку значение блокировки из стека блокировки должно использоваться во время запроса поздней блокировки, то до сохранения останова вышестоящих операций останавливается сам запрос поздней блокировки до тех пор, пока значение блокировки не обновит стек блокировки в узле 325.

Далее, в узле 330 инициируется запрос поздней блокировки. В одном из вариантов осуществления инициация запроса поздней блокировки включает в себя инициацию операции сохранения для сохранения значения блокировки из стека блокировки в ячейку блокировки с целью запроса блокировки. Следует отметить, что запрос поздней блокировки может потерпеть неудачу, как в узле 345, и критический участок может быть отменен и повторно выполнен в узле 355. Например, во время запроса поздней блокировки, блокировка может быть уже запрошена другим процессорным элементом. В этом случае запрос поздней блокировки откладывается до снятия блокировки, после чего запрашивается блокировка в момент ее снятия другим процессорным элементом. В качестве альтернативы запрос поздней блокировки немедленно терпит неудачу, и критический участок прерывается/перезапускается.

В одном из вариантов осуществления вышестоящие операции сохранения останавливаются во время запроса поздней блокировки, как проиллюстрировано в узле 335. Следует отметить, что запрос поздней блокировки может успешно завершиться в узле 345, без определения следующего критического участка; в этом случае загрузки и вышестоящие сохранения разблокируются, а выполнение критического участка с блокировками продолжается в узле 350. Однако, в случае если следующий критический участок обнаруживается в узле 340, то поток операций продолжается через соединительный узел 360 на Фигуры 3a и 3b.

На Фигуре 3a проиллюстрирован один вариант осуществления обработки следующего критического участка, например, подряд идущего критического участка, во время запроса поздней блокировки для критического участка. В этом случае в узле 365 производится останов следующей операции начала критического участка. Например, операция загрузки с целью сохранения блокируется в буфере загрузки вплоть до завершения запроса поздней блокировки. На Фигуре 3b проиллюстрирован другой вариант осуществления обработки следующего критического участка во время запроса поздней блокировки для текущего критического участка.

В узле 370 определяется, произошел ли сброс буфера сохранения. Если сброс буфера сохранения не произошел, то загрузки следующего критического участка блокируются до тех пор, пока не произойдет сброс буфера сохранения в узле 375. В одном из вариантов осуществления записи буфера загрузки содержат поле block_code. Когда поле block_code содержит заблокированное значение, выполнение соответствующей загрузки блокируется. В этом случае при сбросе буфера сохранения значение, например, ID, передается в буфер загрузки. Записи буфера загрузки, соответствующие значению, разблокируются/освобождаются для выполнения.

После сброса буфера сохранения в узле 380 определяется, является ли следующий критический участок вложенным критическим участком. В одном из вариантов осуществления, в случае если снятие блокировки, то есть сохранение для снятия блокировки, не было обнаружено для текущего критического участка при сбросе буфера сохранения, то следующий критический участок является вложенным критическим участком. В этом случае контрольная точка не создается, поскольку исходная контрольная точка для самого ближнего внешнего критического участка потенциально является достаточной. В отличие от этого доступы следующего критического участка, например доступ загрузки с целью сохранения, блокируются вплоть до завершения запроса поздней блокировки. В одном из вариантов осуществления останов L_S_I включает в себя блокирование создания L_S_I контрольной точки. В этом случае поле кода блока, аналогичное вышеописанному полю кода блока, может использоваться для блокирования доступов. Для иллюстрации, первое поле кода блока является полем MOBBLOCKCODE, и второе поле кода блока является полем HLEBLOCKCODE. Аналогично, после завершения запроса поздней блокировки, передается значение для освобождения/разблокировки L_S_I.

Как проиллюстрировано выше, критические участки могут выполняться с применением транзакционной памяти и/или пропуска аппаратной блокировки (HLE). Вместо прерывания критического участка и потери предыдущих циклов выполнения при повторном запуске критического участка, посредством запроса поздней блокировки можно попытаться продолжить дальнейшее выполнение критического участка. Однако в целях предотвращения тупиков и недостоверности данных до инициации запроса поздней блокировки и во время запроса поздней блокировки в качестве варианта могут налагаться дополнительные условия. Например, следующий идущий подряд критический участок может быть остановлен до завершения запроса поздней блокировки для текущего критического участка с целью обеспечения когерентности и достоверности данных.

Варианты осуществления способов, программного обеспечения, аппаратно-программного обеспечения или кода, изложенных выше, могут быть реализованы посредством команд или кода, хранящихся на машинодоступном или машиночитаемом носителе, и которые могут быть выполнены процессорным элементом. Машинодоступный/машиночитаемый носитель включает в себя любой механизм обеспечения (то есть сохранения и/или передачи) информации в форме, читаемой машиной, такой как компьютерная или электронная система. Например, машинодоступный носитель включает в себя оперативное запоминающее устройство (RAM), например статическое ОЗУ (SRAM) или динамическое ОЗУ (DRAM); постоянное запоминающее устройство (ROM); магнитный или оптический носитель информации; и устройства флеш-памяти. В качестве другого примера, машинодоступный/машиночитаемый носитель включает в себя любой механизм получения, копирования, сохранения, передачи или другой обработки электрической, оптической, акустической или другой формы проходящих сигналов (например, несущих волн, инфракрасных сигналов, цифровых сигналов); и т.д., включающих в себя варианты осуществления способов, программного обеспечения, аппаратно-программного обеспечения или кода, изложенных выше.

В данном описании ссылки на "вариант осуществления" или "один из вариантов осуществления" означают, что конкретное свойство, структура или характеристика, описанная в связи с вариантом осуществления, включена в один из вариантов осуществления представленного изобретения, и при этом не требуется ее присутствия во всех обсуждаемых вариантах осуществления. Таким образом, фразы "в одном из вариантов осуществления" или "в этом варианте осуществления" в различных местах данного описания не обязательно относятся к одному и тому же варианту осуществления. Кроме того, конкретные свойства, структуры или характеристики могут комбинироваться любым подходящим способов в одном или нескольких вариантах осуществления.

В предшествующем описании было дано подробное описание со ссылкой на конкретные примеры вариантов осуществления. Однако очевидно, что в дополнение к этому могут быть внесены различные модификации и изменения без отклонения от сущности и объема изобретения согласно изложенному в прилагаемой формуле изобретения. Описание чертежей соответственно должно рассматриваться в качестве иллюстрации, а не в качестве ограничения. Кроме того, предшествующее использование вариантов осуществления и других описаний на примерах не обязательно относится к одному и тому же варианту осуществления или примеру, но может относиться к различным и отличающимся вариантам осуществления, так же как и, потенциально, к одному и тому же варианту осуществления.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАСШИРЕНИЕ СОГЛАСУЮЩЕГО ПРОТОКОЛА ДЛЯ ИНДИКАЦИИ СОСТОЯНИЯ ТРАНЗАКЦИИ | 2015 |

|

RU2665306C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ УСОВЕРШЕНСТВОВАННЫХ ТЕХНОЛОГИЙ ПРОПУСКА БЛОКИРОВКИ | 2014 |

|

RU2595925C2 |

| НЕОГРАНИЧЕННАЯ ТРАНЗАКЦИОННАЯ ПАМЯТЬ С ГАРАНТИЯМИ ПРОДВИЖЕНИЯ ПРИ ПЕРЕСЫЛКЕ, ИСПОЛЬЗУЯ АППАРАТНУЮ ГЛОБАЛЬНУЮ БЛОКИРОВКУ | 2014 |

|

RU2597506C2 |

| БЛОК ДИАГНОСТИКИ ТРАНЗАКЦИЙ | 2012 |

|

RU2571397C2 |

| СОХРАНЕНИЕ/ВОССТАНОВЛЕНИЕ ВЫБРАННЫХ РЕГИСТРОВ ПРИ ТРАНЗАКЦИОННОЙ ОБРАБОТКЕ | 2012 |

|

RU2562424C2 |

| СПОСОБ И СИСТЕМА ДЛЯ УПРАВЛЕНИЯ ВЫПОЛНЕНИЕМ ВНУТРИ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2012 |

|

RU2577487C2 |

| ФИЛЬТРАЦИЯ ПРОГРАММНОГО ПРЕРЫВАНИЯ В ТРАНЗАКЦИОННОМ ВЫПОЛНЕНИИ | 2012 |

|

RU2568923C2 |

| ВЫПОЛНЕНИЕ ВЫНУЖДЕННОЙ ТРАНЗАКЦИИ | 2012 |

|

RU2549112C2 |

| КОМАНДА НА НЕТРАНЗАКЦИОННОЕ СОХРАНЕНИЕ | 2012 |

|

RU2568324C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЛОКИРОВКИ СИГНАЛА СИНХРОНИЗАЦИИ В МНОГОПОТОЧНОМ ПРОЦЕССОРЕ | 2000 |

|

RU2233470C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в обеспечении достоверности данных. Устройство запроса поздней блокировки, содержащее логический узел декодирования, выполненный с возможностью распознавания команды блокировки в начале критического участка для получения блокировки для критического участка; логический узел выполнения, выполненный с возможностью пропуска, по меньшей мере, части команды блокировки так, чтобы получить блокировку для критического участка, сохранения адреса и значения блокировки, на которые ссылается команда блокировки в записи блокировки, и выполнения критического участка без блокировки для критического участка; и логический узел запроса поздней блокировки, соединенный с логическим узлом выполнения, причем логический узел запроса поздней блокировки выполнен с возможностью инструктировать логический узел выполнения осуществлять попытку выполнения, по меньшей мере, части команды блокировки для получения блокировки для критического участка после начала критического участка и без перезапуска критического участка в ответ на выявление события запроса поздней блокировки при ожидании обработки критического участка. 3 н. и 21 з.п. ф-лы, 5 ил.

1. Устройство запроса поздней блокировки, содержащее:

логический узел декодирования, выполненный с возможностью распознавания команды блокировки в начале критического участка для получения блокировки для критического участка;

логический узел выполнения, выполненный с возможностью пропуска, по меньшей мере, части команды блокировки так, чтобы получить блокировку для критического участка, сохранения адреса и значения блокировки, на которые ссылается команда блокировки в записи блокировки, и выполнения критического участка без блокировки для критического участка; и

логический узел запроса поздней блокировки, соединенный с логическим узлом выполнения, причем логический узел запроса поздней блокировки выполнен с возможностью инструктировать логический узел выполнения осуществлять попытку выполнения, по меньшей мере, части команды блокировки для получения блокировки для критического участка после начала критического участка и без перезапуска критического участка в ответ на выявление события запроса поздней блокировки при ожидании обработки критического участка.

2. Устройство запроса поздней блокировки по п.1, дополнительно содержащее кэш-память, связанную с логическим узлом выполнения, при этом команда блокировки должна ссылаться на значение блокировки и адрес, которые должны быть ассоциированы со строкой кэш-памяти, и при этом логический узел запроса поздней блокировки, выполненный с возможностью инструктировать логический узел выполнения осуществлять попытку выполнения команды блокировки для получения блокировки для критического участка, содержит логический узел запроса поздней блокировки, выполненный с возможностью инструктировать логический узел выполнения выполнять сохранение значения блокировки в строке кэш-памяти, которая ассоциирована с адресом, если строка кэш-памяти показывает, что блокировка для критического участка доступна.

3. Устройство запроса поздней блокировки по п.2, дополнительно содержащее:

участок памяти, соединенный с логическим узлом выполнения и логическим узлом запроса поздней блокировки, причем участок памяти выполнен с возможностью хранения адреса, ассоциированного со значением блокировки в записи блокировки в стеке записей блокировки, и

логический узел выявления, соединенный с логическим узлом декодирования и логическим узлом выполнения, причем логический узел выявления выполнен с возможностью идентифицировать, по меньшей мере, часть команды блокировки, предназначенную для пропуска, и инструктировать логический узел выполнения пропускать, по меньшей мере, часть команды блокировки, причем, по меньшей мере, часть команды блокировки содержит сохранение в адрес значения блокировки.

4. Устройство запроса поздней блокировки по п.3, в котором буфер хранения, связанный с логическим узлом выполнения, выполнен с возможностью хранения записи буфера хранения, связанной с сохранением в адрес значения блокировки, при этом запись буфера хранения выполнена с возможностью хранения поля кода блока, при этом логический узел обновления, связанный с буфером хранения, выполнен с возможностью обновлять поле кода блока с присвоением значения блокировки в ответ на выявления события запроса поздней блокировки.

5. Устройство запроса поздней блокировки по п.4, в котором логический узел обновления дополнительно выполнен с возможностью обновлять поле кода блока с присвоением незаблокированного значения в ответ на инструктирование логического узла выполнения логическим узлом запроса поздней блокировки успешно завершить попытку выполнить команду блокировки для получения блокировки для критического участка.

6. Устройство запроса поздней блокировки по п.5, в котором команда блокировки включает в себя команду чтения, изменения, записи (RMW) с операцией чтения команды RMW, включающей в себя операцию загрузки с целью сохранения (LSI), и при этом логический узел запроса поздней блокировки, инструктирующий логический узел выполнения успешно завершить попытку выполнения команды блокировки для получения блокировки для критического участка, содержит логический узел запроса поздней блокировки, инструктирующий логический узел выполнения выполнять операцию LSI для загрузки загруженного значения из адреса, выполнять операцию изменения для изменения загруженного значения из доступного значения в значение блокировки, и записывать значение блокировки в адрес для получения блокировки.

7. Устройство запроса поздней блокировки по п.1, в котором событие запроса поздней блокировки выбирается из группы, состоящей из истечения срока таймера, указывающего, что команда снятия блокировки, соответствующая команде блокировки, не была выявлена логическим узлом декодирования в течение предварительно определенного периода времени, выявления того, что все строки множества кэшей содержат спекулятивную информацию и возникновения неотменяемого события.

8. Устройство запроса поздней блокировки, содержащее:

процессорный элемент, выполненный с возможностью выполнения текущего критического участка и следующего критического участка, причем процессорный элемент дополнительно выполнен с возможностью пропуска запроса блокировки в начале текущего и следующего критических участков;

буфер доступа, связанный с процессорным элементом, причем буфер доступа выполнен с возможностью хранения записи доступа, ассоциированной с операцией доступа из следующего критического участка, причем запись буфера доступа выполнена с возможностью хранения поля кода блока, при этом операция доступа должна быть заблокирована от выполнения в ответ на запись доступа, сохраняющую поле кода блока, включая заблокированное значение; и

логический узел обновления, соединенный с буфером доступа, причем логический узел обновления выполнен с возможностью обновления поля кода блока для включения заблокированного значения в ответ на осуществление процессорным элементом попытки запроса поздней блокировки для текущего критического участка без перезапуска текущего критического участка после того, как процессорный элемент пропускает запрос блокировки для текущего критического участка.

9. Устройство запроса поздней блокировки по п.8, в котором поле кода блока выполнено с возможностью по умолчанию хранить незаблокированное значение, причем операция доступа свободна для выполнения в ответ на поле кода блока, включающее в себя незаблокированное значение.

10. Устройство запроса поздней блокировки по п.8, в котором попытка запроса поздней блокировки для текущего критического участка должна быть осуществлена в ответ на выявление события запроса поздней блокировки во время выполнения текущего критического участка после того, как процессорный элемент пропускает запрос блокировки для текущего критического участка, и при этом событие запроса поздней блокировки выбирается из группы, состоящей из события истечения срока таймера, события заполнения множества кэшей и неотменяемого события.

11. Устройство запроса поздней блокировки по п.8, в котором логический узел обновления, выполненный с возможностью обновлять поле кода блока для включения заблокированного значения в ответ на осуществление процессорным элементом попытки запроса поздней блокировки для текущего критического участка без перезапуска текущего критического участка, после того как процессорный элемент пропускает запрос блокировки для текущего критического участка, содержит логический узел обновления, выполненный с возможностью обновлять поле кода блока для включения заблокированного значения в ответ на выявление события запроса поздней блокировки и дополнительно в ответ на выполнение предварительного условия запроса поздней блокировки.

12. Устройство запроса поздней блокировки по п.11, в котором предварительное условие запроса поздней блокировки включает в себя разрешение того, чтобы множество ожидающих обработки записей буфера заполнения было глобально видимым.

13. Устройство запроса поздней блокировки по п.11, в котором буфер доступа является буфером загрузки, и в котором операция доступа включает в себя последующую операцию загрузки с целью сохранения (LSI) для обозначения начала следующего критического участка.

14. Устройство запроса поздней блокировки по п.13, дополнительно содержащее стек блокировки, который содержит запись стека блокировки, связанную с текущей операцией LSI для обозначения начала текущего критического участка, в котором предварительное условие запроса поздней блокировки включает в себя ожидание операции сохранения, связанной с текущей LSI для текущего критического участка, которая должна обновить запись стека блокировки.

15. Устройство запроса поздней блокировки по п.13, в котором заблокированное значение содержит идентификатор и в котором в ответ на завершение запроса поздней блокировки логический узел обновления дополнительно выполнен с возможностью передать идентификатор в запись буфера загрузки для обновления поля кода блока с присвоением незаблокированного значения.

16. Способ запроса поздней блокировки, включающий в себя:

пропуск операции запроса блокировки в начале текущего критического участка;

выявление события запроса поздней блокировки при выполнении текущего критического участка;

инициацию запроса поздней блокировки для текущего критического участка без перезапуска текущего критического участка в ответ на выявление события запроса поздней блокировки при выполнении текущего критического участка; и

останов следующей операции запроса блокировки для следующего критического участка в ответ на сохранение буфером доступа ссылки на следующую операцию запроса блокировки и на инициацию запроса поздней блокировки для текущего критического участка.

17. Способ запроса поздней блокировки по п.16, в котором событие запроса поздней блокировки выбирается из группы, включающей в себя истечение времени контрольного таймера, выбор для замещения строки кэша, в которой осуществлялась трассировка доступа к памяти во время выполнения критического участка, и обнаружение неотменяемого события.

18. Способ запроса поздней блокировки по п.16, в котором инициация запроса поздней блокировки для текущего критического участка включает в себя инициацию сохранения значения блокировки, ссылающегося на адрес блокировки, при этом значение блокировки и адрес должны храниться в записи стека блокировки, связанной со ссылкой на операцию запроса блокировки для текущего критического участка.

19. Способ запроса поздней блокировки по п.18, дополнительно содержащий останов множества вышестоящих сохранений, сохраненных в буфере сохранения, в ответ на инициирование запроса поздней блокировки для текущего критического участка, причем множество вышестоящих сохранений разблокируется для выполнения в ответ на сохранение значения блокировки, ссылающегося на аннулирование адреса блокировки.

20. Способ запроса поздней блокировки по п.16, в котором инициация запроса поздней блокировки для критического участка дополнительно выполняется в ответ на глобальную видимость множества ожидающих обработки записей буфера заполнения и обнаружения того, что запись стека блокировки, связанная с критическим участком, обновляется с присвоением значения блокировки.

21. Способ запроса поздней блокировки по п.20, дополнительно содержащий блокирование создания контрольной точки, связанной со следующим критическим участком в ответ на останов следующей операции запроса блокировки для следующего критического участка.

22. Способ запроса поздней блокировки по п.21, дополнительно включающий в себя: определение того, что следующий критический участок не является вложенным критическим участком, при этом блокирование создания контрольной точки дополнительно осуществляется в ответ на определение того, что следующий критический участок не является вложенным критическим участком.

23. Способ запроса поздней блокировки по п.22, в котором определение того, что следующий критический участок не является вложенным критическим участком, содержит:

сброс буфера сохранения в ответ на то, что буфер сохранения содержит записи буфера сохранения;

в ответ на сброс буфера сохранения:

определение, что следующий критический участок является вложенным критическим участком, реагирующим на отсутствие обнаружения текущей операции окончания критического участка; и

определение, что следующий критический участок не является вложенным критическим участком, реагирующим на обнаружение текущей операции окончания критического участка.

24. Способ запроса поздней блокировки по п.21, в котором следующая операция запроса блокировки для следующего критического участка включает в себя операцию загрузки с целью сохранения (LSI), и в котором блокирование создания контрольной точки, связанной со следующим критическим участком включает: блокирование операции LSI от отправки из буфера загрузки.

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| US 6560776 B1, 06.05.2003 | |||

| US 6697935 B1, 24.02.2004 | |||

| МЕХАНИЗМ ОБРАБОТКИ ПРЕРЫВАНИЙ В КОМПЬЮТЕРНЫХ СИСТЕМАХ, ПОДДЕРЖИВАЮЩИХ ОДНОВРЕМЕННОЕ ИСПОЛНЕНИЕ МНОЖЕСТВА ПОТОКОВ | 2002 |

|

RU2280272C2 |

Авторы

Даты

2013-12-10—Публикация

2008-11-06—Подача