та И, второй вход которого соединен с первым входом блока, выход элемента И соединен с первым входом второго буферного регистра, с входом третьего буферного регистра и с первым выходом блока, выход первого буферного регистра соединен с вторым входом схемы сравнения и через узел возведения в степень ,(-и ) - с вторым входом умножителя

выход которого соединен с вторым входом сумматора, выход ЛотЬрого соединен с вторым входом второго буферного регистра, выход которого соединен с вторым выходом блока выход третьего буферного регистра соединен с третьим выходом блока, второй вход узла возведения в степень {-и ) и третий вход умножителя соединены с вторым входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения управляющей вычислительной машины с периферийными устройствами | 1983 |

|

SU1201841A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109752A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

1. УСТРОЙСТВО УПРАВЛЕНИЯ ПОСЛЕДОВАТЕЛЬНОСТЬЮ ОПЕРАЦИЙ, содержащее счетчик переключения программ, блок памяти временных уставок, схему сравнения, блок формирования Команд, блок выработки временных интервалов, содержащий счетчик и генератор импульсов, выход счетчика блока выработки временных интервалов соединен с первым входом схемы сравнения, о т л и ч а ю щ ё-, е с я тем, что, с целью. асигарения функциональных возможностей путем обеспечения изменения длительности микропрограммного такта, в него введены буферный регистр адреса микрокоманды, регистр микрокоман- . ды, регистр кода длительности микрокоманды, блок вычисления временных уставок, причем выход схемы сравнения соединен со счетным входом счетчика переключения программ, с первым управляющим входом буферного регистра адреса микрокоманды, с управляющими входами регистра кода длительности микрокоманды и регистра микрокоманды, с входом установки в нуль счетчика блока выработки временных интервалов не первым входом блока вычисления временных уставок, второй вход которого соединен с выходом генератора импульсов и счётным входом счетчика блоjKa выработки временных интервалов. группа входов блока вычисления временных уставок является группой входов устройства, первый.выход блока вычисления временных уставок соединен с информационным входом блока памяти временных уставок и с вторым управлянмцим входом буферного регистра вщреса микрокоманды, выход которого соединен с сщресными входами блока формирования ,команд и блока памяти временных устайок, вход записи-считывания которого соединен с вторым входом блока вычисления временных уставок, третий выход которого соединен с информационным входом блока формирования команд, выход которого соединен с информационным входом регистра мик(О рокоманды, первый и второй выходы которого соединены соответственно с выходом устройства и с входом установки в нуль счетчика переключе § ния программ, выход которого соединен с информационным входом буферного регистра адреса микрокоманды выход блока памяти временных уставок соединен с информационным входом о :о регистра кода длительности микрокоманды, выход которого соединен с вторым входом схемы сравнения. . vl 2. Устройство по п. 1,отлиN3 У1 чающееся тем, что блок вы- . числения временных уставок содержит три буферных регистра, схему сравнения, элемент задержки, элемент И, узел возведения в степень (-Й), умножитель, сумматор, причем первые входы умножителя и сумматора соединены с соответствующими входами группы входов блока, первые входы первого буферного регй стра и схемы сравнения соединены с соответствуквдим входом группы входов, блока, выход схемы сравнения соединен с вторым входом первого буферного регистра и через элемент задержки - с первым входом элемен

Изобретение относится к вычисительной технике и автоматике и ожет быть использовано для построения, например,блока управления стройством ввода информации в бортовую цифровую вычислительную машну (БЦВМ), выполняющую функцию вычислителя регулирующего воздействия в системе автоматического регулирования (САР авиационного газотурбинного двигателя (ГТД.

Известно устройство управления последовательностью операций, выполненное в виде микропрограммного устройства управления с изменяемой лительностью микропрограммного такта, содержащее блок памяти микропрограмм, регистр адреса, регистр микрокоманды, дешифраторы, , блок управления длительностью микponporpaNiMHoro такта, секционную линию задержки для задания длительности такта С 1

Наиболее близким по технической сущности к изобретению является устройство управления последовательностью операций, содержащее блок хранения программы, первая группа, входов которого соединена с соот- . ветствующими входами устройства, блок формирования команд, группа управляющих вхрдов которого соединена с группой управляющих входов блЬка хранения программы и группой выходов блока переключения программы, выход блока формирования команд соединен с выходом устройства, блок памяти временных уставок, вхо- ды которого соединены с соответствующими выходами блока переключения программы, а выход - с первым входом схемы сравнения, второй вход и выход которой подключены соответственно к первому выходу и-входу блока выработки временных интервалов , управляющие входы которого соответственно подключены к выходу блока хранения- программы и входу j устройства, второй выход блока выработки временных интервалов подключен к синхронизирующему входу блока формирования команд f2 .

Недостатком известного устройства является невозможность изменения длительности микропрограммного такта в зависимости от изменения каких-либо условий в процессе функционирования устройства.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения изменения длительности микропрограммного такта.

Поставленная цель достигается тем, что в устройство управления последовательностью операций, содержащее счетчик переключения программ блок памяти временных уставок, схему сравнения, блок формирования команд, блок выработки временных интервалов , содержсодий счетчик и генератор импульсов, выход счетчика Слока выработки временных интервалов соединен с первым входом схемы сравнения, введены буферный регистр адреса микрокоманды, регистр микрокоманды, регистр кода длительности микрокоманды, блок вычисления временных уставок, причем выход схемы сравнения соединен со счетным входом счетчика переключения программ, с первым управляющим входом буферного регистра адреса микроко,мандды, с управляющими входами регистра кода длительности микрокоманды и регистра микрокоманды, с входом установки в нуль счетчика блока выработки временных интервалов и с первым входом блока вычисления временных уставок, второй вход которого соединен с выходом генератора импульсов и счетным входом .счетчика блока выработки временных интервалов, группа входов блока вычисления временных уставок является группой входов устройства, первый выход блока вычисления временных уставок соединен с информационным входом блока памяти временных уставок и с вторым управляющим

входом буферного регистра адреса микрокоманды, выход которого соединен с адресными входами блока формирования команд и блока памяти временных уставок, вход записи-считывания которого соединен с вторым входом блока вычисления временных уставок, третий выход которого соединен с информационным входом блока формирования команд, выход которого соединен с информационным входом регистра микрокоманды, первый и второй выходы которого соединены соответственно с выходом . устройства и с входом установки в нуль счетчика переключения программ выход которого соединен с информационным входом «уферного регистра адреса микрокоманды, выход блока памяти временных уставок соединен с информационным входом регистра кода длительности микрокоманды, выход которого соединен с вторым входОм схемы сравнения.

Кроме того, блок вычисления временных уставок .содержит три буферных регистра, схему сравнения, элемент задержки, элемент И, узел возведения в степень (-и) , умножитель, сумматор, причем первые входы умножителя и сумматора соединены с соответствующими входами группы входов блока, первые входы первого буферного регистра и схемы сравнения соединены с соответствующим входом группы входов, блока, выход схемы сравнения соединен со вторым входом первого буферного регистра к через элемент задержки с первым входом элемента И, второй вход которого соединён с первым входом блока, выход элемента И соединен с первым входом второго буферного регистра, с входом третьего буферного регистра и с первым выходом блока, выход первого буферного регистра соединен с; вторым входом схемы сравнения и через узел возведения в степень (-И) с вторым входом умножителя, выход которого соединен с вторым входом сумматора, выход которого соединен с вторь 1 входом второго буферного регистра, выход которого соединен с вторым выходом блока, выход третьего буферного регистра соединен с третьим выходом блока, второй вход узла возведения в степень () и третий вход уыножктепя соединены с вторым входом блока.

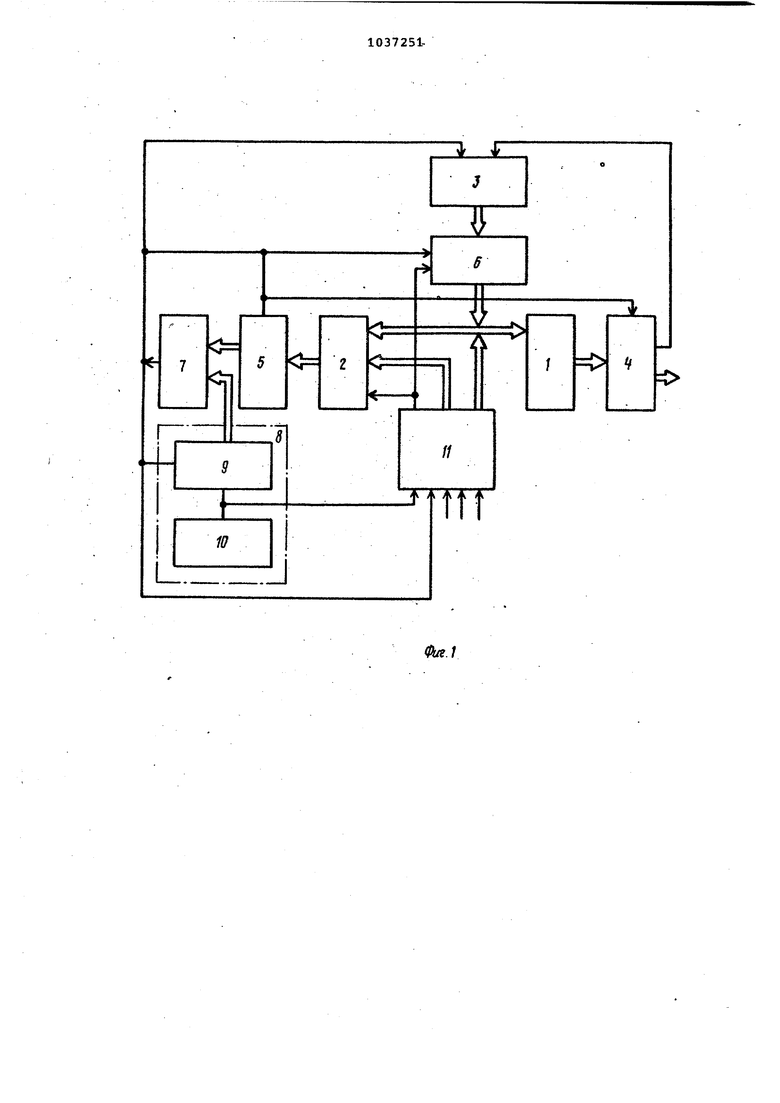

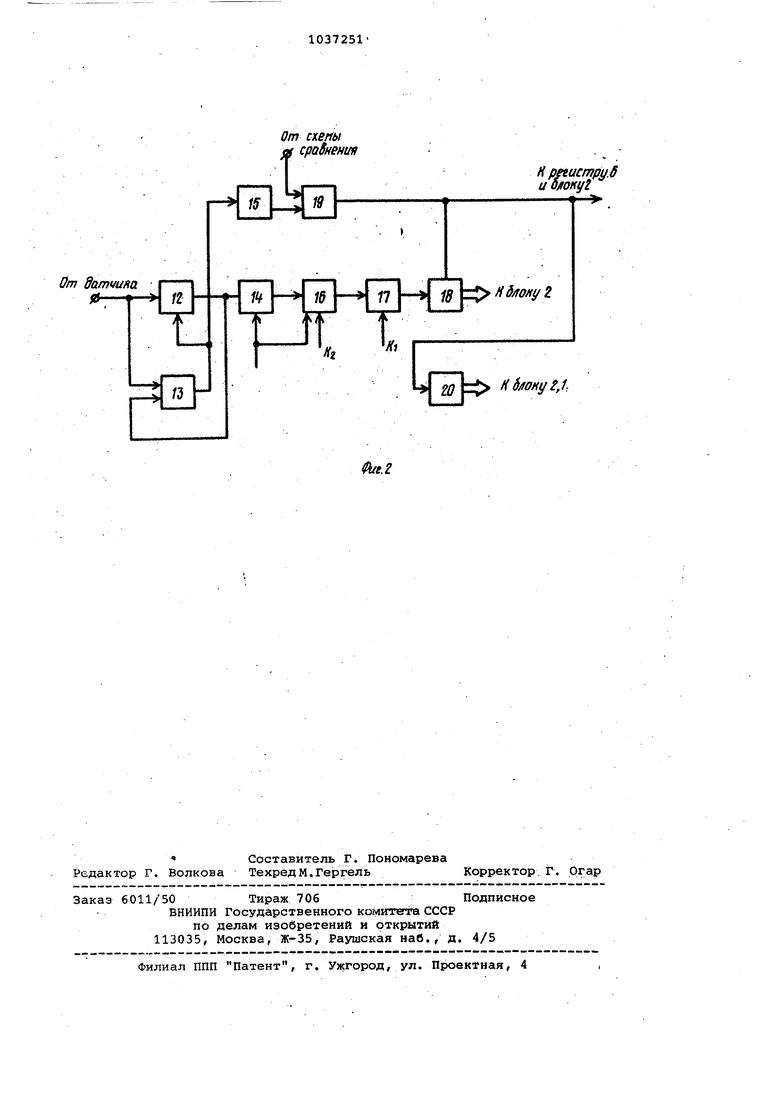

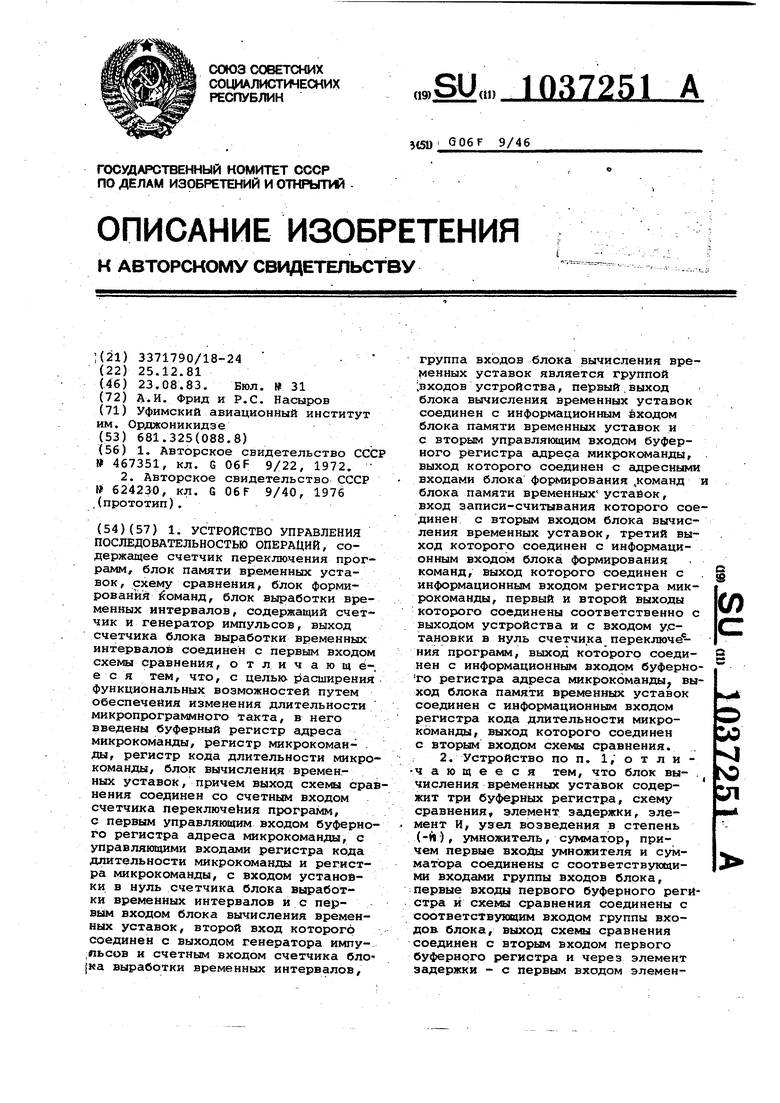

Ка фиг. 1 представлена блок-схема предлагаемого устройства, на фиг. 2 - структурная схема одной из возможных реализаций блока вычис-яения временных уставок.

Устройство управления последовательностью операций содержит блок 1 формирования команд, блок 2 памяти

временных уставок, счетчик .3 пере- ключения программ, регистр 4 микрокоманды, регистр 5 кода длительности микрокоманды, буферный регистр

6адреса микрокоманды, схему 7 сравнения, блок 8 выработки временных интервалов, состоящий из-счетчика 9 и генератора 10 импульсов, блок 11 v вычисления временных уставок.

Блок 1 представляет собой постоянное запоминающее устройство, блок

o 3 - счетчик, а блок 2 - оперативное запоминающее устройство.

Блок 11 содержит первый буферный регистр 12, схему 13 сравнениду, узел 14 возведения в степень (-п),

5 элемент 15 задержки, умножитель 16, сумматор 17, второй буферный регистр 18, элемент И 19 и третий буферный регистр 20.

Устройство работает следуияднм

0 образом.

Перед началом работы в блоке 11 вычисления временных уставок .на основании информации, полученной от датчиков внешних условий или с бло5ка контроля, вычисляются необходимые коды временных уставок, которые записываются в блок 2 памяти временных уставок. Затем в соответствии с кодом на выходах счетчика 3 пере0ключения программ, переписанным в буферный регистр 6 адреса микрокоманды из блока 1 формирования команд и блока 2 памяти временных уставок выбираются, соответственно, код микрокоманды и код длительности

5 микропрограммного такта, которые переписываются в регистры 4 и 5 и устанавливаются на их выходах. Код длительности микропрограммного такта сравнивается на схеме 7 срав0нения с кодом на выходе счетчика 9 блока 8 выработки временных ив;тервадов1 При их совпадении схема

7сравнения вырабатывает сигнал, устанавливающий в О счетчик 9,

5

дающий приращение на 1 коду на выходе счетчика 3, стробирующий занесение информации в регистры 4-6 и разрешающий, в случае необходимости, запись информации из блока 11 в блок 2, начинается новый такт

0 работы устройства. После оконча,ния цикла работы устройства, по сигналу с блока 1 формирования команд, переписанному в регистр 4, обнуляется код на выходе счетчика 3

5 переключения программ и происходит обращение к ячейкам с нулевым адресом блока 1 формирования команд и блока 2 памяти временных уставок. Тем самым начинается новый

0 цикл работы устройства.

При изменении в процессе функционирования устройства каких-либо условий (например, при изменеиии условий окружающей среды или по, ;сигналам с блока контроля ) блок 11

5

вычисления временных уставок вычисляет значения кодов временных уставок , соответствующих новьм условиям или показаниям системы контроля, и после разрешающего сигнала со схемы 7 сравнения выдаеГ сигнал, устанавливающий буферный регистр 6 адреса микрокоманды в состояние вы сокого Выходного сопротивления и переводящий блок 2 хранения временных уставок в режим Запись. Затем производится запись в блок 2 нового значения кода времени уставки по адресу, также выдаваемому блоком 11 вычисления временных, уставок. При этом нормальная работа устройства управления не нарушается, так как информация о текущей микрокоманде и времени ее исполнения зап санав регистрах 4 и 5 соответственно. После записи, кода в блок 2 памяти временных уставок блок 11 вычисления временных уставок устанавливается в исходное состояние и другой код может быть записан толко после начала следующего микропрограммного такта (т.е. при наличии сигнала со схемы 7 сравнения; Работа блока 11 синхронизируется генератором 10.

Блок 11 работает следующим образом.

Код, поступающий на вход блока 11 от внешних устройств, сравнивается с ранее имевшимся с помощью , схемы 13 сравнения. В случае несовпадения кодов (в пределах заданного рассогласования) схема 13 сравнения выдает сигнал, по которому в буферный регистр 12 заносится новый код. Одновременно этот сигнал поступает на элемент 15 задержки. Над кодом, записанным в буферном регистре 12, производится соответствующие вычисления в блоках 14, 16 и 17. Элемент 15 задержки задерживает сигнал от схемы 13 сравнения на время, необходимое для прове дения вычислений. Этот сигнал логически умножается элементом И 19 на сигнал сравнения, поступающий на вход блока 11 от схемы сравне;ния, и в случае их совпадения эле- мент И 19 выдает сигнал, переводящий ОЗУ блока памяти временных уставок в режим Запись, открывающий буферные регистры 18, 20 и переводящий буферный регистр 6 адреса микрокоманды в состояние высокого выходного сопротивления. При этом происходит запись нового кода временной уставки в блок памяти временных уставок. После этого устройство возвращается в исходное

5 состояние, так как коды на выходах схемы 13 сравнения совпадают.

Таким образом, предложенное устройство по сравненшо с известным обладает более широкими функпиоn нальными возможностями и позволяет:

уменьшить количество критических ситуаций, возникающих, например, при отказе какого-либо функционального узла в устройстве ввода или отказа датчика информации, за счет перестройки временной диафрагмы функционирования устройства вводи непосредственно в процессе работы

Повысить помехозащищенность устройства ввода информации в БЦВМ за

0 счет анализа блоком 11 спектра входных сигналов, при этом анализируется спектр помехи и время ввода параметра выбирается таким образом, чтобы произвести ее фильтра5 цию;

повысить динамическую точность и быстродействие пр1й вводе некоторых сигналов за счет организации адаптивных корректируюащх контуров;

повысить гибкость применения предлагаемого устройства ввода при работе с различными, ио однотипными объектами. ( например, с различными модификациями одного и того же авиационнозго ГТД, при этом перестройка работы устройства ввода не требует схемных изменений и т.д.

От скепы ел cpof нения

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1972 |

|

SU467351A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления последовательностью операций | 1976 |

|

SU624230A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-08-23—Публикация

1981-12-25—Подача