Область техники, к которой относится изобретение

Настоящее изобретение относится к технике генерирования электрических колебаний, а именно к устройствам прямого цифрового синтеза частоты.

Уровень техники

В системах телекоммуникаций и в измерительной технике широко используются синтезаторы частоты, многообразие вариантов которых можно свести одной из двух групп - синтезаторы частоты на основе фазовой синхронизации (PLL - Phase Lock Loop) и синтезаторы на основе прямого цифрового синтеза (DDS - Direct Digital Synthesis). Все эти устройства можно рассматривать как аналоги настоящего изобретения.Аналогом настоящего изобретения из первой группы является синтезатор частоты на основе управляемого генератора, охваченного обратной связью по фазе через фазовый компаратор и фильтр нижних частот, в котором в цепь обратной связи и во входную цепь по оставшемуся входу фазового компаратора включены делители частоты с различающимися коэффициентами деления (Шахтарин Б.И. и др. Синтезаторы частот: Учебное пособие / Б.И. Шахтарин, Г.Н. Прохладин, А.А. Иванов, А.А. Быков, А.А. Чечулина, Д.Ю. Гречищев. - М.: Горячая линия - Телеком, 2007. - 128 с. - Рисунок 2.1). Его недостатки состоят в значительном времени установления частоты, большом шаге ее перестройки и узком диапазоне генерируемых частот.

Другим аналогом предлагаемого устройства, также использующим способ фазовой синхронизации, является цифровой синтезатор частоты по патенту США № 3401353, в который дополнительно введен блок грубой автоматической настройки управляемого генератора, что позволяет расширить диапазон синтезируемых частот. Однако данный аналог также характеризуется низким быстродействием при перестройке частоты и нестабильностью работы системы фазовой синхронизации.

Аналогом из числа устройств, использующих прямой цифровой синтез, является цифровой синтезатор частоты по патенту США № 5931891, который состоит из последовательно соединенных цифрового сумматора, регистра, логической схемы, цифро-аналогового преобразователя, фильтра и ограничителя напряжения. При этом тактовый вход регистра соединен с выходом тактового генератора, один вход цифрового сумматора подключен к выходу регистра, а другой его вход служит входом инкремента фазы, определяющим частоту генерирования. Это устройство вырабатывает прямоугольные импульсы и не обеспечивает высокой точности перестройки частоты.

Наиболее близкой по технической сущности к предполагаемому изобретению является базовая схема прямого цифрового синтезатора частоты, представленная в многочисленных публикациях, в частности, приведенная на рисунке 4 в статье Л. Ридико «DDS: прямой цифровой синтез частоты / Компоненты и технологии. - 2001, № 7» (Рисунок 4). Устройство-прототип содержит последовательно соединенные цифровой сумматор, регистр, постоянное запоминающее устройство, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является выходом устройства, причем выход регистра, у которого тактовый вход соединен с выходом опорного генератора, подключен к входу первого слагаемого цифрового сумматора, второй вход которого является входом кода управления частотой. Цифровой сумматор с обратной связью по первому входу через регистр образует накапливающий сумматор (аккумулятор). Характеристики устройства-прототипа определяются разрядностью цифровых узлов, а шаг перестройки периода равен периоду опорного генератора, что ограничивает точность установления частоты.

Раскрытие сущности изобретения

Целью настоящего изобретения является повышение точности синтеза частоты за счет дополнительного режима работы устройства с уменьшением на единицу модуля счета сумматора в аккумуляторе.

Указанная цель достигается введением в устройство, содержащее первый цифровой сумматор, один вход которого является входом управления частотой, а второй присоединен к входу постоянного запоминающего устройства и выходу регистра, тактовым входом связанного с выходом опорного генератора, а также цифроаналоговый преобразователь, выходом подключенный к выходному зажиму устройства через фильтр нижних частот, второго сумматора, второго постоянного запоминающего устройства, мультиплексора, логического блока и входного зажима задания режима работы синтезатора. При этом цифровым входом второй сумматор подключен к цифровому выходу первого сумматора, а входом переноса к выходу логического блока, адресный вход второго постоянного запоминающего устройства объединен с адресным входом первого постоянного запоминающего устройства, выходы первого и второго запоминающих устройств подключены к соответствующим информационным входам мультиплексора. Многоразрядный выход мультиплексора соединен с входом цифро-аналогового преобразователя, а его адресный вход с входным зажимом задания режима работы синтезатора и одним входом логического блока, другой вход которого соединен с выходом переноса первого многоразрядного сумматора, а третий цифровой вход - с выходом первого многоразрядного сумматора.

Краткое описание чертежей

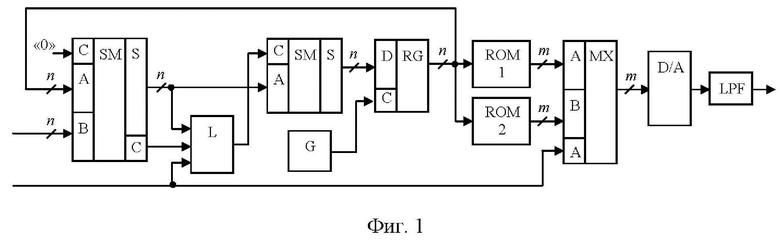

На фиг. 1 представлена функциональная электрическая схема цифрового синтезатора частоты в соответствии с настоящим изобретением.

На фиг. 2 изображена схема варианта исполнения входящего в цифровой синтезатор частоты логического блока.

На фиг. 3 показана возможная логическая структура второго многоразрядного сумматора.

Осуществление изобретения

Представленная на фиг. 1 функциональная схема цифрового синтезатора частоты содержит первый цифровой сумматор 1, выход которого соединен с входом второго цифрового сумматора 2 и цифровым входом логического блока 3, выход которого подключен к входу переноса второго цифрового сумматора 2, а второй и третий входы соответственно - к выходу переноса первого цифрового сумматора 1 и к входному зажиму 4 задания режима работы синтезатора. Выход второго цифрового сумматора 2 присоединен к информационному входу регистра 5, у которого тактовый вход связан с выходом опорного генератора 6, а выход присоединен к входам первого 7 и второго 8 постоянных запоминающих устройств и одному входу первого цифрового сумматора, второй вход 9 которого служит входным зажимом задания режима работы синтезатора. Выходы первого 7 и второго 8 постоянных запоминающих устройств подключены к соответствующим информационным входам мультиплексора 10, адресный вход мультиплексора соединен с входным зажимом 4 задания режима работы синтезатора, а его выходы - к входам цифроаналогового преобразователя 11, выходом связанного через фильтр 12 нижних частот с выходным зажимом 13 синтезатора.

В предпочтительном варианте осуществления, показанном на фиг. 2, логический блок 3 выполняется в виде первого вентиля И 14, входы которого являются цифровым входом логического блока, выход первого вентиля И 14 присоединен к одному входу вентиля ИЛИ 15, второй вход которого служит вторым входом логического блока, и второго вентиля И 16, выход которого служит выходом логического блока, один его вход подключен к выходу вентиля ИЛИ, а оставшийся вход служит третьим входом логического блока. Оба цифровых сумматора 1 и 2, а также регистр 5 являются n-разрядными цифровыми узлами. Постоянные запоминающие устройства 7 и 8 при n адресных входах имеют m-разрядные ячейки памяти, причем первое постоянное запоминающее устройство 7 хранит 2n цифровых образов формы синтезируемого выходного сигнала, а второе постоянное запоминающее устройство 8 - (2n-1) подобных цифровых образов. Информационная емкость обоих постоянных запоминающих устройств 7 и 8 составляет, следовательно, 2n×m бит.

Функция второго цифрового сумматора 2, возможная схема которого показана на фиг. 3, примитивна и состоит в добавлении переноса к единственному слагаемому, ввиду чего он может быть построен по упрощенной схеме на полусумматорах 17, 18, 19, соединенных последовательно по цепи распространения переноса. При этом первый вход первого 17 в цепочке полусумматоров служит входом переноса второго цифрового сумматора, а вторые входы всех полусумматоров - его входом слагаемого.

Мультиплексор 10 представляет собой группу m простейших мультиплексоров «2→1» с объединенными адресными входами (m - разрядность ячейки памяти постоянных запоминающих устройств 7 и 8).

Устройство работает в следующем порядке.

В первом режиме работы при нулевом значении сигнала на входном зажиме 4 задания режима работы синтезатора на выходе логического блока 3 поддерживается уровень логического «0», при этом цифровой сумматор 2 в отсутствии входного сигнала переноса передает на свой выход n-разрядное число с выхода первого цифрового сумматора. Поскольку на адресном входе мультиплексора 10 присутствует уровень логического «0», то он передает на свой цифровой m-разрядный выход текущее выходное состояние первого постоянного запоминающего устройства 7. В данном режиме устройство представляет собой обычное устройство прямого цифрового синтеза (прототип), образующего на выходном зажиме 13 сигналы с формой, запрограммированной в первом постоянном запоминающем устройстве 7, и с частотой, равной

где n - разрядность сумматоров 1, 2 и регистра 5,

Во второй режим работы устройство переходит при поступлении уровня логической «1» на входной зажим 4 задания режима работы синтезатора. Тогда мультиплексор 10 в соответствии с адресным кодом начинает передавать на входы цифроаналогового преобразователя последовательность чисел с выхода второго постоянного запоминающего устройства 8, а в логическом блоке 3 логической единицей по третьему входу разблокируется цепь передачи сигнала через вентиль И 16. В процессе работы аккумулятор в составе цифровых сумматоров 1, 2 и регистра 5 образует последовательность чисел, увеличивающихся с инкрементом

Так продолжается до момента, когда цифровой сумматор 1 достигает состояния всех единиц на своем выходе, что фиксируется вентилем 14 в логическом блоке, либо когда появляется сигнал переноса на его соответствующем выходе, который далее поступает на второй вход вентиля ИЛИ 15. В том и другом случаях на выходе логического блока 3 появляется уровень логической «1», передаваемый на вход переноса второго цифрового сумматора 2. В данном режиме модуль счета аккумулятора, образованного сумматорами и регистром, изменяется: вместо 2n, который был в первом режиме работы, он становится равным (2n-1). Это происходит благодаря тому, что при достижении первым цифровым сумматором состояния (2n-1), либо при превышении этого состояния, из него вычитается модуль счета (2n-1). Вычитание чисел, как известно, в цифровой технике выполняется в дополнительном коде путем сложения уменьшаемого с отрицательным числом - вычитаемым, которое в дополнительном коде представляется его поразрядной инверсией с добавлением единицы. Примитивный второй сумматор 2 не имеет входа второго слагаемого, что равносильно нулю на его отсутствующем втором входе (00…00 - это поразрядная инверсия 11…11 = (2n-1)). Единица добавляется по входу переноса второго цифрового сумматора 2.

Таким образом, модуль счета аккумулятора во втором режиме оказывается равным (2n-1). Благодаря этому частота генерируемых устройством сигналов будет отличаться от (1), а именно, станет равной

Если шаг перестройки частоты в первом режиме работы составлял (при

много меньшим, чем в устройстве-прототипе.

Если же несколько снизить требования к точности формы выходного сигнала, то указанный выигрыш в точности установления частоты можно сопроводить существенным упрощением устройством за счет уменьшения разрядности цифровых узлов.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ С ПЕРЕМЕННЫМ МОДУЛЕМ СЧЕТА | 2000 |

|

RU2179784C2 |

| ИЗМЕРИТЕЛЬНЫЙ ГЕНЕРАТОР ПАРНЫХ ИМПУЛЬСОВ | 2022 |

|

RU2788980C1 |

| ГЕНЕРАТОР С РАЗДЕЛЬНОЙ ЦИФРОВОЙ РЕГУЛИРОВКОЙ ЧАСТОТЫ И ФАЗЫ ИМПУЛЬСОВ | 2000 |

|

RU2168268C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство для цифрового формирования сигналов с амплитудно-фазовой модуляцией и одной боковой полосой | 1988 |

|

SU1598200A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| ГЕНЕРАТОР ПАРНЫХ СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 2022 |

|

RU2795263C1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Накапливающий сумматор | 2017 |

|

RU2642366C1 |

Изобретение относится к технике генерирования электрических колебаний, а именно к устройствам прямого цифрового синтеза частоты. Техническим результатом является повышение точности установления частоты. Для этого предложено устройство, содержащее два цифровых сумматора, которые совместно с тактируемым опорным генератором регистром образуют аккумулятор, а также пару постоянных запоминающих устройств для хранения цифровых образов генерируемых сигналов, цифроаналоговый преобразователь и фильтр нижних частот. Добавление в устройство второго из названных сумматоров, логического блока и мультиплексора дает возможность организации второго режима работы аккумулятора с уменьшенным на единицу модулем счета, за счет чего изменяется шаг перестройки частоты. 2 з.п. ф-лы, 3 ил.

1. Цифровой синтезатор частоты, содержащий первый цифровой сумматор, один вход которого является входом управления частотой, а другой присоединен к адресному входу постоянного запоминающего устройства и выходу регистра, тактовым входом связанного с выходом опорного генератора, а также цифро-аналоговый преобразователь, выходом подключенный к выходному зажиму устройства через фильтр нижних частот, отличающийся тем, что в него дополнительно введен второй цифровой сумматор, второе постоянное запоминающее устройство, мультиплексор, логический блок и входной зажим задания режима работы синтезатора, при этом цифровым входом второй цифровой сумматор подключен к выходу первого сумматора, а входом переноса к выходу логического блока, адресный вход второго постоянного запоминающего устройства объединен с адресным входом первого постоянного запоминающего устройства, выходы первого и второго запоминающих устройств подключены к соответствующим информационным входам мультиплексора, выходы мультиплексора соединены с соответствующими входами цифро-аналогового преобразователя, а его адресный вход – с входным зажимом задания режима работы синтезатора и одним входом логического блока, другой вход которого соединен с выходом переноса первого многоразрядного сумматора, а третий цифровой вход – с выходом первого цифрового сумматора.

2. Цифровой синтезатор частоты по п. 1, отличающийся тем, что логический блок выполнен в виде первого вентиля И, входы которого являются третьим цифровым входом логического блока, выход первого вентиля И присоединен к одному входу вентиля ИЛИ, второй вход которого служит вторым входом логического блока, и второго вентиля И, выход которого служит выходом логического блока, один его вход подключен к выходу вентиля ИЛИ, а оставшийся вход служит первым входом логического блока.

3. Цифровой синтезатор частоты по п. 1, отличающийся тем, что второй многоразрядный сумматор представляет собой цепочку полусумматоров, объединенных по цепям распространения сигнала переноса, первый вход первого в цепочке полусумматора является входом переноса второго многоразрядного сумматора, а вторые входы всех полусумматоров – цифровым входом второго многоразрядного сумматора.

| Л | |||

| РИДИКО "DDS: прямой цифровой синтез частоты", Компоненты и технологии, 2001, N 7, рис | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ С АВТОПОДСТРОЙКОЙ ЧАСТОТЫ | 2004 |

|

RU2260904C1 |

| ГЕНЕРАТОР С РАЗДЕЛЬНОЙ ЦИФРОВОЙ РЕГУЛИРОВКОЙ ЧАСТОТЫ И ФАЗЫ ИМПУЛЬСОВ | 2000 |

|

RU2168268C1 |

| US 3976945 A1, 24.08.1976. | |||

Авторы

Даты

2023-04-06—Публикация

2022-11-09—Подача