Область техники

[1] Настоящее изобретение в целом относится к передаче и приему информации в вещательной системе/системе связи, а конкретнее - к способу и устройству для управления кодовой скоростью в соответствии с передачей и приемом сигнальной информации в вещательной системе/системе связи.

Предшествующий уровень техники

[2] Вещательная система/система связи может столкнуться с низкой производительностью линии связи из-за шума, явления замирания и межсимвольных помех (ISI). Таким образом, чтобы реализовать высокоскоростные цифровые вещательные системы/системы связи, которые требуют высокой пропускной способности и надежности, необходима разработка методики для преодоления шума, замирания и ISI. Чтобы решить эти проблемы, в настоящее время проводится исследование кода исправления ошибок, например кода с низкой плотностью проверок на четность (LDPC), для повышения надежности вещания/связи путем эффективного восстановления искажения информации до исходного состояния.

[3] Точнее говоря, LDPC-кодер принимает информационные биты LDPC (или информационное слово LDPC, или некодированный LDPC-блок), содержащие Kldpc битов, чтобы сформировать кодированные биты LDPC (или кодовое слово LPDC, или кодированный LDPC-блок), содержащие Nldpc битов. Если длина информационных битов LDPC, введенных в LDPC-кодер, Kldpc, короче длины входных информационных битов (или входного информационного слова), которые должны кодироваться, Ksig, то сторона передачи выполняет кодирование после процесса сокращения. Если количество битов четности, используемых стороной передачи, то есть длина битов четности, Ntx_parity, короче длины битов четности, выведенных из кодера, (Nparity=Nldpc-Kldpc), то сторона передачи исключает биты четности, выведенные из кодера, на (Nparity - Ntx_parity).

[4] Если длина битов сокращения увеличивается, то кодовая скорость уменьшается, так что характеристику частоты появления ошибочных битов (BER)/частоты появления ошибочных кадров (FER) можно улучшить по сравнению с кодом до сокращения. Однако если длина битов исключения увеличивается, то кодовая скорость также увеличивается, так что характеристика BER/FER может ухудшаться по сравнению с кодом до исключения. Поэтому, чтобы сохранить аналогичную характеристику независимо от длины информационного слова для стабильности системы, необходима методика для выбора подходящего количества битов исключения в соответствии с длиной информационного слова.

Раскрытие изобретения

Техническая проблема

[5] Соответственно, настоящее изобретение разработано для решения по меньшей мере проблем и/или устранения недостатков, описанных выше, и предоставления по меньшей мере описанных ниже преимуществ.

[6] Аспект настоящего изобретения состоит в предоставлении способа и устройства для передачи и приема информации в вещательной системе/системе связи.

[7] Другой аспект настоящего изобретения состоит в предоставлении способа и устройства для управления кодовой скоростью в вещательной системе/системе связи.

[8] Другой аспект настоящего изобретения состоит в предоставлении способа и устройства для выбора скорости сокращения/исключения в соответствии с длиной информационного слова в вещательной системе/системе связи.

[9] Другой аспект настоящего изобретения состоит в предоставлении способа и устройства для определения количества битов, которые необходимо исключить, в соответствии с длиной входного информационного слова в вещательной системе/системе связи.

Решение проблемы

[10] В соответствии с аспектом настоящего изобретения предоставляется способ для передачи информации в вещательной системе/системе связи. Способ включает в себя сравнение количества битов информационного слова, которое необходимо передать, с заранее установленным пороговым значением, определение первой пары параметров, если количество битов информационного слова меньше порогового значения, определение второй пары параметров, если количество битов информационного слова не меньше порогового значения, определение количества битов, которые необходимо исключить, на основе одной из первой пары параметров и второй пары параметров, и исключение определенного количества битов, которые необходимо исключить, относительно битов четности кодового слова, сформированного путем кодирования информационного слова.

[11] В соответствии с другим аспектом настоящего изобретения предоставляется устройство для передачи информации в вещательной системе/системе связи. Устройство включает в себя кодер для кодирования информационного слова, которое необходимо передать, и выведения кодового слова; контроллер для сравнения количества битов информационного слова с заранее установленным пороговым значением, определения первой пары параметров, если количество битов информационного слова меньше заранее установленного порогового значения, определения второй пары параметров, если количество битов информационного слова не меньше заранее установленного порогового значения, и определения количества битов, которые необходимо исключить, на основе одной из первой пары параметров и второй пары параметров; и исключающий блок для исключения определенного количества битов, которые необходимо исключить, относительно битов четности кодового слова.

[12] В соответствии с другим аспектом настоящего изобретения предоставляется способ для приема информации в вещательной системе/системе связи. Способ включает в себя сравнение количества битов информационного слова, переданного стороной передачи, с заранее установленным пороговым значением, определение первой пары параметров, если количество битов информационного слова меньше заранее установленного порогового значения, определение второй пары параметров, если количество битов информационного слова не меньше заранее установленного порогового значения, определение количества битов, которые необходимо исключить, на основе одной из первой пары параметров и второй пары параметров, формирование значений, соответствующих битам, исключенным стороной передачи, и заполнение сформированными значениями модулированного сигнала принятого сигнала, чтобы сформировать входные данные декодера, используя определенное количество битов, которые необходимо исключить, и декодирование входных данных декодера, чтобы восстановить биты информационного слова.

[13] В соответствии с другим аспектом настоящего изобретения предоставляется устройство для приема информации в вещательной системе/системе связи. Устройство включает в себя демодулятор для демодулирования принятого сигнала; контроллер для получения информации о количестве битов информационного слова, переданного от стороны передачи, сравнения количества битов информационного слова, переданного стороной передачи, с заранее установленным пороговым значением, определения первой пары параметров, если количество битов информационного слова меньше заранее установленного порогового значения, определения второй пары параметров, если количество битов информационного слова не меньше заранее установленного порогового значения, и определения количества битов, которые необходимо исключить, на основе одной из первой пары параметров и второй пары параметров; исключающий процессор для формирования значений, соответствующих битам, исключенным стороной передачи, используя определенное количество битов, которые необходимо исключить, и заполнения сформированными значениями выходного сигнала демодулятора; и декодер для приема и декодирования выходных значений исключающего процессора, чтобы восстановить биты информационного слова.

Краткое описание чертежей

[14] Вышеупомянутые и другие аспекты, признаки и преимущества некоторых вариантов осуществления настоящего изобретения станут более очевидными из нижеследующего подробного описания в сочетании с прилагаемыми чертежами, на которых:

[15] Фиг. 1 - график, иллюстрирующий изменение кодовой скорости в соответствии с вариантом осуществления настоящего изобретения;

[16] Фиг. 2 и 3 - графики, иллюстрирующие эффективность LDPC-кода в соответствии с вариантом осуществления настоящего изобретения;

[17] Фиг. 4 - график, иллюстрирующий изменение эффективной кодовой скорости в соответствии с вариантом осуществления настоящего изобретения;

[18] Фиг. 5 - график, иллюстрирующий эффективность LDPC-кода в соответствии с вариантом осуществления настоящего изобретения;

[19] Фиг. 6 - блок-схема последовательности операций, иллюстрирующая процедуру для исключения битов четности на основе длины информационных битов в соответствии с вариантом осуществления настоящего изобретения;

[20] Фиг. 7 - схема, иллюстрирующая структуру кадра для передачи двух типов битов четности в соответствии с вариантом осуществления настоящего изобретения;

[21] Фиг. 8 - схема, иллюстрирующая структуру LDPC-кода для поддержки передачи битов четности в соответствии с вариантом осуществления настоящего изобретения;

[22] Фиг. 9 - график, иллюстрирующий изменение эффективной кодовой скорости в соответствии с вариантом осуществления настоящего изобретения;

[23] Фиг. 10 - блок-схема последовательности операций, иллюстрирующая процедуру для определения количества двух типов битов четности в соответствии с вариантом осуществления настоящего изобретения;

[24] Фиг. 11 - блок-схема, иллюстрирующая сторону передачи в соответствии с вариантом осуществления настоящего изобретения; и

[25] Фиг. 12 - блок-схема, иллюстрирующая сторону приема в соответствии с вариантом осуществления настоящего изобретения.

Варианты осуществления изобретения

[26] Далее будут подробно описаны различные варианты осуществления настоящего изобретения со ссылкой на прилагаемые чертежи. Общеизвестные функции и структуры не будут описываться, если они могут затруднить понимание сущности настоящего изобретения. Кроме того, используемые в этом документе термины определяются на основе функций в настоящем изобретении и могут меняться в соответствии с пользователями, намерением оператора или установившейся практикой. Поэтому определения терминов следует выполнять в зависимости от содержания по всему описанию изобретения.

[27] Хотя нижеследующее описание настоящего изобретения основывается на системе цифрового наземного видеовещания 2-го поколения (DVB-T2), которая является Европейским стандартом цифрового вещания, и системе цифрового видеовещания следующего поколения на переносные устройства (DVB-NGH), которая стандартизируется в настоящее время, настоящее изобретение в равной степени применяется к другим системам.

[28] Более того, хотя нижеследующее описание управляет кодовой скоростью, соответствующей передаче сигнальной информации, настоящее изобретение также применимо к передаче другой информации.

[29] На стороне передачи вещательной системы/системы связи LDPC-кодер принимает Kldpc информационных битов LDPC, формирует Nparity битов четности и выводит Nldpc (=Kldpc+Nparity) кодированных битов LDPC. В нижеследующем описании для удобства будет описываться ввод и вывод "битов", но такое же описание также применяется к вводу и выводу символов.

[30] Когда в кодер вводятся сигнальные биты переменной длины, сторона передачи может выполнять сокращение и/или исключение (в дальнейшем называемое "сокращением/исключением"). А именно, если длина информационных битов LDPC в LDPC-кодере равна Kldpc, и сигнальные биты, имеющие длину битов Ksig, вводятся в LDPC-кодер, то сокращается (Kldpc-Ksig) битов. В этом документе сокращение означает заполнение (Kldpc-Ksig) "0"-ыми битами сигнальных битов для LDPC-кодирования, а после LDPC-кодирования - удаление заполненных "0"-ых битов, либо уменьшение размера матрицы контроля четности в LDPC-кодере, что обладает таким же эффектом, как сокращение на основе заполнения и удаления. Кроме того, исключение означает изъятие из передачи некоторых кодирующих битов, главным образом битов четности.

[31] Сторона передачи вещательной системы/системы связи может использовать два каскадных кодера. Например, кодер, который каскадирует код Боуза, Чоудхури, Хоквингема (BCH) с LDPC-кодом, то есть BCH/LDPC-кодер, принимает информационные биты BCH (информацию BCH или информационные биты), содержащие Kbch битов, и выводит кодированные биты BCH (или кодовое слово BCH, или кодированный BCH-блок), содержащие Nbch битов. Nbch равно количеству информационных битов LDPC, Kldpc и Nbch битов также могут называться информационными битами LDPC (или некодированным LDPC-блоком), которые являются информацией, введенной в LDPC-кодер. Кодированные биты BCH, то есть информационные биты LDPC, вводятся в LDPC-кодер и выводятся в виде кодированных битов LDPC, кодированного LDPC-блока или кодового слова LPDC, имеющего длину Nldpc.

[32] Когда информационное слово, которое включает в себя сигнальные биты, имеющие переменную длину, вводится в кодер, сторона передачи выполняет сокращение/исключение по отношению к кодовому слову, выведенному из кодера. То есть сигнальные биты, имеющие длину битов Ksig, вводятся в BCH/LDPC-кодер, и сокращается (Kbch-Ksig) битов. Как описано выше, сокращение означает, что (Kbch-Ksig) "0"-ых битов заполняются во входные сигнальные биты и кодируются по BCH/LDPC, а затем заполненные "0"-ые биты удаляются.

[33] Как описано выше, сокращение уменьшает кодовую скорость, так что когда увеличивается количество битов, которые необходимо сократить (то есть длина битов сокращения), эффективность кодирования повышается. Однако, когда кодируется сигнальная информация, предпочтительно, чтобы эффективность кодирования не менялась с длиной входной информации. То есть, когда мощность приема в приемнике постоянна, предпочтительно, чтобы эффективность не варьировалась с длиной входного информационного слова. Поэтому с помощью регулирования количества битов, которые необходимо исключить (то есть длины битов исключения) в соответствии с количеством битов, которые необходимо сократить, обеспечивается устойчивая эффективность кодирования. Количество битов, которые необходимо исключить, определяется в соответствии с длиной битов входного информационного слова, то есть количеством битов входного информационного слова, так что количество битов, которые необходимо исключить, зависит от количества битов входного информационного слова.

[34] Ниже будут описываться варианты осуществления для определения входного параметра, используемого для исключения, то есть количества битов Npunc, которые следует исключить.

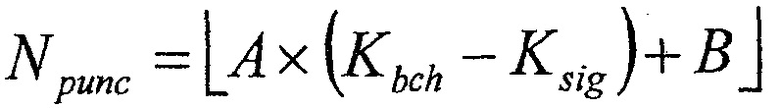

[35] В одном варианте осуществления Npunc может вычисляться с использованием одного из Уравнений с (1) по (4).

[36] Уравнение (1) используется, когда каскадируется BCH-код, а Уравнение (2) используется, когда BCH-код не каскадируется. То есть, когда BCH-код каскадируется, количество битов, которые следует сократить, равно (Kbch-Ksig), так что Npunc может вычисляться с использованием Уравнения (1).

[37]

[38] … (1)

[39] Когда BCH-код не каскадируется, количество битов, которые следует сократить, равно (Kldpc-Ksig), так что Npunc может вычисляться с использованием Уравнения (2).

[40]

[41] … (2)

[42] В Уравнениях (1) и (2) A указывает отношение количества битов, которые следует сократить, к количеству битов, которые необходимо исключить, а (Kbch-Ksig) и (Kldpc-Ksig) указывают количество битов, которые следует сократить. Kbch указывает количество информационных битов BCH (то есть длину информационных битов), введенных для формирования кодированных битов BCH, включающих в себя Kldpc битов, посредством BCH-кодирования. Kldpc указывает количество информационных битов LDPC, введенных для формирования кодированных битов LDPC. Ksig указывает длину битов информационного слова, введенного в кодер, перед сокращением. B указывает поправочный коэффициент. Операция  указывает функцию "ближайшее меньшее целое" и означает наибольшее целое число, меньше либо равное x.

указывает функцию "ближайшее меньшее целое" и означает наибольшее целое число, меньше либо равное x.

[43] Когда количество битов, которые необходимо исключить, вычисляется на основе Уравнений (1) или (2), можно получить кодовую скорость меньше, чем когда сокращение и исключение не выполняются. В вышеприведенном описании, если B равен 0, то его можно опустить.

[44] В качестве альтернативы, когда Npunc вычисляется с использованием Уравнений (3) или (4), можно получить кодовую скорость меньше, чем когда сокращение и исключение не выполняются.

[45] Точнее говоря, когда BCH-код каскадируется, количество битов, которые следует сократить, равно (Kbch-Ksig), так что Npunc может вычисляться с использованием Уравнения (3).

[46]

[47]  … (3)

… (3)

[48] Когда BCH-код не каскадируется, количество битов, которые следует сократить, равно (Kldpc-Ksig), так что Npunc может вычисляться с использованием Уравнения (4).

[49]

[50]  … (4)

… (4)

[51] В Уравнениях (3) и (4) A указывает отношение количества битов, которые необходимо сократить, к количеству битов, которые необходимо исключить, а (Kbch-Ksig) и (Kldpc-Ksig) указывают количество битов, которые необходимо сократить. Kbch указывает количество информационных битов BCH (то есть длину информационных битов), введенных для формирования кодированных битов BCH, состоящих из Kldpc битов, посредством BCH-кодирования. Kldpc указывает количество информационных битов LDPC, введенных для формирования кодированных битов LDPC. Ksig указывает длину битов информационного слова, введенного в кодер, перед сокращением. B указывает поправочный коэффициент. Ksig_min указывает длину битов самого короткого информационного слова среди информационных слов, которые можно ввести в кодер.

[52] В Уравнениях (3) и (4) Npunc меньше количества битов четности, Nparity, только когда выполняется условие B<Nparity-A(Kldpc-Ksig_min).

[53] В Уравнениях с (1) по (4) Npunc может изменяться в соответствии с параметрами A и B. Соответственно, кодовая скорость может изменяться в соответствии с A и B. Когда вводится Kldpc битов и выводится Nldpc кодированных битов, кодовая скорость LDPC-кода, R, может вычисляться с использованием Уравнения (5).

[54]  … (5)

… (5)

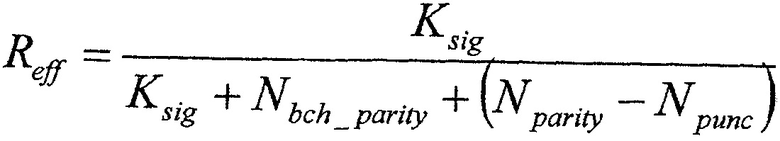

[55] Для Ksig битов входного информационного слова эффективная кодовая скорость Reff после сокращения и исключения вычисляется с использованием Уравнения (6).

[56]  … (6)

… (6)

[57] В Уравнении (6) Nbch_parity указывает количество битов четности BCH-кода, которое равно 0, когда BCH-код не используется.

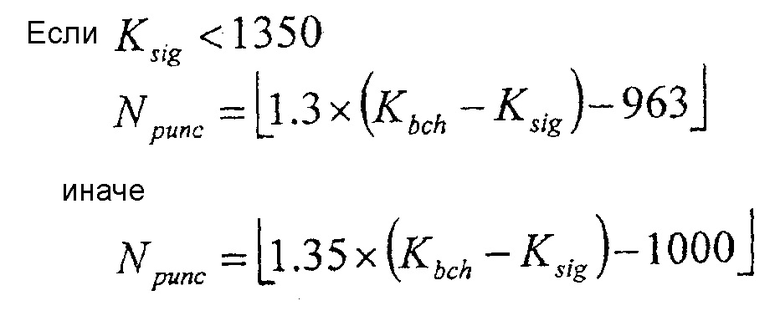

[58] Фиг. 1 - график, иллюстрирующий изменение эффективной кодовой скорости в соответствии с вариантом осуществления настоящего изобретения. В частности, фиг. 1 иллюстрирует изменение кодовой скорости для Kbch=2100, Kldpc=2160 и Nldpc=8640, когда A=1,35 и B=3320 применяются в Уравнении (3), и когда A=1,32 и B=3320 применяются в Уравнении (3). Как показано, кодовая скорость для передачи информации меняется вместе с A, то есть когда A увеличивается, кодовая скорость также увеличивается.

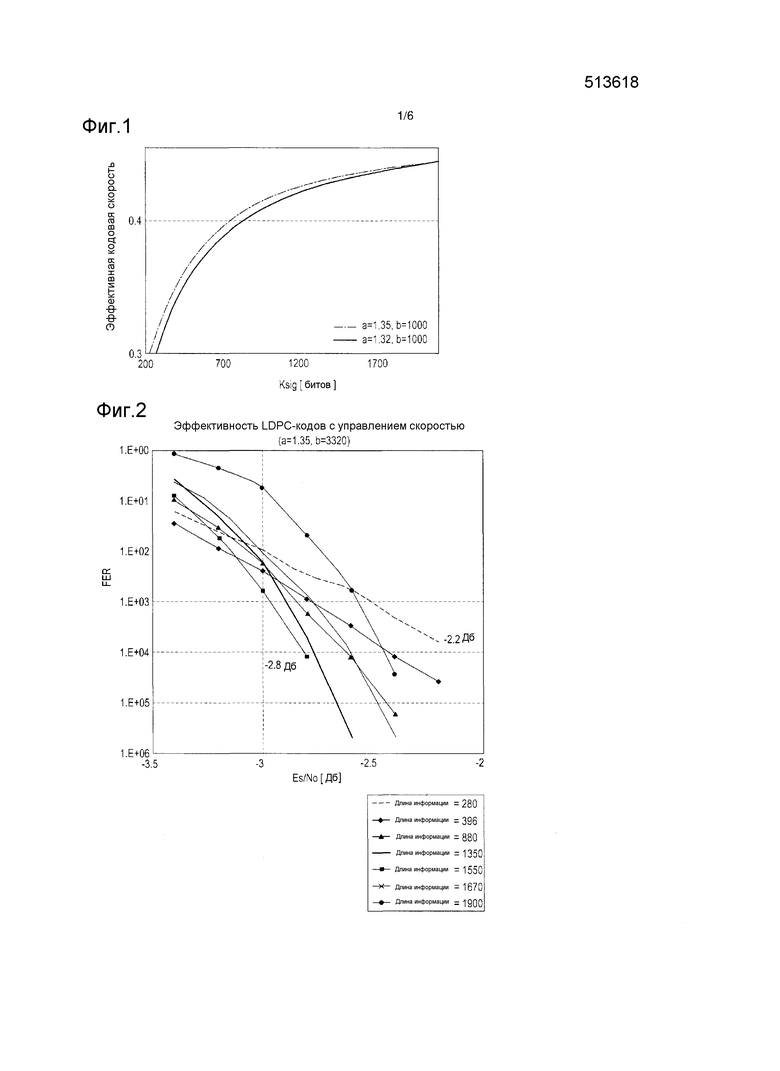

[59] Фиг. 2 иллюстрирует частоту появления ошибочных кадров (FER) кодового слова относительно различных длин информационных битов: 280, 396, 880, 1350, 1550, 1670 и 1900 для A=1,35 и B=3320.

[60] Ссылаясь на фиг. 2, когда количество входных информационных битов, Ksig, равно 280, возникает снижение эффективности. Поэтому для FER=10e-4 разница эффективности между наилучшей эффективностью и наихудшей эффективностью составляет 0,7 дБ.

[61] Фиг. 3 иллюстрирует FER кодового слова относительно различных длин информационных битов: 280, 396, 880, 1350, 1550, 1670, 1900 для A=1,32 и B=3320.

[62] Ссылаясь на фиг. 3, кодовая скорость меньше таковой на фиг. 2, так что достигается повышение общей эффективности. В частности, когда количество входных информационных битов, Ksig, равно 1350, эффективность гораздо лучше, чем в других случаях. Также видно, что для FER=10e-4 разница эффективности между наилучшей эффективностью и наихудшей эффективностью составляет 0,7 дБ.

[63] Как описано выше, предпочтительно, чтобы эффективность кодирования не сильно варьировалась с длиной входных информационных битов. Таким образом, необходим способ для регулирования A и B в Уравнениях с (1) по (4) в соответствии с длиной входных информационных битов.

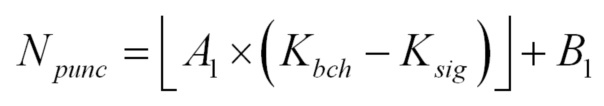

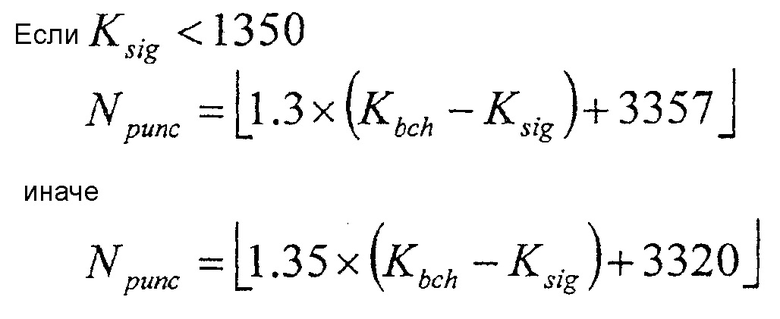

[64] Поэтому в соответствии с вариантом осуществления настоящего изобретения Npunc определяется с использованием Уравнений (7) и (8).

[65]  … (7)

… (7)

[66]  … (8)

… (8)

[67] В Уравнениях (7) и (8) разные значения A и B, то есть A1 и B1 или A2 и B2, используются в соответствии с длиной входных информационных битов.

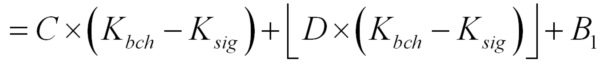

[68] Если B1 является целым числом, то Уравнение (7) можно привести к следующему Уравнению (7a).

[69]  … (7a)

… (7a)

[70] Если A1=C+D (где C - целое число, а D - вещественное число), то Уравнение (7) можно привести к следующему Уравнению (7b).

[71]

[72]  … (7b)

… (7b)

[73] Также Уравнение (8) можно изменить аналогично Уравнениям (7a) и (7b).

[74] В Уравнениях (7) и (8) разделяется случай длины входных информационных битов меньше заранее установленного порогового значения Kth и случай длины входных информационных битов больше порогового значения Kth. Однако для разделения случая длины входных информационных битов может использоваться множество пороговых значений, так что могут использоваться две или более пары A и B.

[75] Kth можно определить опытным путем, чтобы не вызывать разницы в эффективности кодирования с Npunc. В частности, значение, соответствующее случаю, где эффективность относительно хорошая, или случаю, где эффективность относительно плохая, определяется как Kth. К тому же разные пары параметров (A1, B1) и (A2, B2) определяются так, что для Ksig=Kth значения Npunc равны друг другу.

[76] Как описано выше, количество битов, которые необходимо исключить, предпочтительно регулируется в соответствии с количеством битов, которые необходимо сократить, и количество битов, которые необходимо сократить, определяется в соответствии с длиной битов входного информационного слова. Таким образом, A1 и A2, указывающие отношения количества битов, которые необходимо сократить, к количеству битов, которые необходимо исключить, могут быть постоянными значениями, определенными в соответствии с длиной битов входного информационного слова. Поэтому B1 и B2 могут определяться как постоянные значения.

[77] Как только Npunc определяется, как описано выше, сторона передачи исключает биты четности из кодированных битов, сформированных путем кодирования входных информационных битов, с помощью Npunc.

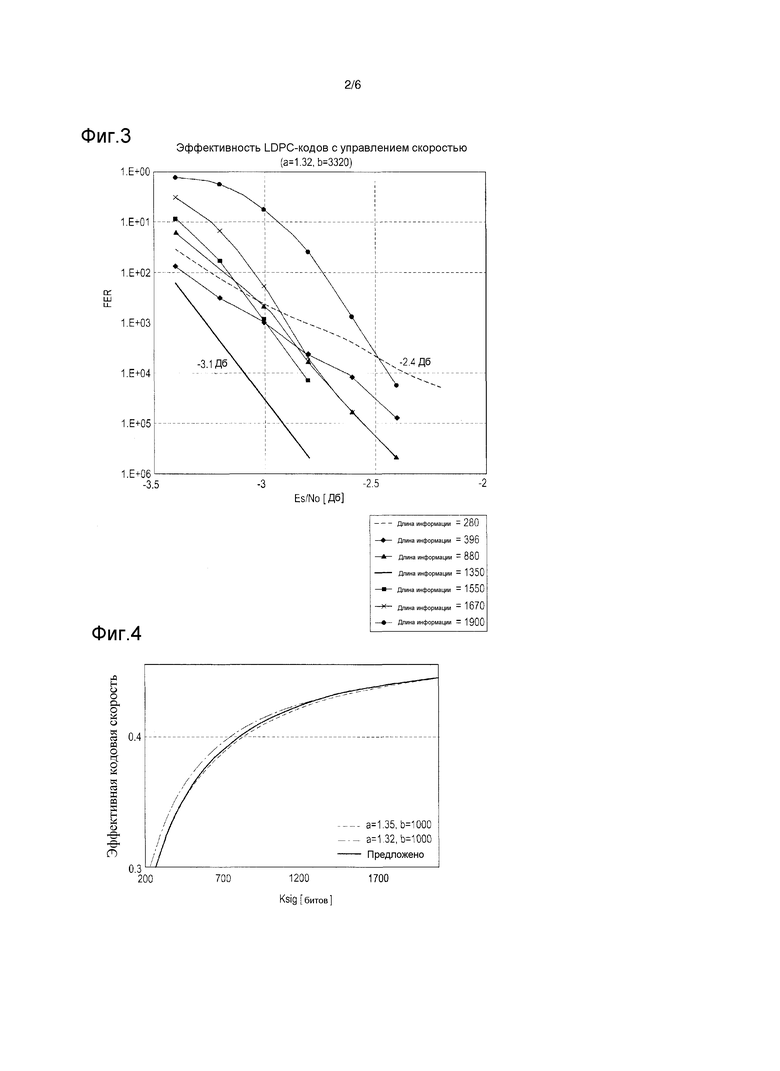

[78] Фиг. 4 - график, иллюстрирующий изменение эффективной кодовой скорости в соответствии с вариантом осуществления настоящего изобретения, где A=1,35 и B=3320 в Уравнении (3), и A=1,32 и B=3320 в Уравнении (3) сравниваются с использованием Уравнений (7) и (8), что помечается как "Предложено".

[79] В частности, "Предложено" указывает, что Kbch=2100, Kldpc=2160, Nldpc=8640, A1=1,3, B1=3357, A2=1,35, B2=3320 и Kth=1350 применяются в Уравнении (7). Как проиллюстрировано на фиг. 4, когда Ksig больше 1350, что равно Kth, "Предложенный" случай показывает такую же кодовую скорость, как и при A=1,35 и B=3320 в Уравнении (3).

[80] Фиг. 5 - график, иллюстрирующий FER в соответствии с вариантом осуществления настоящего изобретения. В частности, фиг. 5 иллюстрирует характеристику FER относительно различных длин информационных битов: 280, 396, 880, 1350, 1550, 1670 и 1900.

[81] Ссылаясь на фиг. 5, для длины входных информационных битов в 280 кодовая скорость меньше проиллюстрированной на фиг. 2, так что эффективность лучше. Для длины входных информационных битов в 1350 кодовая скорость больше проиллюстрированной на фиг. 3, так что возникает снижение эффективности. Поэтому разница общей эффективности составляет 0,3 дБ, и разница эффективности кодирования уменьшается по сравнению с фиг. 2 и 3.

[82] В вышеприведенном описании количество битов Npunc, которые необходимо исключить, вычисляется с использованием вышеупомянутых уравнений. Однако в нижеследующем описании значение, полученное с использованием вышеупомянутых уравнений, предполагается промежуточным значением Npunc, то есть промежуточным количеством битов Npunc_temp, которые необходимо исключить, и посредством нескольких процессов Npunc получается точнее.

[83] В соответствии с вариантом осуществления настоящего изобретения сторона передачи при выполнении исключения с использованием Npunc может точнее регулировать Npunc в соответствии с дополнительными параметрами, например количеством битов четности BCH, порядком модуляции и т. п. Ниже будет описываться процедура для вычисления окончательного количества битов, которые необходимо исключить, с использованием Npunc_temp.

[84] Этап 1:

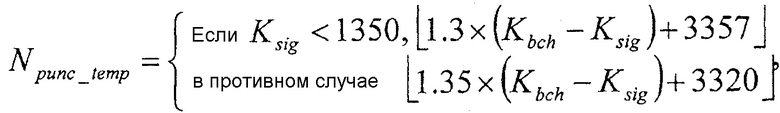

[85] Промежуточное количество битов Npunc_temp, которые необходимо исключить, вычисляется с использованием Уравнения (9), которое практически такое же, как вышеописанное Уравнение (7) и связанное с ним описание.

[86]  …(9)

…(9)

[87] Используется LDPC-код, каскадированный с BCH-кодом, и в Уравнении (9) используются значения (A1, B1)=(1,3, 3357) и (A2, B2)=(1,35, 3320) из фиг. 4.

[88] Этап 2:

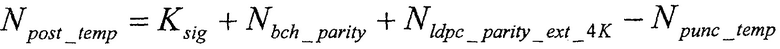

[89] Промежуточное количество битов Npost_temp, которые необходимо кодировать, вычисляется с использованием Npunc_temp, как показано в Уравнении (10).

[90]  …(10)

…(10)

[91] В Уравнении (10) Ksig указывает количество входных информационных битов, как описано выше, и может указывать, например, количество битов сигнальной информации. Nbch_parity указывает количество битов четности BCH, а Nldpc_parity_ext_4K указывает постоянное значение, определенное в соответствии с типом LDPC-кода.

[92] Этап 3:

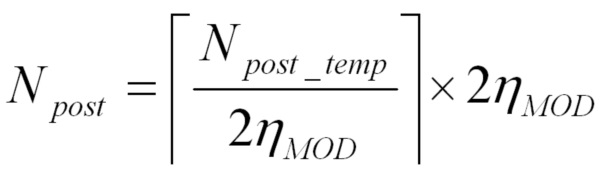

[93] Принимая во внимание Npost_temp и порядок модуляции, окончательное количество битов, которые необходимо кодировать (количество битов каждого LDPC-блока), вычисляется с использованием Уравнения (11a):

[94]  …(11a)

…(11a)

[95] В Уравнении (11a) ηMOD указывает порядок модуляции, который равен 1, 2, 4 и 6 для двухпозиционной фазовой манипуляции (BPSK), квадратурной PSK (QPSK), 16-позиционной квадратурной амплитудной модуляции (16-QAM) и 64-позиционной QAM (64-QAM) соответственно.

[96] Определение количества кодированных битов каждого блока информационного слова, Npost, как показано в Уравнении (11a), заставляет Npost быть величиной, кратной количеству столбцов в блочном перемежителе. Блочный перемежитель, хотя не показан и дополнительно не описан, используется, когда биты каждого LDPC-блока позже перемежаются побитово.

[97] Когда блочный перемежитель не используется, например, когда используются только BPSK и QPSK, Уравнение (11a) можно преобразовать в Уравнение (11b).

[98]  …(11b)

…(11b)

[99] Этап 4:

[100] Количество битов Npunc, которые необходимо исключить из битов четности каждого LDPC-блока, вычисляется с использованием Уравнения (12).

[101] Npunc = Npunc_temp - (Npost - Npost_temp) …(12)

[102] Фиг. 6 - блок-схема последовательности операций, иллюстрирующая процедуру для исключения битов четности на основе длины входных информационных битов в соответствии с вариантом осуществления настоящего изобретения.

[103] Ссылаясь на фиг. 6, на этапе 600 определяется количество входных информационных битов, включая сигнальную информацию для передачи (то есть длина входных информационных битов). На этапе 602 сторона передачи проверяет параметры для вычисления количества битов, которые необходимо исключить, то есть длины битов исключения. А именно, сторона передачи определяет, выбрать ли (A1, B1) или (A2, B2), в соответствии с длиной входных информационных битов, используя Уравнения (7) и (8). Хотя и не показано, одна из двух или более заранее установленных пар параметров может выбираться в соответствии с длиной входных информационных битов. В качестве альтернативы на этапе 602 сторона передачи может получить значения параметров (A1, B1)=(1,3, 3357) или (A2, B2)=(1,35, 3320), которые необходимо использовать в Уравнении (9), в соответствии с результатом сравнения длины входных информационных битов с заранее установленным пороговым значением, равным 1350.

[104] На этапе 604 количество битов четности, которые необходимо исключить (то есть длина битов четности к исключению), вычисляется на основе определенных параметров, например, используя Уравнения 7 и 8 или Уравнения с (9) по (12). На этапе 606 биты четности кодового слова исключаются на основе вычисленной длины битов четности к исключению.

[105] Биты четности, сформированные по отношению к сигнальным битам, которые являются входными информационными битами, могут передаваться распределенным образом посредством того же кадра, что и кадр, в котором передаются сигнальные биты, и предыдущего кадра. Биты четности, переданные посредством того же кадра, что и кадр, который переносит сигнальные биты, в этом документе будут называться первой четностью, а биты четности, переданные посредством предыдущего кадра, в этом документе будут называться второй четностью или дополнительной четностью.

[106] Фиг. 7 - схема, которая иллюстрирует структуру кадра для передачи двух типов битов четности в соответствии с вариантом осуществления настоящего изобретения.

[107] Ссылаясь на фиг. 7, сигнальные биты Уровня-1 передаются посредством i-го кадра 702; первая четность 710, сформированная для сигнальных битов, передается посредством i-го кадра 702 вместе с сигнальными битами; и дополнительная четность 712 передается посредством (i-1)-го кадра 700.

[108] В соответствии с вариантом осуществления настоящего изобретения сторона приема выполняет декодирование на основе сигнальных битов и первой четности 710, принятой посредством i-го кадра 702. Если декодирование терпит неудачу, то сторона приема также выполняет декодирование с использованием дополнительной четности 712, принятой посредством (i-1)-го кадра 700.

[109] В соответствии с другим вариантом осуществления настоящего изобретения, если декодирование относительно сигнальных битов и первой четности 710 терпит неудачу, то сторона приема определяет, что декодирование относительно сигнальных битов терпит неудачу, сохраняет дополнительную четность, включенную в i-ый кадр 702, а затем принимает (i+1)-ый кадр.

[110] В соответствии с еще одним вариантом осуществления настоящего изобретения сторона приема всегда сохраняет дополнительную четность 712, принятую посредством (i-1)-го кадра 700, и выполняет декодирование на основе сигнальных битов и первой четности 710, принятой посредством i-го кадра 702, и сохраненной дополнительной четности 712.

[111] Ниже будет подробнее описываться способ для определения количества битов дополнительной четности.

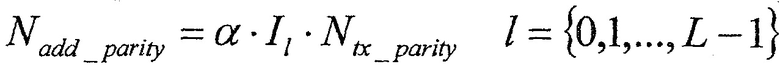

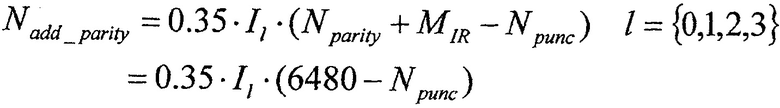

[112] В соответствии с вариантом осуществления настоящего изобретения количество битов дополнительной четности может выражаться с использованием Уравнения (13).

[113]  …(13)

…(13)

[114] В Уравнении (13) α·Il указывает отношение количества битов первой четности к количеству битов дополнительной четности, где α может быть постоянным значением, Ii может выбираться между 0 и L-1, и L1 указывает отношение дополнительной четности L1. Ii может передаваться посредством отдельной сигнализации "L1_AP_RATIO". Когда Ii=0, биты дополнительной четности не используются. Ntx_parity указывает количество битов четности, переданных посредством того же кадра, что и кадр для информационного слова (то есть битов первой четности), и также может означать количество битов четности, которые необходимо фактически передать. В этом случае Ntx_parity может вычисляться в виде Nparity - Npunc.

[115] Фиг. 8 - схема, иллюстрирующая LDPC-код для поддержки передачи четности в соответствии с вариантом осуществления настоящего изобретения.

[116] Ссылаясь на фиг. 8, кодовое слово LPDC включает в себя Kldpc информационных битов 800 LDPC, Nparity битов 802 четности и MIR битов 804 четности с нарастающей избыточностью (IR). Для удобства Nparity битов 802 четности и MIR битов 804 четности с IR в этом документе вместе называются битами четности. Структура LDPC-кода, проиллюстрированная на фиг. 8, разрабатывается с учетом битов 802 четности. Поэтому при исключении биты 804 четности с IR исключаются. LDPC-код из фиг. 8 может быть выражен в виде битов четности без установления различий между битами 802 четности и битами 804 четности с IR.

[117] Чтобы кодировать сигнальные биты 806, информационные биты 800 LDPC могут включать в себя сигнальные биты 806, биты 807 четности для BCH-кода и "0"-ые заполняющие биты 808 для сокращения. Биты 802 четности и биты 804 четности с IR включают в себя неисключенные биты 810 четности и исключенные биты 812 четности. В этом документе точное положение (то есть индекс) каждого бита не является существенным для предмета настоящего изобретения, а именно, какие биты между битами 802 четности и битами 804 четности с IR нужно исключать, а какие биты между ними исключать не нужно. Соответственно, конкретный шаблон исключения в этом документе описываться не будет.

[118] Биты 807 четности BCH-кода существуют, когда используется каскадный код из BCH-кода и LDPC-кода, и биты 807 четности BCH будут отброшены, когда используется только LDPC-код.

[119] Сигнальные биты 806, биты 807 четности BCH и неисключенные биты 810 четности образуют первую часть 814, которая передается позже посредством i-го кадра 702, как проиллюстрировано на фиг. 7. Некоторые из исключенных битов 812 четности образуют дополнительную четность 816, которая передается позже посредством (i-1)-го кадра 700, как проиллюстрировано на фиг. 7. То есть некоторые из исключенных битов 812 четности являются тем же самым, что и дополнительные четности 807 и 712.

[120] Дополнительная четность 708 может определяться разными способами. Например, исключенные биты 812 четности предпочтительно могут выбираться в качестве дополнительной четности.

[121] Для Kbch=2100, Kldpc=2160, Nldpc=4320 и MIR=4320, Rldpc=Kldpc/Nldpc=1/2 и RIR=Kldpc/(Nldpc+Mldpc)=1/4. В этом случае в соответствии с вариантом осуществления настоящего изобретения Npunc может вычисляться на основе Уравнения 7 с использованием Уравнения (14) ниже.

[122]  …(14)

…(14)

[123] В Уравнении (14) A1=1,3, B1=3357, A2=1,35, B2=3320 и Kth=1350. Поэтому из битов 802 четности и битов 804 четности с IR исключается Npunc битов четности на основе Уравнения (14).

[124] В соответствии с другим вариантом осуществления настоящего изобретения можно исключить Npunc битов четности, полученных на основе Npunc_temp в Уравнении (9) с использованием Уравнений с (10) по (12).

[125] Точные значения параметров, используемые для вычисления Npunc, можно определить в соответствии со схемой модуляции, используемой для передачи, и количеством символов мультиплексирования с ортогональным частотным разделением каналов (OFDM). Например, когда 2n-квадратурная амплитудная модуляция (QAM) используется в качестве схемы модуляции, количество битов (Ksig+Nbch_parity+Nparity+MIR-Npunc), которые необходимо передавать, является величиной, кратной n. В этом документе Ksig указывает количество входных битов сигнальной информации, Nbch_parity указывает количество битов четности BCH-кода, а n указывает порядок схемы модуляции.

[126] Количество битов дополнительной четности 712 из фиг. 7 или дополнительной четности 816 из фиг. 8 может вычисляться с использованием Уравнения (15).

[127]  …(15)

…(15)

[128] В Уравнении (15) I0=0, I1=1, I2=2 и I3=3. Кроме того, α=0,35 применяется в Уравнении (13), где α является значением, выбранным, чтобы удовлетворять Уравнению (16) ниже.

[129]

[130] …(16)

[131] То есть α определяется как максимальное значение среди значений, в которых сумма количества битов первой четности, Ntx_parity, и количества битов дополнительной четности, Nadd_parity, которые передаются, когда Il является максимальным значением IL-1 и Ksig является максимальной длиной среди входных информационных битов, Ksig_max, то есть (Ntx_parity + Nadd_parity), является максимальной, и эта сумма меньше (Nparity + MIR).

[132] Когда максимальная длина среди входных информационных битов, Ksig_max, равна 2100, Npunc=3320, так что Ntx_parity=3160, а когда Il является максимальным значением IL-1=I3=3, Nadd_parity=0,35×3×3160 = 3318, так что Ntx_parity + Nadd_parity=6478, что меньше Nparity + MIR=6480.

[133] Ниже будет описываться вариант осуществления для получения более точного Nadd_parity с учетом схемы модуляции, используемой для передачи на основе Nadd_parity, полученной посредством вышеупомянутых уравнений.

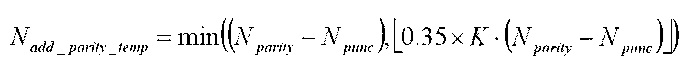

[134] Уравнение (16) предполагает, что используется схема модуляции BPSK. То есть α определяется так, что количество битов первой четности и количество битов дополнительной четности, переданных при использовании схемы модуляции BPSK, меньше Nparity+MIR. Поэтому, когда используется другая схема модуляции, например QPSK, 16-QAM или 64-QAM, необходима поправка относительно Nadd_parity, чтобы количество битов первой четности и количество битов дополнительной четности было меньше Nparity + MIR. Поэтому количество промежуточных битов дополнительной четности можно получить с использованием Уравнения (17).

[135]  …(17)

…(17)

[136] В Уравнении (17) K указывает отношение дополнительной четности L1 и является другим выражением Ii из Уравнений (13) и (15). В соответствии с вариантом осуществления настоящего изобретения K может передаваться от передатчика к приемнику посредством сигнализации "L1_AP_RATIO". Например, "L1_AP_RATIO" является 2-битным параметром, и когда этот параметр равен "00", K=0; для параметра "01" K=1; K=2 для параметра "10"; и K=3 для параметра "11".

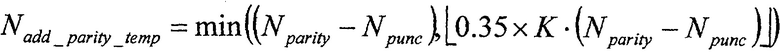

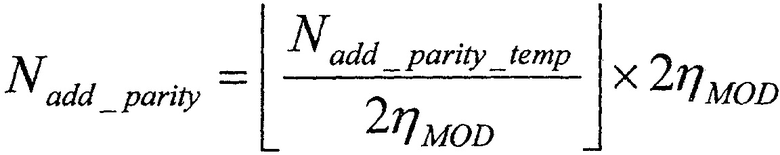

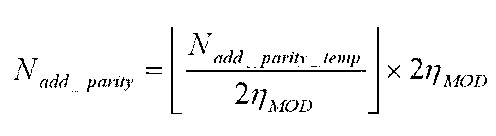

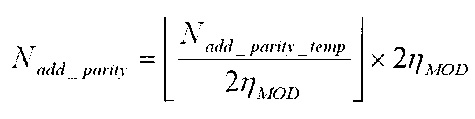

[137] Принимая во внимание Nadd_parity_temp из Уравнения (17) и порядок модуляции, окончательное количество битов дополнительной четности можно вычислить с использованием Уравнения (18a).

[138]  …(18a)

…(18a)

[139] В Уравнении (18a) ηMOD указывает порядок модуляции, который равен 1, 2, 4 и 6 для BPSK, QPSK, 16-QAM и 64-QAM соответственно.

[140] Количество битов дополнительной четности, Nadd_parity, регулируется в Уравнении (18a), чтобы предписать Nadd_parity быть величиной, кратной количеству столбцов в блочном перемежителе. Блочный перемежитель используется, когда каждый бит дополнительной четности перемежается побитно.

[141] Когда блочный перемежитель не используется, например, когда используются только BPSK и QPSK, Уравнение (18a) можно преобразовать в Уравнение (18b).

[142]  …(18b)

…(18b)

[143] Nadd_parity определяется в соответствии с количеством символов OFDM, используемых для передачи.

[144] Информация о количестве битов дополнительной четности может передаваться от передатчика приемнику посредством сигнального параметра "L1_AP_SIZE". Если для передачи используется множество кодированных LDPC-блоков, то L1_AP_SIZE указывает произведение количества кодированных блоков и Nadd_parity. Например, когда используются два кодированных блока, "L1_AP_SIZE" может указывать 2×Nadd_parity. Приемник может узнать количество битов дополнительной четности из этого сигнального параметра.

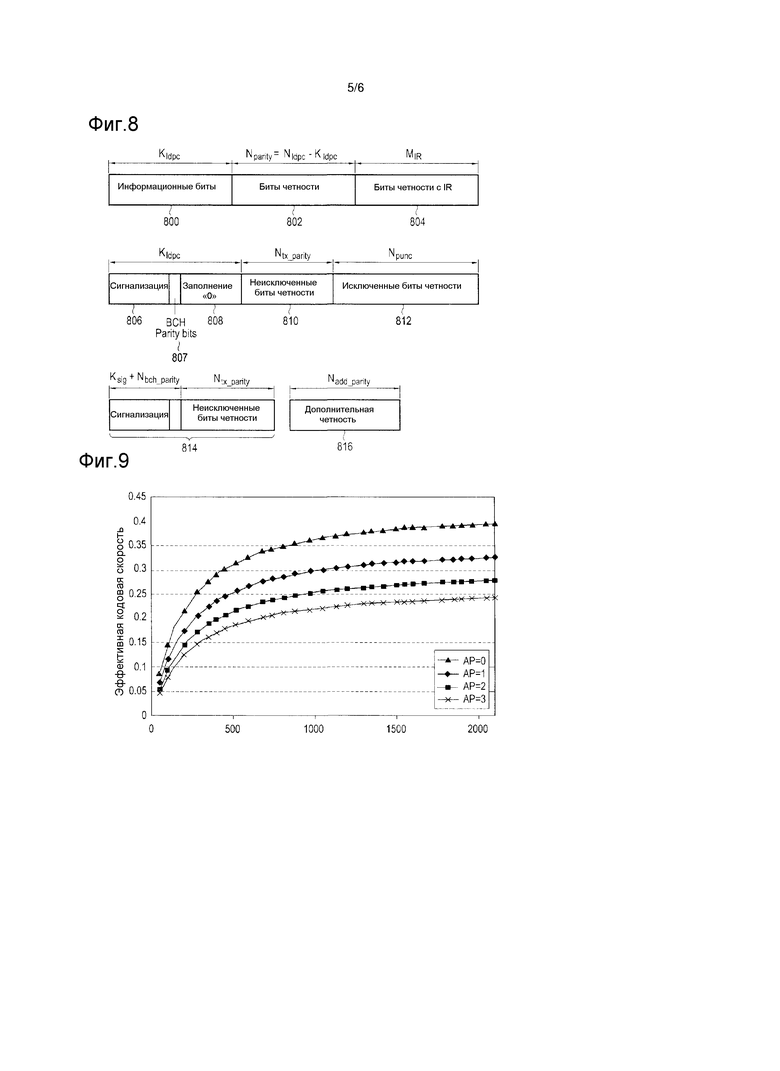

[145] Фиг. 9 - график, иллюстрирующий кодовую скорость, когда количество битов дополнительной четности вычисляется с использованием Уравнения (15), в соответствии с вариантом осуществления настоящего изобретения.

[146] В частности, кодовая скорость вычисляется с использованием Уравнения (19).

[147]  …(19)

…(19)

[148] В Уравнении (19) Ntx_parity указывает количество битов четности в первой части 814 из фиг. 8, и Nldpc + MIR - Npunc=6480-Npunc. Nadd_parity указывает количество битов дополнительной четности в части 816 из фиг. 8.

[149] На фиг. 9 Дополнительная четность (AP)=0 соответствует кодовой скорости для I0=0, при которой дополнительная четность не используется, AP=1 соответствует кодовой скорости для I1=1, AP=2 соответствует кодовой скорости для I2=2, и AP=3 соответствует кодовой скорости для I3=3.

[150] В соответствии с другим вариантом осуществления настоящего изобретения биты 804 четности с IR в LDPC-коде на фиг. 8 могут использоваться выборочно. То есть биты 802 четности предпочтительно формируются для битов входного информационного слова, а биты 804 четности с IR могут формироваться, только когда необходима четность с IR, посредством этого повышая эффективность кодирования/декодирования.

[151] Как описано выше, биты 802 четности предпочтительно формируются для входных информационных битов, и для битов 802 четности Npunc может вычисляться на основе Уравнения (7), как показано в Уравнении (20).

[152]  …(20)

…(20)

[153] В Уравнении (20), если Npunc является положительным целым числом, то формируются только биты 802 четности, и исключается только Npunc битов четности из битов 802 четности. Однако, если Npunc является отрицательным значением, то формируются биты 802 четности и биты 804 четности с IR, а затем исключается только (MIR + Npunc) битов из битов 804 четности с IR.

[154] В соответствии с другим вариантом осуществления настоящего изобретения исключается Npunc (полученное с использованием Уравнений с (10) по (12), на основе Уравнения (20)) битов четности.

[155] Фиг. 10 - блок-схема последовательности операций, иллюстрирующая процедуру для определения количества двух типов битов четности в соответствии с вариантом осуществления настоящего изобретения.

[156] Ссылаясь на фиг. 10, на этапе 1000 количество битов четности, которые необходимо исключить, вычисляется с использованием Уравнений (7) и (8) или Уравнений с (9) по (12). На этапе 1002 определяются параметры α, Il и Ntx_parity, которые используются в Уравнении (13), (15) и (17). На этапе 1002 могут использоваться уже определенные α или Il, и Il выражается в виде K в Уравнениях (17) и (18). Как описано выше, K может указываться отдельной сигнализацией "L1_AP_RATIO".

[157] На этапе 1004 количество битов дополнительной четности, Nadd_parity, определяется на основе Уравнения (13) или Уравнений (17) и (18), используя параметры, определенные на этапе 1002. На этапе 1006 биты дополнительной четности конфигурируются в соответствии с вычисленным количеством битов дополнительной четности.

[158] Фиг. 11 - блок-схема стороны передачи в соответствии с вариантом осуществления настоящего изобретения.

[159] Ссылаясь на фиг. 11, сторона передачи включает в себя кодер 1101, исключающий блок 1103, контроллер 1105, модулятор 1107, радиочастотный (РЧ) процессор 1109 и, выборочно, блок 1111 конфигурирования дополнительной четности.

[160] Кодер 1101 выводит кодированные биты, сформированные путем кодирования битов информационного слова для передачи. Например, когда используется BCH/LDPC-код, кодер 1101 кодирует информационные биты BCH, содержащие Kbch битов, чтобы сформировать кодовое слово BCH, содержащее Kldpc битов. После этого кодер 1101 выполняет LDPC-кодирование над кодовым словом BCH, соответственно формируя и выводя кодовое слово LPDC, содержащее Nldpc битов.

[161] В качестве альтернативы кодер 1101 формирует и выводит кодовое слово LPDC, содержащее (Nldpc + MIR) битов.

[162] Хотя и не проиллюстрировано, информационные биты BCH, содержащие Kbch битов, могут конфигурироваться путем заполнения (Kbch - Ksig) "0"-ыми битами Ksig входных информационных битов. Заполненные (Kbch - Ksig) "0"-ых битов не должны передаваться.

[163] Исключающий блок 1103 исключает кодовое слово, предоставленное от кодера 1101, в соответствии с шаблоном исключения и длиной битов исключения (Kbch - Ksig), которые предоставляются от контроллера 1105. Контроллер 1105 вычисляет длину битов исключения в соответствии с количеством информационных битов для управления исключающим блоком 1103. Например, контроллер 1105 определяет A и B в соответствии с количеством входных информационных битов (или количеством сигнальных битов) для передачи на стороне передачи и предоставляет определенные A и B исключающему блоку 1103.

[164] В качестве альтернативы контроллер 1105 получает количество битов, которые необходимо исключить, из определенных параметров A и B и предоставляет исключающему блоку 1103 полученное количество битов, которые необходимо исключить. Модулятор 1107 в соответствии с соответствующей схемой модуляции модулирует и выводит сигнал, предоставленный от исключающего блока 1103. РЧ-блок 1109 преобразует модулированный сигнал, предоставленный от модулятора 1107, в высокочастотный сигнал и передает высокочастотный сигнал посредством антенны.

[165] Если должны передаваться биты дополнительной четности, то контроллер 1105 определяет количество битов дополнительной четности, как проиллюстрировано на фиг. 10, и предоставляет определенное количество битов дополнительной четности блоку 1111 конфигурирования дополнительной четности. Блок 1111 конфигурирования дополнительной четности конфигурирует биты дополнительной четности и предоставляет их модулятору 1107. Следует отметить, что дополнительные четности, сформированные в текущем кадре, передаются посредством предыдущего кадра.

[166] Предполагая LDPC-кодирование (Nldpc, Kldpc), (Kldpc - Ksig) битов сокращается для длины входных информационных битов Ksig. Если каскадируется BCH-код, то (Kbch - Ksig) битов сокращается для длины информационных битов BCH Kbch.

[167] Фиг. 12 - блок-схема стороны приема в соответствии с вариантом осуществления настоящего изобретения.

[168] Ссылаясь на фиг. 12, сторона приема включает в себя РЧ-блок 1200, демодулятор 1202, сокращающий/исключающий процессор 1204, декодер 1206, контроллер 1208 и, выборочно, блок 1210 обработки дополнительной четности.

[169] РЧ-блок 1200 принимает сигнал, переданный от РЧ-блока 1109 стороны передачи, и предоставляет этот сигнал демодулятору 1202.

[170] Демодулятор 1202 демодулирует сигнал, предоставленный от РЧ-блока 1200, с использованием схемы демодуляции, соответствующей схеме модуляции, использованной в модуляторе 1107 стороны передачи. Например, демодулятор 1202 получает логарифмическое отношение правдоподобия (LLR) путем логарифмирования отношения вероятности того, что каждый бит равен 1, к вероятности того, что каждый бит равен 0, для каждого из сокращенных/исключенных кодированных битов и битов дополнительной четности, переданных от модулятора 1107, и предоставляет полученное LLR сокращающему/исключающему процессору 1204 и блоку 1210 обработки дополнительной четности. Процессор 1201 дополнительной четности является необязательным в том, что он не используется, когда не принимается дополнительная четность.

[171] Сокращающий/исключающий процессор 1204 принимает выходной сигнал демодулятора 1202, формирует значения, соответствующие сокращению и исключению по отношению к битам, сокращенным и исключенным стороной передачи, и заполняет этими значениями выходной сигнал демодулятора 1202. Например, для сокращенного бита значение LLR равно (+) или (-) максимальному значению среди входных значений декодера, а для исключенного бита значение LLR равно "0". Сокращающий/исключающий процессор 1204 принимает от контроллера 1208 информацию о количестве сокращенных и исключенных битов и индексе. То есть контроллер 1208 вычисляет длину битов исключения в соответствии с количеством информационных битов кодера 1101 стороны передачи и управляет сокращающим/исключающим процессором 1204.

[172] Например, контроллер 1208 определяет A и B в соответствии с количеством битов сигнальной информации для передачи на стороне передачи, как проиллюстрировано на фиг. 6, и предоставляет определенные A и B сокращающему/исключающему процессору 1204.

[173] В качестве альтернативы контроллер 1208 получает количество битов, которые необходимо исключить, из определенных параметров A и B и предоставляет сокращающему/исключающему процессору 1204 полученное количество битов, которые необходимо исключить. Информация о количестве входных информационных битов, введенных в кодер стороны передачи, может передаваться контроллеру 1208 приемника посредством, например, дополнительной сигнализации.

[174] Декодер 1206 принимает и декодирует выходные значения сокращающего/исключающего процессора 1204, чтобы восстановить биты информационного слова. Например, когда используется BCH/LDPC-код, декодер 1206 принимает Nldpc или (Nldpc+MIR) значений LLR и выполняет LDPC-декодирование над ними, чтобы восстановить Kldpc битов, а затем восстанавливает Kbch битов информационного слова посредством BCH-декодирования.

[175] Когда передаются биты дополнительной четности, контроллер 1208 определяет количество битов дополнительной четности, как проиллюстрировано на фиг. 10, и предоставляет определенное количество битов дополнительной четности блоку 1210 обработки дополнительной четности. Блок 1210 обработки дополнительной четности принимает от демодулятора 1202 значения LLR для битов дополнительной четности, сформированных стороной передачи, и предоставляет значения LLR декодеру 1206. Декодер 1206 выполняет декодирование с использованием значений, предоставленных от сокращающего/исключающего процессора 1204, и значений, предоставленных от блока 1210 обработки дополнительной четности. Следует отметить, что дополнительные четности, принятые в текущем кадре, используются при декодировании следующего кадра в соответствии с обработкой на передатчике. То есть при декодировании кода, принятого в текущем кадре, используются биты дополнительной четности, принятые в предыдущем кадре.

[176] В соответствии с вышеописанными вариантами осуществления настоящего изобретения с помощью адаптивного выбора скорости сокращения/исключения на основе информации о состоянии канала, необходимой в вещательной системе/системе связи, поддерживается сходная эффективность независимо от длины информационного слова, посредством этого поддерживая стабильность системы.

[177] Несмотря на то, что настоящее изобретение подробно показано и описано со ссылкой на его некоторые варианты осуществления, средним специалистам в данной области техники будет понятно, что в нем могут быть сделаны различные изменения в форме и деталях без отклонения от сущности и объема настоящего изобретения, которые определены нижеследующей формулой изобретения и ее эквивалентами.

Группа изобретений относится к области связи и может быть использована для передачи и приема информации в вещательной системе/системе связи. Техническим результатом является обеспечение стабильности системы. Способ содержит сравнение количества битов информационного слова, которое необходимо передать, с заранее установленным пороговым значением; определение первой пары параметров, если количество битов информационного слова меньше заранее установленного порогового значения; определение второй пары параметров, если количество битов информационного слова не меньше заранее установленного порогового значения; определение количества битов, которые необходимо исключить, на основе одной из первой пары параметров и второй пары параметров; и исключение определенного количества битов, которые необходимо исключить, относительно битов четности кодового слова, сформированного путем кодирования информационного слова. 4 н. и 10 з.п. ф-лы, 12 ил.

1. Способ передачи информации в вещательной системе/системе связи, содержащий этапы, на которых:

сравнивают количество битов информационного слова, которое необходимо передавать, с заранее установленным пороговым значением;

получают заранее установленную первую пару параметров, содержащую первое отношение и первый поправочный коэффициент, если количество битов информационного слова меньше заранее установленного порогового значения;

получают заранее установленную вторую пару параметров, содержащую второе отношение и второй поправочный коэффициент, если количество битов информационного слова не меньше заранее установленного порогового значения;

определяют количество битов, которые необходимо исключить, на основе одной из первой пары параметров и второй пары параметров; и

исключают определенное количество битов, которые необходимо исключить, относительно битов четности кодового слова, сформированного путем кодирования информационного слова,

причем каждое из первого отношения и второго отношения является отношением количества битов, которые необходимо сократить, к количеству битов, которые необходимо исключить; и

причем количество битов, которые необходимо исключить, определяется на основании значения, вычисленного применяя одну из первой пары параметров и второй пары параметров к разности между количеством битов входных данных для кодера и количеством битов информационного слова.

2. Способ по п. 1, в котором этап, на котором определяют количество битов, которые необходимо исключить, содержит этапы, на которых:

вычисляют промежуточное количество битов, которые необходимо исключить, на основе одной из первой пары параметров и второй пары параметров;

вычисляют промежуточное количество кодированных битов на основе вычисленного промежуточного количества битов, которые необходимо исключить;

вычисляют окончательное количество кодированных битов на основе промежуточного количества кодированных битов и порядка модуляции; и

определяют количество битов, которые необходимо исключить, на основе промежуточного количества битов, которые необходимо исключить, промежуточного количества кодированных битов и окончательного количества кодированных битов.

3. Способ по п. 2, в котором промежуточное количество битов, которые необходимо исключить, определяется с помощью:

где Npunc_temp указывает промежуточное количество битов, которые необходимо исключить, Kbch указывает длину битов входных данных кодера Боуза, Чоудхури, Хоквингема (ВСН), Ksig указывает количество битов информационного слова, (1,3, 3357) указывает первую пару параметров, (1,35, 3320) указывает вторую пару параметров и заранее установленное пороговое значение равно 1350.

4. Способ по п. 1, дополнительно содержащий этапы, на которых:

определяют по меньшей мере один третий параметр для определения длины битов дополнительной четности;

определяют длину битов дополнительной четности на основе по меньшей мере одного третьего параметра; и

кодируют информационное слово для формирования битов дополнительной четности на основе длины битов дополнительной четности.

5. Способ по п. 4, в котором по меньшей мере один третий параметр включает в себя отношение количества битов первой четности, переданных в кадре, передающем информационное слово, к количеству битов дополнительной четности, или количество битов первой четности, Ntx_parity.

6. Способ по п. 4, в котором длина битов дополнительной четности определяется с помощью:

где ηMOD указывает порядок модуляции, который равен 1, 2, 4 и 6 для двухпозиционной фазовой манипуляции (BPSK), квадратурной PSK (QPSK), 16-позиционной квадратурной амплитудной модуляции (16-QAM) и 64-позиционной QAM (64-QAM) соответственно, а Nadd_parity_temp определяется с помощью:

где Nparity указывает количество битов четности, Npunc указывает количество битов, которые необходимо исключить, и K указывает отношение дополнительной четности.

7. Способ приема информации в вещательной системе/системе связи, содержащий этапы, на которых:

сравнивают количество битов информационного слова, переданного стороной передачи, с заранее установленным пороговым значением;

получают заранее установленную первую пару параметров, содержащую первое отношение и первый поправочный коэффициент, если количество битов информационного слова меньше заранее установленного порогового значения;

получают заранее установленную вторую пару параметров, содержащую второе отношение и второй поправочный коэффициент, если количество битов информационного слова не меньше заранее установленного порогового значения;

определяют количество битов, которые необходимо исключить, на основе одной из первой пары параметров и второй пары параметров;

формируют значения, соответствующие битам, исключенным стороной передачи, и заполняют сформированными значениями модулированный сигнал принятого сигнала, чтобы сформировать входные данные декодера, используя определенное количество битов, которые необходимо исключить; и

декодируют входные данные декодера, чтобы восстановить биты информационного слова,

причем каждое из первого отношения и второго отношения является отношением количества битов, которые необходимо сократить, к количеству битов, которые необходимо исключить; и

причем количество битов, которые необходимо исключить, определяется на основании значения, вычисленного применяя одну из первой пары параметров и второй пары параметров к разности между количеством битов входных данных для кодера и количеством битов информационного слова.

8. Способ по п. 7, в котором этап, на котором определяют количество битов, которые необходимо исключить, содержит этапы, на которых:

вычисляют промежуточное количество битов, которые необходимо исключить, на основе одной из первой пары параметров и второй пары параметров;

вычисляют промежуточное количество кодированных битов на основе вычисленного промежуточного количества битов, которые необходимо исключить;

вычисляют окончательное количество кодированных битов на основе промежуточного количества кодированных битов и порядка модуляции; и

определяют количество битов, которые необходимо исключить, на основе промежуточного количества битов, которые необходимо исключить, промежуточного количества кодированных битов и окончательного количества кодированных битов.

9. Способ по п. 8, в котором промежуточное количество битов, которые необходимо исключить, определяется с помощью:

где Npunc_temp указывает промежуточное количество битов, которые необходимо исключить, Kbch указывает длину битов входных данных кодера Боуза, Чоудхури, Хоквингема (ВСН), Ksig указывает количество битов информационного слова, (1,3, 3357) указывает первую пару параметров, (1,35, 3320) указывает вторую пару параметров и заранее установленное пороговое значение равно 1350.

10. Способ по п. 7, дополнительно содержащий этапы, на которых:

определяют по меньшей мере один третий параметр для определения длины битов дополнительной четности;

определяют длину битов дополнительной четности на основе по меньшей мере одного третьего параметра; и

формируют значения, соответствующие битам, дополнительно исключенным стороной передачи, используя длину битов дополнительной четности, и заполняют сформированными значениями, соответствующими дополнительно исключенным битам, модулированный сигнал принятого сигнала, чтобы сформировать входные данные декодера.

11. Способ по п. 10, в котором по меньшей мере один третий параметр включает в себя по меньшей мере одно из отношения количества битов первой четности, переданных в кадре, передающем информационное слово, к количеству битов дополнительной четности, и количество битов первой четности, Ntx_parity.

12. Способ по п. 10, в котором длина битов дополнительной четности определяется с помощью:

где ηMOD указывает порядок модуляции, который равен 1, 2, 4 и 6 для двухпозиционной фазовой манипуляции (BPSK), квадратурной PSK (QPSK), 16-позиционной квадратурной амплитудной модуляции (16-QAM) и 64-позиционной QAM (64-QAM) соответственно, а Nadd_parity_temp определяется с помощью:

,

,

где Nparity указывает количество битов четности, Npunc указывает количество битов, которые необходимо исключить, и K указывает отношение дополнительной четности.

13. Устройство для передачи информации в вещательной системе/системе связи и для выполнения всех или части этапов способа по любому из пп. 1-6.

14. Устройство для приема информации в вещательной системе/системе связи и для выполнения всех или части этапов способа по любому из пп. 7-12.

| US 2006123277 A1, 08.06.2006 | |||

| US 2011119568 A1, 19.05.2011 | |||

| WO 2009110739 A2, 11.09.2009 | |||

| АНАЛИЗАТОР ДЛЯ МНОЖЕСТВА ПОТОКОВ ДАННЫХ В СИСТЕМЕ СВЯЗИ | 2006 |

|

RU2392747C2 |

Авторы

Даты

2017-01-30—Публикация

2012-08-16—Подача