УРОВЕНЬ ТЕХНИКИ ИЗОБРЕТЕНИЯ

И изобретение относится к устройству и способу для отображения и обратного отображения сигналов в системе, использующей код с малой плотностью проверок на четность (LDPC).

Описание связанного уровня техники

В системе связи эффективность линии связи может быть значительно снижена посредством шума, затухания и межсимвольных помех (ISI) канала. Вследствие этого система связи следующего поколения активно рассматривает использование LDPC-кодов в качестве кодов коррекции ошибок.

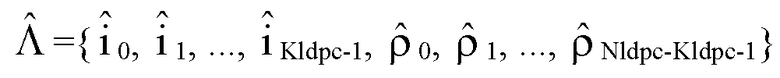

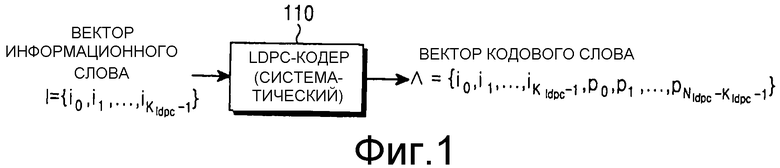

Фиг.1 иллюстрирует традиционную операцию LDPC-кодирования. Ссылаясь на фиг.1, LDPC-кодер 110 кодирует вектор информационного слова с длиной Kldpc, I={i0, i1,..., iKldpc-1} в вектор Λ ={i0, i1,..., iKldpc-1, ρ0, ρ1,..., ρNldpc-Kldpc-1} LDPC-кодового слова. Вектор информационного слова включает в себя Kldpc информационных битов. То есть каждый элемент вектора I={i0, i1,..., iKldpc-1} информационного слова является информационным битом.

LDPC-кодер 110 генерирует вектор четности с длиной Nldpc-Kldpc, {ρ0, ρ1,..., ρNldpc-Kldpc-1} с использованием матрицы проверки на четность, имеющей Nldpc столбцов, и генерирует LDPC-код, т.е. вектор Λ ={i0, i1,..., iKldpc-1, ρ0, ρ1,..., ρNldpc-Kldpc-1} LDPC-кодового слова, с использованием вектора информационного слова и вектора четности.

Вместе с растущими потребностями в высокоскоростной передаче данных и разработке аппаратного обеспечения система связи будущего поколения активно рассматривает использование квадратурной амплитудной модуляции (QAM), которая является превосходной в том, что касается эффективности частот. В QAM разные биты модуляции, включенные в один символ QAM, имеют разные вероятности ошибок.

Способность коррекции ошибок для каждого бита LDPC-кодового слова, включенного в вектор LDPC-кодового слова, определяется согласно степени переменного узла, соответствующего биту LDPC-кодового слова.

Следовательно, даже если используется одинаковый LDPC-код, вероятность ошибок символа QAM варьируется в зависимости от битов модуляции символа QAM, в которые отображаются биты LDPC-кодового слова. Соответственно, существует необходимость в методе для отображения битов LDPC-кодового слова в биты модуляции символа QAM, который минимизирует вероятность ошибок символа QAM.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Соответственно варианты осуществления изобретения выполнены для решения по меньшей мере проблем и/или недостатков, описанных выше, и для предоставления по меньшей мере преимуществ, описанных ниже.

Аспект изобретения служит для предоставления устройства или способа для отображения и обратного отображения сигналов в системе, использующей LDPC-код.

Другой аспект изобретения служит для предоставления устройства или способа для отображения и обратного отображения между LDPC-кодовыми словами и символами QAM в системе, использующей LDPC-код.

В соответствии с аспектом изобретения передатчик сигнала предоставлен для использования в системе, использующей LDPC-код. Переданный сигнал включает в себя перемежитель, который записывает биты LDPC-кодового слова по столбцам и считывает записанные биты LDPC-кодового слова по строкам, демультиплексор, который генерирует подпотоки посредством демультиплексирования считанных битов с использованием схемы демультиплексирования, и блок отображения символов, который отображает биты, включенные в каждый из подпотоков, в символы в группе (созвездии) сигналов, при этом схема демультиплексирования определяется в соответствии со схемой модуляции, используемой в передатчике сигналов, длиной LDPC-кодового слова и числом подпотоков.

В соответствии с другим аспектом изобретения приемник сигналов предоставляется для использования в системе, использующей LDPC-код. Приемник сигналов включает в себя мультиплексор, который мультиплексирует подпотоки с использованием схемы мультиплексирования, обратный перемежитель, который обратно перемежает мультиплексированные биты, и LDPC-декодер, который генерирует биты LDPC-кодового слова посредством LDPC-декодирования обратно перемеженных битов, при этом схема мультиплексирования определяется в соответствии со схемой демультиплексирования, используемой в передатчике сигналов, и схема демультиплексирования определяется в соответствии со схемой модуляции, используемой в передатчике сигналов, длиной LDPC-кодового слова и числом подпотоков.

В соответствии с другим аспектом изобретения способ отображения сигналов предоставляется для передатчика сигналов в системе, использующей LDPC-код. В данном способе, биты LDPC-кодового слова записываются по столбцам и считываются по строкам, подпотоки генерируются посредством демультиплексирования считанных битов с использованием схемы демультиплексирования, и биты, включенные в каждый из подпотоков, отображаются в символы в группе сигналов, при этом схема демультиплексирования определяется в соответствии со схемой модуляции, используемой в передатчике сигналов, длиной LDPC-кодового слова, и числом подпотоков.

В соответствии с другим аспектом изобретения способ обратного отображения сигналов предоставляется для приемника сигналов в системе, использующей LDPC-код. В данном способе подпотоки мультиплексируются с использованием схемы мультиплексирования, мультиплексированные биты обратно перемежаются, и биты LDPC-кодового слова генерируются посредством LDPC-декодирования обратно перемеженных битов, при этом схема мультиплексирования определяется в соответствии со схемой демультиплексирования, используемой в передатчике сигналов, и схема демультиплексирования определяется в соответствии со схемой модуляции, используемой в передатчике сигналов, длиной LDPC-кодового слова и числом подпотоков.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Вышеописанные и другие аспекты, признаки и преимущества определенных вариантов осуществления изобретения станут более очевидны из следующего подробного описания, взятого совместно с сопутствующими чертежами, в которых:

Фиг.1 иллюстрирует традиционную операцию LDPC-кодирования;

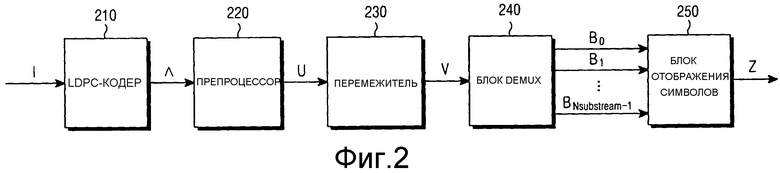

Фиг.2 является блок-схемой, иллюстрирующей передатчик сигналов в системе, использующей LDPC-код согласно варианту осуществления изобретения;

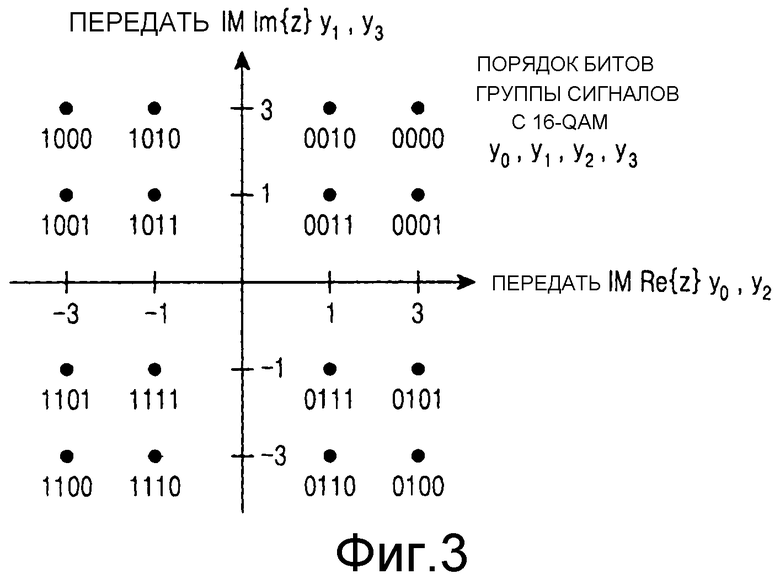

Фиг.3 иллюстрирует группу сигналов с 16-арной QAM (16-QAM) согласно варианту осуществления изобретения;

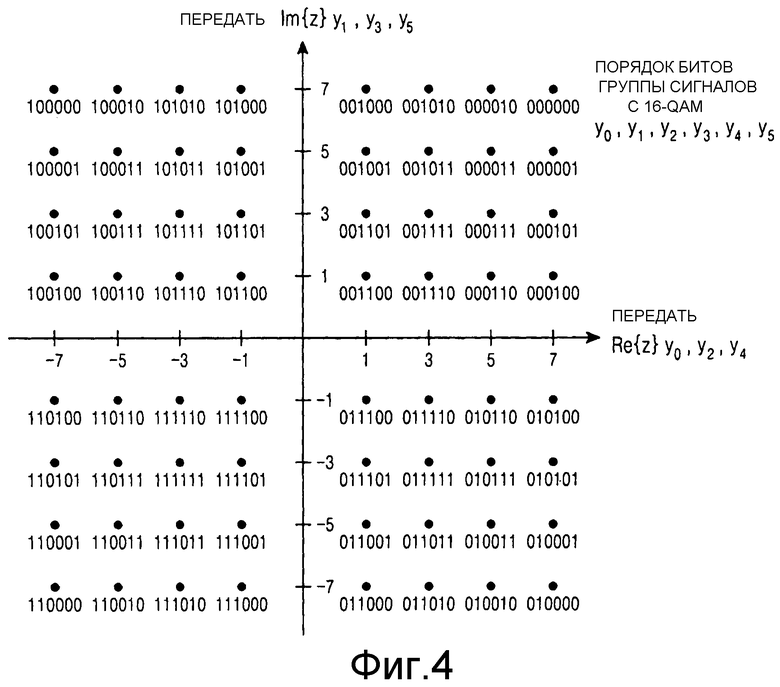

Фиг.4 иллюстрирует группу сигналов с 64-арной QAM (64-QAM) согласно варианту осуществления изобретения;

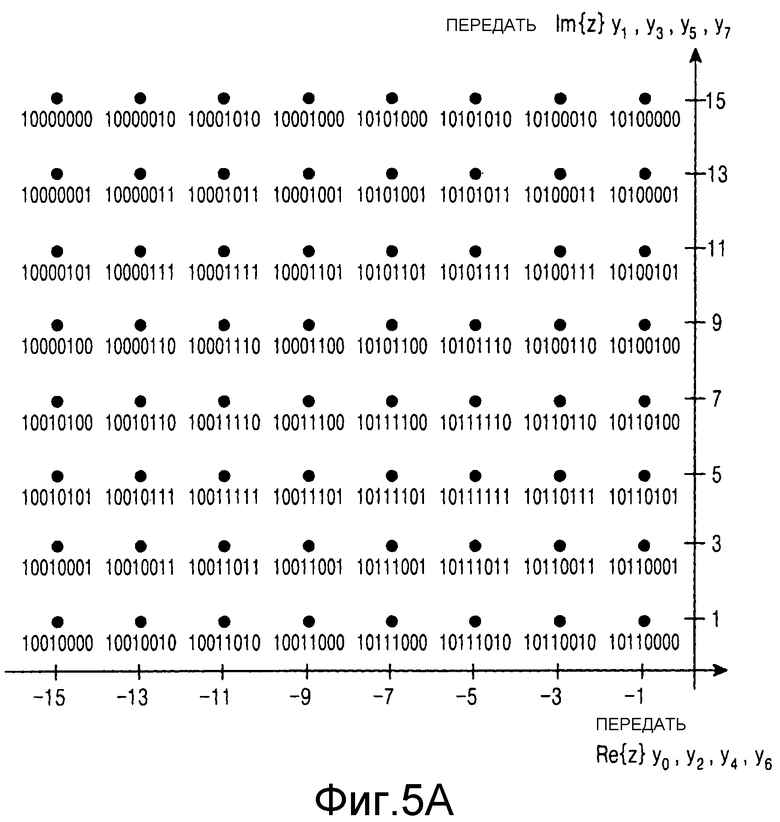

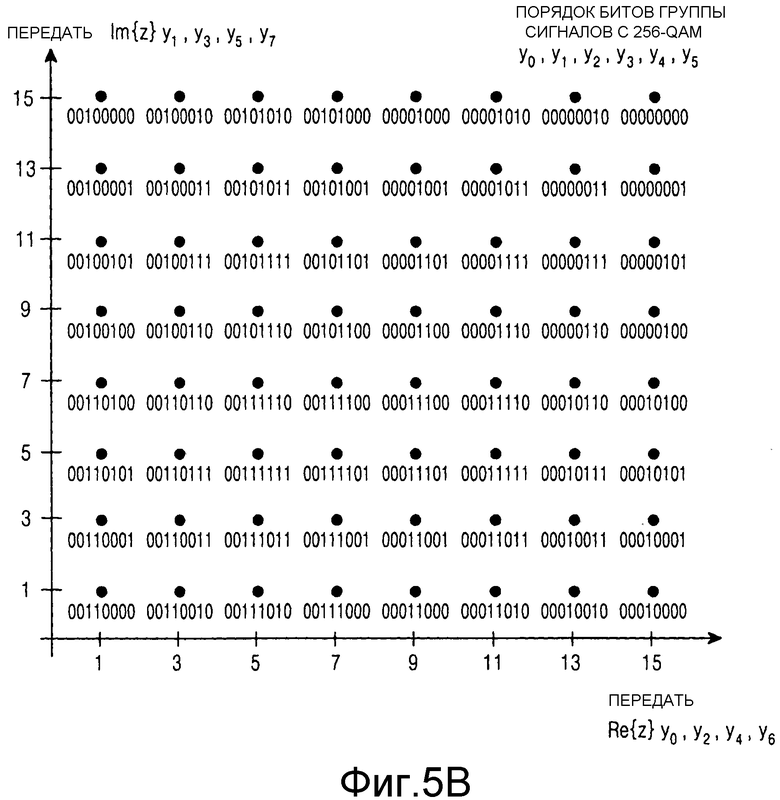

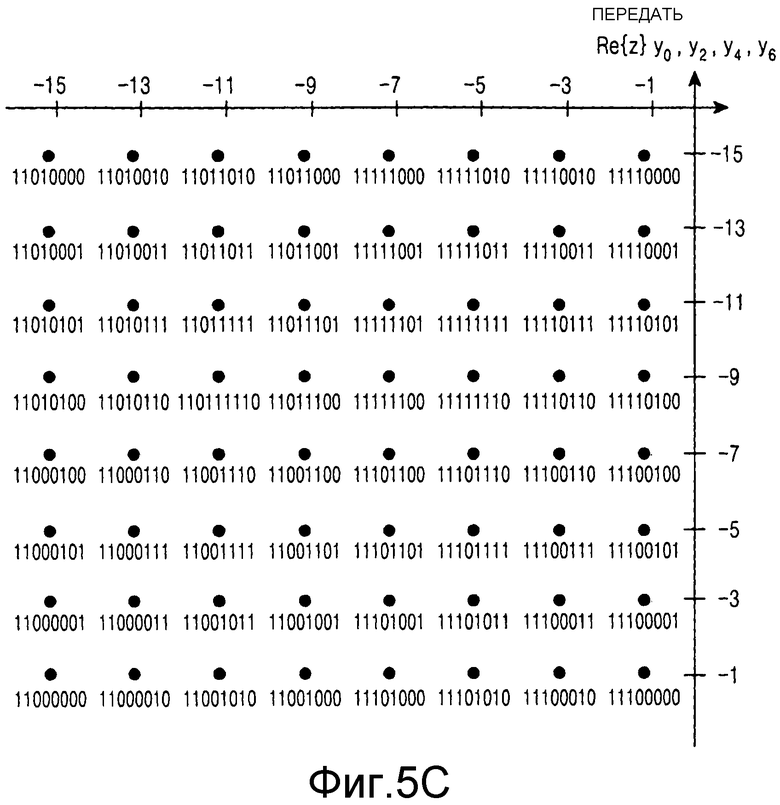

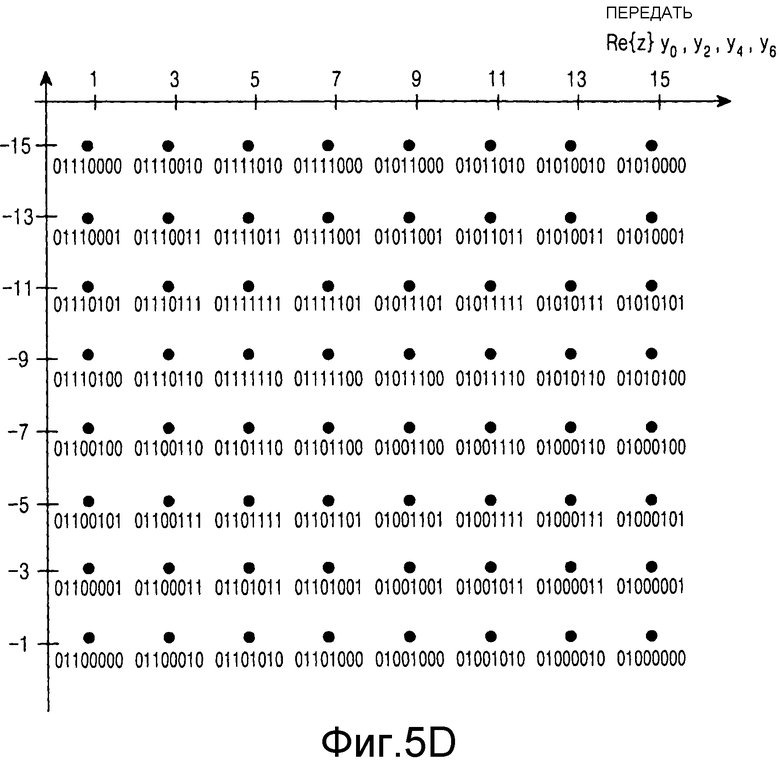

Фиг.5 иллюстрирует группу сигналов с 256-арной QAM (256-QAM) согласно варианту осуществления изобретения;

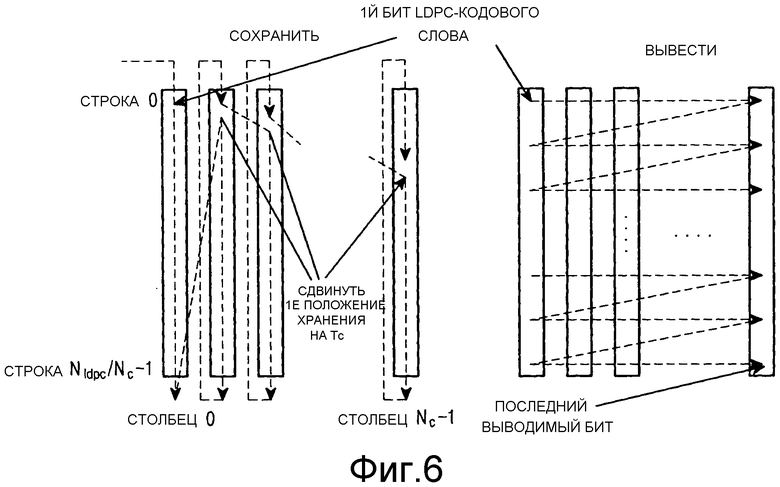

Фиг.6 иллюстрирует операцию перемежителя, проиллюстрированного на фиг.2, согласно варианту осуществления изобретения;

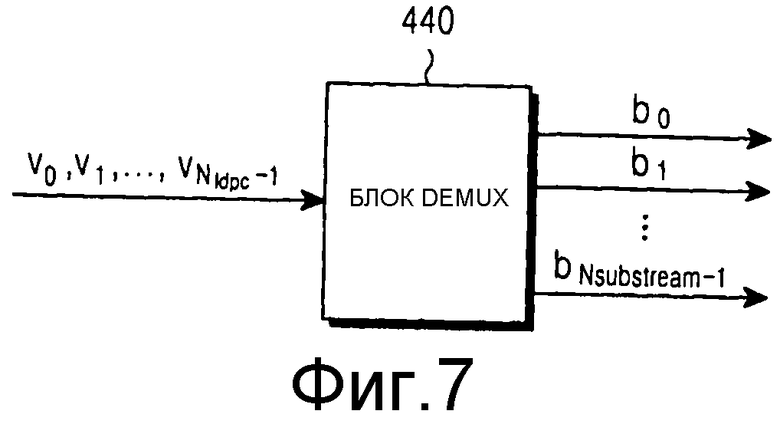

Фиг.7 иллюстрирует операцию блока демультиплексора (DEMUX), проиллюстрированного на фиг.2, согласно варианту осуществления изобретения;

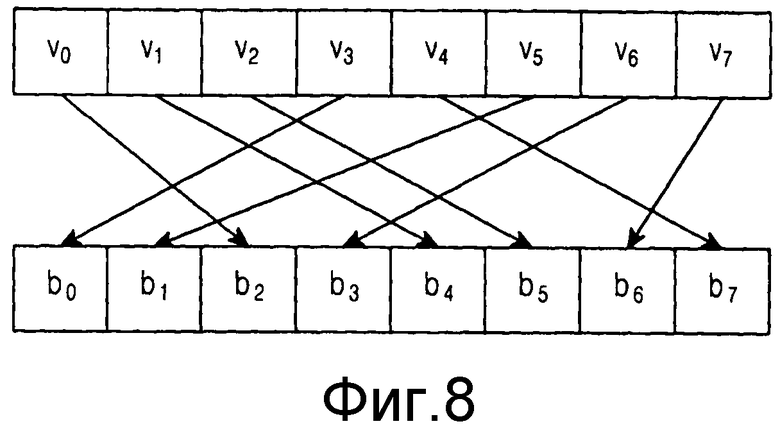

Фиг.8 иллюстрирует операцию блока DEMUX, когда используется Nldpc=16200 и 16-QAM, согласно варианту осуществления изобретения;

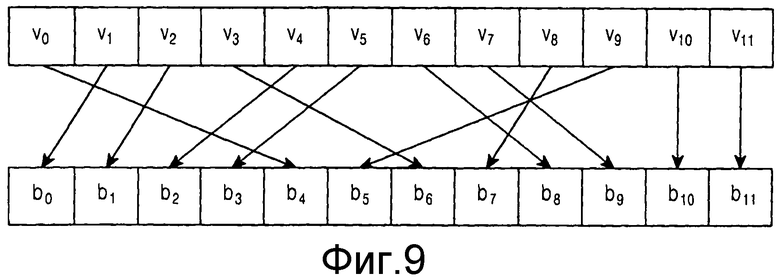

Фиг.9 иллюстрирует операцию блока DEMUX, когда используется Nldpc=16200 и 64-QAM, согласно варианту осуществления изобретения;

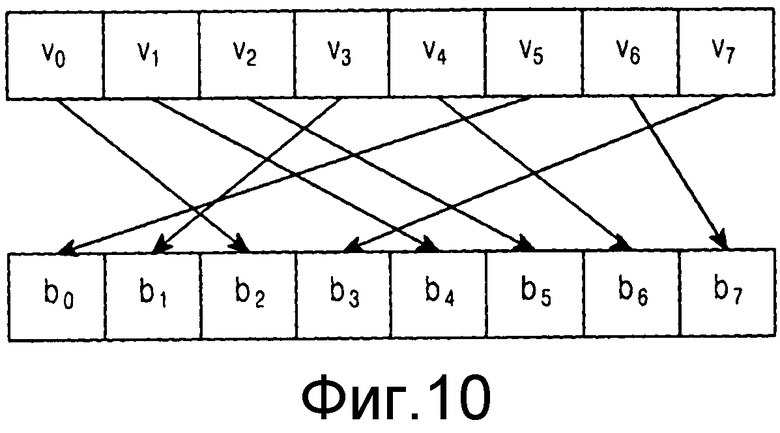

Фиг.10 иллюстрирует другую операцию блока DEMUX, когда используется Nldpc=16200 и 16-QAM, согласно варианту осуществления изобретения;

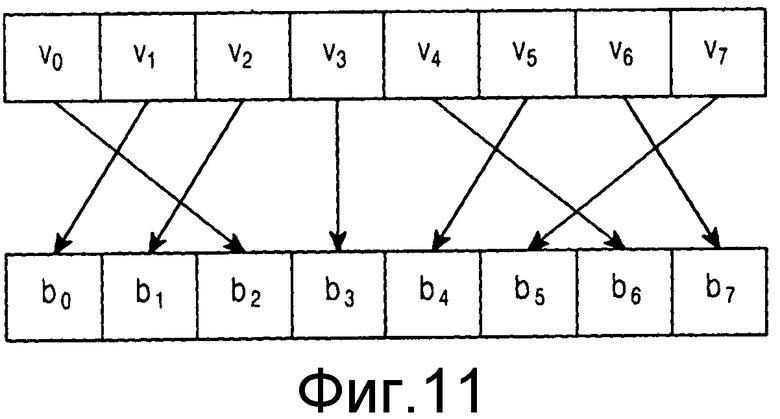

Фиг.11 иллюстрирует другую операцию блока DEMUX, когда используется Nldpc=16200 и 16-QAM, согласно варианту осуществления изобретения;

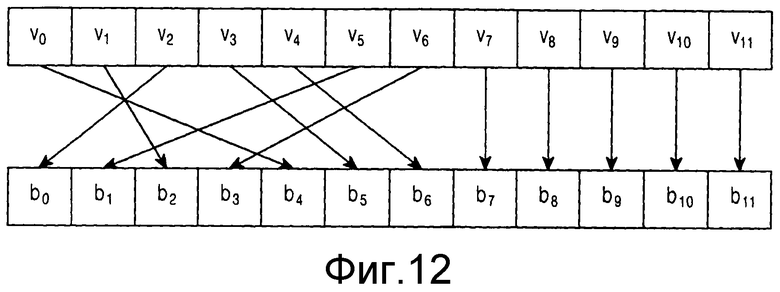

Фиг.12 иллюстрирует другую операцию блока DEMUX, когда используется Nldpc=16200 и 64-QAM, согласно варианту осуществления изобретения;

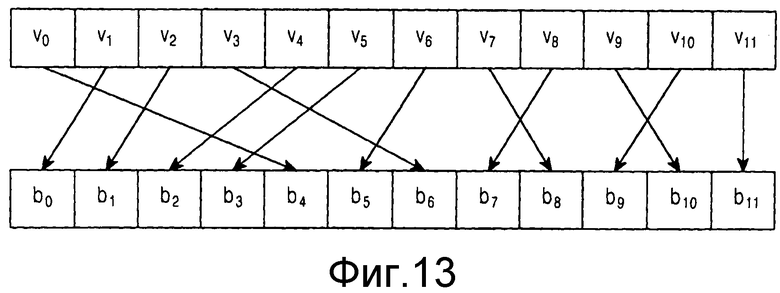

Фиг.13 иллюстрирует другую операцию блока DEMUX, когда используется Nldpc=16200 и 64-QAM, согласно варианту осуществления изобретения;

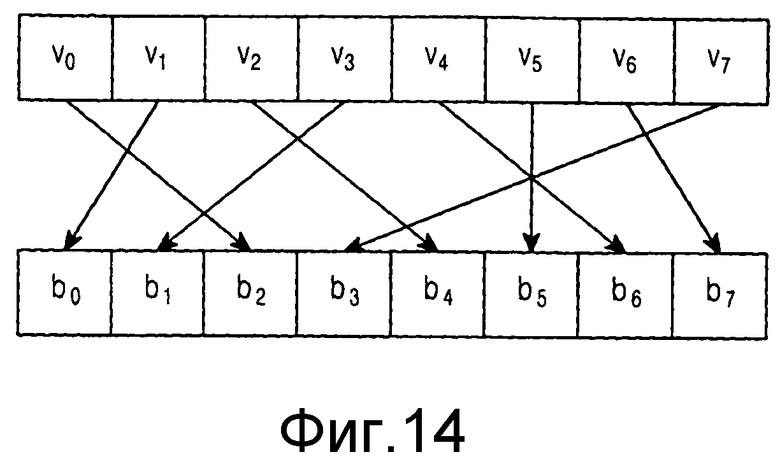

Фиг.14 иллюстрирует дополнительную операцию блока DEMUX, когда используется Nldpc=16200 и 16-QAM, согласно варианту осуществления изобретения;

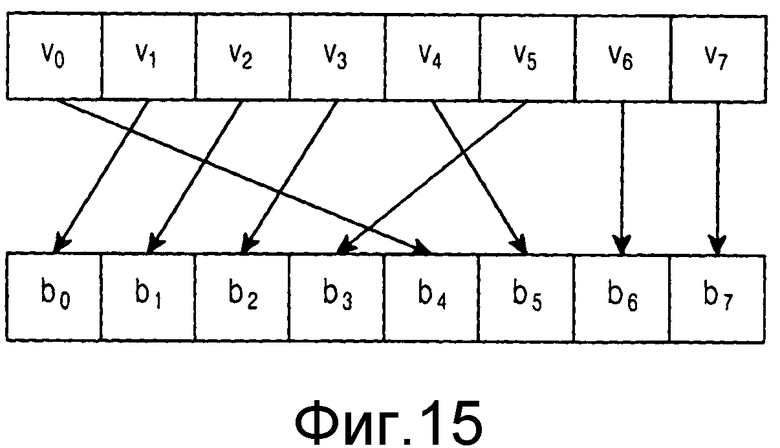

Фиг.15 иллюстрирует операцию блока DEMUX, когда используется Nldpc=16200 и 256-QAM, согласно варианту осуществления изобретения;

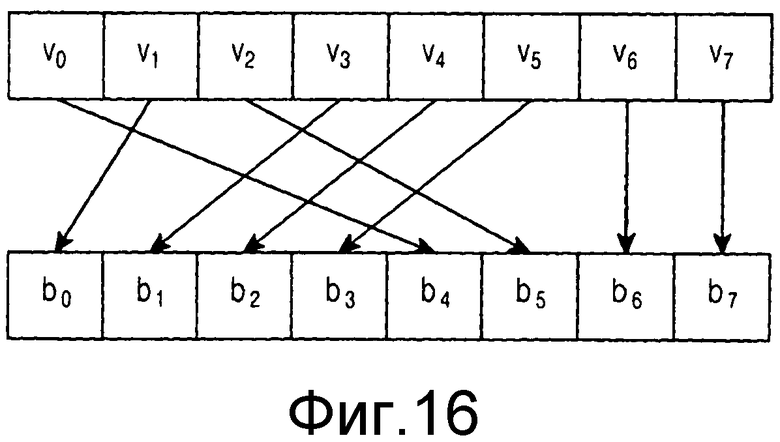

Фиг.16 иллюстрирует операцию блока DEMUX, когда используется Nldpc=16200 и 256-QAM, согласно варианту осуществления изобретения;

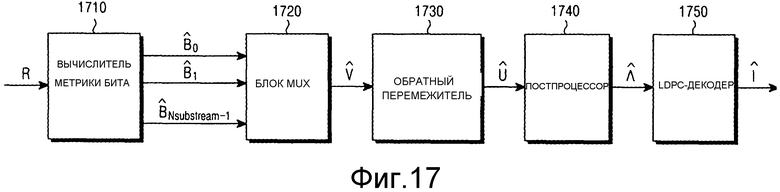

Фиг.17 является блок-схемой, иллюстрирующей приемник сигналов в системе, использующей LDPC-код, согласно варианту осуществления изобретения;

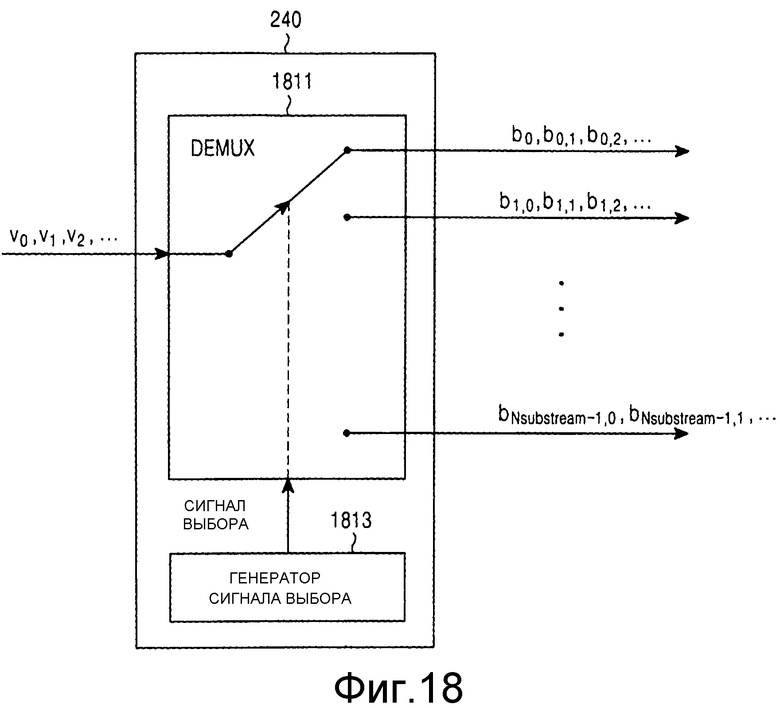

Фиг.18 является блок-схемой, иллюстрирующей блок демультиплексора (DEMUX) на фиг.2, согласно варианту осуществления изобретения; и

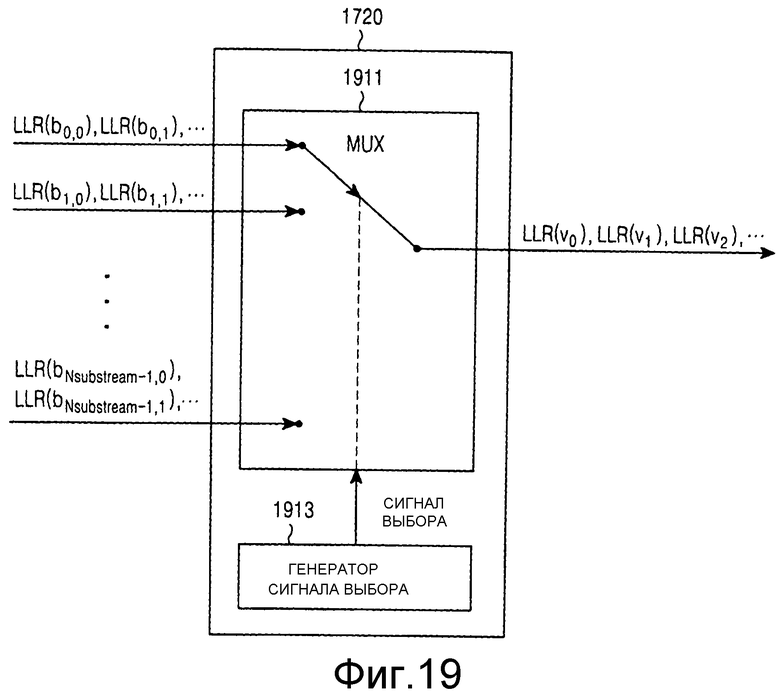

Фиг.19 является блок-схемой, иллюстрирующей блок мультиплексора (MUX) на фиг.17, согласно варианту осуществления изобретения.

На чертежах одинаковые ссылочные номера следует понимать как ссылающиеся на одни и те же элементы, признаки и структуры.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Различные варианты осуществления изобретения теперь будут подробно описаны со ссылкой на сопутствующие чертежи. В следующем описании конкретные подробности, такие как подробные конфигурация и компоненты, предоставляются лишь для помощи в общем понимании этих вариантов осуществления изобретения. Вследствие этого специалисты в данной области техники должны осознавать, что различные изменения и модификации вариантов осуществления, описанных в настоящем документе, могут быть сделаны без отступления от объема и сущности изобретения. К тому же описания общеизвестных функций и конструкций опущены для ясности и краткости.

В соответствии с вариантом осуществления изобретения устройство и способ предоставляются для отображения и обратного отображения сигналов в системе, использующей LDPC-код.

В соответствии с другим вариантом осуществления изобретения устройство и способ предоставляются для отображения и обратного отображения между LDPC-кодовыми словами и символами QAM.

Следующее описание изобретения предоставлено для систем, использующих LDPC-коды, например, вещательных систем, таких как системы следующего поколения (NGH) цифрового видеовещания на портативные устройства (DVB), или систем связи, таких как транспортировка медиаданных (MMT) экспертной группы по кинематографии (MPEG), усовершенствованная система пакетной передачи данных (EPS), проект долгосрочного развития (LTE), и 802.16m института инженеров по электротехнике и радиоэлектронике (IEEE).

Хотя изобретение описано в контексте LDPC-кода и схем QAM-модуляции, следует ясно понимать, что устройство и способ изобретения также применимы к другим кодам и другим схемам модуляции.

Фиг.2 является блок-схемой, иллюстрирующей передатчик сигналов в системе, использующей LDPC-код, согласно варианту осуществления изобретения.

Ссылаясь на фиг.2, передатчик сигналов включает в себя LDPC-кодер 210, препроцессор 220, перемежитель 230, блок 240 DEMUX и блок 250 отображения символов.

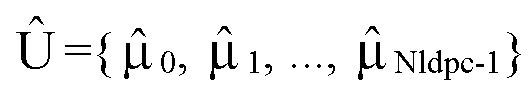

LDPC-кодер 210 генерирует вектор {ρ0, ρ1,..., ρNldpc-Kldpc-1} четности, включающий в себя Nldpc-Kldpc битов четности, и затем вектор LDPC-кодового слова с длиной Nldpc посредством кодирования вектора I={i0, i1,..., iKldpc-1} информационного слова. Препроцессор 220 генерирует вектор U={μ0, μ1,..., μNldpc} посредством предварительной обработки вектора Λ LDPC-кодового слова, принятого от LDPC-кодера 210, с использованием предварительно определенной схемы предварительной обработки. В качестве альтернативы препроцессор 220 может быть опущен или его функции могут быть включены в перемежитель 230. Подробное описание схемы предварительной обработки здесь не предоставлено.

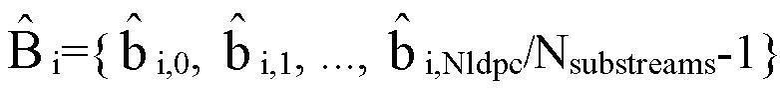

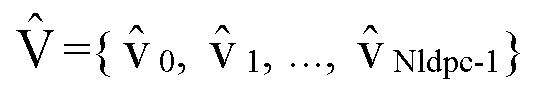

Перемежитель 230 записывает вектор U, принятый от препроцессора 220, по столбцам в Nc столбцов и считывает вектор U по строкам, таким образом выводя вектор V={ν0, ν1,..., νNldpc-1} в блок 240 DEMUX. Блок 240 DEMUX демультиплексирует вектор V в Nsubstreams подпотоков Bi={bi,0, bi,1,..., bi,Nldpc/Nsubstreams-1}(i=0,1,..., Nsubstreams-1), причем каждый имеет Nc битов. Для ввода битов каждого из Nsubstreams подпотоков блок 250 отображения символов генерирует слово ячейки с длиной ηMOD, ┌y0, y1,..., yμMOD-1┐ и отображает слово ячейки в сигнальные точки в группе (созвездии) сигналов, тем самым производя символ Z. Здесь ηMOD является делителем Nsubstreams.

Фиг.3, 4, и 5 иллюстрируют взаимосвязи отображения между словами ячеек и группами сигналов при 16-QAM, 64-QAM и 256-QAM соответственно согласно вариантам осуществления изобретения.

Фиг.6 иллюстрирует операцию перемежителя 230, проиллюстрированного на фиг.2, согласно варианту осуществления изобретения. Конкретно, на фиг.6, предположено, что перемежитель 230 имеет Nc строк × Nldpc/Nc столбцов.

Если Nldpc=16200, число строк Nr и число столбцов Nc задаются для 16-QAM и 64-QAM как показано в таблице 1.

Перемежитель 230 последовательно записывает принятый вектор U по столбцам в Nc столбцов и считывает записанный вектор по строкам. Здесь первое положение хранения каждого столбца может быть сдвинуто на параметр Tc кручения. Параметр Tc кручения может иметь значения, показанные в таблице 2 для 16-QAM и 64-QAM, когда Nldpc=16200, например.

Фиг.7 иллюстрирует операцию блока DEMUX, проиллюстрированного на фиг.2, согласно варианту осуществления изобретения.

Ссылаясь на фиг.7, операция блока 240 DEMUX может быть выражена как взаимосвязь между Vi(i=0, 1,..., Nldpc-1) и bj(j=0,1,..., Nsubstreams-1), которая может быть расширена по тому же правилу, если Nldpc является кратным Nsubstreams.

Фиг.8 иллюстрирует операцию блока 240 DEMUX, когда используется Nldpc=16200 и 16-QAM, согласно варианту осуществления изобретения.

Ссылаясь на фиг.8, предполагая Nsubstreams=8, блок 240 DEMUX отображает входные биты с v0 по v7 в выходные биты с b0 по b7. Конкретно, блок 240 DEMUX отображает бит v0 в бит b2, бит v1 в b4, бит v2 в бит b5, бит v3 в бит b0, бит v4 в бит b7, бит v5 в бит b1, бит v6 в b3, и бит v7 в бит b6.

Фиг.9 иллюстрирует операцию блока 240 DEMUX, когда используется Nldpc=16200 и 64-QAM, согласно варианту осуществления изобретения.

Ссылаясь на фиг.9, предполагая Nsubstreams=12, блок 240 DEMUX отображает входные биты с v0 по v11 в выходные биты с b0 по b11. Конкретно, блок 240 DEMUX отображает бит v0 в бит b4, бит v1 в b0, бит v2 в бит b1, бит v3 в бит b6, бит v4 в бит b2, бит v5 в бит b3, бит v6 в b8, бит v7 в бит b9, бит v8 в бит b7, бит v9 в бит b5, бит v10 в бит b10, и бит v11 в бит b11.

Фиг.10 иллюстрирует другую операцию блока 240 DEMUX, когда используется Nldpc=16200 и 16-QAM, согласно варианту осуществления изобретения.

Ссылаясь на фиг.10, предполагая Nsubstreams=8, блок 240 DEMUX отображает входные биты с v0 по v7 в выходные биты с b0 по b7. Конкретно, блок 240 DEMUX отображает бит v0 в бит b2, бит v1 в b4, бит v2 в бит b5, бит v3 в бит b1, бит v4 в бит b6, бит v5 в бит b0, бит v6 в b7, и бит v7 в бит b3.

Фиг.11 иллюстрирует другую операцию блока 240 DEMUX, когда используется Nldpc=16200 и 16-QAM, согласно варианту осуществления изобретения.

Ссылаясь на фиг.11, предполагая Nsubstreams=8, блок 240 DEMUX отображает входные биты с v0 по v7 в выходные биты с b0 по b7. Конкретно, блок 240 DEMUX отображает бит v0 в бит b2, бит v1 в b0, бит v2 в бит b1, бит v3 в бит b3, бит v4 в бит b6, бит v5 в бит b4, бит v6 в b7, и бит v7 в бит b5.

Фиг.12 иллюстрирует другую операцию блока 240 DEMUX, когда используется Nldpc=16200 и 64-QAM, согласно варианту осуществления изобретения.

Ссылаясь на фиг.12, предполагая Nsubstreams=12, блок 240 DEMUX отображает входные биты с v0 по v11 в выходные биты с b0 по b11. Конкретно, блок 240 DEMUX отображает бит v0 в бит b4, бит v1 в b2, бит v2 в бит b0, бит v3 в бит b5, бит v4 в бит b6, бит v5 в бит b1, бит v6 в b3, бит v7 в бит b7, бит v8 в бит b8, бит v9 в бит b9, бит v10 в бит b10, и бит v11 в бит b11.

Фиг.13 иллюстрирует другую операцию блока 240 DEMUX, когда используется Nldpc=16200 и 64-QAM, согласно варианту осуществления изобретения.

Ссылаясь на фиг.13, предполагая Nsubstreams=12, блок 240 DEMUX отображает входные биты с v0 по v11 в выходные биты с b0 по b11. Конкретно, блок 240 DEMUX отображает бит v0 в бит b4, бит v1 в b0, бит v2 в бит b1, бит v3 в бит b6, бит v4 в бит b2, бит v5 в бит b3, бит v6 в b5, бит v7 в бит b8, бит v8 в бит b7, бит v9 в бит b10, бит v10 в бит b9, и бит v11 в бит b11.

Фиг.14 иллюстрирует другую операцию блока 240 DEMUX, когда используется Nldpc=16200 и 64-QAM, согласно варианту осуществления изобретения.

Ссылаясь на фиг.14, предполагая Nsubstreams=8, блок 240 DEMUX отображает входные биты с v0 по v7 в выходные биты с b0 по b7. Конкретно, блок 240 DEMUX отображает бит v0 в бит b2, бит v1 в b0, бит v2 в бит b4, бит v3 в бит b1, бит v4 в бит b6, бит v5 в бит b5, бит v6 в b7, и бит v7 в бит b3.

Фиг.15 иллюстрирует операцию блока 240 DEMUX, когда используется Nldpc=16200 и 256-QAM, согласно варианту осуществления изобретения.

Ссылаясь на фиг.15, предполагая Nsubstreams=8, блок 240 DEMUX отображает входные биты с v0 по v7 в выходные биты с b0 по b7. Конкретно, блок 240 DEMUX отображает бит v0 в бит b4, бит v1 в b0, бит v2 в бит b1, бит v3 в бит b2, бит v4 в бит b5, бит v5 в бит b3, бит v6 в b6, и бит v7 в бит b7.

Фиг.16 иллюстрирует другую операцию блока 240 DEMUX, когда используется Nldpc=16200 и 256-QAM, согласно варианту осуществления изобретения.

Ссылаясь на фиг.16, предполагая Nsubstreams=8, блок 240 DEMUX отображает входные биты с v0 по v7 в выходные биты с b0 по b7. Конкретно, блок 240 DEMUX отображает бит v0 в бит b4, бит v1 в b0, бит v2 в бит b5, бит v3 в бит b1, бит v4 в бит b2, бит v5 в бит b3, бит v6 в b6, и бит v7 в бит b7.

Как описано выше, в соответствии с вариантами осуществления изобретения блок DEMUX предоставляет биты LDPC-кодового слова блоку отображения символов согласно предварительно определенному правилу отображения. Вследствие этого, когда биты LDPC-кодового слова отображаются в символы (например, символы в группе QAM-сигналов), символы имеют разные характеристики согласно разным правилам отображения.

Фиг.17 является блок-схемой, иллюстрирующей приемник сигналов в системе использующей LDPC-код согласно варианту осуществления изобретения.

Ссылаясь на фиг.17, приемник сигналов включает в себя вычислитель 1710 метрики битов, блок 1720 MUX, обратный перемежитель 1730, постпроцессор 1740 и LDPC-декодер 1750.

После приема вектора символа с длиной Nldpc/ηMOD, R={r0, r1,..., rNldpc/ηMOD-1}, калькулятор 1710 метрики битов оценивает  (i=0,1,..., Nsubstreams-1) Nsubstreams подпотоков Bi={bi,0, bi,1,..., bi,Nldpc/Nsubstreams-1} (i=0,1,..., Nsubstreams-1). Метрики битов используются для декодирования LDPC-кода. Например, логарифмические отношения правдоподобия (LLR) могут быть использованы в качестве метрик битов.

(i=0,1,..., Nsubstreams-1) Nsubstreams подпотоков Bi={bi,0, bi,1,..., bi,Nldpc/Nsubstreams-1} (i=0,1,..., Nsubstreams-1). Метрики битов используются для декодирования LDPC-кода. Например, логарифмические отношения правдоподобия (LLR) могут быть использованы в качестве метрик битов.

Блок 1720 MUX генерирует оценку вектора метрики бита с длиной Nldpc,  посредством мультиплексирования оценок

посредством мультиплексирования оценок

вектора метрики бита для U={μ0, μ1,..., μNldpc-1}.

вектора метрики бита для U={μ0, μ1,..., μNldpc-1}.

Постпроцессор 1740 генерирует оценку  вектора метрики бита переданного LDPC-кодового слова Λ={i0, i1,..., iKldpc-1, ρ0, ρ1,..., ρNldpc-Kldpc-1} посредством обработки оценки вектора метрики бита

вектора метрики бита переданного LDPC-кодового слова Λ={i0, i1,..., iKldpc-1, ρ0, ρ1,..., ρNldpc-Kldpc-1} посредством обработки оценки вектора метрики бита  с использованием схемы постобработки, соответствующей схеме предварительной обработки, используемой в препроцессоре передатчика сигналов, т.е. препроцессоре 220, проиллюстрированном на фиг.2. LDPC-декодер 1740 декодирует вектор

с использованием схемы постобработки, соответствующей схеме предварительной обработки, используемой в препроцессоре передатчика сигналов, т.е. препроцессоре 220, проиллюстрированном на фиг.2. LDPC-декодер 1740 декодирует вектор

вектора I={i0, i1,..., iKldpc-1} информационного слова.

вектора I={i0, i1,..., iKldpc-1} информационного слова.

Фиг.18 является блок-схемой, иллюстрирующей блок 240 DEMUX, проиллюстрированный на фиг.2, согласно варианту осуществления изобретения.

Ссылаясь на фиг.18, блок 240 DEMUX включает в себя DEMUX 1811 и генератор 1813 сигнала выбора.

DEMUX 1811 генерирует Nsubstreams подпотоков из вектора V, принятого из перемежителя 230, с использованием сигналов выбора, принятых из генератора 1813 сигнала выбора. Генератор 1813 сигнала выбора определяет подпоток, которому должен быть назначен каждый бит вектора V, и затем выводит сигнал выбора посредством считывания значения, хранящегося в хранилище, например, памяти, или генерирования сигнала с использованием предварительно определенного правила. Вывод сигнала выбора из генератора 1813 сигнала выбора определяется согласно типу, длине кодового слова, кодовой скорости и схеме модуляции кода коррекции ошибок, используемой в данной системе. Сигнал выбора является важным фактором, который влияет на способность коррекции ошибок системы.

Фиг.19 является блок-схемой, иллюстрирующей блок 1720 MUX, проиллюстрированный на фиг.17, согласно варианту осуществления изобретения.

Ссылаясь на фиг.19, блок 1720 MUX включает в себя MUX 1911 и генератор 1913 сигнала выбора. MUX 1911 выводит оценку перемеженного кодового слова из Nsubstreams подпотоков с использованием сигналов выбора, принятых из генератора 1913 сигнала выбора. Генератор 1913 сигнала выбора определяет подпоток, из которого получен каждый бит оцененного перемеженного кодового слова. Генератор 1913 сигнала выбора выводит сигнал выбора посредством считывания значения, хранящегося в памяти, или генерирования сигнала с использованием предварительно определенного правила. Блок 1720 MUX выполняет мультиплексирование с использованием манеры, соответствующей демультиплексированию блока 240 DEMUX, как проиллюстрировано на фиг.2.

Как очевидно из описания выше, различные варианты осуществления изобретения могут минимизировать вероятность ошибок системы использующей LDPC-код, и таким образом, улучшить общую производительность системы посредством обеспечения возможности отображения битов LDPC-кодового слова в символы модуляции согласно используемой схеме модуляции.

Хотя изобретение было конкретно показано и описано со ссылкой на некоторые варианты его осуществления, специалистам в данной области техники будет понятно, что различные изменения в виде и деталях могут быть сделаны в нем без отступления от сущности и объема изобретения, как определено следующими пунктами формулы изобретения и их эквивалентами.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО И СПОСОБ ДЛЯ ОТОБРАЖЕНИЯ И ОБРАТНОГО ОТОБРАЖЕНИЯ СИГНАЛОВ В СИСТЕМЕ СВЯЗИ С ИСПОЛЬЗОВАНИЕМ КОДА С МАЛОЙ ПЛОТНОСТЬЮ ПРОВЕРОК НА ЧЕТНОСТЬ | 2016 |

|

RU2701085C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2012 |

|

RU2595579C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2011 |

|

RU2574828C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛА И СПОСОБ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛА | 2008 |

|

RU2437237C1 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2014 |

|

RU2656723C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2011 |

|

RU2574822C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2014 |

|

RU2658791C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2012 |

|

RU2595581C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2012 |

|

RU2595585C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ ОБРАБОТКИ ДАННЫХ | 2014 |

|

RU2656725C2 |

Изобретение относится к передаче данных и предназначено для отображения и обратного отображения сигнала в системе, использующей код с малой плотностью проверок на четность (LDPC). Технический результат - минимизация вероятности ошибок символа QAM. В данном способе биты LDPC-кодового слова записываются по столбцам и считываются по строкам, подпотоки генерируются посредством демультиплексирования считанных битов с использованием схемы демультиплексирования, и биты, включенные в каждый из подпотоков, отображаются в символы в группе сигналов, при этом схема демультиплексирования определяется в соответствии со схемой модуляции, используемой в передатчике сигналов, длиной LDPC-кодового слова и числом подпотоков. 4 н. и 8 з.п. ф-лы, 22 ил.

1. Способ отображения сигналов передатчика сигналов в системе, использующей код с малой плотностью проверок на четность (LDPC), причем способ отображения сигналов содержит этапы, на которых:

записывают биты LDPC-кодового слова по столбцам;

считывают записанные биты LDPC-кодового слова по строкам;

генерируют подпотоки посредством демультиплексирования считанных битов с использованием схемы демультиплексирования; и

отображают биты, включенные в каждый из подпотоков, в символы в группе сигналов,

при этом схема демультиплексирования определяется в соответствии со схемой модуляции, используемой в передатчике сигналов, длиной LDPC-кодового слова и числом подпотоков.

2. Способ отображения сигналов по п. 1, в котором, если 64-арная квадратурная амплитудная модуляция (64-QAM) используется в качестве схемы модуляции, длина LDPC-кодового слова Nldpc составляет 16200 (Nldpc=16200), число подпотоков Nsubstreams составляет 12 (Nsubstreams=12) и считанные биты с v0 по v11 назначаются 12 подпотокам с b0 по b11, генерирование подпотоков содержит назначение бита v0 биту b4, бита v1 биту b2, бита v2 биту b0, бита v3 биту b5, бита v4 биту b6, бита v5 биту b1, бита v6 биту b3, бита v7 биту b7, бита v8 биту b8, бита v9 биту b9, бита v10 биту b10, и бита v11 биту b11.

3. Способ отображения сигналов по п. 1, в котором, если 64-арная квадратурная амплитудная модуляция (64-QAM) используется в качестве схемы модуляции, длина LDPC-кодового слова Nldpc составляет 16200 (Nldpc=16200), число подпотоков Nsubstreams составляет 12 (Nsubstreams=12) и считанные биты с v0 по v11 назначаются 12 подпотокам с b0 по b11, генерирование подпотоков содержит назначение бита v0 биту b4, бита v1 биту b0, бита v2 биту b1, бита v3 биту b6, бита v4 биту b2, бита v5 биту b3, бита v6 биту b5, бита v7 биту b8, бита v8 биту b7, бита v9 биту b10, бита v10 биту b9, и бита v11 биту b11.

4. Способ отображения сигналов по п. 1, в котором, если 256-арная квадратурная амплитудная модуляция (256-QAM) используется в качестве схемы модуляции, длина LDPC-кодового слова Nldpc составляет 16200 (Nldpc=16200), число подпотоков Nsubstreams составляет 8 (Nsubstreams=8) и считанные биты с v0 по v7 назначаются 8 подпотокам с b0 по b7, генерирование подпотоков содержит назначение бита v0 биту b4, бита v1 биту b0, бита v2 биту b1, бита v3 биту b2, бита v4 биту b5, бита v5 биту b3, бита v6 биту b6, и бита v7 биту b7.

5. Способ отображения сигналов по п. 1, в котором, если 256-арная квадратурная амплитудная модуляция (256-QAM) используется в качестве схемы модуляции, длина LDPC-кодового слова Nldpc составляет 16200 (Nldpc=16200), число подпотоков Nsubstreams составляет 8 (Nsubstreams=8) и считанные биты с v0 по v7 назначаются 8 подпотокам с b0 по b7, генерирование подпотоков содержит назначение бита v0 биту b4, бита v1 биту b0, бита v2 биту b5, бита v3 биту b1, бита v4 биту b2, бита v5 биту b3, бита v6 биту b6, и бита v7 биту b7.

6. Передатчик сигналов в системе использующей код с малой плотностью проверок на четность (LDPC), адаптированный для выполнения способа по одному из пп. 1-5.

7. Способ обратного отображения сигналов приемника сигналов в системе, использующей код с малой плотностью проверок на четность (LDPC), причем способ обратного отображения сигналов содержит этапы, на которых:

мультиплексируют подпотоки с использованием схемы мультиплексирования;

обратно перемежают мультиплексированные биты из мультиплексированных подпотоков; и

генерируют биты LDPC-кодового слова посредством LDPC-декодирования обратно перемеженных битов,

при этом схема мультиплексирования определяется соответствующей схеме демультиплексирования, используемой в передатчике сигналов, и схема демультиплексирования определяется соответствующей схеме модуляции, используемой в передатчике сигналов, длиной LDPC-кодового слова и числом подпотоков.

8. Способ обратного отображения сигналов по п. 7, в котором, если 64-арная квадратурная амплитудная модуляция (64-QAM) используется в качестве схемы модуляции, длина LDPC-кодового слова Nldpc составляет 16200 (Nldpc=16200), число подпотоков Nsubstreams составляет 12 (Nsubstreams=12) и 12 подпотоков с b0 по b11 назначаются мультиплексированным битам с v0 по v11, мультиплексирование подпотоков содержит назначение бита b0 биту v2, бита b1 биту v5, бита b2 биту v1, бита b3 биту v6, бита b4 биту v0, бита b5 биту v3, бита b6 биту v4, бита b7 биту v7, бита b8 биту v8, бита b9 биту v9, бита b10 биту v10, и бита b11 биту v11.

9. Способ обратного отображения сигналов по п. 7, в котором, если 64-арная квадратурная амплитудная модуляция (64-QAM) используется в качестве схемы модуляции, длина LDPC-кодового слова Nldpc составляет 16200 (Nldpc=16200), число подпотоков Nsubstreams составляет 12 (Nsubstreams=12) и 12 подпотоков с b0 по b11 назначаются мультиплексированным битам с v0 по v11, мультиплексирование подпотоков содержит назначение бита b0 биту v1, бита b1 биту v2, бита b2 биту v4, бита b3 биту v5, бита b4 биту v0, бита b5 биту v6, бита b6 биту v3, бита b7 биту v8, бита b8 биту v7, бита b9 биту v10, бита b10 биту v9, и бита b11 биту v11.

10. Способ обратного отображения сигналов по п. 7, в котором, если 256-арная квадратурная амплитудная модуляция (256-QAM) используется в качестве схемы модуляции, длина LDPC-кодового слова Nldpc составляет 16200 (Nldpc=16200), число подпотоков Nsubstreams составляет 8 (Nsubstreams=8) и 8 подпотоков с b0 по b8 назначаются мультиплексированным битам с v0 по v8, мультиплексирование подпотоков содержит назначение бита b0 биту v1, бита b1 биту v2, бита b2 биту v3, бита b3 биту v5, бита b4 биту v0, бита b5 биту v4, бита b6 биту v6, и бита b7 биту v7.

11. Способ обратного отображения сигналов по п. 7, в котором, если 256-арная квадратурная амплитудная модуляция (256-QAM) используется в качестве схемы модуляции, длина LDPC-кодового слова Nldpc составляет 16200 (Nldpc=16200), число подпотоков Nsubstreams составляет 8 (Nsubstreams=8) и 8 подпотоков с b0 по b8 назначаются мультиплексированным битам с v0 по v8, мультиплексирование подпотоков содержит назначение бита b0 биту v1, бита b1 биту v3, бита b2 биту v4, бита b3 биту v5, бита b4 биту v0, бита b5 биту v2, бита b6 биту v6, и бита b7 биту v7.

12. Приемник сигналов в системе, использующей код с малой плотностью проверок на четность (LDPC), адаптированный для выполнения способа по одному из пп. 7-11.

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| СПОСОБ КОДИРОВАНИЯ КОДА РАЗРЕЖЕННОГО КОНТРОЛЯ ЧЕТНОСТИ | 2004 |

|

RU2308803C2 |

| УСТРОЙСТВО И СПОСОБ КОДИРОВАНИЯ/ДЕКОДИРОВАНИЯ КАНАЛА С ИСПОЛЬЗОВАНИЕМ ПАРАЛЛЕЛЬНОГО КАСКАДНОГО КОДА ПРОВЕРКИ НА ЧЕТНОСТЬ С НИЗКОЙ ПЛОТНОСТЬЮ | 2004 |

|

RU2310274C1 |

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| УСТРОЙСТВО ДЛЯ ОГРАНИЧЕНИЯ ПЕРЕНАПРЯЖЕНИЙ | 2000 |

|

RU2178214C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ОТНОШЕНИЯ ЗНАЧЕНИЙ АМПЛИТУД КВАЗИСИНУСОИДАЛЬНЫХ СИГНАЛОВ | 1994 |

|

RU2093886C1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

Авторы

Даты

2016-04-10—Публикация

2012-03-28—Подача