Область техники

Примеры реализации настоящего изобретения в целом относятся к системам связи и, в частности, к маломощному радиочастотному приемнику, преобразующему радиочастотный сигнал в цифровую форму, который может выполнять произвольную полосовую фильтрацию в радиочастотной (RF) области и может преобразовать с понижением частоты отфильтрованные радиочастотные (RF) сигналы в цифровой области.

Радиоприемник может преобразовывать сигналы от радиоантенны в форму, в которой их можно использовать. Конструкции для преобразования сигналов, полученных от антенны, могут содержать малошумящий усилитель (LNA), понижающие преобразователи частоты, управляемый напряжением генератор (VCO), низкочастотные фильтры (LPF), синтезирующую систему, опорный генератор, аналого-цифровые преобразователи (ADC) и цифровой сигнальный процессор (DSP), который может содержать модулятор. Создание этих встроенных в приемник узлов радиочастотных блоков и схем с аналоговой полосой пропускания и комбинированными сигналами может потребовать значительных конструкторских усилий и затрат. Кроме того, использование нецифровых схем может поднять вопрос ограниченности запаса по напряжению (амплитуде), возникающей по мере развития технологий и уменьшения питающего напряжения.

В одной из конструкций, выполненной для упрощения и смягчения остроты указанного вопроса ограниченности по напряжению путем удаления большей части схем с радиочастотными и аналоговыми полосами пропускания, входные сигналы от антенны могут быть усилены посредством малошумящего усилителя (LNA) и непосредственно дискретизированы посредством аналого-цифрового преобразователя (ADC). Большая часть обработки аналогового сигнала может быть перемещена в цифровой сигнальный процессор (DSP). Данная конструкция может вводить жесткие требования к аналого-цифровым преобразователям (ADC). Частота дискретизации аналого-цифрового преобразователя (ADC) может представлять собой частоту Найквиста несущей радиочастоты, которая может быть выше, чем ширина полосы частот сигнала. Это может привести к увеличению сложности конструкции и энергопотребления синхронизатора дискретизации для аналого-цифрового преобразователя (ADC). Даже при условии принятия стратегии дискретизации, в полосу пропускания может попасть дополнительный шум, что может уменьшить соотношение сигнал-шум (SNR) приемника.

Таким образом, было бы целесообразно создать систему и способ, решающий описанные выше проблемы.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Радиочастотный приемник, преобразующий радиочастотный сигнал в цифровую форму, содержит модулятор, дискретизирующий сигнал на первой частоте. Приемник содержит по меньшей мере один обрабатывающий блок. Обрабатывающий блок содержит множество цифровых полосовых фильтров, разделяющих сигнал и восстанавливающих сигнал на частоте, меньшей первой частоты. Обрабатывающий блок содержит цифровой понижающий преобразователь, регулирующий частотный сдвиг или центрирующий сигнал на частоте, меньшей первой частоты. Приемник содержит по меньшей мере одно буферное управляющее устройство для управления частотой, соединенное с соседними обрабатывающими блоками при размещении в приемнике по меньшей мере двух обрабатывающих блоков.

Многочастотный повышающий преобразователь содержит цифровой повышающий преобразователь, выполненный с возможностью приема сигнала. Множество цифровых полосовых фильтров соединено с цифровым повышающим преобразователем, выполненным с возможностью разделения сигнала. Цифровой маршрутизатор соединен с множеством полосовых фильтров для объединения сигнала. Цифро-аналоговый преобразователь присоединен к цифровому маршрутизатору для преобразования сигнала в аналоговый сигнал.

Способ уменьшения энергопотребления с использованием радиочастотного приемника включает прием сигнала; фильтрацию сигнала; дискретизацию сигнала на первой частоте; и выполнение по меньшей мере в одном обрабатывающем блоке разделения сигнала на субполосы на частоте обработки, меньшей первой частоты, восстановление сигнала из субполос на частоте обработки и корректирование частотного сдвига или центрирование сигнала на частоте обработки.

Особенности, функции и преимущества могут быть обеспечены независимо друг от друга в различных примерах реализации настоящего изобретения или могут быть объединены в других примерах реализации.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Примеры реализации настоящего изобретения будут более понятны из подробного описания и прилагаемых чертежей.

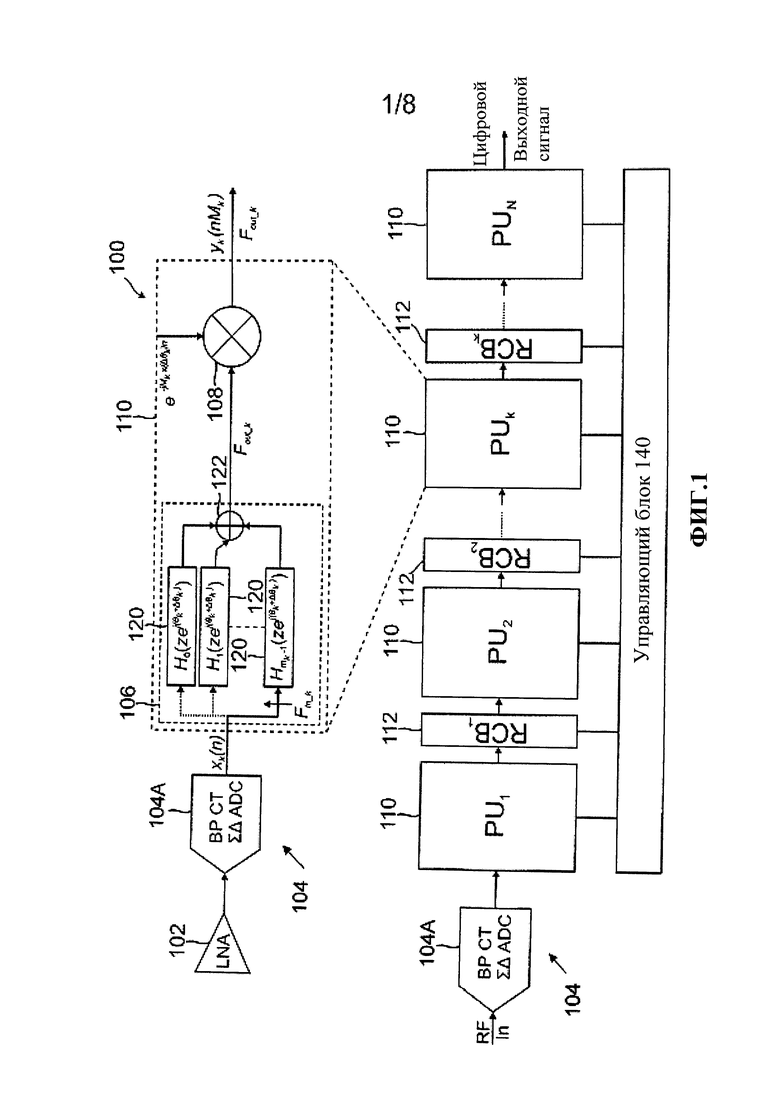

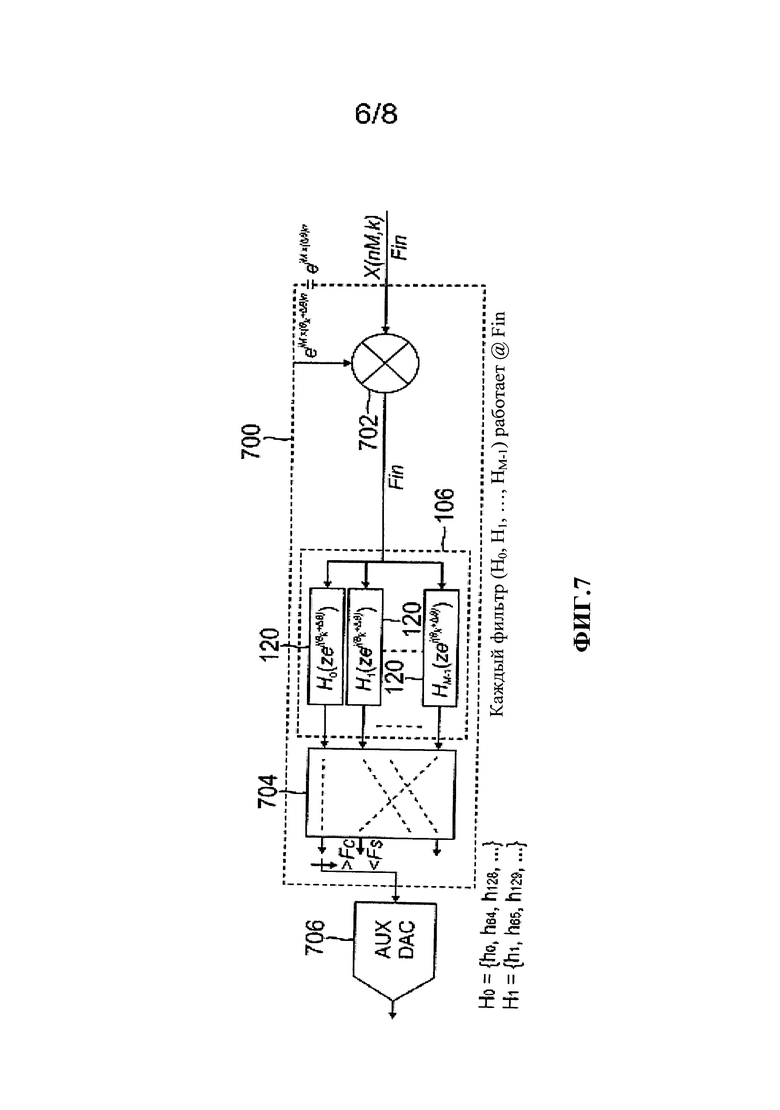

На фиг.1 показана блок-схема обобщенной конструкции приемника с однородным процессом обработки.

На фиг.2 показан график процесса преобразования сигнала от несущей частоты к полосе пропускания через множество стадий, каждая из которых выполнена посредством обрабатывающего блока.

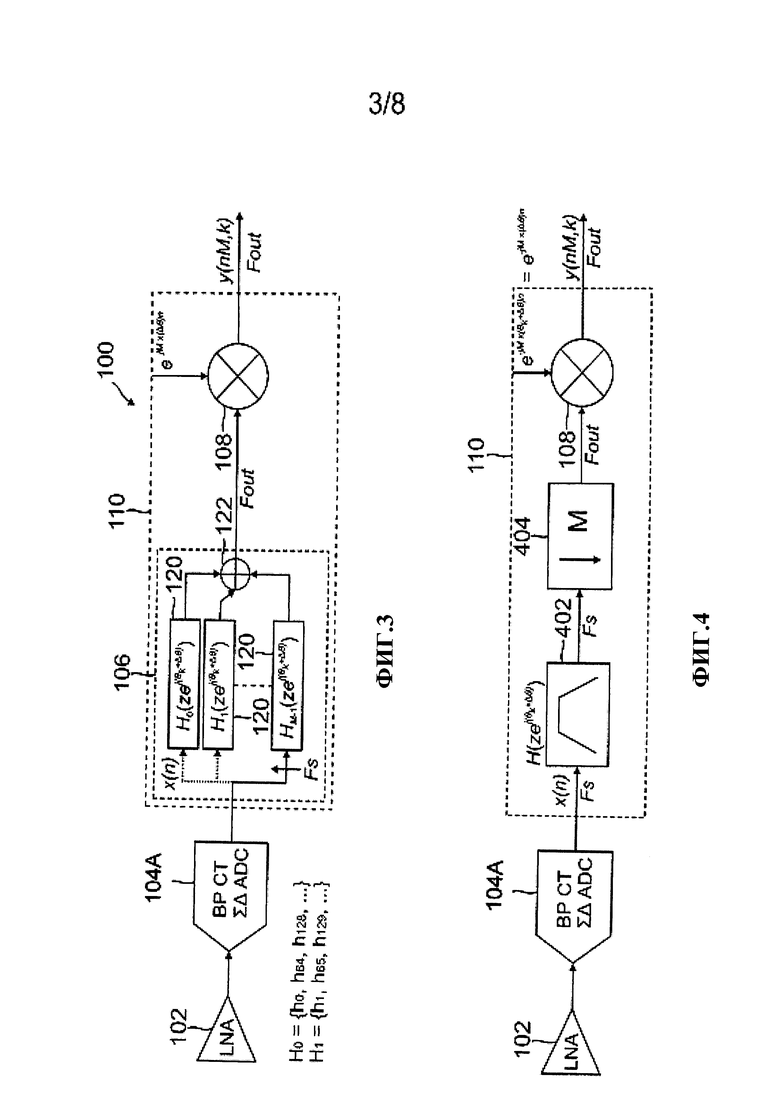

На фиг.3 показана блок-схема конкретного варианта приемника.

На фиг.4 показана блок-схема эквивалентного варианта реализации приемника.

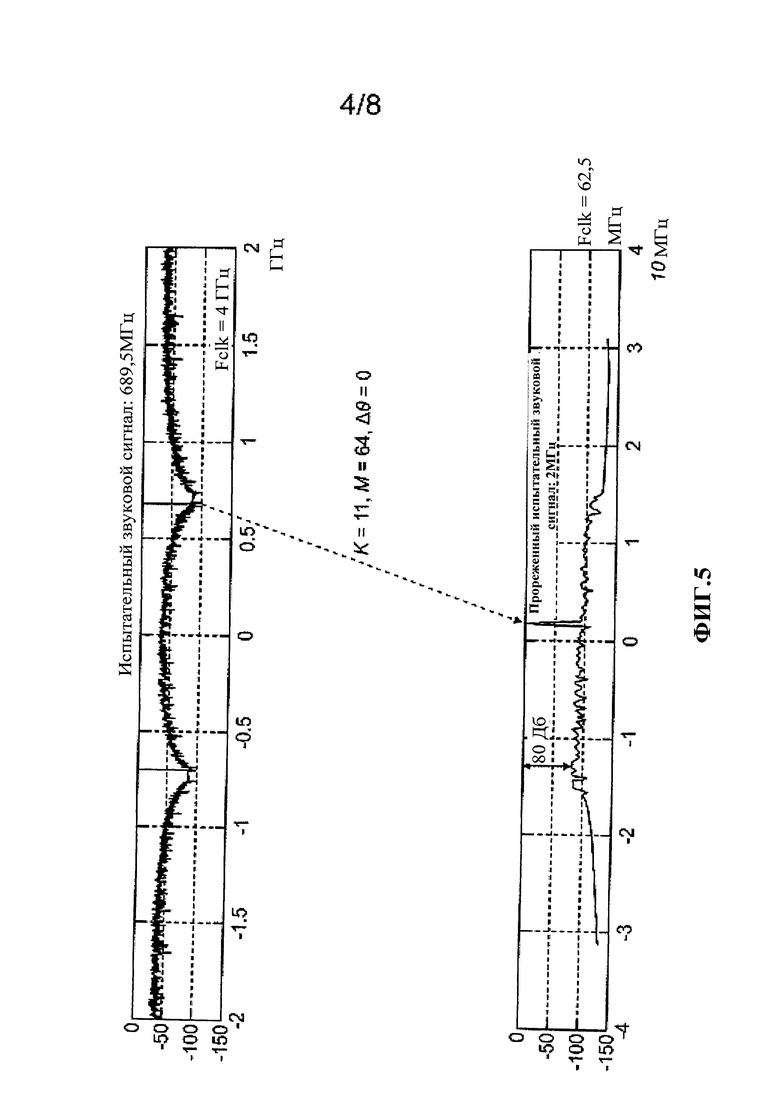

На фиг.5 показан график результатов моделирования для конкретного варианта приемника.

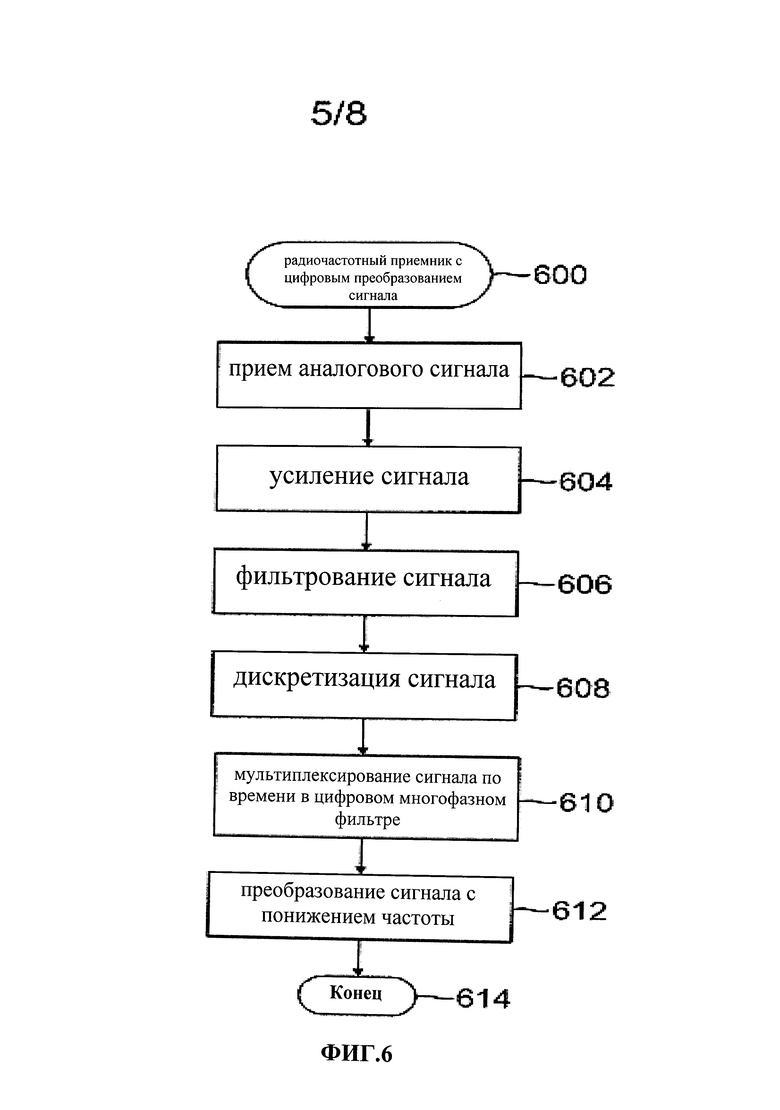

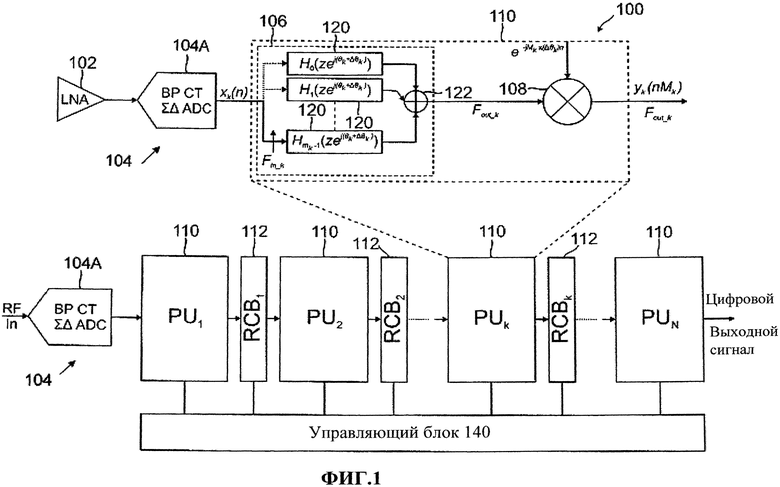

На фиг.6 показана схема процесса работы приемника.

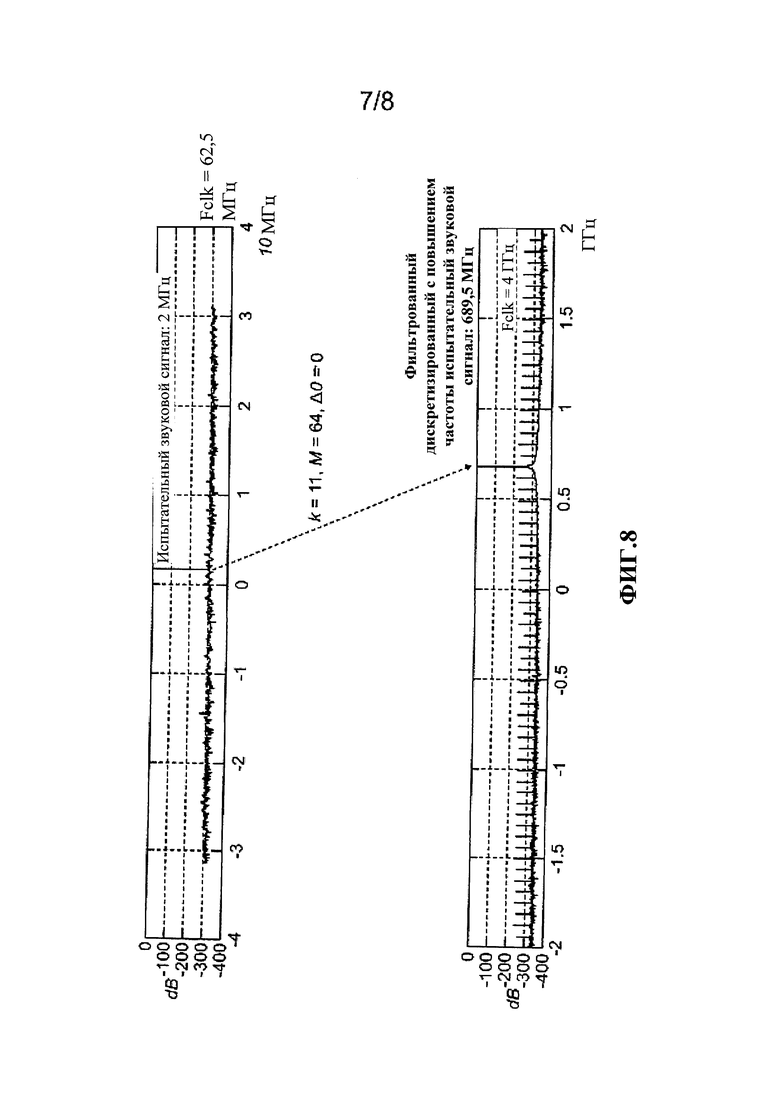

На фиг.7 показана блок-схема высокочастотного звукового генератора.

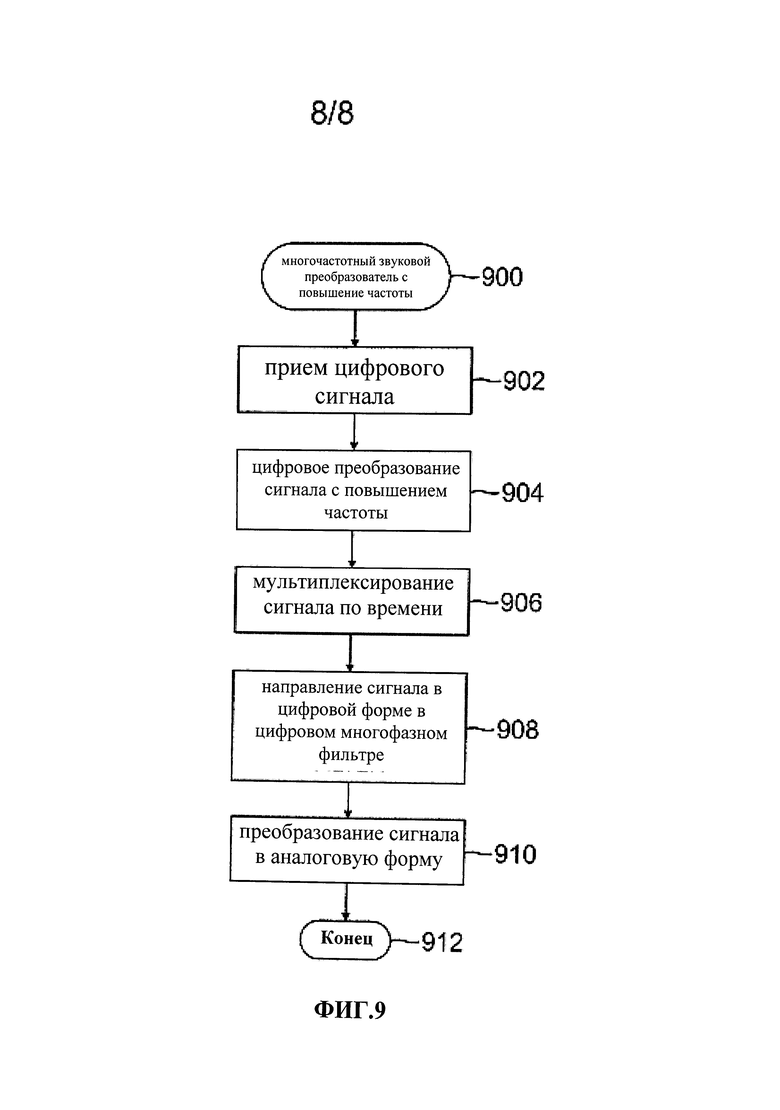

На фиг.8 показана схема процесса работы высокочастотного звукового генератора.

На фиг.9 показан график результатов моделирования для высокочастотного звукового генератора.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Согласно фиг.1 может быть показана блок-схема обобщенной конструкции приемника 100 с однородным процессом обработки. Приемник 100 может иметь маломощную конструкцию с цифровым преобразованием радиочастотного сигнала. Приемник 100 может быть описан далее в отношении мобильной платформы. Приемник 100 может быть размещен в смартфоне, мобильном телефоне или аналогичном устройстве, которое обрабатывает входящие радиочастотные сообщения. Кроме того, приемник 100 может быть использован в программно-определяемых радиосистемах (SDR), интеллектуальных радиосистемах, автомобильных средствах связи, мультимедийных системах для транспортных средств и т.п.

Приемник 100 может выполнять процесс полосовой фильтрации, дискретизацию, понижающее преобразование и прореживание при низком уровне сложности и энергоэффективным образом. В отличие от существующих подходов, которые могут содержать несколько конструктивных блоков для совокупности радиочастотной, аналоговой и цифровой областей и могут функционировать на очень высоких синхронизирующих частотах в цифровых схемах, приемник 100 может использовать сочетание многодиапазонной цифровой обработки сигнала (MDSP) и полосовой сигма-дельта аналого-цифровой преобразователь с непрерывным преобразованием (BP-CT-ΔΣ-ADC) для выполнения вышеописанных процессов в обтекаемом и прозрачном приспособлении, функционирующем на синхронизирующей частоте необходимой ширины полосы частот сигнала. Это может обеспечивать уменьшение времени ожидания от входных сигналов до выходных данных, уменьшение количества необходимых конструктивных блоков и уменьшение энергопотребления по сравнению с конструкциями уровня техники. Кроме того, конструкция может устранить жесткие требования к аналого-цифровым преобразователям (ADC). Приемник 100 может содержать конструктивные блоки, которые представляют собой аналоговые схемы или цифровые схемы, уменьшающие радиочастотные схемы, обеспечивающие устойчивость приемника 100 к изменению параметров процесса в современных технологиях сверхбольших интегральных схем (VLSI).

Приемник 100 может выполнять произвольную полосовую фильтрацию (BPF) в радиочастотной (RF) области. В примере реализации по фиг.1 приемник 100 может преобразовывать с понижением частоты отфильтрованные радиочастотные (RF) сигналы в цифровой области. Приемник 100 может применять методологию разработки схем с комбинированными сигналами и обрабатывать сигналы на частоте Найквиста. Приемник 100 может обеспечивать значительные преимущества, состоящие в низком энергопотреблении и небольшой сложности конструкции. Приемник 100 может быть основан на технологии многодиапазонной цифровой обработки сигнала (MDSP) и технологии полосового сигма-дельта аналого-цифрового преобразователя 104 с непрерывным преобразованием (BP-CT-ΔΣ-ADC).

Вместо обработки сигналов на частоте, которая кратна несущей частоте, приемник 100 может работать с сигналами на частоте, которая охватывает ширину полосы частот сигнала. Это уменьшение в частоте обработки может сохранить производительность системы обработки данных и уменьшить общее энергопотребление. Кроме того, маломощный радиочастотный приемник 100, преобразующий радиочастотный сигнал в цифровую форму, может содержать конструктивные блоки, которые могут быть запрограммированы и отрегулированы на необходимую входную частотную область и частоту выходных данных через программируемые модули. Часть многодиапазонной цифровой обработки сигнала (MDSP) приемника 100 может быть переконфигурирована для ее преобразования в многочастотный повышающий преобразователь, который может функционировать в качестве звукового генератора для калибровки в начале работы приемника 100.

В примере реализации по фиг.1 входные радиочастотные (RF) сигналы могут быть введены через антенну (не показано). Антенна может принимать радиоволны и преобразовывать их в электрической схеме. Антенна может быть соединена с усилителем 102. Усилитель 102 может представлять собой малошумящий усилитель (LNA) 102 и может увеличивать мощность сигнала, принимаемого посредством антенны приемника 100.

Малошумящий усилитель (LNA) 102 может быть присоединен к модулятору 104. Модулятор 104 может принимать сигнал от усилителя 102. В примере реализации по фиг.1 модулятор 104 может представлять собой полосовой сигма-дельта аналого-цифровой преобразователь 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) и может обрабатывать сигнал путем его фильтрации и дискретизации. Путем перевода сигнала в цифровую область полосовой сигма-дельта аналого-цифровой преобразователь 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) может обеспечивать помехозащищенность, надежность и универсальность и может привнести потенциальные улучшения в технические характеристики, энергопотребление и уменьшение затрат. Полосовой сигма-дельта аналого-цифровой преобразователь 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) может обеспечивать возможность высокоскоростной работы при одновременном сохранении низкого энергопотребления и площади кристалла. Отсчеты отфильтрованного сигнала, показанные в качестве Xk(n), могут быть созданы на выходе полосового сигма-дельта аналого-цифрового преобразователя 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) на частоте Fin_k. Выходной сигнал может обеспечивать высокую степень программируемости и может представлять собой идеальный сигнал для многостандартных радиочастотных приемников 100.

Полосовой сигма-дельта аналого-цифровой преобразователь 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) может преобразовывать с понижением частоты входной сигнал, принятый малошумящим усилителем (LNA) 102 в полосе пропускания. Модулятор 104 может подходить для выполнения аналого-цифрового преобразования (ADC) в полосе пропускания на основании узкополосных сигналов. Отфильтрованный сигнал может быть оцифрован частью модулятора 104 с непрерывной дельта-сигма модуляцией (CT-AI). Полосовой сигма-дельта аналого-цифровой преобразователь 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) может комбинировать входной сигнал и оцифровывать его, что может потребовать усиления посредством малошумящего усилителя (LNA) 102. Полосовой сигма-дельта аналого-цифровой преобразователь 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) может обеспечить использование целого числа синусоидальных импульсов для обратной связи. Основная функция обратной связи может представлять собой по существу полосу пропускания. Это может значительно улучшить технические характеристики модулятора 104 при наличии флуктуации времени задержки и паразитной модуляции длительности импульса. Кроме того, частота дискретизации модулятора 104 может быть меньше несущей частоты, на которую настроен модулятор 104.

Модулятор 104 может быть присоединен к цифровому многофазному фильтру (DPF) 106 согласно примеру реализации по фиг.1. Цифровой многофазный фильтр (DPF) 106 может принимать выходной сигнал полосового сигма-дельта аналого-цифрового преобразователя 104А с непрерывным преобразованием (ВР-СТ-ΔΣ-ADC), показанный как Xk(n). Цифровой многофазный фильтр (DPF) 106 может реализовать многодиапазонную цифровую обработку сигнала (MDSP), что обеспечивает преобразование сигнала с понижением частоты и его прореживание. Фильтр 106 может разделять входной сигнал Xk(n) на некоторое количество равноотстоящих субполос 120, которые субдискретизированы посредством коэффициента М таким образом, что они могут быть дискретизированы в необходимых пределах.

Субполосы 120 могут представлять собой матрицу полосовых фильтров 120 с конечной импульсной характеристикой (FLF), которые разделяют входной сигнал, Xk(n), на множество компонент и каждый из которых фильтрует первоначальный сигнал с различными фильтрационными коэффициентами. Например, фильтрационный коэффициент может составлять Hn(zej(θk+…). Согласно фиг.1 первый фильтрационный коэффициент может составлять H0(zej(θk+…). Цифровой многофазный фильтр (DPF) 106 может восстановить сигнал через объединитель 122 из субполос 120 на частоте Fout_k. Частота Fout_k может быть дифференцирована от частоты Fin_k и может представлять собой частоту, меньшую частоты Fin_k.

Каждый из полосовых фильтров 120 цифрового многофазного фильтра (DPF) 106 может работать на частоте Fout_k. Частота Fout_k может быть больше, чем необходимая ширина полосы пропускания сигнала. Частота Fout_k обычно может быть намного меньше, чем частота Fin_k и может быть выбрана таким образом, что частота Fin_k кратна частоте Fout_k. Количество фильтров 120 с конечной импульсной характеристикой (FLF), обозначенное через М, может быть задано в качестве отношения частоты Fin_k к частоте Fout_k. В цифровом многофазном фильтре (DPF) 106 всего может быть выполнено М субфильтров 120 с конечной импульсной характеристикой (FLF), каждый из которых функционирует на частоте Fout_k. Выходные сигналы Xk(n) полосового сигма-дельта аналого-цифрового преобразователя 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) мультиплексированы по времени в каждой субполосе 120, как обозначено пунктирными линиями, показывающими разделение сигнала.

На фиг.2 показан график процесса преобразования сигнала от несущей частоты к полосе пропускания через множество этапов (сверху вниз), каждый из которых выполнен посредством обрабатывающего блока (PU) 110. Конечные импульсные характеристики (FIR) могут быть использованы цифровым многофазным фильтром (DPF) 106 для получения отсчетов из входного сигнала Xk(n). Выходные сигналы от фильтров 120 с конечной импульсной характеристикой (FLF) 120 могут быть затем объединены в объединителе 122 на частоте Fout_k.

В примере реализации по фиг.1 цифровой многофазный фильтр (DPF) 106 может быть присоединен к цифровому понижающему преобразователю (DDC) 108, причем они оба могут работать на частоте Fout_k. Цифровой понижающий преобразователь (DDC) 108 может преобразовывать выходной сигнал цифрового многофазного фильтра (DPF) 106 в оцифрованный действующий сигнал, центрированный на промежуточной частоте (IF), или полосовой комплексный сигнал, центрированный на нулевой частоте. Цифровой понижающий преобразователь (DDC) 108 приемника 100 может затем обеспечить выходной сигнал yk(nMk) на частоте Fout_k.

Приемник 100 может быть размещен в устройстве или может составлять часть единой конструкции с обрабатывающим блоком (PU) 110, в которой множество цифровых многофазных фильтров (DPF) 106 и цифровых понижающих преобразователей (DDC) 108 могут быть размещены последовательно с усилителем 102 и модулятором 104. В одном из показанных примеров реализации полосовой сигма-дельта аналого-цифровой преобразователь 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) может быть присоединен к первому обрабатывающему блоку (PU) 110, а именно к PU1, и по существу ко многим другим обрабатывающим блокам (PU) 110. Каждый обрабатывающий блок (PU) 110 может обрабатывать сигнал. Буферное запоминающее устройство 112 для преобразования частоты (RCB) может быть соединено между обрабатывающими блоками (PU) 110 в приемнике 100. Буферные запоминающие устройства 112 для преобразования частоты (RCB) могут быть использованы для обработки сигнала на одной частоте дискретизации и преобразовывания его в новую частоту дискретизации. Количество обрабатывающих блоков (PU) 110 и буферных запоминающих устройств 112 для преобразования частоты (RCB) может быть отрегулировано. Цифровой выходной сигнал может быть получен путем объединения обрабатывающих блоков (PU) 110 и буферных запоминающих устройств 112 для преобразования частоты (RCB).

Согласно фиг. 1 приемник 100 может содержать по меньшей мере один обрабатывающий блок (PU) 110. Каждый обрабатывающий блок (PU) 110 может содержать множество цифровых полосовых фильтров 120 в цифровом многофазном фильтре (DPF) 106. Множество цифровых полосовых фильтров 120 может разделить сигнал, поступающий на частоте Fin_k, и может восстановить сигнал на частоте Fout_k, которая меньше частоты входного сигнала Fin_k. Частоты Fin_k и Fout_k могут быть различны для каждого обрабатывающего блока (PU) 110. Цифровые понижающие преобразователи (DDC) 108 в обрабатывающих блоках (PU) 110 могут регулировать частотный сдвиг или могут центрировать сигнал на частоте, меньшей частоты входного сигнала Fout_k. По меньшей мере одно буферное запоминающее устройство 112 для преобразования частоты (RCB) может быть присоединено к соседним обрабатывающим блокам (PU) 110 при размещении в приемнике 100 по меньшей мере двух обрабатывающих блоков (PU) 110.

Приемник 100 может содержать управляющее устройство 140. Управляющее устройство 140 может быть встроено в приемник 100 при условии работы по меньшей мере двух обрабатывающих блоков (PU) 110. Согласно фиг. 1, управляющее устройство 140 может быть присоединено к каждому из обрабатывающих блоков (PU) 110 и буферных запоминающих устройств 112 для преобразования частоты (RCB) в приемнике 100. Это соединение может обеспечивать возможность конфигурирования обрабатывающих блоков (PU) 110 и буферных запоминающих устройств 112 для преобразования частоты (RCB). При конфигурировании могут быть отрегулированы частоты, на которых происходит обработка сигнала.

Управляющее устройство 140 может быть запрограммировано в программном обеспечении, аппаратном обеспечении или их сочетании. В программной реализации код может быть реализован на нетранзисторном машиночитаемом носителе. Нетранзисторный машиночитаемый носитель управляющего устройства 140 может содержать, без ограничения, энергозависимую память, неэнергозависимую память, магнитные и оптические запоминающие устройства или другие носители, которые выполнены с возможностью хранения кода и/или данных и которые известны или будут разработаны в уровне техники. Код может быть считан и выполнен посредством компьютерной системы, выполняющей способы и процессы, реализованные в качестве структур данных и кода, сохраненных в нетранзисторном машиночитаемом носителе. Кроме того, способы и процессы для управляющего устройства 140 могут быть включены в аппаратные модули. Эти аппаратные модули могут включать чипы со специализированными интегральными схемами (ASIC), логические матрицы с программированием в условиях эксплуатации (FPGA) и другие программируемые логические устройства, известные в уровне техники или разработанные в дальнейшем.

Управляющее устройство 140 может конфигурировать каждый обрабатывающий блок (PU) 110 путем регулирования цифровых полосовых фильтров 120 и цифровых понижающих преобразователей (DDC) 108. В одном из примеров реализации обрабатывающие блоки (PU) 110 и буферные запоминающие устройства 112 для преобразования частоты (RCB) могут быть конфигурированы другим способом, например аппаратным. Управляющее устройство 140 может обходить цифровой понижающий преобразователь (DDC) 108 в обрабатывающем блоке (PU) 110 путем регулирования входной частоты в качестве частоты, кратной частоте обработки текущего обрабатывающего блока (PU) 110, и регулирования несущей частоты в качестве частоты, кратной частоте обработки текущего обрабатывающего блока (PU) 110, при соединении текущего обрабатывающего блока (PU) 110 с модулятором 104. В альтернативном варианте управляющее устройство 140 может регулировать частоту обработки предыдущего обрабатывающего блока (PU) 110 в качестве частоты, кратной частоте обработки текущего обрабатывающего блока (PU) 110, и может регулировать промежуточную частоту в качестве частоты, кратной частоте обработки текущего обрабатывающего блока (PU) 110.

Полученный сигнал может быть разделен в каждом обрабатывающем блоке (PU) 110 путем мультиплексирования по времени. При соединении обрабатывающего блока (PU) 110 с модулятором 104 дискретизированный сигнал от модулятора 104 может быть обеспечен в каждой субполосе 120 цифрового многофазного фильтра (DPF) 106. В альтернативном варианте выходные сигналы предыдущего обрабатывающего блока (PU) 110 могут быть мультиплексированы по времени в субполосах 120 цифрового многофазного фильтра (DPF) 106 текущего обрабатывающего блока (PU) 110.

При использовании множества обрабатывающих блоков (PU) 110 в приемнике 100 всего может функционировать М субфильтров 120 с конечной импульсной характеристикой на частоте Fout_k, меньшей входной частоты Fin_k. М может представлять собой отношение первой частоты к частоте обработки текущего обрабатывающего блока (PU) 110 при размещении обрабатывающего блока (PU) 110 после модулятора 104. При отсутствии соединения обрабатывающего блока (PU) 110 с модулятором 104, например, PU2110, PUk 110 или PUN 110, М может представлять собой отношение частоты обработки предыдущего обрабатывающего блока (PU) 110 к частоте обработки текущего обрабатывающего блока (PU) 110.

Согласно приведенному выше описанию модулятор 104 может обрабатывать сигнал на первой частоте. Первая частота может быть больше несущей частоты. Обрабатывающие блоки (PU) 110, содержащие множество цифровых полосовых фильтров 120 и цифровых понижающих преобразователей (DDC) 108, могут обрабатывать сигнал на частоте большей или равной частоте Найквиста в полосе пропускания сигнала. Обычно эта частота может быть меньше несущей частоты.

Цифровые понижающие преобразователи (DDC) 108 в каждом обрабатывающем блоке (PU) 110 могут функционировать и создавать выходные сигналы на частоте, идентичной частоте М субфильтров 120 с конечной импульсной характеристикой в идентичном обрабатывающем блоке (PU) 110. В одном из примеров реализации цифровой понижающий преобразователь (DDC) 108 в каждом обрабатывающем блоке (PU) 110 может центрировать сигнал на нулевой частоте, если обрабатывающий блок последним создает выходные сигналы. В альтернативном варианте цифровые понижающие преобразователи (DDC) 108 могут корректировать частотный сдвиг до необходимой промежуточной частоты. Первая частота может быть больше несущей частоты. Частота обработки каждого обрабатывающего блока (PU) 110 может охватывать полосу пропускания сигнала и может быть меньше несущей частоты.

Согласно фиг.3 может быть описана блок-схема отдельного варианта приемника 100. Приемник 100 может работать с одним обрабатывающим блоком (PU) 110. Радиочастотный (RF) сигнал может быть принят посредством антенны (не показана). Малошумящий усилитель (LNA) 102 может быть присоединен к антенне. Малошумящий усилитель (LNA) 102 может улучшить сигнал, принятый от антенны. Модулятор 104 может быть присоединен к малошумящему усилителю (LNA) 102. Полосовой сигма-дельта аналого-цифровой преобразователь 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) может обрабатывать сигнал от малошумящего усилителя (LNA) 102 путем его фильтрации и дискретизации. Сигнал может быть обработан на первой частоте FS. Частота FS может быть кратна несущей частоте.

Сигнал после его обработки модулятором 104 может быть передан на цифровой многофазный фильтр (DPF) 106. Выходной сигнал модулятора 104 может составлять х(n). В примере реализации по фиг.3 сигнал может быть обработан посредством фильтров 120 с конечной импульсной характеристикой (FLF). Фильтры 120 с конечной импульсной характеристикой (FLF) могут обеспечивать субполосы, причем каждый из этих фильтров фильтрует первоначальный сигнал с различными фильтрационными коэффициентами. Например, фильтрационный коэффициент может составлять Hn(zej(θk+…). Согласно фиг.3 первый фильтрационный коэффициент может составлять H0(zej(θk+…). В данном примере реализации субполосы 120 могут быть представлены для 64 дискретных компонент. Например, каждая субполоса 120 может дискретизировать при коэффициенте, составляющем 64, для предельной дискретизации. Сигнал может быть восстановлен из шестидесяти четырех субполос 120 на второй частоте FOUT посредством объединителя 122. Количество субполос 120, составляющее шестьдесят четыре, может быть эквивалентно или пропорционально отношению первой частоты FS ко второй частоте FOUT. Восстановленный сигнал может быть передан на цифровой понижающий преобразователь (DDC) 108 и выдан в качестве выходного сигнала y(nM,k). Частота FS может быть кратна несущей частоте, а частота FOUT может охватывать полосу пропускания сигнала.

Вся работа цифрового многофазного фильтра (DPF) 106 может быть эквивалентна сочетанию цифрового полосового фильтра (DBF) 402 и цифрового прореживателя 404 (DDEC) с шагом прореживания М-1, показанных в примере реализации по фиг.4. Согласно чертежу сигнал может быть принят от антенны посредством малошумящего усилителя (LNA) 102. Полосовой сигма-дельта аналого-цифровой преобразователь 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) может оцифровывать сигнал и подавать его на цифровой полосовой фильтр (DBF) 402 в обрабатывающем блоке (PU) 110. Сигнал х(n) может быть выдан на частоте FS согласно приведенному выше описанию.

Цифровой полосовой фильтр (DBF) 402 может выполнять операции для фильтрации сигнала в заданной полосе пропускания. К цифровому полосовому фильтру (DBF) 402 может быть присоединен цифровой прореживатель (DDEC) 404. Цифровой прореживатель (DDEC) 404 может уменьшать количество отсчетов в дискретном сигнале, принимаемом от цифрового полосового фильтра (DBF) 402. Цифровой прореживатель (DDEC) 404 может довести сигнал, принятый от цифрового полосового фильтра (DBF) 402 до полосы пропускания. Уменьшение может быть пропорционально М, которое было задано в качестве отношения частоты FS к частоте FOUT. Цифровой понижающий преобразователь (DDC) 108, присоединенный к цифровому прореживателю (DDEC) 404, может затем преобразовывать сигнал с понижением частоты на частоте FOUT. Цифровой понижающий преобразователь (DDC) 108 может затем обеспечить выходной сигнал y(nM,k). Сочетание цифрового полосового фильтра (DBF) 402 и цифрового прореживателя (DDEC) 404 может быть эквивалентно цифровому многофазному фильтру (DPF) 106. Цифровой полосовой фильтр (DBF) 402 и цифровой прореживатель (DDEC) 404 могут функционировать на частоте FS. Несмотря на то, что оба этих устройства функционируют на более высокой частоте FS, цифровой многофазный фильтр (DPF) 106 по фиг.3, функционирующий на частоте FOUT, потребляет меньше энергии, чем сочетание цифрового полосового фильтра (DBF) 402 и цифрового прореживателя (DDEC) 404 по фиг.4.

Фильтрационные коэффициенты для каждой субполосы или фильтра 120 с конечной импульсной характеристикой (FLF) могут быть представлять собой мультиплексированные по времени значения соответствующих коэффициентов цифрового полосового фильтра (DBF) 402. В одном из примеров реализации коэффициенты цифрового полосового фильтра (DBF) 402 могут представлять собой перевернутые или преобразованные версии коэффициентов фильтра нижних частот (DLF). Фильтр нижних частот (DLF) может иметь фильтровую ширину полосы пропускания, идентичную цифровому полосовому фильтру (DBF) 402, однако он обрабатывает преобразованные с понижением частоты отсчеты в полосе пропускания. Угол поворота может составлять θk+Δθ, причем θk равно 2π×k×FS/М, а Δθ может составлять разницу между несущей частотой (FC) и θk.

На фиг.5 показан график результатов моделирования для приемника 100. На графике показано объединение процессов полосового сигма-дельта аналого-цифрового преобразователя 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC) и цифрового многофазного фильтра (DPF) 106.

Согласно фиг.6 может быть описана диаграмма процесса работы приемника 100. Начало процессов для приемника 100 может происходить в блоке 600. В блоке 602 антенна приемника 100 может принимать радиочастотный сигнал. Радиочастотный (FR) сигнал может быть усилен посредством малошумящего усилителя (LNA) 102 в блоке 604. Сигнал может быть отфильтрован в блоке 606. Сигнал может быть дискретизирован в блоке 608. Фильтрация и дискретизация сигнала могут быть выполнены посредством полосового сигма-дельта аналого-цифрового преобразователя 104А с непрерывным преобразованием (BP-CT-ΔΣ-ADC).

В блоке 610 сигнал может быть мультиплексирован по времени в цифровом многофазном фильтре. Цифровой многофазный фильтр (DPF) 106 может разделить оцифрованный сигнал, принятый от модулятора 104, на субполосы 120. Сигнал может быть создан из этих субполос 120 через объединитель 122 цифрового многофазного фильтра (DPF) 106. Восстановленный сигнал может быть преобразован с понижением частоты в блоке 612. Выходной сигнал цифрового понижающего преобразователя (DDC) 108 может быть затем дополнительно обработан или использован путем применений на устройстве. Процессы могут быть завершены в блоке 614.

Согласно фиг.7 может быть описан высокочастотный звуковой генератор 700. Сигнальные пути приемника 100, описанного ранее, могут быть переконфигурированы для обеспечения генератора 700. Высокочастотный звуковой генератор 700 может содержать цифровой повышающий преобразователь (DUC) 702, цифровой многофазный фильтр (DPF) 106 и цифровой маршрутизатор (DR) 704. Дополнительный цифро-аналоговый преобразователь (AUX DAC) 706 может быть присоединен к генератору 700 через цифровой маршрутизатор (DR) 704. Цифровой сигнал, x(nM,k) может быть передан на цифровой повышающий преобразователь (DUC) 702. Сигнал может быть комбинирован с комплексным сигналом посредством цифрового повышающего преобразователя (DUC) 702 и передан на цифровой многофазный фильтр (DPF) 106 на частоте Fin.

В примере реализации по фиг.7 сигнальные пути для цифрового многофазного фильтра (DPF) 106 и цифрового понижающего преобразователя (DDC) 108 приемника 100 могут быть просто переконфигурированы в противоположном направлении таким образом, что весь приемник 100 может быть преобразован в высокочастотный звуковой генератор 700 посредством цифро-аналогового преобразователя (DAC). Каждая субполоса 120 цифрового многофазного фильтра (DPF) 106 может брать часть входного сигнала. Субполосы 120 могут быть присоединены к цифровому маршрутизатору (DR) 704. Цифровой маршрутизатор (DR) 704 может мультиплексировать выходной сигнал субполос в единичный сигнал. Дополнительный цифро-аналоговый преобразователь (AUX DAC) 706 может быть присоединен к цифровому маршрутизатору (DR 704). Дополнительный цифро-аналоговый преобразователь (AUX DAC) 706 может брать сигнал и преобразовывать его в аналоговую форму. Сигнал может быть передан на передатчик. Передатчик может преобразовывать электрические сигналы в радиочастотные сообщения. Частота Fin меньше высокочастотной звуковой частоты, что может уменьшить энергопотребление.

На фиг.8 показан график результатов моделирования для высокочастотного звукового генератора 700. Выходные сигналы этого звукового генератора 700 могут выполнять функцию испытательных сигналов, подаваемых на входы малошумящего усилителя (LNA) 102 или полосового сигма-дельта аналого-цифрового преобразователя 104 с непрерывным преобразованием (BP-CT-ΔΣ-ADC) для выполнения калибровки в начале работы приемника 100.

Согласно фиг.9 может быть описана диаграмма процесса работы высокочастотного звукового генератора 700. Начало процессов генератора 700 может происходить в блоке 900. В блоке 902 цифровой повышающий преобразователь (DUC) 702 генератора 700 может принимать цифровой сигнал. В блоке 904 цифровой повышающий преобразователь (DUC) 702 может надлежащим образом форматировать оцифрованный сигнал путем его преобразования с повышением частоты. Сигнал может быть мультиплексирован по времени посредством цифрового многофазного фильтра (DPF) 106 в блоке 906. Цифровой многофазный фильтр (DPF) 106 может быть видоизменен для генератора 700 и может разделять сигнал на частоте Fin.

В блоке 908 сигнал может быть перенаправлен в цифровой форме через цифровой маршрутизатор (DR) 704 в цифровом многофазном фильтре. Восстановление сигнала на частоте большей Fin может быть использовано цифровым маршрутизатором (DR) 704. Вследствие более низких скоростей обработки на первоначальных стадиях обработки может быть обеспечено сохранение энергии. В блоке 910 сигнал может быть преобразован в аналоговый сигнал посредством дополнительного цифро-аналогового преобразователя (AUX DAC) 706. Завершение процессов может происходить в блоке 912.

Согласно чертежам и приведенному выше описанию раскрыт радиочастотный приемник 100, преобразующий радиочастотный сигнал в цифровую форму, содержащий модулятор 104, дискретизирующий сигнал на первой частоте; по меньшей мере один обрабатывающий блок 110, содержащий множество цифровых полосовых фильтров 120, разделяющих сигнал и восстанавливающих сигнал на частоте, меньшей первой частоты; цифровой понижающий преобразователь 108, регулирующий частотный сдвиг или центрирующий сигнал на частоте, меньшей первой частоты; и по меньшей мере одно буферное управляющее устройство для управления частотой, соединенный с соседними обрабатывающими блоками 110 при размещении по меньшей мере двух обрабатывающих блоков 110 в приемнике 100.

В одном из вариантов радиочастотный приемник 100 с цифровым преобразованием сигнала содержит управляющее устройство 140, конфигурирующее соединения по меньшей мере между одним обрабатывающим блоком 110 и по меньшей мере одним буферным управляющим устройством для управления частотой при размещении по меньшей мере двух обрабатывающих блока 110 в приемнике 100. Еще в одном варианте радиочастотный приемник 100, преобразующий радиочастотный сигнал в цифровую форму, содержит усилитель 102 для приема и усиления сигнала до его приема модулятором 104. Еще в одном варианте модулятор 104 представляет собой полосовой сигма-дельта аналого-цифровой преобразователь с непрерывным преобразованием. Еще в одном варианте множество цифровых полосовых фильтров 120 в каждом обрабатывающем блоке 110 выполнены в виде цифрового многофазного фильтра 106.

В одном из альтернативных вариантов множество цифровых полосовых фильтров 120 в каждом обрабатывающем блоке 110 содержит всего М субфильтров с конечной импульсной характеристикой, каждый из которых функционирует на частоте, меньшей первой частоты, причем М представляет собой отношение первой частоты к частоте обработки текущего обрабатывающего блока 110 при размещении текущего обрабатывающего блока 110 после модулятора 104 или М представляет собой отношение частоты обработки предыдущего обрабатывающего блока 110 к частоте обработки текущего обрабатывающего блока 110. Еще в одном варианте входные сигналы на М субфильтров с конечной импульсной характеристик в каждом обрабатывающем блоке 110 поданы путем мультиплексирования по времени выходных сигналов модулятора 104 при размещении текущего обрабатывающего блока 110 после модулятора 104 или мультиплексирования по времени выходных сигналов обрабатывающего блока 110.

Еще в одном варианте, в котором модулятор 104 обрабатывает сигнал на первой частоте, которая больше несущей частоты, множество цифровых полосовых фильтров 120 и цифровые понижающие преобразователи 108 в каждом обрабатывающем блоке 110 обрабатывают сигнал на частоте, которая больше или равна частоте Найквиста в полосе пропускания сигнала, однако меньше несущей частоты. Еще в одном варианте цифровой преобразователь 108 с понижением частоты в каждом обрабатывающем блоке 110 функционирует и создает выходные сигналы для обрабатывающего блока 110 на частоте, идентичной частоте М субфильтров с конечной импульсной характеристикой в идентичном обрабатывающем блоке 110. В одном из примеров цифровой преобразователь 108 с понижением частоты в каждом обрабатывающем блоке 110 центрирует сигнал на нулевой частоте при условии, что обрабатывающий блок 110 последним создает окончательные выходные сигналы, в противном случае он корректирует частотный сдвиг до необходимой промежуточной частоты. Еще в одном варианте, в котором первая частота больше несущей частоты, частота обработки каждого обрабатывающего блока 110 охватывает полосу пропускания сигнала и меньше несущей частоты.

В одном из вариантов раскрыт многочастотный повышающий преобразователь, содержащий цифровой повышающий преобразователь 702 для приема сигнала, множество цифровых полосовых фильтров 120, соединенных с цифровым повышающим преобразователем 702 для разделения сигнала; цифровой маршрутизатор, соединенный с множеством цифровых полосовых фильтров120 для объединения сигнала; и цифро-аналоговый преобразователь 706, присоединенный к цифровому маршрутизатору для преобразования сигнала в аналоговый сигнал. В одном из вариантов сигнал подан в качестве тестирующего сигнала на малошумящий усилитель 102 или модулятор 104 в радиочастотном приемнике 100 с цифровой обработкой сигнала для выполнения калибровки. Еще в одном варианте многочастотный повышающий преобразователь содержит радиочастотный приемник 100 с цифровой обработкой сигнала. В одном из вариантов цифровой повышающий преобразователь 702 и множество цифровых полосовых фильтров 120 повторно использованы в качестве обрабатывающего блока 110 в радиочастотном приемнике 100, преобразующем радиочастотный сигнал в цифровую форму. В одном из альтернативных вариантов радиочастотный приемник 100 содержит модулятор 104, дискретизирующий сигнал на первой частоте; множество обрабатывающих блоков 110, каждый из которых содержит: множество цифровых полосовых фильтров 120, разделяющих сигнал и восстанавливающих сигнал на частоте, меньшей первой частоты; цифровой понижающий преобразователь 108, регулирующий частотный сдвиг или центрирующий сигнал; по меньшей мере одно буферное управляющее устройство для управления частотой, соединенное с соседними обрабатывающими блоками 110; и управляющее устройство 140, конфигурирующее соединения между каждым обрабатывающим блоком 110 и буферным управляющим устройством для управления частотой.

В одном из вариантов раскрыт способ для уменьшения энергопотребления на приемнике 100, включающий: прием сигнала; фильтрацию сигнала; дискретизацию сигнала на первой частоте; по меньшей мере в одном обрабатывающем блоке 110: разделение сигнала на субполосы 120 на частоте обработки, меньшей первой частоты; восстановление сигнала из субполос 120 на частоте обработки; и корректирование частотного сдвига или центрирование сигнала на частоте обработки.

В одном из вариантов способ включает обход цифрового понижающего преобразователя 108 в обрабатывающем блоке 110 путем регулирования первой частоты в качестве частоты, кратной частоте обработки текущего обрабатывающего блока 110, и регулирования несущей частоты в качестве частоты, кратной частоте обработки текущего обрабатывающего блока 110 при соединении текущего обрабатывающего блока 110 с модулятором 104 или регулирования частоты обработки предыдущего обрабатывающего блока 110 в качестве частоты, кратной частоте обработки текущего обрабатывающего блока 110, и регулирования промежуточной частоты в качестве частоты, кратной частоте обработки текущего обрабатывающего блока 110.

В одном из вариантов разделение сигнала включает временное мультиплексирование дискретизированного сигнала в каждой субполосе 120 при соединении текущего обрабатывающего блока 110 с модулятором 104 или временное мультиплексирование выходных сигналов предыдущего обрабатывающего блока 110 в каждой субполосе 120 в текущем обрабатывающем блоке 110. Еще в одном варианте способ может включать конфигурирование каждого обрабатывающего блока 110 путем регулирования множества цифровых полосовых фильтров 120 и цифрового понижающего преобразователя 108 в обрабатывающем блоке 110 посредством управляющего устройства 140 или обход множества цифровых полосовых фильтров 120 и цифрового преобразователя 108 с понижением частоты в обрабатывающем блоке 110 посредством управляющего устройства 140.

Несмотря на то, что примеры реализации настоящего изобретения были в терминах различных конкретных примеров реализации, специалисту в области техники будет понятно, что примеры реализации настоящего изобретения могут быть реализованы с изменениями в рамках сущности и объема формулы изобретения.

Изобретение относится к системам связи, в частности к приемнику, преобразующему радиочастотный сигнал в цифровую форму, и предназначено для уменьшения соотношения сигнал-шум приемника. Приемник, преобразующий радиочастотный сигнал в цифровую форму, содержит модулятор, дискретизирующий сигнал на первой частоте. Приемник содержит по меньшей мере один обрабатывающий блок. Обрабатывающий блок содержит множество цифровых полосовых фильтров, разделяющих сигнал и восстанавливающих сигнал на частоте, меньшей первой частоты. Обрабатывающий блок содержит цифровой понижающий преобразователь, регулирующий частотный сдвиг или центрирующий сигнал на частоте, меньшей первой частоты. Приемник содержит по меньшей мере одно буферное управляющее устройство для управления частотой, соединенное с соседними обрабатывающими блоками при размещении в приемнике по меньшей мере двух обрабатывающих блоков. 3 н. и 11 з.п. ф-лы, 9 ил.

1. Приемник (100), преобразующий радиочастотный сигнал в цифровую форму и содержащий:

модулятор (104), дискретизирующий сигнал на первой частоте;

по меньшей мере два обрабатывающих блока (110), каждый из которых содержит:

множество цифровых полосовых фильтров (120), разделяющих сигнал и восстанавливающих его на частоте, меньшей первой частоты;

цифровой понижающий преобразователь (108), регулирующий частотный сдвиг или центрирующий сигнал на частоте, меньшей первой частоты; и

по меньшей мере одно буферное управляющее устройство для управления частотой, соединенное с соседними обрабатывающими блоками (110).

2. Приемник (100) по п. 1, содержащий управляющее устройство (140), конфигурирующее соединения по меньшей мере между одним обрабатывающим блоком (110) и по меньшей мере одним буферным управляющим устройством для управления частотой.

3. Приемник (100) по п. 1 или 2, дополнительно содержащий усилитель (102) для приема и усиления сигнала до приема сигнала модулятором (104).

4. Приемник (100) по п. 1 или 2, в котором модулятор (104) представляет собой полосовой дельта-сигма аналого-цифровой преобразователь с непрерывным преобразованием.

5. Приемник (100) по п. 1 или 2, в котором множество цифровых полосовых фильтров (120) в каждом обрабатывающем блоке (110) выполнены в виде цифрового многофазного фильтра (106).

6. Приемник (100) по п. 1 или 2, в котором множество цифровых полосовых фильтров (120) в каждом обрабатывающем блоке (110) всего содержит М субфильтров с характеристиками конечной длительности, каждый из которых функционирует на частоте, меньшей первой частоты,

причем значение М представляет собой отношение первой частоты к частоте обработки текущего обрабатывающего блока (110) при размещении текущего обрабатывающего блока (110) рядом с модулятором (104) или отношение частоты обработки предыдущего обрабатывающего блока (110) к частоте обработки текущего обрабатывающего блока (110).

7. Приемник (100) по п. 6, в котором входные сигналы на М субфильтров с характеристиками конечной длительности в каждом обрабатывающем блоке (110) поданы путем мультиплексирования по времени выходных сигналов модулятора (104) при размещении текущего обрабатывающего блока (110) рядом с модулятором (104) или мультиплексирования по времени выходных сигналов предыдущего обрабатывающего блока (110).

8. Приемник (100) по любому из пп. 1-2, 7, в котором модулятор (104) выполнен с возможностью обработки сигнала на первой частоте, которая больше несущей частоты, а множество цифровых полосовых фильтров (120) и цифровые понижающие преобразователи в каждом обрабатывающем блоке (110) выполнены с возможностью обработки сигнала на частоте, большей или равной частоте Найквиста в полосе пропускания сигнала, но меньшей несущей частоты.

9. Приемник по любому из пп. 1-2, 7, в котором цифровой преобразователь с понижением частоты в каждом обрабатывающем блоке (110) выполнен с возможностью функционирования и создания выходных сигналов для обрабатывающего блока (110) на частоте, идентичной частоте М субфильтров с характеристиками конечной длительности в идентичном обрабатывающем блоке (110).

10. Приемник по любому из пп. 1-2, 7, в котором цифровой преобразователь (108) с понижением частоты в каждом обрабатывающем блоке (110) центрирует сигнал на нулевой частоте при условии, что обрабатывающий блок (110) последним создает окончательные выходные сигналы, или корректирует частотный сдвиг до необходимой промежуточной частоты.

11. Способ уменьшения энергопотребления на приемнике (100), преобразующем радиочастотный сигнал в цифровую форму, включающий:

прием сигнала;

фильтрацию сигнала;

дискретизацию сигнала на первой частоте;

выполнение по меньшей мере в одном обрабатывающем блоке (110):

разделения сигнала на субполосы (120) на частоте обработки, меньшей первой частоты;

восстановления сигнала из субполос (120) на частоте обработки; и

корректирования частотного сдвига или центрирования сигнала на частоте обработки,

причем способ дополнительно включает конфигурирование каждого обрабатывающего блока (110) путем регулирования множества цифровых полосовых фильтров (120) и цифрового понижающего преобразователя (108) в обрабатывающем блоке (110) посредством управляющего устройства (140) или обхода множества цифровых полосовых фильтров (120) и цифрового преобразователя (108) с понижением частоты в обрабатывающем блоке (110) посредством управляющего устройства (140).

12. Способ по п. 11, включающий обход цифрового понижающего преобразователя (108) в обрабатывающем блоке (110) путем регулирования первой частоты в качестве частоты, кратной частоте обработки текущего обрабатывающего блока (110), и регулирования несущей частоты в качестве частоты, кратной частоте обработки текущего обрабатывающего блока (110), при соединении текущего обрабатывающего блока (110) с модулятором (104) или путем регулирования частоты обработки предыдущего обрабатывающего блока (110) в качестве частоты, кратной частоте обработки текущего обрабатывающего блока (110), и регулирования промежуточной частоты в качестве частоты, кратной частоте обработки текущего обрабатывающего блока (110).

13. Способ по п. 11, в котором разделение сигнала включает временное мультиплексирование дискретизированного сигнала в каждой субполосе (120) при соединении текущего обрабатывающего блока (110) с модулятором (104) или временное мультиплексирование выходных сигналов предыдущего обрабатывающего блока (110) в каждой субполосе (120) в текущем обрабатывающем блоке (110).

14. Система для уменьшения энергопотребления, содержащая приемник по любому из пп. 1-10 и/или выполненная с возможностью выполнения способа по любому из пп. 11-13.

| ЦИФРОВОЙ МНОГОЧАСТОТНЫЙ ПРИЕМОПЕРЕДАТЧИК | 2002 |

|

RU2292658C2 |

| US 2004192229 A1, 30.09.2004 | |||

| US 2004190660 A1, 30.09.2004 | |||

| US 2006222116 A1, 05.10.2006 | |||

| US 2008159453 A1, 03.07.2008. | |||

Авторы

Даты

2017-03-22—Публикация

2012-09-13—Подача