Предлагаемое устройство служит для построения программируемых контроллеров и систем логико-программного управления и регулирования технологическими объектами в различных отраслях производства и на транспорте, а также средством решения логических задач.

Известно устройство содержащее входной блок, принимающий сигналы от датчиков и формирующий определенный двоичный код на своем выходе, выходной блок для записи и хранении полученных результатов, поступающих из многоканального операционного и коммутационно-вычислительного блоков, программный блок, где хранится программа работы устройства, блок оперативной памяти для хранения промежуточных результатов вычислений, блок синхронизации, блок ускоренного переноса (1).

Недостатком данного устройства является функциональная ограниченность, относительно невысокое быстродействие из-за относительно большого количества необходимых тактов при поразрядном вычислении логических функций И и ИЛИ, сложность блока ускоренного переноса при вычислении арифметических функций, отсутствие ускоренной реакции на появление аварийного сигнала, например из объекта управления.

Наиболее технически близким является устройство содержащее входной блок, принимающий сигналы от датчиков и формирующий определенный код на своем выходе, выходной блок для хранения полученных результатов, поступающих из многоканального операционного и коммутационно-вычислительного блоков, программный блок, где хранится программа работы устройства, блок оперативной памяти для хранения промежуточных результатов вычислений, блок синхронизации, логические каналы с функционально изменяемыми триггерами. (2).

Недостатком данного устройства является относительно сложная структура многоканального операционного блока и входящих в него логических каналов, функциональная ограниченность из-за невозможности реализации операций с использованием многоразрядных и одноразрядных кодов на одних и тех же тактах работы устройства при изменении порядка выполнения программы в зависимости от значений промежуточных результатов вычислений, отсутствие быстрой реакции при появлении аварийного сигнала.

Ставится задача создания нового изобретения с целью упрощения устройства, расширения его функциональных возможностей и повышения быстродействия в определенных условиях по сравнению с прототипом.

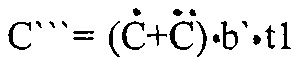

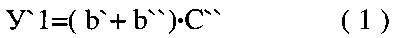

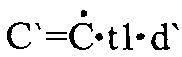

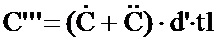

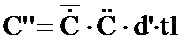

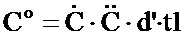

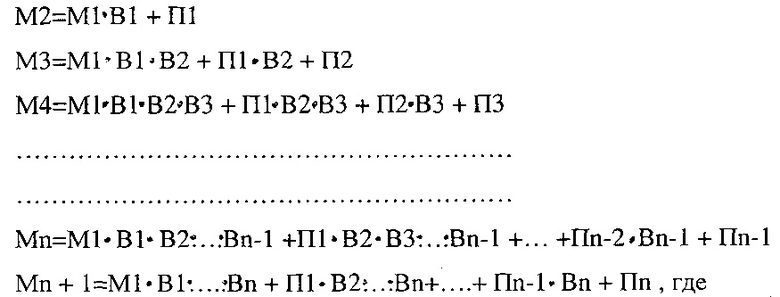

Для решения этой задачи в устройство для построения программируемых цифровых микропроцессорных систем, содержащее в себе входной блок, принимающий сигналы от датчиков и формирующий определенный код на своем выходе, выходной блок для записи значений кодов, поступающих из всех логических каналов в ячейки памяти, и передачи их через цифроаналоговые преобразователи на электронные устройства и электроприводные механизмы, программный блок, блок оперативной памяти, блок синхронизации и коммутационно-вычислительный блок, состоящий из элемента И-ИЛИ, элемента и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четырех элементов И, счетного триггера, дешифратора, подключенного входами к выходам программного блока, первые входы двух первых И элемента И-ИЛИ соединены с третьим и четвертым выходами дешифратора, а вторые входы подключены к выходу входного блока, соединенного первой и второй группами входов с группой информационных выходов объекта управления и с группой адресных выходов программного блока, а также к выходу блока оперативной памяти, выход элемента И-ИЛИ подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с определенным выходом программного блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ связан с первым входом третьего элемента И, соединенного вторым входом с соответствующим выходом блока синхронизации, а выходом с счетным входом счетного триггера, входы четвертого элемента И подключены к выходу программного блока и к соответствующему выходу блока синхронизации, а выход связан с входом установки счетного триггера в «1», выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ связан с информационными входами выходного блока и блока оперативной памяти, первые входы первого и второго элементов И подключены к первому и второму выходам дешифратора, их вторые входы объединены и связаны с выходами блока синхронизации, а выходы соединены с входами выходного блока и блока оперативной памяти для управления записью информации, многоканальный операционный блок, содержащий управляемый элемент, второй, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, первый и с третьего по восьмой элементы ИЛИ, первый и второй дешифраторы, соединенные своими входами с соответствующими выходами программного блока, управляемую ячейку памяти, управляемый триггер, электронный выключатель, элемент НЕ, элемент и первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и «n» параллельно работающих логических каналов, имеющих одинаковую структуру и каждый из которых содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, три элемента И, элемент ИЛИ, два счетных триггера, модули сдвига разрядов, при этом в каждом логическом канале многоканального операционного блока выход логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ связан с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выход элемента ИЛИ соединен с первым входом третьего элемента И, выход последнего связан со счетным входом первого счетного триггера, выход которого подключен к счетному входу второго счетного триггера, при этом в многоканальном операционном блоке выход первого элемента ИЛИ связан с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ логических каналов, первый и второй входы первого элемента ИЛИ связаны соответственно с выходами второго дешифратора и седьмого элемента И, причем два входа первого элемента И подключены к одному из выходов второго дешифратора и выходу третьего элемента ИЛИ, входы которого соединены с двумя соответствующими выходами первого дешифратора, первый и второй входы второго элемента И связаны с одним из выходов блока синхронизации и с определенным выходом первого дешифратора, а выход соединен с управляющим входом управляемого триггера, вход элемента НЕ связан с выходом третьего элемента ИЛИ, первый вход седьмого элемента И подключен к соответствующему выходу второго дешифратора, выход элемента НЕ также связан с третьим входом модуля ЛМ, вторые входы шестого и седьмого элементов И связаны соответственно с прямым и инверсным выходами управляемой ячейки памяти, информационный вход которой соединен с выходом второго элемента ИЛИ дискретного модуля ДМ, содержащего первый и второй элементы И, элемент НЕ, первый и второй элементы ИЛИ, причем входы первого элемента ИЛИ соединены с выходами первых счетных триггеров предпоследнего и последнего каналов, входы второго элемента И соединены с выходом первого элемента ИЛИ и с соответствующим выходом программного блока, который также подключен к входу элемента НЕ, выход последнего соединен с входом первого элемента И, другой вход которого связан с одним из выходов блока БУП, а выход подключен к первому входу второго элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, управляющий вход управляемой ячейки памяти связан с выходом четвертого элемента И, в многоканальном операционном блоке, информационный вход управляемого триггера связан с прямым выходом управляемой ячейки памяти, инверсный выход управляемого триггера подключен через одну из общих шин системы связи к выходному блоку, управляющие входы управляемого элемента соединены с тремя определенными командными шинами программного блока и одной из них с первым входом пятого элемента ИЛИ, выход последнего подключен к первому входу девятого элемента И, в коммутационно-вычислительном блоке первые входы третьего и четвертого элементов И, элемента И-ИЛИ подключены к соответствующим двум выходам первого дешифратора, а вторые входы связаны с выходом управляемого элемента многоканального операционного блока и с определенным выходом блока ускоренного переноса БУП, входы первого и второго дешифраторов многоканального операционного блока подключены к соответствующим командным шинам программного блока, определенные выходы блока БУП соединены с вторыми входами второго элемента И всех логических каналов, кроме первого, второй вход второго элемента И первого логического канала подключен вместе с соответствующим входом блока БУП к выходу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ многоканального операционного блока, где второй вход девятого элемента И связан с выходом третьего элемента ИЛИ, входы восьмого элемента И соединены с выходами блока синхронизации и шестого элемента ИЛИ, а выход связан с первым входом четвертого элемента ИЛИ, выход которого подключен к входам сброса в «О» вторых счетных триггеров всех логических каналов, входы пятого элемента И соединены с определенной командной шиной программного блока и соответствующим выходом блока синхронизации, а выход связан с вторым входом четвертого элемента ИЛИ и с входами сброса в «О» первых счетных триггеров всех логических каналов, систему связи, содержащую общие шины, первый и второй электронные ключи, логический элемент, формирующий сигналы на своих выходах аналогично первым четырем выходам первого дешифратора многоканального операционного блока, логический модуль ЛМ, структура которого и его функционирование определяются логическими функциями  ,

,  ,

,  ,

,  , где

, где  и

и  являются входами логического модуля ЛМ и связаны с соответствующими командными шинами программного блока, t1 поступает с выхода элемента НЕ блока 7,

являются входами логического модуля ЛМ и связаны с соответствующими командными шинами программного блока, t1 поступает с выхода элемента НЕ блока 7,  подключен к выходу шестого элемента И коммутационно-вычислительного блока, а

подключен к выходу шестого элемента И коммутационно-вычислительного блока, а  ,

,  ,

,  ,

,  это выходы логического модуля ЛМ и соединены выходом

это выходы логического модуля ЛМ и соединены выходом  с первым входом шестого элемента ИЛИ многоканального операционного блока, другими выходами с соответствующими входами модулей сдвига разрядов МСР в каждом логическом канале, причем модуль сдвига разрядов МСР1 находится во всех логических каналах, кроме первого и последнего, и реализует логические функции

с первым входом шестого элемента ИЛИ многоканального операционного блока, другими выходами с соответствующими входами модулей сдвига разрядов МСР в каждом логическом канале, причем модуль сдвига разрядов МСР1 находится во всех логических каналах, кроме первого и последнего, и реализует логические функции  ,

,  , где

, где  и

и  являются выходами модуля МСР1 и связаны с третьим и четвертым входами элемента ИЛИ данного и последующего логических каналов, переменные

являются выходами модуля МСР1 и связаны с третьим и четвертым входами элемента ИЛИ данного и последующего логических каналов, переменные  ,

,  ,

,  ,

,  являются входными сигналами для МСР1, причем

являются входными сигналами для МСР1, причем  ,

,  поступают с выходов первых счетных триггеров данного и последующего логических каналов,

поступают с выходов первых счетных триггеров данного и последующего логических каналов,  , и

, и  поступают с выходов логического модуля ЛМ, модуль МСР2 в первом логическом канале реализует логические функции

поступают с выходов логического модуля ЛМ, модуль МСР2 в первом логическом канале реализует логические функции

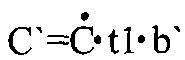

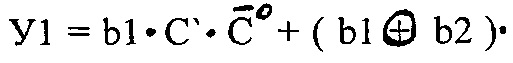

,

,  и

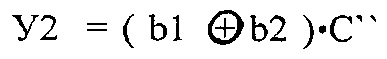

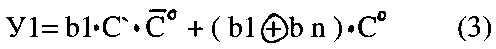

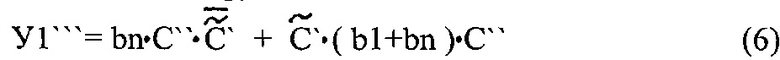

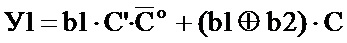

и  , где У1, У2 и У3 служат выходами модуля МСР2 и связаны с третьим и четвертым входами элемента ИЛИ первого логического канала и с четвертым входом первого элемента ИЛИ второго логического канала, а b1, b2,

, где У1, У2 и У3 служат выходами модуля МСР2 и связаны с третьим и четвертым входами элемента ИЛИ первого логического канала и с четвертым входом первого элемента ИЛИ второго логического канала, а b1, b2,  ,

,  ,

,  являются входами модуля МСР2 и соединены с выходами первых счетных триггеров первого и второго логических каналов, с тремя выходами логического модуля ЛМ, модуль МСР3 вычисляет логическую функцию

являются входами модуля МСР2 и соединены с выходами первых счетных триггеров первого и второго логических каналов, с тремя выходами логического модуля ЛМ, модуль МСР3 вычисляет логическую функцию  , где сигнал

, где сигнал  поступает с выхода модуля МСР3 на третий вход первого элемента ИЛИ последнего логического канала, сигналы b1, bn,

поступает с выхода модуля МСР3 на третий вход первого элемента ИЛИ последнего логического канала, сигналы b1, bn,  ,

,  поступают на входы модуля МСР3 соответственно с выходов первых счетных триггеров первого и последнего логических каналов, с выхода логического модуля ЛМ и определенного выхода программного блока, в многоканальном операционном блоке, где первый вход четвертого элемента И связан с определенной командной шиной программного блока, второй вход соединен с соответствующим выходом блока синхронизации, а третий вход подключен к выходу первого элемента НЕ, управляющий вход электронного выключателя связан с выходом седьмого элемента ИЛИ, входы которого подключены к двум соответствующим выходам первого дешифратора, выход девятого элемента И соединен с первыми входами первых элементов И в каждом логическом канале, вторые входы первых элементов И каждого логического канала вместе с информационными выходами электронного выключателя многоканального операционного блока связаны с общими шинами системы связи, а выходы первых элементов И в каждом логическом канале соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, общие шины также подключены к выходам первого и второго электронных ключей системы связи и к соответствующим входам блока оперативной памяти и выходного блока, входы первого и второго электронных ключей связаны с определенными выходами входного блока и блока оперативной памяти, управляющие входы первого и второго электронных ключей, блока оперативной памяти и выходного блока соединены с соответствующими выходами логического элемента системы связи, три входа которого объединены с соответствующими тремя входами первого дешифратора многоканального операционного блока и с тремя выходами программного блока, второй вход элемента И счетчика импульсов связан с соответствующим выходом блока синхронизации, а выход подключен к управляющему входу электронного ключа счетчика импульсов блока программ, прямые выходы всех первых счетных триггеров связаны с определенными входами модулей сдвига разрядов МСР1, МСР2 и МСР3 в соответствующих логических каналах, восьмой элемент ИЛИ первым и вторым входами связан с вторым и третьим выходами второго дешифратора, а выходом соединен с первым входом шестого элемента И, входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к определенной командной шине и к первой Т1 шине из числа общих шин системы связи, а выход связан с вторым входом пятого элемента ИЛИ, имеется «n» одинаковых схемных фрагментов Ф1…Фn по числу логических каналов, каждый схемный фрагмент связан с соответствующим логическим каналом и содержит два логических элемента ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый, второй и третий входы элемента ИЛИ связаны с выходом первого элемента ИЛИ многоканального операционного блока, с вторым входом второго элемента И соответствующего логического канала и с соответствующим выходом дешифратора коммутационно-вычислительного блока, а выход соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу первого счетного триггера соответствующего логического канала, а выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходами соответствующих схемных фрагментов и соединены с информационными входами электронного выключателя и управляемого элемента многоканального операционного блока, где первый и второй входы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом шестого элемента И и с выходом программного блока, а второй управляющий вход управляемого элемента связан с выходом программного блока и с входом дискретного модуля ДМ, дополнительно введен блок триггеров БТ, подключенных информационными входами к информационным данным Т1…Tn, поступающим из общих шин, а входами управления к выходу элемента И, соединенного входами с определенным выходом программного блока и соответствующим выходом блока синхронизации, а выходами с адресными входами стандартного перепрограммируемого постоянного запоминающего устройства ППЗУ, который информационными выходами связан с входами электронного ключа программного блока, в коммутационно - вычислительном блоке введены элемент И-НЕ, второй счетный триггер, пятый, шестой, седьмой, восьмой и девятый элементы И, элемент ИЛИ и первый элемент ИЛИ, причем входы девятого элемента И связаны с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с определенным выходом программного блок, а выход подключен к входу первого элемента ИЛИ, счетный вход второго счетного триггера соединен с выходом восьмого элемента И, вход сброса в нуль связан с выходом седьмого элемента И, входы пятого элемента И подключены к выходам дешифратора и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы элемента ИЛИ соединены с определенным выходом программного блока и с шиной Ст передачи аварийного сигнала с объекта управления, а выход подключен к блокировочному входу дешифратора, входы шестого элемента И связаны с выходом второго счетного триггера и с выходом элемента ИЛИ, а выход соединен с модулем ЛМ, с соответствующим входом четвертого элемента И, с блокировочными входами первого и второго дешифраторов и с соответствующим входом десятого элемента И многоканального операционного блока, а также к блокировочному входу дешифратора системы связи устройства, входы восьмого элемента И подключены к выходу блока синхронизации и к выходу первого элемента ИЛИ, входы которого соединены с выходом программного блока и с выходом пятого элемента И, выход элемента И-НЕ подключен к третьему входу третьего элемента И, а входы элемента И-НЕ соединены с соответствующим выходом программного блока и с инверсным выходом счетного триггера, вход сброса в '1' которого связан с выходом четвертого элемента И, второй вход введенного десятого элемента И в многоканальном операционном блоке соединен с определенным выходом программного блока, а выход связан с вторым входом шестого элемента ИЛИ и с первыми входами вторых элементов И всех логических каналов, в каждый из них введен логический элемент И-НЕ, своими входами подключенный к выходам первого счетного триггера и третьего элемента ИЛИ многоканального операционного блока, а также к выходу программного блока, а выходом соединенного с третьим входом третьего элемента И в каждом логическом канале, блок ускоренного переноса БУП имеет новую структуру, с соответствующими логическими функциями.

поступают на входы модуля МСР3 соответственно с выходов первых счетных триггеров первого и последнего логических каналов, с выхода логического модуля ЛМ и определенного выхода программного блока, в многоканальном операционном блоке, где первый вход четвертого элемента И связан с определенной командной шиной программного блока, второй вход соединен с соответствующим выходом блока синхронизации, а третий вход подключен к выходу первого элемента НЕ, управляющий вход электронного выключателя связан с выходом седьмого элемента ИЛИ, входы которого подключены к двум соответствующим выходам первого дешифратора, выход девятого элемента И соединен с первыми входами первых элементов И в каждом логическом канале, вторые входы первых элементов И каждого логического канала вместе с информационными выходами электронного выключателя многоканального операционного блока связаны с общими шинами системы связи, а выходы первых элементов И в каждом логическом канале соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, общие шины также подключены к выходам первого и второго электронных ключей системы связи и к соответствующим входам блока оперативной памяти и выходного блока, входы первого и второго электронных ключей связаны с определенными выходами входного блока и блока оперативной памяти, управляющие входы первого и второго электронных ключей, блока оперативной памяти и выходного блока соединены с соответствующими выходами логического элемента системы связи, три входа которого объединены с соответствующими тремя входами первого дешифратора многоканального операционного блока и с тремя выходами программного блока, второй вход элемента И счетчика импульсов связан с соответствующим выходом блока синхронизации, а выход подключен к управляющему входу электронного ключа счетчика импульсов блока программ, прямые выходы всех первых счетных триггеров связаны с определенными входами модулей сдвига разрядов МСР1, МСР2 и МСР3 в соответствующих логических каналах, восьмой элемент ИЛИ первым и вторым входами связан с вторым и третьим выходами второго дешифратора, а выходом соединен с первым входом шестого элемента И, входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к определенной командной шине и к первой Т1 шине из числа общих шин системы связи, а выход связан с вторым входом пятого элемента ИЛИ, имеется «n» одинаковых схемных фрагментов Ф1…Фn по числу логических каналов, каждый схемный фрагмент связан с соответствующим логическим каналом и содержит два логических элемента ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый, второй и третий входы элемента ИЛИ связаны с выходом первого элемента ИЛИ многоканального операционного блока, с вторым входом второго элемента И соответствующего логического канала и с соответствующим выходом дешифратора коммутационно-вычислительного блока, а выход соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу первого счетного триггера соответствующего логического канала, а выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходами соответствующих схемных фрагментов и соединены с информационными входами электронного выключателя и управляемого элемента многоканального операционного блока, где первый и второй входы первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом шестого элемента И и с выходом программного блока, а второй управляющий вход управляемого элемента связан с выходом программного блока и с входом дискретного модуля ДМ, дополнительно введен блок триггеров БТ, подключенных информационными входами к информационным данным Т1…Tn, поступающим из общих шин, а входами управления к выходу элемента И, соединенного входами с определенным выходом программного блока и соответствующим выходом блока синхронизации, а выходами с адресными входами стандартного перепрограммируемого постоянного запоминающего устройства ППЗУ, который информационными выходами связан с входами электронного ключа программного блока, в коммутационно - вычислительном блоке введены элемент И-НЕ, второй счетный триггер, пятый, шестой, седьмой, восьмой и девятый элементы И, элемент ИЛИ и первый элемент ИЛИ, причем входы девятого элемента И связаны с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с определенным выходом программного блок, а выход подключен к входу первого элемента ИЛИ, счетный вход второго счетного триггера соединен с выходом восьмого элемента И, вход сброса в нуль связан с выходом седьмого элемента И, входы пятого элемента И подключены к выходам дешифратора и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, входы элемента ИЛИ соединены с определенным выходом программного блока и с шиной Ст передачи аварийного сигнала с объекта управления, а выход подключен к блокировочному входу дешифратора, входы шестого элемента И связаны с выходом второго счетного триггера и с выходом элемента ИЛИ, а выход соединен с модулем ЛМ, с соответствующим входом четвертого элемента И, с блокировочными входами первого и второго дешифраторов и с соответствующим входом десятого элемента И многоканального операционного блока, а также к блокировочному входу дешифратора системы связи устройства, входы восьмого элемента И подключены к выходу блока синхронизации и к выходу первого элемента ИЛИ, входы которого соединены с выходом программного блока и с выходом пятого элемента И, выход элемента И-НЕ подключен к третьему входу третьего элемента И, а входы элемента И-НЕ соединены с соответствующим выходом программного блока и с инверсным выходом счетного триггера, вход сброса в '1' которого связан с выходом четвертого элемента И, второй вход введенного десятого элемента И в многоканальном операционном блоке соединен с определенным выходом программного блока, а выход связан с вторым входом шестого элемента ИЛИ и с первыми входами вторых элементов И всех логических каналов, в каждый из них введен логический элемент И-НЕ, своими входами подключенный к выходам первого счетного триггера и третьего элемента ИЛИ многоканального операционного блока, а также к выходу программного блока, а выходом соединенного с третьим входом третьего элемента И в каждом логическом канале, блок ускоренного переноса БУП имеет новую структуру, с соответствующими логическими функциями.

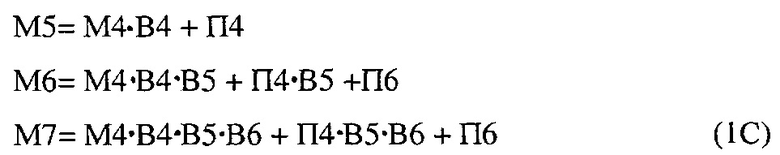

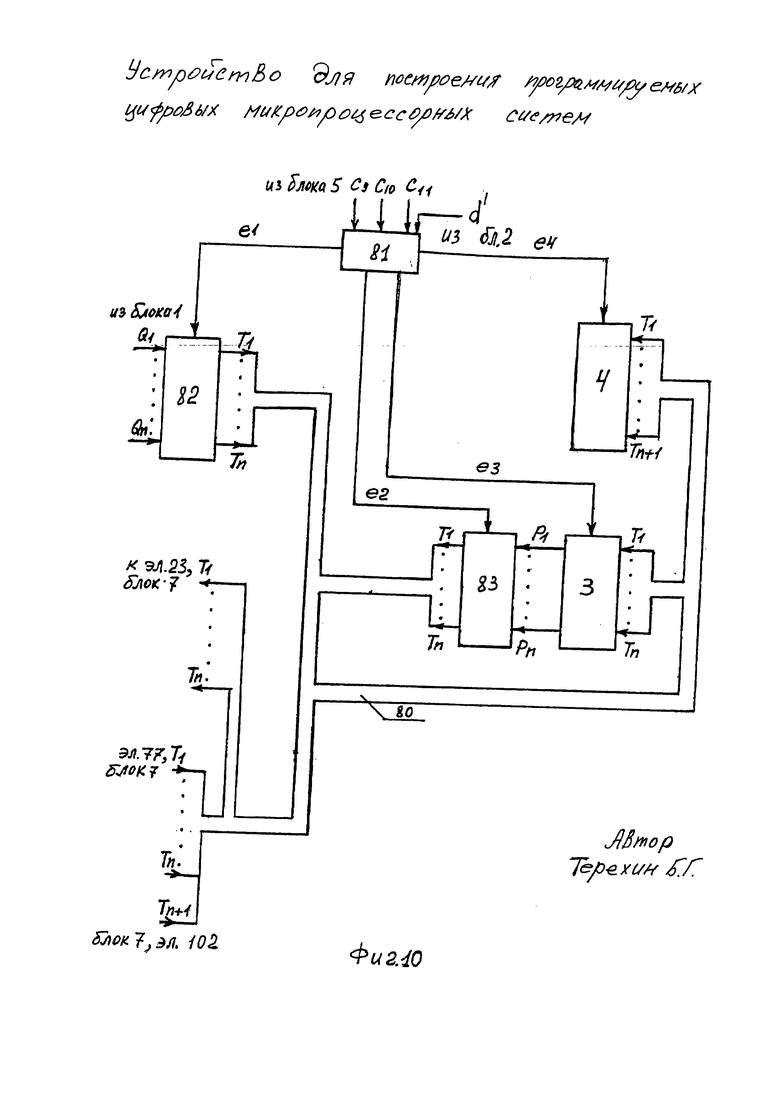

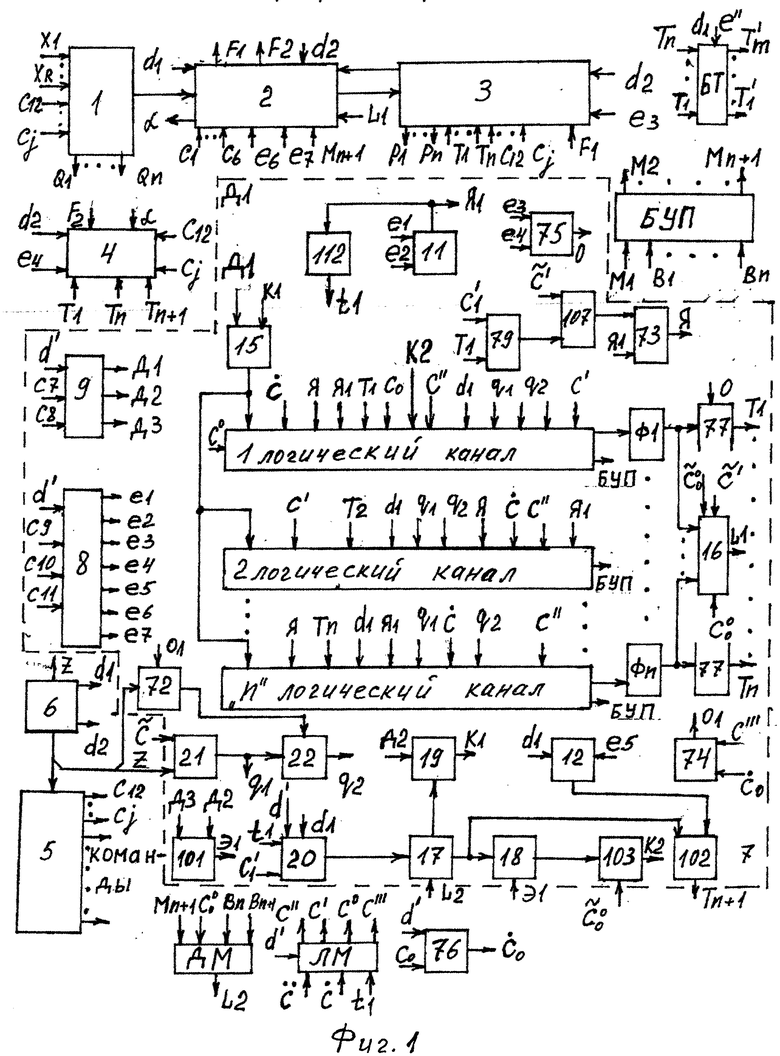

Устройство состоит из изображенных на фиг. 1 входного блока, одна группа входов которого подключена к дискретным датчикам и источникам двоичного кода (на схеме не показаны) X1…XR, a вторая группа входов соединена с адресными шинами С12…Cj, связанного с коммутационно-вычислительным блоком 2, подключенным к блоку оперативной памяти 3, выходному блоку 4, программному блоку 5, блоку синхронизации 6, многоканальному операционному блоку 7, содержащему «n» логических каналов, первый и второй дешифраторы 8 и 9, третий элемента ИЛИ 11, второй элемент И 12, связанный первым входом с определенным выходом блока синхронизации, первый элемента ИЛИ 15, выход которого связан с соответствующими входами всех логических каналов, управляемый элемент 16, управляемую ячейку памяти 17, шестой элемент И 18, седьмой элемент И 19, четвертый элемент И 20, пятый элемент И 21, четвертый элемент ИЛИ 22, девятый и десятый элементы И 73, И 76, шестой и седьмой элементы ИЛИ 74, ИЛИ 75, восьмой элемент И 72, соединенный одним входом с выходом Z элемента И63 блока 6, электронный выключатель 77, элемент и первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 79 и 103, восьмой элемент ИЛИ 101, управляемый триггер 102, пятый элемент ИЛИ 107, элемент НЕ 112 и изображенной на фиг. 10 системы связи, имеющей общие шины 80, логический элемент (дешифратор) 81, связанный четырьмя выходами e1, e2, e3 и е4 с управляющими входами первого 82 и второго 83 электронных ключей, а также с двумя соответствующими входами блока оперативно памяти и выходного блока, блока выбора программ 86, логического модуля ЛМ и дискретного модуля ДМ.

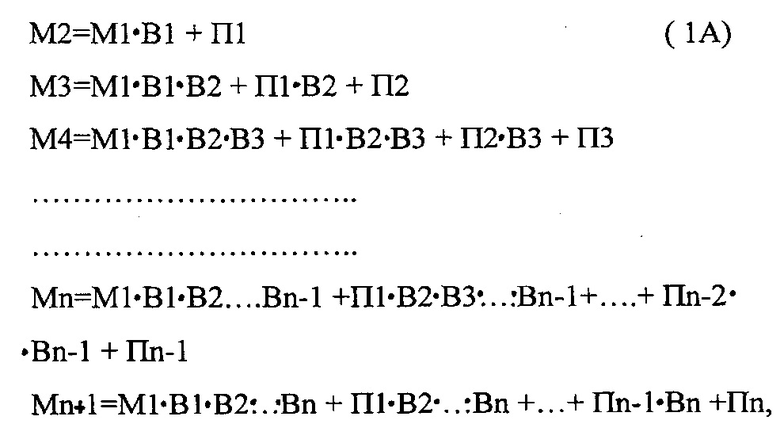

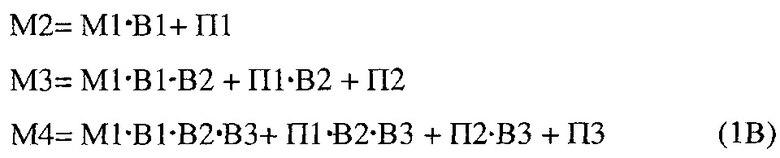

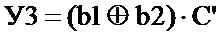

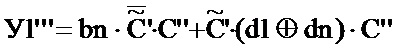

Блок ускоренного переноса имеет новую структуру определяемую нижеследующими логическими функциями:

где

где

M1 - сигнал с выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 103 многоканального операционного блока 7, поступающий на вход блока БУП;

М2…Mn - сигналы переноса, поступающие с определенных выходов блока БУП на соответствующие входы вторых элементов И27 всех логических каналов, кроме первого в блоке 7;

Mn+1 - сигнал переноса, поступающий с определенного выхода блока БУП на соответствующий вход модуля ДМ;

В1…Bn - сигналы с выходов первых счетных триггеров 29 соответствующих логических каналов блока 7, поступающие на соответствующие входы блока БУП;

П1…Пn - сигналы с выходов всех вторых счетных триггеров 30 логических каналов блока 7, поступающие на входы блока БУП. Знаки «точка» и «плюс» во всех функциях означают соответственно операции И и ИЛИ.

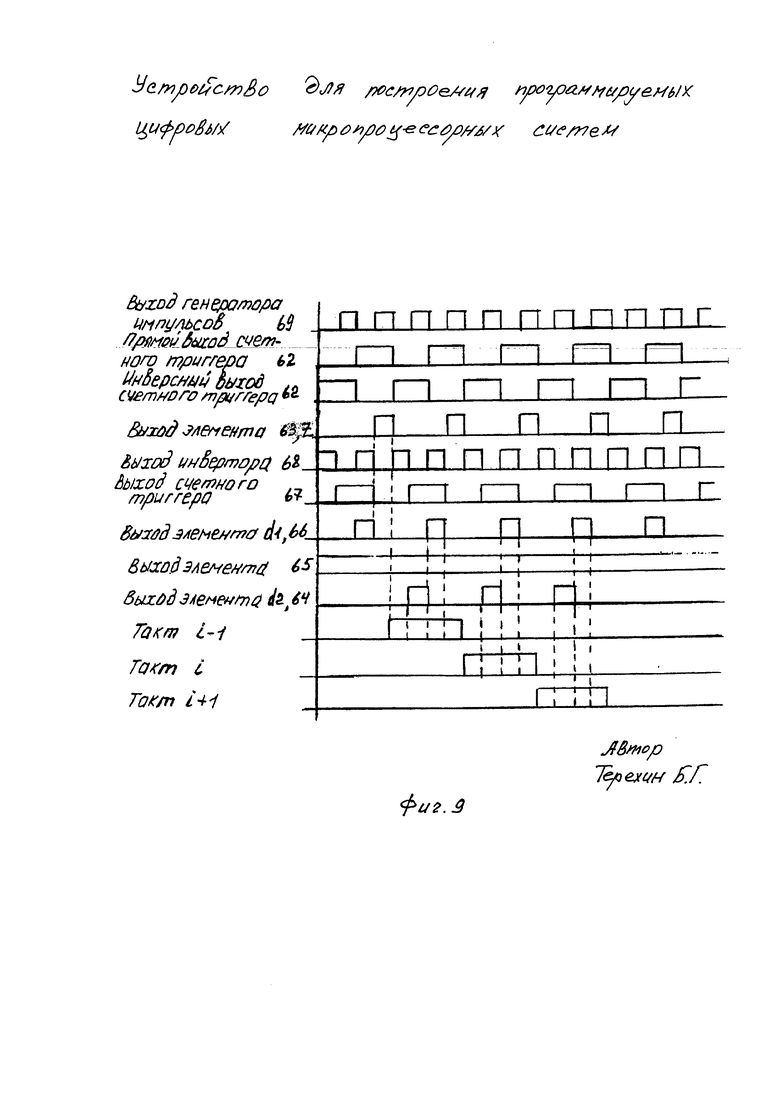

Устройства работает по тактам, сформированным в блоке синхронизации 6, каждый такт поделен на четыре импульса по одной четверти такта, все триггеры меняют свое состояние по одному из этих импульсов, т.е. условно в первой, второй, третьей и четвертой четвертях такта (фиг. 9).

В блоке 7 выходы дешифраторов 8 и 9 обозначены соответственно e1…e7 и Д1…Д3. Значения сигналов (переменных) на входах С9, С10 и С11, и выходах e1, е2, е3, и е4 в дешифраторах 8 и 81 одинаковы, слова логический элемент И(ИЛИ, НЕ и т.д.) и элемент с аналогичными обозначениями одно и тоже. При необходимости, дешифратор 81, имея свободные выходы, может управляться командами  ,

,  и

и  , отдельными от команд С9, С10 и С11, при этом выходы дешифратора 81 могут служить сигналами подключения и других, не указанных в описании, блоков к общим шинам 80.

, отдельными от команд С9, С10 и С11, при этом выходы дешифратора 81 могут служить сигналами подключения и других, не указанных в описании, блоков к общим шинам 80.

Система связи, в наших примерах, служит для организации обмена информации между блоками 1, 3, 4 и 7. При активизации сигнала e1 ключ 82 пропускает значение кода Q1…Qn с выходов входного блока 1 на входы логических каналов в блоке 7 по общим шинам 80 в виде информационных донных Т1…Tn+1. В случае активизации выхода е2 ключ 83 пропускает по общим шинам 80 код Р1…Pn с выходов блока 3 в виде Т1…Tn на входы элементов И 23 всех логических каналов. При активизации е3, либо е4, в блоке 7 активизируется выход О элемента ИЛИ 75 и выключатель 77 пропускает значение кода В1…Bn с выходов логических каналов, через схемные фрагменты Ф1…Фn на общие шины 80 в виде информационных данных Т1…Tn на входа рядов ячеек памяти соответственно в блок 3, либо в блок 4.

Через С1…С11,  ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  ,

,  , Со,

, Со,  ,

,  , Ck, Сх обозначены командные шины (сигналы) на выходах программного блока 5, связанные с соответствующими входами блоков 2, 7, 86, модулями ЛМ и ДМ, управляемого элемента 16 и управляющие их работой.

, Ck, Сх обозначены командные шины (сигналы) на выходах программного блока 5, связанные с соответствующими входами блоков 2, 7, 86, модулями ЛМ и ДМ, управляемого элемента 16 и управляющие их работой.

Через C12…Cj обозначены адресные шины (команды), определяющие адреса источников и приемников информации в блоках 1, 3 и 4 и поступающие с выходов программного блока 5.

X1…Xn, …, Xm…Xk - многоразрядные двоичные коды (сигналы), поступающие например с выходов аналого-цифровых преобразователей, где левые разряды являются младшими.

Xk+1…Xr - входные дискретные сигналы от датчиков (кнопки, путевые выключатели и т.д.).

Т1…Tn+1 - информационные данные (сигналы) на входах и выходах соответствующих электронных ключей, выключателей, блоков, а также на общих шинах 80 системы связи (фиг. 10).

Входы блоков, логических каналов элементов и т.д. указаны входящими стрелками, а выходы - исходящими стрелками.

В закрытом состоянии все электронные ключи и выключатели имеют на выходах высокое сопротивление.

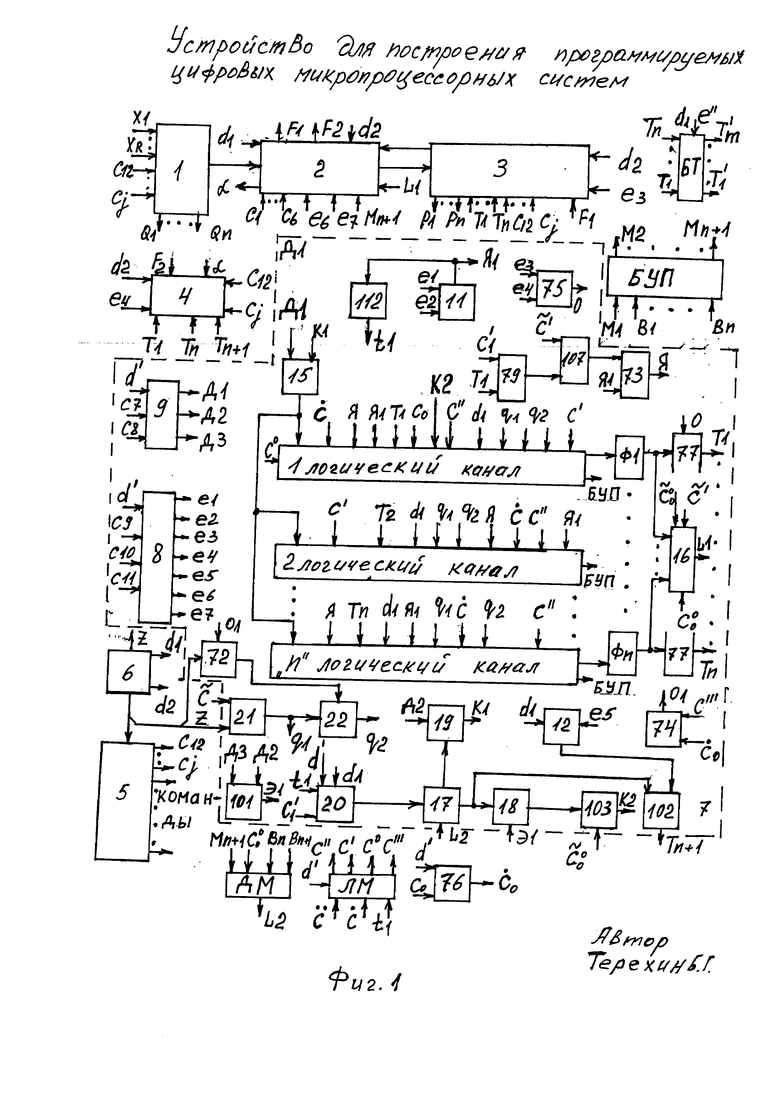

На фиг. 2 изображена структура логических каналов. Каждый из «n» каналов состоит из первого элемента И 23, связанного выходом с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24, выход которого соединен с первым входом первого элемента ИЛИ 25, выход этого элемента связан с входом третьего элемента И 28, выход которого подключен к счетному входу первого счетного триггера 29, выход которого связан с входом элемента И-НЕ 26 и со счетным входом второго счетного триггера 30, выходом соединенного с соответствующим входом блока ускоренного переноса БУП, модуля сдвига разрядов двоичного кода МСР2 для первого канала, модуля сдвига разрядов МСР3 для последнего канала и модулей сдвига разрядов МСР1 для остальных каналов, с соответствующими связями, второго элемента И27, связанного выходом с входом элемента ИЛИ25.

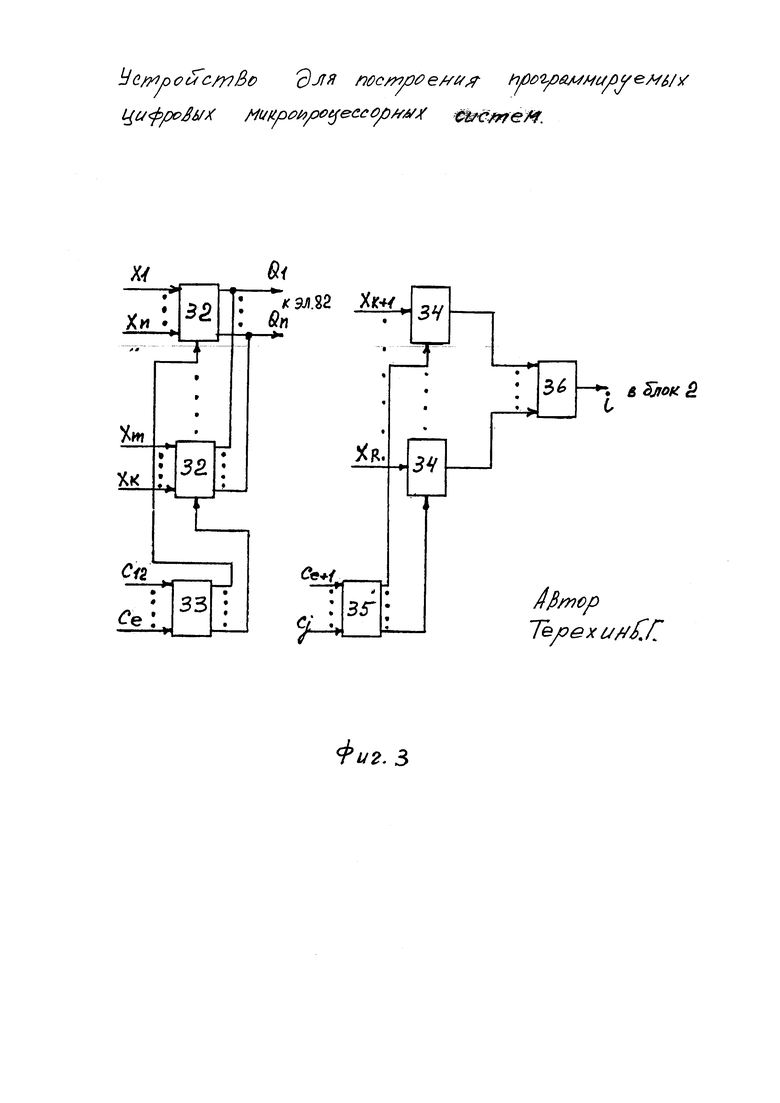

Пример входного блока 1 представлен на фиг. 3 и содержит ряд электронных ключей 32 на входы которых поступают разряды двоичных кодов X1…Xn, Xm…Xk и которые поочередно, по сигналу первого дешифратора 33, пропускают двоичный код на выходы Q1…Qn в зависимости от значений адресных команд С12…Се, элементы И 34 на первые входы которых поступают биты информационных сигналов Xk+1…Xr, вторые входы элементов И 34 подключены к выходам второго дешифратора 35 и в зависимости от значений адресных команд на соответствующих адресных шинах Се+1…Cj, при помощи активизации определенного выхода дешифратора 35, соответствующий бит информации появляется на выходе элемента ИЛИ 36, т.е. на выходе блока 1 для одно разрядных переменных.

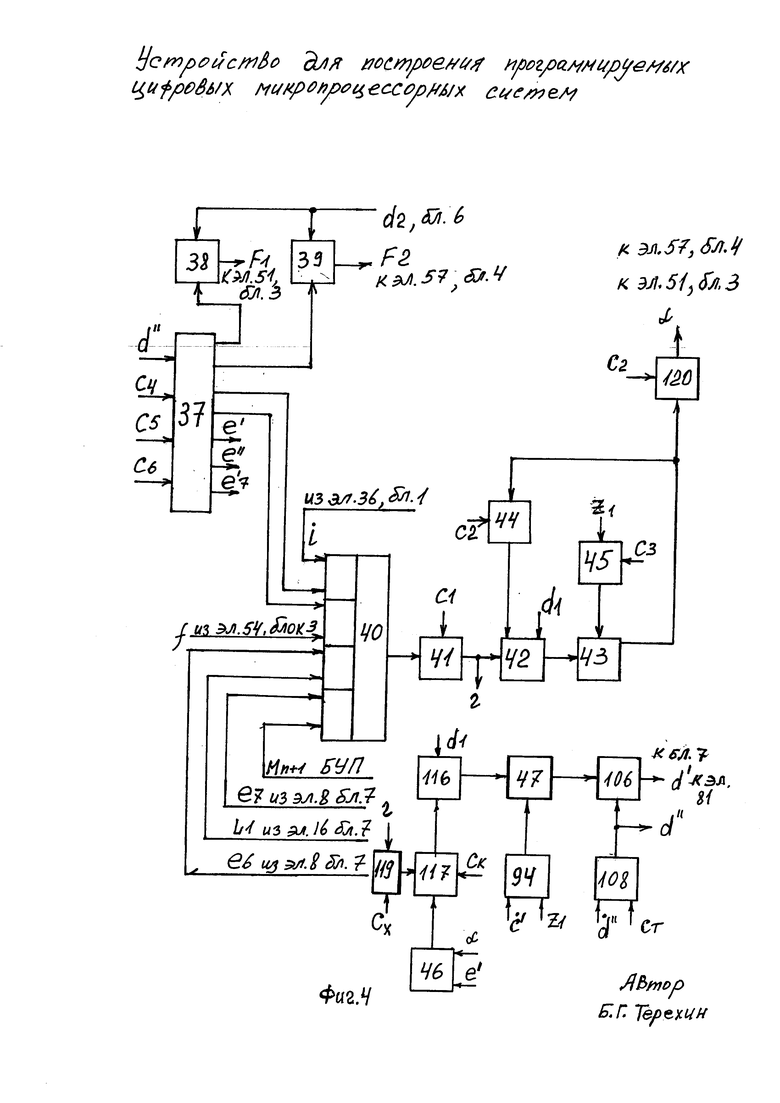

Пример коммутационно-вычислительного блока 2 представлен на фиг. 4, он состоит из дешифратора 37, подключенного входами к программному блоку 5, первыми двумя выходами дешифратор 37 соединен с первыми входами первого и второго элементов И38, И39, а третьим и четвертым выходами подключен к входам двух элементов И элемента И-ИЛИ (2-2-2-2И-4ИЛИ) 40, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41, второй вход которого подключен к выходу программного блока 5, а выход связан с первым входом девятого элемента И119 и с входом третьего элемента И42, подключенного выходом к счетному входу счетного триггера 43 с одним инверсным выходом, вход сброса в «1» которого соединен с выходом четвертого элемента И45, первый вход которого связан с выходом программного блока 5, а второй вход подключен к выходу пятого элемента И115 блока синхронизации 6, второй вход элемента И119 соединен с определенным выходом программного блока, а выход подключен к входу первого элемента ИЛИ117, входы второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 120 связаны с выходом счетного триггера и с выходом программного блока 5, а выходы соединены с информационными входами ячеек памяти 57 выходного блока 4 и с соответствующим входом элемента 51 блока 3, второй счетный триггера 47, счетный вход которого связан с выходом восьмого элемента И116, входы последнего подключены соответственно к выходу первого элемента ИЛИ117, к соответствующему выходу блока синхронизации 6, инверсный выход второго счетного триггера 47 соединен с первым входом шестого элемента И106, выход которого связан с блокирующими входами дешифраторов 8, 9, 81 и первым входом десятого элемента И76 блока 7, где второй вход элемента И76 связан с соответствующей командной шиной программного блока 5, а выход подключен к определенному входу элементов И27 всех логических каналов блока 7, в коммутационно-вычислительном блоке соответствующие входы первого и второго элементов И логического элемента И-ИЛИ(2-2-2-2И-4ИЛИ)40 соединены с выходом i элемента 36 блока 1 и с выходом f элемента 54 блока 3, а входы третьего и четвертого элементов И логического элемента 40 связаны соответственно с двумя выходами дешифратора 9, выходом логического элемента 16 блока 7 и определенным выходом блока БУП, вторые входы первого и второго элементов И38 и И39 объединены и связаны с выходом d2 элемента И64 блока 6, а выходы подключены к входу F1 элементов 51 блока 3 и к входам F2 элементов 57 блока 4, второй и третий входы третьего элемента И42 соединены соответственно с выходом первого элемента И66 блока бис выходом элемента И-НЕ44, первый и второй входы которого связаны с выходом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 120 и с командной шиной С2 программного блока 5, шестым выходом  дешифратор 37 соединен с первым входом элемента И111 блока триггеров БТ, второй вход элемента И111 подключен к определенному выходу блока синхронизации 6, второй вход элемента И106 вместе с блокирующим входом дешифратора 37 блока 2 соединен с выходом элемента ИЛИ 108 входы которого связаны с определенным выходом программного блока 5 и с аварийным сигналом Ст из объекта управления.

дешифратор 37 соединен с первым входом элемента И111 блока триггеров БТ, второй вход элемента И111 подключен к определенному выходу блока синхронизации 6, второй вход элемента И106 вместе с блокирующим входом дешифратора 37 блока 2 соединен с выходом элемента ИЛИ 108 входы которого связаны с определенным выходом программного блока 5 и с аварийным сигналом Ст из объекта управления.

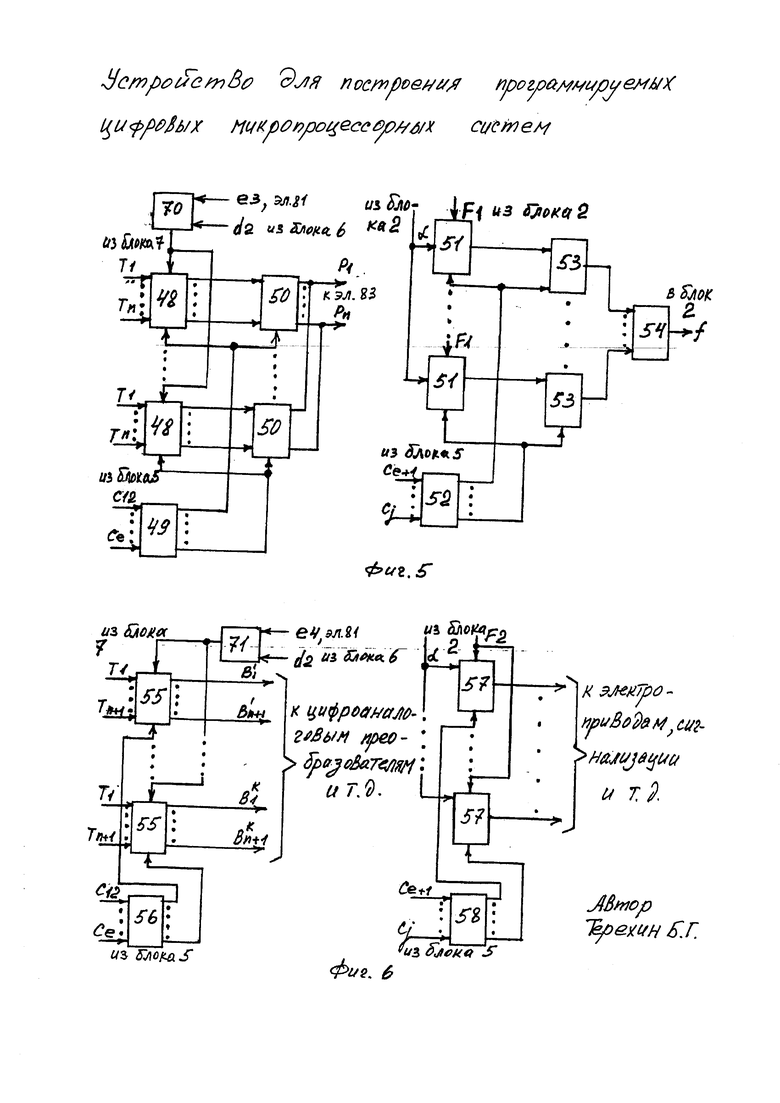

Пример блока оперативной памяти 3 представлен на фиг. 5 и содержит ряды ячеек памяти 48, в один из которых записывается информационный код (данные) Т1…Tn из общих шин 80 по команде е3 и импульсу d2, поступающих на входы первого элемента И 70 с выхода дешифратора 81 системы связи и блока 6, адрес ячеек памяти формируется на адресных шинах С12…Се и выходах дешифратора 49, Считывание двоичного кода с выхода одного из рядов ячеек памяти 48 осуществляется электронным ключом 50 по сигналам с выхода дешифратора 49, в зависимости от значений сигналов на адресных шинах С12…Се и по команде е2 считанный код поступает на общие шины 80, через ключ 83 системы связи, ряд однобитовых ячеек памяти 51 куда записываются результаты промежуточных вычислений булевых функций на выходе счетного триггера 43 по команде с выхода элемента И 38 блока 2 и в соответствии с сигналами на адресных шинах Се+1…Cj и выходах второго дешифратора 52, который определяет также ячейку памяти 51 откуда происходит считывание бита информации через элементы И 53 и ИЛИ 54, запись и считывание происходит на разных тактах работы устройства.

Пример структуры выходного блока 4 представлен на фиг. 6, он состоит из рядов ячеек памяти 55, куда записываются значения двоичных кодов Т1…Tn с общих шин 80, которые формируются на выходах логических каналов, через схемные фрагменты Ф1…Фn и выключатель 77 блока 7, по команде с выхода элемента И 71, на вход которого поступают сигналы е4 и d2 соответственно с выхода дешифратора 81 и из блока 6, адреса рядов ячеек памяти определяются сигналами на адресных шинах С12…Се, поступающих с выхода программного блока 5 и активизацией соответствующего выхода первого дешифратора 56, с выходов ячеек памяти 55 двоичный код может поступать, например, в информационные системы, цифро-аналоговые преобразователи и т.д., однобитовые ячейки памяти 57 служат для записи результатов вычисления булевых функций поступающих с выхода счетного триггера 43 блока 2 по команде с выхода элемента И 39 блока 2, адрес ячейки памяти 57 определяется сигналами на адресных шинах Се+1…Cj и активизацией соответствующего выхода дешифратора 58. Переменные с выходов ячеек памяти 57 могут поступать на электроприводы, сигнализацию и т.д.

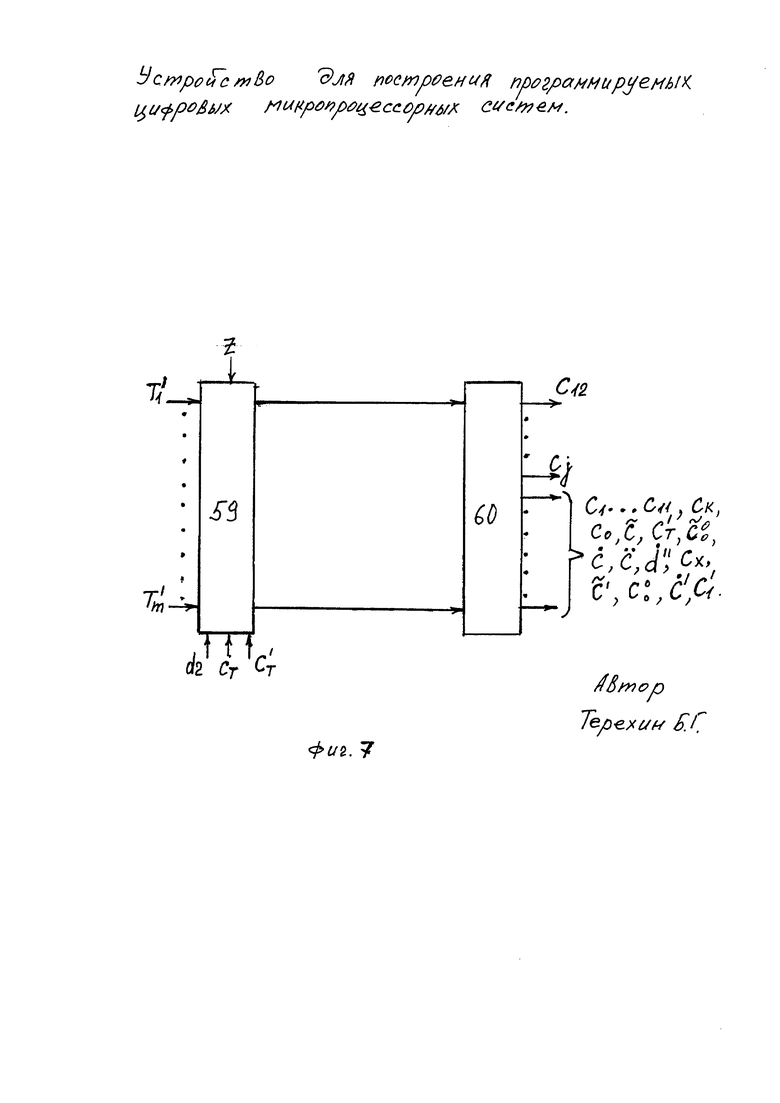

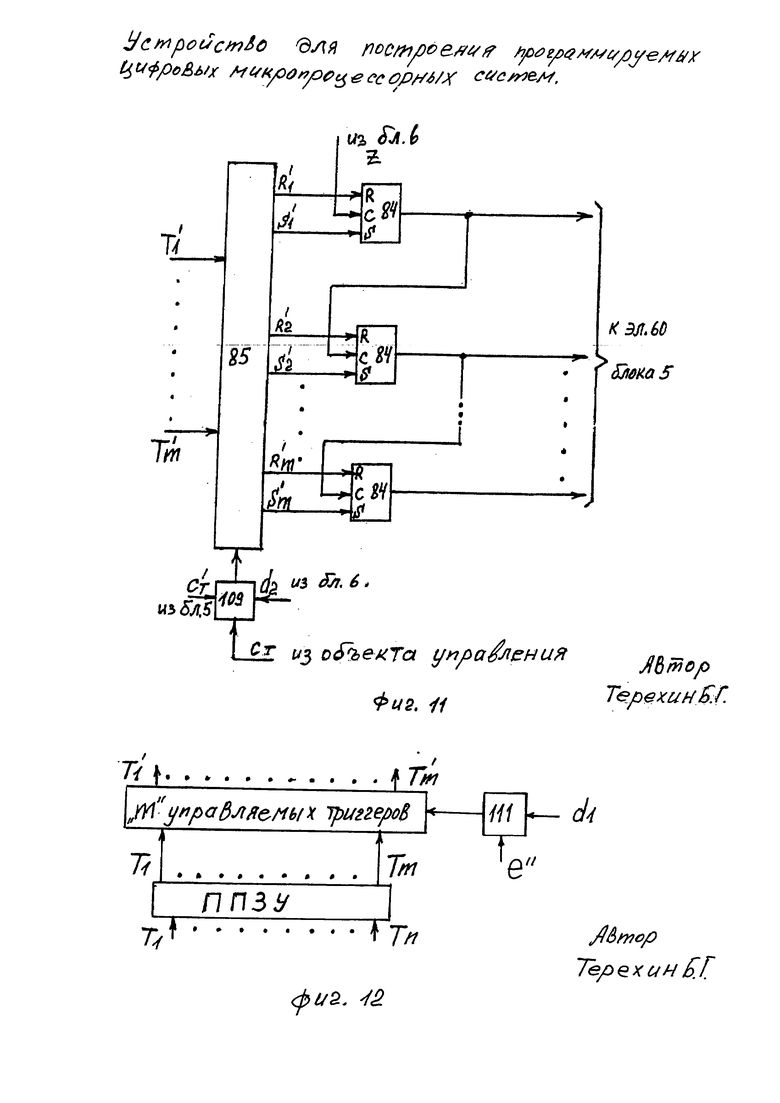

Пример схемы программного блока 5 представлен на фиг. 7, он содержит постоянное запоминающее устройство ПЗУ60, счетчик импульсов 59 (фиг. 11), имеющий элемент И 109, соединенный входами с определенной шиной программного блока 5, с шиной передачи аварийного сигнала и с выходом элемента И 64 блока 6, электронный ключ 85, управляющий и информационные входы которого связаны с выходом элемента 109 и с информационными выходами  блока триггеров БТ а выходы соединены с установочными входами счетных триггеров 84, реализующих счет импульсов, поступающих на счетный вход первого счетного триггера 84 с выхода первого элемента И 63 блока синхронизации 6, а выходы счетных триггеров 84 являются выходами счетчика импульсов 59 и подключены к выходам ПЗУ60, часть выходов которого адресными шинами C12…Cj поступают на соответствующие входы блока оперативной памяти 3, входного и выходного блоков 1, 4, а другая часть выходов ПЗУ60 в виде командных (управляющих) шин Ck,

блока триггеров БТ а выходы соединены с установочными входами счетных триггеров 84, реализующих счет импульсов, поступающих на счетный вход первого счетного триггера 84 с выхода первого элемента И 63 блока синхронизации 6, а выходы счетных триггеров 84 являются выходами счетчика импульсов 59 и подключены к выходам ПЗУ60, часть выходов которого адресными шинами C12…Cj поступают на соответствующие входы блока оперативной памяти 3, входного и выходного блоков 1, 4, а другая часть выходов ПЗУ60 в виде командных (управляющих) шин Ck,  , Ст,

, Ст,  ,

,  ,

,  , Со,

, Со,  ,

,  ,

,  ,

,  , Сх,

, Сх,  , С1…C11, поступает в виде одноименных сигналов на соответствующие входы блоков 2,7 и модулей ЛМ, ДМ.

, С1…C11, поступает в виде одноименных сигналов на соответствующие входы блоков 2,7 и модулей ЛМ, ДМ.

Функциональная взаимосвязь между выходами и входами электронного ключа 85 представлена ниже при Ст=1 и Ст=1

Где  и

и  - выходы электронного ключа 85.

- выходы электронного ключа 85.

- значение кода на выходе блока БТ и входе электронного ключа 85.

- значение кода на выходе блока БТ и входе электронного ключа 85.

Т1…Тп - значения кодов на адресных входах ППЗУ блока БТ, поступающих из общих шин 80.

T1…Tm - значения кодов на выходе ППЗУ блока БТ.

Двоичная переменная  является инверсией С, знаки «точка» и «плюс» в логических функциях означают логические умножение и сложение.

является инверсией С, знаки «точка» и «плюс» в логических функциях означают логические умножение и сложение.

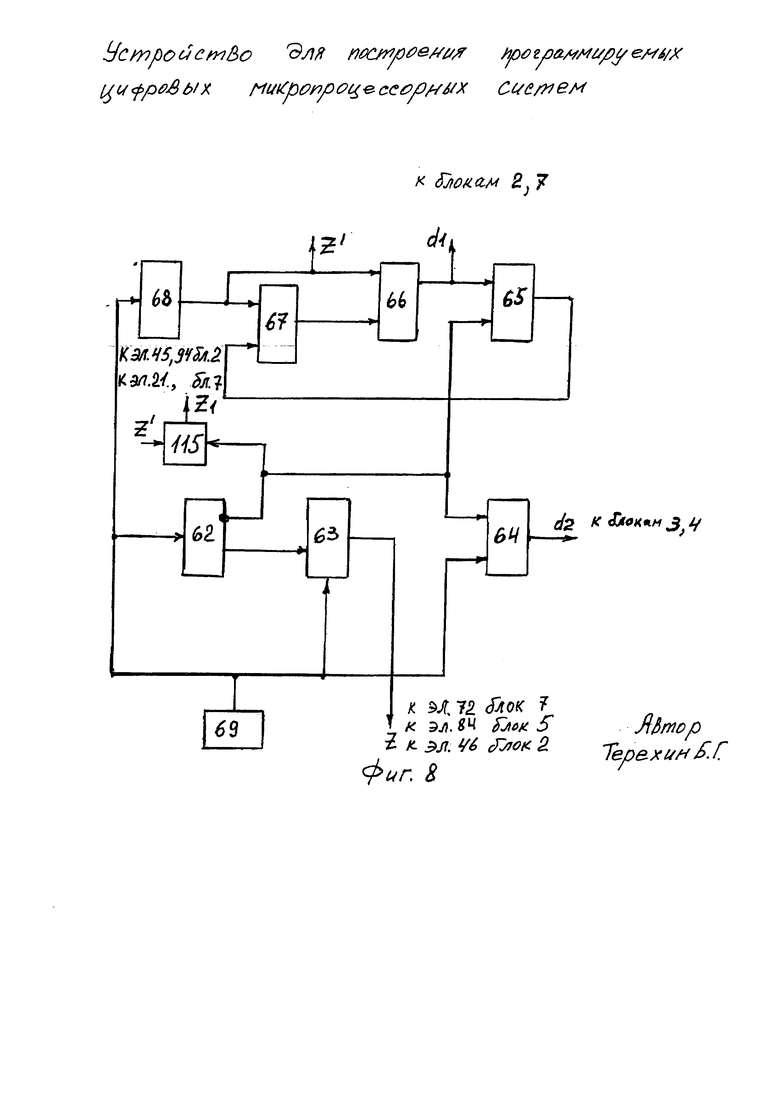

Пример и работа блока синхронизации 6 представлен на фиг. 8 и фиг. 9, он содержит первый счетный триггер 62, подключенный прямым выходом к первому элементу И63, а инверсным выходом к первым входам второго и третьего элементов И64, И65, второй вход последнего подключен к выходу четвертого элемента И66, входы которого связаны с выходом второго счетного триггера 67, с его счетным входом и с выходом инвертора 68, вход последнего вместе с входами триггера 62, элемента И63 и элемента И64 подключены к генератору импульсов 69, выход элемента И65 связан с входом сброса в «0» счетного триггера 67, пятый элемент И115, подключенный входами к инверсному выходу счетного триггера 62 и к выходу инвертора 68, а выходом связан с определенными входами элементов четвертого И45 и седьмого И94 блока 2 и входом пятого элемента И21 блока 7, выход первого элемента И63 соединен с входом восьмого элемента И72 блока 7.

Все триггеры и ячейки памяти срабатывают по заднему фронту импульсов, поступающих на их управляющие, сбрасывающие и счетные входы. Перед началом работы все триггеры и ячейки памяти установлены в «0».

Принцип работы блока 2 состоит в реализации булевых функций И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, НЕ, а также в управлении процессами в блоках 3, 4, 5 и 7, соответствующими сигналами с выхода дешифратора 37. Перед вычислением функции И и других функций, триггер 43 устанавливается в единичное состояние и на его счетный вход через элемент 41, при соответствующем значении команды С1, поступают инверсные значения переменных входящие в искомую функцию И, при появлении первой нулевой двоичной переменной триггер 43 изменит состояние на нулевое и заблокируется нулевым сигналом на выходе элемента И-НЕ 44 при С2=1 и единичным сигналом на инверсном выходе триггера 43. После подачи последней переменной из функции И, на следующем такте результат вычисления можно считывать с выхода элемента 120 при С2=1. Если вычисляется функция ИЛИ, то триггер 43 устанавливается в единичное состояние сигналом с элемента И 45 и на счетный вход триггера 43, через элемент 41, последовательно подаются в прямом виде двоичные переменные из функции ИЛИ, как только появится первое единичное значение указанной переменной триггер 43 перейдет в нулевое состояние и работа его заблокируется нулевым сигналом с выхода элемента И-НЕ 44, после подачи последней переменной из вычисляемой функции ИЛИ, на следующем такте на выходе элемента 120, при С2=0, имеется результат вычисления искомой функции. Вычисление функции ИСКЛЮЧАЮЩЕЕ ИЛИ триггером 43 происходит при помощи последовательной подачи переменных, входящих в искомую функцию. Функция НЕ с выхода триггера 41 реализуется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 120 при команде С2=1.

В блоке 7, при  и

и  на управляющих входах управляемого элемента 16, последний реализует логическую функцию ИЛИ, если

на управляющих входах управляемого элемента 16, последний реализует логическую функцию ИЛИ, если  и

и

, то элемент 16 реализует логическую функцию ИСКЛЮЧАЮЩЕЕ ИЛИ, если

, то элемент 16 реализует логическую функцию ИСКЛЮЧАЮЩЕЕ ИЛИ, если  и

и  , то элемент 16 реализует функцию ИСКЛЮЧАЮЩЕЕ ИЛИ двух последних разрядов двоичного кода на выходах схемных фрагментов Ф1…Фn, а при

, то элемент 16 реализует функцию ИСКЛЮЧАЮЩЕЕ ИЛИ двух последних разрядов двоичного кода на выходах схемных фрагментов Ф1…Фn, а при  и

и  на выходе элемента 16 появляется сигнал с выхода последнего логического канала, при

на выходе элемента 16 появляется сигнал с выхода последнего логического канала, при  ,

,  и

и  на выходе элемента 16 блока 7 появляется значение первого разряда двоичного кода, записанного в счетные триггеры 29 логических каналов блока 7.

на выходе элемента 16 блока 7 появляется значение первого разряда двоичного кода, записанного в счетные триггеры 29 логических каналов блока 7.

Работа устройства состоит в вычислении логических функций в блоке 2 с одновременной реализацией операций над многоразрядными двоичными кодами в блоке 7 и при необходимости устройство обеспечивает совместную работу блоков 2 и 7, например в случае исследования заданных и полученных (принятых) двоичных кодов и принятия решений по результатам логического анализа полученных результатов. Устройство работает по тактам, сформированным в блоке 6.

Работу устройства поясним на нескольких примерах. Допустим, что С'=1.

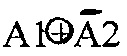

Сравним два двоичных числа А1 и А2 и допустим, что А1=А2 и оба выражены двоичным кодом 11001011. Допустим число А1 находится в блоке 1 в виде X1…Xn и n=8, а число А2 хранится в блоке оперативной памяти 3 в значениях Р1…Pn и n=8, т.е. блок 7 имеет восемь логических каналов. Равенство чисел определим методом алгебраического сложения чисел А1 и -А2, представленного в дополнительном коде, примем, что  и

и  .

.

На первом такте значения X1…Х8, при соответствующих значениях С12…Се,  ,

,  ,

,  и e1=1, поступят из блока 1, через ключ 82 на общие шины 80 системы связи и затем на входы четвертых элементов И 23 всех логических каналов блока 7, где по командам С9…С11 активизируется выход e1 дешифратора 8 и число А1 при единичном выходе элемента И 73, через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 24, ИЛИ 25, И 28 и d1=1, запишется в счетные триггеры 29. По сигналу

и e1=1, поступят из блока 1, через ключ 82 на общие шины 80 системы связи и затем на входы четвертых элементов И 23 всех логических каналов блока 7, где по командам С9…С11 активизируется выход e1 дешифратора 8 и число А1 при единичном выходе элемента И 73, через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 24, ИЛИ 25, И 28 и d1=1, запишется в счетные триггеры 29. По сигналу  с выхода элемента 94 блока 2 триггер 47 перейдет в единичное состояние.

с выхода элемента 94 блока 2 триггер 47 перейдет в единичное состояние.

На втором такте, при соответствующих сигналах С12…Се и е2=1 в блоке 3 активизируется соответствующий выход дешифратора 49 и с выхода ключа 50 число А2, через ключ 83 и общие шины 80 системы связи поступит на входы элементов И 23 всех логических каналов и при Д1=1 по сигналу с выходов элементов ИЛИ 15 и ИСКЛЮЧАЮЩЕЕ ИЛИ 24, ИЛИ 25 и И 28 инверсия числа А2 поступит на счетные входы счетных триггеров 29 всех логических каналов и при d1=1 реализуется по разрядно функция ИСКЛЮЧАЮЩЕЕ ИЛИ для чисел А1 и  , при этом на выходах счетных триггеров 29 всех логических каналов устанавливаются единичные значения, счетный триггер 43 блока 2 устанавливается в состояние «1» по сигналу С3=1.

, при этом на выходах счетных триггеров 29 всех логических каналов устанавливаются единичные значения, счетный триггер 43 блока 2 устанавливается в состояние «1» по сигналу С3=1.

На третьем такте, при

,

,  , d=1 логическая «1» с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ103 и И27 первого канала поступит на соответствующие входы элементов ИЛИ 25 и блока БУП и логическая «1» с выхода М2 блока БУП появится на входе элемента И 27 второго логического канала и далее в соответствии с функциями (1А) по единичным сигналам М3…Mn из блока БУП, через элементы И 27, ИЛИ 25 и И28 последующих каналов, при импульсе d1=1, все счетные триггеры 29 переключатся в состояние «нуля» т.е. появился результат разности двух равных чисел А1 и А2, а все триггеры 30 переключатся в состояние «1» и произойдет запись информации с выхода Mn+1 блока БУП при

, d=1 логическая «1» с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ103 и И27 первого канала поступит на соответствующие входы элементов ИЛИ 25 и блока БУП и логическая «1» с выхода М2 блока БУП появится на входе элемента И 27 второго логического канала и далее в соответствии с функциями (1А) по единичным сигналам М3…Mn из блока БУП, через элементы И 27, ИЛИ 25 и И28 последующих каналов, при импульсе d1=1, все счетные триггеры 29 переключатся в состояние «нуля» т.е. появился результат разности двух равных чисел А1 и А2, а все триггеры 30 переключатся в состояние «1» и произойдет запись информации с выхода Mn+1 блока БУП при  , через модуль ДМ в ячейку памяти 17 по единичному сигналу с выхода элемента И 20 блока 7.

, через модуль ДМ в ячейку памяти 17 по единичному сигналу с выхода элемента И 20 блока 7.

На том же третьем такте при  логический «0» с выходов схемных фрагментов Ф1…Фn, через элемент ИЛИ 16, при соответствующих сигналах С9…С11 по команде е6 с выхода первого дешифратора 8 блока 7 поступает, через элемент 40 на вход элемента 41 блока 2 и при С1=0, в третьей четверти такта при C2=1, d1=1 и С3=0 единичное значение сигнала на выходе счетного триггера 43 сохранится. На четвертом такте логическая «1» с выхода счетного триггера 43, при определенных командах С4…С6 и активизации соответствующего выхода дешифратора 37 блока 2 и выхода элемента И 39 при импульсе d2=1, поступающим с выхода элемента И 64 блока 6, запишется в определенную значениями Се…Cj ячейку памяти 57 выходного блока 4, как информация о том, что А1=А2.

логический «0» с выходов схемных фрагментов Ф1…Фn, через элемент ИЛИ 16, при соответствующих сигналах С9…С11 по команде е6 с выхода первого дешифратора 8 блока 7 поступает, через элемент 40 на вход элемента 41 блока 2 и при С1=0, в третьей четверти такта при C2=1, d1=1 и С3=0 единичное значение сигнала на выходе счетного триггера 43 сохранится. На четвертом такте логическая «1» с выхода счетного триггера 43, при определенных командах С4…С6 и активизации соответствующего выхода дешифратора 37 блока 2 и выхода элемента И 39 при импульсе d2=1, поступающим с выхода элемента И 64 блока 6, запишется в определенную значениями Се…Cj ячейку памяти 57 выходного блока 4, как информация о том, что А1=А2.

Рассмотрим второй пример, когда А1<А2 и А1=11001011, а А2 равно 10011011, триггеры 29 установлены в нулевое состояние, а триггер 43 в единичное, триггеры 29 и 30 во всех логических каналах переводятся в нулевые состояния при импульсах q1 и q2, а триггер 43 устанавливается в единичное состояние при С3=1.

На первом такте по аналогии с первым примером число А1 записывается в счетные триггеры 29 по разрядам в каждый логический канал блока 7.

На втором такте при е2=1 аналогично первому примеру, когда Д1=1, инверсия числа А2 поступает на входы элементов И 28 и в третьей четверти такта (d1=1) единичные значения разрядов числа А2 меняют состояние счетных триггеров 29 на противоположное и на выходе триггеров 29 появляется результат равный A1+А2 (10011111), при этом во втором логическом канале триггер 29 за два такта дважды поменял свое состояние, что привело к изменению состояния второго счетного триггера 30 с нулевого в единичное и произошла фиксация факта переноса из второго разряда в третий или из второго логического канала в третий в блоке БУП, что происходит при аналогичных ситуациях во всех логических каналах блока 7.

На третьем такте по единичным сигналам  и

и  , логическая «1», через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 103 и И27 первого канала поступает на соответствующие входы блока БУП и элемента ИЛИ 25 первого логического канала и далее в соответствии с функциями (1А) блока БУП происходит процесс переноса в соответствующие логические каналы по сигналам с выхода блока БУП, поступающим одновременно на входы элементов И27 определенных логических каналов и на выходах триггеров 29 всех логических каналов устанавливается результат алгебраической суммы А1+(-А2) в дополнительном коде 01011111, одновременно по сигналу с выхода элемента И 20 произойдет запись нулевой информации с выхода триггера 30 последнего канала через блок БУП в ячейку памяти 17 блока 7, при этом нулевое значение на выходе Mn+1, блока БУП показывает, что А1<А2 и получен результат алгебраической суммы в дополнительном коде. На третьем же такте по сигналу е7=1 с выхода дешифратора 8 блока 7 значение Mn+1=0 с выхода, блока БУП поступает на выход элемента И-ИЛИ 40 блока 2 и при С 1=1 на выходе элемента И 41 имеется логическая «1» и при d1=1 на выходе счетного триггера 43 появляется логический нуль. На четвертом такте при

, логическая «1», через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 103 и И27 первого канала поступает на соответствующие входы блока БУП и элемента ИЛИ 25 первого логического канала и далее в соответствии с функциями (1А) блока БУП происходит процесс переноса в соответствующие логические каналы по сигналам с выхода блока БУП, поступающим одновременно на входы элементов И27 определенных логических каналов и на выходах триггеров 29 всех логических каналов устанавливается результат алгебраической суммы А1+(-А2) в дополнительном коде 01011111, одновременно по сигналу с выхода элемента И 20 произойдет запись нулевой информации с выхода триггера 30 последнего канала через блок БУП в ячейку памяти 17 блока 7, при этом нулевое значение на выходе Mn+1, блока БУП показывает, что А1<А2 и получен результат алгебраической суммы в дополнительном коде. На третьем же такте по сигналу е7=1 с выхода дешифратора 8 блока 7 значение Mn+1=0 с выхода, блока БУП поступает на выход элемента И-ИЛИ 40 блока 2 и при С 1=1 на выходе элемента И 41 имеется логическая «1» и при d1=1 на выходе счетного триггера 43 появляется логический нуль. На четвертом такте при  ,

,  и е6=1 значение L1=1 с выхода элемента ИЛИ 16 блока 7 поступит, через элемент И-ИЛИ 40 на вход элемента И 41 и при С1=1 на выходе последнего образуется логический «0» и значение на выходе счетного триггера 43 не изменится и полученный результат вычисления логической функции Mn+1⋅L1=0, подтверждает, что двоичное число А1 меньше двоичного числа А2.

и е6=1 значение L1=1 с выхода элемента ИЛИ 16 блока 7 поступит, через элемент И-ИЛИ 40 на вход элемента И 41 и при С1=1 на выходе последнего образуется логический «0» и значение на выходе счетного триггера 43 не изменится и полученный результат вычисления логической функции Mn+1⋅L1=0, подтверждает, что двоичное число А1 меньше двоичного числа А2.

На пятом такте полученный выше результат с выхода счетного триггера 43 блока 2 при соответствующей команде дешифратора 37 и d2=1, в соответствии с сигналом на выходе элемента И 39 запишется в выходной блок 4 в одну из ячеек памяти по соответствующему адресу Се…Cj.

Дальше следовало бы, описанным выше способом, в блоке 2 вычислить логическую функцию L1⋅Mn+1 и если А1>А2, то функция L1⋅Mn+1 равнялась логической «1».

Вернемся к третьему такту, когда был получен результат алгебраической суммы двух чисел А1 и -А2 в дополнительном коде и продолжим решение задачи по определению результата вычисления алгебраической суммы A1+(-А2).

На третьем такте при Со=1 завершится процесс переноса, образовавшийся на выходах триггеров 30 и затем в блоке БУП, при этом через элементы И 27, ИЛИ 25, И 28 логических каналов, по импульсу dl значения переносов поступят на счетные входы триггеров 29 и на их выходах появится результат сложения чисел А1 и А2. Если по абсолютному значению число А1 больше числа А2 т.е. /А1/>/А2/, то на четвертом такте следует прибавить к значению А1+А2 единицу и получим искомый результат A1+(-А2), а если /А1/</А2/ следует инвертировать результат сложения А1+А2 и тогда получим искомый результат сложения А1+(-А2).

С целью реализации выше приведенного алгоритма в многоканальный операционный блок 7 имеется восьмой элемент ИЛИ 101 и соответствующие связи. Входы элемента ИЛИ 101 соединены с выходами Д2 и Д3 дешифратора 9, а выход подключен к определенному входу элемента И 18, другой вход которого связан с прямым выходом управляемой ячейки памяти 17, а выход элемента И18 соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 103 выход К2 которого подключен к входу второго элемента И27 первого логического канала и к определенному входу блока БУП, а выход К1 элемента И 19 связан с одним из входов первого элемента ИЛИ 15, два входа элемента И19 подключены к инверсному выходу ячейки памяти 17 и входу Д2 дешифратора 9 блока 7.

Предложенная схема работает следующим образом. Если /А1/>/А2/, то на третьем такте работы в ячейку памяти 17 блока 7 при  и импульсе d1=1, по сигналу с выхода элемента И 20 запишется единичный перенос из старшего разряда т.е. с выхода Mn+1 блока БУП и на этом же такте произойдет сброс всех триггеров 30 в четвертой четверти такта при q2=1.

и импульсе d1=1, по сигналу с выхода элемента И 20 запишется единичный перенос из старшего разряда т.е. с выхода Mn+1 блока БУП и на этом же такте произойдет сброс всех триггеров 30 в четвертой четверти такта при q2=1.

На четвертом такте при  , Д2=1,

, Д2=1,  и К2=1 в число

и К2=1 в число  запишется единичный перенос через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 103, И 27, ИЛИ 25, И 28 и на выходах триггеров 29 образуется значение искомой суммы А1+(-А2).

запишется единичный перенос через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 103, И 27, ИЛИ 25, И 28 и на выходах триггеров 29 образуется значение искомой суммы А1+(-А2).

Если /А1/</А2/ или /А1/=/А2/, то на третьем такте триггеры 30 всех логических каналов сбросятся в «0» и в ячейку памяти 17 запишется «0», а на четвертом такте триггеры 30 всех логических каналов сбросятся в «0» в первой четверти такта и при  , Д2=1, К1=1 и К2=0 по сигналу с выхода элемента ИЛИ 15 произойдет инвертирование числа

, Д2=1, К1=1 и К2=0 по сигналу с выхода элемента ИЛИ 15 произойдет инвертирование числа  и на выходах триггеров 29 появится результат алгебраической суммы А1+(-А2).

и на выходах триггеров 29 появится результат алгебраической суммы А1+(-А2).

Далее полученный результат можно записать в блок оперативной памяти 3 или в выходной блок 4 на следующем пятом такте. Предлагаемый алгоритм и соответствующая схема позволяют это сделать на том же четвертом такте, сокращая общее число тактов на реализацию алгебраического сложения и записи результата в блоки 3 или 4.

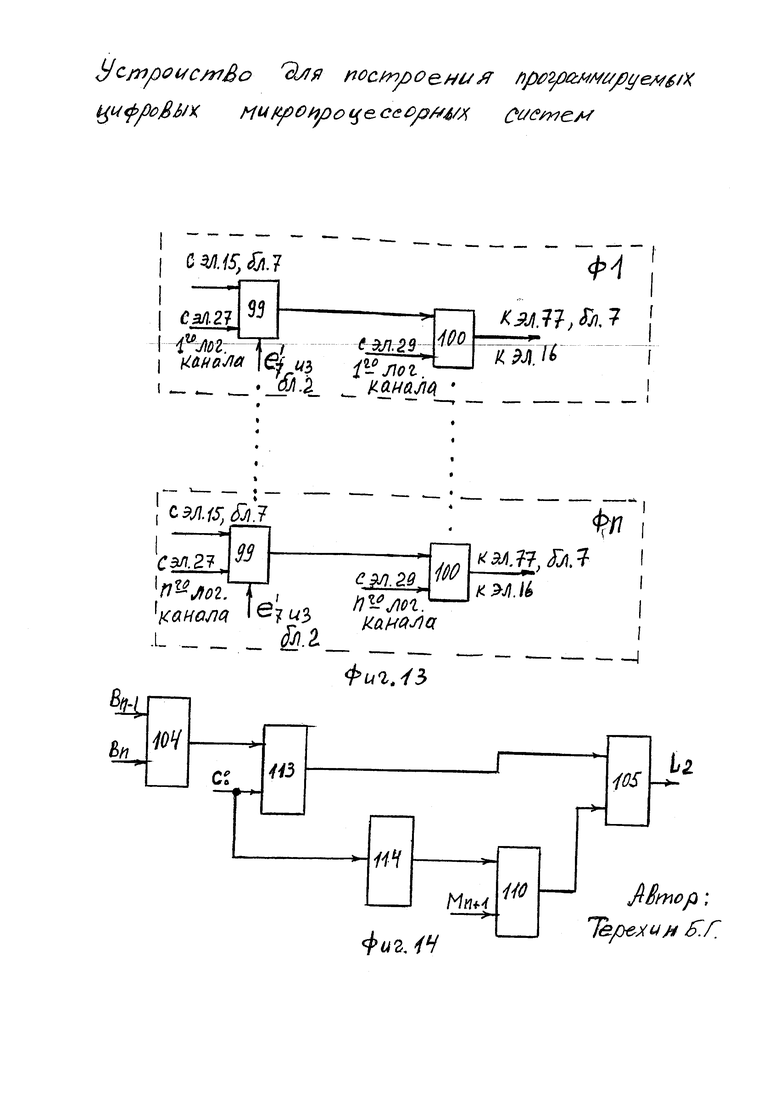

Для этого в блоке 7 имеется «n» одинаковых схемных фрагментов Ф1…Фn по числу логических каналов, каждый из которых (фиг. 13) содержит два элемента ИЛИ 99 и ИСКЛЮЧАЮЩЕЕ ИЛИ 100, в каждом схемном фрагменте три входа элемента ИЛИ 99 связаны соответственно с выходом элемента ИЛИ 15 блока 7, с вторым входом элемента И 27 соответствующего логического канала и с седьмым выходом  дешифратора 37 блока 2, выход элемента ИЛИ 99 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 100. второй вход которого подключен к выходу триггера 29 соответствующего логического канала, а выход связан с определенными информационными входами электронного выключателя 77 и управляемого элемента 16 блока 7. Схемные фрагменты Ф1…Фn позволяют записать полученный результат или его инверсию (

дешифратора 37 блока 2, выход элемента ИЛИ 99 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 100. второй вход которого подключен к выходу триггера 29 соответствующего логического канала, а выход связан с определенными информационными входами электронного выключателя 77 и управляемого элемента 16 блока 7. Схемные фрагменты Ф1…Фn позволяют записать полученный результат или его инверсию ( ) в блоки 3 или 4.

) в блоки 3 или 4.

Вернемся к четвертому такту вычисления алгебраической суммы А1+(-А2). Если /А1/>/А2/ то при Д2=1 и К2=1 в блоке 7 с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 103 на вход элемента И 27 первого логического канала поступит логическая «1» и путем переноса через блок БУП, она поступит на входы элементов И 27 определенных логических каналов, а затем с выходов соответствующих элементов И27 на входы и выходы элементов ИЛИ 99 соответствующих схемных фрагментов и с учетом сигналов на выходах триггеров 29 на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 100 всех схемных фрагментов Ф1…Фn появится искомое значение суммы А1+(-А2), которое можно записать например в блок оперативной памяти 3 на этом же такте при сигнале еЗ=1 с выхода первого дешифратора 8 блока 7. При /А1/</А2/ и Д2=1, К1=1 на выходе элемента ИЛИ 15 блока 7 появится логическая «1», которая поступит на входы элементов ИЛИ 99 и затем на входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 100 всех схемных фрагментов, при этом на выходах последних элементов появится результат суммы А1+(-А2), который через выключатель 77 при е3=1 можно записать в блок оперативной памяти 3. Введение схемных фрагментов повысило быстродействие устройства и за счет того, что при  , используя схемные фрагменты Ф1…Фn, можно за один такт произвести инверсию кода хранящегося на выходах триггеров 29 и при е3=1 записать эту инверсию например в блок оперативной памяти 3, что очевидно следует из анализа работы схемных фрагментов.

, используя схемные фрагменты Ф1…Фn, можно за один такт произвести инверсию кода хранящегося на выходах триггеров 29 и при е3=1 записать эту инверсию например в блок оперативной памяти 3, что очевидно следует из анализа работы схемных фрагментов.

Управляемый триггер 102 блока 7 соединенный входом управления с выходом элемента И 12 и информационным входом с прямым выходом ячейки памяти 17, а выходом с шиной Tn+1, которая определяет знак разности двух чисел и позволяет сохранить этот знак на протяжении любого количества тактов работы устройства, когда состояние ячейки памяти 17 может меняться.. Входы элемента И 12 связаны с определенным выходом дешифратора 8 блока 7 и с выходом элемента 66 блока синхронизации 6. Шина Tn+1 подключена к соответствующему входу выходного блока 4. Команда Д1 с выхода второго дешифратора 9 блока 7 позволяет инвертировать значение кода, записанного в триггеры 29.

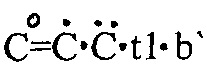

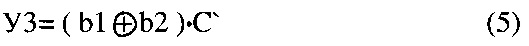

Модуль сдвига разрядов МСР1 для каждого логического канала в блоке 7 кроме первого и последнего имеет два выхода  и

и  и четыре входа

и четыре входа  ,

,  ,

,  ,

,  , его работа определяется булевыми функциями:

, его работа определяется булевыми функциями:

Где первый выход  соединен с третьим входом первого элемента ИЛИ 25 данного логического канала, второй выход

соединен с третьим входом первого элемента ИЛИ 25 данного логического канала, второй выход  связан с четвертым входом элемента ИЛИ 25 последующего канала, вход

связан с четвертым входом элемента ИЛИ 25 последующего канала, вход  подключен к выходу счетного триггера 29 данного логического канала, вход

подключен к выходу счетного триггера 29 данного логического канала, вход  соединен с выходом первого счетного триггера 29 последующего логического канала, входы

соединен с выходом первого счетного триггера 29 последующего логического канала, входы  и

и  связаны с соответствующими выходами логического модуля ЛМ.

связаны с соответствующими выходами логического модуля ЛМ.

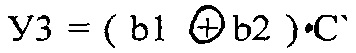

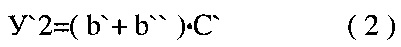

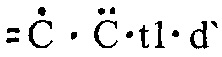

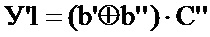

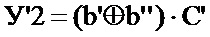

Модуль сдвига разрядов МСР2 первого логического канала имеет три выхода У1, У2, У3 и пять входов b1, b2,  ,

,  ,

,  и его работа определяется булевыми функциями:

и его работа определяется булевыми функциями:

Где первый выход У1 соединен с четвертым входом элемента ИЛИ 25 первого логического канала, второй выход У2 связан с третьим входом элемента ИЛИ 25 того же канала, третий выход У3 подключен к четвертому входу элемента ИЛИ 25 второго логического канала, вход b1 связан с выходом первого счетного триггера 29 первого логического канала, вход b2 подключен к выходу счетного триггера 29 второго логического канала, входы  ,

,

соединены с соответствующими выходами логического модуля ЛМ, в котором выходы определяются логическими функциями

соединены с соответствующими выходами логического модуля ЛМ, в котором выходы определяются логическими функциями  ,

,  ,

,

,

,  , где

, где  ,

,  являются входными сигналами логического модуля ЛМ и поступают на его входы с выходов программного блока 5, t1 является выходом элемента НЕЛ 12 блока 7, а

являются входными сигналами логического модуля ЛМ и поступают на его входы с выходов программного блока 5, t1 является выходом элемента НЕЛ 12 блока 7, а  подключен к выходу элемента И106 блока 2.

подключен к выходу элемента И106 блока 2.

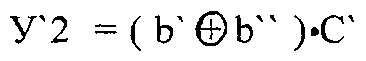

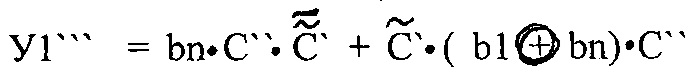

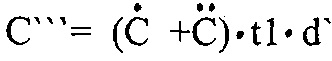

Модуль сдвига разрядов МСР3 последнего логического канала имеет один выход  , пять входов bn,

, пять входов bn,  ,

,  b1,

b1,  и функционирует в соответствии с булевой функцией:

и функционирует в соответствии с булевой функцией:

Где выход  соединен с определенным входом элемента ИЛИ 25 последнего логического канала, входы b1, bn связаны соответственно с выходами триггеров 29 первого и последнего логических каналов, вход

соединен с определенным входом элемента ИЛИ 25 последнего логического канала, входы b1, bn связаны соответственно с выходами триггеров 29 первого и последнего логических каналов, вход  подключен к соответствующему выходу логического модуля ЛМ,

подключен к соответствующему выходу логического модуля ЛМ,  соединен с определенным выходом программного блока 5, а

соединен с определенным выходом программного блока 5, а  есть инверсия

есть инверсия  .

.

Сдвиг разрядов кода вниз от первого до последнего логического канала осуществляется по команде  , при

, при  , t1=1,

, t1=1,  . В этом случае для модуля МСР2, если b1=1, и на выходе триггера 29 второго логического канала имеется логический «0», то в соответствии с функциями (3) и (5) на выходе У1 установится логическая единица и она так же появится на выходе элемента ИЛИ 25, поступит на вход элемента И 28 и при d1=1 триггер 29 первого канала изменит свое состояние на нулевое. Одновременно при неравенстве сигналов на входах b1, d2 выход У3 активизируется и логическая «1» поступит на вход элемента И 28 и по окончанию импульса d1 выход триггера 29 второго канала примет противоположное значение, т.е. значение которое было на выходе триггера 29 первого логического канала. Одновременно в модулях МСР1 в соответствии с функцией (2) при неравенстве сигналов на выходах триггеров 29 данного и последующих логических каналов активизируется выход

. В этом случае для модуля МСР2, если b1=1, и на выходе триггера 29 второго логического канала имеется логический «0», то в соответствии с функциями (3) и (5) на выходе У1 установится логическая единица и она так же появится на выходе элемента ИЛИ 25, поступит на вход элемента И 28 и при d1=1 триггер 29 первого канала изменит свое состояние на нулевое. Одновременно при неравенстве сигналов на входах b1, d2 выход У3 активизируется и логическая «1» поступит на вход элемента И 28 и по окончанию импульса d1 выход триггера 29 второго канала примет противоположное значение, т.е. значение которое было на выходе триггера 29 первого логического канала. Одновременно в модулях МСР1 в соответствии с функцией (2) при неравенстве сигналов на выходах триггеров 29 данного и последующих логических каналов активизируется выход  во всех модулях МСР1 и логическая «1» через соответствующие элементы ИЛИ 25 поступят на входы элементов И 28 соответствующих логических каналов и на выходе триггера 29 каждого последующего канала появится значение выхода триггера 29 данного логического канала т.е. произойдет сдвиг вниз разрядов кода, ранее записанного в триггеры 29.

во всех модулях МСР1 и логическая «1» через соответствующие элементы ИЛИ 25 поступят на входы элементов И 28 соответствующих логических каналов и на выходе триггера 29 каждого последующего канала появится значение выхода триггера 29 данного логического канала т.е. произойдет сдвиг вниз разрядов кода, ранее записанного в триггеры 29.

Сдвиг разрядов кода вверх имеет место при наличии команды  , когда

, когда  ,

,  , t1=1 и

, t1=1 и  . Тогда в соответствии с функциями (1)…(6) могут активизироваться выходы У2 в модуле МСР2,

. Тогда в соответствии с функциями (1)…(6) могут активизироваться выходы У2 в модуле МСР2,  в модуле МСР1 и выход

в модуле МСР1 и выход  в модуле МСР3, при этом выход У2 активизируется, если входные сигналы b1, n2 на входах модуля МСР2 не равны и в этом случае, через элемент ИЛИ 25 на вход элемента И 28 первого логического канала поступит логическая «1» и триггер 29 первого канала примет значение триггера 29 второго логического канала. Одновременно для любого модуля МСР1 при неравенстве сигналов

в модуле МСР3, при этом выход У2 активизируется, если входные сигналы b1, n2 на входах модуля МСР2 не равны и в этом случае, через элемент ИЛИ 25 на вход элемента И 28 первого логического канала поступит логическая «1» и триггер 29 первого канала примет значение триггера 29 второго логического канала. Одновременно для любого модуля МСР1 при неравенстве сигналов  ,

,  активизируется выход

активизируется выход  и логическая «1», через элемент ИЛИ 25 поступит на вход элемента И 28 данного канала, где находится соответствующий модуль МСР1 и на выходе триггера 29 данного логического канала установится значение выхода триггера 29 последующего логического канала. Одновременно при b n=1 активизируется выход

и логическая «1», через элемент ИЛИ 25 поступит на вход элемента И 28 данного канала, где находится соответствующий модуль МСР1 и на выходе триггера 29 данного логического канала установится значение выхода триггера 29 последующего логического канала. Одновременно при b n=1 активизируется выход  модуля МСР3 и на выходе элементе И 28 появится логическая «1» и триггер 29 последнего логического канала перейдет в состояние «0». Таким образом произойдет сдвиг снизу-вверх разрядов кода записанного в триггеры 29.

модуля МСР3 и на выходе элементе И 28 появится логическая «1» и триггер 29 последнего логического канала перейдет в состояние «0». Таким образом произойдет сдвиг снизу-вверх разрядов кода записанного в триггеры 29.

Наличие логического модуля ЛМ в устройстве позволило организовать циклический сдвиг двоичных кодов вверх с переносом младшего разряда в старший при  , что следует из анализа логической формулы (6) для модуля МСР3 и вниз с переносом старшего разряда в младший разряд при значении С°=1, что непосредственно следует из анализа формулы (3), определяющей значение У1 в модуле МСР2.

, что следует из анализа логической формулы (6) для модуля МСР3 и вниз с переносом старшего разряда в младший разряд при значении С°=1, что непосредственно следует из анализа формулы (3), определяющей значение У1 в модуле МСР2.

Единичное значение прямого выхода ячейки памяти 17 в блоке 7 означает наличие переноса, например после арифметического сложения n разрядов двух двоичных чисел значение переноса в следующий n+1 разряд активизируется при Д3=1 на выходе дешифратора 9 блока 7 и поступит, через элементы И18, ИСКЛЮЧАЮЩЕЕ ИЛИ103 и ИЛИ13 на вход элемента И 27 первого логического канала блока 7.

Для определения четных или нечетных чисел в блок 7 введен элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 79 входы которого подключены к первой шине Т1 и командной шине С1 блока 5, а выход связан с входом элемента ИЛИ 107 блока 7, что сократило число тактов при определении четного числа или нечетного и записи его в логические каналы при С1=1 или С1=0.

Элемент И-НЕ 44 в блоке 2, имеющий связь своими входами с соответствующим выходом программного блока 5 и инверсным выходом счетного триггера 43, а выходом с третьим входом третьего элемента И42, блокирует работу счетного триггера 43 при его нулевом состоянии и при С2=1, введенный в блок 2 второй счетный триггер 47, подключенный счетным входом к выходу восьмого элемента И116, входом сброса в «0» соединен с выходом седьмого элемента И94, а инверсным выходом через элемент И106 подключен к блокирующим входам дешифраторов 8 и 9, также к входам десятого элемента И76 и четвертого элемента И20 блока 7 и дешифратору 81 позволяет блокировать работу блоков 3, 4 и 7 с многоразрядными двоичными кодами, при этом блок 2 может продолжать работать с одноразрядными двоичными кодами.

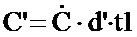

Дискретный модуль ДМ (Фиг. 14) содержит первый и второй элементы И 110 и 113, элемент НЕ 114, причем входы первого элемента ИЛИ 104 соединены с выходами первых счетных триггеров 29 предпоследнего и последнего каналов, выход второго элемента ИЛИ 105 соединен с информационным входом управляемой ячейки памяти 17 многоканального операционного блока 7. Через выход (L2) модуля ДМ (Фиг. 1) в ячейку памяти 17 записывается значение Mn+1 из блока БУП при  и

и  , а при

, а при  и

и

записывается значение ИЛИ двух последних разрядов двоичного кода, записанного в триггерах 29 соответствующих логических каналов блока 7, где первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 103 позволяет инвертировать сигнал на выходе элемента И 18 по команде

записывается значение ИЛИ двух последних разрядов двоичного кода, записанного в триггерах 29 соответствующих логических каналов блока 7, где первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 103 позволяет инвертировать сигнал на выходе элемента И 18 по команде  .

.

Введенный в каждый логический канал элемент И-НЕ26 соединен тремя входами соответственно с прямым выходом счетного триггера 29, с определенным выходом программного блока 5 и с выходом элемента ИЛИ11 блока 7, а выходом связан с третьим входом элемента И28, позволяет организовать в каждом логическом канале поразрядное вычисление функций И. ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ одним счетным триггером 29.

При поразрядном вычислении функции ИЛИ триггеры 29 во всех логических каналах устанавливаются в «0» и на счетные входы триггеров 29 подаются двоичные коды и как только первое единичное значение переменной появится на счетном входе триггера 29 последний переменит свое состояние на «1» и его работа заблокируется нулевым выходом И-НЕ26, после окончания вычисления искомой функции ИЛИ на выходах триггеров 29 будем иметь результат поразрядного вычисления искомой функции ИЛИ и затем полученный результат записать например в блок оперативной памяти 3

При поразрядном вычислении функции И надо установит триггеры 29 в состояние «О» и подавать инверсию двоичных кодов на счетные входы триггеров 29 и как только первая нулевая переменная в виде «1» окажется на счетном входе триггера 29 последний изменит свое состояние на «1» в соответствующих логических каналах и заблокируется нулевым выходом элемента И-НЕ26 и после подачи последнего двоичного кода на выходах триггеров 29 появится инверсный результат поразрядного вычисления функции И, который можно инвертировать в схемных фрагментах Ф1…Фn и записать окончательный результат например в блок оперативной памяти 3. Вычисление функции ИСКЛЮЧАЮЩЕЕ ИЛИ счетными триггерами 29 известно и продемонстрировано выше при сложении двух двоичных чисел А1 и А2.

Предлагаемая реализация поразрядного вычисления функций И и ИЛИ одним счетным триггером 29 позволяет в отличии от аналога и прототипа сократить число логических элементов и линий связи в каждом логическом канале, что упрощает их структуру при сохранении их функциональных возможностей, предложенная структура многоканального операционного блока 7 позволяет, по сравнению с прототипом, сократить число логических элементов и линий связи, что позволяет упростить блок 7, сохраняя его функциональные возможности.

Введение в предлагаемое устройство блока триггеров БТ, содержащего "m" управляемых триггеров, программируемое постоянное запоминающее устройство ППЗУ и управляющий элемент И111 (фиг. 12) позволяет организовать ускоренную реакцию устройства на появление, например аварийного сигнала Ст, поступающего на вход устройства из объекта управления. При этом в блоке БТ, информационные входы управляемых триггеров подключены к информационным выходам Т1…Tm ППЗУ, а входы управления управляемых триггеров связаны с выходом управляющего элемента И111, входы которого соединены с шестым выходом  дешифратора коммутационно-вычислительного блока 2 и с выходом d1 блока синхронизации 6, выходы управляемых триггеров связаны с информационными входами Т1…Tm электронного ключа 85 блока 5, а адресные входы ППЗУ подключены к общим шинам 80.

дешифратора коммутационно-вычислительного блока 2 и с выходом d1 блока синхронизации 6, выходы управляемых триггеров связаны с информационными входами Т1…Tm электронного ключа 85 блока 5, а адресные входы ППЗУ подключены к общим шинам 80.

Предварительно в стандартное ППЗУ блока БТ по адресу Т1…Tn, поступающему с адресных шин 80 записывается значение кода  при установки которого в счетные триггеры 84 программного блока 5 начинается выполнение аварийной подпрограммы с первого такта.

при установки которого в счетные триггеры 84 программного блока 5 начинается выполнение аварийной подпрограммы с первого такта.

В начале выполнения программы в блок триггеров БТ, по сигналу с выхода управляющего элемента И111, при  и d1=1 записывается двоичный код с выходов ППЗУ по адресу Т1…Tn, соответствующий адресу первого такта выполнения аварийной подпрограммы, хранящейся в программном блоке 5. При появлении аварийного сигнала Ст и соответствующего сигнала Ст=1 при d2=1 через элемент И109 происходит включение ключа 85 и установка счетных триггеров 84 блока 5 в соответствующее положение для выполнения аварийной подпрограммы, предотвращающей развитие аварийной ситуации на объекте управления при этом блокировка дешифраторов снимается логическими операциями в элементах ИЛИ108 и И106. Сигнал

и d1=1 записывается двоичный код с выходов ППЗУ по адресу Т1…Tn, соответствующий адресу первого такта выполнения аварийной подпрограммы, хранящейся в программном блоке 5. При появлении аварийного сигнала Ст и соответствующего сигнала Ст=1 при d2=1 через элемент И109 происходит включение ключа 85 и установка счетных триггеров 84 блока 5 в соответствующее положение для выполнения аварийной подпрограммы, предотвращающей развитие аварийной ситуации на объекте управления при этом блокировка дешифраторов снимается логическими операциями в элементах ИЛИ108 и И106. Сигнал  обеспечивает внеочередное включение в работу аварийной подпрограммы в нужный момент работы устройства, когда Ст=1. Сигнал

обеспечивает внеочередное включение в работу аварийной подпрограммы в нужный момент работы устройства, когда Ст=1. Сигнал  поступающий из программного блока 5 на вход элемента ИЛИ108 всегда равен «1» при выполнении основной программы и равен «0» при выполнении аварийной программы. При Ст=0, за счет работы элемента ИЛИ108, элемента И106 в блоке 2 и элемента И109 в блоке 5 сигналом

поступающий из программного блока 5 на вход элемента ИЛИ108 всегда равен «1» при выполнении основной программы и равен «0» при выполнении аварийной программы. При Ст=0, за счет работы элемента ИЛИ108, элемента И106 в блоке 2 и элемента И109 в блоке 5 сигналом  равным «0» блокируются дешифраторы 8, 9, элемент И76 блока 7, дешифратор 81 системы связи устройства, запрещается включение ключа 85 блока 5, а также по сигналу

равным «0» блокируются дешифраторы 8, 9, элемент И76 блока 7, дешифратор 81 системы связи устройства, запрещается включение ключа 85 блока 5, а также по сигналу  блокируется работа дешифратора 37 блока 2, при этом аварийная подпрограмма не выполняется. После прохождения всех тактов работы аварийной программы при

блокируется работа дешифратора 37 блока 2, при этом аварийная подпрограмма не выполняется. После прохождения всех тактов работы аварийной программы при  работа устройства продолжается. Роль аварийного сигнала Ст может выполнять и другой сигнал, поступающий из другого блока в предлагаемом устройстве, если это потребует конкретный алгоритм управления объектом.

работа устройства продолжается. Роль аварийного сигнала Ст может выполнять и другой сигнал, поступающий из другого блока в предлагаемом устройстве, если это потребует конкретный алгоритм управления объектом.

Использование блока БТ, элементов ИЛИ108, шестого и седьмого элементов И106 и И94 в блоке 2 с соответствующими связями позволяет ускорить реакцию устройства при появлении аварийной ситуации на объекте управления, что невозможно в аналоге и прототипе.