Предлагаемое устройство относится к системам логико-программного управления и регулирования технологическими объектами в различных отраслях производства и к средствам решения логических задач.

Известно устройство, содержащее входной и выходной блоки, блоки оперативной памяти и синхронизации, адресные шины, генератор импульсов, программный блок, блок коммутации и вычисления, состоящий из трехвходового дешифратора, трех двухвходовых элементов И, элемента ИЛИ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и управляемой ячейки памяти, командных шин, поступающих, как и адресные шины, с выходов программного блока /1/.

Недостатком данного устройства является относительно низкое быстродействие, большой объем ячеек памяти в программном блоке при реализации, например, процесса сравнения двоичных кодов.

Наиболее технически близким является устройство, содержащее соединенные между собой определенным образом входной блок, принимавший сигналы от датчиков и формирующий определенный код на своем выходе, выходной блок для записи и хранения полученных значений кодов, поступающих из логических каналов многоканального операционного блока, а также из коммутационно-вычислительного блока, программный блок, где хранится программа работы устройства, блок оперативной памяти для хранения промежуточных результатов вычислений и других логических операций, блок синхронизации, обеспечивающий устойчивую работу всего устройства /2/.

К недостаткам данного устройства можно отнести необходимость, каждый раз заново вводить в основную программу повторяющиеся ее части, например, при каждом вычитании двоичных чисел, а также отсутствие возможности передавать те или иные данные внутри устройства в зависимости от результатов анализа этих данных в коммутационно-вычислительном блоке и невозможность функциональной реализации приоритетного прерывания при выполнении основной программы по сигналам от датчиков объекта управления.

Целью предлагаемого изобретения является расширение функциональных возможностей устройства за счет организации процесса приоритетного прерывания и связи результатов вычислений с процессом пересылки данных, а также сокращения объема программирования.

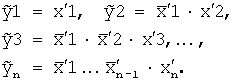

С этой целью в устройство, содержащее входной блок, принимающий сигналы от датчиков и формирующий определенный код на своем выходе, выходной блок для записи значений кодов, поступающих из всех логических каналов в ячейки памяти и передачи их через цифроаналоговые преобразователи на электроисполнительные механизмы, программный блок, блок оперативной памяти, блок синхронизации и коммутационно-вычислительный блок, состоящий из элемента И-ИЛИ элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, пяти элементов И, ячейки памяти, элементов ИЛИ и НЕ, первые входы двух и элемента И-ИЛИ соединены соответственно с третьим и четвертым выходами дешифратора, а вторые входы подключены к выходу входного блока, соединенного первой и второй группами входов с группой информационных выходов объекта управления и с группой адресных выходов программного блока, а также к выходу блока оперативной памяти, выход элемента И-ИЛИ подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с определенным выходом программного блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ связан с первым входом третьего элемента И, соединенного вторым входом с соответствующим выходом блока синхронизации, а выходом с управляющим входом ячейки памяти, а ее информационный вход связан с выходом элемента ИЛИ, второй вход которого подключен к выходу пятого элемента И, второй вход последнего соединен с определенной шиной программного блока, первый вход пятого элемента И подключен к выходу элемента НЕ, а вход последнего связан с вторым входом четвертого элемента И с соответствующей шиной программного блока, первый вход четвертого элемента И подключен к инверсному выходу ячейки памяти, а его выход соединен с первым входом элемента ИЛИ, прямой выход ячейки памяти связан с информационными входами выходного блока и блока оперативной памяти, первые входы первого и второго элементов И подключены к первому и второму выходам дешифратора, их вторые входы объединены и связаны с соответствующим выходом блока синхронизации, а выходы соединены с соответствующими входами выходного блока и блока оперативной памяти для управления записью информации, многоканальный операционный блок, содержащий управляемый элемент, девять элементов И, семь элементов ИЛИ, первый и второй дешифраторы, управляемую ячейку памяти и "n" параллельно работающих логических каналов, имеющих одинаковую структуру, каждый их которых содержит внутри самого себя элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй и третий элементы И, первый и второй элементы ИЛИ, первый и второй счетные триггеры, при этом в каждом логическом канале многоканального операционного блока выход логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ связан с первым входом первого элемента ИЛИ, второй вход которого подключен к первому входу первого элемента И и к выходу второго элемента И, а выход соединен с первым входом третьего элемента И, выход последнего связан со счетным входом первого счетного триггера, выход которого подключен к второму входу, первого элемента И и к счетному входу второго счетного триггера, выход последнего соединен с первым входом второго элемента ИЛИ, второй вход которого подключен к выходу первого элемента И, при этом внутри многоканального операционного блока, выход первого элемента ИЛИ связан с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ логических каналов, первый и второй входы первого элемента ИЛИ связаны соответственно с выходами первого и второго элементов И, причем два входа первого элемента И подключены к одному из выходов второго дешифратора и выходу третьего элемента ИЛИ, входы которого соединены с двумя соответствующими выходами первого дешифратора, первый вход второго элемента И связан с одним из входов третьего элемента ИЛИ и с определенным выходом первого дешифратора, второй вход второго элемента И подключен к выводу седьмого элемента И, первый и второй входы второго элемента ИЛИ подключены к выходам шестого и седьмого элементов И, а третий вход к выходу третьего элемента И, входы которого соединены с соответствующим выходом второго дешифратора и с логической "1", первые входы шестого и седьмого элементов И подключены к соответствующим выходам второго дешифратора, а вторые входы соответственно к прямому и инверсному выходам ячейки памяти, информационный вход которой соединен с выходом второго элемента ИЛИ последнего логического канала, а управляющий вход управляемой ячейки памяти связан с выходом четвертого элемента И, первый вход которого подключен, вместе с первыми входами вторых элементов И всех логических каналов, к соответствующему выходу первого дешифратора, второй вход четвертого элемента И, вместе с вторыми входами третьих элементов И всех логических каналов соединены с определенным выходом блока синхронизации, а третий вход четвертого элемента И связан с определенным выходом второго дешифратора, в многоканальном операционном блоке управляющий вход управляемого элемента соединен с определенным выходом программного блока и с первым входом пятого элемента ИЛИ, выход последнего подключен к первому входу девятого элемента И, в коммутационно-вычислительном блоке, первые входы третьего и четвертого элементов И элемента И-ИЛИ соответствующим образом подключены к определенным выходам первого дешифратора, а вторые входы связаны соответственно с выходом управляемого элемента И с инверсным выходом второго счетного триггера последнего логического канала в многоканальном операционном блоке, входы первого и второго дешифраторов подключены к командным шинам программного блока, выход второго элемента ИЛИ первого логического канала соединен с вторым входом второго элемента И второго логического канала, выход второго момента ИЛИ второго логического канала связан с вторым входом второго элемента И третьего логического канала и т.д. до последнего логического канала, второй вход второго элемента И первого логического канала подключен к выходу второго элемента ИЛИ многоканального операционного блока, где инверсный выход управляемой ячейки памяти соединен с соответствующим входом выходного блока, второй вход пятого элемента ИЛИ соединен с одной из общих шин системы связи, передающей первый разряд кодового слова, второй вход девятого элемента И связан с выходом шестого элемента ИЛИ, входы восьмого элемента И соединены с соответствующими выходами первого дешифратора и блока синхронизации, а выход связан с первым входом четвертого элемента ИЛИ, выход последнего соединен с входами сброса в "0" вторых счетных триггеров всех логических каналов, входы пятого элемента И подключены к определенным выходам программного блока и блока синхронизации, а выход соединен с вторым входом четвертого элемента ИЛИ и с входами сброса в "0" первых счетных триггеров всех логических каналов, также систему связи, которая охватывает соответствующие блоки и содержит первый и второй электронные ключи, общие шины, логический элемент, в многоканальном операционном блоке имеются шестой и седьмой элементы ИЛИ, элемента НЕ и электронный выключатель, а в каждом логическом канале имеются четвертый элемент И, модуль сдвига разрядов /МСР/ и модуль реализации логических функций /МРФ/, модули МСР1 имеются во всех каналах, кроме первого и последнего и реализуют логические функции (1) и (2), имеют шесть входов и два выхода, из которых первые входы модулей MCP1 всех логических каналов, кроме первого и последнего, объединены и связаны с выходом элемента НЕ многоканального операционного блока, остальные входы модулей МСР1 соединены соответственно с двумя определенными выходами программного блока, с выходами двух первых счетных триггеров данного и последующего каналов, а выходы модуля МСР1 подключены соответственно к третьему и четвертому входам первых элементов ИЛИ данного и последующего канала, модуль МСР2 первого канала имеет шесть входов, три выхода, реализует булевы функции (3), (4), (5), два выхода модуля МСР2 связаны соответственно с третьим и четвертым входами первого элемента ИЛИ первого канала, а третий выход модуля МСР2 соединен с четвертым входом первого элемента ИЛИ второго логического канала, входы модуля МСР2 подключены соответственно к выходу элемента НЕ многоканального операционного блока, к двум определенным выходам программного блока и к выходам двух первых счетных триггеров первого и второго логических каналов, модуль МСР3 последнего логического канала имеет один выход, четыре входа, реализует булеву функцию (6), выход модуля МСР3 соединен с третьим входом первого элемента ИЛИ последнего канала, а входы МСР3 связаны соответственно с выходом элемента НЕ многоканального операционного блока, с одним из выходов программного блока и с выходом первого счетного триггера последнего логического канала, модули МРФ в каждом логическом канале реализуют одинаковые булевы функции (7), входы модуля МРФ в каждом логическом канале подключены соответственно к выходам первого и второго счетных триггеров внутри каждого логического канала и к двум определенным выходам программного блока, а выходы модулей МРФ являются выходами соответствующих, логических каналов и соединены в многоканальном операционном блоке с входами, управляемого элемента и с входами информации электронного выключателя, управляющий вход которого объединен с входом элемента НЕ и связан с выходом седьмого элемента ИЛИ, два входа которого и два входа шестого элемента ИЛИ подключены к соответствующим четырем выходам первого дешифратора, выход девятого элемента И соединен с первыми входами четвертых элементов И в каждом логическом канале, вторые входы четвертых элементов И каждого логического канала вместе с информационными выходами электронного выключателя многоканального операционного блока связаны с общими шинами системы связи, а выходы четвертых элементов И в каждом логическом канале соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, общие шины также подключены к выходам первого и второго электронных ключей системы связи, и к определенным входам блока оперативной памяти и выходного блока, входы первого и второго электронных ключей связаны с многоразрядными выходами входного блока и блока оперативной памяти, управляющие входы первого и второго электронных ключей, блока оперативной памяти и выходного блока соединены с соответствующими выходами логического элемента, три входа которого объединены с соответствующими тремя входами первого дешифратора многоканального операционного блока и связаны с определенными выходами программного блока, шестые входы модулей МСР1 и МСР2 и четвертый вход модуля МСР3 объединены и связаны с определенным выходом первого дешифратора многоканального операционного блока, дополнительные две шины управления, выходящие из программного блока, блок условных переходов, содержащий первые и вторые шины, счетчики импульсов, например один, несколько рядов ячеек памяти, например два ряда, соответствующее число электронных ключей, например четыре, модуль управления, имеющий, например, девять входов и восемь выходов, причем первые шины связаны с адресными шинами программного блока, с соответствующими входами счетчика импульсов, первого и второго рядов ячеек памяти, с входами четвертого электронного ключа и с тремя входами модуля управления, вторые шины в блоке условных переходов соединены с соответствующими выходами четырех электронных ключей и с определенными входами, определяющими адреса источников и приемников информации во входном блоке, блоке оперативной памяти и выходном блоке, четвертый и третий входы модуля управления подключены к соответствующим командным шинам программного блока, еще два входа модуля управления связаны соответственно с двумя дополнительными шинами управления, восьмой и девятый входы модуля управления соединены с соответствующими выходами коммутационно-вычислительного блока и блока синхронизации, в блоке условного перехода три выхода модуля управления подключены к входам управления записью двоичного кода соответственно счетчика импульсов, первого и второго рядов ячеек памяти, четвертый, пятый, а также шестой выходы модуля управления связаны с входами включения трех электронных ключей, седьмой выход модуля управления блока условных переходов соединен со счетным входом счетчика импульсов блока условных переходов, вторая и первая дополнительные шины управления программного блока связаны с блокировочным входом второго дешифратора многоканального операционного блока и с входом управления четвертого электронного ключа в имеющемся блоке условных переходов и вторые шины в блоке условных переходов, соединены с соответствующими входами электронного ключа в счетчике программного блока, еще введен блок подпрограмм, содержащий первый и второй электронные ключи, двоичный счетчик импульсов, первый и второй элементы И, управляемый триггер, третий элемент И, модуль памяти, причем информационные входы первого электронного ключа соединены с соответствующими адресными выходами /шинами/ программного блока, вход управления первого электронного ключа связан с выходом первого элемента И, входы которого подключены к дополнительной шине программного блока и к определенному выходу блока синхронизации, выходы первого электронного ключа соединены с установочными входами счетчика импульсов; счетный вход, который связан с выходом второго элемента И, входы последнего подключены к выходу блока синхронизации и к прямому выходу управляемого триггера, инверсный выход последнего соединен с управляющим входом электронного ключа программного блока и с первым входом третьего элемента И, второй вход которого связан с соответствующим выходом блока синхронизации, выход третьего элемента И подключен к счетному входу счетчика импульсов программного блока, выходы двоичного счетчика импульсов соединены с входами модуля памяти, выходы которого связаны соответственно с информационными входами управляемого триггера и второго электронного ключа, управляющий ввод последнего подключен к прямому выходу управляемого триггера, управляющий вход которого связан с соответствующим выходом блока синхронизации, выходы второго электронного ключа блока подпрограмм подключены к соответствующим командным и адресным выходам /шинам/ электронного ключа программного блока, в коммутационно-вычислительный блок введены элемент И-НЕ и шестой элемент И, а в счетчик программного блока введены второй ключ, элементы И и ИЛИ, также блок прерывания, содержащий элемента Н, триггеры приема прерываний, модуль выбора очередности прерываний, который реализует булевы функции

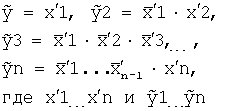

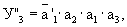

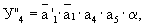

являются входными и выходными сигналами, поступающими на соответствующие входы и выходы модуля выбора очередности прерываний, шифратор, постоянное запоминающее устройство ПЗУ, электронный ключ, логические элементы И и ИЛИ, причем на информационные и управляющие входы триггеров приема сигналов прерываний поступают, соответственно, сигналы запроса на прерывание от определенных датчиков и сигнал с соответствующего выхода блока синхронизации, а выходы указанных триггеров соединены с  входами модуля выбора очередности прерываний, выходы которого

входами модуля выбора очередности прерываний, выходы которого  связаны с входами шифратора, выходы последнего подключены к входам элемента ИЛИ и к входам ПЗУ, выходы которого соединены с информационными входами электронного ключа, вход управления последнего связан с выходом элемента И, первый и второй входы которого связаны с выходом элемента ИЛИ и с соответствующим выходом блока синхронизации, третий вход элемента И связан с выходом элемента НЕ, вход которого соединен с введенной шиной, многоразрядная ячейка памяти и многоразрядный электронный ключ, а в программный блок введены еще две шины управления, при этом информационные и управляющий входы многоразрядной ячейки памяти соединены соответственно с общими шинами и с первой из двух введенных шин управления, а выходы многоразрядной ячейки памяти подключены к информационным входам многоразрядного электронного ключа, вход управления которого соединен через вторую введенную шину с определенным выходом программного блока и с вторым входом управления электронным ключом программного блока, выходы многоразрядного электронного ключа связаны с адресными шинам.

связаны с входами шифратора, выходы последнего подключены к входам элемента ИЛИ и к входам ПЗУ, выходы которого соединены с информационными входами электронного ключа, вход управления последнего связан с выходом элемента И, первый и второй входы которого связаны с выходом элемента ИЛИ и с соответствующим выходом блока синхронизации, третий вход элемента И связан с выходом элемента НЕ, вход которого соединен с введенной шиной, многоразрядная ячейка памяти и многоразрядный электронный ключ, а в программный блок введены еще две шины управления, при этом информационные и управляющий входы многоразрядной ячейки памяти соединены соответственно с общими шинами и с первой из двух введенных шин управления, а выходы многоразрядной ячейки памяти подключены к информационным входам многоразрядного электронного ключа, вход управления которого соединен через вторую введенную шину с определенным выходом программного блока и с вторым входом управления электронным ключом программного блока, выходы многоразрядного электронного ключа связаны с адресными шинам.

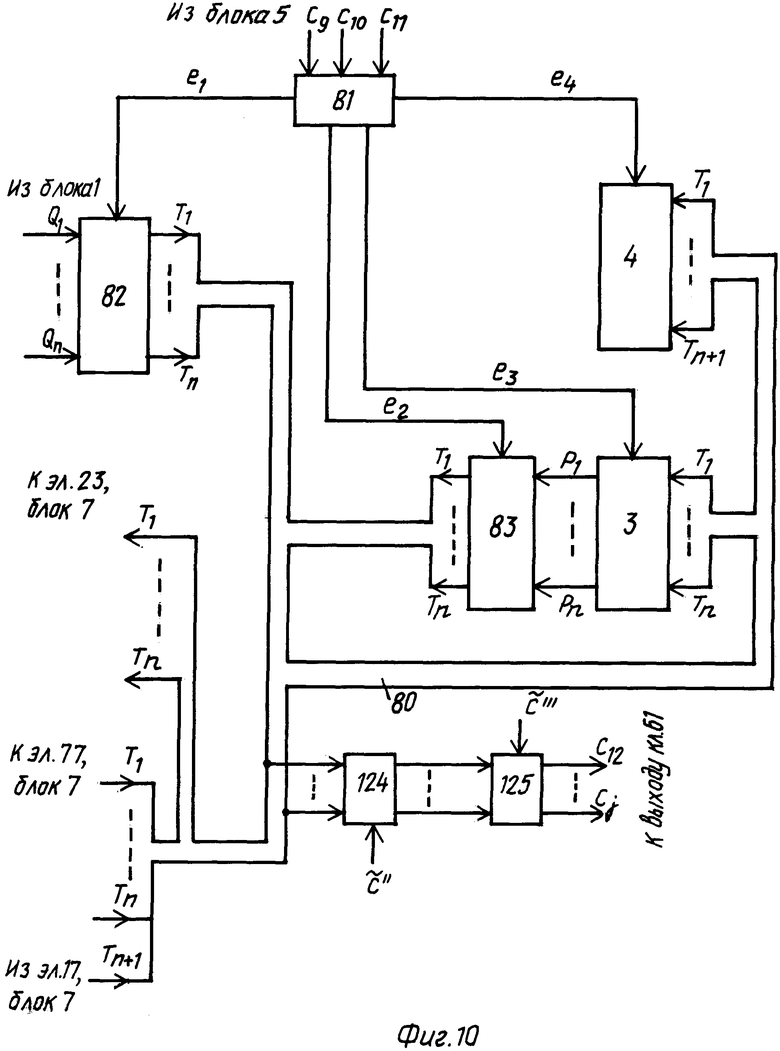

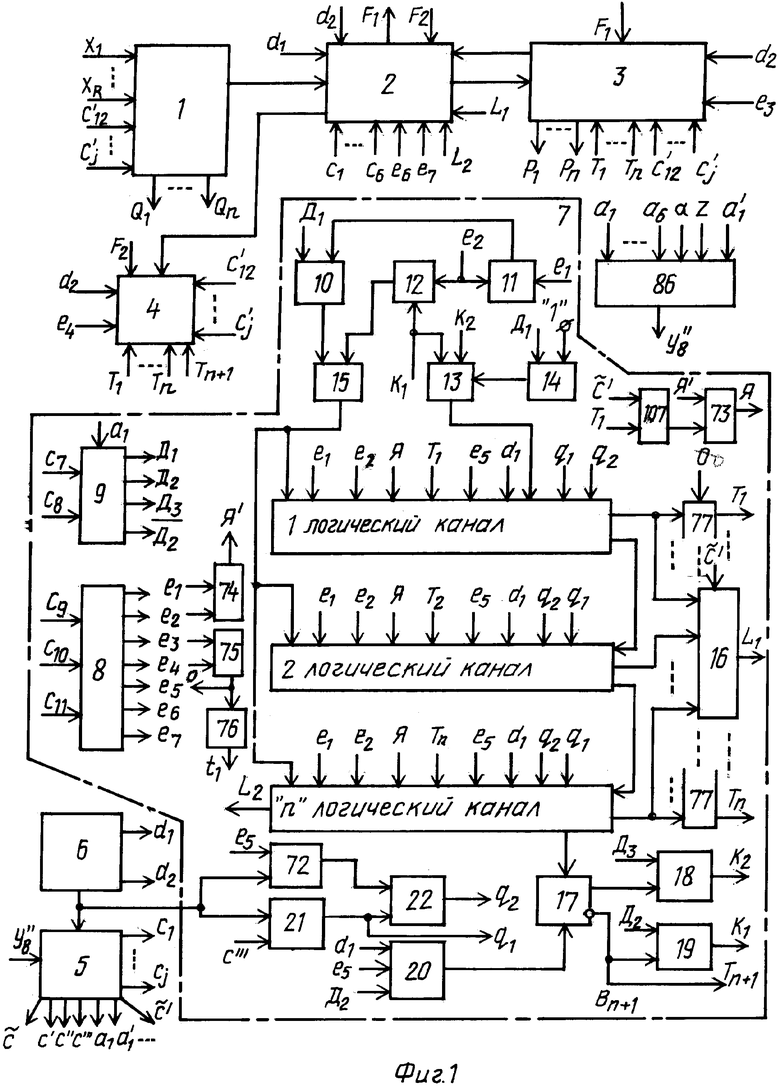

Устройство состоит из изображенных на фиг.1 входного блока 1, одна группа входов которого подключена к дискретным датчикам и источникам двоичного кода /на схеме не показаны/ Х1...ХR, а вторая группа входов соединена с адресными динами С12...Сj, связанного с коммутационно-вычислительным блоком 2, подключенным к блоку оперативной памяти 3, выходному блоку 4, программному блоку 5, блоку синхронизации 6, выход которого соединен с многоканальным операционным блоком 7, содержащим первый и второй дешифраторы 8 и 9, последний связан с первым входом первого элемента И 10, подключенным вторым входом к выходу третьего элемента ИЛИ 11, соединенному своим входом с первым входом второго элемента И 12, подключенному вторым входом, через второй элемент ИЛИ 13 к третьему элементу И 14, а выходом к первому элементу ИЛИ 15, выход которого связан с соответствующими входами всех логических каналов из "n", пятый элемент ИЛИ 107, управляемый элемент 16, управляемую ячейку памяти 17, шестой элемент И 18, седьмой элемент И 19, четвертый элемент И 20, пятый элемент И 21, четвертый элемент ИЛИ 22, восьмой 72 и девятый 73 элементы И, шестой элемент ИЛИ 74, седьмой элемент ИЛИ 75, элемента НЕ 76, электронный выключатель 77 и изображенных на фиг.10 общих шин 80, логического элемента /дешифратора/ 81, два выхода которого связаны с первым электронным ключом 82 и вторым электронным ключом 83 и управляют их работой, а два других выхода логического элемента 81 соединены с соответствующими входами блока оперативной памяти и выходного блока, блока условных переходов 86, блока подпрограмм 97, е1...е7, D1...D3,  выходы элементов 8, 9. Управляемый элемент 16 реализует функции ИЛИ, либо исключающее ИЛИ.

выходы элементов 8, 9. Управляемый элемент 16 реализует функции ИЛИ, либо исключающее ИЛИ.

Два выхода элемента 81, связанных с входами ключей 82 и 83 обозначены через е1 и е2 соответственно, а два других выхода элемента 81, связанных с блоками 3 и 4 обозначены соответственно через е3 и е4. Значения сигналов е1...е4 на выходе элемента 81 аналогичны значениям сигналов е1...е4 на выходах дешифратора 8 в блока 7, соответственно. Одновременно активизируется только один сигнал.

Электронный выключатель 77 в блоке 7, ключи 82 и 83, элемент 81 и общие шины 80 введены для организации обмена информацией по общим шинам 80, между блоками 1, 3, 4 и блоком 7 в обе стороны. При активизации сигнала е1 соответственно на выходах элемента 81 и дешифратора 8 блока 7 ключ 82 пропускает значение кода Q1...Qn с выходов входного блока 1 на входы логических каналов в блоке 7 по общим динам 80. При этом выходы /сигналы/ e2...e4 не активизированы, выключатель 77 в блоке 7 и ключ 83 закрыты и на их выходах присутствует высокий импеданс сопротивления. В случае активизации сигнала /выходов/ е2 ключ 83 пропускает код Р1...Рn с выходов блока 3 на входы логических каналов в блоке 7 по общим шинам 80. При этом ключ 82 и выключатель 77 в блоке 7 закрыты и на их выходах имеется высокий импеданс сопротивления. При активизации е3 либо е4 активизируется выход элемента ИЛИ 75 и выключатель 77 в блоке 7 пропускает значение кода В1...Вn с выходов логических каналов на ряды ячеек памяти соответственно в блок 3 либо в блок 4, а на выходах ключей 82 и 83 присутствует высокий импеданс сопротивления.  - командные сигналы /шины/ на выходах блока 5, управляющие блоками 2, 7, 86, 97. c'12...c'j - адресные команды /шины/, определяющие адреса источников и приемников информации в блоках 1, 3, 4, идут с выходов блока 86.

- командные сигналы /шины/ на выходах блока 5, управляющие блоками 2, 7, 86, 97. c'12...c'j - адресные команды /шины/, определяющие адреса источников и приемников информации в блоках 1, 3, 4, идут с выходов блока 86.

Xk+1...XR - входные дискретные сигналы от датчиков /кнопки, путевые выключатели и т.д./. В1...Вn - выходы логических каналов.

Х1...Хn, ..., Xm...Xk - многоразрядные двоичные коды /сигналы/, например с аналого-цифровых преобразователей, где левые разряды являются младшими, Т1...Тn+1 - информационные данные на общих шинах 80.

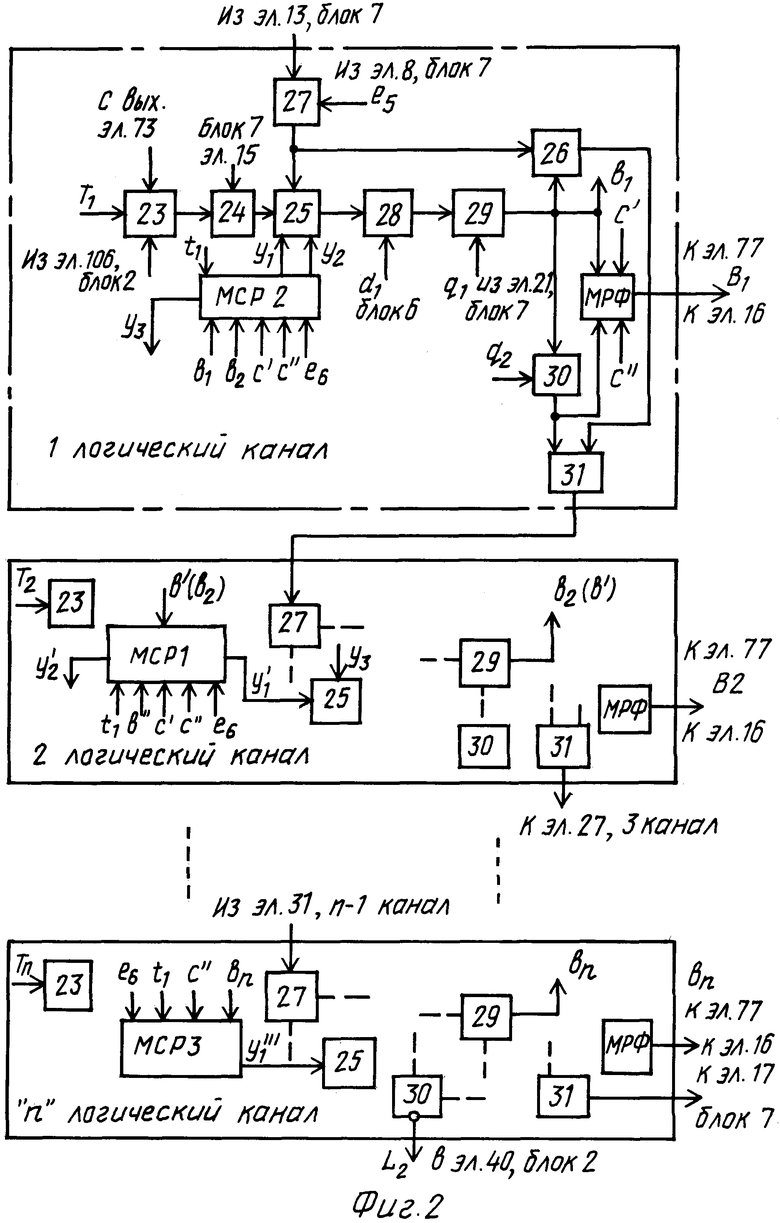

Входы блоков, каналов и элементов указаны входящими стрелками. На фиг.2 изображена структура логических каналов, входящих в многоканальный операционный блок 7. Каждый из "n" логических каналов состоит из четвертого элемента И 23, связанного выходом с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24, выход которого соединен с первым входом первого элемента ИЛИ 25, второй вход последнего подключен к первому входу первого элемента И 26 к выходу второго элемента И 27, а выход соединен с входом третьего элемента И 28, выход которого связан с счетным входом первого счетного триггера 29, вход которого связан со счетным входом второго счетного триггера 30, к выходу последнего подключен первый вход второго элемента ИЛИ 31, второй вход этого элемента связан с выходом элемента И 26, модуля сдвига разрядов двоичного кода МСР2 для первого канала, модуля сдвига разрядов МСР3 для последнего канала и модулей сдвига разрядов МСР1 для остальных каналов, модуля реализуемой функции МРФ для вычисления различных логических функций поразрядно от двух или трех кодов, поочередно подаваемых на входы логических каналов.

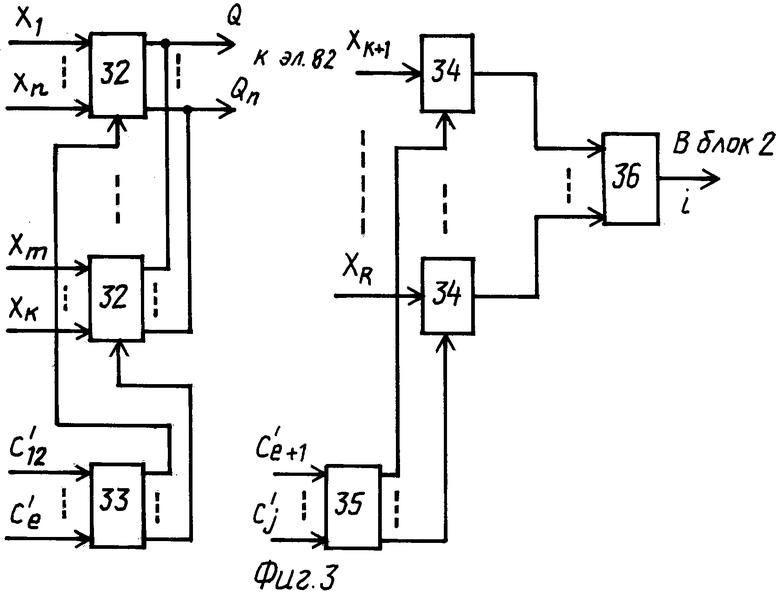

Пример входного блока 1 представлен на фиг.3 и содержит ряд электронных ключей 32, на входы которых поступают разряды двоичных кодов Х1...Хn...Xm...Xk, и которые поочередно, по соответствующему сигналу первого дешифратора 33, пропускают определенный двоичный код на выходы Q1...Qn в зависимости от значений адресных команд С12...Се, элементы и 34, на первые входы которых поступают биты информационных сигналов Xk+1...ХR вторые входы элементов И34 подключены к выходам второго дешифратора 35 и в зависимости от значений адресных команд Се+1...Сj, при помощи активизации определенного выхода дешифратора 35, соответствующий бит информации появляется на выходе элемента ИЛИ 36.

Пример коммутационно-вычислительного блока 2 представлен на фиг.4, он состоит из дешифратора 37, подключенного входами к блоку программ 5, первыми двумя выходами дешифратор 37 соединен с входами первого и второго элементов И 38 и И 39, а вторыми двумя выходами к входам элемента 2-2-2-2И-4 ИЛИ 40, выход которого соединен с входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41, выход последнего связан с входом третьего элемента И42, подключенного выходом к управляющему входу ячейки памяти 43, информационный вход которой соединен с выходом элемента ИЛИ 44, первый вход этого элемента связан с выходом четвертого элемента И 45, а второй вход подключен к выходу пятого элемента И 46, первый вход которого соединен с выходом элемента НЕ 47, элемента И-НЕ 106, шестого элемента И 108, со своими связями.

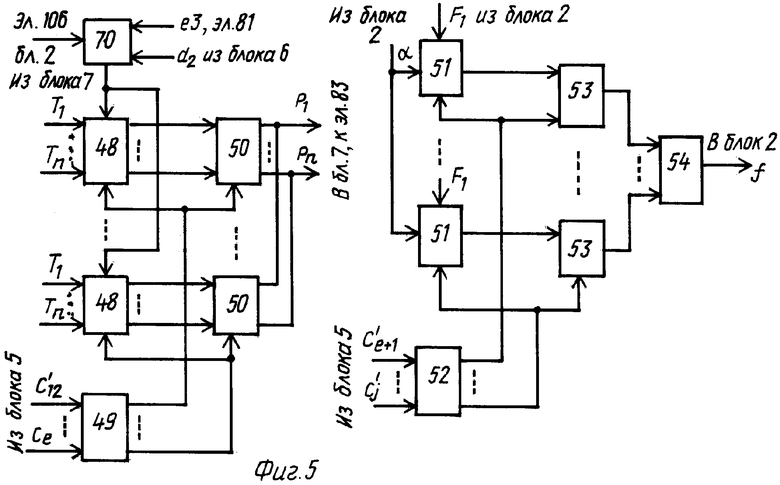

Пример блока оперативной памяти 3 представлен на фиг.5 и он содержит ряды ячеек памяти 48, в один из этих рядов ячеек памяти записываются значения двоичного кода Т1...Тn, поступающие с выходов, модулей МРФ, через выключатель 77 блока 7, по импульсу d2 и команде е3, поступающих на входы первого элемента И 70 из блоков 6 и 7 и выхода элемента 81, формируя импульс разрешения запись в ряды ячеек памяти 48. Считывание двоичного кода с выходов одного из рядов ячеек памяти 48 осуществляется электронными ключами 50 команде с выхода дешифратора 49, в зависимости от значений адресов С'12...С'е, ряд однобитовых ячеек памяти 51, куда записываются результаты промежуточных вычислений булевых функций в блоке 2, по команде из блока 2 и по адресу, определяемому выходом второго дешифратора 52 в соответствии с адресными командами С′е+1...С′j, считывание из ячеек памяти 51 происходит через элементы И 53 и элемент ИЛИ 54, по адресу, определяемому выходом второго дешифратора 52. Запись и считывание происходит на разных тактах.

Пример структуры выходного блока 4 представлен на фиг.6, он состоит из рядов ячеек памяти 55, куда записываются значения двоичных кодов с выходов модулей МРФ логических каналов, через выключатель 77 блока 7, по команде с выхода элемента И 71, на вход которого поступают сигналы d2 и е4 из блока 6 и элемента 81 и по адресам, определяемым выходами дешифратора 56, значения В′1...В′n на выходах рядов ячеек памяти 55 могут поступать на входы цифроаналоговых преобразователей и далее в виде аналоговых сигналов, например, на входы электроисполнительных механизмов, из ряда ячеек памяти 57, в которые записываются результаты вычислений рулевых функций в виде бит информации из блока 2 по команде F2, также из блока 2 и по адресу, определяемому выходом второго дешифратора 58, в зависимости от значений С′е+1...С′j.

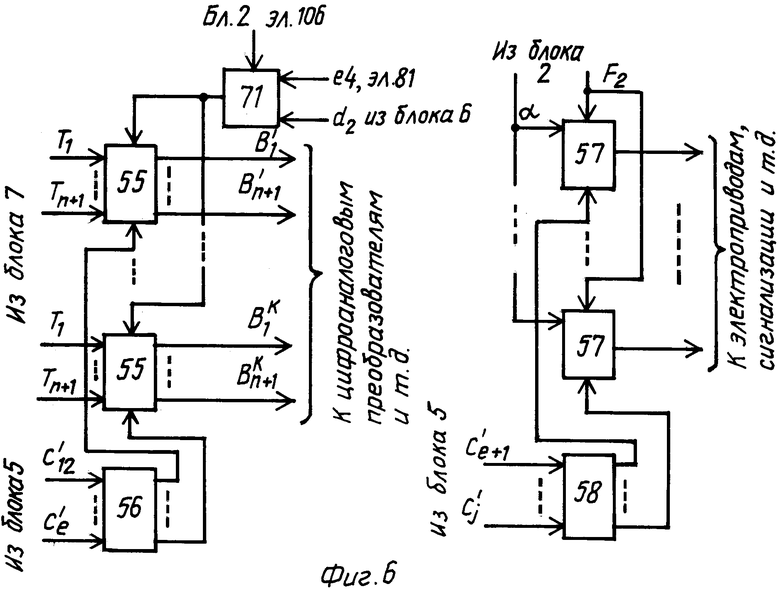

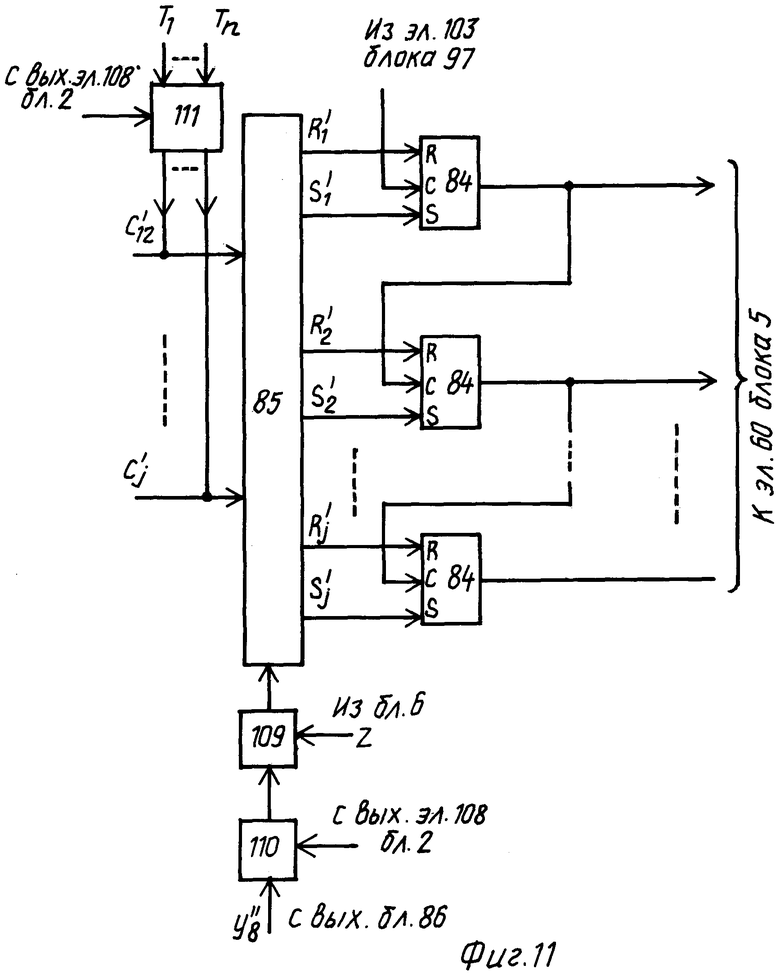

Программный блок 5 /фиг.7/ содержит счетчик импульсов 59, на счетный вход которого поступают сигналы с выхода блока 97,постоянное запоминающее устройство с ячейками памяти /ПЗУ/ 60, для записи программы и ее считывания по адресам на выходах счетчика 59, связанных с входами ПЗУ 60, программа считывается с выходов ПЗУ 60, соединенных с входами электронного ключа 61, выходы которого есть выходы блока 5, содержат командные /управляющие/  и адресные с12...сj шины и связаны с выходом ключа 105 блока 97. Счетчик импульсов 59 содержит счетные триггеры 84, связанные в многоразрядный двоичный счетчик, их прямые выходы являются выходами счетчика 59, счетный вход первого триггера 84 служит счетным входом счетчика 59, a R и S входы счетных триггеров 84 подключены к выходам электронного ключа 85, входящего как и элементы ИЛИ 110 и И 109 в состав счетчика 59. Информационные входы ключа 85 связаны с вторыми шинами блока условных переходов 86 и, через второй ключ 111, с общими шинами 80, а вход включения ключа 85 соединен, через элемент И 109 и элемент ИЛИ 110 с выходом модуля управления 96 блока 86 и с выходом шестого элемента И 108 блока 2, Взаимосвязь входов С′12...С′j, электронного ключа 85 с его выходами представлена ниже:

и адресные с12...сj шины и связаны с выходом ключа 105 блока 97. Счетчик импульсов 59 содержит счетные триггеры 84, связанные в многоразрядный двоичный счетчик, их прямые выходы являются выходами счетчика 59, счетный вход первого триггера 84 служит счетным входом счетчика 59, a R и S входы счетных триггеров 84 подключены к выходам электронного ключа 85, входящего как и элементы ИЛИ 110 и И 109 в состав счетчика 59. Информационные входы ключа 85 связаны с вторыми шинами блока условных переходов 86 и, через второй ключ 111, с общими шинами 80, а вход включения ключа 85 соединен, через элемент И 109 и элемент ИЛИ 110 с выходом модуля управления 96 блока 86 и с выходом шестого элемента И 108 блока 2, Взаимосвязь входов С′12...С′j, электронного ключа 85 с его выходами представлена ниже:

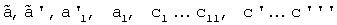

где R′1...R′j и S′1...S′j выходы электронного ключа, связанные соответственно с R и S входами счетных триггеров 84;

С′12...С′j значения кодов на вторых динах 90, блока 86;

значение выхода модуля управления 96, блока 86;

значение выхода модуля управления 96, блока 86;

является инверсией С. Счетчик импульсов 59 представлен схемой на фиг.11.

является инверсией С. Счетчик импульсов 59 представлен схемой на фиг.11.

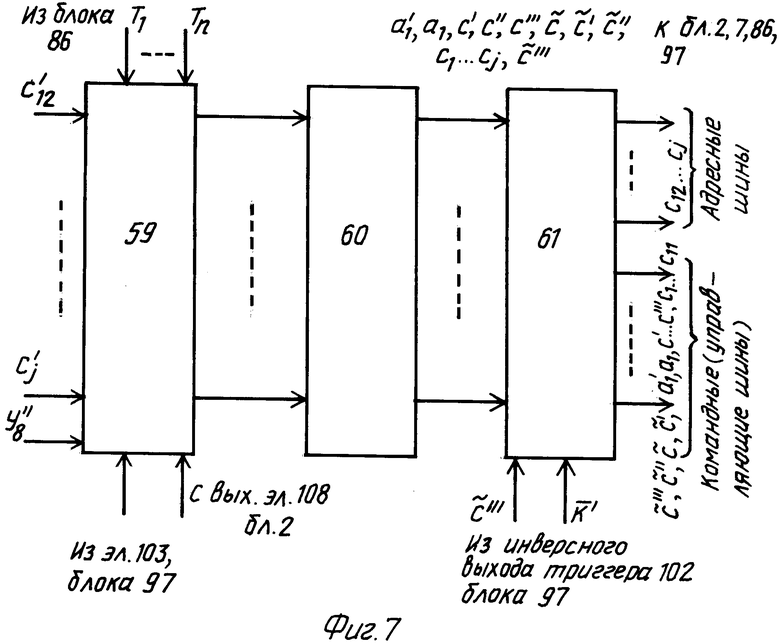

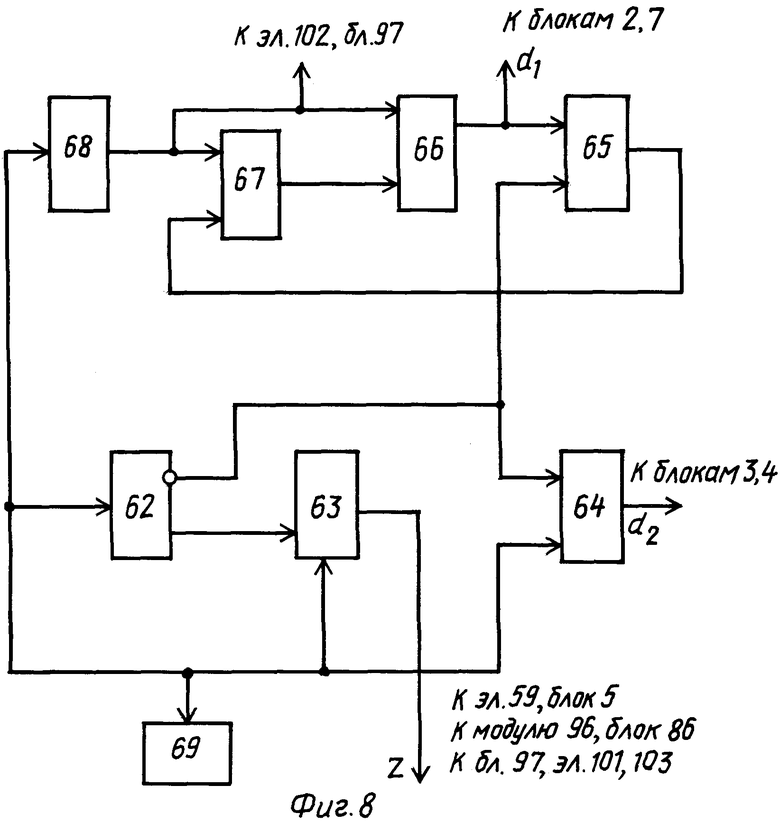

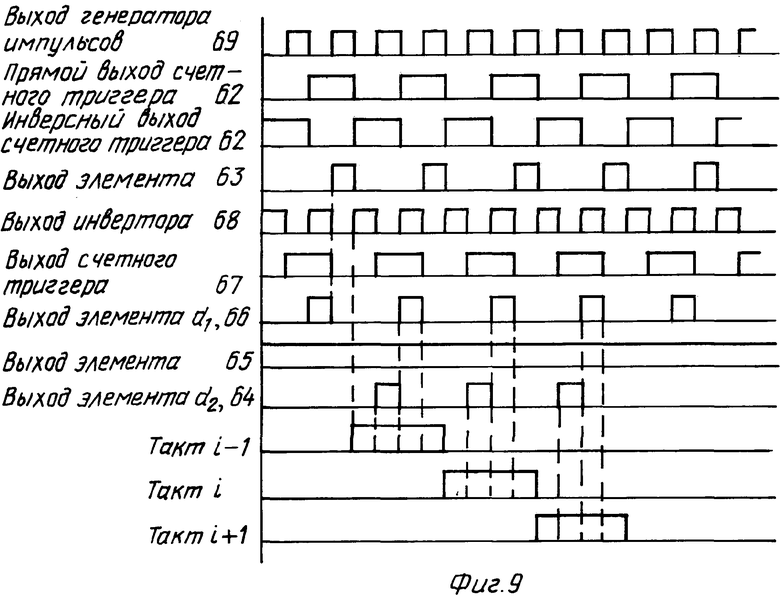

Пример блока синхронизации 6 представлен на фиг.8, он содержит первый счетный триггер 62, подключенный прямым выходом к элементу И 63, а инверсным выходом к первым входам элементов И 64 и И 65, второй вход последнего подключен к выходу элемента И 66, входы которого связаны с прямым выходом второго счетного триггера 67 и с выходом инвертора 68, вход последнего вместе с входом триггера 62 подключены к генератору прямоугольных импульсов 69. Работа блока 6 поясняется диаграммами на фиг.9.

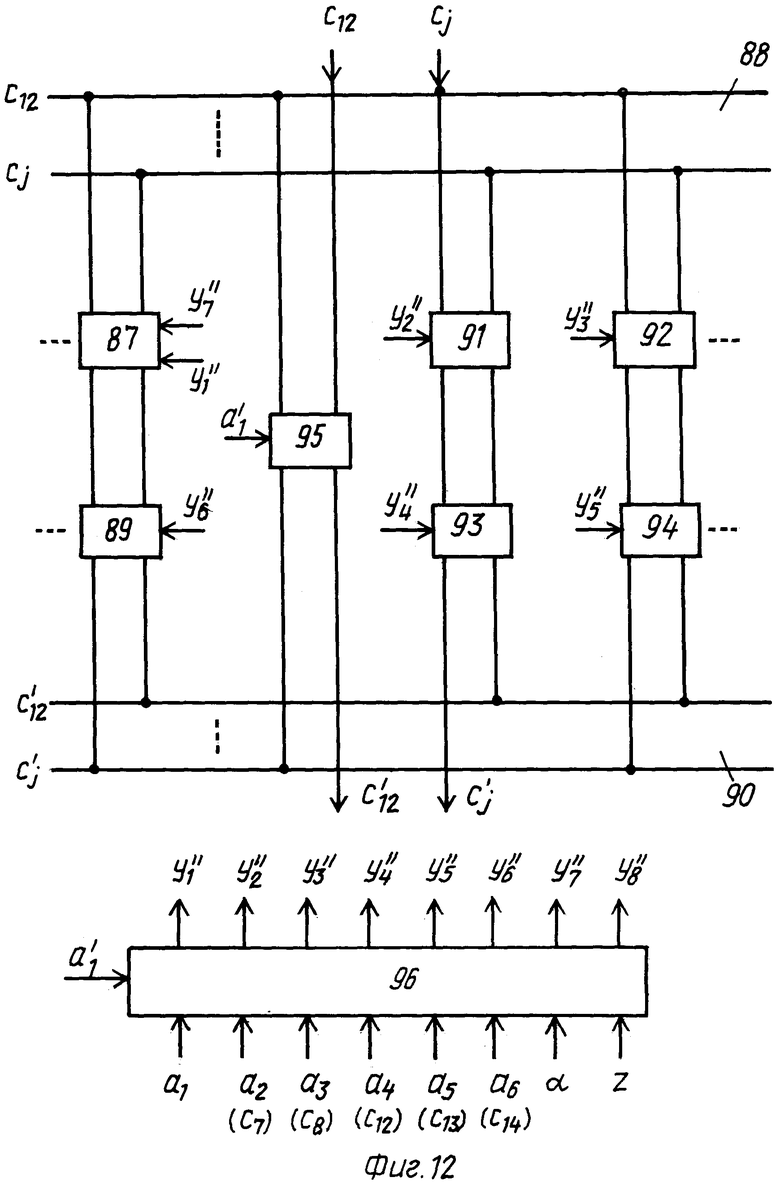

Блок условных переходов 86 представлен на фиг.12 и состоит из счетчика импульсов 87, имеющего установочные входы, связанные с первыми шинами 88, третьего электронного ключа 89, соединенного входами с выходами счетчика импульсов, а выходами со вторыми шинами 90 первого и второго рядов ячеек памяти 91 и 92, подключенных входами к первым шинам, а выходами к входам соответственно первого и второго рядов электронных ключей 93 и 94, выходы последних соединены с вторыми шинами, четвертого электронного ключа 95, связанного входами с первыми шинами, а выходами с вторыми шинами блока 86, модуля управления 96, входами соединенного с двумя дополнительными шинами управления, идущими из блока 5, а′1 и а1, а также с двумя командными шинами С7, С8, тремя адресными шинами С12, С13, С14 и с выходами блоков 2, 6, выходы модуля 96 связаны с входами управления счетчика 87, с двумя рядами ячеек памяти 91, 92, с тремя электронными ключами 89, 93, 94 и через элементы ИЛИ 110 и ИЛИ 109, с входом ключа 85.

В блоке 7, нижний выход дешифратора 9, есть инверсия выхода Д2. Оговоримся, что все триггеры и ячейки памяти срабатывают по заднему фронту импульсов, поступающих на их управляющие или счетные входы и перед началом работы устройства сброшены в "0".

Принцип работы блока 2 известен, он состоит в реализации булевых функций И, ИЛИ, НЕ, при С3=0, и функцию ИСКЛЮЧАЮЩЕЕ ИЛИ, при С3=1, последовательно по тактам, а также в управлении соответствующими процессами в блоках 3 и 4. Под активизацией выхода или сигнала подразумевается появление логической "1".

В приведенных, без блока 86, примерах работы устройства предполагалось, что электронный ключ 95 открыт и значения кодов С12...Сj и С′12...С′j совпадают при а′1=1.

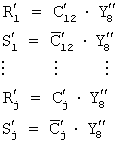

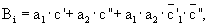

Структура модуля управления 96 представляет собой автомат без памяти и его аналитическую интерпретацию в виде булевых функций, связывающих его входы a′1, a1...a6, α и Z с его выходами Y′′1...Y′′8 дана ниже:

где a′1 - входной сигнал, поступающий, с первой дополнительной шины из блока 5, на вход модуля 96,

а1 - входной сигнал, поступающий по второй дополнительной шины из блока 5 на вход модуля 96,

а2, а3 - входные сигналы, поступающие по командным шинам С7, С8 в процессе работы модуля 96 в режиме записи информации в счетчик импульсов 87, или в ячейки памяти 91, 92,

а4, а5 - входные сигналы, поступающие, через шины 88, по адресным шинам, например С12, С13, в режиме считывания информации о выходов счетчика импульсов 87, ячеек памяти 91, 92, через электронные ключи 89, 93, 94,

а6 - входной сигнал, поступающий по адресной шине, например С14, и определяющий одно из условий записи /прибавления/ "1" в счетчик 87,

α - входной сигнал, поступающий с выхода триггера 43 блока 2,

Z - входной сигнал, идущий с выхода элемента 63 блока 6,

Y′′1, Y′′2, Y′′3 - выходные сигналы, поступающие на входы управления записью соответственно в счетчик 87 и в ячейки памяти 91, 92,

Y′′4, Y′′5, Y′′6 - выходные сигналы, поступающие на входы включения электронных ключей 89, 93, 94 в режиме считывания информации с выходов счетчика 87 и ячеек памяти 91, 92,

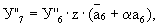

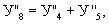

Y′′7 - выходной сигнал, поступающий на счетный вход счетчика 87

Y′′8 - выходной сигнал, поступающий через элементы, ИЛИ 110 и И 109, на вход включения электронного ключа 85, информационные входы которого связаны с шинами 90, а выходы с установочными входами счетных триггеров 84.

Одновременно, т.е. на одном такте, только один из выходов Y′′1...Y′′6 активизируется, принимая значение логической "1".

Отметим, что электронным ключом 95 в блоке 86 управляет сигнал, идущий по дополнительной шине управления а′1, имеющей связь с входом управления четвертого электронного ключа 95 и блоком 5.

При единичном значении сигнала на второй дополнительной шине управления а1 на выходах Д1, Д2, Д3 дешифратора 9 блока 7 имеются логические нули. Значение  на входе элемента 16, связанного с выходом блока 5, определяет реализуемую элементом 16 функцию, при

на входе элемента 16, связанного с выходом блока 5, определяет реализуемую элементом 16 функцию, при  реализуется функция ИЛИ.

реализуется функция ИЛИ.

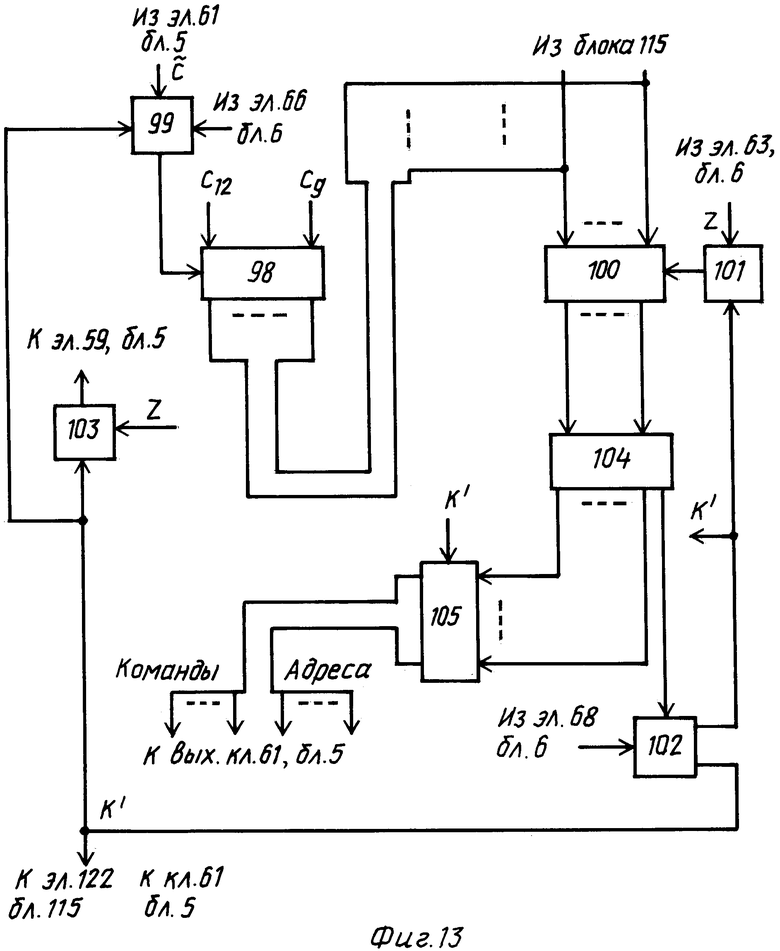

Блок подпрограмм 97, представленный схемой на фиг.13, содержит первый электронный ключ 98, двоичный счетчик импульсов 100, первый и второй элементы И 99 И 101, управляемый триггер 102, третий элемент И 103, модуль памяти 104, второй электронный ключ 105, причем информационные входы первого электронного ключа 98 соединены о соответствующими адресными выходами /шинами/ программного блока 5, вход управления первого электронного ключа 98 связан с выходом первого элемента И 99, входы которого подключены к дополнительной шине  блока 5, к инверсному выходу триггера 102, и к определенному выходу блока синхронизации, на котором появляется импульс в третьей четверти такта, выходы первого электронного ключа 98 соединены с установочными входами счетчика импульсов 100, счетный вход которого связан с выходом второго элемента И 101, входы последнего подключены к выходу блока синхронизации 6 и прямому выходу триггера 102, инверсный выход которого соединен с первым входом элемента И 103, второй вход последнего связан с соответствующим выходом блока синхронизации 6, выход третьего элемента И подключен к счетному входу счетчика импульсов 59 программного блока 5, выходы двоичного счетчика импульсов 100 соединены с входами модуля памяти 104, выходы которого связаны соответственно с информационными входами второго электронного ключа 105, управляющий вход последнего подключен к прямому выходу управляемого триггера 102 блока подпрограмм 97, инверсный выход управляемого триггера соединен и с управляющим входом электронного ключа 61 программного блока 5, управляющий и информационный входы управляемого триггера 102 связаны соответственно с выходами блока синхронизации 6 и с выходом модуля памяти 104, выходы второго электронного ключа 105 блока подпрограмм подключены к соответствующим выходам /шинам/ электронного ключа 61 блока 5. В отключенном состоянии ключи 61 и 105 имеют высокий импеданс сопротивления на своих выходах.

блока 5, к инверсному выходу триггера 102, и к определенному выходу блока синхронизации, на котором появляется импульс в третьей четверти такта, выходы первого электронного ключа 98 соединены с установочными входами счетчика импульсов 100, счетный вход которого связан с выходом второго элемента И 101, входы последнего подключены к выходу блока синхронизации 6 и прямому выходу триггера 102, инверсный выход которого соединен с первым входом элемента И 103, второй вход последнего связан с соответствующим выходом блока синхронизации 6, выход третьего элемента И подключен к счетному входу счетчика импульсов 59 программного блока 5, выходы двоичного счетчика импульсов 100 соединены с входами модуля памяти 104, выходы которого связаны соответственно с информационными входами второго электронного ключа 105, управляющий вход последнего подключен к прямому выходу управляемого триггера 102 блока подпрограмм 97, инверсный выход управляемого триггера соединен и с управляющим входом электронного ключа 61 программного блока 5, управляющий и информационный входы управляемого триггера 102 связаны соответственно с выходами блока синхронизации 6 и с выходом модуля памяти 104, выходы второго электронного ключа 105 блока подпрограмм подключены к соответствующим выходам /шинам/ электронного ключа 61 блока 5. В отключенном состоянии ключи 61 и 105 имеют высокий импеданс сопротивления на своих выходах.

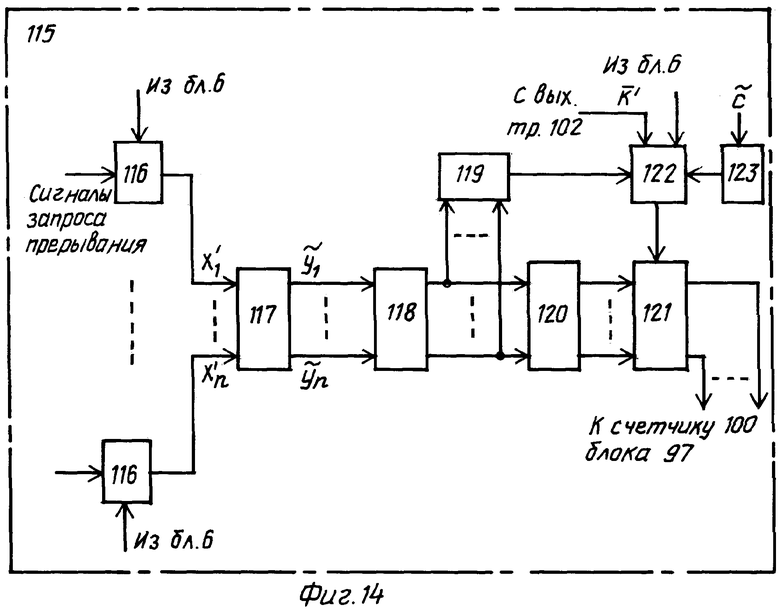

Блок прерываний 115 представлен на фиг.14 и содержит триггеры приема сигналов прерывания 116, выходы которого связаны с входами модуля выбора очередности прерываний 117, соединенного выходами с входами шифратора 118, подключенного своими выходами в входам элемента ИЛИ 119 и к входам постоянного запоминающего устройства, далее ПЗУ, 120, связанного выходами с входами электронного ключа 121, управляющий вход которого соединен с выходом элемента И 122, четыре входа последнего подключены к выходу элемента НЕ 123, вход которого связан с введенной шиной и соответствующим входом элементам И 99, к выходу элемента ИЛИ 119, к соответствующему выходу блока синхронизации и к инверсному выходу управляемого триггера 102 блока подпрограмм 97, входы управления триггеров 116 соединены с определенным выходом блока синхронизации, выходы электронного ключа 121 связаны с установочными входами счетчика импульсов 100 блока подпрограмм.

Модуль 117 является автоматом без памяти и реализует булевы функции

где  - входные сигналы, поступающие с выходов триггеров 116 на соответствующие входы модуля 117,

- входные сигналы, поступающие с выходов триггеров 116 на соответствующие входы модуля 117,  - сигналы формирующиеся на соответствующих выходах модуля 117.

- сигналы формирующиеся на соответствующих выходах модуля 117.

На информационные входы триггеров 116 поступают сигналы запроса на прерывание основной программы, записанной в блоке 5, от, например, аварийных датчиков, пульта управления и т.д.

Многоразрядная ячейка памяти 124 и многоразрядный электронный ключ 125 представлены на фиг.10, при этом информационные и управляющий входы ячейки 124 соединены с общими шинами Т1...Тn и с первой из двух введенных шин управления, а выходы связаны с информационными входами ключа 125, вход управления которого подключен к второй введенной шине управления, а выходы к адресным шинам на выходе ключа 61 блока 5.

Работа устройства состоит в вычислении булевых функций по битам в блоке 2, с одновременной реализацией операций с многоразрядными двоичными кодами в блоке 7 и при необходимости устройство обеспечивает совместную работу блоков 2 и 7, например в случае сравнения двух двоичных кодов. Устройство работает по тактам, сформированным в блоке 5.

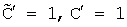

Работу устройства поясним на нескольких примерах. Примем, что  . Сравним два двоичных числа А1 и А2, при А1=А2 и для примера число А1 равно числу А2 и оба выражены двоичным кодом 11001011. Допустим число A1 находится в блоке 1 в виде Х1...Хn, где n=8, а число А2 хранится в блоке оперативной памяти 3 в значениях Р1...Рn, где n=8 и блок 7 имеет восемь логических каналов. Равенство чисел определим методом алгебраического сложения числа А1 и отрицательного числа А2, представленного в дополнительном коде, т.е. инвертировав его и прибавив "1" к младшему разряду. Примем, что А2 является инверсией А2, а С′=1 и С′′=1.

. Сравним два двоичных числа А1 и А2, при А1=А2 и для примера число А1 равно числу А2 и оба выражены двоичным кодом 11001011. Допустим число A1 находится в блоке 1 в виде Х1...Хn, где n=8, а число А2 хранится в блоке оперативной памяти 3 в значениях Р1...Рn, где n=8 и блок 7 имеет восемь логических каналов. Равенство чисел определим методом алгебраического сложения числа А1 и отрицательного числа А2, представленного в дополнительном коде, т.е. инвертировав его и прибавив "1" к младшему разряду. Примем, что А2 является инверсией А2, а С′=1 и С′′=1.

На первом такте значения Х1...Х8, при соответствующих значениях С4...Се, и e1=1 поступят в виде Q1...Q8 на входы T1...Tn элементов 23 всех каналов, из блока 1 в блок 7, где под действием команд С9...С11 дешифратор 8 блока 7 активизирует выход e1 и число А1, через элементы 23 всех каналов, при активизации выхода элемента ИЛИ 74, поступит на входы элементов 24 и при Д1=0, е2=0, d1=1, значение числа А1 запишется в счетные триггеры 29, т.к. К1=0 и К2=0, а′1=1.

На втором также, при соответствующих сигналах С4...Се и е2=1 в блоке 3 активизируется верхний выход дешифратора 49 и число А2 в виде значений Р1...Рn, с выхода электронного ключа 50 поступает на входы элемента 23 всех каналов блока 7 и при e2=1, Д1=1, e1=0, К1=0 и К2=0, значение инверсии числа А2 поступает на счетные входы счетных триггеров 29 всех каналов в третьей четверти такта при d1=1 и реализуется поразрядно функция ИСКЛЮЧАЮЩЕЕ ИЛИ для чисел А1 и  , при этом на выходах триггеров 29 всех каналов устанавливаются единичные значения.

, при этом на выходах триггеров 29 всех каналов устанавливаются единичные значения.

На третьем такте, для окончания перевода числа А2 в дополнительный код, под действием команд С7...С11 активизируется выход Д1 и выход е5 дешифраторов 9 и 8 блока 7 и логическая "1" с выхода элемента 14 через элементы ИЛИ 13 и И 27 первого канала поступит на второй и первый входы элементов ИЛИ 25 и И 26, на второй вход последнего поступает "1" с выхода триггера 29, при этом логическая "1" с выхода элемента И 26, через элемент ИЛИ 31 первого канала, появится на входе элемента И 27 второго канала и далее, через элементы И 27, И 26 и ИЛИ 31 последующих каналов, указанная логическая "1" появится на выходах элементов ИЛИ 31 всех каналов блока 7 и в третьей четверти такта при импульсе d1 все счетные триггеры 29 всех каналов переключатся в состояние логического "0" на выходе, т.е. мы получили результат разности двух равных чисел, при этом триггеры 30 всех каналов переключились в состояние "1" произошла запись информации с выхода триггера 30 последнего канала в ячейку памяти 17, по сигналу с выхода элемента И 20 блока 7.

На четвертом такте, при  , логический "0" с выхода элемента ИЛИ16, при соответствующих сигналах С9...С11 по команде е6 с выхода дешифратора 8 блока7, поступает, через элемент 40 на вход элемента 41 блока 2, где инвертируется при С1=1 и затем в третьей четверти такта, когда d1=1 и С2=1, а С3=0 единичное значение сигнала с выхода элемента ИЛИ 44 запишется в ячейку памяти 43 по команде с выхода элемента И 42.

, логический "0" с выхода элемента ИЛИ16, при соответствующих сигналах С9...С11 по команде е6 с выхода дешифратора 8 блока7, поступает, через элемент 40 на вход элемента 41 блока 2, где инвертируется при С1=1 и затем в третьей четверти такта, когда d1=1 и С2=1, а С3=0 единичное значение сигнала с выхода элемента ИЛИ 44 запишется в ячейку памяти 43 по команде с выхода элемента И 42.

На пятом такте логическая "1" с выхода ячейки 43 при определенных командах С4...С6, активизации нижнего выхода дешифратора 37 блока 2 и выхода элемента И39, в момент d2=1, запишется в определенную значениями Се+1...Сj ячейку памяти 57 выходного блока 4, как информация о том, что А1=А2.

Рассмотрим второй пример, когда А1<А2 и А1=11001011, а А2 равно 10011011. Учтем, что выход  дешифратора 9 связан с входом И 20, блока 7.

дешифратора 9 связан с входом И 20, блока 7.

На первом такте по аналогии с первым примером число А1 записывается в счетные триггеры 29 по разрядам в каждый канал блока 7.

На втором такте при е1=1, Д1=1 инверсия числа А2, т.е. 01100100 поступает на входы элементов И 28 и по импульсу а d1=1, в третьей четверти такта, единичные значения разрядов числа  меняют состояние счетных триггеров 29 на противоположное и на выходе триггеров 29 появляется результат, равный

меняют состояние счетных триггеров 29 на противоположное и на выходе триггеров 29 появляется результат, равный  , т.е. 10101111, при этом в втором канале счетный триггер 29 за два такта дважды поменял свое состояние с "0" в "1" и снова в "0", что привело к изменению состояния второго счетного триггера 30 с нулевого в единичное и фактически произошла фиксация факта образования переноса из второго разряда в третий разряд ИЛИ из второго канала в третий, с этой целью и были введены счетные триггеры 30 во все каналы блока 7.

, т.е. 10101111, при этом в втором канале счетный триггер 29 за два такта дважды поменял свое состояние с "0" в "1" и снова в "0", что привело к изменению состояния второго счетного триггера 30 с нулевого в единичное и фактически произошла фиксация факта образования переноса из второго разряда в третий разряд ИЛИ из второго канала в третий, с этой целью и были введены счетные триггеры 30 во все каналы блока 7.

На третьем такте по сигналам Д1 и е5 логическая "1" через элементы И 14, ИЛИ 13 и И 27 первого канала поступает на второй и первый входы элементов ИЛИ 25 и И 26 первого канала и с выхода последнего элемента И 26 через элемент ИЛИ 31 логическая "1" поступает на вход элемента 27 второго канала и далее на входы элементов ИЛИ 25 и И 26, с выхода элемента ИЛИ 31 логическая "1", как результат переноса, о котором говорилось выше /на втором такте/ поступила на вход элемента И 27 третьего канала и далее на входы элементов И 28 и И 26, с выхода последнего элемента логическая "1", через элемент ИЛИ 31 поступает на вход элемента И 27 четвертого канала и затем на входы И 26 и И 28, далее перенос не проходит, т.к. на выходах триггеров 29 и 30 логические нули. Таким образом элементы И 26 к ИЛИ 31 обеспечивают сквозной перенос из канала /разряда/ в канал /разряд/, когда перенос имеется, затем в третьей четверти такта при d1=1 происходит изменение состояний триггеров 29 в первых четырех каналах и на выходах всех триггеров 29 всех каналов устанавливается результат алгебраической суммы А1+/-А2/ в дополнительном коде 01011111, одновременно по сигналу с выхода элемента 20 произойдет запись информации /0/ с выхода триггера 30 последнего канала, через элемент ИЛИ 31 в ячейку памяти 17 блока 7, при этом нулевое значение выхода триггера 30 показывает, что А1<А2 и получен результат алгебраической суммы А1+/-А2/ в дополнительном коде. На этом же такте в блоке 2, при С1=1, С2=1, С3...С6 равными "0", через элементы И 46 и ИЛИ 44 на информационный вход ячейки 43 поступает логическая "1", которая при нулевых выходах дешифратора 37 записывается в ячейку 43 по сигналу, поступающему с выхода элемента 41, через элемент И 42 на управляющий вход ячейки 43, при d1=1.

На четвертом такте по сигналу с выхода дешифратора 8 блока 7 е7=1, значение L2=1, с инверсного выхода триггера 30 последнего канала поступает на выход элемента 40 блока 2 и затем при С1=1 на выходе элемента 41 находится "0" и значение ячейки памяти 43 не меняется, оставаясь "1".

На пятом такте при  значение L1=1 с выхода элемента ИЛИ16, при е6=1 поступит, через элемент 40, на вход элемента 41 и при С1=1 на выходе последнего будет "0" и единичное значение ячейки 43 не изменится, мы получили результат вычисления функции L2·L1, подтверждающий, что А1<А2.

значение L1=1 с выхода элемента ИЛИ16, при е6=1 поступит, через элемент 40, на вход элемента 41 и при С1=1 на выходе последнего будет "0" и единичное значение ячейки 43 не изменится, мы получили результат вычисления функции L2·L1, подтверждающий, что А1<А2.

На шестом такте результат вычисления функции L2·L1 с выхода ячейки 43 блока 2 при соответствующей команде с выхода дешифратора 37 и при d2=1, т.е. во второй четверти такта, по команде с выхода элемента И39 запишется в выходной блок 4, в одну из ячеек памяти по адресу Cе+1...Cj.

Дальше следовало бы описанным выше образом в блоке 2 вычислить функцию L1· и если бы А1>А2, то функция L1·

и если бы А1>А2, то функция L1· равнялась "1".

равнялась "1".

Вернемся к третьему такту, когда мы получили результат алгебраической суммы чисел А1 и -А2, в дополнительном коде и продолжим для нового примера, выполнения операций по решению задачи определения окончательного результата вычисления суммы А1+/-А2/.

Для этого на четвертом такте в блоке 7 полученный результат с выходов триггеров 29 всех каналов при С′=1 записывается в блок оперативной памяти 3 по сигналу с выхода элемента И 70 при е3=1 и d2=1, в ряд ячеек памяти, определенным значениями С12...Се и выходом дешифратора 49. Одновременно под действием сигнала q1=1 с выхода элемента И21, все счетные триггера всех каналов сбрасываются в "0", при этом на выходе элемента ИЛИ 22 имеется логическая "1" в виде импульса, т.к. С′′′=1.

На пятом такте записанная на предыдущем такте информация из блока 7 в блок 3, в соответствии с адресом С12...Сe, считывается из ряда электронных ключей 50 по сигналу с выхода дешифратора 49 и при активизации выхода е2 элемента 81 и дешифратора 8 блока 7, указанная информация через элементы 23 всех каналов поступает на входы элементов 24, где все разряды инвертируются под действием сигнала с выхода элемента ИЛИ 15, при Д2=1 и поступают, через элементы ИЛИ 25 при К1=1 на счетные входы триггеров 29, при этом единичные разряды меняют состояния триггеров 29, на выходах которых устанавливается инверсное значение указанной информации, т.е. 10100000.

На шестом такте к полученному результату в виде кода 10100000 прибавляется логическая "1" путем поступления с выхода элемента 19, Д2=1 блока 7 единичного значения К1, которое с выхода элемента ИЛИ 13 приходит, через элемент И 27, при е5=1 на вход элемента И 28 и на вход элемента И 26, учитывая, что на втором входе элемента И 26 присутствует "1", с его выхода единичный сигнал, через элементы ИЛИ 31 и И 27 второй канала поступят на вход элемента И 28 второго канала и в третьей четверти такта при d1=1, на выходах триггеров 29 появится результат вычисления А1+/-А2/ в прямом коде 01100000, при этом состояние ячейки памяти 17 блока 7 не изменится  и на инверсном выходе ячейки 17 сохранится единичное значение, означающее, что результат вычисления является отрицательным числом /знаковый разряд/.

и на инверсном выходе ячейки 17 сохранится единичное значение, означающее, что результат вычисления является отрицательным числом /знаковый разряд/.

На седьмом такте полученный на предыдущем такте результат и знаковый разряд с выходов тpиггров 29 через модуль МРФ и с инверсного выхода ячейки 17 запишутся, под действием сигналов С′=1, е4=1 и d2=1 и соответственно единичном выходе элемента И 71, в группу ячеек памяти 55 выходного блока 4.

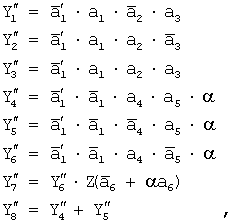

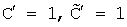

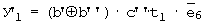

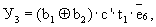

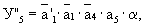

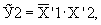

Модуль сдвига разрядов МСР1 для каждого логического канала из "n" логических каналов, кроме первого и последнего в многоканальном операционном блоке 7, имеет два выхода У1 и у2 и входов, обозначенных через t1, С′, С′′, b′, b′′, e6, его работа определяется следующими булевыми функциями:

где первый выход У′1 соединен с третьим входом первого элемента ИЛИ 25 данного логического канала, второй выход У′2 связан с четвертым входом элемента ИЛИ 25 последующего канала, вход b» подключен к выходу счетного триггера 29 данного логического канала, вход b′ соединен с выходом первого счетного триггера 29 последующего логического канала, входы С′ и С′′ связаны с соответствующими выходами программного блока 5, t1 соединен с выходом элемента НЕ 76,  связан с выходом первого дешифратора 8, блока 7.

связан с выходом первого дешифратора 8, блока 7.

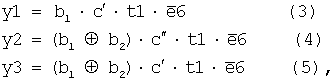

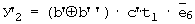

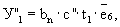

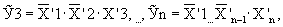

Модуль сдвига разрядов МСР2 первого логического канала блока 7 имеет три выхода У1, У2, У3 и шесть входов, обозначенных через b1·b2·t1, c′, c′′ и e6 и его работа определяется булевыми функциями:

где первый выход У1 соединен с четвертым входом элемента ИЛИ 25 первого логического канала, второй выход У2 связан с третьим входом элемента ИЛИ 25 того же канала, третий выход У3 подключен к четвертому входу элемента ИЛИ 25 второго логического канала, вход b1 связан с выходом первого счетного триггера 29 первого логического канала, вход b2 подключен к выходу счетного триггера 29 второго логического канала блока 7, входы С′ и С′′ соединены с соответствующими выходами программного блока 5, вход t1 связан с выходом элемента НЕ 76 и вход  подключен к соответствующему выходу дешифратора 8 блока 7.

подключен к соответствующему выходу дешифратора 8 блока 7.

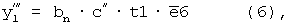

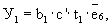

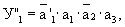

Модуль сдвига разрядов МСР3 последнего логического канала имеет один выход y′′′1 и четыре входа, обозначенные через bn, С′′, t1 и  функционирует в соответствии с булевой функцией:

функционирует в соответствии с булевой функцией:

где выход y′′′1 соединен с третьим входом элемента ИЛИ 25 последнего логического канала, вход bn связан с выходом триггера 29 последнего канала, вход C» подключен к соответствующему выходу блока 5, вход t1 соединен с выходом элемента НЕ 76 блока 7, вход e6 соединен с соответствующим выходом дешифратора блока 7.

Напомним, что все триггеры срабатывают по заднему фронту импульса, а например, сигнал  означает инверсию сигнала е6.

означает инверсию сигнала е6.

Сдвиг разрядов кода вниз от первого к "n" каналу осуществляется по команде C′=1 при C′′=0, t1=1, и e6=0. В этом случае, при условии, что все счетные триггеры 29 содержат определенный код для модуля МСР2 в соответствии с функциями (3) и (5) на выходе У1 установится логическая "1", если b1=1, и, проходя через элемент ИЛИ 25, логическая "1" окажется на входе элемента И 28 и в момент окончания импульса d1 на выходе триггера 29 первого канала установится "0". Одновременно при неравенстве сигналов на входах b1 и b2 выход У3 активизируется и логическая "1" поступает на вход элемента И 28 и по окончанию импульса d1 выход триггера 29 второго канала примет противоположное значение, т.е. значение, которое было на выходе триггера 29 первого логического канала. Одновременно в модулях МСР1 в соответствии с функцией (2) при неравенстве значение сигналов на логических выходах триггеров 29 данного и последующего каналов блока 7 активизируется выход У'2 во всех модулях МСР1 и логические "1" через соответствующие элементы ИЛИ 25 поступят на входы элементов И 28 соответствующих логических каналов и при окончании импульса d1 на выходе триггера 29 каждого последующего канала появится значение выхода триггера 29 данного логического канала, т.е. произойдет сдвиг вниз разрядов кода, записанного ранее в триггеры 29, начиная с третьего логического канала.

Сдвиг разрядов кода, записанного в триггеры 29 вверх имeeт место при наличии команды С′′=1, когда С′=0, е6=0, t1=1, Тогда в соответствии с функциями (1)...(6) могут активизироваться выходы У2 в модуле МСР2, У′1 в модуле МСР1 и выход У'''1 в модуле МСР3, при этом выход У2 активизируется, если входные сигналы b1 и b2 на соответствующих входах модуля МСР2 не равны и в этом случае, через элемент ИЛИ 25 на вход элемента И28 первого логического канала поступит логическая "1" и по заднему фронту импульса d1 триггер 29 первого канала примет значение триггера 29 второго логического канала. Одновременно, т.е. на этом же такте, для любого модуля МСР1 при неравенстве сигналов на его входах b′ и b′′ активизируется выход У'1 и логическая "1", через элемент ИЛИ25 поступает на вход элемента 28 данного канала, где находится соответствующий модуль МСР1 и в момент окончания импульса d1 на выходе триггера 29 данного канала устанавливается значение выхода триггера 29 последующего логического канала. Одновременно, если bn=1 активизируется выход y′′′1 модуля МСР3 и на входе элемента И 28 появится логическая "1" и по окончанию импульса d1 триггер 29 последнего логического канала перейдет в состояние "0". Таким образом произойдет сдвиг разрядов кода, записанного в триггеры 29 снизу-вверх.

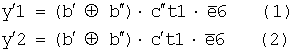

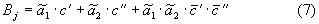

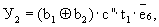

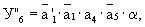

Каждый модуль МРФ поразрядной реализации булевых функций от двоичных кодов имеет четыре входа и один выход. Входы модуля МРФ  связаны с выходами соответственно триггеров 29 и 30 в каждом логическом канале, а входы C′ и С′′ соединены с соответствующими командными шинами программного блока 5. Модуль МРФ содержится в каждом логическом канале блока 7. Выход модуля МРФ является выходом соответствующего логического канала, обозначен через Вj и каждый из них подключен к определенному входу электронного выключателя 77 и соответствующему входу элемента 16 блока 7. Работа каждого модуля МРФ определяется булевой функцией

связаны с выходами соответственно триггеров 29 и 30 в каждом логическом канале, а входы C′ и С′′ соединены с соответствующими командными шинами программного блока 5. Модуль МРФ содержится в каждом логическом канале блока 7. Выход модуля МРФ является выходом соответствующего логического канала, обозначен через Вj и каждый из них подключен к определенному входу электронного выключателя 77 и соответствующему входу элемента 16 блока 7. Работа каждого модуля МРФ определяется булевой функцией

Допустим, требуется определить поразрядное логическое И, поразрядное ИЛИ и поразрядное ИСКЛЮЧАЮЩЕЕ ИЛИ от трех двоичных кодов, хранящихся либо во входном блоке, либо в блоке оперативной и записать результат в выходной блок или в блок оперативной памяти, На первых трех тактах, предварительно сбросив триггеры 29 всех логических каналов в "0", поочередно записываем /подаем/, описанным выше способом, указанные коды в счетные триггеры 29 логических каналов, Затем в соответствии е функцией (7) при значении команд С′=1 и С′′=0 на выходах модулей МРФ будет находиться результаты вычисления функции ИСКЛЮЧАЮЩЕЕ ИЛИ /поразрядно/ от трех двоичных кодов, который по команде е3=1 можно записать в блок 3. Далее на следующем такте при С′=1 и С′′=1 на выходах МРФ имеется результат поразрядного вычисления функции ИЛИ от трех указанных кодов и его также можно записать в блок 3 на этом же такте при е3=1. Затем на третьем такте при С′=0 и С′′=0 на выходах модулей МРФ будет иметь место результат вычисления поразрядного и от тех же трех кодов и его можно записать в блок 3 при е3=1. Таким образом введенные модули МРФ позволяют поразрядно вычислять указанные логические функции непосредственно от трех кодов, подавая их в логические каналы один раз, что повышает быстродействие устройства при вычислении указанных функций.

Введенный в блок 7 элемент ИЛИ 107, связанный входами с соответствующим выходом  программного блока 5 и с одной Т1 из общих шин 80, а выходом с первым входом элемента И 73, второй вход которого соединен с выходом элемента И 74, выход элемента И 73 подключен к первым входам всех элементов И 23 всех логических каналов, позволяет при

программного блока 5 и с одной Т1 из общих шин 80, а выходом с первым входом элемента И 73, второй вход которого соединен с выходом элемента И 74, выход элемента И 73 подключен к первым входам всех элементов И 23 всех логических каналов, позволяет при  записывать информацию в триггеры 25 только при T1=1.

записывать информацию в триггеры 25 только при T1=1.

Единичное значение прямого выхода ячейки памяти 17 в блоке 7 означает наличие переноса, например после арифметического сложения n разрядов двух двоичных чисел, в следующий n+1 разряд указанных чисел, значение переноса активизируется при Д3=1 на выходе дешифратора 9 блока 7 и поступает через элемент ИЛИ 13 на вход элемента И 27 первого логического канала блока 7.

Работу блока условных переходов в предлагаемом устройстве поясним на примерах.

Допустим, что в одном из фрагментов программы необходимо из множества чисел, представленных в двоичном коде и хранящихся во входном блоке 1, следует отобрать нечетные числа и поместить их в ячейки памяти блока 3 по адресам, начиная с кода А и далее по порядку с разницей в единицу.

Определять нечетные числа будем по значению младшего разряда Т1, поступающего на информационный вход элемента 107, блока 7.

На первом такте реализации указанного фрагмента программы при  , произойдет запись кода А в счетчик 87 из блока 5 по шинам С12...Сj.

, произойдет запись кода А в счетчик 87 из блока 5 по шинам С12...Сj.

На следующем такте, по вышеописанному способу, из входного блока 1 считывается первое число, допустим оно нечетно, и тогда, при  =0 и значении Т1=1, указанное нечетное число на этом же такте, при определенных командах С9...С11, запишется в триггеры 29 логических каналов блока 7 и другом такте под действием команд С1...С6 логическая "1" запомнится в триггере 43 блока 2. На следующем такте при соответствующих сигналах С9...С11, С', С» и α=1,

=0 и значении Т1=1, указанное нечетное число на этом же такте, при определенных командах С9...С11, запишется в триггеры 29 логических каналов блока 7 и другом такте под действием команд С1...С6 логическая "1" запомнится в триггере 43 блока 2. На следующем такте при соответствующих сигналах С9...С11, С', С» и α=1,

значение первого числа с выходов модуля МРФ логических каналов блока 7 запишется в блок 3, в ячейку памяти с адресом А, который будет считан из счетчика 87 при помощи ключа 89, а в конце этого такта по окончании импульса Z, с учетом

значение первого числа с выходов модуля МРФ логических каналов блока 7 запишется в блок 3, в ячейку памяти с адресом А, который будет считан из счетчика 87 при помощи ключа 89, а в конце этого такта по окончании импульса Z, с учетом  произойдет увеличение кода А на единицу, что является кодом следующего адреса для записи следующего нечетного числа из указанного множества. Далее, на следующем такте произойдет считывание второго числа из блока 1 и, если оно нечетно, то процесс повторится, а если оно четно и Т1=0, значения сигналов

произойдет увеличение кода А на единицу, что является кодом следующего адреса для записи следующего нечетного числа из указанного множества. Далее, на следующем такте произойдет считывание второго числа из блока 1 и, если оно нечетно, то процесс повторится, а если оно четно и Т1=0, значения сигналов  и Т1=0 обеспечат логический нуль на выходах элементов ИЛИ 107 и И 73 блока 7, по этой причине на данном такте второе число не будет записано в триггеры 29 логических каналов, которые переведены в нулевое состояние на предыдущем такте, вместе с состоянием триггера 43 блока 2 при соответствующих сигналах С′′′, С1...С6. При этом на выходе элемента 16 блока 7 имеется "0" и поэтому состояние триггера 43 не меняется α=0,

и Т1=0 обеспечат логический нуль на выходах элементов ИЛИ 107 и И 73 блока 7, по этой причине на данном такте второе число не будет записано в триггеры 29 логических каналов, которые переведены в нулевое состояние на предыдущем такте, вместе с состоянием триггера 43 блока 2 при соответствующих сигналах С′′′, С1...С6. При этом на выходе элемента 16 блока 7 имеется "0" и поэтому состояние триггера 43 не меняется α=0,

поэтому считывание кода А+1 с выходов счетчика 87 не произойдет и указанный код не увеличатся на "1", Подобный процесс будет повторятся до тех пор, пока из входного блока 1 не будет считано нечетное число, которое запишется в блок 3 в ячейку памяти по адресному коду А+1 в соответствии с процессом, описанным в начале данного примера.

поэтому считывание кода А+1 с выходов счетчика 87 не произойдет и указанный код не увеличатся на "1", Подобный процесс будет повторятся до тех пор, пока из входного блока 1 не будет считано нечетное число, которое запишется в блок 3 в ячейку памяти по адресному коду А+1 в соответствии с процессом, описанным в начале данного примера.

С введением блока 86 появилась возможность отбора и фиксации информации с определенными признаками среди множества различной информации, что расширяет функциональные возможности предлагаемого устройства по сравнению с прототипом.

Другой пример. Допустим, нам следует при определенном значении /смысле/ кодового слова из "М" имеющихся кодовых слов в блоке 1 перейти к программному коду А1, обеспечивавшему включение сигнального устройства, подключенного к выходу соответствующей ячейки памяти выходного блока 4 и затем перейти к программному коду А2.

На соответствующем такте в ячейку памяти 91 блока 86 при  записывается программный код А1, поступающий по шинам С12...Сj из программного блока 5. На следующем такте программный код А2 при,

записывается программный код А1, поступающий по шинам С12...Сj из программного блока 5. На следующем такте программный код А2 при,  записывается в ячейку памяти 92.

записывается в ячейку памяти 92.

Допустим, что определенное значение кодового слова хранится в блоке 3 и на следующем такте при соответствующих сигналах С1...Сj a′1=1 этот код считается с выходов блока 3 и запишется в триггеры 29 логических каналов. На следующем такте один код из "М" кодов, под действием командных и адресных сигналов С1...Сj и a′1=1 поступит на входы триггеров 29 логических каналов и сравнится с ранее записанным туда кодом и, если коды совпадают, то на выходе элемента 16 блока 7 появится "0" и на следующем такте при соответствующих сигналах С1...С6 в триггер 43 блока 2 запишется "1". На следующем такте, под действием сигналов α=1,

происходит считывание из ячеек памяти 91 программного кода А1 и установка счетных триггеров 84, счетчика 59 блока 5 в состояние А1. На следующем такте реализуется программный код А1 и при соответствующих сигналах С1...Сj и a′1=1 происходит запись "1" в соответствующую ячейку памяти выходного блока 4, куда подключено сигнальное устройство по условиям примера. На следующем такте под действием сигналов α=1,

происходит считывание из ячеек памяти 91 программного кода А1 и установка счетных триггеров 84, счетчика 59 блока 5 в состояние А1. На следующем такте реализуется программный код А1 и при соответствующих сигналах С1...Сj и a′1=1 происходит запись "1" в соответствующую ячейку памяти выходного блока 4, куда подключено сигнальное устройство по условиям примера. На следующем такте под действием сигналов α=1,  и

и  через ключ 94, происходит считывание программного кода А2 из ячеек памяти 92 и его запись, через ключ 85, в триггеры 84 блока 5. Далее реализуется программа в соответствии с программным кодом А2, т.к. сравнивать следующие коды из "М" кодов нет смысла и таким образом сокращается число тактов при решении задачи, в зависимости от результатов сравнения кодовых слов. При этом повышается быстродействие устройства и появляется возможность решать смысловые задачи, расширяя сферу использования устройства.

через ключ 94, происходит считывание программного кода А2 из ячеек памяти 92 и его запись, через ключ 85, в триггеры 84 блока 5. Далее реализуется программа в соответствии с программным кодом А2, т.к. сравнивать следующие коды из "М" кодов нет смысла и таким образом сокращается число тактов при решении задачи, в зависимости от результатов сравнения кодовых слов. При этом повышается быстродействие устройства и появляется возможность решать смысловые задачи, расширяя сферу использования устройства.

Количество счетчиков импульсов, рядов ячеек памяти и соответствующее им число электронных ключей в блоке условных переходов может быть любым, а их связи и принцип работы аналогичны выбранным в предлагаемом устройстве. Включение в данное устройство блока подпрограмм 97 позволяет реализовывать многократно повторяющиеся многотактовые операции за счет обращения к одним и тем же подпрограммам, записанным в модуле памяти 104 блока 97. При атом адрес первого такта данной подпрограммы и команда обращения в блок 97 записываются в основную программу, хранящуюся в блоке программ 5.

Поясним вышесказанное на примере. Вернемся к третьему такту второго примера, когда был получен результат суммы чисел А1 и -А2 в дополнительном коде. В продолжении примера, начиная с конца стр.20, на 4, 5, 6 и 7 тактах, были выполнены операции по окончательному определению результата алгебраической суммы А1+/-А2/, по программе, записанной в блок 5, причем аналогичную программу необходимо записывать в блок 5 при каждом вычитании с другими числами. В случае использования блока подпрограмм 97 эту часть программы в качестве подпрограммы можно записать в модуль памяти 104 блока 97 один раз и обращаться к ней каждый раз при реализации процесса вычитания с разными числами. Еще раз вернемся к указанному выше третьему такту, на котором активизируется введенная шина  и в третьей четверти такта по сигналу с выхода элемента И 99, двоичный код с адресных шин С12...Сq, где Cq≤Cj через открытый ключ 98 появится в третьей четверти такта на установочных входах счетчика импульсов 100 и установит его в положение при котором на выходах модуля памяти 104 появится программный код, соответствующий указанному выше 4 такту работы устройства и состояние "1" примет выход, связанный с входом управляемого триггера 102. На четвертом такте, в первой его четверти по сигналу из блока синхронизации 6, произойдет изменение состояния триггера 102, активизируется его прямой выход и подключит, через элемент И 101, соответствующий выход блока синхронизации к счетному входу счетчика импульсов 100 и отключит этот же выход, через элемент И 103, от счетного входа счетчика импульсов 59 блока 5. Одновременно по сигналам с прямого выхода триггера 102 закроется электронный ключ 61 блока 5 и откроется второй электронный ключ 105. Начиная с четвертого такта, соответствующие командные и адресные сигналы будут поступать на определенные входы всех блоков устройства из модуля памяти 104, через ключ 105.

и в третьей четверти такта по сигналу с выхода элемента И 99, двоичный код с адресных шин С12...Сq, где Cq≤Cj через открытый ключ 98 появится в третьей четверти такта на установочных входах счетчика импульсов 100 и установит его в положение при котором на выходах модуля памяти 104 появится программный код, соответствующий указанному выше 4 такту работы устройства и состояние "1" примет выход, связанный с входом управляемого триггера 102. На четвертом такте, в первой его четверти по сигналу из блока синхронизации 6, произойдет изменение состояния триггера 102, активизируется его прямой выход и подключит, через элемент И 101, соответствующий выход блока синхронизации к счетному входу счетчика импульсов 100 и отключит этот же выход, через элемент И 103, от счетного входа счетчика импульсов 59 блока 5. Одновременно по сигналам с прямого выхода триггера 102 закроется электронный ключ 61 блока 5 и откроется второй электронный ключ 105. Начиная с четвертого такта, соответствующие командные и адресные сигналы будут поступать на определенные входы всех блоков устройства из модуля памяти 104, через ключ 105.

На 5, 6 и 7 тактах работы устройства происходит по подпрограмме, записанной в модуль памяти блока 97. На 8 такте выход модуля памяти 104, связанный с информационным входом управляемого триггера 102, принимает значение "0", значения выходов триггера 102 меняются и в первой четверти восьмого такта, через элементы И101 и И103 происходит отключение счетного входа счетчика импульсов 100 от соответствующего выхода блока синхронизации и подключение этого выхода к счетному входу счетчика импульсов 59 блока 5 и одновременно отключается электронный ключ 105 и в дальнейшем работа устройства идет в соответствии с программой, записанной в программный блок 5. Очевидно из вышеизложенного, что любые повторяющиеся подпрограммы могут быть один раз записаны в модуль памяти 104 блока подпрограмм 97 и к ним можно многократно обращаться. При этом сокращается процесс программирования и уменьшается общее количество ячеек памяти, требующееся для хранения программы, по сравнению с прототипом.

Введение в коммутационно-вычислительный блок 2 элемента И-НЕ 106, у которого входы связаны соответственно с пятым выходом дешифратора 37 и с выходом ячейки памяти 43, а выход соединен с определенными входами элементов И 23, И 70 и И 71 в блоках 7, 3 и 4, позволяет подавать или блокировать подачу двоичного кода через элементы И 23 в логические каналы блока 7, а также записывать или не записывать результаты операций над двоичными кодами в блоки 3 и 4, в зависимости от выходного сигнала ячейки 43, что расширяет функциональные возможности при обработке кодов этим устройством по сравнению с прототипом, например при выполнении операции арифметического деления или логического выбора между двоичными кодами и т.д. При работе блока 97 сигнал на шине а′1 равен "1".

Введение связи между шинами 80 системы связи, обозначенными через Т1...Тn и через второй ключ 111 и электронный ключ 85, установочными входами счетных триггеров программного блока 5, позволяет реализовывать программу работы предлагаемого устройства в зависимости от результатов анализа данных на выходах модулей МРФ всех логических каналов блока 7, проводимого, при определенных значениях команд С4...С6, в блоке 2, т.к. команды на управление работой ключами 111 и 85 поступают с выхода элемента И 108 блока 2, что расширяет функциональные возможности предлагаемого устройства.

Блок прерывания 115 работает следующим образом. При появлении запросов на прерывание на входах триггеров 116, по сигналу с выхода элемента 63 блока 6, эти запросы записываются в триггеры 116 и поступают на входы X1...Xn модуля 117, где происходит определение наиболее приоритетного запроса из поступивших запросов, При этом сигнал приоритетного запроса появляется на одном из выходов Y1...Yn блока 117, затем он шифруется в двоичный код в шифраторе 118 и далее полученный двоичный код считывает в ПЗУ 120 ранее записанный туда нужный двоичный код для начала реализации подпрограммы, вызываемой приоритетным запросом и нужный двоичный код по сигналу с выхода элемента И 122, при единичных сигналах на выходах элементов 119 и 123, через ключ 121, во второй четверти такта установится в счетчике 100, блока 97 и далее появится на входах модуля памяти 104. На выходе модуля 104 появится логическая "1", поступающая на информационный вход управляемого триггера 102 и последний по сигналу с выхода элемента 68 блока 6 установит на всем прямом выходе логическую "1" и с выхода элемента И 101 начинают поступать импульсы на счетный вход счетчика 100. При этом двоичный код с выхода счетчика 100 считывает программу из модуля памяти 104, ранее туда записанную для реализации приоритетного запроса, и эта программа через электронный ключ 105 при К=1 поступает на командные и адресные шины, при этом ключ 61 закрывается, блокируя основную программу, записанную в программном блоке 5.

Введение в устройство многоразрядной ячейки памяти 124 и электронного ключа 125 позволяет по сигналу  , поступающего по первой введенной шине управления, записывать двоичный, код с общих шин в ячейку 124 и затем при определенном сигнале

, поступающего по первой введенной шине управления, записывать двоичный, код с общих шин в ячейку 124 и затем при определенном сигнале  на второй введенной шине, связанной с управляющем входом ключа 125 и вторым входом управления электронным ключом 61 программного блока 5, указанный двоичный код с выходов ячейки памяти 124 поступает на адресные шины С12...Сj, выходящие из ключа 61 программного блока.

на второй введенной шине, связанной с управляющем входом ключа 125 и вторым входом управления электронным ключом 61 программного блока 5, указанный двоичный код с выходов ячейки памяти 124 поступает на адресные шины С12...Сj, выходящие из ключа 61 программного блока.

Электронный ключ 61 работает следующем образом. Обозначим сигнал, поступающий на управляющий вход ключа 61 через  а сигнал, поступающий на второй вход управления ключом 61 обозначим через

а сигнал, поступающий на второй вход управления ключом 61 обозначим через  , так же как и вторую введенную шину управления. При

, так же как и вторую введенную шину управления. При  ключ 61 закрыт и на его выходах имеется высоки импеданс сопротивления, независимо от значения сигнала

ключ 61 закрыт и на его выходах имеется высоки импеданс сопротивления, независимо от значения сигнала  . Если

. Если  и

и  то ключ 61 открыт для управляющих сигналов, идущих по управляющим шинам и закрыт для адресных сигналов, т.е. на выходах С12...Сj, ключа 61 имеется высокий импеданс сопротивления. В случае, когда K′=1, а

то ключ 61 открыт для управляющих сигналов, идущих по управляющим шинам и закрыт для адресных сигналов, т.е. на выходах С12...Сj, ключа 61 имеется высокий импеданс сопротивления. В случае, когда K′=1, а  ключ 61 открыт для всех сигналов, идущих по командным /управляющим/ шинам и по адресным шинам.

ключ 61 открыт для всех сигналов, идущих по командным /управляющим/ шинам и по адресным шинам.

Технико-экономический эффект от предлагаемого изобретения состоит в расширении функциональных возможностей за счет организации приоритетного прерывания выполнения основной программы и определения кода адресов в зависимости от значения данных на общих шинах, а также в уменьшении объема основной программы при решении вычислительных задач по сравнению с прототипом.

Литература

1. Патент на изобретение №2154852 от 20.08.2000 г.

2. Патент на изобретение №2174700 от 10.10.2001 г.

Устройство относится к системам логико-программного управления и регулирования технологическими объектами в различных отраслях производства и к средствам решения логических задач. Техническим результатом является расширение функциональных возможностей устройства за счет организации процесса приоритетного прерывания и связи результатов вычислений с процессом пересылки данных, а также сокращение объема программирования. Устройство содержит входной блок, коммутационно-вычислительный блок, блок оперативной памяти, выходной блок, программный блок, блок синхронизации, многоканальный операционный блок, блок условных переходов, блок подпрограмм, блок прерываний, общие шины. 14 ил.