Устройство относится к средствам управления и может применяться в системах управления технологическими объектами и в производстве.

Известно устройство, содержащее входной и выходной блоки, блоки оперативной памяти и синхронизации, адресные шины, генератор импульсов, программный блок, блок коммутации и вычисления, состоящий из трехвходового дешифратора, трех двухвходовых элементов И, элемента ИЛИ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и управляемой ячейки памяти, командных шин, поступающих, как и адресные шины, с выходов программного блока /1/.

Недостатком данного устройства является относительно низкое быстродействие, большой объем ячеек памяти в программном блоке при реализации, например, процесса сравнения двоичных кодов.

Наиболее близким по технической сущности является устройство, содержащее входной и выходной блоки, блок оперативной памяти, блок синхронизации, коммутационно-вычислительный блок, содержащий трехвходовой дешифратор, связанный выходами с соответствующими входами элемента 2-2И-2ИЛИ, соединенного выходом с входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к управляющему входу ячейки памяти, информационный вход последней связан через элементы И, ИЛИ и НЕ с командными шинами программного блока и своим инверсным выходом, а прямой выход ячейки памяти соединен с входом еще одного элемента И, выход которого подключен к входу блока прерываний /2/.

К недостаткам этого устройства можно отнести относительно низкое быстродействие при решении задач управления объектами, связанных с выполнением базовых арифметических команд сложения и вычитания многоразрядных двоичных чисел, а также их сравнения по отдельным разрядам.

Целью предлагаемого изобретения является повышение быстродействия устройства и сокращение числа ячеек памяти в программном блоке, при реализации указанных операций и программировании.

С этой целью в устройство, содержащее входной блок, принимающий сигналы от датчиков и формирующий определенный код на своем выходе, выходной блок для записи значений кодов, поступающих из всех логических каналов в ячейки памяти и передачи их через цифроаналоговые преобразователи на электроисполнительные механизмы, программный блок, блок оперативной памяти, блок синхронизации и коммутационно-вычислительный блок, состоящий из элемента 2-2И-2ИЛИ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, пяти элементов И, ячейки памяти, элементов ИЛИ и НЕ, причем первые входы элемента 2-2И-2ИЛИ соединены соответственно с третьим и четвертым выходами дешифратора, а вторые входы подключены к выходу входного блока, соединенного первой и второй группами входов с группой информационных выходов объекта управления и с группой адресных выходов программного блока, а также к выходу блока оперативной памяти, выход элемента 2-2И-2ИЛИ подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с определенным выходом программного блока.

Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ связан с первым входом третьего элемента И, соединенного выходом с управляющим входом ячейки памяти, а ее информационный вход связан с выходом элемента ИЛИ, второй вход которого подключен к выходу пятого элемента И, второй вход последнего соединен с определенной шиной программного блока, первый вход пятого элемента И подключен к выходу элемента НЕ, а вход последнего связан с вторым входом четвертого элемента И и с соответствующей шиной программного блока, первый вход четвертого элемента И подключен к инверсному выходу ячейки памяти, а его выход соединен с первым входом элемента ИЛИ.

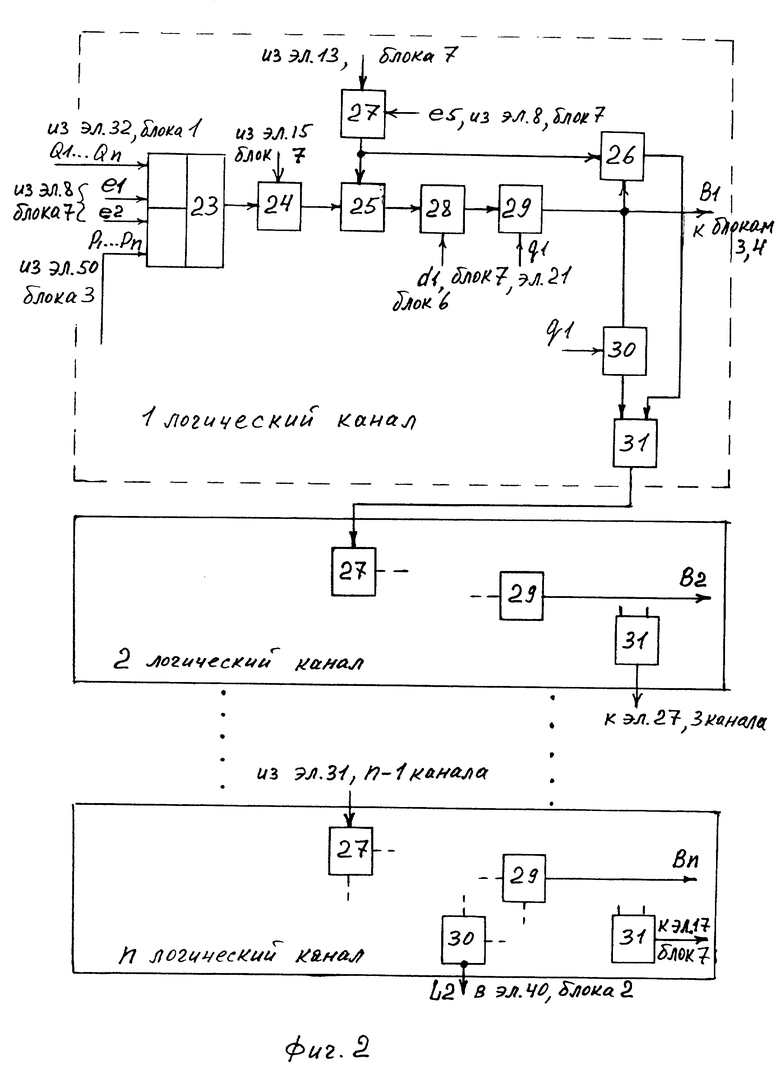

Прямой выход ячейки памяти связан с информационными входами выходного блока и блока оперативной памяти, первые входы первого к второго элементов И подключены к первому и второму выходам дешифратора, их вторые входы объединены и связаны с соответствующим выходом блока синхронизации, а выходы соединены с соответствующими входами выходного блока и блока оперативной памяти, в устройство дополнительно введен многоканальный операционный блок, содержащий элементы И с первого по седьмой, элементы ИЛИ с первого по пятый, первый и второй дешифраторы, управляемую ячейку памяти и "n" параллельно работающих логических каналов, имеющих одинаковую структуру, каждый из которых содержит элемент 2-2И-2ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ первый, второй и третий элементы И, первый и второй элементы ИЛИ, первый и второй счетные триггеры.

При этом в каждом канале выход элемента 2-2И-2ИЛИ соединен с входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход последнего связан с первым входом первого элемента ИЛИ, второй вход которого подключен к первому входу первого элемента И и к выходу второго элемента И, а выход соединен с первым входом третьего элемента И, выход последнего связан с счетным входом первого счетного триггера, выход которого подключен к второму входу первого элемента И и к счетному входу второго счетного триггера, выход последнего соединен с первым входом второго элемента ИЛИ, второй вход которого связан с выходом первого элемента И.

При этом два первых входа двух И элемента 2-2И-2ИЛИ всех логических каналов связаны с определенными выходами входного блока и блока оперативной памяти, а два вторых входа двух И элемента 2-2И-2ИЛИ всех логических каналов соединены с двумя соответствующими выходами первого дешифратора многоканального операционного блока, в котором выход первого элемента ИЛИ связан с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ логических каналов, первый и второй входы первого элемента ИЛИ связаны соответственно с выходами первого и второго элементов И, причем два входа первого элемента И подключены к одному из выходов второго дешифратора и выходу третьего элемента ИЛИ, входы которого соединены с двумя соответствующими выходами первого дешифратора.

Первый вход второго элемента И связан с одним из входов третьего элемента ИЛИ и с определенным выходом первого дешифратора, второй вход второго элемента И подключен к выходу седьмого элемента И, первый и второй входы второго элемента ИЛИ подключены к выходам шестого и седьмого элементов И, а третий вход к выходу третьего элемента И, входы которого соединены с соответствующим выходом второго дешифратора и с логической "1", первые входы шестого и седьмого элементов И подключены к соответствующим выходам второго дешифратора, а вторые входы соответственно к прямому и инверсному выходам ячейки памяти, информационный вход которой соединен с выходом второго элемента ИЛИ последнего логического канала, а управляющий вход управляемой ячейки памяти связан с выходом четвертого элемента И, первый вход которого подключен, вместе с первыми входами вторых элементов И всех логических каналов, к соответствующему выходу первого дешифратора.

Второй вход четвертого элемента И, вместе с вторыми входами третьих элементов И всех логических каналов соединены с определенным выходом блока синхронизации, а третий вход четвертого элемента И связан с определенным выходом второго дешифратора, пятый элемент И соединен входами с одним из выходов блока синхронизации и с выходом четвертого элемента ИЛИ, входы которого связаны с определенными выходами первого дешифратора, также подключенными к соответствующим входам блока оперативной памяти и выходного блока.

Выход пятого элемента И соединен с входами сброса в "0" первых и вторых счетных триггеров всех логических каналов, выходы всех первых счетных триггеров логических каналов соединены с информационными входами блока оперативной памяти и выходного блока и с входами пятого элемента ИЛИ, выход пятого элемента ИЛИ, соответствующие выходы первого дешифратора и инверсный выход второго счетного триггера последнего логического канала связаны с определенными входами коммутационно-вычислительного блока, в котором элемент 2-2И-2ИЛИ дополнен до элемента 2-2-2-2И-4ИЛИ, в котором первые входы третьего и четвертого И подключены к определенным выходам первого дешифратора, а вторые входы связаны соответственно с выходом пятого элемента ИЛИ и с инверсным выходом второго счетного триггера последнего логического канала в многоканальном операционным блоке, входы первого и второго дешифраторов подключены к командным шинам программного блока, выход второго элемента ИЛИ первого логического канала соединен с вторым входом второго элемента И второго логического канала, выход второго элемента ИЛИ второго логического канала связан с вторым входом второго элементы И третьего логического канала и т. д. до последнего логического канала, второй вход второго элемента И первого логического канала подключен к выходу второго элемента ИЛИ многоканального операционного блока, инверсный выход управляемой ячейки памяти соединен с входом выходного блока.

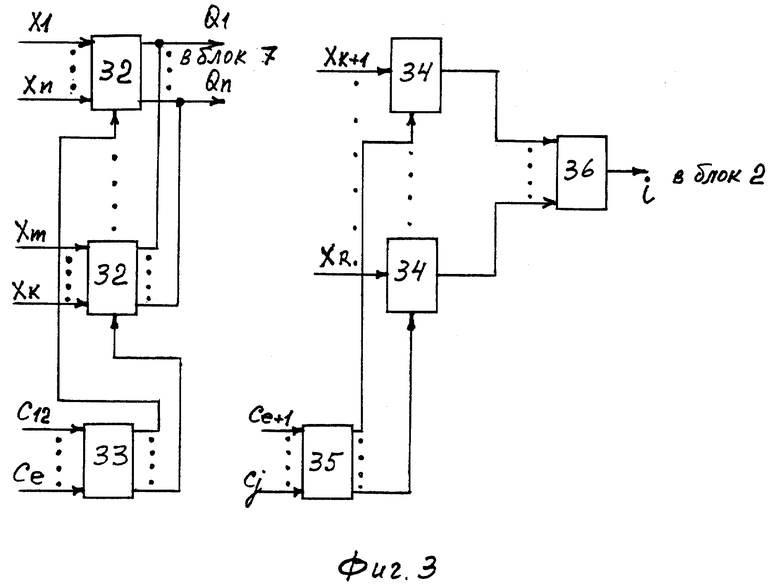

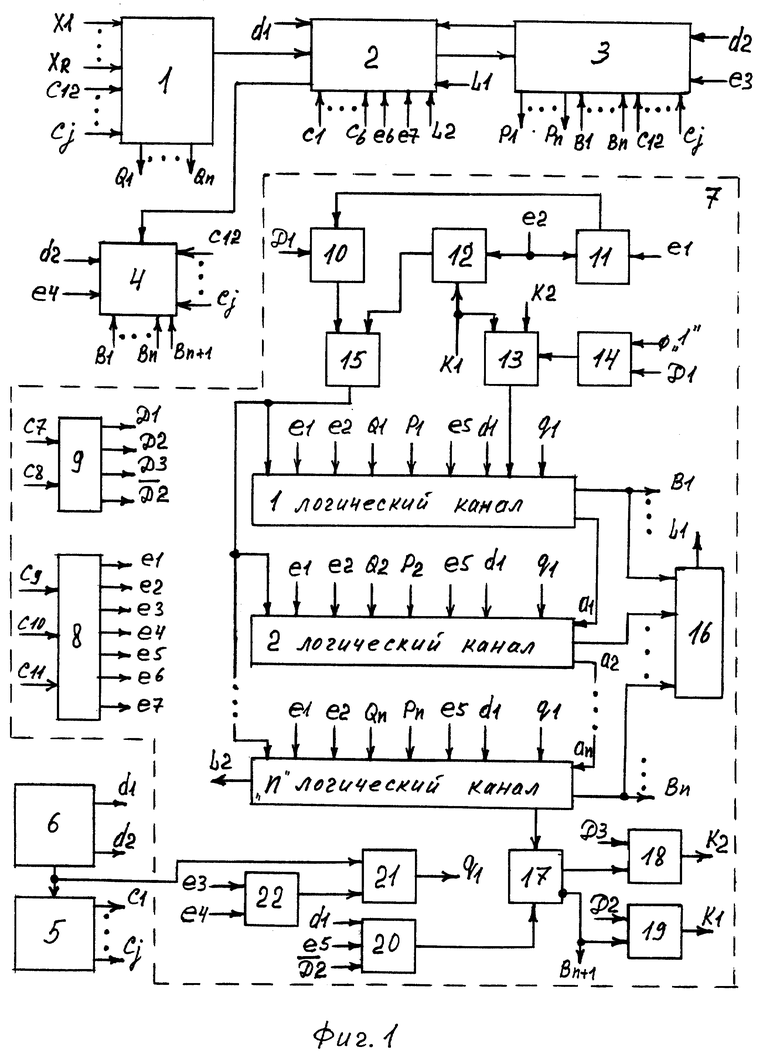

Предлагаемое устройство пояснено чертежами (фиг. 1 ... фиг. 10). Устройство состоит из входного блока 1, одна группа входов которого подключена к дискретным датчикам и источникам двоичного кода /на чертеже не показаны /. X1. ..XR, а вторая группа входов соединена с адресными шинами C12...Cj, связанного с коммутационно-вычислительным блоком 2, подключенного к блоку оперативной памяти 3, выходному блоку 4, блоку программ 5 и блоку синхронизации 6, выход которого соединен с многоканальным операционным блоком 7, содержащим первый и второй дешифраторы 8 и 9, последний связан с первым входом первого элемента И 10, подключенного вторым входом к выходу третьего элемента ИЛИ 11, соединенному своим входом с первым входом второго элемента И 12, подключенному вторым входом через второй элемент ИЛИ 13 к третьему элементу И 14, а выходом к первому элементу ИЛИ 15, выход которого связан с соответствующими входами всех логических каналов из "n", подключенных определенными выходами к входам пятого элемента ИЛИ 16 и информационному входу управляемой ячейки памяти 17, соединенной прямым выходом с входом шестого элемента И 18, инверсным выходом с входом седьмого элемента И 19, а управляющим входом к выходу четвертого элемента И 20, пятый элемент И 21, связанный с выходом четвертого элемента ИЛИ 22.

C1...C6, C7...C11 - командные сигналы, управляющие работой блоков 2, 7

B1...Bn+1 - выходы многоканального операционного блока 7

C12...Cj - адресные команды, определяющие адреса источников и приемников информации в блоках 1, 3, 4.

Xk+1. ..XR - входные дискретные сигналы от датчиков /кнопки, путевые выключатели и т.д./

X1. ..Xn, ..., Xm...Xk - многоразрядные двоичные сигналы, например с выходов цифровых задатчиков, аналого-цифровых преобразователей и т.д., причем левые разряды X1 и Xm являются младшими разрядами.

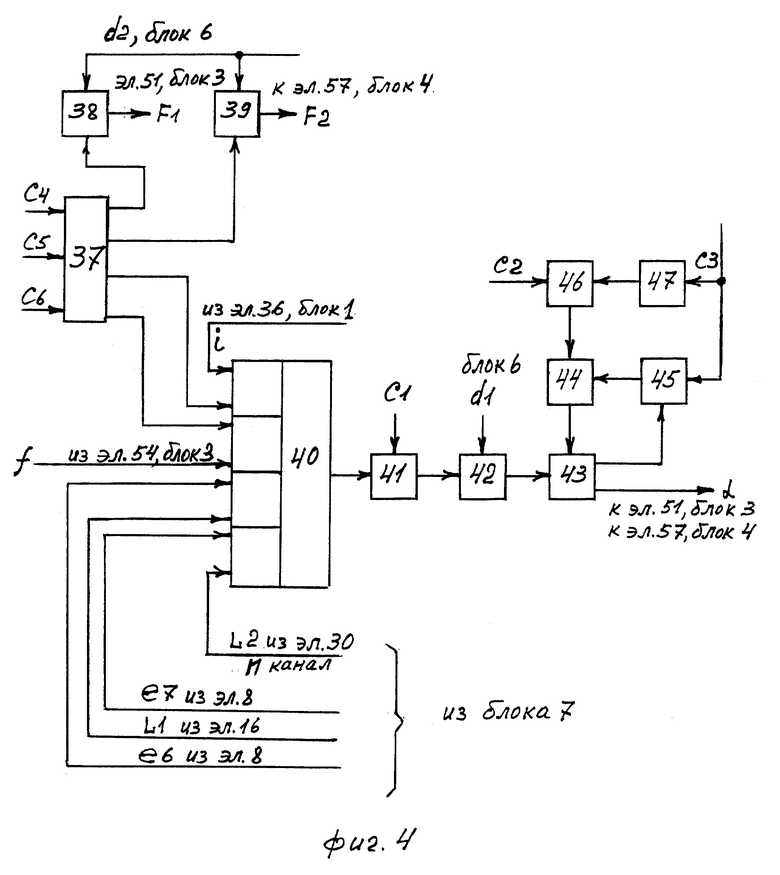

Входы блоков, каналов и элементов указаны входящими стрелками второго элементов И 38 и И 39, а вторыми двумя выходами к входам элемента 2-2-2-2И-4ИЛИ 40, выход которого соединен с входом элемента ИСКЛЮЧАЮЩИЕ ИЛИ 41, выход последнего связан с входом третьего элемента И 42, подключенного выходом к управляющему входу ячейки памяти 43, информационный вход которой соединен с выходом элемента ИЛИ 44, первый вход этого элемента связан с выходом четвертого элемента И 45, а второй вход подключен к выходу пятого элемента И 46, первый вход которого соединен с выходом элемента НЕ 47.

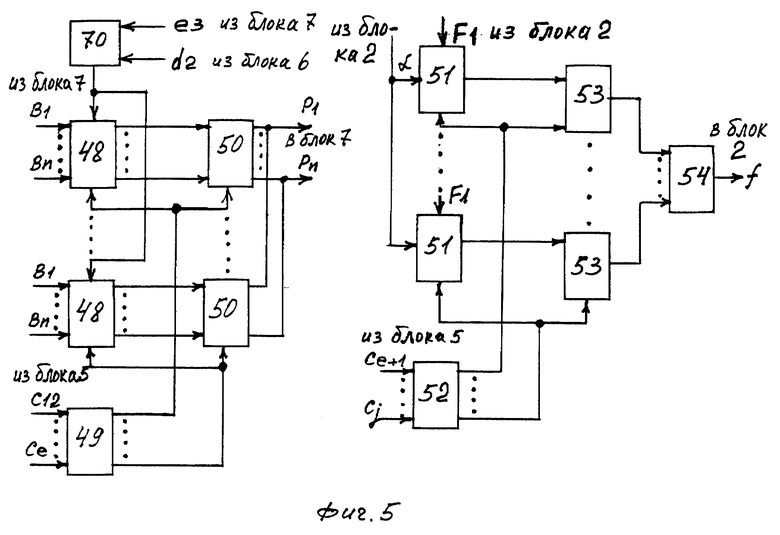

Пример блока оперативной памяти 3 представлен на фиг. 5 и он содержит ряды ячеек памяти 48, в один из этих рядов ячеек памяти записываются значения двоичного кода B1...Bn, поступающие с выходов первых счетных триггеров всех каналов блока 7, по импульсу d2 и команде e3, поступающих на входы элемента И 70, из блоков 6 в 7, формируя импульс разрешения запись в ряды ячеек памяти 48. Считывание двоичного кода с выходов одного из рядов ячеек памяти 48 осуществляется электронными ключами 50 по команде с выхода дешифратора 49, в зависимости от значений адресов C12...Ce, ряд однобитовых ячеек памяти 51, куда записываются результаты промежуточных вычислений булевых функций в блоке 2, по команде из блока 2 и по адресу, определяемому выходом второго дешифратора 52 в соответствии с адресными командами Ce+1...Cj, считывание из ячеек памяти 51 происходит через элементы И 53 и элемент ИЛИ 54 по адресу, определяемому выходом второго дешифратора 52. Запись и считывание происходит на разных тактах.

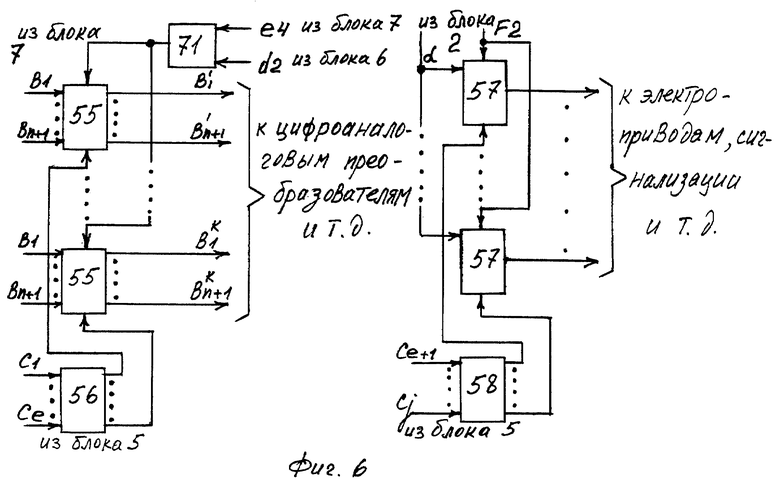

Пример структуры выходного блока 4 представлен на фиг. 6, он состоит из рядов ячеек памяти 55, куда записываются значения двоичных кодов с выходов первых счетных триггеров из всех логических каналов блока 7, по команде с выхода элемента И 71, на вход которого поступают сигналы d2 и e4 и по адресам, определяемым выходами дешифратора 56, значения B'1...B'n на выходах рядов ячеек памяти 55 могут поступать на входы цифроаналоговых преобразователей и далее в виде аналоговых сигналов, например на входы злектроисполнительных механизмов, из ряда ячеек памяти 57, в которые записываются результаты вычислений булевых функций в виде бит информации из блока 2 по команде F2, также из блока 2 и по адресу, определяемому выходом второго дешифратора 58, в зависимости от значений Ce+1...Cj.

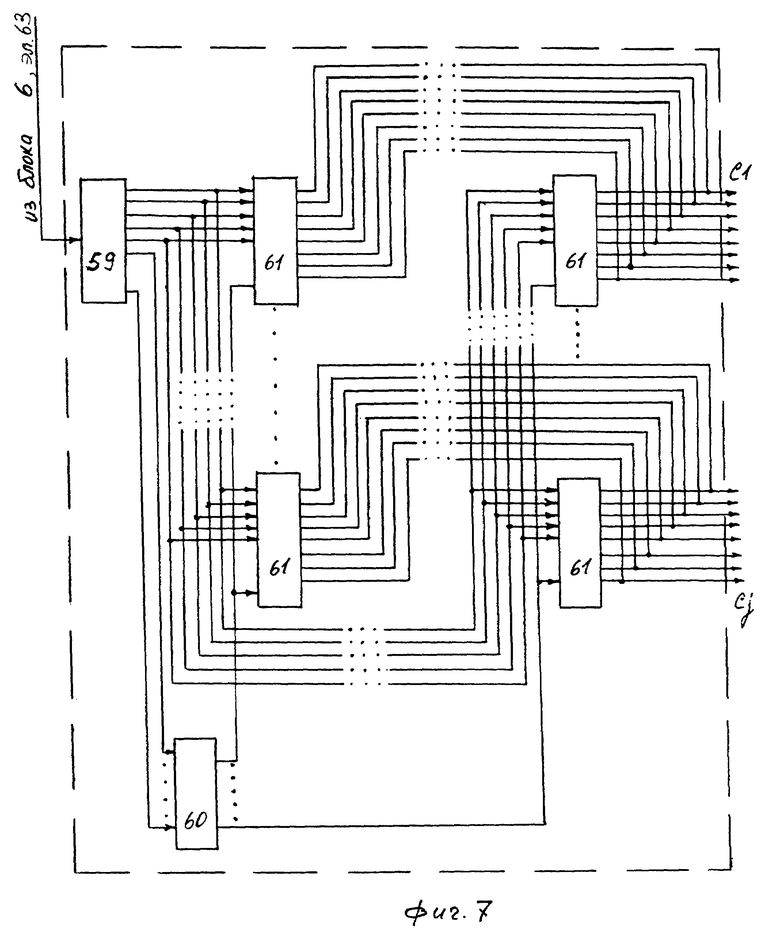

Пример структуры программного блока 5 представлен на фиг. 7, он содержит счетчик импульсов 59, на вход которого поступают импульсы с определенного выхода блока синхронизации 6, дешифратора 60, связанного выходами с входами ППЗУ 61, откуда считываются командные и адресные сигналы C1...Cj, причем выходы счетчика 59 подключены к входам дешифратора 60. Считывание происходит по тактам, известным способом.

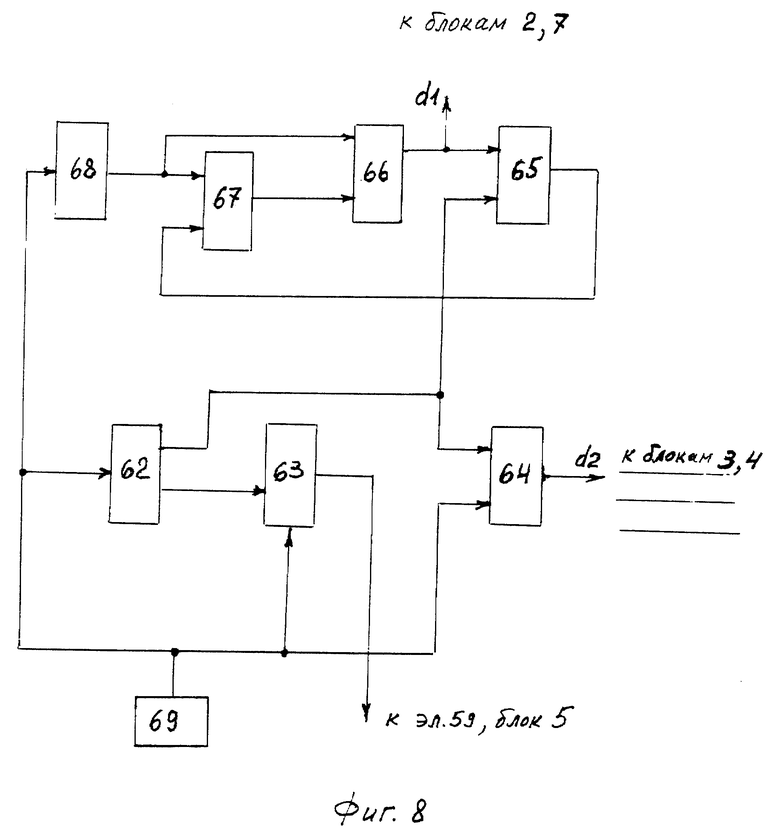

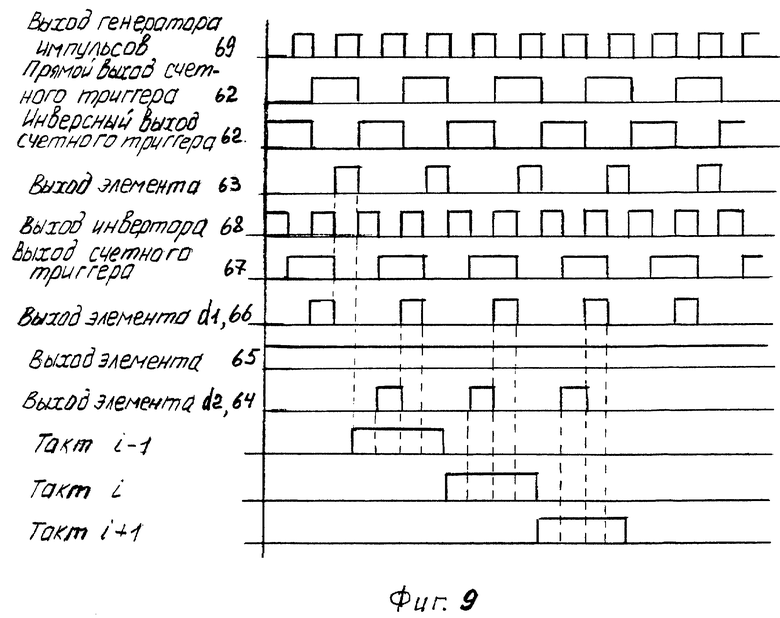

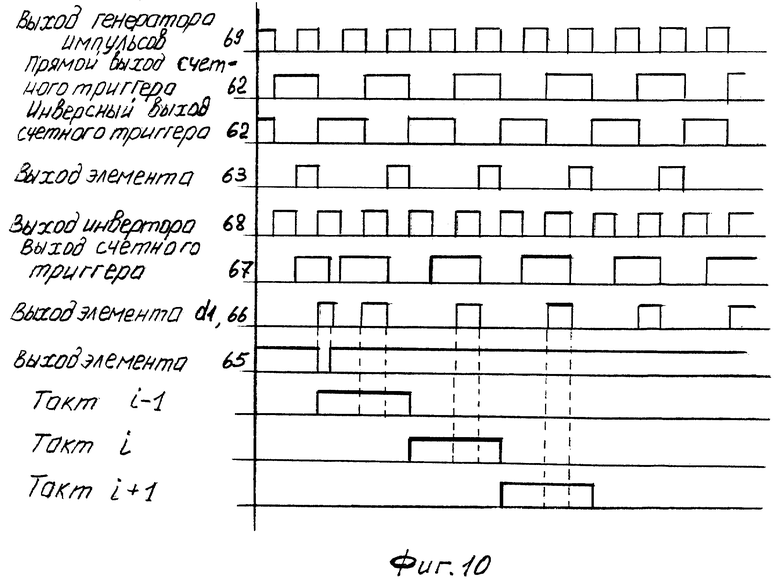

Пример блока синхронизации 6 представлен на фиг. 8, он сдержит первый счетный триггер 62, подключенный прямым выходом к элементу И 63, а инверсным выходом к первым входам элементов И 64 и И 65, второй вход последнего подключен к выходу элемента И 66, входы которого связаны с прямым выходом второго счетного триггера 67 и с выходом инвертора 68, вход последнего вместе с входом триггера 62 подключены к генератору прямоугольных импульсов 69. Работа блока 6 поясняется диаграммами на фиг. 9 и фиг. 10.

В блоке 7, нижний выход дешифратора 9 есть инверсия выхода D2. Оговоримся, что все триггеры и ячейки памяти срабатывают по заднему фронту импульсов, поступающих на их управляющие или счетные входы и перед началом работы устройства сброшены в "0".

Принцип работы блока 2 известен, он состоит в реализации булевых функций И, ИЛИ, НЕ, при C3 = 0 и функцию ИСКЛЮЧАЮЩЕЕ ИЛИ, при C3 = 1, последовательно по тактам, а также в управлении соответствующими процессами в блоках 3 и 4.

Работа устройства состоит в вычислении булевых функций по битам в блоке 2, с одновременной реализацией операций с многоразрядными двоичными кодами в блоке 7 и при необходимости устройство обеспечивает совместно работу блоков 2 и 7, например в случае сравнения двух двоичных кодов. Устройство работает по тактам, сформированным в блоке 5.

Работу устройства поясним на нескольких примерах.

Сравним два двоичных числа A1 и A2, при A1=A2 и для примера число A1 равно числу A2 и оба выражены двоичным кодом 11001011. Допустим число A1 находится в блоке 1 в виде X1...Xn, где n=8, а число A2 хранится в блоке оперативной памяти 3 в значениях P1...Pn, где n=8 и блок 7 имеет восемь логических каналов. Равенство чисел определим методом алгебраического сложения числа A1 и отрицательного числа A2, представленного в дополнительном коде, т. е. инвестировав его и прибавив "1" к младшему разряду. Примем, что  является инверсией A2.

является инверсией A2.

На первом такте значения X1...X8 при соответствующих значениях C12...Ce поступят в виде Q1...Q8 на входы элементов 23 всех каналов из блока 1 в блок 7, далее под действием команд C9...C11 дешифратор 8 блока 7 активизирует выход e1 и число A1 через элементы 23 всех каналов поступит на входы элементов 24 и при D1=0, e2=0, d1=1 значение числа A1 запишется в счетные триггеры 29, т. к. K1=0 и K2=0.

На втором такте при соответствующих сигналах C12...Ce в блоке 3 активизируется верхний выход дешифратора 49 и число A2 в виде значений P1...Pn с выхода электронного ключа 50 поступает на входы элемента 23 всех каналов блока 7 и при e2=1, D1=1, e1=0, K1=0 и K2=0 значение инверсии числа A2 поступает на счетные входы счетных триггеров 29 всех каналов в третьей четверти такта при d1=1 и реализуется поразрядно функция ИСКЛЮЧАЮЩЕЕ ИЛИ для чисел A1 и  при этом на выходах триггеров 29 всех каналов устанавливаются единичные значения.

при этом на выходах триггеров 29 всех каналов устанавливаются единичные значения.

На третьем такте для окончания перевода числа A2 в дополнительный код под действием команд C7...C11 активизируется выход D1 и выход e5 дешифраторов 9 и 8 блока 7 и логическая "1" с выхода элемента 14 через элементы ИЛИ 13 и И 27 первого канала поступит на второй и первый входы элементов ИЛИ 25 и И 26, на второй вход последнего поступает "1" с выхода триггера 29, при этом логическая "1" с выхода элемента И 26 через элемент ИЛИ 31 - первого канала появится на входе элемента И 27 второго канала и далее через элементы И 27, И 26 и ИЛИ 31 последующих каналов указанная логическая "1" появится на выходах элементов ИЛИ 31 всех каналов блока 7, в третьей четверти такта при импульсе d1 все счетные триггеры 29 всех каналов переключатся в состояние логического "0" на выходе, т.е. мы получили результат разности двух равных чисел, при этом триггеры 30 всех каналов переключились в состояние "1" и произошла запись информации с выхода триггера 30 последнего канала в ячейку памяти 17 по сигналу с выхода элемента И 20 блока 7.

На четвертом такте логический "0" с выхода элемента ИЛИ 16 при соответствующих сигналах C9. . . C11 по команде e6 с выхода дешифратора 8 блока 7 поступает через элемент 40 на вход элемента 41 блока 2, где инвертируется при C1= 1 и затем в третьей четверти такта, когда d1=1 и C2=1, а C3=0 единичное значение сигнала с выхода элемента ИЛИ 44 запишется в ячейку памяти 43 по команде с выхода элемента И 42.

На пятом такте логическая "1" с выхода ячейки 43 при определенных командах C4. . .C6 активизации нижнего выхода дешифратора 37 блока 2 и выхода элемента И 39, в момент d2=1, запишется в определенную значениями Ce+1...Cj ячейку памяти 57 выходного блока 4, как информация о том, что A1=A2.

Рассмотрим второй пример, когда A1<A2 и A1= 11001011, а A2 равно 10011011. Учтем, что выход  дешифратора 9 связан с входом И 20, блока 7.

дешифратора 9 связан с входом И 20, блока 7.

На первом такте по аналогии с первым примером число A1 записывается в счетные триггеры 29 по разрядам в каждый канал блока 7.

На втором такте при e1=1, D1=1 инверсия числа A2, т.е. 01100100 поступает на входы элементов И 28 и по импульсу d1=1, в третьей четверти такта, единичные значения разрядов числа  меняют состояние счетных триггеров 29 на противоположное и на выходе триггеров 29 появляется результат, равный

меняют состояние счетных триггеров 29 на противоположное и на выходе триггеров 29 появляется результат, равный  т. е. 10101111, при этом в втором канале счетный триггер 29, за два такта дважды поменял свое состояние с "0" в "1" и снова в "0", что привело к изменению состояния второго счетного триггера 30 с нулевого в единичное и фактически произошла фиксация факта образования переноса из второго разряда в третий разряд или из второго канала в третий, с этой целью и были введены счетные триггеры 30 во все каналы блока 7.

т. е. 10101111, при этом в втором канале счетный триггер 29, за два такта дважды поменял свое состояние с "0" в "1" и снова в "0", что привело к изменению состояния второго счетного триггера 30 с нулевого в единичное и фактически произошла фиксация факта образования переноса из второго разряда в третий разряд или из второго канала в третий, с этой целью и были введены счетные триггеры 30 во все каналы блока 7.

На третьем такте по сигналам D1 и e1 логическая "1" через элементы И 14, ИЛИ 13 и И 27 первого канала поступает на второй и первый входы элементов ИЛИ 25 и И 26 первого канала и с выхода последнего элемента И 26 через элемент ИЛИ 31 логическая "1" поступает на вход элемента 27 второго канала и далее на входы элементов ИЛИ 25 и И 26, с выхода элемента ИЛИ 31 логическая "1", как результат переноса, о котором говорилось выше /на втором такте/ поступила на вход элемента И 27 третьего канала и далее на входы элементов И 28 и И 26, с выхода последнего элемента логическая "1" через элемент ИЛИ 31 поступает на вход элемента И 27 четвертого канала и затем на входы И 26 и И 28, далее перенос не проходит, т.к. на выходах триггеров 29 и 30 логические нули. Таким образом элементы И 26 и ИЛИ 31 обеспечивают сквозной перенос из канала /разряда/ в канал /разряд/, когда перенос имеется, затем в третьей четверти такта при d1=1 происходит изменение состояний триггеров 29 в первых четырех каналах и на выходах всех триггеров 29 всех каналов устанавливается результат алгебраической суммы A1+/-A2/ в дополнительном коде 01011111, одновременно по сигналу с выхода элемента 20 произойдет запись информации /0/ с выхода триггера 30 последнего канала через элемент ИЛИ 31 в ячейку памяти 17 блока 7, при этом нулевое значение выхода триггера 30 показывает, что A1<A2 и получен результат алгебраической суммы A1+/-A2/ в дополнительном коде. На этом же такте в блоке 2 при C1=1, C2=1, C3...C6 равных "0" через элементы И 46 и ИЛИ 44 на информационный вход ячейки 43 поступает логическая "1", которая при нулевых выходах дешифратора 37, записывается в ячейку 43 по сигналу, поступающему с выхода элемента 41 через элемент И 42 на управляющий вход ячейки 43 при d1=1.

На четвертом такте по сигналу с выхода дешифратора 8 блока 7, e7=1 значение L2=1, с инверсного выхода триггера 30 последнего канала, поступает на выход элемента 40 блока 2 и затем при C1=1 на выходе элемента 41 находится "0" и значение ячейки памяти 43 не меняется, оставаясь "1".

На пятом такте значение L1=1 с выхода элемента ИЛИ 16, e6=1 поступит через элемент 40 на вход элемента 41 и при C1=1 на выходе последнего будет "0" и единичное значение ячейки 43 не изменится, мы получили результат вычисления функции L2•L1, подтверждающий, что A1<A2.

На шестом такте результат вычисления функции L2•L1 с выхода ячейки 43 блока 2 при соответствующей команде с выхода дешифратора 37 и при d2=1, т.e. во второй четверти такта, по команде с выхода элемента И 39 запишется в выходной блок 4, в одну из ячеек памяти по адресу Ce+1...Cj.

Дальше следовало бы описанным выше образом в блоке 2 вычислить функцию L1•  и, если бы A1>A2, то функция L1•

и, если бы A1>A2, то функция L1•  равнялась "1".

равнялась "1".

Вернемся к третьему такту, когда мы получили результат алгебраической суммы чисел A1 и -A2 в дополнительном коде, и продолжим для нового примера выполнение операций по решению задачи определения окончательного результата вычисления суммы A1+/-A2/.

Для этого на четвертом такте в блоке 7 полученный результат с выходов триггеров 29 всех каналов записывается в блок оперативной памяти 3 по сигналу с выхода элемента И 70 при e3=1 и d2=1 в ряд ячеек памяти, определенных значениями C12. . . Ce и выходом дешифратора 49. Одновременно под действием сигнала q1= 1 с выхода элемента И 21, все счетные триггеры всех каналов сбрасываются в "0", при этом на выходе элемента ИЛИ 22 имеется логическая "1".

На пятом такте записанная на предыдущем такте информация из блока 7 в блок 3, в соответствии с адресом C12...Ce, считывается из ряда электронных ключей 50 по сигналу с выхода дешифратора 49 и при активизации выхода e2 дешифратора 8 блока 7. Указанная информация через элементы 23 всех каналов поступает на входы элементов 24, где все разряды инвертируются под действием сигнала с выхода элемента ИЛИ 15 при D2=1 и поступают через элементы ИЛИ 25 при K1= 1 на счетные входы триггеров 29, при этом единичные разряды меняют состояния триггеров 29, на выходах которых устанавливается инверсное значение указанной информации, т.е. 10100000.

На шестом такте к полученному результату в виде кода 10100000 прибавляется логическая "1" путем поступления с выхода элемента 19, D2=1, блока 7 единичного значения K1, которое с выхода элемента ИЛИ 13 приходит через элемент И 27 при e5=1 на вход элемента И 28 и на вход элемента И 26, учитывая, что на втором входе элемента И 26 присутствует "1", с его выхода единичный сигнал через элементы ИЛИ 31 и И 27 второго канала поступят на вход элемента И 28 второго канала и в третьей четверти такта при d1=1 на выходах триггеров 29 появится результат вычисления A1+/-A2/ в прямом коде 01100000, при этом состояние ячейки памяти 17 блока 7 не изменится /  =0/ и на инверсном выходе ячейки 17 сохранится единичное значение, означающее, что результат вычисления является отрицательным числом /знаковый разряд/ /3/.

=0/ и на инверсном выходе ячейки 17 сохранится единичное значение, означающее, что результат вычисления является отрицательным числом /знаковый разряд/ /3/.

На седьмом такте полученный на предыдущем такте результат и знаковый разряд с выходов триггеров 29 и с инверсного выхода ячейки 17 запишутся под действием сигналов e4=1 и d2=1 и при соответственно единичном выходе элемента И 71 в группу ячеек памяти 55 выходного блока 4 по адресу, определенному значениями C1...C и соответствующим выходом дешифратора 56.

Единичное значение прямого выхода ячейки памяти 17 в блоке 7 означает наличие переноса, например после арифметического сложения n разрядов двух двоичных чисел, в следующий n+1 разряд указанных чисел, значение переноса активизируется при D3= 1 на выходе дешифратора 9 блока 7 и поступает через элемент ИЛИ 13 на вход элемента И 27 первого канала.

Программирование команд C1...C6 и C7...C11, а также адресных команд C12. . .Ce и Ce+1...Cj осуществляется в блоке 5 независимо, поэтому работа блоков 2 и 7 может осуществляться параллельно, т.е. процесс реализации операций с многоразрядными числами в блоке 7 и процесс вычисления булевых функций в блоке 2 могут осуществляться одновременно, что существенно повышает быстродействие устройства, и его применение очень эффективно в системах управления технологическими объектами, где часто требуется и вычисление булевых функций и обработка многоразрядных кодов, например с аналого-цифровых преобразователей и т.д.

Реализация операций сложения и вычитания возможно и в прототипе, но для этого требуется большое количество тактов, т.к. при арифметическом суммировании для каждого разряда многоразрядного числа требуется вычислить следующие булевы функции: У = Ai⊕ Bi⊕ Pi-1, P=Ai•Bi + Ai•Pi + Bi•Pi-1, где Y - результат i-разряда суммы, Ai - бит первого слагаемого, Bi - бит второго слагаемого, Pi-1 - бит переноса от суммы предыдущего разряда.

Технико-экономический эффект от использования предлагаемого устройства состоит в повышении быстродействия при обработке дискретных сигналов и кодовых слов, поступающих с объекта управления, что позволяет снизить время реакции системы управления на технологические изменения в объекте управления и тем самым повысить качество управления и регулирования, а также в простом программировании, за счет того, что на одном такте совмещается процесс вызова информации из входного блока или блока оперативной памяти с процессом обработки информации.

Изобретение может применяться при автоматизации в технологических процессах и в производстве. В устройство дополнительно введен многоканальный операционный блок, имеющий соответствующие связи и содержащий семь элементов И, пять элементов ИЛИ, первый и второй дешифраторы, управляемую ячейку памяти и n параллельно работающих логических каналов, имеющих одинаковую структуру, в каждом из которых происходит логическая обработка одного разряда двоичного кода с использованием в качестве функциональных элементов счетных триггеров. Технический результат - простая архитектура устройства, упрощенный процесс пересылки данных и элементарное программирование за счет совмещения вычислительного процесса и процесса пересылки данных, а также повышенное быстродействие. 10 ил.

Устройство для программного управления электроприводами, электронными ключами и сигнализацией, содержащее входной блок, принимающий сигналы от датчиков и формирующий определенный код на своем выходе, выходной блок для записи значения кодов, поступающих из всех логических каналов в ячейки памяти и передачи их, через цифроаналоговые преобразователи, на электроисполнительные механизмы, программный блок, блок оперативной памяти, блок синхронизации и коммутационно-вычислительный блок, состоящий из элемента 2-2И-2ИЛИ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, пяти элементов И, ячейки памяти, элементов ИЛИ и НЕ, причем первые входы элемента 2-2И-2ИЛИ соединены соответственно с третьим и четвертым выходами дешифратора, а вторые входы подключены к выходу входного блока, соединенного первой и второй группами входов с группой информационных выходов объекта управления и с группой адресных выходов программного блока, а также к выходу блока оперативной памяти, выход элемента 2-2И-2ИЛИ подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с определенным выходом программного блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ связан с первым входом третьего элемента И, соединенного выходом с управляющим входом ячейки памяти, а ее информационный вход связан с выходом элемента ИЛИ, второй вход которого подключен к выходу пятого элемента И, второй вход последнего соединен с определенной шиной программного блока, первый вход пятого элемента И подключен к выходу элемента НЕ, а вход последнего связан с вторым входом четвертого элемента И и с соответствующей шиной программного блока, первый вход четвертого И подключен к инверсному выходу ячейки памяти, а его выход соединен с первым входом элемента ИЛИ, прямой выход ячейки памяти связан с информационными входами выходного блока и блока оперативной памяти, первые входы первого и второго элемента И подключены к первому и второму выходам дешифратора, а их вторые входы объединены и связаны с соответствующим выходом блока синхронизации, а выходы соединены с соответствующими входами выходного блока и блока оперативной памяти, отличающееся тем, что в него введен многоканальный операционный блок, содержащий элементы И с первого по седьмой, элементы ИЛИ с первого по пятый, первый и второй дешифраторы, управляемую ячейку памяти и n параллельно работающих логических каналов, имеющих одинаковую структуру, каждый из которых содержит элемент 2-2И-2ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй и третий элементы И, первый и второй элементы И, первый и второй элементы ИЛИ, первый и второй счетные триггеры, при этом в каждом канале выход элемента 2-2И-2ИЛИ соединен с входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход последнего связан с первым входом первого элемента ИЛИ, второй вход которого подключен к первому входу первого элемента И и к выходу второго элемента И, а выход соединен с первым входом третьего элемента И, выход последнего связан со счетным входом первого счетного триггера, выход которого подключен к второму входу первого элемента И и к счетному входу второго счетного триггера, выход последнего соединен с первым входом второго элемента ИЛИ, второй вход которого связан с выходом первого элемента И, при этом два первых входа двух И элемента 2-2И-2ИЛИ всех логических каналов связан с определенными выходами входного блока и блока оперативной памяти, а два вторых входа двух И элемента 2-2И-2ИЛИ всех логических каналов соединены с двумя соответствующими выходами первого дешифратора многоканального операционного блока, в котором выход первого элемента ИЛИ связан с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ логических каналов, первый и второй входы первого элемента ИЛИ связан соответственно с выходами первого и второго элементов И, причем два входа первого элемента И подключены к одному из выходов второго дешифратора и выходу третьего элемента ИЛИ, входы которого соединены с двумя соответствующими выходами первого дешифратора, первый вход второго элемента И связан с одним из входов третьего элемента ИЛИ и с определенным выходом первого дешифратора, второй вход второго элемента И подключен к выходу седьмого элемента И, первый и второй входы второго элемента ИЛИ подключены к выходам шестого и седьмого элементов И, а третий вход - к выходу третьего элемента И, выходы которого соединен с соответствующим выходом второго дешифратора и с логической "1", первые входы шестого и седьмого элементов И подключен к соответствующим выходам второго дешифратора, а вторые входы соответственно к прямому и инверсному выходам ячейки памяти, информационный вход которой соединен с выходом второго элемента ИЛИ последнего логического канала, а управляющий вход управляемой ячейки памяти связан с выходом четвертого элемента И, первый вход которого подключен, вместе с первыми входами вторых элементов И всех логических каналов, к соответствующему выходу первого дешифратора, второй вход четвертого элемента И, вместе с вторыми входами третьих элементов И всех логических каналов, соединены с определенным выходом блока синхронизации, а третий вход четвертого элемента И связан с определенным выходом второго дешифратора, пятый элемент И соединен входами с одним из выходов блока синхронизации и с выходом четвертого элемента ИЛИ, входы которого связаны с определенными выходами первого дешифратора, также подключенными к соответствующим входам блока оперативной памяти и выходного блока, выход пятого элемента И соединен с входами сброса в "0" первых и вторых счетных триггеров всех логических каналов, выходы всех первых счетных триггеров логических каналов соединены с информационными входами блока оперативной памяти и выходного блока и с входами пятого элемента ИЛИ, выход пятого элемента ИЛИ, соответствующие выходы первого дешифратора и инверсный выход второго счетного триггера последнего логического канала связаны с определенными входами коммутационно-вычислительного блока, в котором элемент 2-2И-2ИЛИ дополнен до элемента 2-2-2-2И-2ИЛИ, в котором первые входы третьего и четвертого элементов И подключены к определенным выходам первого дешифратора, а вторые входы связаны соответственно с выходом пятого элемента ИЛИ и с инверсным выходом второго счетного триггера последнего логического канала в многоканальном операционном блоке, входы первого и второго дешифратора подключены к командным шинам программного блока, выход второго элемента ИЛИ первого логического канала соединен с вторым входом второго элемента И второго логического канала, выход второго элемента ИЛИ второго логического канала связан с вторым входом второго элемента И третьего логического канала и т.д. до последнего логического канала, второй вход второго элемента И первого логического канала подключен к выходу второго элемента ИЛИ многоканального операционного блока, инверсный выход управляемой ячейки памяти соединен с входом выходного блока.

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 1997 |

|

RU2134442C1 |

| Устройство для дистанционного программного управления сигнализацией и электропроводными механизмами | 1990 |

|

SU1801223A3 |

| RU 21066676 C1, 10.03.1998 | |||

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ И СИГНАЛИЗАЦИЕЙ | 1994 |

|

RU2095846C1 |

| DE 2846686 B1, 27.09.1979. | |||

Авторы

Даты

2001-10-10—Публикация

2000-05-24—Подача