Изобретение относится к средствам автоматизации и может быть использовано в частности в системах управления электроагрегатов генераторных с приводом от двигателя внутреннего сгорания.

Известны аналоговые реле различного типа, содержащие измерительный преобразователь и выходной каскад, использующие различные способы измерения контролируемой физической величины /1, 2/.

Их недостатками являются ограниченные функциональные возможности в частности достоверность выходной информации и точность настройки.

Известен цифровой измеритель скорости вращения, содержащий импульсный датчик, генератор эталонной частоты, счетчик импульсов, элемент задержки и электронные ключи /3/. Он обеспечивает удовлетворительную точность.

Его недостатком являются невысокие функциональные возможности, заключающиеся в наличии лишь одного выходного канала и невысокая достоверность выходной информации.

Известно реле частоты вращения (РЧВ) с трехканальным выходом по числу уставок, содержащее формирователь коротких импульсов, преобразователь частоты в постоянное напряжение, три пороговых устройства с задатчиками уставок, шесть индикаторов состояния и выходное устройство с тремя каскадами /4/. Наличие трех выходных каналов расширяет возможности РЧВ.

Однако возможные сбои в измерительной части и в выходных каналах при отсутствии самодиагностики отражаются на достоверности выходной информации РЧВ и могут привести к сбою в работе системы управления.

Наиболее близким по технической сущности к изобретению является цифровое реле частоты вращения с функцией реконструктивной диагностики, содержащее формирователь коротких импульсов, первый, второй и третий числовые компараторы, к разрядам первых входов которых подключены соответствующие разряды выходов соответственно первого, второго и третьего задающего регистра, выходное устройство с тремя выходными каскадами, три индикатора и элемент задержки, выход которого подключен к сбросовым входам первого и второго счетчика и входу записи исходного числа реверсивного счетчика, а вход соединен с выходом формирователя коротких импульсов, к которому так же подключены: вход распределителя импульсов, вход записи первого регистра памяти, единичный вход второго RS-триггера и первые входы пятого и десятого логического элемента И, вторые входы которых подключены соответственно к первому и второму выходу четвертого числового компаратора, разряды первого входа которого соединены с соответствующими разрядами выхода четвертого задающего регистра, разряды второго входа - с соответствующими разрядами выхода реверсивного счетчика, суммирующий вход которого подключен к выходу четвертого логического элемента И, вычитающий вход - к выходу третьего логического элемента И, а выход заема - к сбросовому входу второго RS-триггера прямой и инверсный выходы которого соответственно соединены со вторыми входами третьего и четвертого логических элементов И, первые входы которых подключены к выходу генератора импульсов стабильной частоты, к которому так же подключены первые входы первого и второго логических элементов И, ко вторым входам которых подключены соответственно прямой и инверсный выходы первого RS-триггера, а к выходам - счетные входы соответственно первого и второго счетчика, разряды выходов которых соответственно через первый и второй электронные ключи подключены к соответствующим разрядам входа первого регистра памяти, причем управляющий вход первого электронного ключа связан со вторым выходом распределителя импульсов и сбросовым входом первого RS-триггера, а управляющий вход второго электронного ключа - с первым выходом распределителя импульсов и единичным входом первого RS-триггера, кроме того соответствующие разряды выхода первого регистра памяти подключены к соответствующим разрядам входа исходного числа реверсивного счетчика и вторых входов первого, второго и третьего числовых компараторов выходы БОЛЬШЕ которых подключены соответственно к первому, второму и третьему разрядам входа дешифратора нулевой выход которого подключен к сбросовому входу третьего RS-триггера инверсный выход которого соединен с первым входом восьмого логического элемента И, прямой выход - с первым входом девятого логического элемента И, а единичный вход - с третьим выходом дешифратора, второй выход которого подключен к вторым входам восьмого и девятого логического элемента И, четвертый выход - к входу третьего индикатора входу первого логического элемента НЕ, выход которого подключен ко второму входу шестого логического элемента И, соединенного первым входом с выходом третьего числового компаратора, а выходом - с третьим разрядом входа второго регистра памяти, первый, второй и третий разряды выхода которого подключены соответственно к входам первого, второго и третьего выходного каскада, второй разряд входа - к выходу третьего логического элемента ИЛИ, а первый разряд входа - к выходу первого логического элемента ИЛИ, первый вход которого связан с выходом первого числового компаратора, второй вход - с вторым входом второго логического элемента ИЛИ и шестым выходом дешифратора, пятый выход которого соединен со вторым входом третьего логического элемента ИЛИ и первым входом четвертого логического элемента ИЛИ, выход которого подключен к входу второго индикатора, а второй вход - к выходу восьмого логического элемента И, связанного с входом второго логического элемента НЕ, выход которого соединен со вторым входом седьмого логического элемента И, подключенного выходом к первому входу третьего логического элемента ИЛИ, а первым входом - к выходу второго числового компаратора, кроме того выход девятого логического элемента И связан с третьим входом первого логического элемента ИЛИ и первым входом второго логического элемента ИЛИ, связанного выходом со входом первого индикатора, а выход десятого логического элемента И соединен с единичным входом четвертого RS-триггера, сбросовый вход которого подключен к шине сброс, а выход пятого логического элемента И - к входу записи второго регистра памяти 151. Три задающих регистра и три числовых компаратора по существу представляют три приемных реле. Самоконтроль обеспечивает достоверность выходной информации.

Однако это реле имеет возможность контроля лишь трех каналов информации.

Цель изобретения - расширение функциональных возможностей путем увеличения числа контролируемых каналов выходной информации.

Цифровое n-канальное реле с функцией самодиагностики, содержащее n приемных реле, выходы которых соединены с соответствующими входами дешифратора, индикатор состояния, первый и второй числовой компаратор, первый и второй логические элементы И, первый из n логический элемент НЕ, второй логический элемент НЕ, первый и второй RS-триггер, регистр памяти, первый, второй и третий логический элемент ИЛИ, первый из n формирователей коротких импульсов, ОТЛИЧАЮЩЕЕСЯ тем, что с целью расширения функциональных возможностей снабжено со второго по n-й первыми формирователями коротких импульсов, n вторыми формирователями коротких импульсов и третьим формирователем коротких импульсов, четвертым и пятым логическими элементами ИЛИ, шиной СБРОС, первым и вторым блоками памяти, разряды входа адреса которых соединены с соответствующими разрядами выхода регистра памяти, а разряды выходов подключены к соответствующим разрядам вторых входов соответственно первого и второго числового компаратора, разряды первых входов которых связаны с соответствующими разрядами входа регистра памяти, выходами соответствующих с первого по n-й приемных реле, входами соответствующих с первого по n-й первых логических элементов НЕ и входами соответствующих с первого по n-й первых формирователей коротких импульсов, выходы которых подключены к соответствующим четным входам первого логического элемента ИЛИ, к нечетным входам которого подключены выходы соответствующих с первого по n-й вторых формирователей коротких импульсов, с входами которых соединены выходы соответствующих с первого по n-й первых логических элементов НЕ, а выход первого логического элемента ИЛИ подключен к первому входу второго логического элемента И и третьему входу первого логического элемента И, выход которого подключен к второму входу третьего логического элемента ИЛИ, связанного выходом с входом записи регистра памяти, а первым входом - с выходом третьего формирователя коротких импульсов, вход которого соединен с прямым выходом первого RS-триггера, связанного нулевым входом с шиной СБРОС, а единичным входом - с выходом второго логического элемента ИЛИ, входом второго логического элемента НЕ и первым входом первого логического элемента И, второй вход которого подключен к выходу пятого логического элемента ИЛИ, соединенного первым входом с выходом РАВНО первого числового компаратора, выход БОЛЬШЕ которого подключен к третьему входу четвертого логического элемента ИЛИ, связанного пятым входом с выходом второго логического элемента НЕ, четвертым входом - с выходом МЕНЬШЕ первого числового компаратора, вторым входом - с выходом МЕНЬШЕ второго числового компаратора, первым входом - с выходом БОЛЬШЕ второго числового компаратора, выход РАВНО которого подключен к второму входу пятого логического элемента ИЛИ, причем выход четвертого логического эле-мента ИЛИ соединен с вторым входом второго логического элемента И, выход которого соединен с единичным входом второго RS-триггера, связанного нулевым входом с шиной СБРОС, а выходом - с входом индикатора, кроме того (2i-1)-e разряды выхода дешифратора, где i=0, 1, 2, …, n, соединены с соответствующими входами второго логического элемента ИЛИ, а выходы регистра памяти являются выходами устройства. Введенные в схему логические элементы НЕ, формирователи коротких импульсов и их связи обеспечивают выбор момента для контроля состояния информационных каналов. Первый и второй блоки памяти содержат информацию для проверки исправности этих каналов. Четвертый логический элемент ИЛИ формирует сигнал, указывающий на неисправность информационных каналов, а пятый логический элемент ИЛИ формирует сигнал на передачу информации в САУ при исправном состоянии всех информационных каналах.

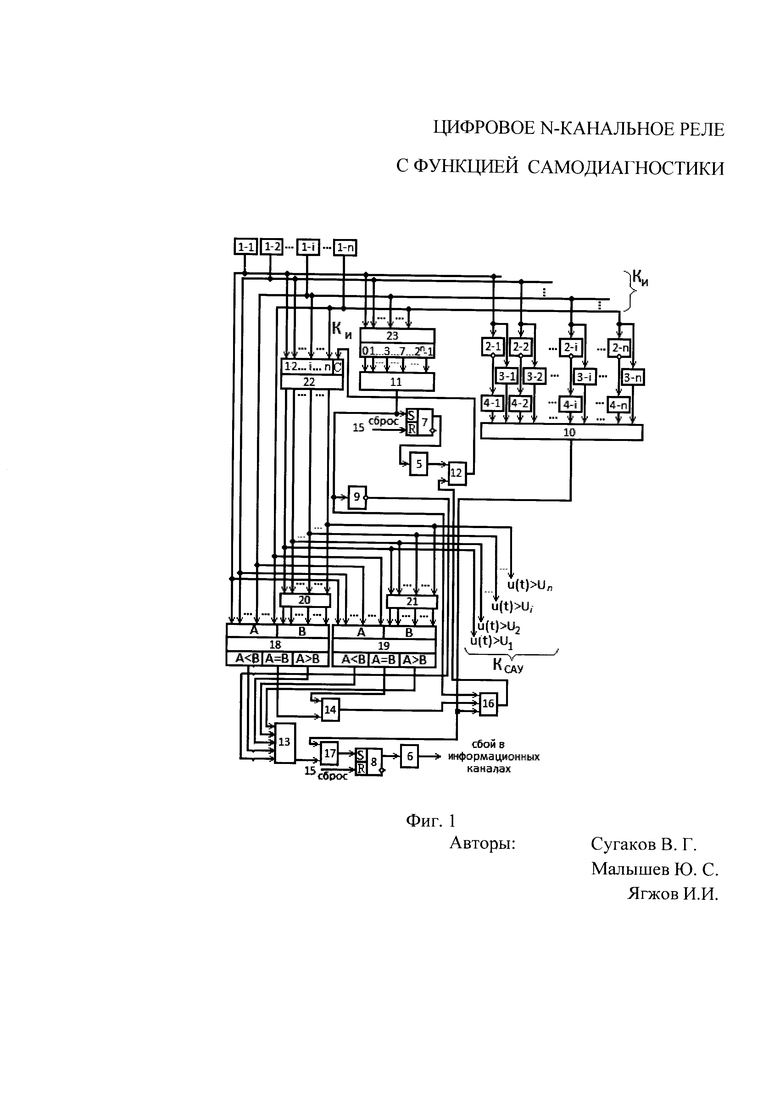

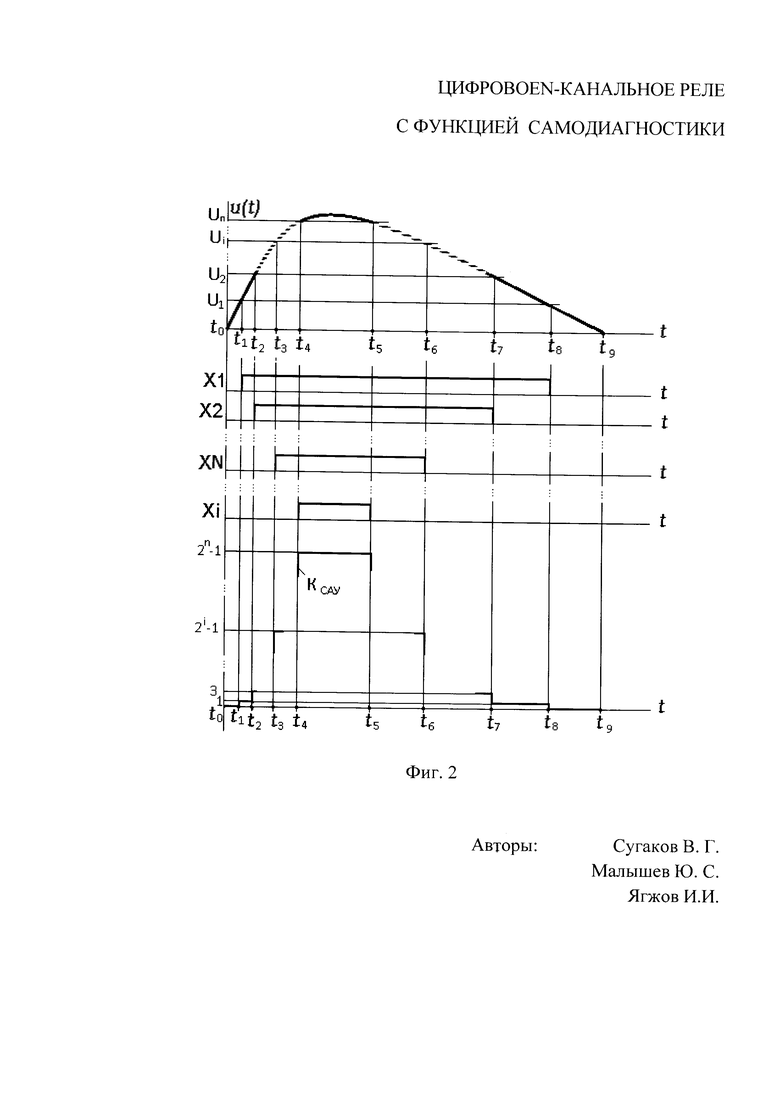

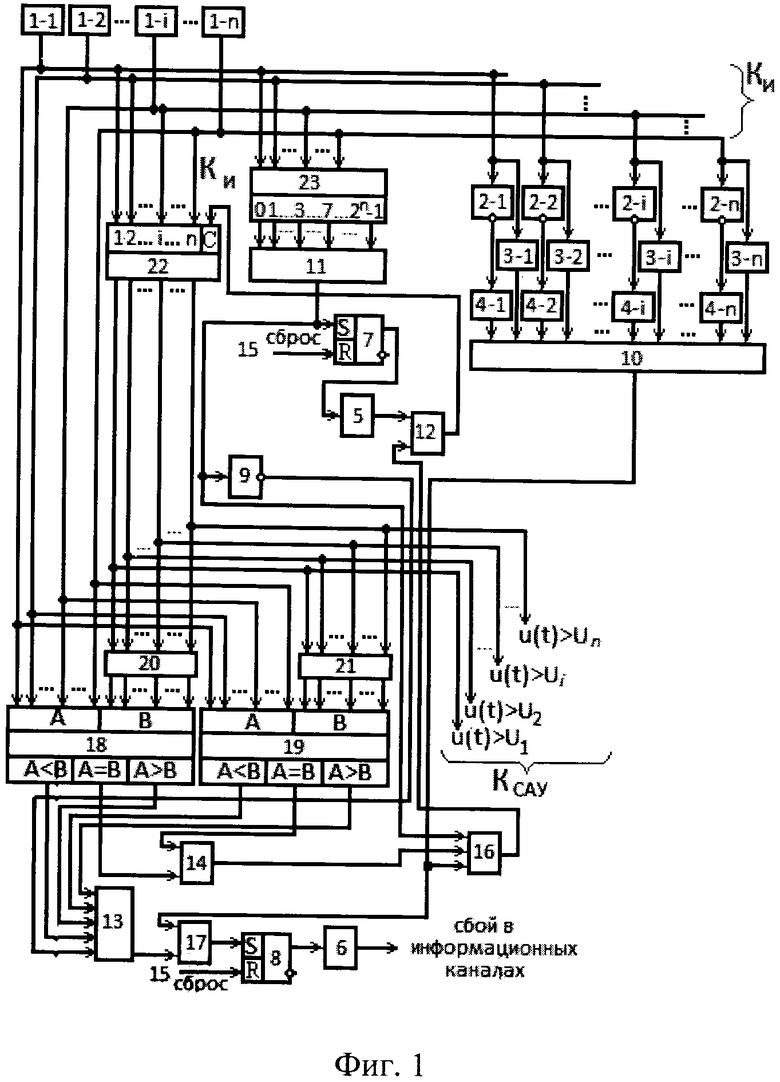

На фиг. 1 представлена схема цифрового пятиканального реле с функцией самодиагностики, на фиг. 2 - эпюры сигналов на элементах устройства.

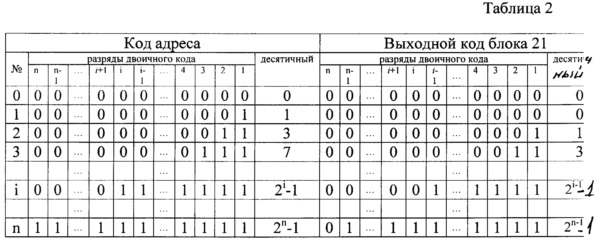

Реле (фиг. 1) включает n приемных датчиков 1-1, 1-2…, 1-i…, 1-n соответствующих уставок, n первых логических элементов НЕ 2-1, 2-2…, 2-i…, 2-n, n первых формирователей коротких импульсов 3-1, 3-2…, 3-i…, 3-n, , n вторых формирователей коротких импульсов 4-1, 4-2…, 4-i…, 4-n, третий формирователь коротких импульсов 5, индикатор 6 сбоя в информационных каналах, первый 7 и второй 8 RS-триггеры, второй логический элемент НЕ 9, первый 10, второй 11, третий 12, четвертый 13 и пятый 14 логические элементы ИЛИ, шину СБРОС 15, первый 16 и второй 17 логические элементы И, первый 18 и второй 19 числовой компаратор, первый 20 и второй 21 блок памяти, регистр памяти 22 и дешифратор 23. По адресам блока памяти 20 записаны коды, представленные в табл. 1, а по адресам блока памяти 21 - в табл. 2.

Реле работает следующим образом. Датчики 1-1, 1-2,…, 1-i, …, 1-n настроены на параметры срабатывания соответственно U1, U2, … Ui,… Un, причем Un>Un-1…>Ui>Ui-1…>U2>U1 (фиг. 2). При включении системы автоматического управления (САУ) подается сигнал на шину СБРОС 15, который поступает на сбросовые входы триггера 7 и 8. На прямых выходах триггеров 7 и 8 сигналы исчезают.

Пусть в исходный момент времени t0 (фиг. 2) контролируемая величина u(t) меньше первой уставки U1, тогда на выходах датчиков 1-1, 1-2, 1-i, …, 1-n сигналы X1, X1, … XI, XN отсутствуют, поэтому на входы регистра 22 и дешифратора 23 поступает нулевой код КИ. Появляется сигнал на нулевом выходе дешифратора 23, который поступает на вход логического элемента ИЛИ 11. Сигнал с выхода переводит элемента ИЛИ 11 переводит триггер 7 в единичное состояние. По фронту сигнала с прямого выхода триггера 7 формирователь коротких импульсов 5 вырабатывает импульс, который проходит через элемента ИЛИ 12 и поступает на вход записи регистра 22. В регистр 22 записывается нулевой код КСАУ=КИ=00…000…00002=010, поступающий в САУ и на входы адреса блоков памяти 20 и 21.

По мере возрастания контролируемой величины u(t) в момент времени t1 (фиг. 2) срабатывает датчик 1-1 и на его выходе появляется сигнал X1. На входы регистра 22, первый вход компаратора 18 и дешифратора 23 поступает код КИ=00…000…00012=110. На первом выходе дешифратора 23 появляется сигнал, который подготавливает по первому входу логический элемент И 16. По нулевому коду на входе адреса блок памяти 20 подает на второй вход компаратора 18 код совпадающий с кодом КИ на первом входе (см. табл. 1), поэтому появляется сигнал на выходе РАВНО компаратора 18, который через элемент ИЛИ 14 подготавливает по второму входу элемент И 16.

Одновременно сигнал X1 с выхода датчика 1-1 поступает на формирователь коротких импульсов 3-1. Импульс с его выхода через элемент ИЛИ 10, элемент И 16 и элемент ИЛИ 12 поступает на вход записи регистра 22, в который заносится очередной код КСАУ=КИ=00…000…00012=110 поступающий в САУ и на входы адреса блоков памяти 20 и 21.

В момент времени t2 (фиг. 2) срабатывает датчик 1-2 и на его выходе появляется сигнал Х2. На входы дешифратора 23, регистра 22 и первый вход компаратора 18 поступает код КИ=00…000…00112=310. На входе адреса блока памяти 20 присутствует предыдущий код КИ, по которому на выходе блока 20 появляется код совпадающий с кодом на первом входе компаратора 18 (см. табл. 1). Сигнал с выхода РАВНО компаратора 18 через элемент ИЛИ 14 подготавливает по второму входу элемент И 16, который по первому входу подготовлен сигналом с третьего выхода дешифратора 23, поступающим через элемент ИЛИ 11. По фронту сигнала Х2 с выхода датчика 1-2 формирователь коротких импульсов 3-2 вырабатывает импульс, который проходя через элементы И 16 и ИЛИ 12 записывает в регистр 22 новый код КСАУ=КИ=00…000…00112=310, подаваемый в САУ и на входы адреса блоков памяти 20 и 21.

При последующем возрастании контролируемой величины u(t) с появлением каждого очередного сигнала XI на выходах датчиков 1-i (момент времени 13 на фиг. 2) формирователь 3-i вырабатывает импульс, посредством которого в регистр 22 производится запись очередного большего кода КСАУ=КИ=00…011…11112=(2i-1)10. Запись кода предваряется его проверкой на компараторе 18, как описано выше.

Когда контролируемая величина u(t) достигает предельного значения в момент времени t4 (фиг. 2) и появляется сигнал XN на выходе датчика 1-n формирователь 3-n вырабатывает импульс, которым в регистр 22 записывается единичный код КСАУ=КИ=11…111…11112=(2n-1)10.

Таким образом по мере монотонного возрастания контролируемой величины u(t) и исправном состоянии информационных каналов они формируют естественную последовательность кодов: КИ=00…000…00002=010, КИ=00…000…00012=110, КИ=00…000…00112=310, …, КИ=00…011…11112=(2n-1)10, …, КИ=11…111…11112=(2n-1)10, поступающих в САУ. Приведенная естественная последовательность кодов подчиняется закону КИ=(2i-1)10, при i=0, 1, 2, 3, …, n.

При уменьшении контролируемой величины u(t) в момент времени t5 (фиг. 2) исчезает сигнал XN на выходе датчика 1-n, и на первый вход компаратора 19, входы регистра 22 и дешифратора 23 поступает код КИ=01…111…11112=(2n-1)10. Появляется сигнал на выходе дешифратора 23, который через элемент ИЛИ 11 подготавливает элемент И 16 по первому входу. По единичному коду, поступающему с выхода регистра 22 на вход адреса блока памяти 21 последний выдает на второй вход компаратора 19 код равный коду на первом его входе (см табл. 2). Сигнал с выхода РАВНО компаратора 19 через элемент ИЛИ 14 подготавливает элемент И 16 по второму входу. Одновременно с исчезновением сигнала XN на выходе датчика 1-n, появляется сигнал на выходе элемента НЕ 2-п, который поступает на вход формирователя 4-n. Импульс с выхода формирователя 4-п через элемент ИЛИ 10 поступает на третий вход элемента И 16. Импульс с выхода элемента И 16 через элемент ИЛИ 12 поступает на вход записи регистра 22, в который производится запись нового кода КСАУ=КИ=01…111…11112=(2n-1-1)10, поступающего в САУ.

По мере дальнейшего уменьшения контролируемой величины u(t) в момент времени t6 (фиг. 2) исчезает сигнал XI на выходе очередного датчика 1-i, а на выходе элемента НЕ 2-i сигнал появляется, и по его фронту формирователь 4-i вырабатывает импульс, с участием которого в регистр 22 заносится новый меньший код КСАУ=КИ=00…011…11112=(2i-1)10. Перед записью код проверяется на компараторе 19, как описано выше.

Аналогично происходит перезапись кода в регистр 22 при последующем уменьшении контролируемой величины.

В момент времени t7 (фиг. 2), когда исчезает сигнал Х2 на выходе датчика 1-2 и появлении импульса на выходе формирователя 4-2 в регистр 22 заносится код КСАУ=КИ=00…000…00012=110.

В момент времени t8 (фиг. 2) пропадает сигнал X1 на выходе датчика 1-1. Появляется импульс на выходе формирования 4-1, и в регистр 22 заносится код КСАУ=КИ=00…000…00002=010.

В результате при монотонном уменьшении контролируемой величины и исправности измерительных каналов в САУ поступают коды из указанной выше естественное последовательности кодов.

Таким образом, при любом поведении контролируемой величины и исправности измерительных каналов в САУ поступают коды, входящие в естественную последовательность кодов. Появление сбойного кода, не принадлежащего этой последовательности, или нарушение очередности появления кодов является признаком неисправности измерительного канала.

Поступление сбойного кода предотвращается устройством следующим образом.

К входам логического элемента ИЛИ 11 подключены выходы дешифратора 23 с номерами соответствующими естественной последовательности кодов 0, 1, 3, 7, 15, …, (2n-1). Пусть в исходном состоянии на выходах всех датчиков 1-1…1-n присутствуют сигналы и в регистр 22 записан код КСАУ=КИ=11…111…11112, подаваемый в САУ.

Если возникает сбой, например, датчика 1-1 и сигнал XI на его выходе пропадает, на вход дешифратора 23 поступает код КИ=11…111…11102, не принадлежащий к числу кодов из естественной последовательности, то сигнал появляется на выходе дешифратора 23, который не подключен к входу элемента ИЛИ 11. Поэтому сигнал на выходе элемента ИЛИ 11 исчезает. Элемент И 16 закрывается по первому входу, предотвращая перезапись кода в регистр 22. Вместе с тем появляется сигнал на выходе элемента НЕ 9. С выхода элемента НЕ 9 сигнал через элемент ИЛИ 13 подготавливает элемент И 17 по второму входу.

Одновременно с исчезновением сигнала XI на входе датчика 1-1 появляется сигнал на выходе элемента НЕ 2-1. По фронту этого сигнала формирователь 4-1 вырабатывает импульс, который через элемент И 17 поступает на единичный вход триггера 8 и он меняет состояние. Сигнал с прямого выхода триггера 8 включает индикатор 6, указывающий на сбой в информационных каналах.

При возникновении других сбойных кодов работа устройства осуществляется как описано выше.

Коды, входящие в естественную последовательность, должны появляться в определенном порядке. За кодом КИ=(2i-1)10 при росте контролируемой величины должен следовать код КИ=(2i+1-1)10, а при уменьшении - код КИ=(2i+1-1)10. Нарушение такой последовательности появления кодов является признаком сбоя в информационных каналах. В таких случаях устройство работает следующим образом. В блоке памяти 20 по адресам записаны последующие коды при возрастании контролируемой величины, а в блоке памяти 21 - при снижении контролируемой величины. Пусть в регистр 22 записан код КСАУ=КИ=00…000…00112 при возрастании контролируемой величины, а в результате сбоя в информационных каналах одновременно появляются сигналы Х3, Х4 на выходах датчиков 1-3, 1-4 и формируется код КИ=00…000…11112, который поступает на входы регистра 22, дешифратора 23 и первые входы компараторов 18 и 19. По адресу заданному регистром 22 на выходе блока памяти 20 установится код 00…000…01112 (см. табл. 1), который поступает на второй вход компаратора 18. На выходе БОЛЬШЕ (А>В) компаратора 18 появляется сигнал, который подается на третий вход элемента ИЛИ 13. Сигнал с выхода элемента ИЛИ 13 подготавливает элемент И 17 по второму входу. Одновременно по фронту сигналов Х3, Х4 с выходов датчиков 1-3, 1-4 формируются импульсы на выходах формирователей 2-3, 2-4, которые поступают на входы элемента ИЛИ 10. Сигнал с выхода элемента ИЛИ 10 поступает на первый вход элемента И 17 и он открывается, подавая импульс на единичный вход триггера 8, который меняет свое состояние. Сигнал с прямого выхода триггера 8 включает индикатор 6, указывающего на сбой в информационных каналах. Вместе с тем по адресу заданному регистром 22 на выходе блока памяти 21 установится код 00…000…00012 (см. табл. 2), который подается на второй вход компаратора 19, поэтому сигнал появляется на его выходе БОЛЬШЕ (А>В). На выходах РАВНО компараторов 18 и 19 сигналы отсутствуют, потому сигнал отсутствует на выходе элемента ИЛИ 14, а элемент оказывается закрытым по второму входу, препятствуя записи в регистр 22 недостоверного кода КИ.

При других случаях нарушения последовательности появления кодов устройство работает аналогично описанному выше.

Таким образом, реле имеет расширенные функциональные возможности, заключающиеся в повышении достоверности выходной информации путем предотвращения поступления в САУ информации по необходимому числу n каналов при их сбое.

Источники информации

1. Сугаков В.Г. Основы автоматизации военных передвижных источников электрической энергии: учеб. пособие. - Кстово: НФВИУ, 2003. 168 с.

2. Дудченко В.Н., Аверкиев А. Н. Измерение неэлектрических величин: конспект лекций. - Кстово: НВВИКУ, 1997. 54 с.

3. Цифровой измеритель скорости вращения. Описание изобретения к авторскому свидетельству RU 1075167, 1984.

4. Комплекс средств контроля дизеля КСКД 17.5. Техническое описание и инструкция по эксплуатации ЗУ2.008.006 ТО. 1994. С. 35-37.

5. Патент на изобретение №261495 по заявке 2016112100 от 30.03.2016, кл. G01P 3/54

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ ЧЕТЫРЕХКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2017 |

|

RU2659990C1 |

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ САМОДИАГНОСТИКИ | 2017 |

|

RU2671545C1 |

| ЧЕТЫРЕХКАНАЛЬНОЕ ЦИФРОВОЕ РЕЛЕ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2018 |

|

RU2707420C1 |

| СИСТЕМА РЕГУЛИРОВАНИЯ ВОЗБУЖДЕНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ВНЕШНЕЙ ФОРСИРОВКОЙ | 2019 |

|

RU2723989C1 |

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2018 |

|

RU2706198C1 |

| ЦИФРОВОЕ РЕЛЕ ЧАСТОТЫ ВРАЩЕНИЯ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2016 |

|

RU2618495C1 |

| ДВУНАПРАВЛЕННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ | 2024 |

|

RU2826860C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2819573C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2022 |

|

RU2795501C1 |

| ДВУЗОННОЕ УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ УСТАНОВИВШЕГОСЯ ОТКЛОНЕНИЯ ЧАСТОТЫ | 2023 |

|

RU2799658C1 |

Изобретение относится к средствам автоматизации и может быть использовано, в частности, в системах управления электроагрегатов генераторных с приводом от двигателя внутреннего сгорания. Технический результат: расширение функциональных возможностей путем увеличения числа контролируемых каналов выходной информации. Сущность: устройство включает n приемных датчиков 1-1, 1-2…, 1-i…, 1-n соответствующих уставок, n первых логических элементов НЕ 2-1, 2-2…, 2-i…, 2-n, n первых формирователей коротких импульсов 3-1, 3-2…, 3-i…, 3-n, n вторых формирователей коротких импульсов 4-1, 4-2…, 4-i…, 4-n, третий формирователь коротких импульсов 5, индикатор 6 сбоя в информационных каналах, первый 7 и второй 8 RS-триггеры, второй логический элемент НЕ 9, первый 10, второй 11, третий 12, четвертый 13 и пятый 14 логические элементы ИЛИ, шину СБРОС 15, первый 16 и второй 17 логические элементы И, первый 18 и второй 19 числовой компаратор, первый 20 и второй 21 блок памяти, регистр памяти 22 и дешифратор 23. 1 ил., 2 табл.

Цифровое n-канальное реле с функцией самодиагностики, содержащее n приемных реле, выходы которых соединены с соответствующими входами дешифратора, индикатор состояния, первый и второй числовой компаратор, первый и второй логические элементы И, первый из n логический элемент НЕ, второй логический элемент НЕ, первый и второй RS-триггер, регистр памяти, первый, второй и третий логический элемент ИЛИ, первый из n формирователей коротких импульсов, отличающееся тем, что с целью расширения функциональных возможностей снабжено со второго по n-й первыми формирователями коротких импульсов, n вторыми формирователями коротких импульсов и третьим формирователем коротких импульсов, четвертым и пятым логическими элементами ИЛИ, шиной СБРОС, первым и вторым блоками памяти, разряды входа адреса которых соединены с соответствующими разрядами выхода регистра памяти, а разряды выходов подключены к соответствующим разрядам вторых входов соответственно первого и второго числового компаратора, разряды первых входов которых связаны с соответствующими разрядами входа регистра памяти, выходами соответствующих с первого по n-й приемных реле, входами соответствующих с первого по n-й первых логических элементов НЕ и входами соответствующих с первого по n-й первых формирователей коротких импульсов, выходы которых подключены к соответствующим четным входам первого логического элемента ИЛИ, к нечетным входам которого подключены выходы соответствующих с первого по n-й вторых формирователей коротких импульсов, с входами которых соединены выходы соответствующих с первого по n-й первых логических элементов НЕ, а выход первого логического элемента ИЛИ подключен к первому входу второго логического элемента И и третьему входу первого логического элемента И, выход которого подключен к второму входу третьего логического элемента ИЛИ, связанного выходом с входом записи регистра памяти, а первым входом - с выходом третьего формирователя коротких импульсов, вход которого соединен с прямым выходом первого RS-триггера, связанного нулевым входом с шиной СБРОС, а единичным входом - с выходом второго логического элемента ИЛИ, входом второго логического элемента НЕ и первым входом первого логического элемента И, второй вход которого подключен к выходу пятого логического элемента ИЛИ, соединенного первым входом с выходом РАВНО первого числового компаратора, выход БОЛЬШЕ которого подключен к третьему входу четвертого логического элемента ИЛИ, связанного пятым входом с выходом второго логического элемента НЕ, четвертым входом - с выходом МЕНЬШЕ первого числового компаратора, вторым входом - с выходом МЕНЬШЕ второго числового компаратора, первым входом - с выходом БОЛЬШЕ второго числового компаратора, выход РАВНО которого подключен к второму входу пятого логического элемента ИЛИ, причем выход четвертого логического элемента ИЛИ соединен с вторым входом второго логического элемента И, выход которого соединен с единичным входом второго RS-триггера, связанного нулевым входом с шиной СБРОС, а выходом - с входом индикатора, кроме того, (2i-1)-е разряды выхода дешифратора, где i=0, 1, 2, …, n, соединены с соответствующими входами второго логического элемента ИЛИ, а выходы регистра памяти являются выходами устройства.

| ЦИФРОВОЕ РЕЛЕ ЧАСТОТЫ ВРАЩЕНИЯ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2016 |

|

RU2618495C1 |

| Цифровой измеритель величины отклонения скорости от заданной | 1981 |

|

SU953570A1 |

| Цифровой измеритель скорости вращения | 1981 |

|

SU1075167A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЧАСТОТЫ ВРАЩЕНИЯ ВРАЩАЮЩЕЙСЯ ДЕТАЛИ МАШИНЫ | 2003 |

|

RU2313099C2 |

| US 5404304, 04.04.1995 | |||

| US 5740083, 14.04.1998. | |||

Авторы

Даты

2019-04-18—Публикация

2018-03-21—Подача