Изобретение относится к области измерительной техники и может быть использовано для преобразования аналоговых электрических сигналов эквивалентно позиционному или модулярному представлению.

Известен аналого-цифровой преобразователь в системе остаточных классов (пат. 2433527 Российская Федерация, МПК7 Н03М 1/28; заявл. 12.04.2010; опубл. 10.11.2011), содержащий блоки слежения-хранения, аналогово-цифровые преобразователи, цифроаналоговые преобразователи, блоки вычитания, выходные шины кодов остатков в СОК, вход. Недостаток - низкие функциональные возможности.

Известен аналого-цифровой преобразователь в системе остаточных классов (пат. 2546621 Российская Федерация, МПК7 Н03М 1/28; заявл. 09.01.2014; опубл. 10.04.2015), содержащий вход, блоки слежения-хранения, аналого-цифровой преобразователь, цифроаналоговый преобразователь, блок вычитания, источник напряжения смещения, регистры-защелки, выходные шины кодов остатков в СОК. Недостаток - низкие функциональные возможности.

Наиболее близким к заявляемому является изобретение (пат. 2103698 Российская Федерация, МПК6 G01R 25/00; заявл. 20.05.1996; опубл. 27.01.1998), содержащее формирователь импульсов, два блока деления, блок дифференцирования, два блока выборки и хранения, два компаратора, тригонометрический преобразователь, источник опорного напряжения, усилитель с регулируемым коэффициентом передачи, сумматор. Недостаток - низкие функциональные возможности, ограниченные преобразованием сдвига фазы в уровень напряжения только пропорционально позиционному представлению.

Техническая задача, на решение которой направлено заявляемое устройство, состоит в расширении функциональных возможностей устройства.

Технический результат выражается в возможности преобразования уровня входного сигнала пропорционально заданному модулю системы остаточных классов, а также сдвига фазы гармонического сигнала пропорционально позиционному и модулярному представлению через реализацию единого метода измерения разности фаз.

Технический результат достигается тем, что в модулярный измерительный преобразователь, содержащий первый и второй блок выборки и хранения, первый и второй компаратор, первый тригонометрический преобразователь, источник опорного напряжения, введены первый, второй, третий, четвертый, пятый и шестой коммутаторы, первый и второй генераторы, управляемые напряжением, первый и второй элементы И, первый и второй интеграторы, третий, четвертый, пятый, шестой, седьмой и восьмой блоки выборки и хранения, первый и второй триггеры, третий и четвертый компараторы, первый и второй демультиплексоры, второй тригонометрический преобразователь, первый, второй, третий и четвертый блоки вычитания, элемент НЕ, шифратор, цифроаналоговый преобразователь, входы устройства «такт», «фаза», «опора» и «уровень», при этом вход устройства «фаза» объединен с первым входом первого коммутатора, при этом выход первого генератора, управляемого напряжением соединен со вторым входом первого коммутатора, выход которого соединен с входом первого и второго тригонометрического преобразователя, а также входом первого компаратора, выход которого соединен с входом элемента НЕ, первым входом первого триггера, а также первым входом первого элемента И, выход которого соединен с входом первого интегратора, выход которого соединен с первым входом первого блока выборки и хранения, выход которого соединен с первым входом третьего компаратора, выход которого соединен с первым входом второго демультиплексора, выход которого соединен со вторым входом шифратора, при этом выход первого триггера соединен с первым входом шифратора, второй выход которого соединен с третьим входом четвертого коммутатора, при этом первый выход шифратора соединен с входом цифроаналогового преобразователя, выход которого соединен со вторым входом первого блока вычитания, выход которого соединен с первым входом шестого коммутатора, а также с входом пятого, шестого и восьмого блока выборки и хранения, выход которого соединен со вторым входом третьего коммутатора, при этом вход устройства «уровень» объединен с первым входом третьего коммутатора, выход которого соединен с входом первого и второго генератора управляемого напряжением, выход которого соединен со вторым входом второго коммутатора, при этом вход устройства «опора» объединен с первым входом второго коммутатора, выход которого соединен с входом второго компаратора, выход которого соединен со вторым входом первого и второго элемента И, первым входом второго триггера, а также первым входом первого демультиплексора, при этом вход устройства «такт» объединен со вторым входом первого демультиплексора, выход которого соединен со вторым входом первого, второго, третьего и четвертого блока выборки и хранения, а также вторым входом первого и второго триггера, выход которого соединен со вторым входом второго демультиплексора, при этом выход элемента НЕ соединен с первым входом второго элемента И, выход которого соединен с входом второго интегратора, выход которого соединен с первым входом второго блока выборки и хранения, выход которого соединен со вторым входом третьего компаратора, при этом выход первого тригонометрического преобразователя соединен с первым входом третьего блока выборки и хранения, выход которого соединен с первым входом четвертого коммутатора, при этом выход второго тригонометрического преобразователя соединен с первым входом четвертого блока выборки и хранения, выход которого соединен со вторым входом четвертого коммутатора, выход которого соединен с первым входом первого блока вычитания, при этом первый выход источника опорного напряжения соединен с первым входом пятого коммутатора и вторым входом второго блока вычитания, при этом второй выход источника опорного напряжения соединен со вторым входом пятого коммутатора, выход которого соединен со вторым входом третьего блока вычитания, выход которого соединен с первым входом четвертого блока вычитания, при этом выход шестого блока выборки и хранения соединен с первым входом третьего блока вычитания и вторым входом четвертого компаратора, выход которого соединен с третьим входом пятого коммутатора, при этом выход пятого блока выборки и хранения соединен с первым входом четвертого компаратора и первым входом второго блока вычитания, выход которого соединен со вторым входом четвертого блока вычитания, выход которого соединен со вторым входом шестого коммутатора, выход которого соединен с входом седьмого блока выборки и хранения, выход которого является выходом устройства.

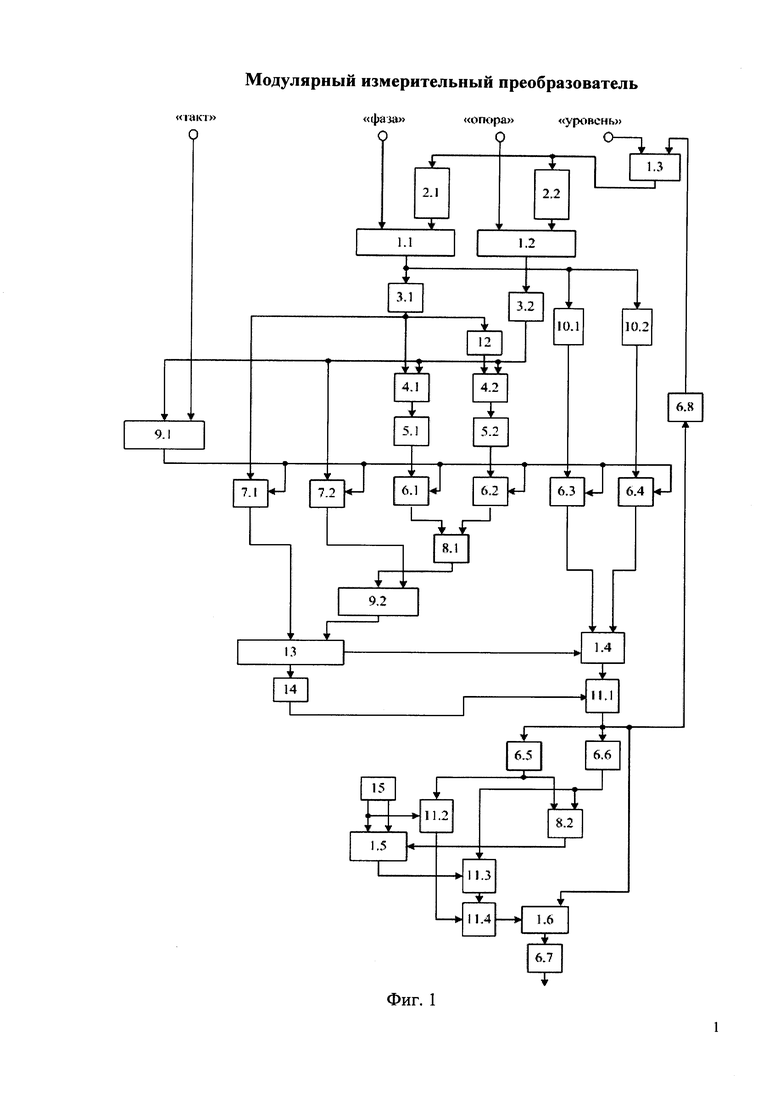

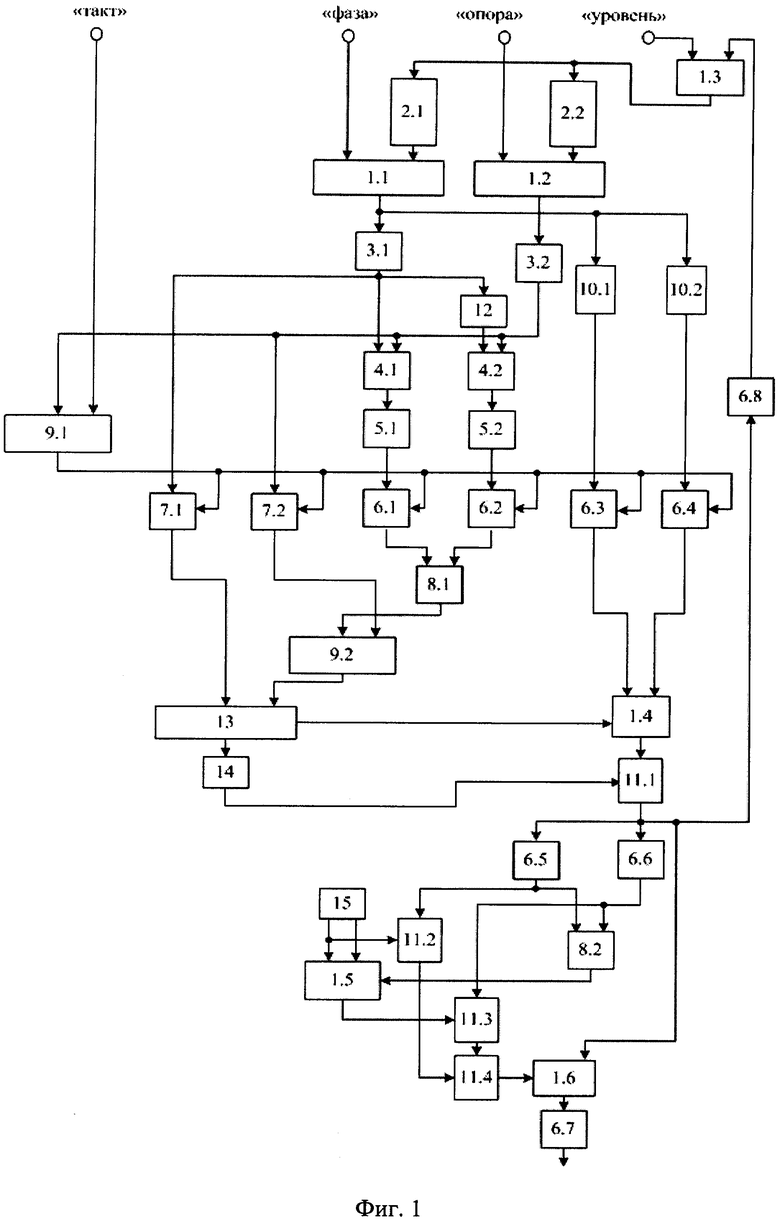

На фиг. 1 представлена структурная схема модулярного измерительного преобразователя.

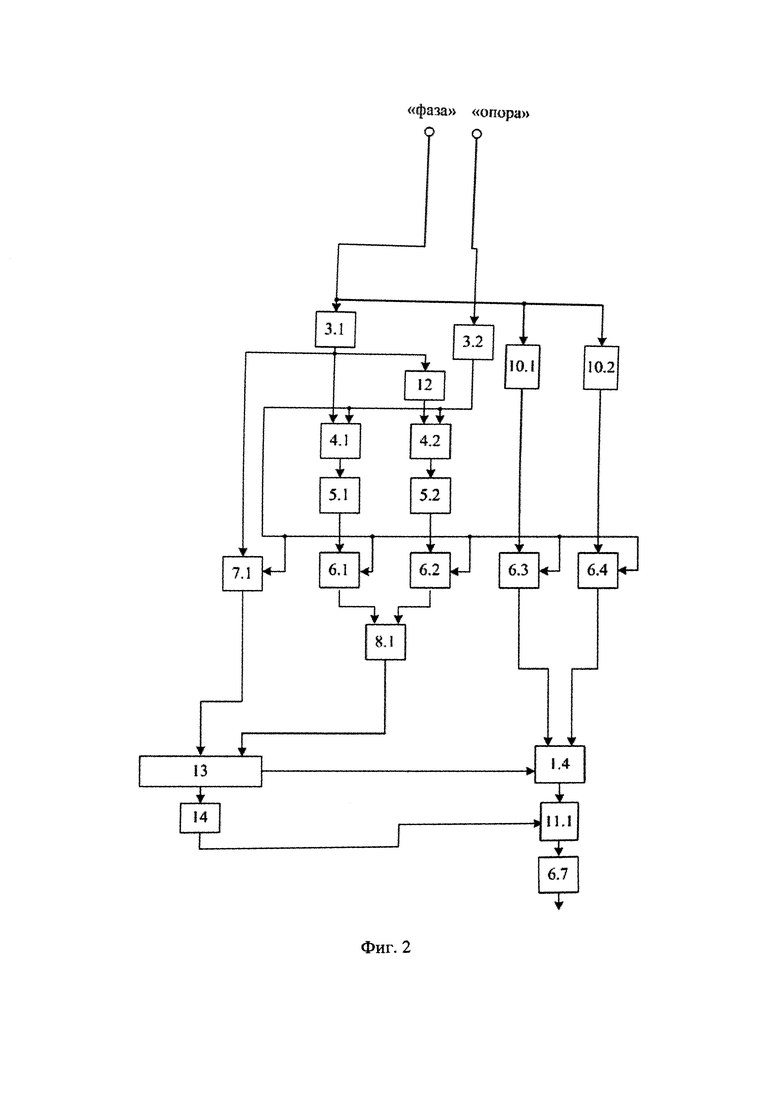

На фиг. 2 приведена схема коммутации устройства для работы в режиме №1.

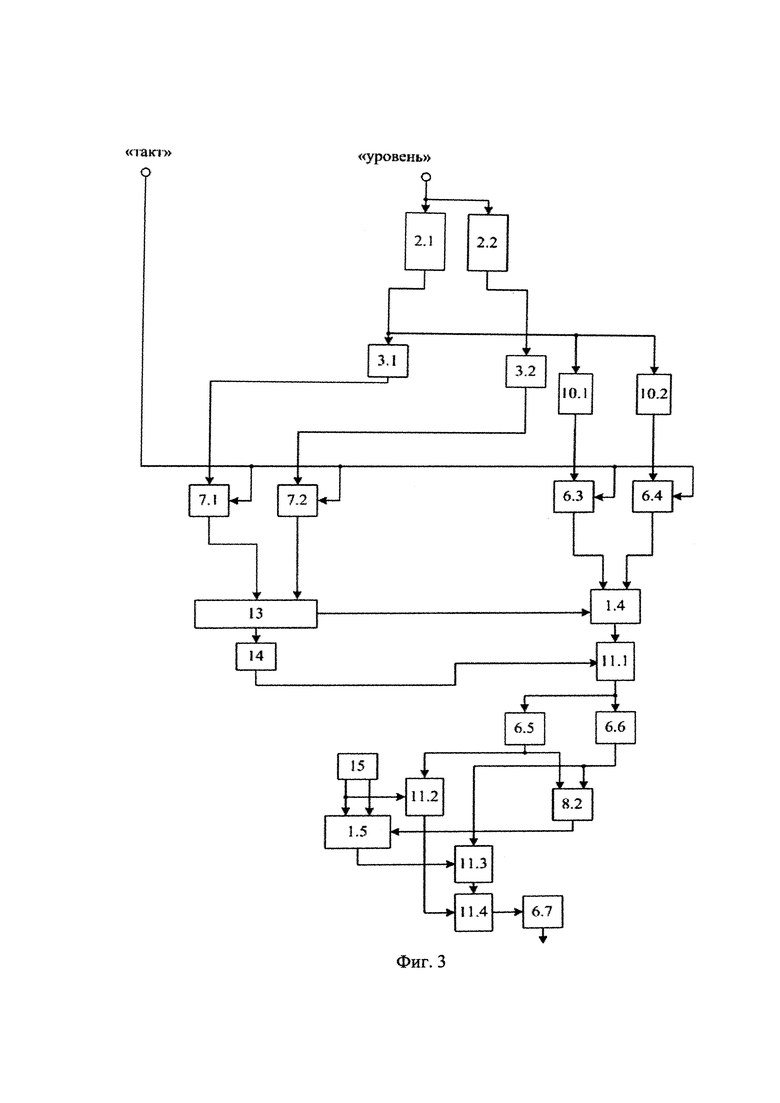

На фиг. 3 приведена схема коммутации устройства для работы в режиме №2.

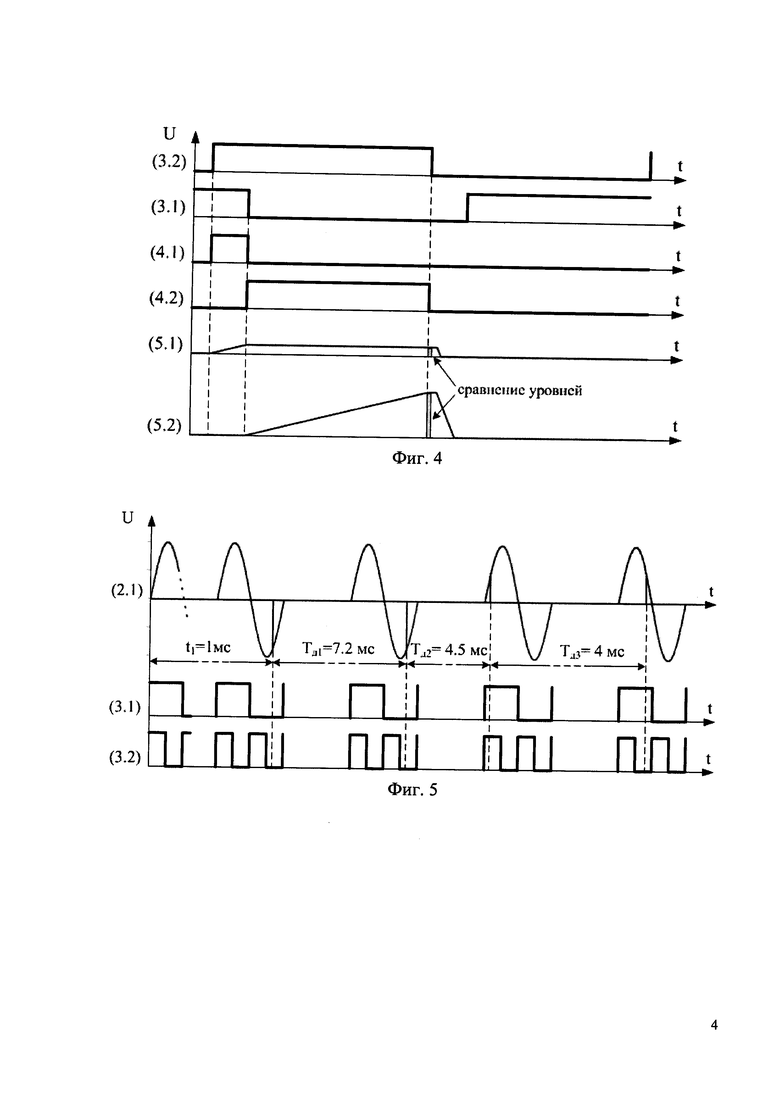

На фиг. 4 представлена динамическая диаграмма напряжений на выходах ряда блоков при работе устройства в режиме №1.

На фиг. 5 представлена динамическая диаграмма напряжений на выходах ряда блоков при работе устройства в режиме №2.

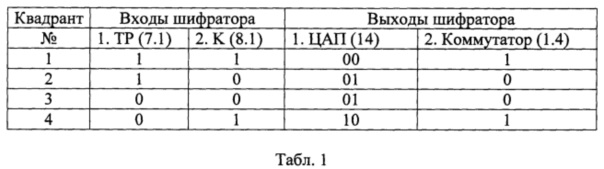

В табл. 1 представлены входные и выходные значения шифратора 13 в режиме №1.

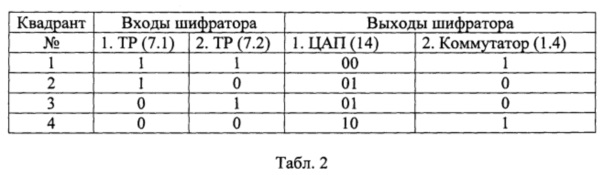

В табл. 2 представлены входные и выходные значения шифратора 13 в режиме №2.

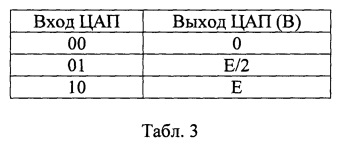

В табл. 3 представлены входные и выходные значения ЦАП 14.

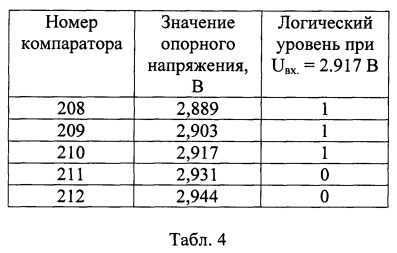

В табл. 4 представлены опорные напряжений параллельного АЦП, и взвешивание на их основе соответствующего входного сигнала.

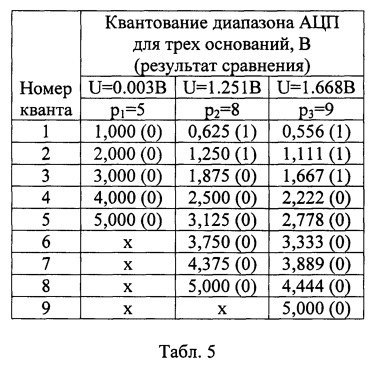

В табл. 5 представлены опорные напряжений параллельных АЦП для оснований СОК p1=5, p2=8, р3=9, и результаты взвешивания соответствующих модулярных аналоговых эквивалентов.

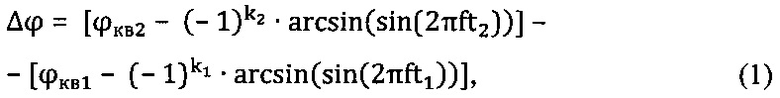

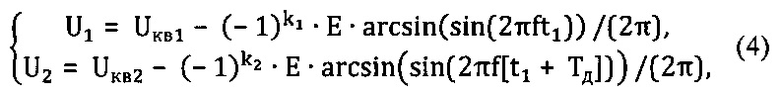

Сущность изобретения заключается в реализации метода вычисления разности фаз гармонического колебания:

где ϕкв1 и ϕкв2 - угол кратный 90° в моменты времени t1 и t2; k1 и k2 - коэффициенты в моменты времени t1 и t2, принимающие значение «0» или «1» в зависимости от квадранта и режима; f - частота гармонического колебания.

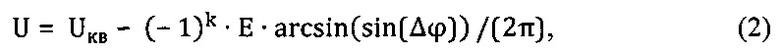

Поскольку в первом режиме замеряются фазы двух гармонических сигналов, то этот процесс осуществляется одновременно, при этом основная гармоника является тактирующей. На момент завершения первого полупериода основной гармоники (ϕ1=2πft1=π), необходимого для определения квадранта, осуществляется замер фазы отстающей гармоники ϕ2=2πft2=π+Δϕ. Избавление полученных фаз от величины π приводит к обнулению ϕ1 и ϕкв1. Результат преобразования представлен эквивалентным уровнем положительного напряжения в диапазоне от 0 до Е:

где Uкв - напряжение, кратное Е/4, определяемое по номеру квадранта из табл. 3, k - коэффициент, определяемый по номеру квадранта из табл. 1 как выход «2. Коммутатор».

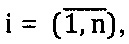

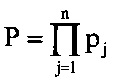

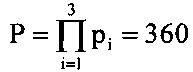

Во втором режиме преобразуется уровень входного напряжения к уровню выходного напряжения пропорционально вычету по основанию pi, где  a n - количество оснований применяемой системы остаточных классов (СОК). При линейном росте входного напряжения от 0 до Е, выходное напряжение P/pi раз линейно изменяется от 0 до Е, мгновенно переходя в 0 при достижении уровня Е. Здесь

a n - количество оснований применяемой системы остаточных классов (СОК). При линейном росте входного напряжения от 0 до Е, выходное напряжение P/pi раз линейно изменяется от 0 до Е, мгновенно переходя в 0 при достижении уровня Е. Здесь  - объем диапазона чисел СОК. Для применения метода (1) входной уровень преобразуется генератором управляемого напряжением (ГУН) в гармонику. Поскольку разность фаз гармоники на постоянном промежутке времени прямо пропорциональна частоте, а частота с ГУН прямо пропорциональна входному напряжению, то первое эквивалентно последнему. Пусть изменению входного напряжения от 0 до Е соответствует диапазон выходных частот ГУН от 0 до Fmax, тогда время между двумя замерами t2-t1=Тд - период дискретизации, есть:

- объем диапазона чисел СОК. Для применения метода (1) входной уровень преобразуется генератором управляемого напряжением (ГУН) в гармонику. Поскольку разность фаз гармоники на постоянном промежутке времени прямо пропорциональна частоте, а частота с ГУН прямо пропорциональна входному напряжению, то первое эквивалентно последнему. Пусть изменению входного напряжения от 0 до Е соответствует диапазон выходных частот ГУН от 0 до Fmax, тогда время между двумя замерами t2-t1=Тд - период дискретизации, есть:

Эквиваленты замеров фаз - уровни напряжения - в моменты времени t1 и t2 определяются из выражений:

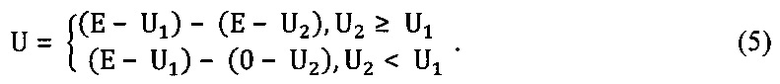

где Uкв1,2 - напряжения, кратные Е/4 и определяемые по номеру квадранта из табл. 3, k1,2 - коэффициенты, определяемые по номеру квадранта из табл. 2 как выход «2. Коммутатор». Конечный результат, соответствующий разности фаз и модулярному представлению входного уровня напряжения, есть:

Цифровые демультиплексоры и ряд аналоговых коммутаторов непосредственно не участвуют в процессе измерения фазы, а только соединяют блоки схемы согласно первому, второму или третьему режиму, поэтому на фиг. 2 и фиг. 3 они не указаны. Тригонометрический преобразователь арксинуса может быть реализован, например, на основе диодов (патент РФ №2195074, фиг. 2, блок 14). Тактирование блоков, требующих управления, таких как интеграторы, коммутаторы, шифратор, демультиплексоры, БВХ и ГУН, кроме случаев, когда это непосредственно указано в схеме преобразователя, осуществляется внешним устройством, например процессором, здесь (на фиг. 1) не отраженным. Вход «такт» соединен с одним из выходов данного внешнего устройства управления.

Дополнительным эффектом является возможность работы преобразователя по произвольному основанию pi не только выбранной СОК, но и произвольной СОК с объемом диапазона чисел вплоть до 108, за счет манипуляции периодом дискретизации Тд и максимальной частотой ГУН Fmax.

Показанный на фиг. 1 модулярный измерительный преобразователь содержит коммутаторы 1.1-1.6, генераторы управляемые напряжением (ГУН) 2.1-2.2, компараторы 3.1-3.2 и 8.1-8.2, элементы И 4.1-4.2, интеграторы 5.1-5.2, блоки выборки и хранения (БВХ) 6.1-6.8, триггеры 7.1-7.2, демультиплексоры 9.1-9.2, тригонометрические преобразователи 10.1-10.2, блоки вычитания 11.1-11.4, элемент НЕ 12, шифратор 13, цифроаналоговый преобразователь (ЦАП) 14, источник опорного напряжения 15, входы «такт», «фаза», «опора» и «уровень».

Вход устройства «фаза» объединен с первым входом коммутатора 1.1, при этом выход ГУН 2.1 соединен со вторым входом коммутатора 1.1, выход которого соединен с входом тригонометрических преобразователей 10.1 и 10.2, а также входом компаратора 3.1, выход которого соединен с входом элемента НЕ 12, первым входом триггера 7.1, а также первым входом элемента И 4.1, выход которого соединен с входом интегратора 5.1, выход которого соединен с первым входом БВХ 6.1, выход которого соединен с первым входом компаратора 8.1, выход которого соединен с первым входом демультиплексора 9.2, выход которого соединен со вторым входом шифратора 13, при этом выход триггера 7.1 соединен с первым входом шифратора 13, второй выход которого соединен с третьим входом коммутатора 1.4, при этом первый выход шифратора 13 соединен с входом ЦАП 14, выход которого соединен со вторым входом блока вычитания 11.1, выход которого соединен с первым входом коммутатора 1.6, а также с входом БВХ 6.5, БВХ 6.6 и БВХ 6.8, выход которого соединен со вторым входом коммутатора 1.3, при этом вход устройства «уровень» объединен с первым входом коммутатора 1.3, выход которого соединен с входом ГУН 2.1 и ГУН 2.2, выход которого соединен со вторым входом коммутатора 1.2, при этом вход устройства «опора» объединен с первым входом коммутатора 1.2, выход которого соединен с входом компаратора 3.2, выход которого соединен со вторым входом элементов И 4.1-4.2, первым входом триггера 7.2, а также первым входом демультиплексора 9.1, при этом вход устройства «такт» объединен со вторым входом демультиплексора 9.1, выход которого соединен со вторым входом БВХ 6.1-6.4, а также вторым входом триггера 7.1 и триггера 7.2, выход которого соединен со вторым входом демультиплексора 9.2, при этом выход элемента НЕ 12 соединен с первым входом элемента И 4.2, выход которого соединен с входом интегратора 5.2, выход которого соединен с первым входом БВХ 6.2, выход которого соединен со вторым входом компаратора 8.1, при этом выход тригонометрического преобразователя 10.1 соединен с первым входом БВХ 6.3, выход которого соединен с первым входом коммутатора 1.4, при этом выход тригонометрического преобразователя 10.2 соединен с первым входом БВХ 6.4, выход которого соединен со вторым входом коммутатора 1.4, выход которого соединен с первым входом блока вычитания 11.1, при этом первый выход источника опорного напряжения 15 соединен с первым входом коммутатора 1.5 и вторым входом блока вычитания 11.2, при этом второй выход источника опорного напряжения 15 соединен со вторым входом коммутатора 1.5, выход которого соединен со вторым входом блока вычитания 11.3, выход которого соединен с первым входом блока вычитания 11.4, при этом выход БВХ 6.6 соединен с первым входом блока вычитания 11.3 и вторым входом компаратора 8.2, выход которого соединен с третьим входом коммутатора 1.5, при этом выход БВХ 6.5 соединен с первым входом компаратора 8.2 и первым входом блока вычитания 11.2, выход которого соединен со вторым входом блока вычитания 11.4, выход которого соединен со вторым входом коммутатора 1.6, выход которого соединен с входом БВХ 6.7, выход которого является выходом устройства.

Показанная на фиг. 2 схема коммутации устройства для работы в режиме №1 содержит коммутатор 1.4, компараторы 3.1-3.2 и компаратор 8.1, элементы И 4.1-4.2, интеграторы 5.1-5.2, БВХ 6.1-6.4 и БВХ 6.7, триггер 7.1, тригонометрические преобразователи 10.1-10.2, блок вычитания 11.1, элемент НЕ 12, шифратор 13, ЦАП 14, входы «фаза» и «опора».

Вход устройства «фаза» объединен с входом тригонометрических преобразователей 10.1 и 10.2, а также входом компаратора 3.1, выход которого соединен с входом элемента НЕ 12, первым входом триггера 7.1, а также первым входом элемента И 4.1, выход которого соединен с входом интегратора 5.1, выход которого соединен с первым входом БВХ 6.1, выход которого соединен с первым входом компаратора 8.1, выход которого соединен со вторым входом шифратора 13, при этом выход триггера 7.1 соединен с первым входом шифратора 13, второй выход которого соединен с третьим входом коммутатора 1.4, при этом первый выход шифратора 13 соединен с входом ЦАП 14, выход которого соединен со вторым входом блока вычитания 11.1, при этом вход устройства «опора» объединен с входом компаратора 3.2, выход которого соединен со вторым входом элементов И 4.1-4.2, со вторым входом БВХ 6.1-6.4, а также вторым входом триггера 7.1, при этом выход элемента НЕ 12 соединен с первым входом элемента И 4.2, выход которого соединен с входом интегратора 5.2, выход которого соединен с первым входом БВХ 6.2, выход которого соединен со вторым входом компаратора 8.1, при этом выход тригонометрического преобразователя 10.1 соединен с первым входом БВХ 6.3, выход которого соединен с первым входом коммутатора 1.4, при этом выход тригонометрического преобразователя 10.2 соединен с первым входом БВХ 6.4, выход которого соединен со вторым входом коммутатора 1.4, выход которого соединен с первым входом блока вычитания 11.1, выход которого соединен с входом БВХ 6.7, выход которого является выходом устройства.

Показанная на фиг. 3 схема коммутации устройства для работы в режиме №2 содержит коммутаторы 1.4-1.5, ГУН 2.1-2.2, компараторы 3.1-3.2 и компаратор 8.2, БВХ 6.3-6.7, триггеры 7.1-7.2, тригонометрические преобразователи 10.1-10.2, блоки вычитания 11.1-11.4, шифратор 13, ЦАП 14, источник опорного напряжения 15, входы «такт» и «уровень».

Вход устройства «уровень» объединен с входом ГУН 2.2 и ГУН 2.1, выход которого соединен с входом тригонометрических преобразователей 10.1 и 10.2, а также входом компаратора 3.1, выход которого соединен с первым входом триггера 7.1, выход которого соединен с первым входом шифратора 13, второй выход которого соединен с третьим входом коммутатора 1.4, при этом первый выход шифратора 13 соединен с входом ЦАП 14, выход которого соединен со вторым входом блока вычитания 11.1, выход которого соединен с входом БВХ 6.5-6.6, при этом выход ГУН 2.2 соединен с входом компаратора 3.2, выход которого соединен с первым входом триггера 7.2, выход которого соединен со вторым входом шифратора 13, при этом вход устройства «такт» объединен со вторым входом триггеров 7.1-7.2 и БВХ 6.3-6.4, при этом выход тригонометрического преобразователя 10.1 соединен с первым входом БВХ 6.3, выход которого соединен с первым входом коммутатора 1.4, при этом выход тригонометрического преобразователя 10.2 соединен с первым входом БВХ 6.4, выход которого соединен со вторым входом коммутатора 1.4, выход которого соединен с первым входом блока вычитания 11.1, при этом первый выход источника опорного напряжения 15 соединен с первым входом коммутатора 1.5 и вторым входом блока вычитания 11.2, при этом второй выход источника опорного напряжения 15 соединен со вторым входом коммутатора 1.5, выход которого соединен со вторым входом блока вычитания 11.3, выход которого соединен с первым входом блока вычитания 11.4, при этом выход БВХ 6.6 соединен с первым входом блока вычитания 11.3 и вторым входом компаратора 8.2, выход которого соединен с третьим входом коммутатора 1.5, при этом выход БВХ 6.5 соединен с первым входом компаратора 8.2 и первым входом блока вычитания 11.2, выход которого соединен со вторым входом блока вычитания 11.4, выход которого соединен с входом БВХ 6.7, выход которого является выходом устройства.

Работа устройства осуществляется в трех режимах. Первый режим предназначен для преобразования сдвига фазы гармонического сигнала пропорционально позиционному представлению. Второй - для уровня входного сигнала пропорционально заданному модулю системы остаточных классов. Третий является последовательной комбинацией первого и второго режимов и осуществляет преобразование сдвига фазы гармонического сигнала пропорционально модулярному представлению.

Для работы в первом режиме устройство коммутируется, как показано на фиг. 2. На вход «опора» подается основной гармонический сигнал, а на вход «фаза» смещенный (отстающий по фазе). Компараторы 3.1 и 3.2, сравнивая с уровнем нуля, преобразуют гармонические сигналы в прямоугольные. Продолжительность единичного уровня основного прямоугольного сигнала с 3.2 разбивается элементами И 4.1 и 4.2 на две части в соответствии с фазовым сдвигом сигнала с 3.1. Полученные таким образом прямоугольные сигналы изменяют на интеграторах 5.1 и 5.2 выходные напряжения, конечные уровни которых фиксируются БВХ 6.1 и 6.2 при переключении основного прямоугольного сигнала с 3.2 в «0». В этот же момент фиксируются: цифровое значение с компаратора 3.1 на триггере 7.1, значения функций +arcsin(x) и -arcsin(x) от входного смещенного гармонического сигнала - на БВХ 6.3 и 6.4. Значения напряжения с выходов БВХ 6.1 и 6.2 сравниваются компаратором 8.1. Результат сравнения и зафиксированное на триггере 7.1 значение формируют представление о квадранте измеряемой фазы. Шифратор 13 синтезирует соответствующий определенному квадранту код, который преобразуется ЦАП 14 в уровень аналогового сигнала. Из напряжения квадранта вычитается значение функции +arcsin(x) или -arcsin(x) в блоке 11.1. Результат фиксируется БВХ 6.7. Таким образом реализуется измерение сдвига фазы гармонического сигнала пропорционально позиционному представлению.

Для работы во втором режиме устройство коммутируется, как показано на фиг. 3. На вход «уровень» подается преобразуемый уровень напряжения. ГУН 2.1 синтезирует гармонический сигнал с частотой, пропорциональной входному уровню. ГУН 2.2 синтезирует гармонический синхронизированный с ГУН 2.1 сигнал с удвоенной частотой. Гармоники с ГУН 2.1 и 2.2 преобразуются в прямоугольные сигналы на компараторах 3.1 и 3.2, при этом формируется положительное и отрицательное значение арксинуса на 10.1 и 10.2 от ГУН 2.1. По первому импульсу с входа «такт» запоминаются уровни напряжения с 10.1 и 10.2 в БВХ 6.3 и 6.4, а также цифровые значения с компараторов - в триггерах 7.1 и 7.2. Далее, как в случае режима №1, шифратор 13 синтезирует соответствующий определенному квадранту код, который преобразуется ЦАП 14 в уровень аналогового сигнала. Из напряжения квадранта вычитается положительное или отрицательное значение арксинуса в блоке 11.1 и запоминается БВХ 6.5 (напряжение U1), тем самым фиксируется значение фазы на момент первого импульса по входу «такт». Через время, равное периоду дискретизации (3), с входа «такт» поступает второй импульс и аналогичным образом замеряется фаза, а ее эквивалент в виде уровня напряжения сохраняется в БВХ 6.6 (напряжение U2). Далее исходя из полученных эквивалентов значений фаз формируется конечный результат преобразования согласно выражению (5). Для этого полученные эквиваленты сравниваются компаратором 8.2, и если U1>U2, то на первый вход блока 11.3 поступает напряжение Ε с опорного источника 15, а если U2≥U1, то - 0. Из этого коммутируемого уровня вычитается сохраненный эквивалент с БВХ 6.6, при этом в блоке 11.2 из Ε вычитается эквивалент с БВХ 6.5. После чего полученные результаты проходят блок 11.4 для нахождения итоговой разницы, сохраняемой БВХ 6.7. Таким образом реализуется измерение входного уровня напряжения пропорционально модулярному представлению.

В третьем режиме сначала устройство коммутируется как в режиме №1, а результат преобразования сохраняется БВХ 6.8. Далее устройство коммутируется как в режиме №2, только сигнал подается не с входа «уровень», а с БВХ 6.8. Таким образом реализуется измерение сдвига фазы гармонического сигнала пропорционально модулярному представлению.

Пример.

Рассмотрим работу устройства в третьем режиме, поскольку в процессе его реализации последовательно подключаются первые два. Пусть измеряемый сдвиг фазы Δϕ=210°, максимальное входное и выходное напряжение Е=5В, применяется СОК по основаниям p1=5, р2=8, р3=9,  , максимальная частота ГУН 2.1 Fmax=10кГц. Тогда, согласно выражению (3), периоды дискретизации будут равны: Тд1=7.2 мс, Тд2=4.5 мс, Тд3=4 мс.

, максимальная частота ГУН 2.1 Fmax=10кГц. Тогда, согласно выражению (3), периоды дискретизации будут равны: Тд1=7.2 мс, Тд2=4.5 мс, Тд3=4 мс.

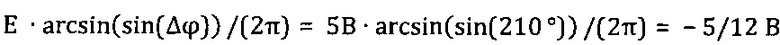

Для работы на первом этапе третьего режима устройство коммутируется, как показано на фиг. 2, за исключением того, что вместо БВХ 6.7 работает БВХ 6.8. На вход «опора» подается основной гармонический сигнал, а на вход «фаза» смещенный (отстающий по фазе). Компараторы 3.1 и 3.2, сравнивая с уровнем нуля, преобразуют гармонические сигналы в прямоугольные. На фиг. 4 сигнал после компаратора по входу «опора» обозначен 3.2, а по входу «фаза» - 3.1. Продолжительность единичного уровня основного прямоугольного сигнала с 3.2 разбивается элементами И 4.1 и 4.2 на две части в соответствии с фазовым сдвигом сигнала с 3.1. Полученные таким образом прямоугольные сигналы изменяют на интеграторах 5.1 и 5.2 выходные напряжения (фиг. 4). Переключение основного прямоугольного сигнала с 3.2 в «0» фиксирует полученные значения уровней напряжения на БВХ 6.1 и 6.2. Одновременно с этим, согласно схеме (фиг. 2), фиксируются: цифровое значение с компаратора 3.1 на триггере 7.1, равное «0» (фиг. 4), эквиваленты значений тригонометрических функций с блоков 10.1 и 10.2 на БВХ 6.3 и 6.4, равные согласно правой части (2):

для функции +arcsin(x) и 5/12 В - для -arcsin(x). Значения напряжения с выходов БВХ 6.1 и 6.2 сравниваются и, согласно фиг. 4, уровень с интегратора 5.1 меньше 5.2, поэтому на выходе компаратора 8.1 «0». Значения с триггера 7.1, равное «0», и с выхода компаратора 8.1, равное «0», поступают на шифратор 13, где преобразуются в соответствующий третьему квадранту код (табл. 1), который поступает на ЦАП 14, синтезирующий уровень аналогового сигнала 2.5 В (табл. 3). Одновременно шифратор 13 подает на коммутатор 1.4, согласно табл.1, цифровой «0», что пропускает дальше эквивалент тригонометрической функции +arcsin(x) с блока 10.1 и БВХ 6.3, равное -5/12 В. Как результат на блоке 11.1 происходит операция вычитания: 2.5 В - (-5/12 В)=35/12 В=2.9167 В. Полученный уровень напряжения сохраняется БВХ 6.8 (фиг. 1).

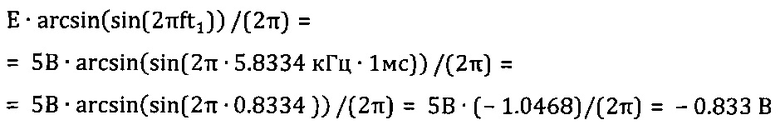

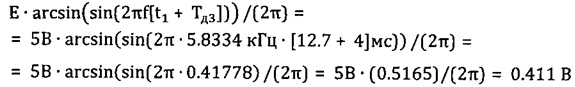

Для работы на втором этапе третьего режима устройство коммутируется, как показано на фиг. 3, за исключением того, что входы ГУН 2.1 и 2.2 подключены не к входу «уровень», а к выходу БВХ 6.8. Сначала рассмотрим преобразование пропорционально модулярному представлению по основанию p1=5 и, соответственно, с периодом дискретизации Тд1=7.2 мс. Напряжение 2.9167 В поступает на вход ГУН 2.1 и 2.2. Частота гармоники на выходе ГУН 2.1 f=2.9167В⋅10кГц/5В=5.8334 кГц. ГУН 2.2 синтезирует гармонический синхронизированный с ГУН 2.1 сигнал с удвоенной частотой. По первому импульсу с входа «такт» запоминаются уровни напряжения с 10.1 и 10.2 в БВХ 6.3 и 6.4, а также цифровые значения с компараторов 3.1 и 3.2 - в триггерах 7.1 и 7.2. Для реализации рассмотренных в предыдущем предложении операций пусть длительность первого импульса по входу «такт» закончится в момент времени t1=1мс. Тогда, согласно правой части выражения (4) для U1 эквиваленты значений тригонометрических функций с блоков 10.1 и 10.2, зафиксированные на БВХ 6.3 и 6.4, равны:

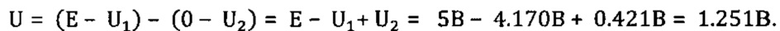

для функции +arcsin(x) и 0.833 В - для -arcsin(x). Значения с выходов компараторов 3.1 и 3.2 (с триггеров 7.1 и 7.2) в момент времени t1 оба равны «0» (фиг. 5). Далее шифратор 13 синтезирует соответствующий четвертому квадранту код (табл. 2), который преобразуется ЦАП 14 в уровень аналогового сигнала, равный 5В (табл. 3). Одновременно шифратор 13 подает на коммутатор 1.4, согласно табл. 2, цифровую «1», что пропускает дальше эквивалент тригонометрической функции -arcsin(x) с БВХ 6.4, равный 0.833В. Как результат на блоке 11.1 происходит операция вычитания:

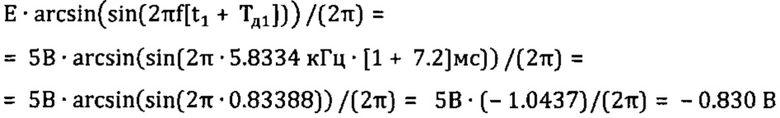

5В-(0.833 В)=4.167В. Полученный уровень напряжения сохраняется БВХ 6.5. Через время, равное периоду дискретизации Тд1, с входа «такт» поступает второй импульс, и аналогичным образом замеряется фаза:

для функции +arcsin(x) и 0.830 В - для -arcsin(x). Согласно фиг. 5, замеряемая фаза находится в четвертом квадранте, поэтому из табл. 2 и табл. 3 можно сделать вывод, что синтезируемый ЦАП 14 уровень аналогового сигнала равен 5В, а шифратор 13 подает на коммутатор 1.4 цифровую «1», что пропускает дальше эквивалент тригонометрической функции -arcsin(x) с БВХ 6.4, равный 0.830 В. Как результат на блоке 11.1 происходит операция вычитания:

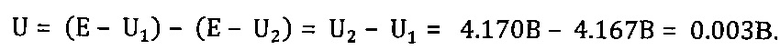

5В-(0.830В)=4.170В. Этот эквивалент сохраняется в БВХ 6.6 (напряжение U2). Далее, исходя из полученных эквивалентов значений фаз, формируется согласно выражению (5) конечный результат преобразования. Т.к. U2>U1, то

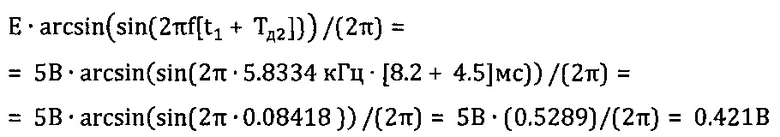

Чтобы получить модулярный эквивалент по основанию p2=8, соответствующий периоду дискретизации Тд2=4.5 мс, можно для упрощения воспользоваться уже известными результатами преобразования, взяв за текущий момент t1 конец предыдущего периода дискретизации, как это показано на фиг. 5. Т.е. считаем, что уже известно U1 и оно равно предыдущему U2, U1=4.170B. Для определения U2 замеряется фаза:

для функции +arcsin(x) и -0.421В - для -arcsin(x). Согласно фиг. 5 замеряемая фаза находится в первом квадранте, поэтому из табл. 2 и табл. 3 можно сделать вывод, что синтезируемый ЦАП 14 уровень аналогового сигнала равен 0В, а шифратор 13 подает на коммутатор 1.4 цифровую «1», что пропускает дальше эквивалент тригонометрической функции -arcsin(x) с БВХ 6.4, равный

-0.421В. Как результат на блоке 11.1 происходит операция вычитания:

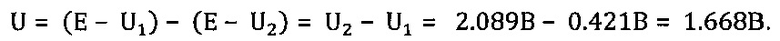

0В-(-0.421В)=0.421В. Этот эквивалент сохраняется в БВХ 6.6 (напряжение U2). Далее, исходя из полученных эквивалентов значений фаз, формируется согласно выражению (5) конечный результат преобразования. Т.к. U1>U2, то

Чтобы получить модулярный эквивалент по основанию р3=9, соответствующий периоду дискретизации Тд3=4 мс, воспользуемся (по аналогии) предыдущими расчетами. U1=0.421B. Для определения U2 замеряется фаза:

для функции +arcsin(x) и -0.411В - для -arcsin(x). Согласно фиг. 5 замеряемая фаза находится во втором квадранте, поэтому из табл. 2 и табл. 3 можно сделать вывод, что синтезируемый ЦАП 14 уровень аналогового сигнала равен 2.5В, а шифратор 13 подает на коммутатор 1.4 цифровой «0», что пропускает дальше эквивалент тригонометрической функции +arcsin(x) с БВХ 6.3, равный 0.411 В. Как результат на блоке 11.1 происходит операция вычитания:

2.5В-(0.411 В)=2.089В. Этот эквивалент сохраняется в БВХ 6.6 (напряжение U2). Далее, исходя из полученных эквивалентов значений фаз, формируется согласно выражению (5) конечный результат преобразования. Т.к. U2>U1, то

Проверим полученный результат, оцифровав аналоговые эквиваленты измеряемой разности фаз. Рассмотрим параллельный АЦП (Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ. - Изд. 6-е. - М.: Мир, 2003. -704 с., рис. 9.49) (без смещения нуля на  младшего разряда), состоящего из делителя опорных напряжений, компараторов, количество которых Р=5*8*9=360, и шифратора. Измеряемое напряжение равно полученному на первом этапе Uвх=2.917В. Реализовав таблицу опорных напряжений (табл. 4), кратных Е/360, где Е=5В, обнаруживаем, что компараторы с 1-го по 210-й установятся в «1», а все остальные в «0». Следовательно, на выходе шифратора установится код, десятичное представление которого равно 210, что подтверждает правильность преобразования разности фаз к позиционному представлению. Для проверки результата второго этапа рассмотрим оцифровку полученных эквивалентов посредством трех АЦП, количество компараторов которых равно p1=5, р2=8, р3=9 соответственно. Получив таблицу опорных напряжений и результатов сравнения (табл. 5), можно сделать вывод, что вычеты в цифровой форме есть α1=0, α2=2, α3=3. Целые остатки от деления числа 210 на 5, 8 и 9 соответственно равны 0, 2 и 3.

младшего разряда), состоящего из делителя опорных напряжений, компараторов, количество которых Р=5*8*9=360, и шифратора. Измеряемое напряжение равно полученному на первом этапе Uвх=2.917В. Реализовав таблицу опорных напряжений (табл. 4), кратных Е/360, где Е=5В, обнаруживаем, что компараторы с 1-го по 210-й установятся в «1», а все остальные в «0». Следовательно, на выходе шифратора установится код, десятичное представление которого равно 210, что подтверждает правильность преобразования разности фаз к позиционному представлению. Для проверки результата второго этапа рассмотрим оцифровку полученных эквивалентов посредством трех АЦП, количество компараторов которых равно p1=5, р2=8, р3=9 соответственно. Получив таблицу опорных напряжений и результатов сравнения (табл. 5), можно сделать вывод, что вычеты в цифровой форме есть α1=0, α2=2, α3=3. Целые остатки от деления числа 210 на 5, 8 и 9 соответственно равны 0, 2 и 3.

Полученное устройство отражает принципы построения вторичных измерительных преобразователей на основе свойств модулярной системы счисления. С точки зрения практического применения преобразователь реализует возможность ввода информации с датчиков в модулярные вычислительные структуры, как на основе цифровых схем (через АЦП), так и когерентных СВЧ-устройств (через фазовращатель), таких как, например, описанных в патентах РФ №2220441, №2263948 и т.д.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПО МОДУЛЮ m | 2020 |

|

RU2747568C1 |

| АЛИАСНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2015 |

|

RU2589388C1 |

| Электронный измеритель мощности и энергии | 1988 |

|

SU1638653A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2014 |

|

RU2546621C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

| Многофункциональный преобразователь | 1985 |

|

SU1267443A1 |

| Функциональный преобразователь угла поворота в цифровой код | 1976 |

|

SU636654A1 |

Изобретение относится к области измерительной техники и может быть использовано для преобразования аналоговых электрических сигналов эквивалентно позиционному или модулярному представлению. Сущность изобретения заключается в реализации метода вычисления разности фаз гармонического колебания. Наряду с возможностью получения как позиционного, так и модулярного эквивалента входного сигнала положительным эффектом является функционирование преобразователя по произвольному основанию pi не только выбранной, но и произвольной системы остаточных классов. Технический результат выражается в возможности преобразования уровня входного сигнала пропорционально заданному модулю системы остаточных классов, а также сдвига фазы гармонического сигнала пропорционально позиционному и модулярному представлению через реализацию единого метода измерения разности фаз. 5 табл., 5 ил.

Модулярный измерительный преобразователь, содержащий первый и второй блок выборки и хранения, первый и второй компаратор, первый тригонометрический преобразователь, источник опорного напряжения, отличающийся тем, что введены первый, второй, третий, четвертый, пятый и шестой коммутаторы, первый и второй генераторы, управляемые напряжением, первый и второй элементы И, первый и второй интеграторы, третий, четвертый, пятый, шестой, седьмой и восьмой блоки выборки и хранения, первый и второй триггеры, третий и четвертый компараторы, первый и второй демультиплексоры, второй тригонометрический преобразователь, первый, второй, третий и четвертый блоки вычитания, элемент НЕ, шифратор, цифроаналоговый преобразователь, входы устройства «такт», «фаза», «опора» и «уровень», при этом вход устройства «фаза» объединен с первым входом первого коммутатора, при этом выход первого генератора, управляемого напряжением соединен со вторым входом первого коммутатора, выход которого соединен с входом первого и второго тригонометрического преобразователя, а также входом первого компаратора, выход которого соединен с входом элемента НЕ, первым входом первого триггера, а также первым входом первого элемента И, выход которого соединен с входом первого интегратора, выход которого соединен с первым входом первого блока выборки и хранения, выход которого соединен с первым входом третьего компаратора, выход которого соединен с первым входом второго демультиплексора, выход которого соединен со вторым входом шифратора, при этом выход первого триггера соединен с первым входом шифратора, второй выход которого соединен с третьим входом четвертого коммутатора, при этом первый выход шифратора соединен с входом цифроаналогового преобразователя, выход которого соединен со вторым входом первого блока вычитания, выход которого соединен с первым входом шестого коммутатора, а также с входом пятого, шестого и восьмого блока выборки и хранения, выход которого соединен со вторым входом третьего коммутатора, при этом вход устройства «уровень» объединен с первым входом третьего коммутатора, выход которого соединен с входом первого и второго генератора управляемого напряжением, выход которого соединен со вторым входом второго коммутатора, при этом вход устройства «опора» объединен с первым входом второго коммутатора, выход которого соединен с входом второго компаратора, выход которого соединен со вторым входом первого и второго элемента И, первым входом второго триггера, а также первым входом первого демультиплексора, при этом вход устройства «такт» объединен со вторым входом первого демультиплексора, выход которого соединен со вторым входом первого, второго, третьего и четвертого блока выборки и хранения, а также вторым входом первого и второго триггера, выход которого соединен со вторым входом второго демультиплексора, при этом выход элемента НЕ соединен с первым входом второго элемента И, выход которого соединен с входом второго интегратора, выход которого соединен с первым входом второго блока выборки и хранения, выход которого соединен со вторым входом третьего компаратора, при этом выход первого тригонометрического преобразователя соединен с первым входом третьего блока выборки и хранения, выход которого соединен с первым входом четвертого коммутатора, при этом выход второго тригонометрического преобразователя соединен с первым входом четвертого блока выборки и хранения, выход которого соединен со вторым входом четвертого коммутатора, выход которого соединен с первым входом первого блока вычитания, при этом первый выход источника опорного напряжения соединен с первым входом пятого коммутатора и вторым входом второго блока вычитания, при этом второй выход источника опорного напряжения соединен со вторым входом пятого коммутатора, выход которого соединен со вторым входом третьего блока вычитания, выход которого соединен с первым входом четвертого блока вычитания, при этом выход шестого блока выборки и хранения соединен с первым входом третьего блока вычитания и вторым входом четвертого компаратора, выход которого соединен с третьим входом пятого коммутатора, при этом выход пятого блока выборки и хранения соединен с первым входом четвертого компаратора и первым входом второго блока вычитания, выход которого соединен со вторым входом четвертого блока вычитания, выход которого соединен со вторым входом шестого коммутатора, выход которого соединен с входом седьмого блока выборки и хранения, выход которого является выходом устройства.

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В НАПРЯЖЕНИЕ | 1987 |

|

RU2056700C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2014 |

|

RU2546621C1 |

| Способ создания и регулирования натяга в передачах винт-гайка качения с упругой гайкой | 1983 |

|

SU1176120A1 |

| US 2013057253 A1, 07.03.2013. | |||

Авторы

Даты

2017-05-18—Публикация

2016-03-21—Подача