Изобретение относится к области автоматики и вычислительной техники, и может быть использовано в вычислительных структурах, работающих с дискретно-фазированным представлением чисел модулярной системы счисления.

Известно устройство (патент 2143723 С1 Российская Федерация, МПК Н03М 1/28 (2006.01). заявл. 29.07.1998; опубл. 27.12.1999.) содержащее два преобразователя двоичного кода числа в унитарный код по первому внутреннему модулю устройства, два преобразователя двоичного кода числа в унитарный код по второму внутреннему модулю устройства, два преобразователя унитарного кода числа в двоичный позиционный код, шесть блоков элементов И, сумматор по модулю устройства. Недостаток устройства - низкие функциональные возможности.

Известно также устройство (пат. 2270476 С1 Российская Федерация, МПК G06F 7/72 (2006.01). заявл. 28.06.2004; опубл. 20.02.2006.), содержащее генератор гармонического сигнала, измеритель фазы гармонического сигнала, фазовращатели на фиксированное значение фазы, дешифратор, управляемый фазовращатель, шифратор, выход устройства, коммутатор, амплитудный детектор, усилитель гармонического сигнала, управляющий вход устройства, мультиплексор, информационные входы устройства. Недостаток устройства - низкие функциональные возможности.

Наиболее близким к заявляемому является изобретение (пат. 2338241 С1 Российская Федерация, МПК G06F 7/523, G06F 7/72 (2006.01). заявл. 22.03.2007; опубл. 10.11.2008.), содержащее генератор гармонического сигнала, управляемые фазовращатели, измеритель фазы гармонического сигнала, группу фазовращателей на фиксированное значение фазы, шифраторы, входы устройства первого операнда, дешифраторы, элементы ИЛИ, блоки умножения на константу по модулю, элементы И, входы устройства разрядов второго операнда, сумматор по модулю два, преобразователь кода числа х в р-х, выход устройства.

Недостаток - низкие функциональные возможности, ограниченные выполнением исключительно мультипликативной модулярной операцией. Это определяется алгоритмом функционирования и структурой составляющих его узлов.

Техническая задача, на решение которой направлено заявляемое устройство, состоит в расширении функциональных возможностей устройства.

Технический результат выражается в возможности выполнения на реализуемом устройстве любой модулярной математической операции с двумя операндами в дискретно-фазированной форме представления чисел.

Технический результат достигается тем, что в арифметическое устройство по модулю m, содержащее входы устройства первого и второго операнда, первую группу из m-1 фазовращателей на фиксированное значение фазы 2π/m, первую группу из m управляемых фазовращателей, дешифратор, выход устройства, введены синхронизирующий вход устройства, вход номера операции устройства, мультиплексор, k блоков памяти (k - количество различных выполняемых устройством операций), первая и вторая группы из m фазированных ключей, еще m-1 групп из m управляемых фазовращателей, m сумматоров, вторая группа из m-1 фазовращателей на фиксированное значение фазы 2π/m, результирующий сумматор, при этом выход блоков памяти соединен с соответствующим входом мультиплексора, вход номера операции устройства объединен с (k+1)-м входом мультиплексора, выход которого соединен с входом дешифратора, группа выходов которого соединена со вторым входом соответствующих управляемых фазовращателей, при этом синхронизирующий вход устройства объединен с входом первых фазовращателей на фиксированное значение фазы 2π/m первой и второй групп, первым входом первых фазированных ключей первой и второй групп, а также третьим входом фазированных ключей первой группы, вход устройства первого операнда объединен со вторым входом фазированных ключей первой группы, вход устройства второго операнда объединен со вторым входом фазированных ключей второй группы, при этом выход s-х фазовращателей на фиксированное значение фазы 2π/m  первой и второй групп соединен с первым входом s+1-х фазированных ключей соответствующих групп, выход t-х фазовращателей на фиксированное значение фазы 2π/m

первой и второй групп соединен с первым входом s+1-х фазированных ключей соответствующих групп, выход t-х фазовращателей на фиксированное значение фазы 2π/m  первой и второй групп также соединен с входом (t+1)-х фазовращателей на фиксированное значение фазы 2π/m соответствующих групп, выход i-го фазированного ключа первой группы

первой и второй групп также соединен с входом (t+1)-х фазовращателей на фиксированное значение фазы 2π/m соответствующих групп, выход i-го фазированного ключа первой группы  соединен с первым входом первого управляемого фазовращателя i-й группы, выход управляемых фазовращателей i-й группы соединен с i-м входом соответствующих сумматоров, при этом выход s-го управляемого фазовращателя

соединен с первым входом первого управляемого фазовращателя i-й группы, выход управляемых фазовращателей i-й группы соединен с i-м входом соответствующих сумматоров, при этом выход s-го управляемого фазовращателя  любой группы также соединен с входом (s+1)-го управляемого фазовращателя той же группы, при этом выход сумматоров соответственно соединен с третьим входом фазированных ключей второй группы, выход которых соединен с соответствующим входом результирующего сумматора, выход которого объединен с выходом устройства.

любой группы также соединен с входом (s+1)-го управляемого фазовращателя той же группы, при этом выход сумматоров соответственно соединен с третьим входом фазированных ключей второй группы, выход которых соединен с соответствующим входом результирующего сумматора, выход которого объединен с выходом устройства.

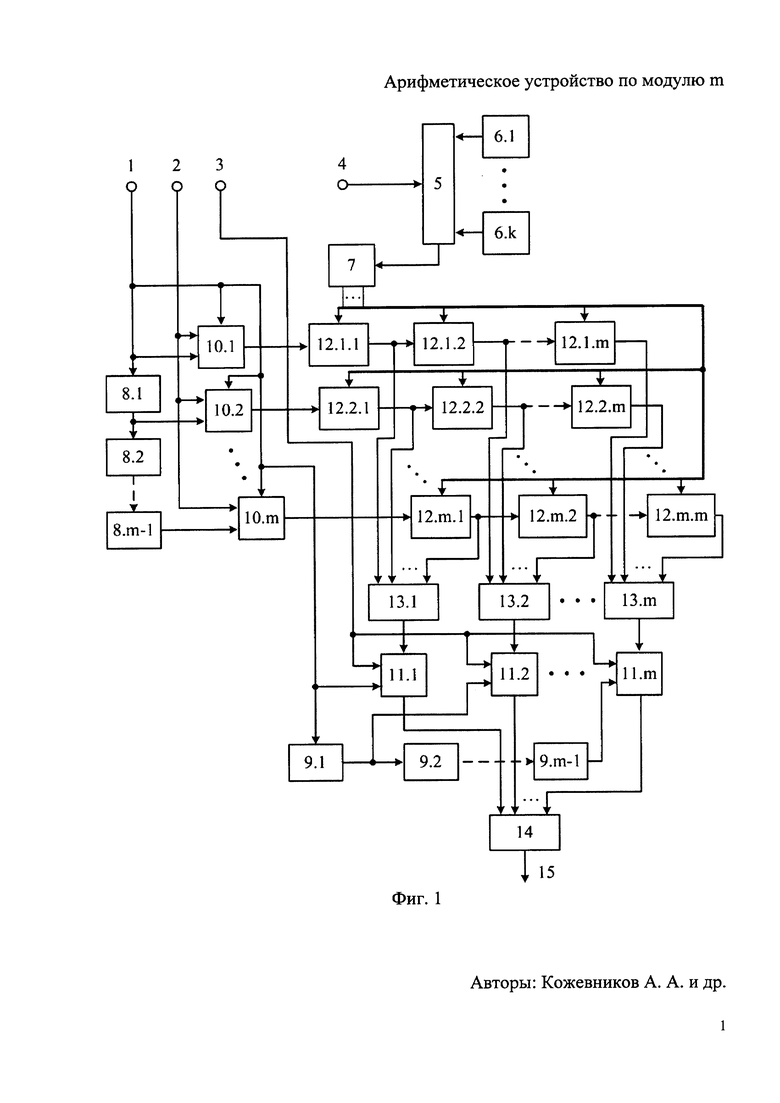

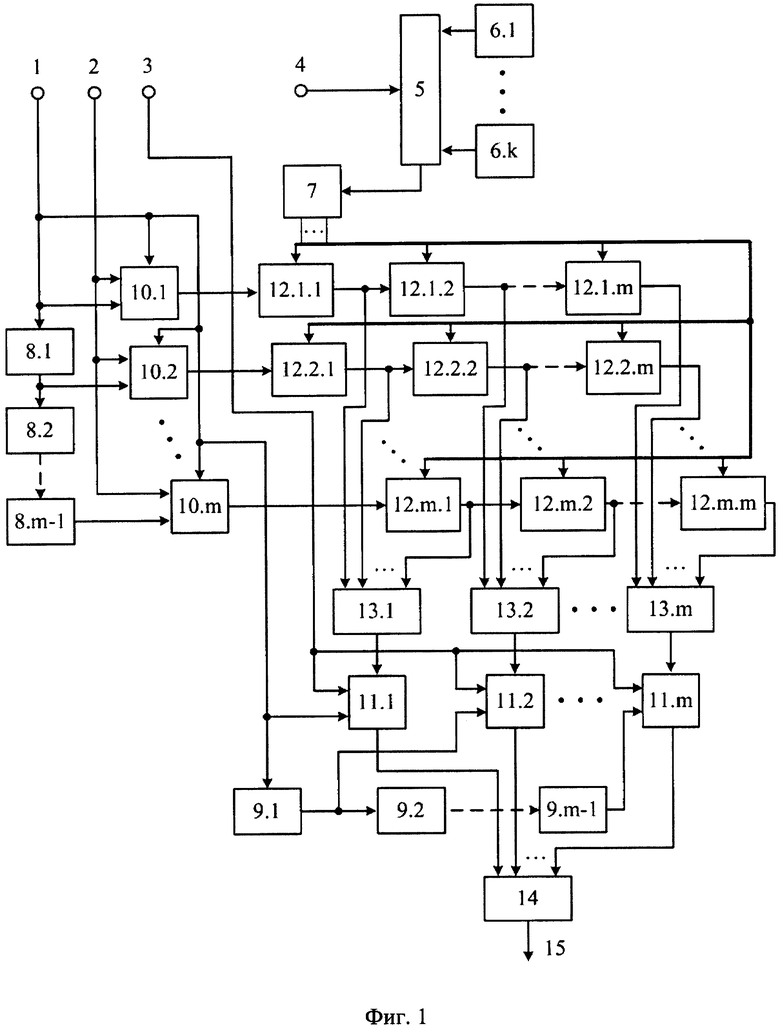

На фиг. 1 представлена структурная схема арифметического устройства по модулю m.

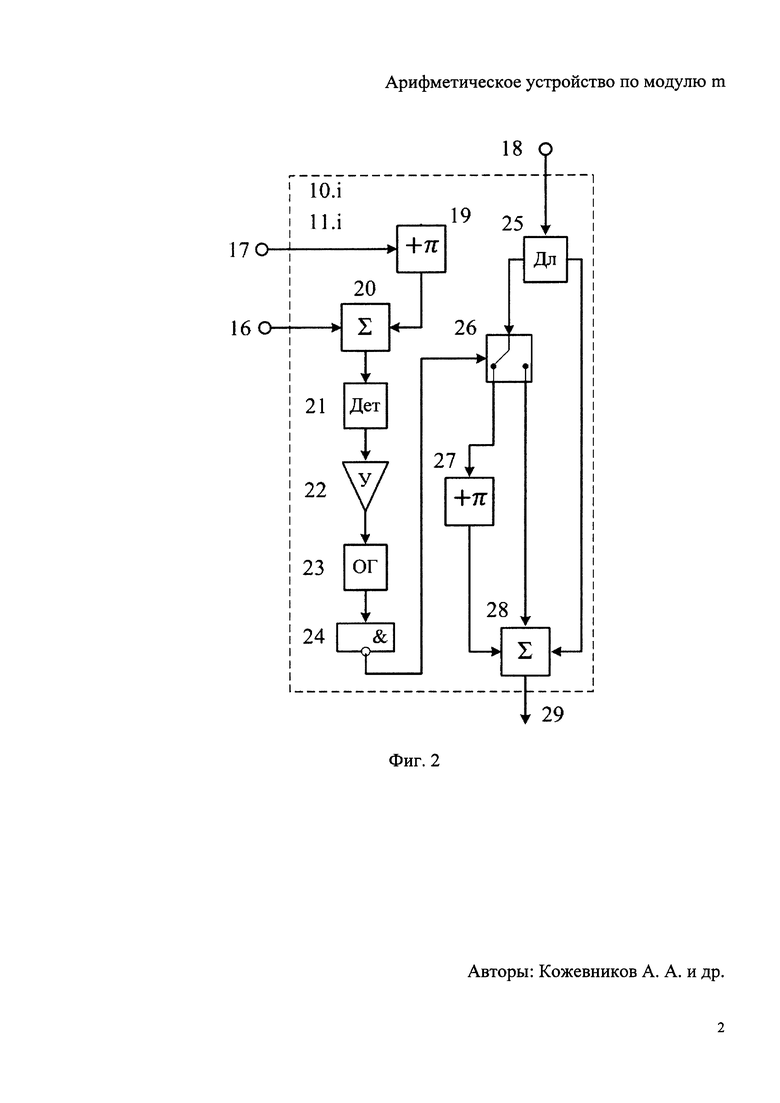

На фиг. 2 приведена схема фазированного ключа.

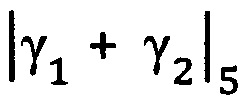

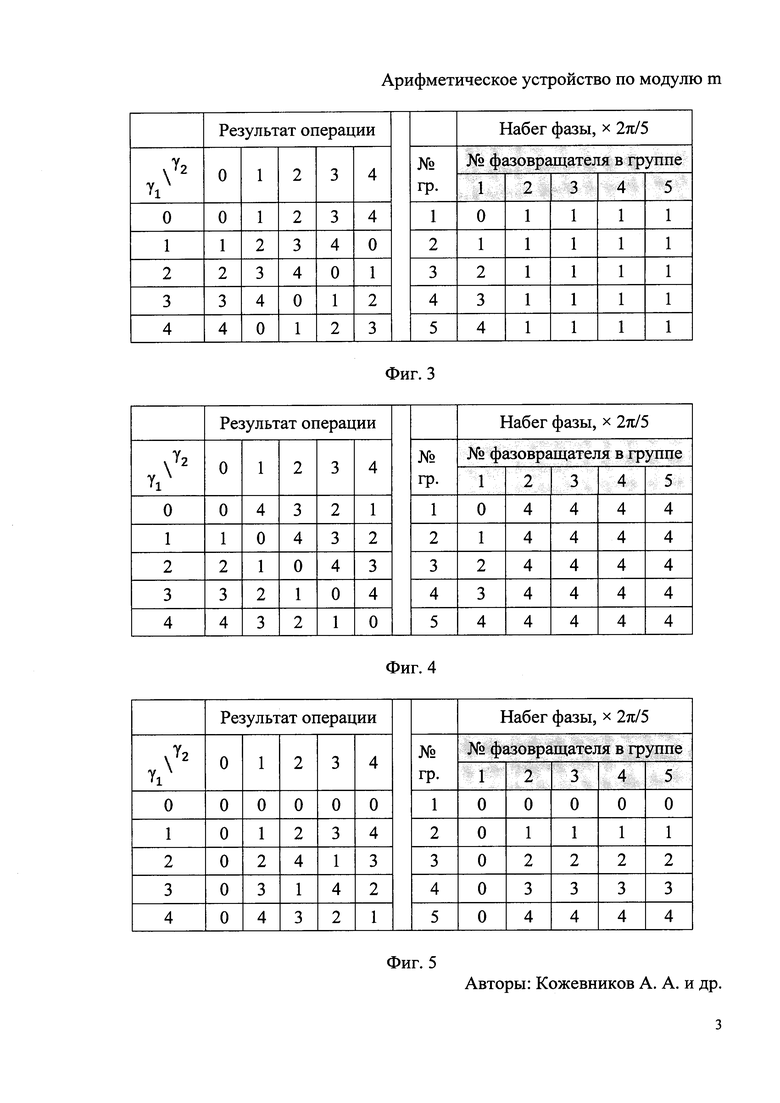

В фиг. 3 представлены результаты операции  и программно устанавливаемый набег фаз на соответствующих фазовращателях.

и программно устанавливаемый набег фаз на соответствующих фазовращателях.

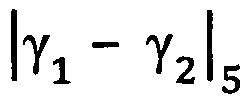

В фиг. 4 представлены результаты операции  и программно устанавливаемый набег фаз на соответствующих фазовращателях.

и программно устанавливаемый набег фаз на соответствующих фазовращателях.

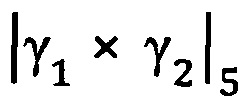

В фиг. 5 представлены результаты операции  и программно устанавливаемый набег фаз на соответствующих фазовращателях.

и программно устанавливаемый набег фаз на соответствующих фазовращателях.

Сущность изобретения заключается в применении табличного способа вычислений для любой из возможных модулярных математических операций с использованием значений операндов в качестве адреса результата в дискретно-фазированной форме представления чисел. К модулярным относятся в первую очередь арифметические операции сложения, вычитания и умножения. Также при некоторых условиях возможно выполнение операции возведения в степень и - следующее из предыдущих - вычисление полиномов. В процессе функционирования устройство осуществляет выборку гармоники с заданной согласно таблице констант для данной операции разностью фаз относительно синхронизирующего сигнала. Выборка осуществляется через сравнение фаз сигналов-операндов и опорных гармоник, получаемых на 8 и 9 фиксированных фазовращателях 2π/m, где m - модуль применяемой системы остаточных классов (СОК) (фиг. 1). Сначала выбирается строка, затем - столбец. Таким образом, используя загрузку результатов требуемой операции, например, из постоянных запоминающих устройств (ПЗУ), в параметр сдвига фазы управляемых фазовращателей с дальнейшей выборкой необходимого по принципу адреса, и реализуется расширение функциональных возможностей устройства.

Следует заметить, что разветвление сигнальных линий СВЧ на фиг. 1, должно сопровождаться наличием делителя мощности и усилителей для увеличения амплитуды гармоник до единичного значения, но для упрощения схем данные элементы опущены.

Дополнительным эффектом является возможность использования устройства в качестве блока считывания памяти программ или данных в аналоговой вычислительной системе, работающей с дискретно-фазированной формой представления чисел. Другим положительным эффектом, при условии ухода от полупроводниковых переключателей в фазированных ключах (фиг. 2), является возможность повышения быстродействия. Для рабочей частоты устройства, например 100 ГГц, возможен рост скорости выполнения операций на один-два порядка. Это следует из того факта, что даже самые быстродействующие полупроводниковые ключи, работающие с сигналами в СВЧ диапазоне, осуществляют включение/выключение в течение единиц наносекунд (стр. 12, Щаврук Н.В. Проектирование и изготовление микроэлектромеханических переключателей на подложках GaAs для СВЧ диапазона: дис. … канд. техн. наук: 05.27.01 / Москва. 2015. 130 с.), поэтому их устранение из состава основных динамически оперирующих элементов даст рассмотренный дополнительный эффект.

Показанная на фиг. 1 структурная схема арифметического устройства по модулю m содержит синхронизирующий вход устройства 1, входы устройства первого 2 и второго 3 операнда, вход номера операции устройства 4, мультиплексор 5, блоки памяти 6.1-6.k, дешифратор 7, первую 8.1-8.(m-1) и вторую 9.1-9.(m-1) группы фазовращателей на фиксированное значение фазы 2π/m, первую 10.1-10.m и вторую 11.1-11.m группы фазированных ключей, m групп управляемых фазовращателей 12.i.1-12.i.m, где i - номер группы, сумматоры 13.1-13.m, результирующий сумматор 14, выход устройства 15.

Выход блоков памяти 6.1-6.k (k - количество различных выполняемых устройством операций) соединен с соответствующим входом мультиплексора 5, вход номера операции устройства 4 объединен с (k+1)-м входом мультиплексора 5, выход которого соединен с входом дешифратора 7, группа выходов которого соединена со вторым входом соответствующих управляемых фазовращателей 12.1.1-12.m.m, при этом синхронизирующий вход устройства 1 объединен с входом фазовращателей на фиксированное значение фазы 2π/m 8.1 и 9.1, первым входом фазированных ключей 10.1 и 11.1, а также третьим входом фазированных ключей 10.1-10.m, вход устройства первого операнда 2 объединен со вторым входом фазированных ключей 10.1-10.m, вход устройства второго операнда 3 объединен со вторым входом фазированных ключей 11.1-11.m, при этом выход фазовращателей на фиксированное значение фазы 2π/m 8.s и 9.s  соответственно соединен с первым входом фазированных ключей 10.(s+1) и 11.(s+1), выход фазовращателей на фиксированное значение фазы 2π/m 8.t и 9.t

соответственно соединен с первым входом фазированных ключей 10.(s+1) и 11.(s+1), выход фазовращателей на фиксированное значение фазы 2π/m 8.t и 9.t  также соответственно соединен с входом фазовращателей на фиксированное значение фазы 2π/m 8.(t+1) и 9.(t+1), выход фазированных ключей 10.1-10.m соответственно соединен с первым входом управляемых фазовращателей 12.1.1-12.m.1, выход управляемых фазовращателей 12.i.1-12.i.m

также соответственно соединен с входом фазовращателей на фиксированное значение фазы 2π/m 8.(t+1) и 9.(t+1), выход фазированных ключей 10.1-10.m соответственно соединен с первым входом управляемых фазовращателей 12.1.1-12.m.1, выход управляемых фазовращателей 12.i.1-12.i.m  соединен с i-м входом соответствующих сумматоров 13.1-13.m, при этом выход управляемых фазовращателей 12.1.s-12.m.s

соединен с i-м входом соответствующих сумматоров 13.1-13.m, при этом выход управляемых фазовращателей 12.1.s-12.m.s  также соответственно соединен с входом управляемых фазовращателей 12.1.(s+1)-12.m.(s+1), при этом выход сумматоров 13.1-13.m соответственно соединен с третьим входом фазированных ключей 11.1-11.m, выход которых соединен с соответствующим входом результирующего сумматора 14, выход которого объединен с выходом устройства 15.

также соответственно соединен с входом управляемых фазовращателей 12.1.(s+1)-12.m.(s+1), при этом выход сумматоров 13.1-13.m соответственно соединен с третьим входом фазированных ключей 11.1-11.m, выход которых соединен с соответствующим входом результирующего сумматора 14, выход которого объединен с выходом устройства 15.

Показанная на фиг. 2 схема фазированного ключа содержит первый 16 и второй 17 информационные входы, синхронизирующий 18 вход, фазовращатель 19 на фиксированное значение фазы π, сумматор 20, детектор 21, усилитель 22, ограничитель 23, инвертор 24, делитель 25, переключатель 26, фазовращатель 27 на фиксированное значение фазы π, сумматор 28, выход 29.

Первый информационный вход 16 объединен с первым входом сумматора 20, второй информационный вход 17 объединен с входом фазовращателя 19 на фиксированное значение фазы π, выход которого соединен со вторым входом сумматора 20, выход которого соединен с детектором 21, выход которого соединен с входом усилителя 22, выход которого соединен с входом ограничителя 23, выход которого соединен с входом инвертора 24, выход которого соединен с первым входом переключателя 26, при этом синхронизирующий вход 18 объединен с входом делителя 25, второй выход которого соединен с третьим входом сумматора 28, первый выход делителя 25 соединен со вторым входом переключателя 26, второй выход которого соединен со вторым входом сумматора 28, при этом первый выход переключателя 26 через фазовращатель на фиксированное значение фазы π 27 соединен с первым входом сумматора 28, выход которого объединен с выходом 29.

Работа устройства осуществляется следующим образом. Значение номера операции по входу 4 позволяет подключить к выходу мультиплексора 5 соответствующий блок памяти (фиг. 1). Дешифратор 7 переводит двоичный код в унитарный и коммутирует ключами в электрическую схему линии задержки в управляемых фазовращателях 12.1.1-12.m.m. На синхронизирующий вход устройства 1 поступает гармонический сигнал Sc=sin(ωt). На информационные входы 2 и 3 операндов поступают соответственно дискретно-фазированные гармоники S2=sin(ωt+2π⋅γ1/m) и S3=sin(ωt+2π⋅γ2/m), где γ1,2∈[0,m-1], a m - модуль применяемой системы остаточных классов. Группы фазовращателей на фиксированное значение фазы 2π/m 8 и 9 формируют опорные гармоники:

S8.1,9.1=sin(ωt+2π⋅1/m),

…

S8.(m-1),9.(m-1)=sin(ωt+2π⋅(m-1)/m).

Сначала в работу вступают ключи для выборки строки (10.1-10.m). Соответственно на входах этих блоков (фиг. 2):

S16=sin(ωt+2π⋅(i-1)/m), (i∈[1,m]),

S17=sin(ωt+2π⋅γ1/m),

S18=sin(ωt).

Гармоника S18 делится по мощности пополам, одной частью поступая на вход переключателя 26, а другой - на вход сумматора 28. Гармоника S17 преобразуется блоком 19 в противофазную и складывается с S16 на блоке 20. Если γ1=i-1, то на выходе детектора 21 наблюдается ноль, который инвертируется вентилем 24 в логическую единицу и, соединяя половины, доводит на блоке 28 разделенную ранее синхронизирующую гармонику до исходного уровня, поступающего на выход 29. Если γ1≠i-1, то на выходе детектора 21 формируется ненулевой уровень напряжения, который поступает на блок 22 с коэффициентом усиления большем или равном m. Для защиты входа инвертора 24 от перенапряжения в схеме присутствует ограничитель 23. Пришедший на вход инвертора 24 уровень интерпретируется как единичный и преобразуется в логический ноль, коммутируя переключателем 26 одну из половинок синхронизирующей гармоники на вход фазовращателя на угол π 27. В итоге на сумматоре 28 встречаются два сигнала, равных по амплитуде, но находящиеся в противофазе, формируя на выходе 29 ноль.

Таким образом, синхронизирующая гармоника, пройдя один из ключей (10.1-10.m), поступает на вход (первый фазовращатель) соответствующей группы управляемых фазовращателей 12.i.l-12.i.m, где i - номер группы (i∈[1,m]). На выходах фазовращателей сигнальной группы формируются гармоники с дискретно-кодированными фазами, поступающими на входы соответствующих сумматоров 13.1-13.m. Поскольку на остальных входах сумматоров нулевые уровни напряжения, то итогом сложения являются только сформированные в определенной группе фазовращателей гармоники. Далее фазированные ключи 11.1-11.m, согласно значению второго операнда S3=sin(ωt+2π⋅γ2/m), пропускают на результирующий сумматор 14 и далее на выход 15 только одну дискретно-кодированную гармонику, которая и является результатом вычислений.

Пример.

Рассмотрим работу устройства на примере трех модулярных математических операций: сложения, вычитания и умножения (т.е. k=3). Пусть операции выполняются по модулю СОК m=5, тогда в зависимости от номера операции значения набегов фаз на соответствующих фазовращателях устанавливаются согласно правым частям таблиц на фигурах 3-5. Из блоков с вариативным количеством устройство содержит группы 8 и 9 по четыре фазовращателя на фиксированное значение фазы 2π/5, группы 10 и 11 по пять фазированных ключей, пять групп по пять управляемых фазовращателей 12.i.1-12.i.5 где i - номер группы  , и сумматоры 13.1-13.5. На входы устройства подадим гармонические сигналы:

, и сумматоры 13.1-13.5. На входы устройства подадим гармонические сигналы:

S1=sin(ωt),

S2=sin(ωt+2π⋅1/5),

S3=sin(ωt+2π⋅3/5).

Из этого следует, что остатки по модулю 5, над которыми будут осуществляться ранее озвученные операции, есть: γ1=1, γ2=3. Группы фазовращателей на фиксированное значение фазы 2π/m 8 и 9 формируют опорные гармоники:

S8.1,9.1=sin(ωt+2π⋅1/5),

S8.2,9.2=sin(ωt+2π⋅2/5),

S8.3,9.3=sin(ωt+2π⋅3/5),

S8.4,9.4=sin(ωt+2π⋅4/5).

Через ключи 10.1-10.5 проходит синхронизирующая гармоника только на вторую группу фазовращателей 12.2.1-12.2.5 (вторая строчка табл. Фиг. 3-5). На выходе каждого из них формируется суммарный набег фазы, кратный значению вычета возможного результата операции.

Для суммы:

S12.2.1=sin(ωt+2π⋅1/5),

S12.2.2=sin(ωt+2π⋅2/5),

S12.2.3=sin(ωt+2π⋅3/5),

S12.2.4=sin(ωt+2π⋅4/5),

S12.2.5=sin(ωt+2π⋅5/5).

Для разницы:

S12.2.1=sin(ωt+2π⋅1/5),

S12.2.2=sin(ωt+2π⋅5/5),

S12.2.3=sin(ωt+2π⋅4/5),

S12.2.4=sin(ωt+2π⋅3/5),

S12.2.5=sin(ωt+2π⋅2/5).

Для произведения:

S12.2.1=sin(ωt+2π⋅0/5),

S12.2.2=sin(ωt+2π⋅1/5),

S12.2.3=sin(ωt+2π⋅2/5),

S12.2.4=sin(ωt+2π⋅3/5),

S12.2.5=sin(ωt+2π⋅4/5).

Полученные гармоники поступают через сумматоры 13.1-13.5 на соответствующие фазированные ключи 11.1-11.5, и согласно значению второго операнда S3=sin(ωt+2π⋅3/5), на результирующий сумматор 14 и далее на выход 15 проходит сигнал с четвертого управляемого фазовращателя второй группы:

Для суммы:

S12.2.4=sin(ωt+2π⋅4/5).

Для разницы:

S12.2.4=sin(ωt+2π⋅3/5).

Для произведения:

S12.2.4=sin(ωt+2π⋅3/5).

Полученное устройство отражает принципы построения арифметических устройств на основе системы остаточных классов, работающих с дискретно-фазированной формой представления чисел. С точки зрения практического применения устройство реализует возможность построения аналоговых вычислителей СВЧ диапазона, превосходящих по быстродействию современный уровень ЭВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ m | 2020 |

|

RU2748744C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ m | 2020 |

|

RU2748743C1 |

| ФАЗИРОВАННЫЙ КЛЮЧ ПО МОДУЛЮ m | 2017 |

|

RU2659866C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ К ЧИСЕЛ ПО МОДУЛЮ М | 2017 |

|

RU2653312C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2744475C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЛА ПО МОДУЛЮ НА КОНСТАНТУ | 2017 |

|

RU2653310C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПО МОДУЛЮ m | 2020 |

|

RU2747568C1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2020 |

|

RU2744337C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 1992 |

|

RU2042140C1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА СИГНАЛОВ В РЕАЛЬНОМ МАСШТАБЕ ВРЕМЕНИ | 2009 |

|

RU2404438C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в вычислительных структурах, работающих с дискретно-фазированным представлением чисел модулярной системы счисления. Техническим результатом является осуществление выполнения любой модулярной математической операции с двумя операндами в дискретно-фазированной форме представления чисел. Устройство содержит синхронизирующий вход устройства, входы устройства первого и второго операнда, вход номера операции устройства, мультиплексор, блоки памяти, дешифратор, первую и вторую группы фазовращателей на фиксированное значение фазы 2π/m, первую и вторую группы фазированных ключей, m групп управляемых фазовращателей, сумматоры, результирующий сумматор, выход устройства. 5 ил.

Арифметическое устройство по модулю m, содержащее входы устройства первого и второго операнда, первую группу из m-1 фазовращателей на фиксированное значение фазы 2π/m, первую группу из m управляемых фазовращателей, дешифратор, выход устройства, отличающееся тем, что введены синхронизирующий вход устройства, вход номера операции устройства, мультиплексор, k блоков памяти, где k - количество различных выполняемых устройством операций, первая и вторая группы из m фазированных ключей, еще m-1 групп из m управляемых фазовращателей, m сумматоров, вторая группа из m-1 фазовращателей на фиксированное значение фазы 2π/m, результирующий сумматор, при этом выход блоков памяти соединен с соответствующим входом мультиплексора, вход номера операции устройства объединен с (k+1)-м входом мультиплексора, выход которого соединен с входом дешифратора, группа выходов которого соединена со вторым входом соответствующих управляемых фазовращателей, при этом синхронизирующий вход устройства объединен с входом первых фазовращателей на фиксированное значение фазы 2π/m первой и второй групп, первым входом первых фазированных ключей первой и второй групп, а также третьим входом фазированных ключей первой группы, вход устройства первого операнда объединен со вторым входом фазированных ключей первой группы, вход устройства второго операнда объединен со вторым входом фазированных ключей второй группы, при этом выход s-х фазовращателей на фиксированное значение фазы 2π/m  первой и второй групп соединен с первым входом (s+1)-х фазированных ключей соответствующих групп, выход t-х фазовращателей на фиксированное значение фазы 2π/m

первой и второй групп соединен с первым входом (s+1)-х фазированных ключей соответствующих групп, выход t-х фазовращателей на фиксированное значение фазы 2π/m  первой и второй групп также соединен с входом (t+1)-х фазовращателей на фиксированное значение фазы 2π/m соответствующих групп, выход i-го фазированного ключа первой группы

первой и второй групп также соединен с входом (t+1)-х фазовращателей на фиксированное значение фазы 2π/m соответствующих групп, выход i-го фазированного ключа первой группы  соединен с первым входом первого управляемого фазовращателя i-й группы, выход управляемых фазовращателей соединен с i-м входом соответствующих сумматоров, при этом выход s-го управляемого фазовращателя

соединен с первым входом первого управляемого фазовращателя i-й группы, выход управляемых фазовращателей соединен с i-м входом соответствующих сумматоров, при этом выход s-го управляемого фазовращателя  любой группы также соединен с входом (s+1)-го управляемого фазовращателя той же группы, при этом выход сумматоров соответственно соединен с третьим входом фазированных ключей второй группы, выход которых соединен с соответствующим входом результирующего сумматора, выход которого объединен с выходом устройства.

любой группы также соединен с входом (s+1)-го управляемого фазовращателя той же группы, при этом выход сумматоров соответственно соединен с третьим входом фазированных ключей второй группы, выход которых соединен с соответствующим входом результирующего сумматора, выход которого объединен с выходом устройства.

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2007 |

|

RU2338241C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ N ЧИСЕЛ ПО МОДУЛЮ P | 2004 |

|

RU2270476C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2143723C1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| US 4598266 A, 01.07.1986. | |||

Авторы

Даты

2018-06-07—Публикация

2017-05-24—Подача