Изобретение относится к области измерительной и вычислительной техники и может быть использовано для быстрого преобразования аналоговых электрических сигналов в цифровой код в системах, функционирующих в модулярной системе счисления.

Известно устройство (патент 2546621 С1 Российская Федерация, МПК Н03М 1/28 (2006.01). заявл. 09.01.2014; опубл. 10.04.2015.) содержащий вход, блоки слежения-хранения, аналого-цифровой преобразователь, цифроаналоговый преобразователь, блок вычитания, источник напряжения смещения, регистры-защелки, выходные шины кодов остатков в СОК. Недостаток - низкое быстродействие.

Известно устройство (патент 2589388 С1 Российская Федерация, МПК Н03М 1/34 (2006.01). заявл. 12.01.2015; опубл. 10.07.2016.) содержащий вход, блок слежения-хранения, основные и дополнительные аналого-цифровые преобразователи, выходные шины кодов остатков в системе остаточных классов, основные и дополнительные генераторы управляемых напряжением, основные и дополнительные спецпроцессоры быстрого преобразования Фурье, основные и дополнительные блоки максимальной амплитуды, блоки вычитания и шины кодов оснований системы остаточных классов. Недостаток - низкое быстродействие.

Наиболее близким к заявляемому является изобретение (патент 2619831 С1 Российская Федерация, МПК G01R 25/00, Н03М 1/28, Н03М 1/34 (2006.01). заявл. 21.03.2016; опубл. 18.05.2017.) содержащее блоки выборки и хранения, компараторы, тригонометрические преобразователи, источник опорного напряжения, коммутаторы, генераторы управляемые напряжением, элементы И, интеграторы, триггеры, демультиплексоры, блоки вычитания, элемент НЕ, шифратор, цифроаналоговый преобразователь, входы устройства «такт», «фаза», «опора» и «уровень».

Недостаток прототипа - низкое быстродействие, обусловленное соответствующим аппаратным обеспечением.

Задача, на решение которой направлено заявляемое устройство, состоит в ускорении промежуточного преобразования входной аналоговой величины.

Технический результат выражается в реализации более продуктивного алгоритма преобразования и измерения.

Технический результат достигается тем, что в аналого-цифровой преобразователь по модулю m, содержащий входы «уровень» и «опора», первый, второй, третий и четвертый компараторы, демультиплексор, введены мультипериодный фазовращатель, фазовращатель на 2π/3 и фазовращатель на 4π/3, первый, второй и третий умножители, первый, второй и третий фильтры низких частот, первый, второй и третий мосты, первый, второй и третий АЦП, ПЗУ, при этом вход «уровень» объединен с первым входом мультипериодного фазовращателя, выход которого соединен с первым входом первого умножителя, входом фазовращателя на 2π/3 и входом фазовращателя на 4π/3, выход которого соединен с первым входом третьего умножителя, а выход фазовращателя на 2π/3 соединен с первым входом второго умножителя, вход «опора» является вторым входом мультипериодного фазовращателя, а также объединен с вторыми входами всех трех умножителей, выходы которых соединены с входами соответствующих фильтров низких частот, выходы которых соединены с входами соответствующих мостов и соответствующих АЦП, выходы которых соединены с соответствующими входами демультиплексора, выход которого соединен с первым входом ПЗУ, при этом выходы мостов соединены с первыми входами соответствующих компараторов, выходы которых соединены с четвертым, пятым и шестым входами демультиплексора соответственно, при этом выход первого моста также соединен с вторым входом второго компаратора, выход второго моста также соединен с вторым входом третьего компаратора, а выход третьего моста также соединен с вторым входом первого компаратора, при этом выход первого фильтра низких частот через четвертый компаратор также соединен с вторым входом ПЗУ, выход которого является выходом устройства.

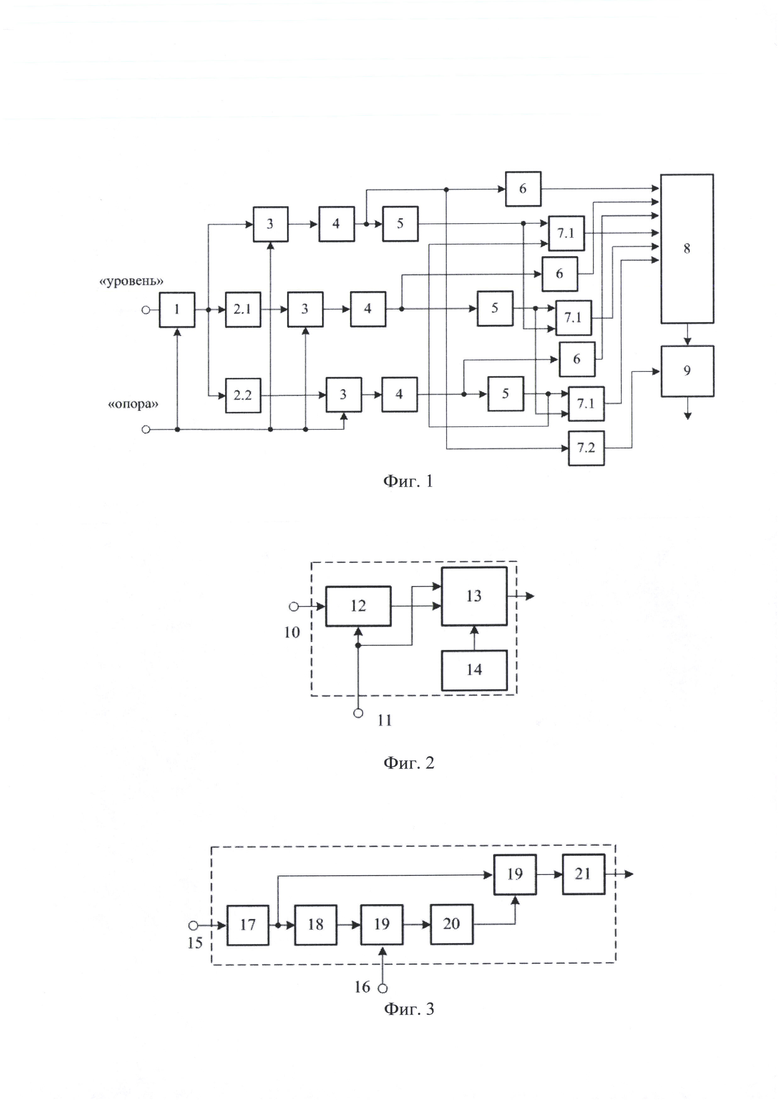

На фиг. 1 представлена структурная схема АЦП по модулю m.

На фиг. 2 представлена структурная схема мультипериодного фазовращателя с умножением фазы.

На фиг. 3 представлен вариант фазовращателя с аналоговым управлением.

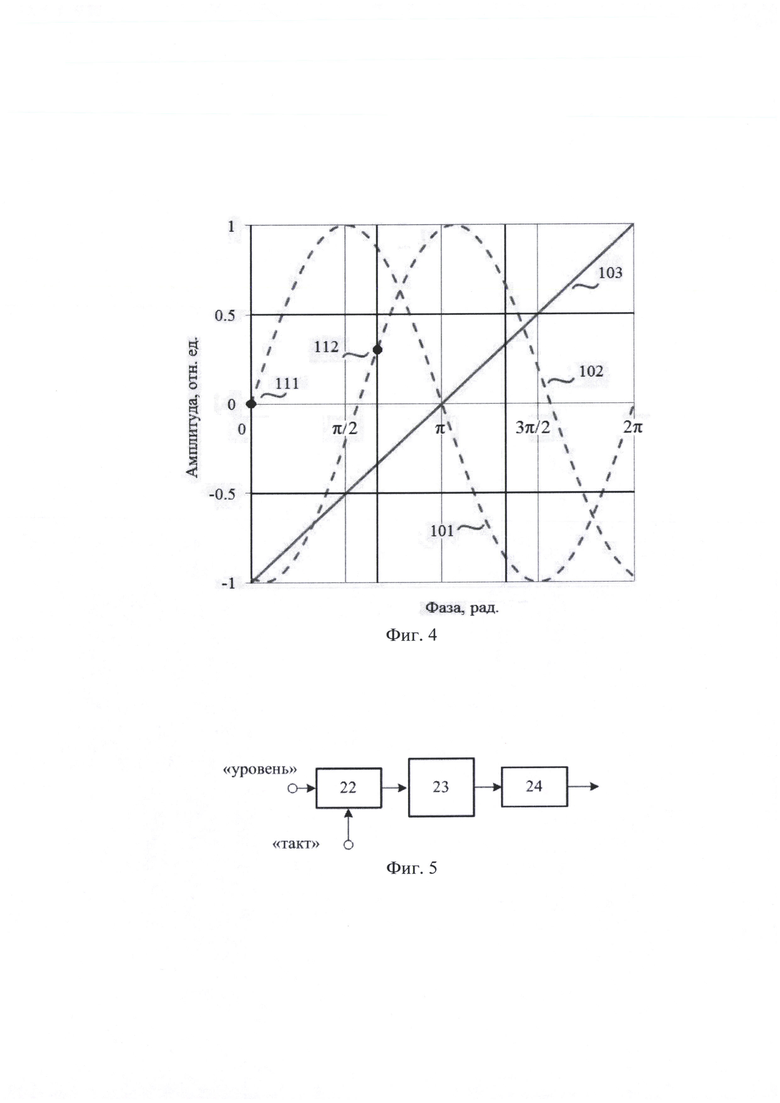

На фиг. 4 представлены результаты промежуточного преобразования входного напряжения.

На фиг. 5 представлена схема АЦП по модулю m на основе прототипа, работающего в режиме №2.

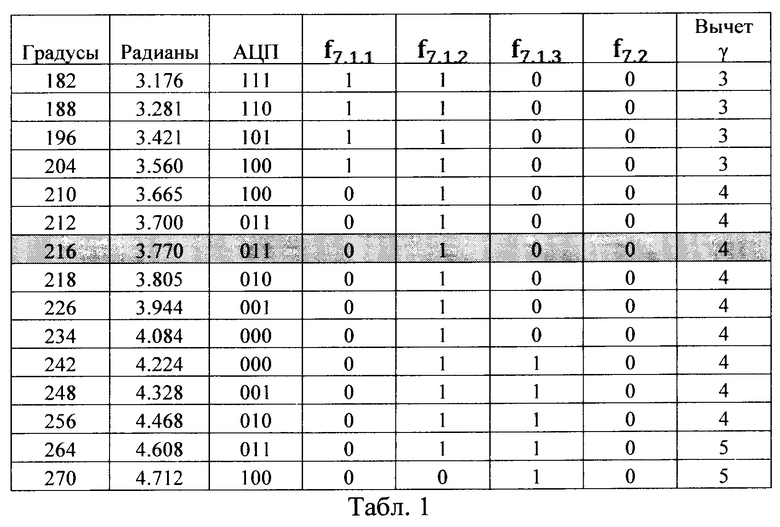

В табл. 1 представлена зависимость значений вычетов от фазы и генерируемых при этом адресов.

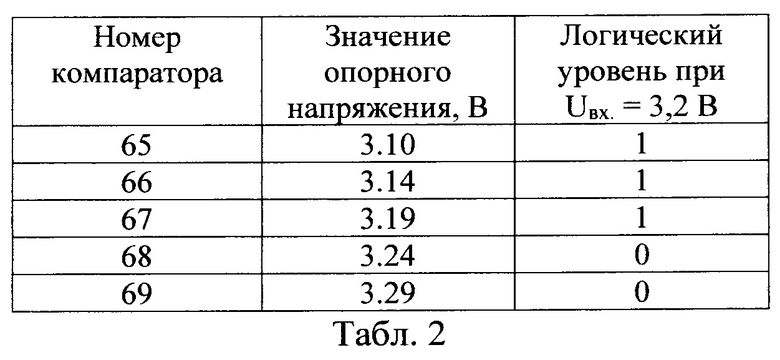

В табл. 2 представлена зависимость опорных напряжений параллельного АЦП и результат сравнения с входным сигналом.

Сущность изобретения заключается в применении более продуктивного алгоритма и соответствующего ему аппаратного обеспечения, позволяющего к тому же внедрить иную схему измерения результатов промежуточного преобразования. Прототип в режиме №2 использует задержку по времени между двумя актами запоминания уровня синтезируемой гармоники, что осуществляется посредством блоков выборки и хранения. Такие устройства работают с частотами сигнала догигагерцового порядка, что ограничивает рост быстродействия всей схемы на их основе. Для ускорения промежуточного преобразования предлагается использовать мультипериодный фазовращатель, представленный на фиг. 2, который реализован на основе фазовращателя 12 с аналоговым управлением и максимальным углом поворота в пределах одного периода (например, патент РФ №2649050), и блока умножения фазы 13 (патент РФ №2653310, где вместо числа закодированного дискретной фазой выступает любое значение фазы) на константу из ПЗУ 14. Такой подход позволяет оперировать уже десятками гигагерц, тем самым повышая на порядок внутреннее быстродействие.

В качестве блока 12 может выступать фазовращатель, представленный на фиг. 3., где синусоидальный сигнал от генератора управляемого напряжением (ГУН) 17 поступает на широкополосную линию задержки СВЧ-сигнала 18 (Гуляев Ю.В. и др. Принципы создания линий задержки сверхвысокочастотного диапазона на основе наноразмерных сегнетоэлектрических пленок // Радиотехника и электроника. - 2014. - №1. - С. 96-101), после чего осуществляется выделение набежавшей фазы и перенос ее на гармонику с жестко заданной частотой. Рассмотрим данный процесс. Генерируемая блоком 17 гармоника sin(ω1t)=sin(2πfГУНt) поступает на линию 18, где формируется набег фазы ϕ, пропорциональный входному напряжению и соответствующей выходной частоте сигнала ГУН. Для перехода к ω2 сначала осуществляется перемножение на первом умножителе 19 и выделение более высокочастотной составляющей на фильтре 20:

sin(ω1t-ϕ)⋅sin(ω2t)→-cos[(ω1+ω2)t-ϕ].

Далее на втором умножителе 19 и низкочастотном фильтре 21 производится аналогичная процедура:

sin(ω1t)⋅{-cos[(ω1+ω2)t-ϕ]}→-sin[-ω2t+ϕ]=sin[ω2t-ϕ].

Таким образом осуществляется поворот фазы опорной гармоники с частотой ω2 пропорционально входному напряжению.

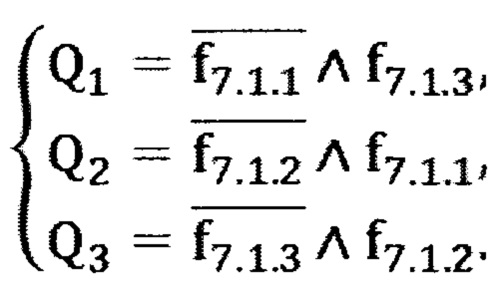

Для измерения полученного на блоке 1 (фиг. 1) смещения фазы производится разделение сигнала на три части, две из которых претерпевают дополнительное вращение на 120° и 240° соответственно, с дальнейшим измерением на АЦП. Рассмотрим преимущества такого подхода в сравнении с прототипом. Если построить АЦП по модулю m на основе работающего в режиме №2 прототипа 22 (фиг. 5), то последний будет выступать в качестве элемента промежуточного преобразования входной аналоговой величины при изменении от 0 до Е (- максимальное значение) в пилообразный сигнал. Количество "зубцов" такой "пилы" будет равно М/m, где  - диапазон чисел применяемой системы остаточных классов (СОК) по модулям mj, a m - актуальное для устройства значение модуля, m ∈ (m1, …, mn), n - количество модулей СОК. На фиг. 4 прямая 103 отображает значение выходного сигнала из блока 22 для одного из "зубцов". АЦП 23 замеряет уровень на оси ординат и преобразует его в код пропорциональный фазе, т.е. значению по оси абсцисс. Далее ПЗУ 24 интерпретирует полученное число в остаток по модулю m. Результатом же промежуточного преобразования в новом устройстве (фиг. 1) до процедуры оцифровки являются уровни сигнала пропорциональные sin(ϕ), sin(ϕ-2π/3) и sin(ϕ-4π/3) соответственно по трактам. Из них для измерения выбирается значение с наименьшим отклонением от 0. Так для кривой 101 (фиг. 4) - это точка 111, а для 102 - точка 112. Свойством таких точек всегда является их расположение пределах от -0.5 до 0.5 уровня амплитуды гармоники, и только этот факт уже влечет двукратное увеличение точности цифрового преобразования при использовании АЦП 6 той же разрядности, что и 23. Аппроксимация прямой 103 линией тренда даст результат у=х-1, а для кривых 101 и 102 (через точки 111 и 112) в обозначенных пределах у=3х. Т.е. крутизна прямолинейного участка синусоиды дает еще трехкратный рост точности представления входной величины. Таким образом, описанная схема измерения, в итоге, увеличивает в шесть раз точность преобразования по сравнению с АЦП по модулю m на основе прототипа (фиг. 5), что является дополнительным положительным эффектом.

- диапазон чисел применяемой системы остаточных классов (СОК) по модулям mj, a m - актуальное для устройства значение модуля, m ∈ (m1, …, mn), n - количество модулей СОК. На фиг. 4 прямая 103 отображает значение выходного сигнала из блока 22 для одного из "зубцов". АЦП 23 замеряет уровень на оси ординат и преобразует его в код пропорциональный фазе, т.е. значению по оси абсцисс. Далее ПЗУ 24 интерпретирует полученное число в остаток по модулю m. Результатом же промежуточного преобразования в новом устройстве (фиг. 1) до процедуры оцифровки являются уровни сигнала пропорциональные sin(ϕ), sin(ϕ-2π/3) и sin(ϕ-4π/3) соответственно по трактам. Из них для измерения выбирается значение с наименьшим отклонением от 0. Так для кривой 101 (фиг. 4) - это точка 111, а для 102 - точка 112. Свойством таких точек всегда является их расположение пределах от -0.5 до 0.5 уровня амплитуды гармоники, и только этот факт уже влечет двукратное увеличение точности цифрового преобразования при использовании АЦП 6 той же разрядности, что и 23. Аппроксимация прямой 103 линией тренда даст результат у=х-1, а для кривых 101 и 102 (через точки 111 и 112) в обозначенных пределах у=3х. Т.е. крутизна прямолинейного участка синусоиды дает еще трехкратный рост точности представления входной величины. Таким образом, описанная схема измерения, в итоге, увеличивает в шесть раз точность преобразования по сравнению с АЦП по модулю m на основе прототипа (фиг. 5), что является дополнительным положительным эффектом.

В отличие от прототипа в новом устройстве отпадает необходимость тактировать блоки выборки и хранения, что упрощает управление и является положительным дополнительным эффектом.

Следует заметить, что разветвление сигнальных линий СВЧ на фиг. 1-3 должно сопровождаться наличием делителя мощности и усилителей для увеличения амплитуды гармоник до единичного значения, но для упрощения схем данные элементы опущены.

Показанный на фиг. 1 АЦП по модулю m содержит входы «уровень» и «опора», мультипериодный фазовращатель 1, фазовращатели на 2π/3 2.1 и на 4π/3 2.2, умножители 3, фильтры низких частот 4, мосты 5, АЦП 6, с первого по третий компараторы 7.1 и четвертый компаратор 7.2, демультиплексор 8, ПЗУ 9.

Вход «уровень» объединен с первым входом мультипериодного фазовращателя 1, выход которого соединен с первым входом первого умножителя 3, входом фазовращателя на 2π/3 2.1 и входом фазовращателя на 4π/3 2.2, выход которого соединен с первым входом третьего умножителя 3, а выход фазовращателя на 2π/3 2.1 соединен с первым входом второго умножителя 3, вход «опора» является вторым входом мультипериодного фазовращателя 1, а также объединен с вторыми входами всех трех умножителей 3, выходы которых соединены с входами соответствующих фильтров низких частот 4, выходы которых соединены с входами соответствующих мостов 5 и соответствующих АЦП 6, выходы которых соединены с соответствующими входами демультиплексора 8, выход которого соединен с первым входом ПЗУ 9, при этом выходы мостов 5 соединены с первыми входами соответствующих компараторов 7.1, выходы которых соединены с четвертым, пятым и шестым входами демультиплексора 8 соответственно, при этом выход первого моста 5 также соединен с вторым входом второго компаратора 7.1, выход второго моста 5 также соединен с вторым входом третьего компаратора 7.1, а выход третьего моста 5 также соединен с вторым входом первого компаратора 7.1, при этом выход первого фильтра низких частот 4 через четвертый компаратор 7.2 также соединен с вторым входом ПЗУ 9, выход которого является выходом устройства.

Показанный на фиг. 2 мультипериодный фазовращатель с умножением фазы содержит входы 10 и 11, фазовращатель с аналоговым управлением 12, блок умножения фазы 13 и ПЗУ 14.

Вход 10 объединен с первым входом фазовращателя с аналоговым управлением 12, выход которого соединен с вторым входом блока умножения фазы 13, вход 11 объединен с вторым входом фазовращателя с аналоговым управлением 12 и первым входом блока умножения фазы 13, выход ПЗУ 14 соединен с третьим входом блока умножения фазы 13, выход которого и является выходом мультипериодного фазовращателя с умножением фазы.

Показанный на фиг. 3 вариант фазовращателя с аналоговым управлением содержит входы 15 и 16, генератор управляемый напряжением 17, линия задержки 18, первый и второй умножители 19, фильтр высоких частот 20, фильтр низких частот 21.

Вход 16 объединен с вторым входом первого умножителя 19, вход 15 объединен с входом генератора управляемого напряжением 17, выход которого соединен с первым входом второго умножителя 19 и входом линии задержки 18, выход которой соединен с первым входом первого умножителя 19, выход которой соединен с входом фильтра высоких частот 20, выход которого соединен с вторым входом второго умножителя 19, выход которого соединен с входом фильтра низких частот 21, выход которого и является выходом фазовращателя с аналоговым управлением.

Представленные на фиг. 4 результаты промежуточного преобразования входного напряжения содержат изображение синусоиды при нулевом смещении фазы 101и при смещении фазы порядка -1.77 рад. 102, зависимость от фазы уровня выходного сигнала из блока 22 для одного из "зубцов" 103, оптимальные точки для измерения при нулевом смещении фазы 111 и при смещении фазы порядка -1.77 рад. 112.

Показанная на фиг. 5 схема АЦП по модулю m на основе прототипа, работающего в режиме №2, содержит входы «уровень» и «такт», прототип 22, АЦП 23 и ПЗУ 24.

Вход «уровень» объединен с первым входом прототипа 22, вход «такт» объединен с вторым входом прототипа 22, выход которого соединен с входом АЦП 23, выход которого соединен с входом ПЗУ 24, выход которого и является выходом АЦП по модулю m на основе прототипа.

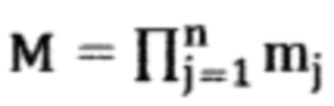

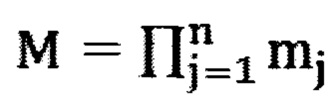

Работа аналого-цифрового преобразователя по модулю m начинается с поступления на вход «уровень» измеряемого напряжения Uвх, а по входу «опора» продолжается подача основного гармонического сигнала с частотой ω2. На выходе мультипериодного фазовращателя 1 формируется гармоника со смещением по фазе относительно основной:

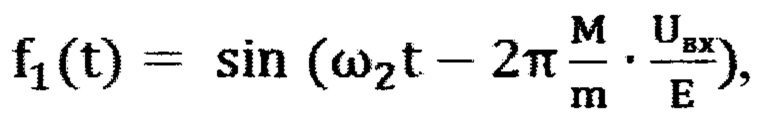

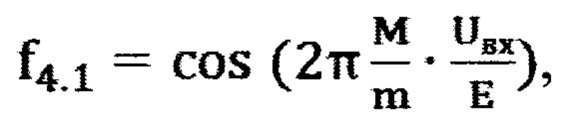

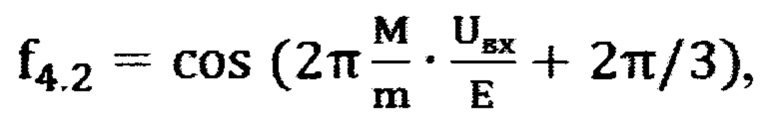

где М/m - максимальное количество периодов поворота фазы фазовращателем 1,  - диапазон чисел применяемой системы остаточных классов (СОК) по модулям mj, a m - актуальное для устройства значение модуля, m ∈ (m1, …, mn), n - количество модулей СОК, Е - максимальное значение входного напряжения. После разделения сигнала на три части и прохождения их через фазовращатели на 2π/3 2.1 и на 4π/3 2.2 происходит перемножение с опорной гармоникой sin (to2t) на блоках 3 и низкочастотная фильтрация, в результате чего на выходах фильтров 4 наблюдается следующее:

- диапазон чисел применяемой системы остаточных классов (СОК) по модулям mj, a m - актуальное для устройства значение модуля, m ∈ (m1, …, mn), n - количество модулей СОК, Е - максимальное значение входного напряжения. После разделения сигнала на три части и прохождения их через фазовращатели на 2π/3 2.1 и на 4π/3 2.2 происходит перемножение с опорной гармоникой sin (to2t) на блоках 3 и низкочастотная фильтрация, в результате чего на выходах фильтров 4 наблюдается следующее:

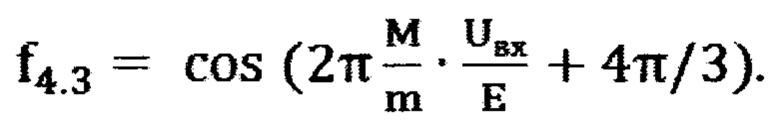

Далее происходит формирование кода адреса ПЗУ 9. Первая часть адреса формируется на АЦП 6 с разрядностью N. Измерение осуществляется в пределах от -0.5 до 0.5 амплитуды гармонического сигнала. В результате формируются следующие цифровые значения, исходя из выражения:

Вторая часть адреса определяется компараторами 7.1, на которые поступают сформированные схемами на основе моста 5 положительные уровни с двух соседних трактов, при этом реализуются сравнения:

f7.1.1=1, если |f4.1|>|f4.2|, иначе 0,

f7.1.2=1, если |f4.2|>|f4.3|, иначе 0,

f7.1.3=1, если |f4.3|>|f4.1|, иначе 0.

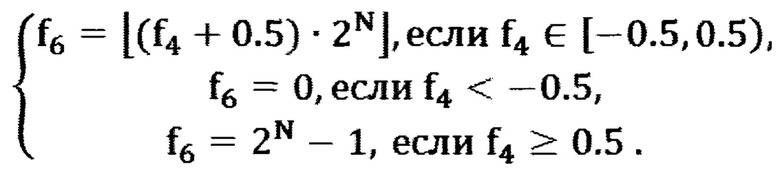

Вместе со второй частью адреса на ПЗУ 9 проходит код одного из АЦП 6 выбираемый демультиплексором 8 исходя из второй части адреса согласно единичному значению одного из логических выражений:

Третья часть формируется компаратором 7.2, предназначенного для исправления ошибок кодирования в предыдущих элементах, в зависимости от выражения:

f7.2=1, если f4.1>0, иначе 0.

Таким образом, на входы ПЗУ 9 поступает адрес разрядностью N+4, в соответствии с которым и выбирается значение остатка по модулю m.

Пример.

Пусть дана система остаточных классов по основаниям m1=3, m2=5, m3=7 (т.е. n=3,  mj=105). Пусть актуальное для устройства значение модуля m=7, тогда М/m=15. На вход «уровень» поступает напряжение Uвх=3.2B, при Е=5В. На выходе мультипериодного фазовращателя 1 формируется гармоника со смещением по фазе относительно основной:

mj=105). Пусть актуальное для устройства значение модуля m=7, тогда М/m=15. На вход «уровень» поступает напряжение Uвх=3.2B, при Е=5В. На выходе мультипериодного фазовращателя 1 формируется гармоника со смещением по фазе относительно основной:

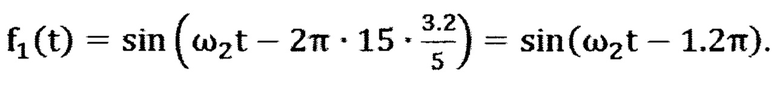

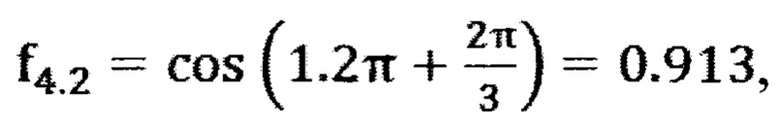

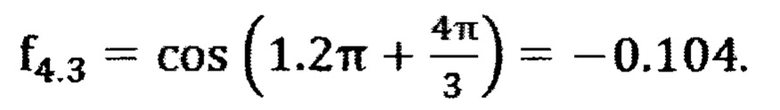

После разделения сигнала на три части и прохождения их через фазовращатели на 2π/3 2.1 и на 4π/3 2.2 происходит перемножение с опорной гармоникой sin (ω2t) на блоках 3 и низкочастотная фильтрация, в результате чего на выходах фильтров 4 наблюдается следующее:

f4.1=cos(1.2π)=-0.809,

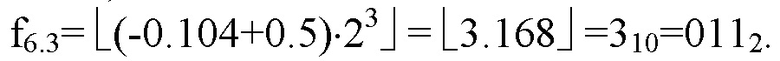

Далее происходит формирование кода адреса ПЗУ 9. Пусть разрядность АЦП 6: N=3. В результате формируются следующие цифровые значения, исходя из выражения:

f6.1=0,

f6.2=7,

Вторая часть адреса определяется компараторами 7.1:

f7.1.1=0, т.к. |-0.809|<|0.913|,

f7.1.2=1, т.к. |0.913|>|-0.104|,

f7.1.3=0, т.к. |-0.104|<|-0.809|,

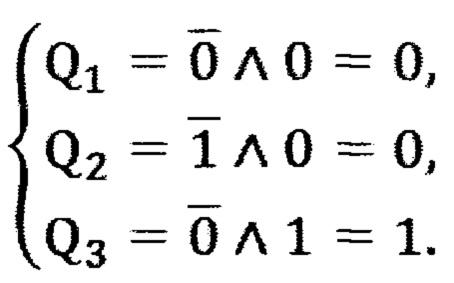

Вместе со второй частью адреса на ПЗУ 9 проходит код одного из АЦП 6 выбираемый демультиплексором 8 исходя из второй части адреса согласно единичному значению одного из логических выражений:

Поскольку Q3=1, то к ПЗУ 9 проходит первая часть кода от третьего АЦП f6.3=0112. Третья часть кода формируется компаратором 7.2 в зависимости от выражения:

f7.2=0, т.к. f4.1<0.

Таким образом, на входы ПЗУ 9 поступает адрес разрядностью N+4:

011 010 0,

в соответствии с которым и выбирается значение остатка по модулю m из ПЗУ 9 (табл. 1): γ=4.

Проверим полученный результат. Рассмотрим параллельный АЦП (Хоровиц П., Хилл У. Искусство схемотехники: Пер. с англ. - Изд. 6-е. - М.: Мир, 2003. - 704 с., рис. 9.49) (без смещения нуля на ½ младшего разряда), состоящего из делителя опорных напряжений, компараторов, количество которых Р=3*5*7=105, и шифратора. Измеряемое напряжение равно 3.2 В. Получив таблицу опорных напряжений (табл. 2), кратных Е/105, где Е=5 В, обнаруживаем, что компараторы с 1-го по 67-й установятся в «1», а все остальные в «0». Следовательно, на выходе шифратора установится код, десятичное представление которого равно 67. Целый остаток от деления числа 67 на 7 соответственно равен 4.

Полученное устройство отражает принципы построения АЦП на основе свойств системы остаточных классов. С точки зрения практического применения преобразователь реализует возможность преобразования уровня аналогового сигнала в цифровую форму модулярных вычислительных структур с максимально возможным быстродействием.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ГАРМОНИКИ НАПРЯЖЕНИЯ | 1990 |

|

RU2030753C1 |

| СЕЛЕКТИВНОЕ УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОДНОФАЗНЫХ ЗАМЫКАНИЙ В КАБЕЛЬНЫХ ЛИНИЯХ | 1994 |

|

RU2079145C1 |

| СПОСОБЫ И УСТРОЙСТВА ПОВЫШЕНИЯ ИНДЕКСА УГЛОВОЙ МОДУЛЯЦИИ | 2012 |

|

RU2493646C2 |

| УСТРОЙСТВО КОМПЕНСАЦИИ НЕСТАБИЛЬНОСТИ НЕСУЩЕЙ ЧАСТОТЫ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2006 |

|

RU2336650C2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ m | 2020 |

|

RU2748743C1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА СИГНАЛОВ В РЕАЛЬНОМ МАСШТАБЕ ВРЕМЕНИ | 2009 |

|

RU2404438C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПО МОДУЛЮ М | 2017 |

|

RU2656992C1 |

| СПОСОБ НАВИГАЦИИ ДЛЯ ПРИНТЕРА, ПРИНТЕР И МАЯК | 2020 |

|

RU2758714C2 |

| ПРИЕМНЫЙ РАДИОЦЕНТР | 2012 |

|

RU2504902C9 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 1992 |

|

RU2042140C1 |

Изобретение относится к области измерительной и вычислительной техники и может быть использовано для преобразования аналоговых электрических сигналов в цифровой код. Технический результат заключается в повышении быстродействия. Преобразователь содержит входы «уровень» и «опора», четыре компаратора, демультиплексор, фазовращатели, мультипериодный фазовращатель, три умножителя, три фильтра низких частот, мосты, ПЗУ, три АЦП, при этом сущность изобретения заключается в обеспечении более продуктивного алгоритма за счет соответствующего ему аппаратного обеспечения, позволяющего внедрить иную схему измерения результатов промежуточного преобразования. 5 ил., 2 табл.

Аналого-цифровой преобразователь по модулю m, содержащий входы «уровень» и «опора», первый, второй, третий и четвертый компараторы, демультиплексор, отличающийся тем, что введены мультипериодный фазовращатель, фазовращатель на 2π/3 и фазовращатель на 4π/3, первый, второй и третий умножители, первый, второй и третий фильтры низких частот, первый, второй и третий мосты, первый, второй и третий АЦП, ПЗУ, при этом вход «уровень» объединен с первым входом мультипериодного фазовращателя, выход которого соединен с первым входом первого умножителя, входом фазовращателя на 2π/3 и входом фазовращателя на 4π/3, выход которого соединен с первым входом третьего умножителя, а выход фазовращателя на 2π/3 соединен с первым входом второго умножителя, вход «опора» является вторым входом мультипериодного фазовращателя, а также объединен с вторыми входами всех трех умножителей, выходы которых соединены с входами соответствующих фильтров низких частот, выходы которых соединены с входами соответствующих мостов и соответствующих АЦП, выходы которых соединены с соответствующими входами демультиплексора, выход которого соединен с первым входом ПЗУ, при этом выходы мостов соединены с первыми входами соответствующих компараторов, выходы которых соединены с четвертым, пятым и шестым входами демультиплексора соответственно, при этом выход первого моста также соединен с вторым входом второго компаратора, выход второго моста также соединен с вторым входом третьего компаратора, а выход третьего моста также соединен с вторым входом первого компаратора, при этом выход первого фильтра низких частот через четвертый компаратор также соединен с вторым входом ПЗУ, выход которого является выходом устройства.

| Модулярный измерительный преобразователь | 2016 |

|

RU2619831C1 |

| АЛИАСНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2015 |

|

RU2589388C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2014 |

|

RU2546621C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2010 |

|

RU2433527C1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1986 |

|

SU1368989A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1690195A1 |

| Способ создания и регулирования натяга в передачах винт-гайка качения с упругой гайкой | 1983 |

|

SU1176120A1 |

| US 20140139365 A1, 22.05.2014. | |||

Авторы

Даты

2021-05-07—Публикация

2020-08-05—Подача