Настоящее изобретение относится к области систем управления реального времени, часто обозначаемых аббревиатурой RTE (real-time executives). Системы RTE применяют в различных отраслях техники при необходимости обеспечить высокий уровень безопасности при исполнении процессов программного обеспечения. Системы управления реального времени, как правило, используют для управления ядерными электростанциями, для контроля и управления различными компонентами летательных средств или для контроля и управления критичными плавательными средствами, такими как военные подводные лодки и другие.

В области систем управления реального времени используется принцип разработки, называемый секционированием (partitioning). Секционирование направлено на обеспечение статического выделения ресурсов, включая память и время. Время, как правило, разбивают на последовательные временные слоты, которые в общем случае имеют одинаковую продолжительность. Такое секционирование призвано обеспечить такое выполнение набора задач в процессоре, при котором каждая задача будет иметь собственные ресурсы, называемые разделами (как правило, это область памяти и набор зарезервированных временных слотов). При этом гарантируется, что любые проблемы при исполнении задачи в каком-либо из разделов не смогут повилять на корректность функционирования других задач в других разделах.

Данный принцип реализуют, помимо прочих, в форме метода периодического задания последовательности выполнения, в котором в периодически повторяющиеся интервалы времени происходит прерывание текущей задачи и выполняется переключение на выполнение новой задачи с обеспечением гарантированной доступности ее ресурсов; это называют «переключением контекста».

В отношении методов разработки, используемых при создании требуемых задач, предназначенных для исполнения в подобных системах, определены сертификационные уровни (certification levels). Сертификационный уровень определяет предпринимаемые меры безопасности и используемые методы разработки; следовательно, он отражает объективный уровень качества программного обеспечения.

Поскольку принцип секционирования позволяет гарантировать, что в случае сбоя текущей задачи этот сбой никак не повлияет на другие задачи, проектирование каждой задачи можно осуществлять с сертификационным уровнем, соответствующим ее уровню критичности. Это удобно, поскольку стоимость разработки по критериям наивысшего сертификационного уровня является очень высокой.

К примеру, в области техники, связанной с микропрограммным обеспечением для авионики, принцип секционирования описан в стандарте ARINC 653, а сертификационные уровни определены стандартами ED-12B и DO-178B.

В последнем из упомянутых стандартов определены пять уровней критичности, или уровней надежности проектирования (design assurance level, DAL), от наивысшего сертификационного уровня A до самого низкого уровня Е.

Эти стандарты позволяют обеспечить высокий уровень надежности проектируемого программного обеспечения при сохранении контроля над стоимостью разработки за счет возможности разработки каждой задачи системы с соответствии с ее критичностью. Эти стандарты приспособлены для разработки программного обеспечения одноядерного процессора, в котором в каждый момент времени выполняется только одна задача.

Однако в последние несколько лет борьба за повышение вычислительной мощности процессоров пошла по направлению развития многоядерных процессоров. Как показывает практика, существующие многоядерные процессоры не гарантируют полной независимости работы ядер. Невозможно гарантировать, что задача, выполняемая в одном из ядер, при возникновении сбоя не повлияет на корректность выполнения другой задачи, исполняемой в другом ядре. Требование полной независимости, или “герметичности”, которое является основным принципом секционирования, следовательно, не позволяет осуществить простой перенос принципа секционирования и сертификационных уровней в сферу многоядерных процессоров для построения безопасных систем управления реального времени.

Настоящее изобретение направлено на решение описанных выше проблем при помощи задания, в дополнение к сертификационным уровням, свойственным каждой задаче, уровня безопасности, связанного с критичностью исполнения каждого экземпляра задачи в ее контексте, и с помощью способа задания последовательности исполнения задач с распределением по различным ядрам, который позволяет в каждом временном слоте обмениваться информацией о сертификационных уровнях и уровнях безопасности каждой из подготавливаемых к запуску задач. Затем в каждом ядре принимается решение о запуске планируемой задачи в соответствии с актуальной информацией, принятой от других ядер.

Настоящее изобретение относится к способу задания последовательности выполнения набора задач в процессоре, имеющем множество исполнительных ядер, при этом ресурсы упомянутого процессора разделяют на множество разделов, упомянутые разделы совместно используют временные ресурсы в форме последовательности временных слотов синхронно в каждом ядре процессора, упомянутый способ исполняется набором модулей задания последовательности исполнения, реализованных в упомянутых ядрах процессора, и в упомянутых модулях задания последовательности исполнения реализован компонент управления, при этом способ включает предварительный шаг задания для каждого экземпляра задачи, исполняемой в системе, уровня безопасности, связанного с критичностью исполнения данного конкретного экземпляра задачи, при этом каждой задаче дополнительно присвоен сертификационный уровень, связанный с методами разработки, применяемыми при ее создании;

причем способ включает, для каждого раздела, шаг обмена сообщениями между различными модулями задания последовательности исполнения в каждом ядре с целью информирования упомянутого компонента управления о сертификационных уровнях и уровнях безопасности задач, подготавливаемых к исполнению различными ядрами в текущем разделе, и шаг принятия решения о разрешении запуска для каждой из задач, подготавливаемых к запуску в каждом ядре, в соответствии с упомянутыми сертификационными уровнями и уровнями безопасности задач, подготавливаемых к запуску в том же разделе.

В соответствии с одним из конкретных вариантов осуществления настоящего изобретения способ включает также, для каждого раздела, шаг обновления уровня безопасности задачи, подготавливаемой к запуску, в соответствии с контекстом исполнения упомянутых задач.

В соответствии с одним из конкретных вариантов осуществления настоящего изобретения, упомянутый компонент управления является централизованным и располагается в одном из модулей задания последовательности исполнения одного из упомянутых ядер, при этом шаг обмена сообщениями состоит из шага передачи каждым модулем задания последовательности исполнения своей информации в этот модуль задания последовательности исполнения.

В соответствии с одним из конкретных вариантов осуществления настоящего изобретения, упомянутый компонент управления является распределенным среди упомянутых модулей задания последовательности исполнения в каждом ядре, при этом шаг обмена сообщениями состоит из шага передачи каждым модулем задания последовательности исполнения своей информации во все модули задания последовательности исполнения.

В соответствии с одним из конкретных вариантов осуществления настоящего изобретения, упомянутый шаг принятия решения о разрешении на запуск для каждой задачи, если количество упомянутых уровней безопасности равно четырем, включает следующие правила:

- задачу, имеющую уровень 1 безопасности, то есть самый низкий, исполняют, если выполнены следующие условия:

- для текущего раздела нет задач с уровнями 3 или 4 безопасности в другом ядре;

- любая из задач с уровнем 2 безопасности, присутствующая в другом ядре, имеет меньший или равный сертификационный уровень;

- задачу, имеющую уровень 2 безопасности, исполняют, если выполнены следующие условия:

- для текущего раздела нет задач с уровнями 3 или 4 безопасности в другом ядре;

- любая из задач с уровнем 2 безопасности, присутствующая в другом ядре, имеет меньший или равный сертификационный уровень;

- задачу, имеющую уровень 3 безопасности, исполняют, если выполнены следующие условия:

- для текущего раздела нет задач с уровнем 4 безопасности в другом ядре;

- любая из задач с уровнем 3 безопасности в другом ядре имеет меньший или равный сертификационный уровень, и в случае равенства, идентификационный номер задачи больше или равен по сравнению с другими;

- задачу, имеющую уровень 4 безопасности, исполняют, если выполнены следующие условия:

- любая из задач с уровнем 4 безопасности в другом ядре имеет меньший или равный сертификационный уровень, и в случае равенства, идентификационный номер задачи строго больше по сравнению с другими.

Упомянутые выше и другие отличительные особенности настоящего изобретения могут быть уяснены более детально при прочтении приведенного ниже описания одного из примеров его осуществления, при этом данное описание приведено со ссылками на приложенные чертежи, где:

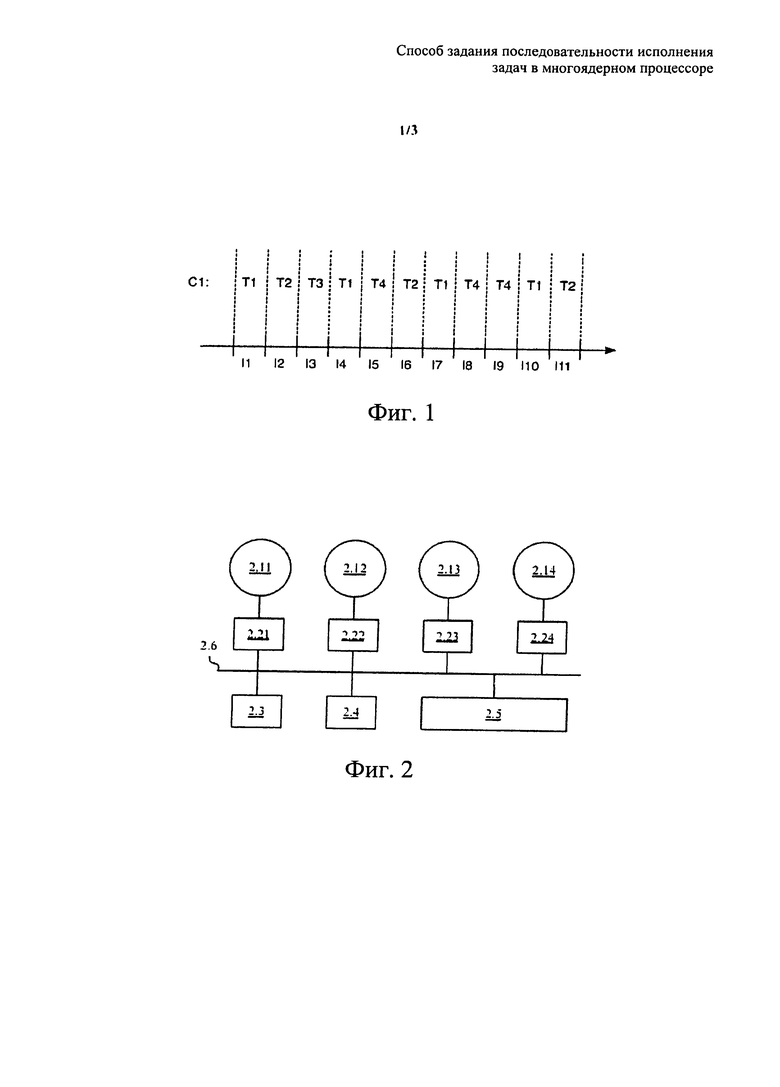

На Фиг. 1 проиллюстрировано задание последовательности исполнения задач в традиционной системе управления реального времени;

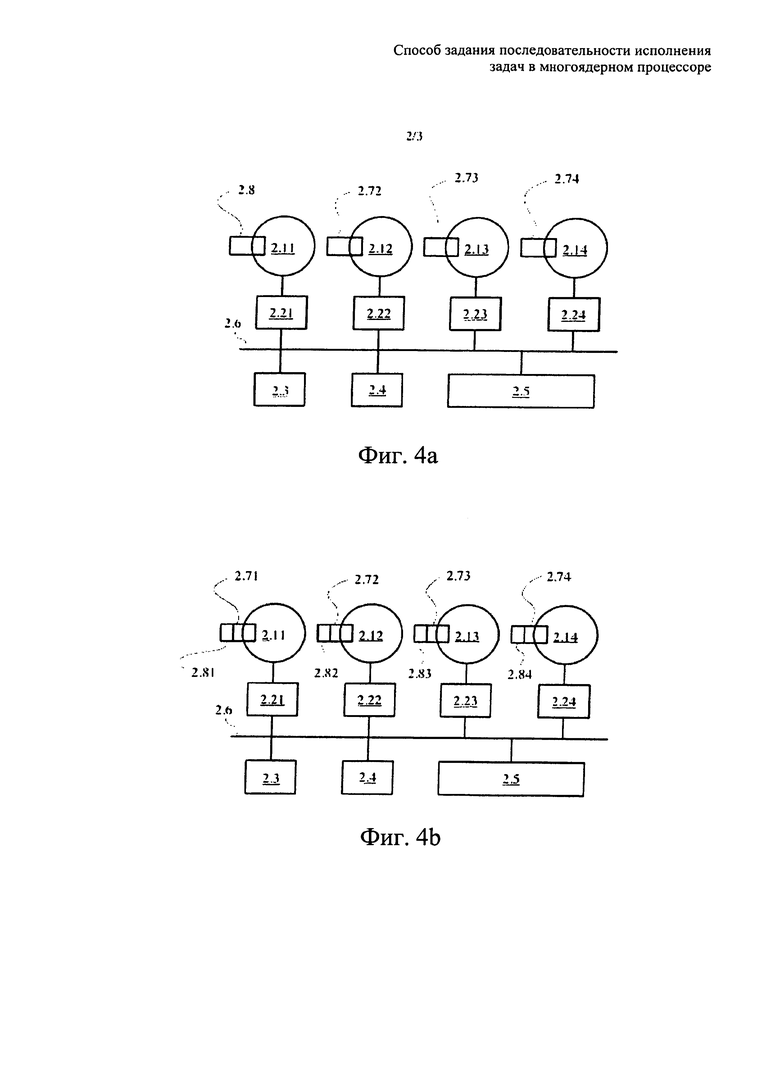

На Фиг. 2 проиллюстрирована типичная архитектура многоядерного процессора,

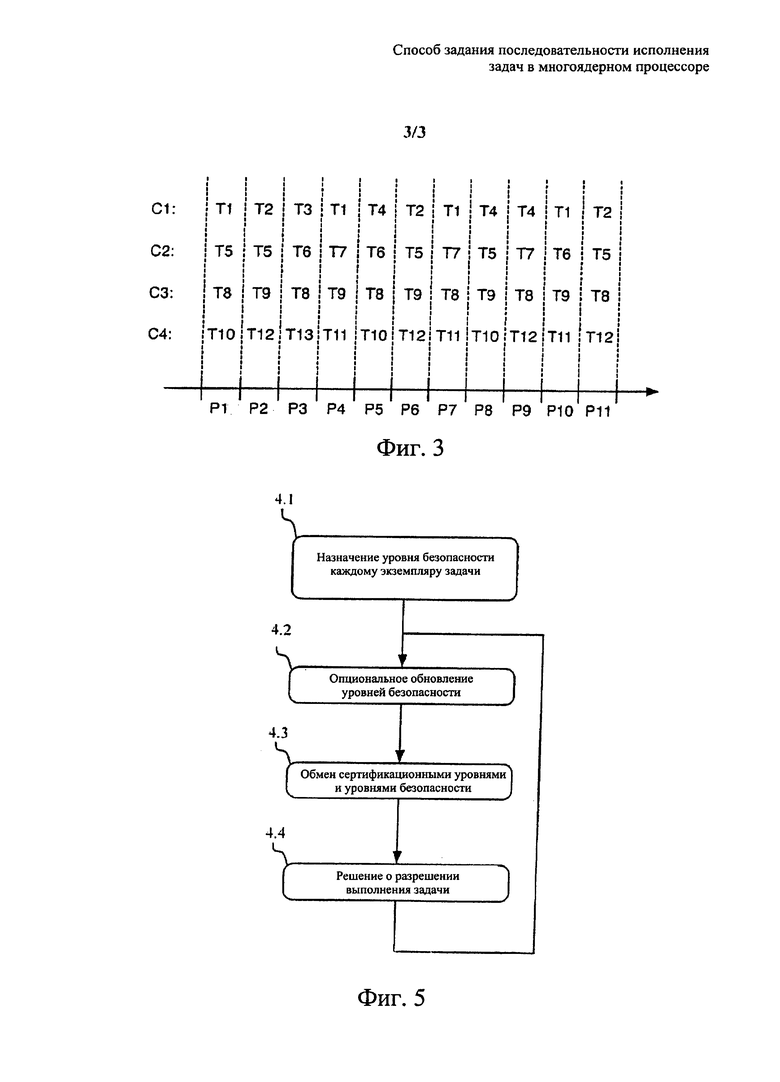

На Фиг. 3 проиллюстрирована работа системы, являющейся средой для реализации настоящего изобретения;

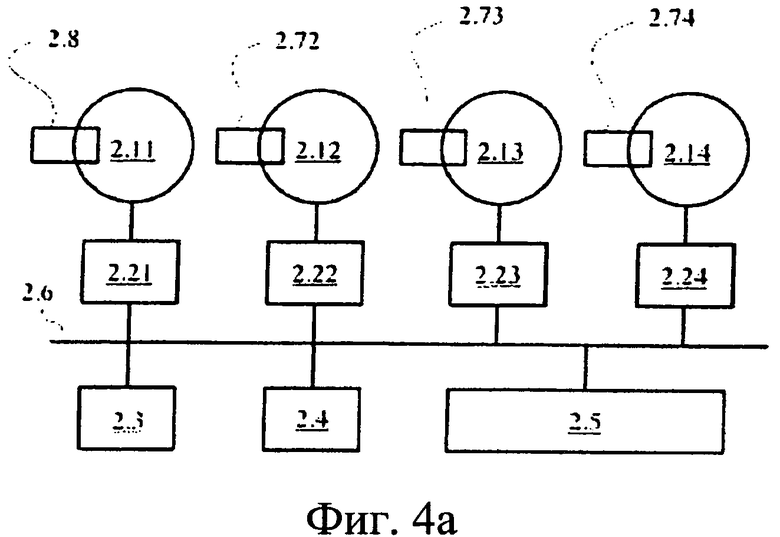

На Фиг. 4а и 4b соответственно проиллюстрированы два варианта осуществления компонента, который осуществляет управление модулями задания последовательности исполнения задач в ядрах процессора, и

На Фиг. 5 проиллюстрирован способ задания последовательности исполнения задач в соответствии с одним из примеров осуществления настоящего изобретения.

На Фиг. 1 проиллюстрировано управление последовательностью исполнения задач в традиционной системе управления реального времени, исполняемой в одноядерном процессоре. Задачи Т1, Т2, Т3 и Т4 поочередно исполняют в ядре С1. Время разбито на последовательные слоты I1 - I11. Каждый из этих слотов представляет собой временную составляющую раздела (в смысле описанного выше секционирования). Секционирование времени в общем случае является периодическим, то есть временные слоты имеют одинаковую продолжительность, однако это не является обязательным.

Каждая задача имеет собственный сертификационный уровень, зависящий от методов разработки, применяемых при ее программировании. Каждый раздел, соответственно, исполняют с сертификационным уровнем, присвоенным задаче, исполняемой в этом разделе. Система секционирования обеспечивает временной барьер между различными разделами. Раздел, в котором выполняется задача с низким сертификационным уровнем, не может, в случае сбоя этой задачи, повлиять на исполнение другой задачи в другом разделе, например, имеющей более высокий сертификационный уровень. Это важно, поскольку с каждым сертификационным уровнем связан определенный риск сбоя. Следовательно, для управления общим риском, связанным с эксплуатацией системы, важно, чтобы этот риск не мог повышаться вследствие работы других задач. Это является одним из важнейших факторов безопасности.

На Фиг. 2 проиллюстрирована типичная архитектура многоядерного процессора, В одном компоненте имеется множество вычислительных блоков 2.11-2.14. Эти вычислительные блоки, называемые ядрами, имеют примерно тот же набор функций, что и обычный одноядерный процессор. Для процессоров, имеющихся в настоящий момент на рынке, количество ядер может составлять от двух до четырех, но без сомнения, в ближайшие годы их количество будет расти. Как правило, каждое ядро оснащено по меньшей мере одной локальной памятью, 2.21-2.24, которую они могут использовать в качестве выделенной локальной рабочей памяти. Как правило, присутствует также общая для всех ядер 2.5 память. Упомянутый компонент имеет также набор из двух модулей 2.3, 2.4, предназначенных для различных операций, таких как ввод-вывод процессора, или специальный вычислительный блок, например, графический сопроцессор. Все эти различные модули осуществляют связь при помощи шины 2.5. В частности, доступ к общей памяти 2.5 организуется с помощью механизма кэширования в локальной памяти 2.21-2.24.

Данная архитектура и методы разработки, использованные при создании этих компонентов, в настоящее время не позволяют обеспечить барьер между задачами, исполняемыми в различных ядрах процессора. К примеру, задача, пострадавшая от сбоя в одном из ядер, может запускать некоторую последовательность операций с памятью, которые создадут эффект насыщения шины 2.6. По этой причине работа задач, исполняемых в других ядрах, может быть нарушена после сбоя упомянутой первой задачи. В этом контексте применение сертификационных уровней при разработке каждой из задач само по себе не гарантирует удовлетворительного уровня безопасности всей системы в целом. Под угрозой оказывается сам принцип секционирования, основанный на полной независимости разделов.

Мы определили понятие сертификационного уровня как внутреннее свойство заданного элемента программного обеспечения, связанное с методами разработки, использованными при его создании. Далее будет определено еще одно понятие, называемое уровнем безопасности. Уровень безопасности не является внутренним свойством программы, а представляет собой требование, связанное с исполнением конкретного экземпляра этой программы в конкретном контексте. Следовательно, он связан с конкретным случаем исполнения (или с конкретным ядром) задачи, которая представляет собой упомянутый исполняемый экземпляр программного обеспечения. Уровень безопасности связан с критичностью исполнения конкретного экземпляра задачи. Для одной и той же задачи критичность может со временем изменяться. К примеру, задача управления закрылками не является очень критичной при выруливании летательного средства, однако становится таковой во время посадки.

Предложенное в настоящем изобретении решение связано с принципом секционирования. А именно, время всегда разделяют на последовательные временные слоты. Это разделение является идентичным для всех ядер процессора. Ядра, соответственно, синхронизированы во времени. Как правило, эти временные слоты являются идентичными, однако данное условие несущественно для корректного функционирования системы.

На Фиг. 3 проиллюстрирована работа системы, являющейся средой для реализации настоящего изобретения. Чередование разделов Р1-Р11 во времени представлено на чертеже по оси X. Предполагается, что процессор имеет четыре ядра С1-С4. Для каждого раздела и для каждого ядра указано появление задачи, которая должна быть исполнена в соответствии с запланированной последовательностью исполнения.

Каждая из задач, или точнее, каждый из экземпляров задачи для каждого раздела и каждого ядра, имеет сертификационный уровень и уровень безопасности.

Поскольку сертификационный уровень связан с методами разработки, использованными для создания задачи, он, соответственно, косвенно связан с ее уровнем надежности, то есть с вероятностью сбоя упомянутой задачи.

Поскольку уровень безопасности связан с критичностью такого сбоя, например, сбоя данного экземпляра задачи в данном контексте исполнения, он связан с тяжестью прогнозируемых последствий подобного сбоя. В данном примере осуществления настоящего изобретения в основе системы лежат сертификационные уровни, определенные в стандарте DO-178B, предназначенном для области авионики. Этих уровней пять, они обозначаются латинскими буквами от А до Е. Уровень Ε соответствует программному обеспечению, проектируемому без каких-либо специальных ограничений. Следовательно, любое программное обеспечение по умолчанию может быть признано имеющим сертификационный уровень Е. Сертификационные уровни D-A налагают возрастающие ограничения по качеству. Также в данном примере осуществления настоящего изобретения имеется четыре уровня безопасности, пронумерованных от 1 до 4. При этом уровень 1 безопасности является самым низким. Он предполагает, что сбой задачи не имеет критичных последствий. По критичности влияния возможных сбоев уровни безопасности растут по порядку до 4-го, наивысшего уровня. Как правило, в авионике этот уровень присваивают задачам, сбой в которых может привести к аварии, ставящей под угрозу жизнь экипажа и/или пассажиров. Назначение уровня безопасности для задачи может осуществляться при помощи любых средств. Как правило, в данном примере осуществления настоящего изобретения, уровень безопасности каждой задачи в соответствии с ее контекстом назначается экспертом. Как уже упоминалось, уровень безопасности одной и той же задачи со временем может меняться, например, в зависимости от фазы полета. Данные сертификационные уровни и уровни безопасности характерны именно для проиллюстрированного примера осуществления настоящего изобретения. В других примерах их количество и наименования могут отличаться.

Предпочтительно, способ задания последовательности исполнения в соответствии с настоящим изобретением реализуется модулем задания последовательности исполнения задач, который исполняется в каждом из ядер процессора. На Фиг. 4а и 4b схематически показаны эти модули 2.71-2.74 в многоядерной архитектуре процессора, аналогичной архитектуре фиг. 2. Аналогичные элементы обозначены аналогичными обозначениями. Модули 2.71-2.74 могут осуществлять связь в форме обмена информацией, как правило, сообщениями. Компонент управления принимает решение о разрешении или не разрешении запуска запланированной задачи в разделе для каждого из ядер 2.11-2.14. Возможны два варианта реализации этого компонента управления.

В соответствии с первым вариантом осуществления настоящего изобретения, проиллюстрированном на фиг. 4а, который представляет собой централизованный режим, в качестве компонента управления выбран модуль задания последовательности исполнения в одном из ядер. На фиг. 4а этим модулем является модуль 2.8 ядра 2.11. Этот модуль 2.8 получает наименования модуля управления и осуществляет связь с другими модулями 2.72-2.74, чтобы: во-первых, получать информацию, необходимую для принятия решений, и во-вторых, для информирования остальных модулей 2.72-2.74 о принятых решениях.

В соответствии со вторым вариантом осуществления настоящего изобретения, который может быть назван распределенным режимом и проиллюстрирован на фиг. 4b, каждый модуль 2.71-2.74 задания последовательности исполнения в каждом ядре 2.11-2.14 реализует управление собственными задачами в модуле 2.81-2.84 управления, относящимися к ним. Все модули 2.81-2.84 в этом случае имеют эквивалентную функциональность, то есть компонент управления распределен между различными модулями. В данном варианте осуществления настоящего изобретения каждый из модулей 2.81-2.84 осуществляет связь с другими модулями для получения информации, необходимой для принятия им решений. Затем он принимает решение в отношении своих задач, при этом он, в отличие от первого варианта осуществления настоящего изобретения, не обязательно участвует в принятии решений для других модулей.

На Фиг. 5 проиллюстрирован способ задания последовательности исполнения в соответствии с настоящим изобретением, нацеленный на обеспечение управляемого уровня безопасности в системе, исполняемой в многоядерном процессоре. На первом шаге 4.1 каждому экземпляру задачи, исполняемой в некотором разделе в одном или более ядрах системы, назначают уровень безопасности в соответствии с предшествующим определением, данным в настоящем документе. Предпочтительно этот шаг выполняют до начала работы системы.

Во время работы для каждого раздела система повторяет следующие шаги.

На шаге 4.2, опционально, обновляют уровень безопасности задач, подготавливаемых к запуску в текущем разделе. Это необходимо, поскольку уровень безопасности связан с контекстом исполнения конкретного экземпляра задачи, поэтому предпочтительным является обеспечение его обновления в соответствии с возможными изменениями контекста каждого раздела. Этот шаг обновления является опциональным улучшением способа настоящего изобретения.

На шаге 4.3 происходит обмен сообщениями между различными модулями задания последовательности исполнения каждого ядра. Каждое ядро информирует компонент управления о сертификационных уровнях и уровнях безопасности задач, подготавливаемых к исполнению в этом ядре в текущем разделе. В случае, когда компонент управления является централизованным, упомянутый обмен сообщениями представляет собой, например, передачу информации из каждого модуля задания последовательности исполнения в тот модуль, где находится компонент управления. В случае, когда управление является распределенным, каждый модуль задания последовательности исполнения информирует все остальные модули в каждом ядре.

Компонент управления на шаге 4.4 принимает решение о разрешении запуска каждой из задач, подготавливаемых к запуску в каждом ядре. Данное решение принимается в соответствии с сертификационным уровнем и уровнем безопасности других задач, подготавливаемых к запуску в том же разделе.

В данном примере осуществления настоящего изобретения, решения принимаются в соответствии со следующими правилами.

Задачу, имеющую уровень 1 безопасности, то есть самый низкий, исполняют, если выполнены следующие условия:

- для текущего раздела нет задач с уровнями 3 или 4 безопасности в другом ядре;

- любая из задач с уровнем 2 безопасности, присутствующая в другом ядре, имеет меньший или равный сертификационный уровень.

Следует отметить, что это правило позволяет обеспечить сосуществование задач с различными сертификационными уровнями. Задача с уровнем 1 безопасности может сосуществовать с задачей с уровнем 2 безопасности, каждая в каком-либо ядре процессора, при условии, что ее сертификационный уровень является по меньшей мере равным сертификационному уровню задачи с уровнем 2 безопасности. Тем самым гарантируется, что задача с уровнем 1 безопасности не будет способна понизить общий сертификационный уровень раздела.

Задачу, имеющую уровень 2 безопасности, исполняют, если выполнены следующие условия:

- для текущего раздела нет задач с уровнями 3 или 4 безопасности в другом ядре;

- любая из задач с уровнем 2 безопасности, присутствующая в другом ядре, имеет меньший или равный сертификационный уровень.

Это правило предназначено главным образом для того, чтобы сделать возможным сосуществование во времени в различных ядрах задач с одинаковыми сертификационными уровнями. Исполняют разделы с уровнем 2, имеющие самые высокие сертификационные уровни, а также разделы уровня 1 безопасности, но с более высоким или равным сертификационным уровнем, если таковые существуют.

Задачу, имеющую уровень 3 безопасности, исполняют, если выполнены следующие условия:

- для текущего раздела нет задач с уровнем 4 безопасности в другом ядре;

- любая из задач с уровнем 3 безопасности, присутствующая в другом ядре, имеет меньший или равный сертификационный уровень. В случае равенства ее идентификационный номер должен быть большим или равным по сравнению с другими.

Это правило включает новый параметр задач - идентификационный номер. Номер обеспечивает уникальную идентификацию задачи. Если две задачи в двух различных ядрах имеют одинаковый идентификационный номер, такая ситуация указывает на то, что в этом случае исполняется одна задача в форме двух параллельных процессов, работающих по меньшей мере в двух ядрах. Это правило означает, что только одна задача с уровнем 3 будет исполняться в процессоре, опционально в распределенном виде в нескольких ядрах. В том же разделе не допускается работа других задач.

Задачу, имеющую уровень 4 безопасности, исполняют, если выполнены следующие условия:

- любая из задач с уровнем 4 безопасности, присутствующая в другом ядре, имеет меньший или равный сертификационный уровень. В случае равенства ее идентификационный номер должен быть строго больше по сравнению с другими.

Данное правило разрешает работу задачи с уровнем 4 только эксклюзивно в одном ядре. В данном случае, в отличие от уровня 3 безопасности, не допускается исполнение задачи с уровнем 4 безопасности в распределенном виде в нескольких ядрах. Задача с уровнем 4 безопасности всегда исполняется в своем разделе одна.

В последних двух правилах идентификатор задачи используется для реализации выбора одной задачи из набора задач. Специалисты в данной области техники должны понимать, что может использоваться любой другой способ выбора с обменом сообщениями; может также применяться и другой критерий, обеспечивающий возможность независимого выбора одной задачи распределенным образом. Эти распределенные алгоритмы выбора хорошо известны специалистам в данной области техники. Соответственно, применение идентификаторов задач не является необходимым для реализации настоящего изобретения. Допускается, к примеру, использование идентификационного номера ядра, который также позволяет осуществлять выбор.

Также необходимо понимать, что описанные правила представляют собой лишь один из примеров осуществления настоящего изобретения. Могут быть заданы другие правила, реализующие политику безопасности, которые могут отличаться количеством заданных уровней безопасности и контекстом применения системы.

Изобретение относится к способу задания последовательности исполнения задач в процессоре. Технический результат заключается в повышении надежности и безопасности выполнения задач в процессоре. Способ исполняется набором модулей задания последовательности исполнения, реализованных в ядрах процессора и реализующих компонент управления, при этом способ содержит шаг (4.3) обмена сообщениями между модулями задания последовательности исполнения и компонентом управления, выполняемый для информирования компонента управления о сертификационных уровнях и уровнях безопасности задач, подготавливаемых к исполнению, шаг (4.4) принятия решения о разрешении запуска для каждой из задач, подготавливаемых к запуску в каждом ядре, выполняемый для принятия решения о разрешении запуска упомянутого экземпляра задачи в соответствии с сертификационными уровнями и уровнями безопасности других задач, подготавливаемых к запуску в том же разделе шаг (4.1), осуществляемый, когда экземпляр задачи подготавливается к исполнению ядром в текущем разделе, путем предварительного задания уровня безопасности, связанного с критичностью исполнения этого экземпляра задачи в контексте системы для текущего раздела, при этом каждая задача также имеет сертификационный уровень, внутренне связанный с методами разработки, использованными при ее создании. 3 з.п. ф-лы, 6 ил.

1. Способ задания последовательности исполнения задач в процессоре, имеющем множество исполнительных ядер, при этом ресурсы упомянутого процессора разделены на множество разделов, упомянутые разделы совместно используют временные ресурсы в форме последовательности временных слотов синхронно в каждом ядре процессора, упомянутый способ исполняется набором модулей задания последовательности исполнения, реализованных в упомянутых ядрах процессора, и в упомянутых модулях задания последовательности исполнения реализован компонент управления, причем упомянутый способ включает:

- шаг (4.3) обмена сообщениями между различными модулями задания последовательности исполнения и упомянутым компонентом управления, и

- шаг (4.4) принятия решения о разрешении запуска для каждой из задач, подготавливаемых к запуску в каждом ядре,

отличающийся тем, что он также включает:

- шаг (4.1), осуществляемый, когда экземпляр задачи подготавливается к исполнению ядром в текущем разделе, путем предварительного задания уровня безопасности, связанного с критичностью исполнения этого экземпляра задачи в контексте упомянутой системы для текущего раздела, причем количество уровней безопасности равно четырем, при этом каждая задача также имеет сертификационный уровень, внутренне связанный с методами разработки, использованными при ее создании;

- при этом упомянутый шаг (4.3) обмена сообщениями выполняют, когда экземпляр задачи подготавливается к исполнению ядром в текущем разделе, посредством модуля задания последовательности исполнения упомянутого ядра для информирования упомянутого компонента управления о сертификационных уровнях и уровнях безопасности задач, подготавливаемых к исполнению, и

- упомянутый шаг (4.4) принятия решения выполняют, когда экземпляр задачи подготавливается к исполнению ядром в текущем разделе, для принятия решения о разрешении запуска упомянутого экземпляра задачи в соответствии с сертификационными уровнями и уровнями безопасности других задач, подготавливаемых к запуску в том же разделе,

причем упомянутый шаг (4.4) принятия решения включает следующие правила:

- задачу, имеющую уровень 1 безопасности, то есть самый низкий, исполняют, если выполнены следующие условия:

• для текущего раздела нет задач с уровнями 3 или 4 безопасности в другом ядре;

• любая из задач с уровнем 2 безопасности, присутствующая в другом ядре, имеет меньший или равный сертификационный уровень,

- задачу, имеющую уровень 2 безопасности, исполняют, если выполнены следующие условия:

• для текущего раздела нет задач с уровнями 3 или 4 безопасности в другом ядре;

• любая из задач с уровнем 2 безопасности, присутствующая в другом ядре, имеет меньший или равный сертификационный уровень;

- задачу, имеющую уровень 3 безопасности, исполняют, если выполнены следующие условия:

• для текущего раздела нет задач с уровнем 4 безопасности в другом ядре;

• любая из задач с уровнем 3 безопасности в другом ядре имеет меньший или равный сертификационный уровень, и в случае равенства идентификационный номер задачи больше или равен по сравнению с другими задачами;

- задачу, имеющую уровень 4 безопасности, исполняют, если выполнены следующие условия:

любая из задач с уровнем 4 безопасности в другом ядре имеет меньший или равный сертификационный уровень, и в случае равенства идентификационный номер задачи строго больше по сравнению с другими задачами.

2. Способ по п. 1, включающий также, для каждого раздела, шаг обновления уровня безопасности задач, подготавливаемых к запуску, в соответствии с контекстом исполнения упомянутых задач.

3. Способ по п. 1 или 2, отличающийся тем, что упомянутый компонент управления является централизованным и располагается в одном из модулей задания последовательности исполнения одного из упомянутых ядер, а упомянутый шаг обмена сообщениями состоит из шага передачи каждым модулем задания последовательности исполнения своей информации в этот модуль задания последовательности исполнения.

4. Способ по п. 1 или 2, отличающийся тем, что упомянутый компонент управления является распределенным среди упомянутых модулей задания последовательности исполнения в каждом ядре, и упомянутый шаг обмена сообщениями состоит из шага передачи каждым модулем задания последовательности исполнения своей информации во все модули задания последовательности исполнения.

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| R | |||

| Fuchsen, "How to address certification for multi-core based IMA platforms: Current status and potential solutions", Digital Avionics Systems Conference (DASC), 2010 IEEE/AIAA 29th, 3 Октября 2010 | |||

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОТЛАДКИ МНОГОЯДЕРНОЙ СИСТЕМЫ | 2007 |

|

RU2405192C2 |

Авторы

Даты

2017-06-29—Публикация

2012-11-08—Подача