Изобретение относится к вычислительной системе и, в частности (но не исключительно) к методам улучшения процедуры обучения и коррекции линии связи.

Краткое описание чертежей

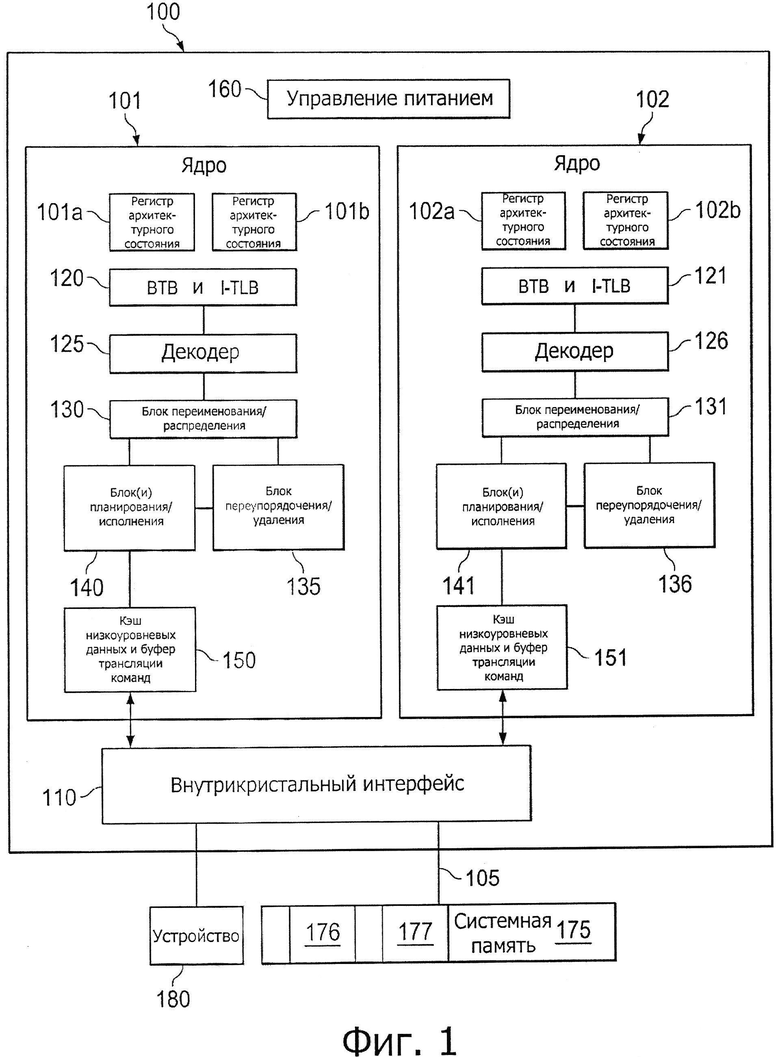

Фиг. 1 является условной схемой, иллюстрирующей вариант осуществления блок-схемы для вычислительной системы, включающей многоядерный процессор.

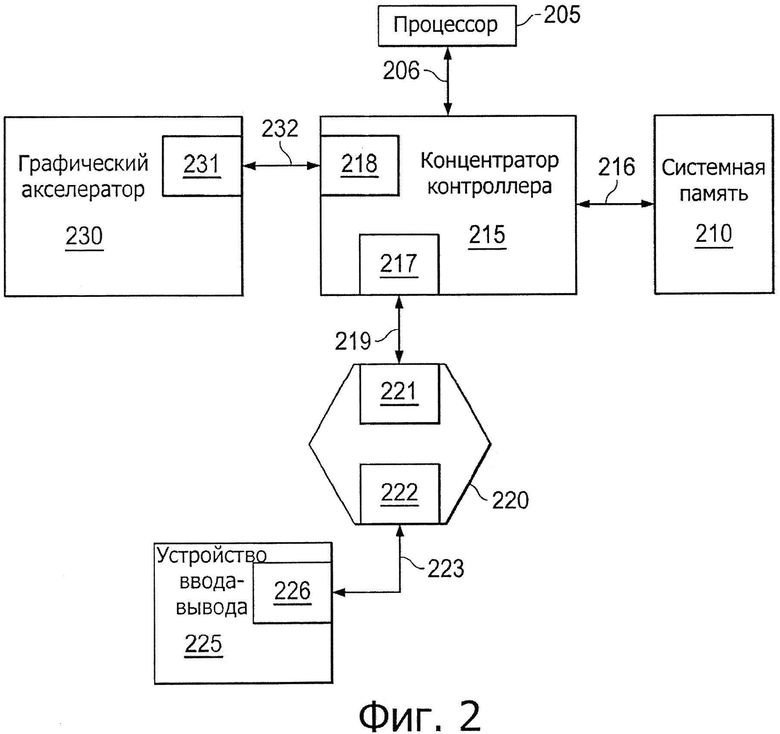

Фиг. 2 является условной схемой, иллюстрирующей вариант осуществления вычислительной системы, включающей в себя архитектуру, совместимую с разъемом взаимодействия периферийных компонентов типа экспресс (РВПКЭ) (PCIe).

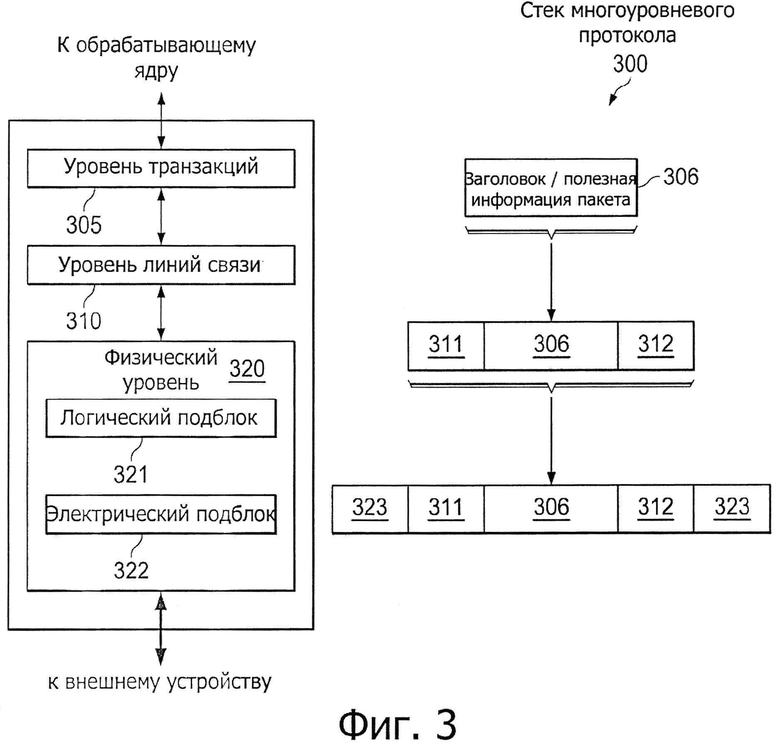

Фиг. 3 является условной схемой, иллюстрирующей вариант осуществления архитектуры межсоединений, совместимый с РВПКЭ, включающей в себя многоуровневую стековую память.

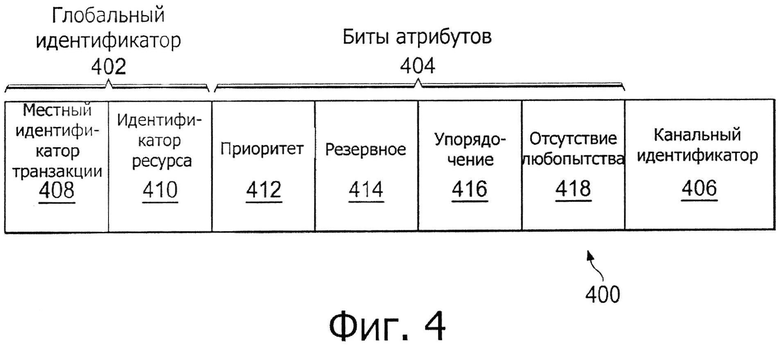

Фиг. 4 является условной схемой, иллюстрирующей вариант осуществления запроса или пакета, совместимого с РВПКЭ, подлежащего приему или передаче в архитектуре межсоединений.

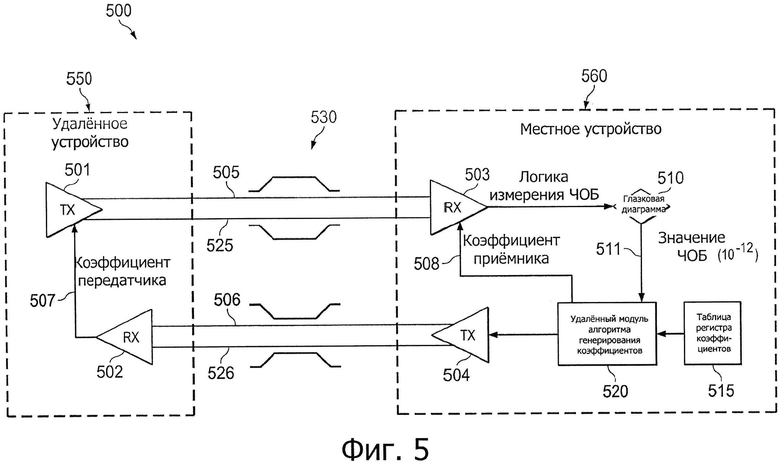

Фиг. 5 является условной схемой, иллюстрирующей вариант осуществления последовательного двухточечного оптоволокна РВПКЭ.

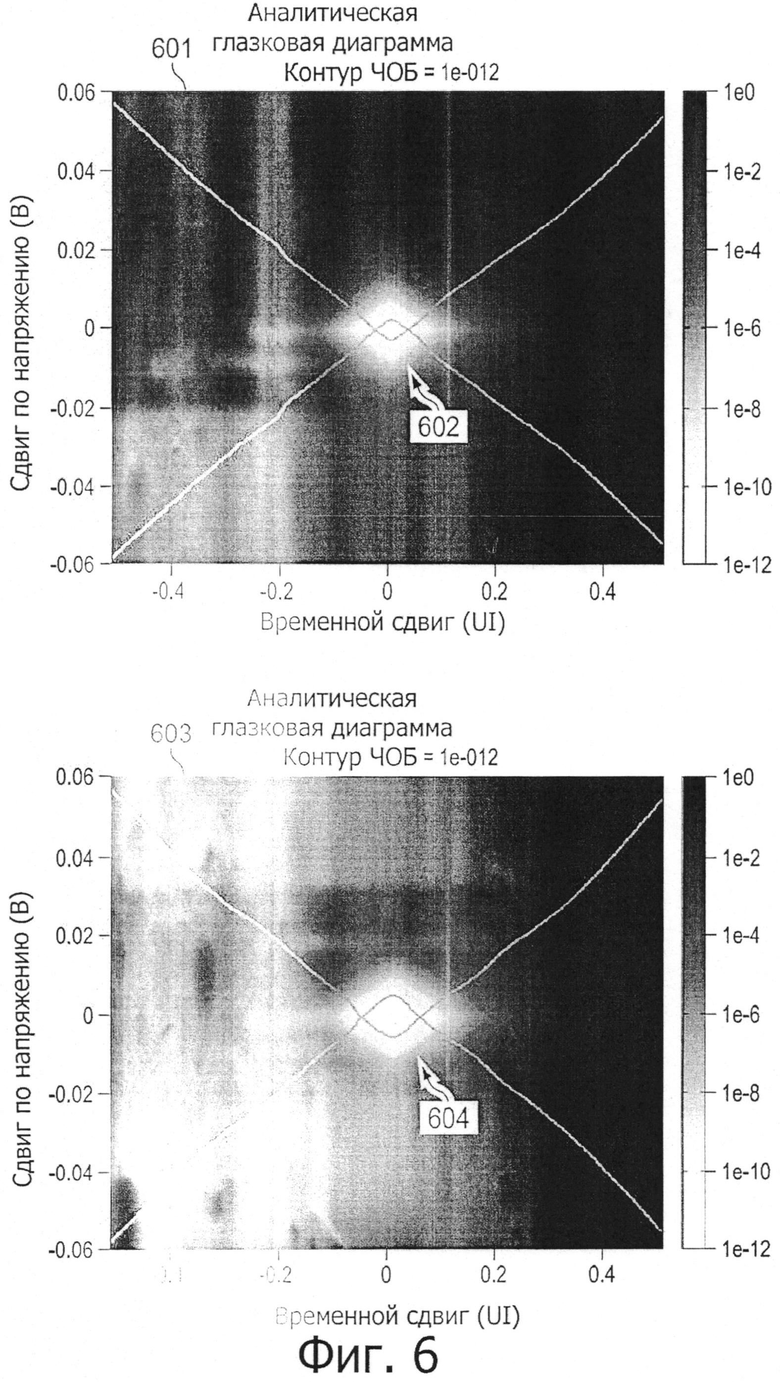

Фиг. 6 является условной схемой, иллюстрирующей глазковую диаграмму частоты ошибочных битов (ЧОБ) (BER) с наилучшей предустановкой и глазковую диаграмму ЧОБ с оптимизированными коэффициентами передачи.

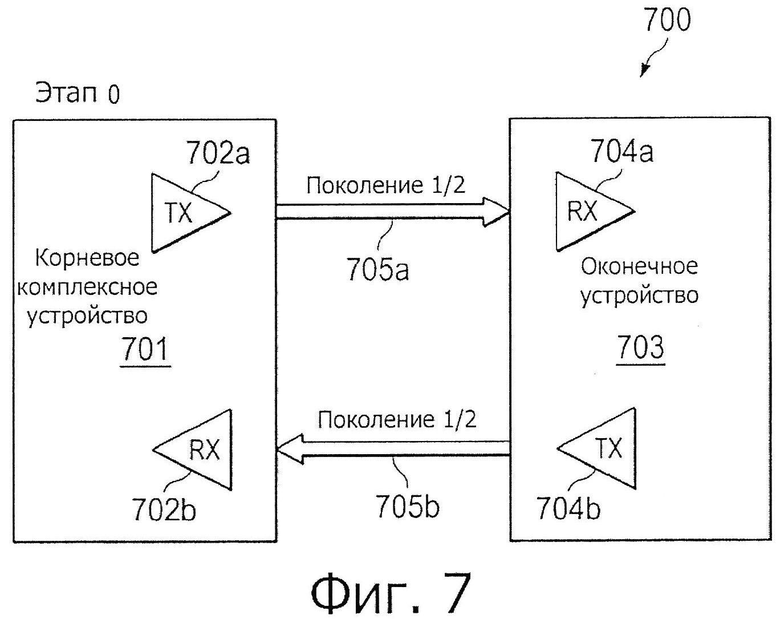

Фиг. 7 является условной схемой, иллюстрирующей вариант осуществления нулевого этапа процедуры обучения и коррекции линии связи.

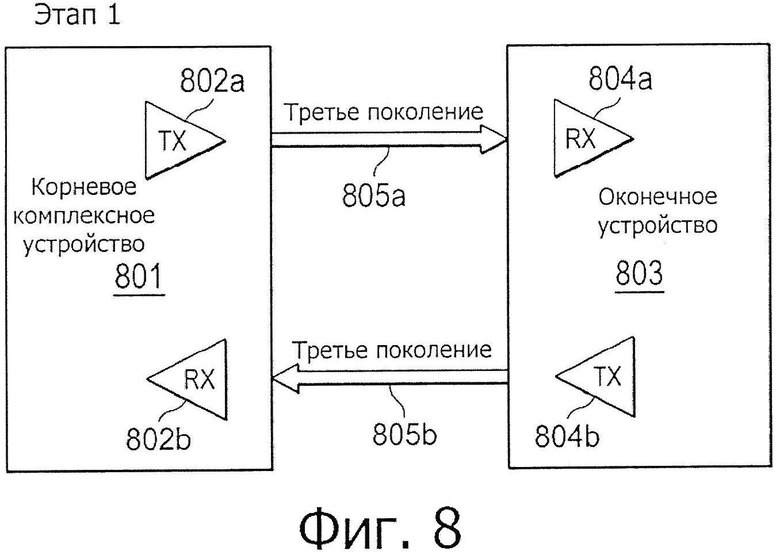

Фиг. 8 является условной схемой, иллюстрирующей вариант осуществления первого этапа процедуры обучения и коррекции линии связи.

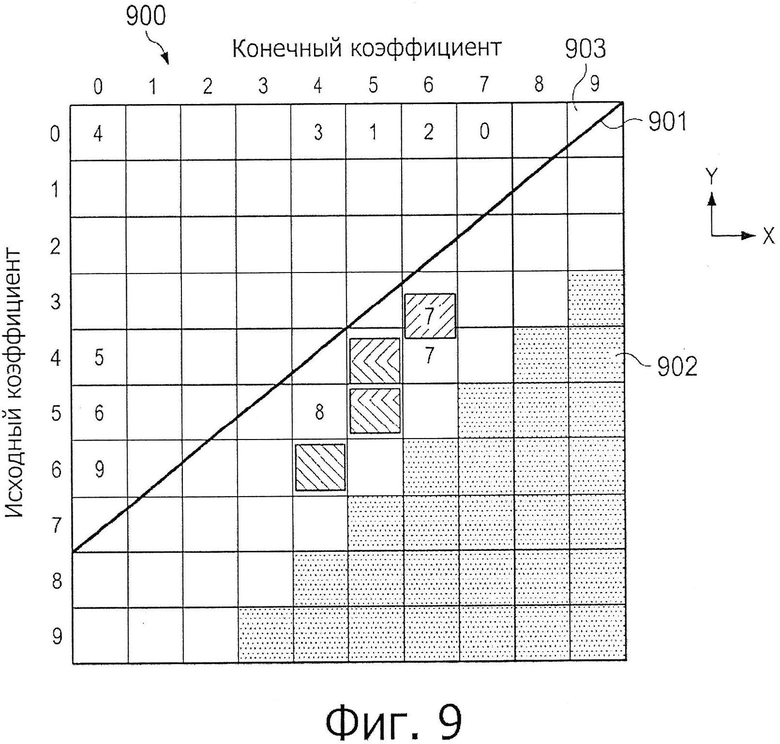

Фиг. 9 является условной схемой, иллюстрирующей таблицу, перечисляющую набор исходных и конечных коэффициентов, которые могут быть применены для установки передатчика или приемника.

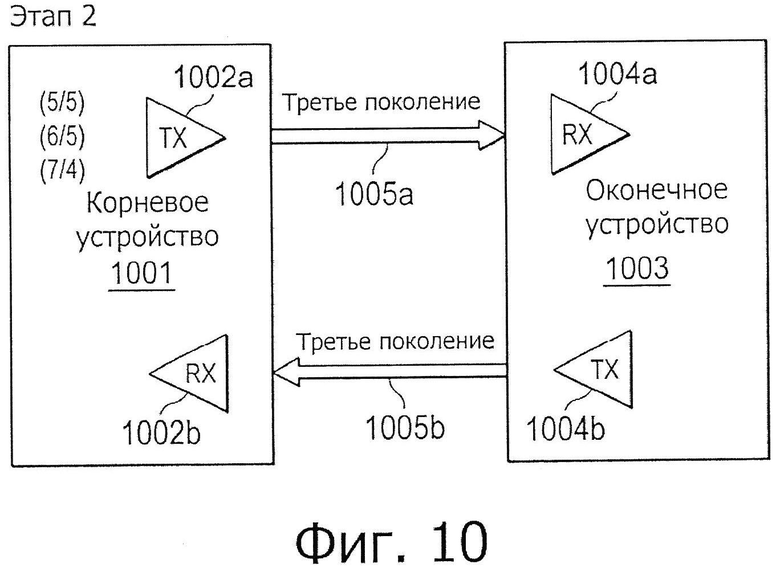

Фиг. 10 является условной схемой, иллюстрирующей вариант осуществления второго этапа процедуры обучения и коррекции линии связи.

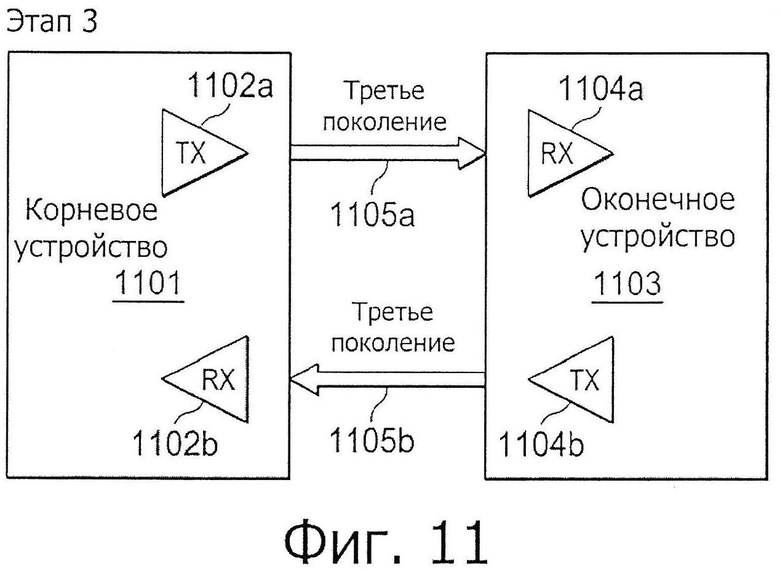

Фиг. 11 является условной схемой, иллюстрирующей вариант осуществления третьего этапа процедуры обучения и коррекции линии связи.

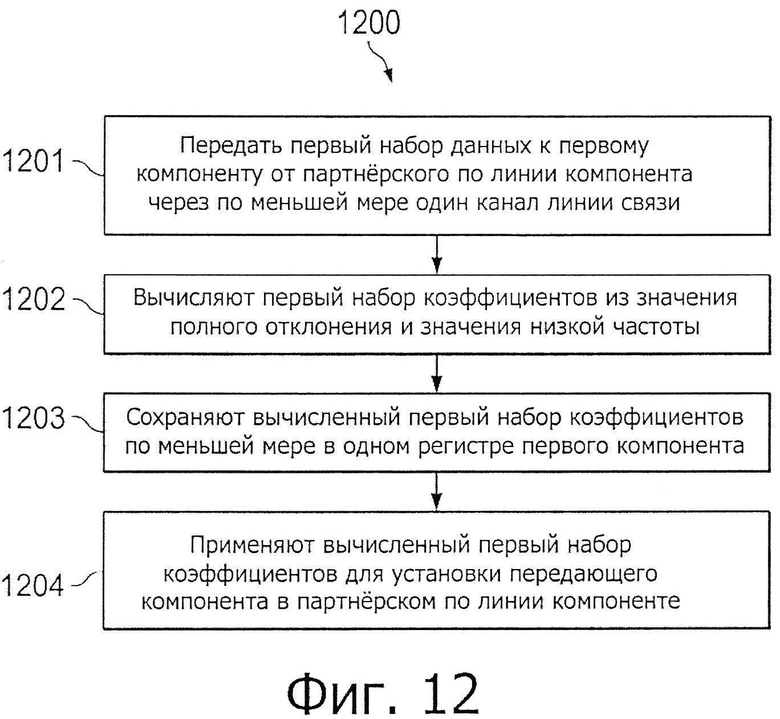

Фиг. 12 показывает способ для обучения и коррекции линии связи, совместимый с вариантом осуществления настоящего изобретения.

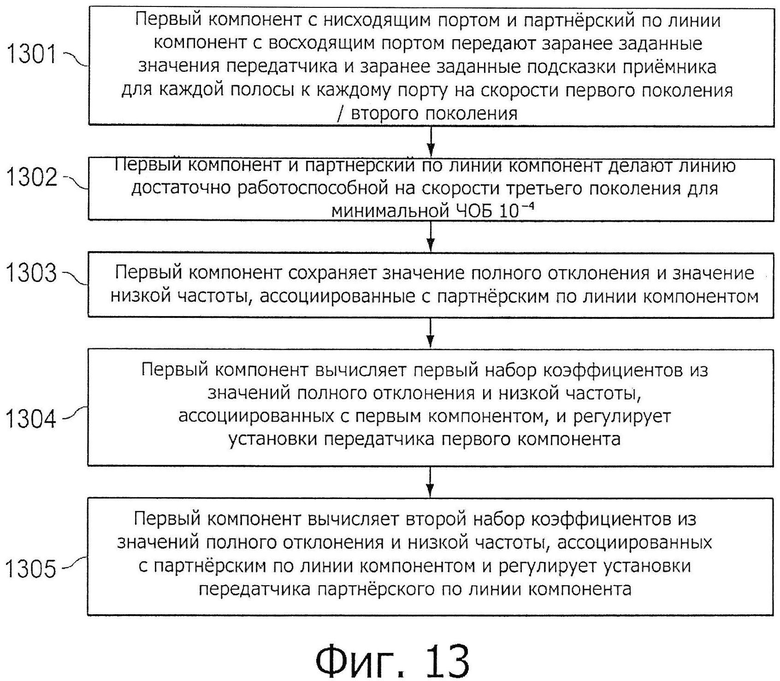

Фиг. 13 показывает другой способ для обучения и коррекции линии связи, совместимый с вариантом осуществления настоящего изобретения.

Подробное описание

В нижеследующем описании изложены многочисленные конкретные детали, такие как примеры конкретных типов процессоров и конфигураций систем, конкретные аппаратные структуры, конкретные подробности архитектуры и микроархитектуры, конкретные конфигурации регистров, конкретные типы команд, конкретные системные компоненты, конкретные измерения (высоты), конкретные ступени и операции процессорного конвейера и т.п., чтобы обеспечить детальное понимание настоящего изобретения. Для специалиста будет, однако, ясно, что эти конкретные подробности не обязательны при практическом применении настоящего изобретения. В иных случаях, общеизвестные компоненты или способы, такие как конкретные и альтернативные процессорные архитектуры, конкретные логические схемы или коды для описанных алгоритмов, конкретный микропрограммный код, конкретная операция межсоединения, конкретные логические конфигурации, конкретные методы изготовления и материалы, конкретные воплощения компилятора, конкретные выражения алгоритмов в коде, конкретные методы или логика отключения или отпирания питания и прочие конкретные подробности компьютерной системы не описаны в деталях, чтобы избежать ненужного запутывания настоящего изобретения.

Хотя нижеследующие варианты осуществления могут описываться со ссылкой на экономию энергии и энергетическую эффективность в конкретных интегральных схемах, таких как вычислительные платформы или микропроцессоры, другие варианты осуществления применимы к иным типам интегральных схем и логических устройств. Методы и пояснения, аналогичные описанным здесь вариантам осуществления, могут применяться к другим типам схем или полупроводниковых устройств, которые могут также получать выгоду от энергетической эффективности и экономии энергии. Например, раскрытые варианты осуществления не ограничены настольными компьютерными системами или системами Ultrabooks™. Они могут также использоваться в других устройствах, таких как карманные устройства, планшеты, иные тонкие ноутбуки, устройства на интегральных схемах и встроенные приложения. Некоторые примеры карманных устройств включают в себя сотовые телефоны, устройства Интернет-протокола, цифровые камеры, персональные цифровые ассистенты (ПЦА) (PDA) и карманные персональные компьютеры (ПК) (PC). Встроенные приложения, как правило, включают в себя микроконтроллер, цифровой сигнальный процессор (ЦСП) (DSP), систему на кристалле, сетевые компьютеры (NetPC), телевизионные приставки, сетевые концентраторы, коммутаторы глобальной вычислительной сети (WAN) или любую иную систему, которая может выполнять функции и операции, поясненные ниже. Кроме того, описанные здесь устройства, способы и системы не ограничены физическими вычислительными устройствами, но могут также относиться к программным оптимизациям для экономии энергии и энергетической эффективности. Как станет сразу ясно из нижеследующего описания, варианты осуществления описанных здесь способов, устройств и систем (касается ли это аппаратного обеспечения, встроенных программ, программного обеспечения или их комбинации) актуальны для будущего «зеленой технологии», сбалансированного с соображениями производительности.

По мере развития вычислительных систем их компоненты становятся все более сложными. В результате сложность архитектуры межсоединений для стыковки и осуществления связи между этими компонентами тоже увеличивается, чтобы гарантировать удовлетворение требований по ширине полосы пропускания для оптимальной работы компонентов. Далее, различные сегменты рынка требуют различных аспектов архитектур межсоединений, чтобы отвечать рыночным нуждам. Например, серверы требуют более высокой производительности, тогда как мобильная экосистема иногда способна жертвовать общей производительностью ради экономии мощности. Кроме того, единственное назначение большинства оптических волокон состоит в обеспечении наивысшей возможной производительности с максимальной экономией мощности. Ниже обсуждаются несколько межсоединений, которые будут иметь потенциальную выгоду из аспектов описанного здесь изобретения.

На фиг. 1 показан вариант осуществления блок-схемы для вычислительной системы, включающей в себя многоядерный процессор. Процессор 100 включает в себя любой процессор или устройство обработки, такое как микропроцессор, встроенный процессор, цифровой сигнальный процессор (ЦСП), сетевой процессор, карманный процессор, прикладной процессор, сопроцессор, система на кристалле (SoC) или иное устройство для исполнения кода. Процессор 100 в одном варианте осуществления включает в себя по меньшей мере два ядра: ядро 101 и 102, которые могут включать в себя асимметричные ядра или симметричные ядра (проиллюстрированный вариант осуществления). Однако процессор 100 может включать в себя любое число элементов обработки, которые могут быть симметричными или асимметричными.

В одном варианте осуществления элемент обработки относится к аппаратному обеспечению или логике для поддержания программного потока. Примеры аппаратных элементов обработки включают в себя: потоковый блок, потоковый слот, поток, блок обработки, контекст, контекстный блок, логический процессор, аппаратный поток, ядро и (или) любой иной элемент, который способен удерживать состояние для процессора, такое как исполняемое состояние или архитектурное состояние. Иными словами, элемент обработки в одном варианте осуществления относится к любой аппаратуре, способной независимо ассоциироваться с кодом, такой как программный поток, операционная система, приложение или иной код. Физическим процессором (или процессорной панелью) обычно называют интегральную схему, которая потенциально включает в себя любое число других элементов обработки, таких как ядра или аппаратные потоки.

Ядром часто именуют логику, расположенную на интегральной схеме, способной поддерживать независимое архитектурное состояние, причем каждое независимо поддерживаемое архитектурное состояние ассоциируется с по меньшей мере некоторыми выделенными источниками исполнения. В противоположность ядрам аппаратный поток обычно относится к любой логике, расположенной на интегральной схеме, способной поддерживать независимое архитектурное состояние, причем эти независимо поддерживаемые архитектурное состояния совместно обращаются к источникам исполнения. Как видно, когда некоторые ресурсы используются совместно, а прочие выделены архитектурному состоянию, протягивается линия между номенклатурой аппаратного потока и ядром. Зачастую, ядро и аппаратный поток рассматриваются операционной системой как отдельные логические процессоры, где операционная система способна по отдельности планировать операции на каждом логическом процессоре.

Физический процессор 100, как показано на фиг. 1, включает два ядра: ядро 101 и ядро 102. Ядро 100 и ядро 102 считаются симметричными ядрами, т.е. ядрами с одинаковыми конфигурациями, функциональными блоками и (или) логикой. В другом варианте осуществления ядро 101 включает в себя особенное процессорное ядро, тогда как ядро 102 включает в себя обычное процессорное ядро. Однако ядра 101 и 102 могут по отдельности выбираться из любого типа ядер, таких как собственное ядро, программно-управляемое ядро, ядро, приспособленное для исполнения собственной структуры системы команд (ССК) (ISA), ядро, приспособленное для исполнения транслированной структуры системы команд, совместно разработанное ядро или иное известное ядро. В среде гетерогенных ядер (т.е. симметричных ядер) некоторая форма трансляции, такая как двоичная трансляция, может использоваться для составления графика или для исполнения кода в одном или обоих ядрах. В продолжение обсуждения, проиллюстрированные в ядре 101 функциональные блоки описаны более подробно ниже, а блоки в ядре 102 в описанном варианте осуществления работают аналогично.

Как показано, ядро 101 включает в себя два аппаратных потока 101а и 101b, которые могут также именоваться как аппаратные потоковые слоты 101а и 101b. Поэтому программные элементы, такие как операционная система, в одном варианте осуществления потенциально рассматривают процессор 100 как четыре раздельных процессора, т.е. четыре логических процессора или элемента обработки, способных одновременно исполнять четыре программных потока. Как упомянуто выше, первый поток ассоциируется с регистрами 101а архитектурного состояния, второй поток ассоциируется с регистрами 101b архитектурного состояния, третий поток может ассоциироваться с регистрами 102а архитектурного состояния, а четвертый поток может ассоциироваться с регистрами 102b архитектурного состояния. Здесь каждый из регистров (101а, 101b, 102а и 102b) архитектурного состояния может пониматься как элементы обработки, потоковые слоты или потоковые блоки, как описано выше. Как показано, регистры 101a архитектурного состояния повторяются в регистрах 101b архитектурного состояния, так что отдельные архитектурные состояния (контексты) способны сохраняться для логического процессора 101а и логического процессора 101b. В ядре 101 другие меньшие ресурсы, такие как указатели команд и логика переименования в блоке 130 распределения и переименования, также могут дублироваться для потоков 101a и 101b. Некоторые ресурсы, такие как переупорядочивающие буферы в блоке 135 переупорядочения/удаления, буфер 120 трансляции команд (БТК) (ITLB), буферы загрузки/хранения и очереди могут совместно использоваться посредством распределения. Другие ресурсы, такие как универсальные внешние регистры, базовый(-ые) регистр(ы) таблицы переадресации страниц, кэш низкоуровневых данных и буфер 150 трансляции данных, функциональный(-ые) модуль(-и) 140 и части особенного блока 135 потенциально являются полностью совместно используемыми.

Процессор 100 зачастую включает в себя другие ресурсы, которые могут быть полностью совместно используемыми, совместно используемыми посредством распределения, или выделяться элементами либо элементам обработки. На фиг. 1 показан вариант осуществления чисто примерного процессора с проиллюстрированными логическими блоками/ресурсами процессора. Отметим, что процессор может включать в себя или опускать любые из этих функциональных блоков, а также включать в себя любые иные непоказанные известные функциональные блоки, логику или встроенное программное обеспечение. Как показано, ядро 101 включает в себя упрощенное характерное особенное процессорное ядро. Но в отличных вариантах осуществления может использоваться обычный процессор. Особенное ядро включает в себя целевой буфер 120 ветвлений для предсказания ветвлений, подлежащих исполнению/получению, и буфер 120 трансляции команд (БТК) (I-TLB) для хранения входных данных трансляции адреса для команд.

Ядро 101 далее включает в себя декодирующий модуль 125, связанный с блоком 120 выборки, для декодирования выбранных элементов. Логика выборки в одном варианте осуществления включает в себя отдельные последовательности, ассоциированные с потоковыми слотами 101а, 101b, соответственно. Обычно ядро 101 ассоциируется с первой структурой системы команд (ССК), которая определяет/конкретизирует команды, исполняемые в процессоре 100. Часто команды машинного кода, которые являются частью первой ССК, включают в себя часть команды (именуемую кодом операции), которая ссылается на (конкретизирует) команду или операцию, подлежащую выполнению. Декодирующая логика 125 включает в себя схему, которая распознает эти команды из их кодов операции и пропускает декодированные команды в конвейер для обработки, как определено первой ССК. Например, как более подробно описано ниже, декодеры 125 в одном варианте осуществления включают в себя логику, разработанную или приспособленную для распознавания конкретных команд, таких как команда транзакции. В результате распознавания декодерами 125 архитектура или ядро 101 воспринимает конкретные заранее заданные действия для выполнения задач, связанных с соответствующей командой. Важно отметить, что любые из описанных здесь задач, блоков, операций и способов могут выполняться в ответ на единственную команду или множество команд, некоторые из которых могут быть новыми или старыми командами. Отметим, что декодеры 126 в одном варианте осуществления распознают одну и туже ССК (или ее поднабор). Альтернативно, в среде гетерогенных ядер декодеры 126 распознают вторую ССК (либо поднабор первой ССК, либо отличную ССК).

В одном примере блок 130 распределения и переименования включает в себя распределитель для резервных ресурсов, таких как регистровые файлы, для хранения результатов обработки команд. Однако потоки 101а и 101b потенциально способны к особенному исполнению, когда блок 130 распределения и переименования также резервирует другие ресурсы, такие как буферы переупорядочения, чтобы прослеживать результаты команд. Блок 130 может также включать в себя переименователь регистров для переименования регистров ссылок на программы/команды в другие регистры, внутренние для процессора 100. Блок 135 переупорядочения/удаления включает в себя такие компоненты как упомянутые выше буферы переупорядочения, буферы загрузки и буферы хранения для поддержания особенного исполнения и последующего обычного удаления команд особенного исполнения.

Блок 140 планировщика и функционального(-ых) модуля(-ей) в одном варианте осуществления включает в себя блок планировщика для планирования команд/операций в функциональных модулях. Например, команда с плавающей запятой планируется в части функционального модуля, который имеет доступный функциональный модуль с плавающей запятой. Регистровые файлы, ассоциированные с функциональными модулями, также включены для хранения результатов обработки информационных команд. Примерные функциональные модули включают в себя функциональный модуль с плавающей запятой, функциональный модуль целых чисел, функциональный модуль операции перехода, функциональный модуль загрузки, функциональный модуль хранения и другие известные функциональные модули.

Кэш низкоуровневых данных и буфер 150 трансляции команд (БТК) (D-TLB) соединен с функциональным(и) модулем(-ями). Кэш данных предназначен для хранения недавно использованных/работавших данных в элементах, таких как операнды данных, которые потенциально удерживаются в связных состояниях памяти. БТК предназначен для хранения недавних трансляций адреса из виртуального/линейного в физический. В качестве конкретного примера процессор может включать в себя структуру таблицы переадресации страниц для разбиения физической памяти на множество виртуальных страниц.

Здесь ядра 101 и 102 совместно обращаются к высокоуровневому или еще более высокому кэшу, такому как кэш второго уровня, связанный с внутрикристальным интерфейсом 110. Отметим, что высокоуровневый или еще более высокий относится к уровням кэша, увеличивающим или дающим дальнейший путь от функциональных модулей. В одном варианте осуществления высокоуровневый кэш представляет собой кэш данных последнего уровня, последний кэш в иерархии памяти в процессоре 100, такой как кэш данных второго или третьего уровня. Однако кэш более высокого уровня не имеет такого ограничения, т.к. он может быть связан с кэшем команд или включать его. Вместо этого кэш трасс - тип кэша команд - может быть связан с декодером 135 для хранения недавно декодированных трасс. Здесь командой потенциально называется макрокоманда (т.е. общая команда, распознанная декодерами), которую можно декодировать в несколько микрокоманд (микроопераций).

В показанной конфигурации процессор 100 также включает в себя модуль 110 внутрикристального интерфейса. Исторически контроллер памяти, который более подробно описан ниже, включен в вычислительную систему, внешнюю для процессора 100. В этом сценарии внутрикристальный интерфейс 110 служит для связи с устройствами, внешними для процессора 100, такими как системная память 175, набор микросхем (часто включающий в себя концентратор контроллера памяти для соединения с памятью 175 и концентратор контроллера ввода-вывода для соединения с периферийными устройствами), концентратор контроллера памяти, северный мост или другую интегральную схему. И в этом сценарии шина 105 может включать в себя любое известное межсоединение, такое как многоточечная шина, двухточечное межсоединение, последовательное межсоединение, параллельная шина, согласованная (к примеру, согласованная с кэшем) шина, архитектура многоуровневого протокола, разностная шина и GTL шина.

Память 175 может быть назначена процессору 100 или совместно использоваться с другими устройствами в системе. Общие примеры типов памяти 175 включают в себя динамическое оперативное запоминающее устройство (ДОЗУ) (DRAM), статическое оперативное запоминающее устройство (СОЗУ) (SRAM), энергонезависимая память и другие известные запоминающие устройства. Отметим, что устройство 180 может включать в себя графический ускоритель, процессор и карту, связанные с концентратором контроллера памяти, накопитель данных, связанный с концентратором контроллера ввода-вывода, беспроводный приемопередатчик, устройство флэш-памяти, аудио контроллер, сетевой контроллер или иное известное устройство.

Однако в последнее время, по мере того, как все больше логики и устройств интегрируются на едином кристалле, таком как интегральная схема, каждое из этих устройств может быть встроено в процессор 100. Например, в одном варианте осуществления концентратор контроллера памяти находится в одном корпусе и (или) кристалле с процессором 100. Здесь часть ядра (часть в ядре) 110 включает в себя один или несколько контроллеров для взаимодействия с другими устройствами, такими как память 175 или графическое устройство. Конфигурация, включающая в себя межсоединение и контроллеры для взаимодействия с такими устройствами, часто именуется резидентной (или конфигурацией un-core). В качестве примера, внутрикристальный интерфейс 110 включает в себя кольцевое межсоединение для внутрикристальной связи и высокоскоростную последовательную двухточечную линию 105 связи для связи вне кристалла. Далее, в среде интегральной схемы даже больше устройств, таких как сетевой интерфейс, сопроцессоры, память 175, графический процессор 180 и любые иные известные компьютерные устройства или интерфейсы могут быть встроены в единственный кристалл или интегральную схему, чтобы обеспечить малые конструктивные параметры при высокой функциональности и низком потреблении мощности.

В одном варианте осуществления процессор 100 способен исполнять код 177 компилятора, оптимизатора и (или) транслятора для компиляции, трансляции и (или) оптимизации прикладного кода 176, чтобы поддерживать описанные здесь устройство и способ или интерфейс к ним. Компилятор часто включает в себя программу или набор программ для трансляции исходного текста/кода в выходной текст/код. Обычно компиляция программного/прикладного кода компилятором происходит во множестве стадий и проходов для преобразования кода высокоуровневого языка программирования в код низкоуровневого машинного или ассемблерного языка. Далее, для простой компиляции могут по-прежнему использоваться компиляторы единственного прохода. Компилятор может использовать любые известные методы компиляции и выполнять любые известные операции компилятора, такие как лексический анализ, предварительная обработка, синтаксический анализ, семантический анализ, генерирование кода, преобразование кода и оптимизация кода.

Более крупные компиляторы часто используют множество стадий, но чаще всего эти стадии включены в два общих этапа: (1) предварительный, т.е. в общем, когда могут иметь место синтаксическая обработка, семантическая обработка и кое-что из преобразования/оптимизации, и (2) завершающий, т.е. в общем, когда имеют место анализ, преобразования, оптимизации и генерирование кода. Некоторые компиляторы именуются средними, что иллюстрирует размывание границы между предварительным и завершающим компиляторами. В результате ссылка на введение, ассоциирование, генерирование или иную операцию могут иметь место в любых из вышеупомянутых стадий или проходов, а также в любых иных стадиях или проходах компилятора. В качестве иллюстративного примера, компилятор потенциально вводит операции, вызовы, функции и т.п.в одной или нескольких стадиях компиляции, как введение вызовов/операций в предварительной стадии компиляции, а затем преобразование этих вызовов/операций в низкоуровневый код во время стадии преобразования. Отметим, что в ходе динамической компиляции код компилятора или код динамической оптимизации может вводить такие операции/вызовы, а также оптимизировать код для исполнения во время прогона. В качестве конкретного иллюстративного примера, двоичный код (уже компилированный код) может динамически оптимизироваться во время прогона. Здесь, программный код может включать в себя код динамической оптимизации, двоичный код или их комбинацию.

Аналогично компилятору транслятор, такой как двоичный транслятор, транслирует код либо статически, либо динамически, для оптимизации и (или) трансляции кода. Поэтому ссылка на исполнение кода, прикладной код, программный код или иную программную среду может быть сделана на: (1) исполнение компилированных(-ой) программ(ы), оптимизатора кода оптимизации или транслятора либо динамически, либо статически, чтобы компилировать программный код для сохранения программных структур, выполнения других операций, оптимизации кода или трансляции кода; (2) исполнение основного программного кода, включающего в себя операции/вызовы, такие как прикладной код, который оптимизирован/компилирован; (3) исполнение другого программного кода, такого как библиотеки, связанного с основным программным кодом, для сохранения программных структур, выполнения другого программного обеспечения, относящегося к операциям, или для оптимизации кода; или (4) их комбинацию.

Одна архитектура межсоединительного оптического волокна включает в себя архитектуру с разъемом взаимодействия периферийных компонентов типа экспресс (РВПКЭ) (PCIe). Первичная цель РВПКЭ состоит в том, чтобы дать возможность компонентам и устройствам от разных поставщиков взаимодействовать в открытой архитектуре, перекрывая множество сегментов рынка: клиентам (настольным и мобильным устройствам), серверам (стандартным и предпринимательским) и встроенным и связным устройствам. РВПК Экспресс является высокопроизводительным универсальным входным-выходным межсоединением для широкого разнообразия будущих вычислительных и связных платформ. Некоторые атрибуты РВПК, такие как модель использования, архитектура загрузки-хранения и программные интерфейсы, поддерживаются посредством их пересмотра, тогда как предыдущие воплощения параллельной шины заменены сильно расширяемым полностью последовательным интерфейсом. Самые последние версии РВПК Экспресс получают преимущество от улучшений двухточечных межсоединений, технологии на основе коммутаций и пакетированного протокола для доставки новых уровней качества и свойств. Среди некоторых из улучшенных свойств, поддерживаемых РВПК Экспресс, управление энергопотреблением, качество сервиса, поддержка горячего включения / горячей замены, целостность данных и обработка ошибок.

На фиг. 2 показан вариант осуществления оптического волокна, составленного из двухточечных линий связи, которые соединяют между собой набор компонентов. Система 200 включает в себя процессор 205 и системную память 210, соединенную с концентратором 215 контроллера. Процессор 205 включает в себя любой элемент обработки, такой как микропроцессор, главный процессор, встроенный процессор, сопроцессор или другой процессор. Процессор 205 соединен с концентратором 215 контроллера посредством внешней шины (ВШ) (FSB) 206. В одном варианте осуществления ВШ 206 является последовательным двухточечным межсоединением, как описано ниже. В другом варианте осуществления линия 206 связи включает в себя последовательную разностную межсоединительную архитектуру, которая совместима со стандартом разностного межсоединения.

Системная память 210 включает в себя любое запоминающее устройство, такое как оперативное запоминающее устройство (ОЗУ) (RAM), энергонезависимая память или другая память, к которой могут обращаться устройства в системе 200. Системная память 210 соединена с концентратором 215 контроллера посредством интерфейса 216 памяти. Примеры интерфейса памяти включают в себя интерфейс памяти с двойной скоростью данных (ДСД) (DDR), двухканальный интерфейс памяти ДСД и интерфейс памяти динамического ОЗУ (ДОЗУ) (DRAM).

В одном варианте осуществления концентратор 215 контроллера является корневым концентратором, корневым комплексом или корневым контроллером в иерархии межсоединений с разъемом взаимодействия периферийных компонентов типа экспресс (РВПКЭ). Примеры концентратора 215 контроллера включают в себя набор микросхем, концентратор контроллера памяти (ККП) (МСН), северный мост, концентратор контроллера межсоединений (ККМ) (ICH), южный мост и корневой контроллер/концентратор. Зачастую термин «набор микросхем» относится к двум физически раздельным концентраторам контроллера, т.е. к концентратору контроллера памяти (ККП), соединенному с концентратором контроллера межсоединений (ККМ). Отметим, что нынешние системы часто включают в себя ККП, интегрированный с процессором 205, тогда как контроллер 215 служит для связи с устройствами ввода-вывода таким же образом, как описано ниже. В некоторых вариантах осуществления одноранговая маршрутизация опционально поддерживается посредством корневого сложного устройства.

Здесь, концентратор 215 контроллера связан с коммутатором/мостом 220 посредством последовательной линии 219 связи. Модули 217 и 218 ввода-вывода, которые могут также именоваться интерфейсами/портами 217 и 218, включают/воплощают стек многоуровневого протокола, чтобы обеспечить связь между концентратором 215 контроллера и коммутатором 220. В одном варианте осуществления множество устройств способны соединяться с коммутатором 220.

Коммутатор/мост 220 маршрутизирует пакеты/сообщения от устройства 225 в восходящем направлении, т.е. вверх по иерархии в направлении корневого комплекса, к концентратору 215 контроллера и в нисходящем направлении, т.е. вниз по иерархии в направлении от корневого контроллера, от процессора 205 или системной памяти 210 к устройству 225. Коммутатором 220 в одном варианте осуществления называется логическая сборка из множества виртуальных мостовых устройств РВПК-РВПК.

Устройство 225 включает в себя любое внутреннее или внешнее устройство или компонент для соединения с электронной системой, такое как устройство ввода-вывода, контроллер сетевого интерфейса (КСИ) (NIC), расширительная плата, аудио процессор, сетевой процессор, жесткий дисковод, запоминающее устройство, CD/DVD ROM, монитор, принтер, мышь, клавиатура, маршрутизатор, портативное запоминающее устройство, устройство сверхбыстродействующей передачи, устройство универсальной последовательной шины (УПШ) (USB), сканер и другие устройства ввода-вывода. Часто на профессиональном жаргоне РВПКЭ такое устройство называется оконечным устройством. Хотя это не показано конкретно, устройство 225 может включать в себя мост от РВПКЭ к РВПК/РВПК-Х для поддержки устаревшей или другой версии устройств РВПК. Оконечные устройства в РВПКЭ часто классифицируются как устаревшие, РВПКЭ или корневые комплексные интегрированные оконечные устройства.

Графический акселератор 230 также связан с концентратором 215 контроллера посредством последовательной линии 232 связи. В одном варианте осуществления графический акселератор 230 соединен с ККП, который соединен с ККМ. Коммутатор 220 и, соответственно, устройство 225 ввода-вывода соединены далее с ККМ. Модули 231 и 218 ввода-вывода также предназначены для воплощения стека многоуровневого протокола для осуществления связи между графическим акселератором 230 и концентратором 215 контроллера. Аналогично обсуждавшемуся выше ККП графический контроллер или графический акселератор 235 может быть сам интегрирован с процессором 205.

На фиг. 3 проиллюстрирован вариант осуществления стека многоуровневого протокола. Стек 300 многоуровневого протокола включает в себя любой вид стека многоуровневой связи, такой как стек быстрого соединения трасс (БСТ) (QPI), стек РВПКЭ, стек межсоединений высокопроизводительных вычислений следующего поколения или другой многоуровневый стек. Хотя непосредственно нижеследующее обсуждение со ссылками на фиг. 2-5 относится к стеку РВПКЭ, те же самые идеи могут быть применены и к иным стекам межсоединений. В одном варианте осуществления стек 300 протокола представляет собой стек протокола РВПКЭ, включающий в себя уровень 305 транзакций, уровень 310 линий связи и физический уровень 320. Интерфейс, такой как интерфейсы 317, 318, 321, 322, 326 и 331 на фиг. 3, могут быть представлены как стек 300 протокола связи. Представление в качестве стека протокола связи может также относиться к модулю или интерфейсу, воплощающему/включающему стек протокола.

РВПК Экспресс использует пакеты для передачи информации между компонентами. Пакеты формируются в уровне 305 транзакций и уровне 310 линий данных для переноса информации от передающего компонента к приемному компоненту. По мере того, как переданные пакеты проходят через другие уровни, они расширяются дополнительной информацией, необходимой для обработки пакетов в этих уровнях. На приемной стороне происходит обратный процесс, и пакеты преобразуются из их представления в физическом уровне 320 в представление в уровне 310 линий данных и, наконец (для пакетов уровня транзакций), в форму, которую можно обрабатывать уровнем 305 транзакций приемного устройства.

Уровень транзакций

В одном варианте осуществления уровень 305 транзакций служит для обеспечения интерфейса между ядром обработки устройства и архитектурой межсоединений, такими как уровень 310 линий данных и физический уровень 320. В этом отношении первичная обязанность уровня 305 транзакций состоит в ассемблировании и дезассемблировании пакетов (т.е. пакетов уровня транзакций, или ПУТ (TLP)). Уровень 305 транзакций, как правило, руководит управлением перемещения на основе кредита для ПУТ. РВПКЭ воплощает разделение транзакций, т.е. транзакций с запросом и откликом, разделенных по времени, разрешая линии связи переносить другой трафик, пока целевое устройство собирает данные для отклика.

В дополнение к этому, РВПКЭ использует управление перемещением на основе кредита. В этой схеме устройство сообщает исходное значение кредита для каждого из приемных буферов в уровне 305 транзакций. Внешнее устройство на противоположном конце линии связи, такое как концентратор 115 контроллера по фиг. 1, подсчитывает число кредитов, потребленных каждым ПУТ. Транзакция может быть передана, если эта транзакция не превышает предел кредита. При приеме отклика значение кредита восстанавливается. Преимущество кредитной схемы заключается в том, что запаздывание возврата кредита не влияет на производительность при том условии, что предел кредита не достигается.

В одном варианте осуществления четыре пространства адресов транзакций включают в себя пространство адресов конфигурации, пространство адресов памяти, пространство адресов ввода-вывода и пространство адресов сообщений. Транзакции пространства памяти включают в себя один или несколько запросов чтения и запросов записи для переноса данных в отображаемое в памяти местоположение или из него. В одном варианте осуществления транзакции пространства памяти способны использовать два различных формата адресов, к примеру, формат короткого адреса, такого как 32-разрядный адрес, или формат длинного адреса, такого как 64-разрядный адрес. Транзакции пространства конфигурации используются для обращения к пространству конфигурации устройств РВПКЭ. Транзакции пространства конфигурации включают в себя запросы чтения и запросы записи. Транзакции пространства сообщений (или просто сообщения) определяются для поддержки связи через сеть между агентами РВПКЭ.

Поэтому в одном варианте осуществления уровень 305 транзакций ассемблирует заголовок / полезную информацию 306 пакета. Формат для заголовков / полезных данных текущего пакета можно найти в спецификации РВПКЭ на сайте спецификаций РВПКЭ.

На фиг. 4 показан вариант осуществления описателя транзакции РВПКЭ. В одном варианте осуществления описатель 400 транзакций представляет собой механизм для переноса информации транзакций. В этом отношении описатель 400 транзакций поддерживает идентификацию транзакций в системе. Прочие потенциальные использования включают в себя прослеживание модификаций в упорядочении транзакций по умолчанию и ассоциирование транзакции с каналами.

Описатель 400 транзакций включает в себя поле 402 глобального идентификатора, поле 404 атрибутов и поле 406 канального идентификатора. В проиллюстрированном примере поле 402 глобального идентификатора показано содержащим поле 408 местного идентификатора транзакции и поле 410 идентификатора ресурса. В одном варианте осуществления глобальный идентификатор 402 транзакции является единственным для всех ожидающих выполнения запросов.

Согласно одной реализации, поле 408 местного идентификатора транзакции представляет собой поле, генерируемое запрашивающим агентом, и оно является единственным для всех ожидающих выполнения запросов, которые требуют завершения для этого запрашивающего агента. Далее, в данном примере идентификатор 410 ресурса однозначно идентифицирует запрашивающий агент в иерархии РВПКЭ. Соответственно, вместе с идентификатором 410 ресурса поле 408 местного идентификатора транзакции обеспечивает глобальную идентификацию транзакции в сфере иерархии.

Поле 404 атрибутов конкретизирует характеристики и соотношения транзакции. В этом отношении поле 404 атрибутов потенциально используется для обеспечения дополнительной информации, которая позволяет модифицировать обработку транзакции по умолчанию. В одном варианте осуществления поле 404 атрибутов включает в себя поле 412 приоритета, резервное поле 414, поле 416 упорядочения и поле 418 отсутствия любопытства. Здесь подполе 412 приоритета может быть модифицировано задатчиком для назначения приоритета транзакции. Резервное поле 404 атрибутов оставлено резервным на будущее или для определяемого поставщиком использования. С помощью этого резервного поля атрибутов могут быть реализованы модели возможного использования, использующие атрибуты приоритета или безопасности.

В данном примере поле 416 атрибутов упорядочения используется для выдачи опциональной информации, сообщающей тип упорядочения, который может модифицировать правила упорядочения по умолчанию. Согласно одному примерному воплощению атрибут упорядочения «О» обозначает, что применяются правила упорядочения по умолчанию, при этом атрибут упорядочения «1» обозначает нестрогое упорядочение, когда записи могут пропускать записи в том же направлении, а завершения считывания могут пропускать записи в том же направлении. Поле 418 атрибутов любопытства используется для определения того, подвержены ли транзакции подглядыванию. Как показано, поле 406 канального идентификатора идентифицирует канал, с которым связана транзакция.

Уровень линий связи (см. фиг. 3)

Уровень 310 линий связи, также именуемый уровнем 310 линий данных, действует как промежуточная ступень между уровнем 305 транзакций и физическим уровнем 320. В одном варианте осуществления ответственность уровня 310 линий данных состоит в обеспечении надежного механизма по обмену пакетов уровня транзакций (ПУТ) между двумя компонентами линии связи. Одна сторона уровня 310 линии данных принимает ПУТ, ассемблированные уровнем 305 транзакций, вводит идентификатор 311 последовательности пакетов, т.е. идентификационный номер или номер пакета, вычисляет и вводит код обнаружения ошибок, т.е. циклический контроль избыточности (ЦКИ) (CRC) 312, и предоставляет модифицированные ПУТ физическому уровню 320 для передачи по физической среде к внешнему устройству.

Физический уровень

В одном варианте осуществления физический уровень 320 включает в себя логический подблок 321 и электрический подблок 322 для физической передачи пакета к внешнему устройству. Здесь логический подблок 321 отвечает за «цифровые» функции физического уровня 320. В этом отношении логический подблок включает в себя секцию передачи для подготовки ожидающей передачи информации для передачи физическим подблоком 322, секцию приема для идентификации и подготовки принятой информации перед пропусканием ее к уровню 310 линий связи.

Физический блок 322 включает в себя передатчик и приемник. В передатчик логическим подблоком 321 подаются символы, которые передатчик выстраивает в последовательность и передает на внешнее устройство. Приемник получает из внешнего устройства символы и преобразует принятые сигналы в битовый поток. Этот битовый поток преобразуется из последовательной формы и подается в логический подблок 321. В одном варианте осуществления применяется код 8b/10b передачи, когда передаются или принимаются десятиразрядные символы. Здесь используются специальные символы для обрамления пакета рамками 323. Помимо этого в одном примере приемник также обеспечивает символьную синхронизацию, восстанавливаемую из поступающего последовательного потока.

Как сказано выше, хотя уровень 305 транзакций, уровень 310 линий связи и физический уровень 320 обсуждаются со ссылкой на конкретный вариант осуществления стека протокола РВПКЭ, стек многоуровневого протокола не ограничен этим. На деле может включаться/ воплощаться любой многоуровневый протокол. В качестве примера, порт/интерфейс, который представлен как многоуровневый протокол, включает в себя: первый уровень для ассемблирования пакетов, т.е. уровень передачи; второй уровень для выстраивания пакетов в последовательность, т.е. уровень линий связи; и третий уровень для передачи пакетов, т.е. физический уровень. В качестве конкретного примера используется многоуровневый протокол единого стандартного интерфейса (ЕСИ) (CSI).

По мере возрастания частоты последовательных линий связи и смещения микросхем к новым технологиям обработки при постоянно уменьшающихся размерах устройств становится все более важным обеспечить способность динамического регулирования установок коррекции передатчика и приемника для учета вариантов платформ и полупроводников.

Третье поколение РВПКЭ является примером промышленного стандарта, который служил для такой коррекции на основе пары передатчик-приемник, чтобы гарантировать возможность совместной работы при 8 Гп/с для широкого спектра систем, которые применяют РВПКЭ. Однако большое разнообразие устройств, изготовленных разными поставщиками с применением разных технологий обработки, имеющих каждое с собственной конструкцией передатчика/приемника и собственными алгоритмами программного обеспечения для применения создают проблему для проектирования компонентов с гарантированной возможностью взаимодействия.

Настоящее изобретение может применяться для восходящего порта, нисходящего порта или обоих. В некоторых вариантах осуществления процедура обучения и коррекции линии связи включает в себя два прохода, как будет подробно описано ниже.

На фиг. 5 показан вариант осуществления последовательного двухточечного оптоволокна 500 РВПКЭ. Хотя проиллюстрирован вариант осуществления последовательной двухточечной линии связи РВПКЭ, последовательная двухточечная линия связи этим не ограничивается, т.к. она включает в себя любой тракт передачи для передачи последовательных данных. В показанном варианте осуществления базисная линия РВПКЭ включает в себя две пары низковольтных дифференциально управляемых сигналов: передаваемую пару 501/504 и приемную пару 502/503.

Соответственно, устройство 550 включает в себя логику 501 передачи для передачи данных к устройству 510 и приемную логику 507 для приема данных от устройства 560. Иными словами по отношению к устройству 550, в линию связи РВПКЭ включены два передающих тракта, т.е. тракты 505 и 525, и два приемных тракта, т.е. тракты 506 и 526.

Передающим трактом можно назвать любой тракт для передачи данных, такой как линия передачи, проводная («медная») линия, оптическая линия, беспроводный канал связи, инфракрасная линия связи или другой тракт связи. Соединение между двумя устройствами, такими как устройство 550 и устройство 560, называется линией связи, такой как линия 530 связи. В некоторых вариантах осуществления линия 530 связи представляет собой линию связи шинного интерфейса РВПКЭ.

Линия связи может поддерживать множество полос, причем каждая полоса представляет набор пар дифференциальных сигналов (одна пара для передачи, одна пара для приема). Чтобы масштабировать ширину полосы пропускания, линия связи может объединять множество полос, обозначенных xN, где N есть любая поддерживаемая ширина линии связи, такая как 1, 2, 4, 8, 12, 16, 32, 64 или шире. В некоторых вариантах осуществления полосой может именоваться канал линии связи (к примеру, линия 530 связи). Кроме того, на условной схеме по фиг. 5 только одна полоса (пары 505/525 и 506/526) показана в последовательном двухточечном оптоволокне 500 РВПКЭ.

Линия 530 связи РВПКЭ может давать возможность устройствам 550, 560 осуществлять связь друг с другом. В некоторых вариантах осуществления настоящего изобретения устройство 560 является местным устройством, тогда как устройство 550 может быть удаленным устройством. Далее, либо устройство 550, либо устройство 560 могут быть охарактеризованы как корневое комплексное устройство или оконечное устройство. Например, в некоторых вариантах осуществления устройство 560 является корневым комплексным устройством, а устройство 550 является оконечным устройством. В частности, поскольку устройство 550 и устройство 560 могут осуществлять связь друг с другом по линии 530 связи, устройство 550 и устройство 560 могут именоваться «партнерами по линии связи» друг для друга.

Дифференциальная пара может относиться к двум трактам передачи, таким как линии 505 и 525 связи, для передачи дифференциальных сигналов. В качестве примера, когда линия 505 связи переключается с низковольтного уровня на высоковольтный уровень, т.е. на нарастающем фронте, линия 525 связи управляется с высокого логического уровня на низкий логический уровень (т.е. на падающем фронте). Дифференциальные сигналы потенциально демонстрируют лучшие электрические характеристики, такие как лучшая целостность сигнала, т.е. перекрестное соединение, положительный/отрицательный выброс напряжения, вызов и т.п. Это обеспечивает лучшее временное окно, что обеспечивает более быстрые частоты передачи.

Помимо этого, передающая или приемная составляющая (к примеру, логика 501/504 передачи, логика 502/503 приема) устройства (к примеру, устройства 550 или устройства 560) может иметь установки передатчика или приемника, соответственно, которые можно устанавливать, регулировать, оптимизировать и т.п. В некоторых вариантах осуществления для установок передатчика или приемника может применяться набор коэффициентов с целью достичь способности связи между устройствами 550, 560 с минимальными потерями данных.

Например, частота ошибочных битов (ЧОБ), которая может определять пороговую частоту ошибок для данных, передаваемых от одного устройства к другому, для любой конкретной полосы или линии связи. Например, ЧОБ для заданной линии связи может быть от 10-4 до 10-12 в зависимости от порога, определенного процедурой обучения и коррекции линии связи в конкретном протоколе связи. В показанном на фиг. 5 варианте осуществления ЧОБ для полосы в линии 530 связи составляет 10-12.

Специалист может оценить, что частота ошибочных битов (ЧОБ) может быть определена как отношение числа битов, принятых неправильно (ошибок), и общего числа принятых битов, согласно некоторым вариантам осуществления настоящего изобретения.

В некоторых вариантах осуществления набор коэффициентов может генерироваться в удаленном модуле 520 алгоритма коэффициентов из данных коэффициентов, хранящихся в таблице 515 регистра коэффициентов. Когда коэффициенты извлечены, они могут переноситься в логику 501/504 передачи и логику 502/503 приема (к примеру, тракты 507, 508 на чертеже). Альтернативно, к логике 506, 507 передачи и приема может быть применен набор коэффициентов по умолчанию, расположенный в регистрах компонентов передатчика или приемника (к примеру, предоставленных производителем) устройств 550, 560. Кроме того, набор коэффициентов может передаваться в каждое устройство 550, 560 посредством символов (символы TS1/TS2) для каждого партнера по линии связи во время определенных протоколом состояний конечного автомата обучения линии связи и состояний (КАОЛС) (LTSSM) согласно варианту осуществления, который применяет РВПКЭ.

В некоторых вариантах осуществления генерируемые коэффициенты могут подаваться в фильтр с конечной импульсной характеристикой (КИХ) (FIR) для определения того, оптимально ли выполнена логика 501/504 передачи или логика 502/503 приема согласно заранее заданным условиям.

Преимущественно, адаптивный фильтр КИХ может быть использован в процедуре обучения и коррекции линии связи, чтобы идентифицировать коэффициенты во время прогона согласно конкретным атрибутам физического канала (к примеру, полосы или линии связи). В некоторых вариантах осуществления произведение генерируемых коэффициентов и набора, если он принят, принятых импульсов добавляются вместе, чтобы создать фильтр. Особо примечательно, что в некоторых вариантах осуществления настоящего изобретения новый набор коэффициентов генерируется и пропускается через логику 501/504 передачи или логику 502/503 приема, соответственно, пока не достигается целевая ЧОБ. Например, если целевая ЧОБ равна 10-12, измеряется частота ошибок передаваемых данных (к примеру, глазковая диаграмма 510 ЧОБ), результаты чего посылаются в удаленный модуль 520 алгоритма генерирования коэффициентов (к примеру, тракт 511), и генерируются новые коэффициенты, если не достигается целевая ЧОБ. Когда же целевая ЧОБ достигнута, новые коэффициенты не генерируются и не применяются к логике 502/503 передачи и приема.

Настоящее изобретение обеспечивает механизм для снижения времени на обучение и коррекцию линии связи и увеличивает его надежность. В некоторых вариантах осуществления процедура обучения и коррекции линии связи, соответствующая настоящему изобретению, может использовать программное приложение, которое исполняет алгоритм для генерирования набора коэффициентов, подлежащих применению к установкам логики передачи или логики приема.

В некоторых вариантах осуществления это программное приложение считывает значение полного отклонения (FS) и значение низкой частоты (LF), связанные с устройством, соединенным с линией связи шинного интерфейса (к примеру, корневое комплексное устройство или оконечное устройство), из запоминающего блока или элемента (к примеру, регистра конфигурации и состояния) и вводит эти значения в алгоритм для генерирования набора коэффициентов, подлежащего применению к установкам передатчика и приемника в устройстве, соединенном с линией связи шинного интерфейса.

В некоторых вариантах осуществления это программное приложение генерирует коэффициенты, подлежащие применению к компоненту передачи оконечного устройства так, что корневое комплексное устройство может соответствовать целевой ЧОБ во время этапа 2 или 3 в процедуре обучения и коррекции линии связи РВПКЭ.

Однако в других вариантах осуществления логика, присутствующая в полосах восходящего порта или нисходящего порта, может использоваться для генерирования набора коэффициентов из значения полного отклонения и значения низкой частоты, как будет подробнее описано ниже.

Обучение и коррекция линии связи может выполняться либо в логике 501/504 передачи, либо в логике 502/503 приема. Специалист может оценить, что поскольку принятый сигнал может быть смешан с канальным шумом, процедура(-ы) обучения и коррекции линии связи может(могут) добавлять шум и ухудшать отношение сигнал/шум (С/Ш) (SNR), связанное с заданной полосой, которая, как правило, не характеризуется логикой 502/503 приема. Поэтому в некоторых вариантах осуществления обучение и коррекция линии связи может быть эффективным на передающей стороне (к примеру, логика 501/504 передачи).

Двигаясь по чертежам, фиг. 6 является условной диаграммой, иллюстрирующей глазковую диаграмму частоты ошибочных битов (ЧОБ) (BER) с наилучшими предустановками и оптимизированными коэффициентами передачи. Специалист может оценить, что глазковая диаграмма ЧОБ является интуитивным графическим представлением электрических и оптических сигналов связи. По существу, качество сигналов, переданных и принятых в канале связи, может оцениваться из внешнего вида глазковой диаграммы ЧОБ. Глазковые диаграммы ЧОБ могут помочь определить, может ли система связи правильно передавать разряды данных с минимальным количеством ошибок.

Фиг. 6 показывает диаграмму, иллюстрирующую график 601 глазкового раскрыва 602 частоты ошибочных битов (ЧОБ) с наилучшими заранее установленными коэффициентами и график 603 глазкового раскрыва 604 ЧОБ с оптимизированными коэффициентами передатчика и приемника. Как показано, высота глазкового раскрыва 602 ЧОБ на графике 601 меньше, чем высота глазкового раскрыва 604 ЧОБ на графике 603. Специалист может оценить, что высота глазкового раскрыва определяет шумовую границу системы. В некоторых вариантах осуществления более высокий глазковый раскрыв ЧОБ указывает на меньший шум в канале связи, чем канальный шум, относящийся к меньшему глазковому раскрыву ЧОБ.

Поэтому, согласно некоторым вариантам осуществления настоящего изобретения, глазковый раскрыв 604 ЧОБ на графике 603 указывает на меньший шум и более низкую частоту ошибочных битов в канале связи вследствие оптимизированных установок передатчика и приемника. Альтернативно, глазковый раскрыв 602 ЧОБ на графике 601 указывает на больший шум и более высокую частоту ошибочных битов в канале связи с наилучшими заранее установленными коэффициентами.

Соответственно, более низкая частота ошибочных битов может достигаться в канале линии связи (к примеру, полоса линии связи шинного интерфейса), когда к компоненту передатчика или приемника (к примеру, к логике передачи или логике приема) применен оптимизированный набор коэффициентов. По существу, оптимизированные коэффициенты передатчика или приемника учитывают физические характеристики конкретного канала в линии связи. Система и способ, соответствующие настоящему изобретению, включают в себя идентификацию оптимальных коэффициентов передатчика или приемника для снижения частоты ошибочных битов, чтобы увеличить скорость передачи данных в системах связи.

Фиг. 7 является условной схемой 700, иллюстрирующей вариант осуществления этапа 0 в процедуре обучения и коррекции линии связи РВПКЭ. Как показано, два компонента, корневое комплексное устройство 701 и оконечное устройство 703, соединены друг с другом по дифференциальным парам 705а/705b (показанным как стрелки) в линии связи.

Далее, корневое комплексное устройство 701 и оконечное устройство 703 включают в себя логику передачи (702а, 704b, соответственно) и логику приема (704а, 702b, соответственно), чтобы обеспечить связь между этими двумя устройствами 701, 703. В некоторых вариантах осуществления корневое комплексное устройство 701 и оконечное устройство 703 могут характеризоваться, соответственно, как нисходящий порт и восходящий порт.

В некоторых вариантах осуществления этап 0 (к примеру, процедура обучения и коррекции линии связи) может включать в себя передачу первого набора данных (к примеру, наборы упорядоченных TS1, заранее заданные значения, рекомендации и т.п.) из восходящего порта (к примеру, оконечного устройства 703) в нисходящий порт (к примеру, корневое комплексное устройство 701).

Данные могут переноситься между этими устройствами 701, 703 с первой скоростью передачи данных. Например, первая скорость передачи данных может быть меньше или равна первой максимальной скорости передачи данных, связанной с корневым комплексным устройством 701, и второй максимальной скорости передачи данных, связанной с оконечным устройством 703.

В некоторых вариантах осуществления настоящего изобретения первая скорость передачи данных является приблизительно максимальной скоростью передачи данных, связанной с РВПКЭ первого или второго поколения. В некоторых вариантах осуществления максимальная скорость передачи данных, связанная с РВПКЭ первого или второго поколения, может составлять приблизительно 5 Гигапереносов в секунду (5 Гп/с).

Помимо этого, во время этапа 0 оба устройства 701, 703 могут сообщать максимальную скорость передачи данных, связанную с каждым устройством 701, 703.

Далее, в некоторых вариантах осуществления оба устройства 701, 703 делают линию связи достаточно работоспособной в РВПК Экспресс первого или второго поколения при некоторой ЧОБ. Например, перед переходом к следующему этапу в процедуре обучения и коррекции линии связи оба устройства 701, 703 должны показать, что они могут передавать сигналы с минимальной ЧОБ 10-4. В некоторых вариантах осуществления, если целевая ЧОБ не достигается, линия связи может работать при более низкой скорости передачи данных.

Фиг. 8 является условной схемой, иллюстрирующей вариант осуществления первого этапа процедуры обучения и коррекции линии связи РВПКЭ. Как показано, корневое комплексное устройство 801 и оконечное устройство 803 (имеющие логику 802а, 804b передачи и логику 802b, 804а приема) перешли к этапу 1 процедуры обучения и коррекции линии связи РВПКЭ.

На этапе 1 процедуры обучения и коррекции линии связи РВПКЭ оба устройства 801, 803 делают каждую полосу в линии связи работоспособной при второй скорости передачи данных для обмена вторым набором данных (к примеру, наборы упорядоченных TS2). В некоторых вариантах осуществления вторая скорость передачи данных больше первой скорости передачи данных. Например, вторая скорость передачи данных может составлять приблизительно 8 Гп/с. Помимо этого, во время этапа 1 между двумя устройствами 801, 803 могут обмениваться наборы упорядоченных TS1.

Особенно примечательно, что во время этапа 1 оба устройства 801, 803 сообщают свои значения полного отклонения (FS) и низкой частоты (LF). В некоторых вариантах осуществления значение полного отклонения может быть определено как максимальное дифференциальное напряжение, которое генерируется передающим компонентом.

Помимо этого, сумма коэффициентов передатчика и приемника должна быть равна FS согласно некоторым вариантам осуществления настоящего изобретения:

FS=|C-1|-|C-1|+|C+1|.

Далее, значение LF может быть определено как минимальное дифференциальное напряжение, которое генерируется передающим компонентом, согласно некоторым вариантам осуществления настоящего изобретения. Значения LF должны всегда быть больше, чем минимальное дифференциальное напряжение:

C0-|C-1|+|C+1|≥LF.

Значения FS и LF могут храниться в соответственных полях TS1 и сообщаться путем обмена наборами упорядоченных TS1. Как будет описано ниже, значения FS и LF могут использоваться при вычислении коэффициентов, которые можно применять к установкам передатчика или приемника каждого устройства 801, 803.

В некоторых вариантах осуществления, когда приняты значения FS и LF, они сохраняются в запоминающем блоке в каждом устройстве 801, 803. Например, значения FS и LF сохраняются в регистре(-ах) конфигурации и состояния. В некоторых вариантах осуществления эти регистры конфигурации и состояния могут быть реализованы как элементы триггерных устройств.

После сохранения настоящее изобретение обеспечивает механизм для вычисления набора коэффициентов (к примеру, C0, C-1, C+1) из значений FS и LF, которые также могут сохраняться в регистре(-ах) конфигурации и состояния. В некоторых вариантах осуществления вычисленный набор коэффициентов включает в себя исходный компонент, текущий компонент и конечный компонент.

В каждом устройстве 801, 803 могут быть многочисленные регистры конфигурации и состояния. Каждый регистр конфигурации и состояния может иметь емкость в десятки битов. В целом, регистры конфигурации и состояния могут иметь емкость в сотни и тысячи битов данных.

В некоторых вариантах осуществления в портах (к примеру, в полосах) каждого устройства 801, 803 может присутствовать логика, которая может определять (к примеру, вычислять) набор коэффициентов со значениями FS и LF в качестве входов. Особо отметим, что в некоторых вариантах осуществления настоящего изобретения вычисленный набор коэффициентов представляет собой координаты средней точки на линии максимального усиления.

Фиг. 9 является условной схемой, иллюстрирующей таблицу 900, перечисляющую набор исходных и конечных коэффициентов, которые могут быть применены для установки передатчика или приемника. Как показано, ось х индицирует конечные значения, тогда как ось у индицирует исходные значения. Особо примечательно, что диагональная линия определяет линию 901 максимального усиления. Максимальное усиление может быть определено как главное усиление, которое появляется, когда имеется инверсия полярности для единственного битового интервала.

Максимальное усиление можно вычислить согласно следующему уравнению:

Максимальное усиление = 20 log10 vd/vb.

Специалисту следует понимать, что максимальное усиление или линия максимального усиления не являются постоянными. По существу, если линия изменяется вследствие обнуления, горячего разъединения / соединения, значение максимального усиления или линия максимального усиления могут изменяться.

Далее, таблица 900 содержит множество клеток 903. В некоторых вариантах осуществления каждая клетка 903 представляет коэффициент. Помимо этого, числа в клетках представляют заранее заданные значения, тогда как клетки 902 за линией 901 максимального усиления являются запрещенным пространством коэффициентов.

Невозможно использовать постоянную заранее заданную установку обучения и коррекции линии связи передатчика или приемника вследствие того, что линии связи нужно устанавливать с устройствами переменных характеристик. По существу установки коэффициентов обучения и коррекции линии связи передатчика и приемника нужно динамически согласовывать.

Как описано выше, удаленный приемник используется для определения того, достигается ли целевая ЧОБ, как указано высокой глазкового раскрыва ЧОБ. Соответственно, процедура обучения и коррекции линии связи может занять множество циклов для достижения оптимальных установок коэффициентов.

Например, процедура обучения и коррекции линии связи применяет конкретную предустановку, соответствующую коэффициенту 3/5, к установкам передатчика или приемника. Если целевая ЧОБ не достигается, как указано высотой генерируемого глазкового раскрыва ЧОБ, могут генерироваться новые коэффициенты для нахождения установок передатчика и приемника, которые соответствуют целевой ЧОБ.

Например, может быть выявлено, что приемник оконечного устройства требует меньший конечный, но больший исходный коэффициенты. По существу, оконечное устройство может посылать коэффициент (4/4) к удаленному комплексному устройству. В свою очередь, удаленное комплексное устройство применяет новый коэффициент (4/4) к установкам передатчика и эхо (4/4) к оконечному устройству.

Когда оконечное устройство принимает сигнал от удаленного комплексного устройства, этот сигнал оценивается приемником оконечного устройства. Эта оценка может определить, например, что конечное значение достаточно, но требуется большее исходное значение. Процесс может продолжаться до тех пор, пока не будет найдены оптимальные значения коэффициентов.

Фиг. 10 является условной схемой, иллюстрирующей вариант осуществления второго этапа процедуры обучения и коррекции линии связи РВПКЭ. Как показано, корневое комплексное устройство 1001 и оконечное устройство 1003 (имеющие логику 1002а, 1004b передачи и логику 1002b, 1004а приема) перешли к этапу 2 процедуры обучения и коррекции линии связи РВПКЭ.

На этапе 2 восходящий порт (к примеру, оконечное устройство) помогает нисходящему порту (к примеру, корневое комплексное устройство) тонко настроить свои установки передачи, чтобы ЧОБ была меньше или равна 10-12 на всех каналах (к примеру, полосах) линии связи. Примерный перечень коэффициентов (5/5, 6/5, 7/4) указывает, что может быть выполнено множество итераций для достижения оптимальных установок обучения и коррекции передатчика (или приемника).

Фиг. 11 является условной схемой, иллюстрирующей вариант осуществления третьего этапа процедуры обучения и коррекции линии связи РВПКЭ. Как показано, корневое комплексное устройство 1101 и оконечное устройство 1103 (имеющие логику 1102а, 1104b передачи и логику 1102b, 1104а приема) перешли к этапу 3 процедуры обучения и коррекции линии связи РВПКЭ. Особенно примечательно то, что система и способ, согласующиеся с настоящим изобретением, могут применять этап 3 процесса обучения и коррекции линии связи только в единственной итерации.

В некоторых вариантах осуществления логика в нисходящем порте (к примеру, корневом комплексном устройстве) использует значения FS и LF, связанные с восходящим портом, для вычисления набора коэффициентов, который можно применять к компоненту передатчика в восходящем порте. В некоторых вариантах осуществления вычисленный набор коэффициентов может представлять собой координаты средней точки на линии максимального усиления.

В некоторых вариантах осуществления средняя точка на линии усиления может быть вычислена согласно следующему описанному ниже алгоритму:

Случай А

Если FS+LF четное и делящееся на 4, C-1=C+1 = абсолютное значение [(FS-LF)/4] и C0=FS-C-1+C+1.

Например, если FS=40 и LF=20, то C-1 и C+1=5 и C0=30. Таким образом, средняя точка на линии максимального усиления и вычисленные коэффициенты равны {5, 30, 5}.

Случай В

Если FS+LF четное, но не делящееся на 4, C-1=Ceil[(FS-LF)/4], C+1=Floor[(FS-LF)/4] и C0=FS-C-1-C+1.

Например, если FS=42 и LF=20, то C-1=6, C+1=5 и C0=31. Таким образом, средняя точка на линии максимального усиления и вычисленные коэффициенты равны {6, 31, 5}.

Случай С

Если FS+LF нечетное, a (FS-LF-1=VAL) делится на 4, C-1=C+1=Floor [VAL/4] и C0=FS-C-1-C+1.

Например, если FS=41 и LF=20, то C-1=C+1=5 и C0=31. Таким образом, средняя точка на линии максимального усиления и вычисленные коэффициенты равны {5, 31, 5}.

Случай D

Если FS+LF нечетное, a (FS-LF-1=VAL) не делится на 4, C-1=Ceil [VAL/4], C+1=Floor [VAL/4] и C0=FS-C-1-C+1.

Например, если FS=42 и LF=23, то C-1=5, C+1=4 и C0=33. Таким образом, средняя точка на линии максимального усиления и вычисленные коэффициенты равны {5, 33, 4}.

Помимо этого, генерируемые коэффициенты могут применяться к заранее заданным или заранее вычисленным начальным номерам. Например, во время конечного лабораторного тестирования полупроводников устройство может характеризоваться так, что начальные номера вычисляются для полосы в случае, когда устройство выполняет меньше, чем идеальное. По существу, генерируемые коэффициенты могут применяться не непосредственно, однако могут применяться с учетом этих заранее заданных или заранее вычисленных начальных номеров.

Следует также понимать, что определение коэффициентов, связанных с координатами средней точки на линии максимального усиления может быть начальной точкой и что тонкая настройка может выполняться для увеличения скорости связи по каждой полосе и линии связи. По существу, настоящее изобретение обеспечивает гибкость, чтобы выйти за координаты средней точки, начиная с точки к любой другой точке на любой линии усиления (с некоторым пределом ошибки).

Например, когда вычислены начальные коэффициенты (к примеру, координаты средней точки на линии максимального усиления), новый набор коэффициентов может быть вычислен путем добавления заранее заданной постоянной или набора заранее заданных постоянных к вычисленному набору коэффициентов, который представляет координаты средней точки на линии максимального усиления, согласно некоторым вариантам осуществления настоящего изобретения.

Например, «1» может быть заранее заданной постоянной, которая может применяться для генерирования нового набора коэффициентов для тонкой настройки. Например, если вычислен набор коэффициентов (3, 4, 5), то применение заранее заданной постоянной «1» должно дать новый набор коэффициентов (4, 6, 5), которые могут быть применены к установкам передатчика или приемника в устройстве, соединенном с линией связи. Если, например, набор заранее заданных постоянных равен (1, 0, 0), то новый набор вычисленных коэффициентов должен быть (4, 5, 4).

Помимо этого, для тонкой регулировки можно применять алгоритм минимальной среднеквадратической ошибки (MCKO) (LMS). В некоторых вариантах осуществления настоящего изобретения каждая полоса восходящего порта или нисходящего порта может быть способна выполнять алгоритм МСКО, заранее установленный в ней.

Специалист оценит, что для вычисления нового(-ых) набора(-ов) коэффициентов можно применять различные постоянные и (или) набор заранее заданных постоянных. Кроме того, уникальный набор заранее заданных постоянных или набор коэффициентов можно применять в любом порядке или итерации для генерирования нового(-ых) набора(-ов) коэффициентов при тонкой настройке скорости связи в полосе или линии связи.

Соответственно, новый(-е) набор(ы) коэффициентов может генерироваться из нижеследующих уравнений:

1) Cm[5:0]=Cm1[5:0]+(csr_add_precursor_wire[2:0] - csr_sub_precursor_wire [2:0])

2) Ср[5:0]=Cp1[5:0]+(csr_add_postcursor_wire[2:0] - csr_sub_postcursor_wire [2:0])

3) C0=FS-Cm-Ср.

В некоторых вариантах осуществления регистр(ы) конфигурации и состояния являются регистрами конфигурации 3 бита на пучок или на полосу, которые используются, чтобы добавлять или вычитать исходное вычисленное значение для отклонения в желательное местоположение.

Кроме того, варианты осуществления настоящего изобретения дополнительно определяют порог FS регистра (FS_threshold) конфигурации. Например, в случае, когда значение FS партнеров по линии связи, которое подбирается во время этапа 1 в процедуре обучения и коррекции линии связи, больше порога FS, используются приведенные выше уравнения 1, 2 и 3. однако в случае, когда значение FS меньше порога FS, то значения csr_add и csr_sub регистров конфигурации делятся на 2 для исходного и конечного значений, чтобы обеспечить больше гибкости.

В некоторых вариантах осуществления система и способ, соответствующие настоящему изобретению, могут использовать этап 3 процедуры обучения и коррекции линии связи с единственной итерацией, так что нисходящий порт корневого комплексного устройства становится более эффективным.

Следует понимать, что настоящее изобретение можно адаптировать так, что этап 2 в процедуре обучения и коррекции линии связи сможет применять описанный здесь способ, чтобы генерировать коэффициенты для нисходящего порта во время этапа 2 этой процедуры. Соответственно, настоящее изобретение не ограничивается этапом 3 в процедуре обучения и коррекции линии связи и может использоваться для генерирования коэффициентов для передатчика или приемника, установленных для удаленного устройства, местного устройства, удаленного комплексного устройства или оконечного устройства. Кроме того, настоящее изобретение при необходимости может отвечать за тонкую настройку.

Способ 1200 обучения и коррекции линии связи, который соответствует некоторым вариантам осуществления настоящего изобретения, показан на фиг. 12. В некоторых вариантах осуществления способ 1200 начинается с передачи первого набора данных к первому компоненту от партнерского по линии связи связи компонента через по меньшей мере один канал линии связи согласно блоку 1201.

Этот первый набор данных может включать в себя упорядоченный(-е) набор(-ы), заранее заданную(-ые) величину(-ы), подсказку(-ки), значения FS и LF и т.п.Соответственно, первый компонент может быть охарактеризован как корневое комплексное или оконечное устройство и может включать в себя восходящий порт или нисходящий порт.

Затем, согласно блоку 1202 вычисляется первый набор коэффициентов из значений FS и LF. Этот первый набор коэффициентов может вычисляться согласно описанному выше алгоритму. В некоторых вариантах осуществления значения FS и LF, полученные от первого партнера по линии связи этого компонента, сохраняются в запоминающих элементах (к примеру, регистрах конфигурации и состояния) в первом компоненте.

В некоторых вариантах осуществления настоящего изобретения на отдельных линиях связи порта используется логика для вычисления первого набора коэффициентов. В некоторых вариантах осуществления эта логика встроена в порт устройства, подвергаемого процедуре обучения и коррекции линии связи (к примеру, корневого комплексного устройства или оконечного устройства).

Затем вычисленный набор коэффициентов сохраняется в запоминающих элементах в первом компоненте (блок 1203). Для некоторых вариантов осуществления вычисленный набор коэффициентов может сохраняться в регистре конфигурации порта.

Со временем первый компонент отправляет вычисленный набор коэффициентов к партнерскому по линии связи компоненту. Затем, вычисленный набор коэффициентов применяется для установки партнерского по линии связи связи передающего компонента (блок 1204).

Помимо этого, согласно некоторым вариантам осуществления настоящего изобретения, от первого компонента могут отсылаться дополнительные данные, если частота ошибочных битов, ассоциированная с линией связи, превышает целевую частоту ошибочных битов.

Фиг. 13 показывает еще один способ 1300 обучения и коррекции линии связи, соответствующий варианту осуществления настоящего изобретения. В некоторых вариантах осуществления способ 1300 начинается с блока 1301: первый компонент с нисходящим портом и партнерский по сети компонент с восходящим портом передают существующие значения передатчика и заранее установленные подсказки приемника для каждой полосы каждому порту на скорости первого поколения / второго поколения.

Затем, как первый компонент, так и партнерский по линии связи компонент делают линию связи достаточно работоспособной на скорости третьего поколения для минимальной ЧОБ 10-4 (блок 1302).

Далее, блок 1303 предусматривает, что первый компонент сохраняет значение полного отклонения и значение низкой частоты, ассоциированные с партнерским по линии связи компонентом. Вслед за этим, первый компонент вычисляет первый набор коэффициентов из значений полного отклонения и низкой частоты, ассоциированных с первым компонентом, и регулирует установки передатчика первого компонента (блок 1304).

В заключение, блок 1305 способа 1300 предусматривает, что первый компонент вычисляет второй набор коэффициентов из значений полного отклонения и низкой частоты, ассоциированных с партнерским по линии связи компонентом и регулирует установки передатчика партнерского по линии связи связи компонента.

Соответственно, способ 1300 описывает порядок того, как единственный компонент, соединенный с шинным интерфейсом, может реализовать настоящее изобретение для этапов 2 и 3 процедуры обучения и коррекции линии связи. По существу, настоящее изобретение отвечает за то, что подключенные к шинному интерфейсу устройства (к примеру, первый компонент и партнерский по линии связи компонент) могут пренебрегать запросом на применение установок, коэффициентов или тому подобного к установкам передающего компонента во время процедуры обучения и коррекции линии связи.

Нижеследующие примеры касаются дальнейших вариантов осуществления. Подробности в.этих примерах могут быть использованы в одном или нескольких вариантах осуществления. Например, все опциональные признаки описанных здесь устройства и системы могут быть реализованы в отношении описанных здесь способа или процесса.

Пример 1: Система может содержать, в ответ на то, что первый компонент и партнерский по линии связи компонент подвергаются коррекции, первый компонент, служащий для передачи первого набора данных партнерскому по линии связи компоненту. Первый компонент может содержать по меньшей мере один приемник для приема первого набора корректирующих данных. Первый компонент может дополнительно содержать память коэффициентов, соединенную с приемником, для хранения корректирующих данных. Помимо этого, может иметь место логика коэффициентов, соединенная с памятью коэффициентов, для генерирования первого набора коэффициентов на основе первого набора данных коррекции. Первый компонент предназначен для отправки первого набора коэффициентов партнерскому по линии связи компоненту.

Пример 2: Первый набор коэффициентов включает в себя координаты средней точки на линии максимального усиления.

Пример 3: Первый компонент может быть также корневым комплексным компонентом, а партнерский по линии связи компонент является оконечным устройством.

Пример 4: Линейный компонент посылает первый набор корректирующих данных первому компоненту по линии связи шинного интерфейса РВПКЭ.

Пример 5: Первый набор корректирующих данных включает в себя значение полного отклонения и значение низкой частоты.

Пример 6: В ответ на то, что первый компонент и партнерский по линии связи компонент подвергаются процедуре коррекции, первый компонент передает партнерскому по линии связи компоненту второй набор данных, причем партнерский по линии связи компонент применяет по меньшей мере часть второго набора данных для установки передатчика партнерского по линии связи связи компонента.

Пример 7: Генерированный первый набор коэффициентов включает в себя исходный компонент, текущий компонент и завершающий компонент.

Пример 8: Способ, содержащий передачу первого набора данных первому компоненту от партнерского по линии связи связи компонента через по меньшей мере один канал линии связи. Первый набор данных включает в себя значение полного отклонения и значение низкой частоты. Значение полного отклонения и значение низкой частоты сохраняются в по меньшей мере одном регистре первого компонента. Исполняются команды по вычислению первого набора коэффициентов из значения полного отклонения и значения низкой частоты. Вычисляется первый набор коэффициентов из значения полного отклонения и значения низкой частоты. Сохраняется вычисленный первый набор коэффициентов в по меньшей мере одном регистре первого компонента. Применяется вычисленный первый набор коэффициентов для установки передающего компонента партнерского по линии связи связи компонента.

Пример 9: Первый набор данных включает в себя первый набор заранее заданных значений, который включает в себя второй набор коэффициентов для установки передающего компонента в партнерском по линии связи компоненте, и первый набор заранее заданных подсказок, который включает в себя второй набор коэффициентов для установки компонента приемника партнерского по линии связи связи компонента.

Пример 10: Вычисленный первый набор коэффициентов включает в себя по меньшей мере один из исходного коэффициента, текущего коэффициента и завершающего коэффициента.

Пример 11: Первый набор коэффициентов, примененный к передающему компоненту партнерского по линии связи компонента, дает возможность этому партнерскому по линии связи компоненту передавать данные к первому компоненту с частотой ошибочных битов меньше или равной одной ошибке на каждые 1012 битов.

Пример 12: Вычисленный первый набор коэффициентов применяется к передающему компоненту партнерского по линии связи компонента во время этапа 3 процедуры обучения и коррекции линии связи РВПКЭ третьего поколения.

Пример 13: Устройство, содержащее нисходящий порт, который в ответ на прохождение процедуры обучения и коррекции линии связи принимает первый упорядоченный набор из восходящего порта. Нисходящий порт включает в себя приемный компонент для приема данных от восходящего порта, а восходящий порт включает себя передающий компонент для передачи данных к нисходящему порту. Восходящий порт и нисходящий порт являются партнерами по линии связи. Первый упорядоченный набор включает в себя значение полного отклонения и значение низкой частоты, ассоциированные с восходящим портом. Нисходящий порт содержит логику для исполнения команд для вычисления первого набора коэффициентов из значения полного отклонения и значения низкой частоты первого упорядоченного набора. Нисходящий порт содержит по меньшей мере один регистр конфигурации для хранения вычисленного первого набора коэффициентов. Восходящий порт применяет вычисленный первый набор коэффициентов к установке передатчика восходящего порта.

Пример 14: Восходящий порт дополнительно включает в себя приемник, который принимает вычисленный первый набор коэффициентов из нисходящего порта.

Пример 15: Вычисленный первый набор коэффициентов сохраняется в единственном регистре конфигураций.

Пример 16: По меньшей мере один регистр конфигураций реализуется как триггерные запоминающие элементы.

Пример 17: Данные в по меньшей мере одном регистре конфигураций обеспечивают состояние восходящего порта.

Пример 18: Восходящий порт соединен в сенсорным дисплейным устройством.