Область техники, к которой относится изобретение

Варианты осуществления, описанные здесь, в общем, относятся к процессорам. В частности, варианты осуществления, описанные здесь, в общем, относятся к процессорам, имеющим инструкции, которые полезны для транскодирования точек кода переменной длины для знаков Unicode.

Уровень техники

Компьютеры, в принципе, обрабатывают двоичные числа. Обычно они не обрабатывают всевозможного типа буквы, десятичные числа, символы или другие знаки, используемые в разных языках и традициях. Скорее, таким различным буквам, десятичным числам, символам и другим знакам назначают двоичные числа, и их представляют двоичными числами.

Универсальный набор знаков (UCS) представляет собой стандартизированный набор знаков, на котором основаны несколько систем кодирования знаков. UCS определен международным стандартом ISO/IEC 10646, Information technology - Universal multiple-octet coded character set (UCS), вместе с изменениями к этому стандарту. UCS включает в себя большое количество разных знаков, включая в себя буквы, числа, символы, идеограммы, логограммы и другие знаки из наиболее распространенных языков, текстов и традиций мира. Каждый из этих знаков идентифицируется целым числом, которое называется точкой кода знаков.

Стандарт Unicode (Unicode) был разработан совместно с USC. Unicode представляет собой стандарт компьютерной промышленности для соответствующего цифрового кодирования, представления и обработки знаков UCS. В соответствии с последними отчетами Unicode обеспечивает уникальное число для каждого знака, независимо от платформы, независимо от программы, независимо от языка. Unicode в настоящее время используется практически всеми современными компьютерами и серверами, как основа для обработки текста по Интернет.

Unicode может быть воплощен через различные системы кодирования знаков. Одна из обычно используемых систем кодирования представляет собой UTF-8 (8-битный формат преобразования UCS). UTF-8 представляет собой кодирование переменной длины (например, с переменным количеством байтов), которое может представлять собой каждый знак в Unicode. Каждый знак в Unicode представлен между одним и четырьмя байтами. Байты также называются октетами в стандарте Unicode. В UTF-8 используется один байт для представления любого из знаков ASCII. UTF-8 обладает обратной совместимость с ASCII, и знаки имеют одинаковое кодирование, как в ASCII, так и в UTF-8. Другие знаки, не входящие в ASCII, представлены двумя, тремя или четырьмя байтами. По оценке UTF-8 представляет собой самое распространенное кодирование Unicode на веб-страницах во всемирной сети, при этом более половины всех веб-страниц кодируют, используя UTF-8. UTF-8 также широко используется программами электронной почты для отображения и формирования почты. Все чаще UTF-8 также используется для кодирования знаков Unicode в определенных языках программирования, операционных системах, интерфейсах программирования приложения (API) и в программных приложениях.

Другое обычно используемое кодирование представляет собой UTF-16 (16-битный формат преобразования UCS). UTF-16 представляет собой кодирование переменной длины (например, с переменным количеством байтов), которое может представлять каждый знак в Unicode. Каждый знак Unicode представлен либо двумя, или четырьмя байтами. UTF-16 не обладает обратной совместимостью с ASCII. UTF-16 обычно используется, как международная форма Unicode в определенных языках программирования таких, как, например, Java, С# и JavaScript, и в определенных операционных системах. Также используются различные другие известные системы кодирования (например, UTF-2, UTF-32, UTF-1 и т.д.).

Обычно, для того чтобы способствовать обработке в компьютерных системах, UTF-8, UTF-16 или другие кодированные данные, могут быть транскодированы в другой формат, такой как, например, Unicode. Транскодирование представляет непосредственное цифро-цифровое преобразование данных из одной системы кодирования в другую. Такое транскодирование может быть выполнено по разным причинам, таким как, например, для того, чтобы помочь повысить эффективность или скорость обработки данных, для преобразования кодированных данных в формат, используемый программным обеспечением, или в более широко распознаваемый формат и т.д. Часто большое количество обработки требуется для транскодирования содержания веб-страниц, документов, отформатированных с использованием языков разметки, документов XML и т.п., из одной системы кодирования (например, UTF-8) в стандартные знаки Unicode или в другие форматы. Благодаря распространенности такого транскодирования и/или его потенциального влияния на рабочие характеристики, новые и полезные подходы для транскодирования могли бы стать предпочтительными. Краткое описание чертежей

Изобретение будет более понятным при ссылке на следующее описание и приложенные чертежи, которые используются для иллюстрации вариантов осуществления. На чертежах:

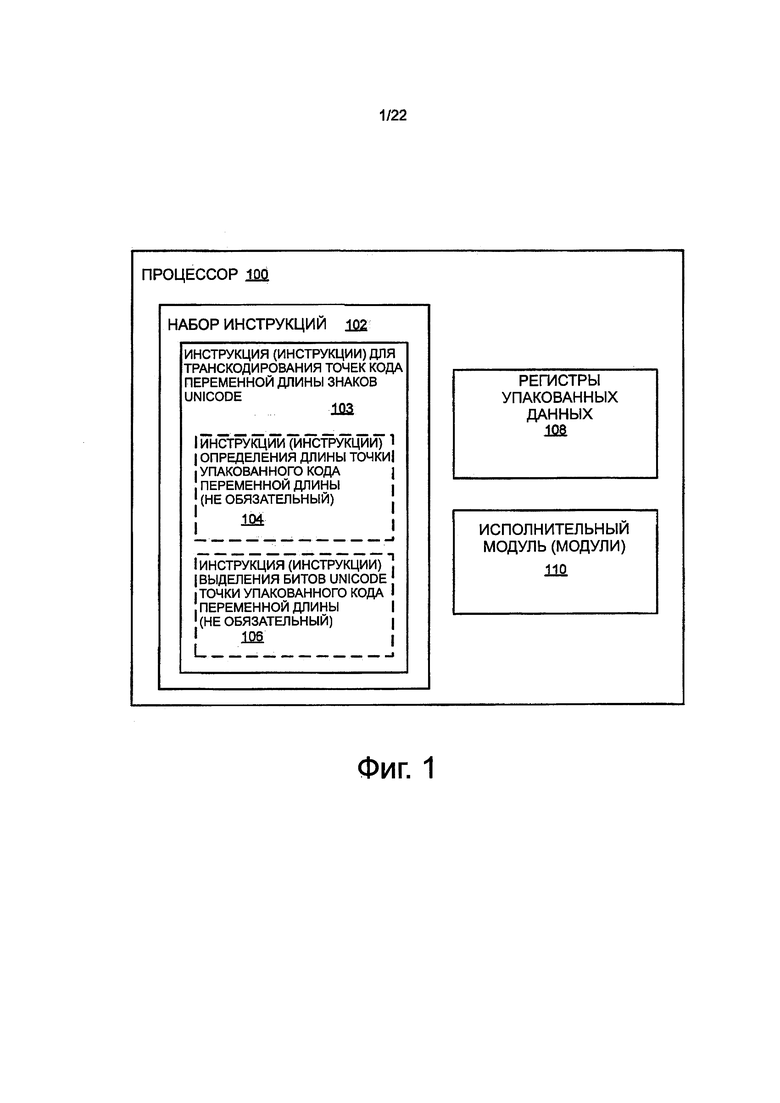

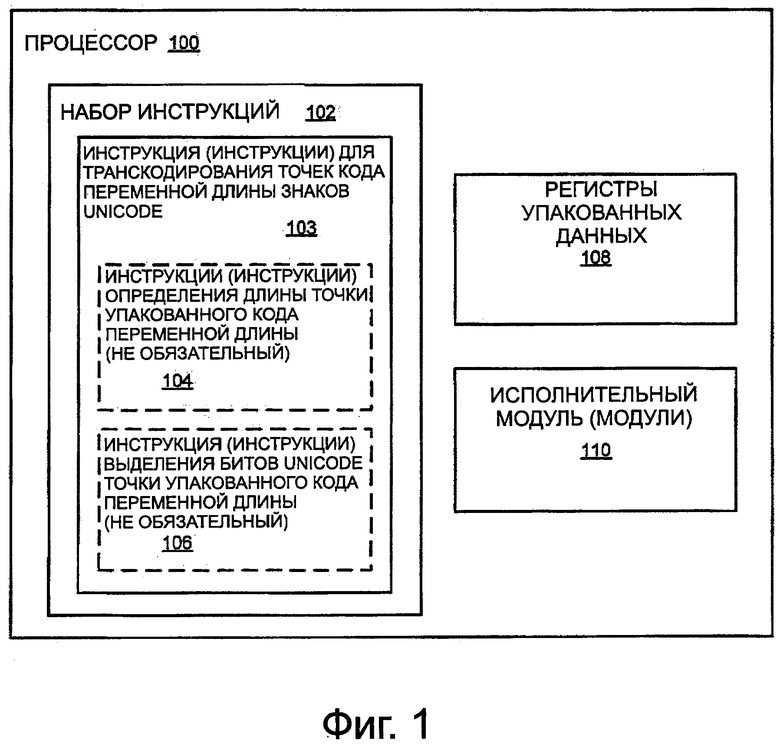

на фиг. 1 показана блок-схема варианта осуществления процессора;

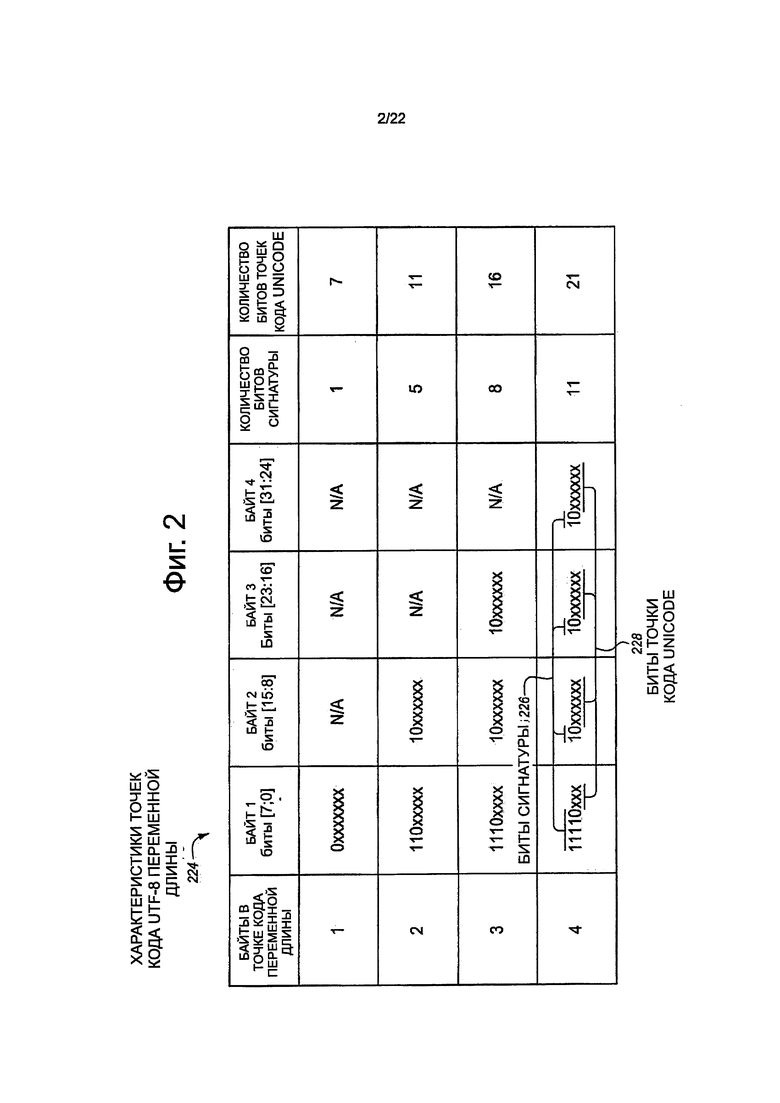

на фиг. 2 показана таблица характеристик точек кода переменной длины UTF-8;

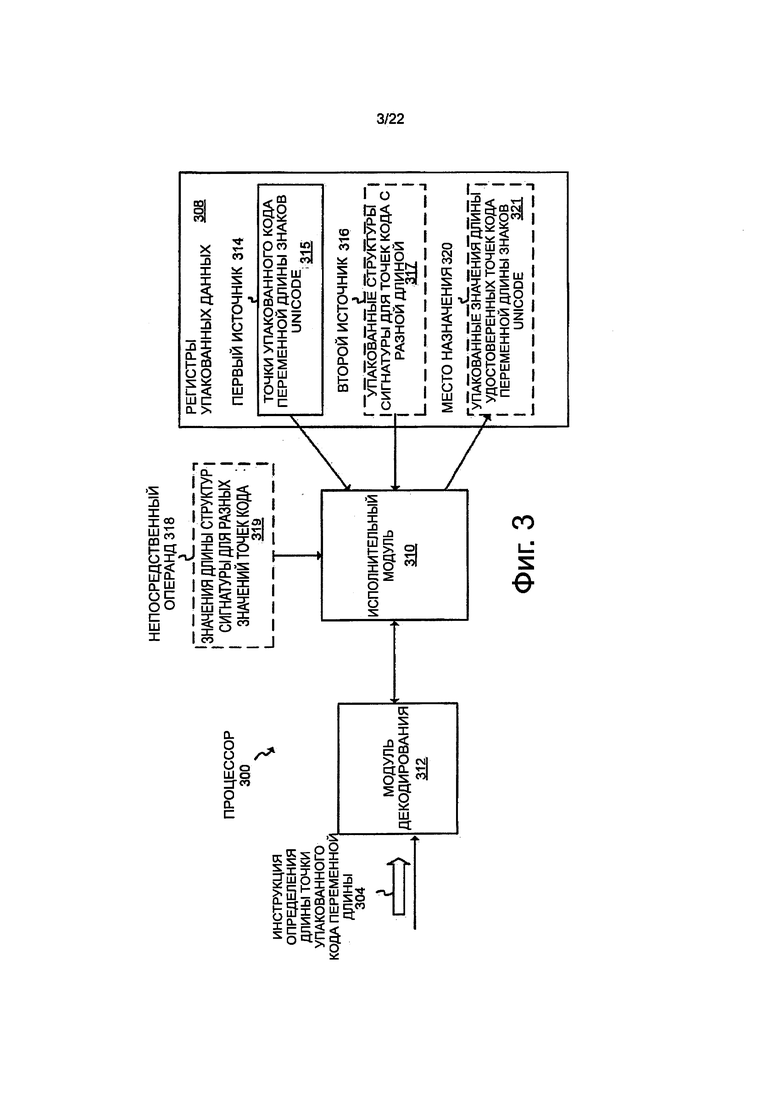

на фиг. 3 показана блок-схема варианта осуществления процессора, который во время работы обрабатывает вариант осуществления инструкции определения длины точки упакованного кода переменной длины;

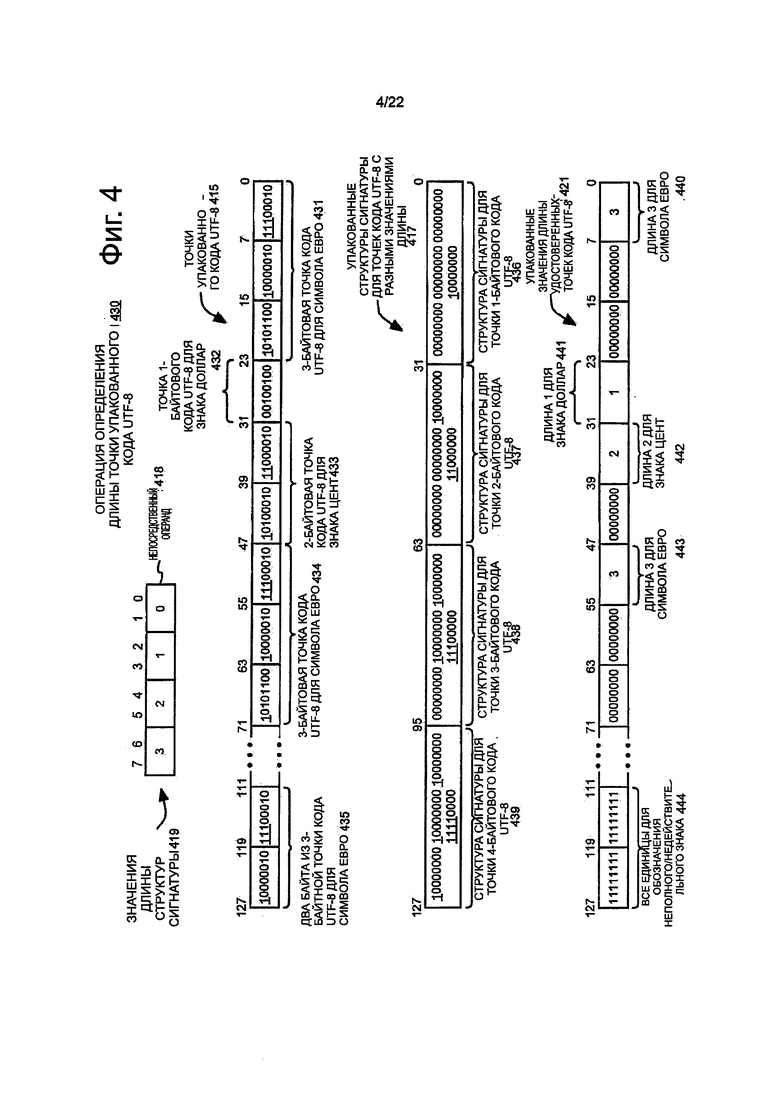

на фиг. 4 показана блок-схема примерного варианта осуществления соответствующей операции определения длины точки упакованного кода переменной длины для точек кода переменной длины UTF-8;

на фиг. 5 показана блок-схема последовательности операций варианта осуществления способа, выполняемого процессором и/или в пределах процессора, в ходе обработки варианта осуществления инструкции определения длины точки упакованного кода переменной длины;

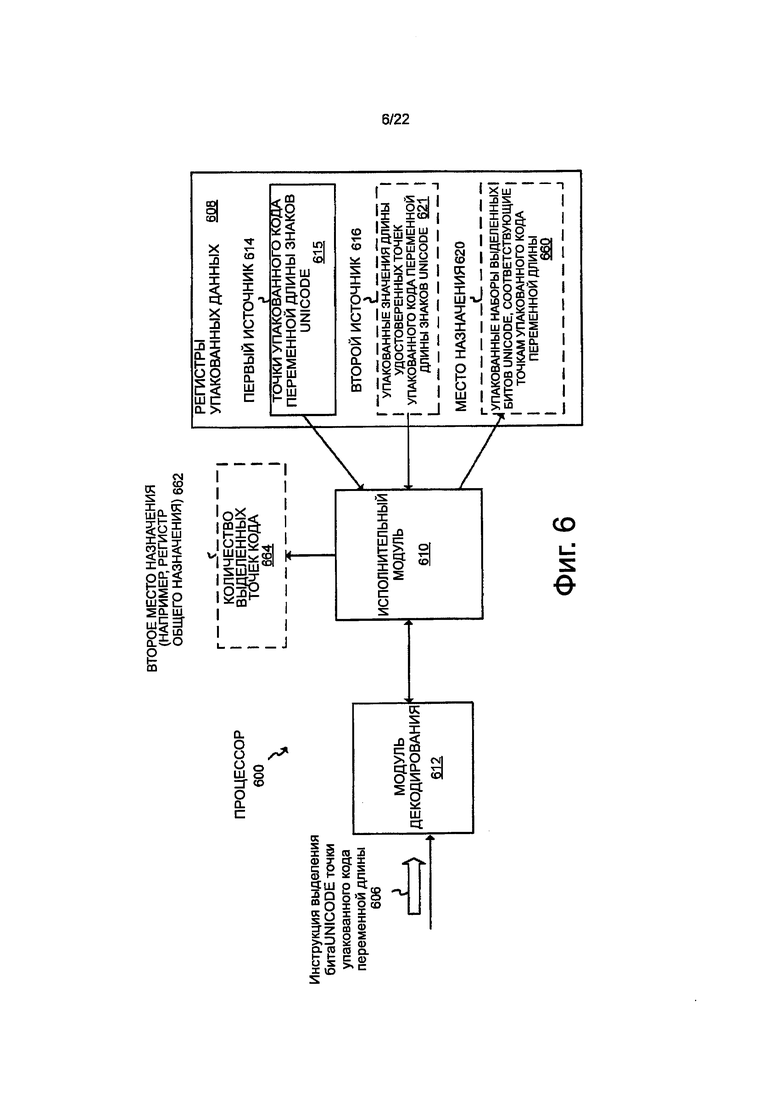

на фиг. 6 показана блок-схема варианта осуществления процессора, который во время работы выполняет или обрабатывает вариант осуществления инструкции выделения битов знака точки упакованного кода переменной длины (например, битов Unicode);

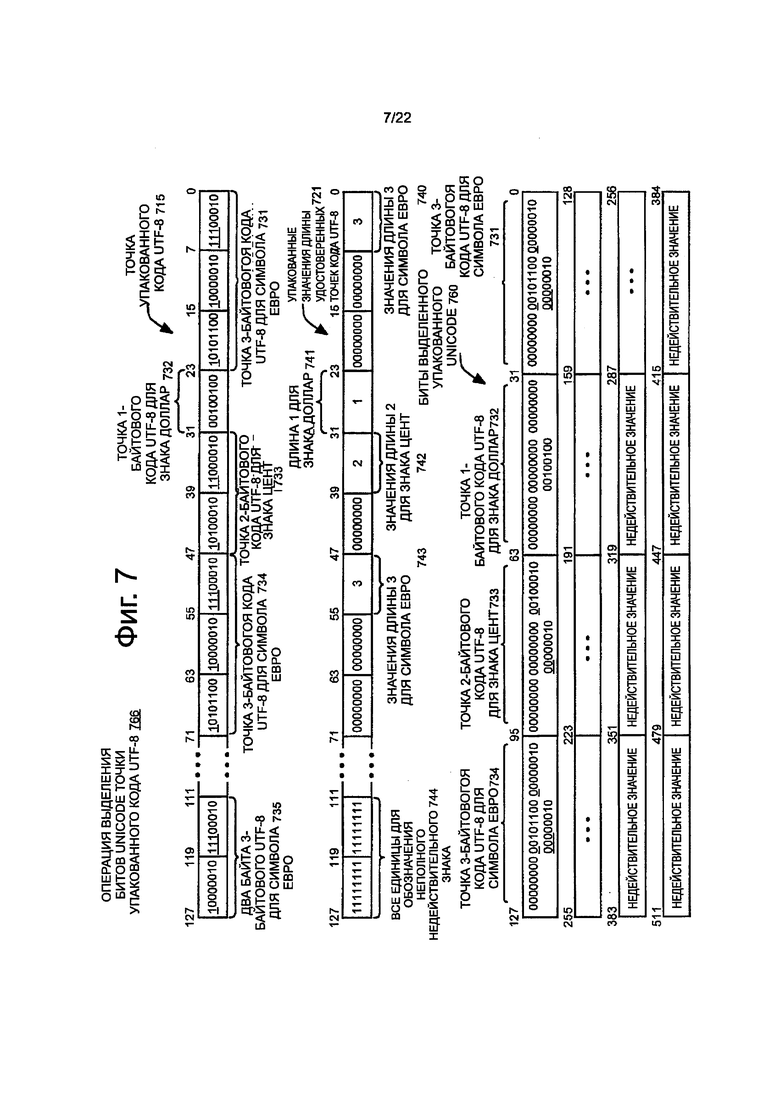

на фиг. 7 показана блок-схема примерного варианта осуществления соответствующих операций выделения битов знака точки упакованного кода UTF-8 (например, битов Unicode) для точек кода UTF-8;

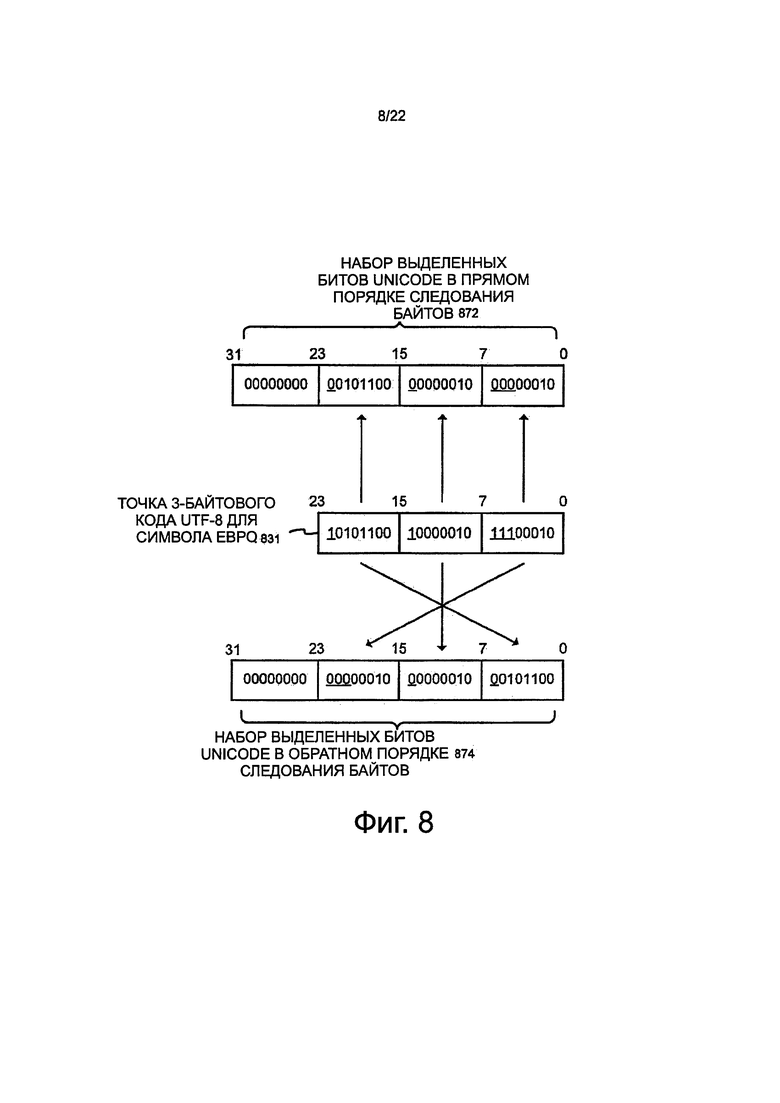

на фиг. 8 показана блок-схема, иллюстрирующая соответствующие способы размещения или упорядочивания наборов выделенных битов Unicode в упакованном элементе данных;

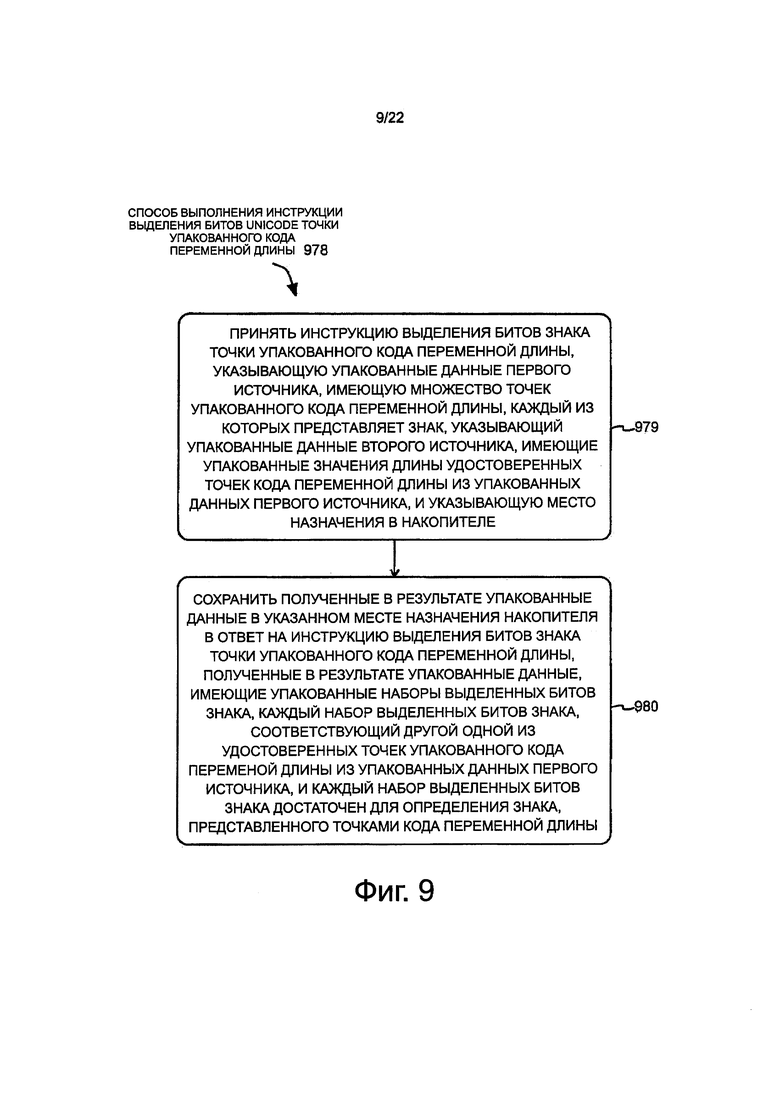

на фиг. 9 показана блок-схема последовательности операций варианта осуществления способа, выполняемого процессором и/или в пределах процессора, в ходе обработки варианта осуществления инструкции выделения битов знака точки упакованного кода переменной длины (например, битов Unicode);

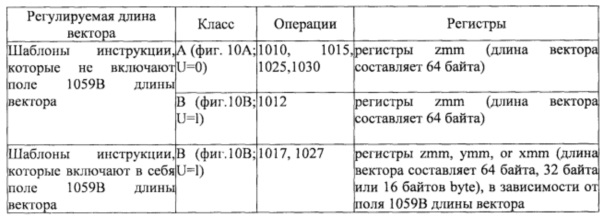

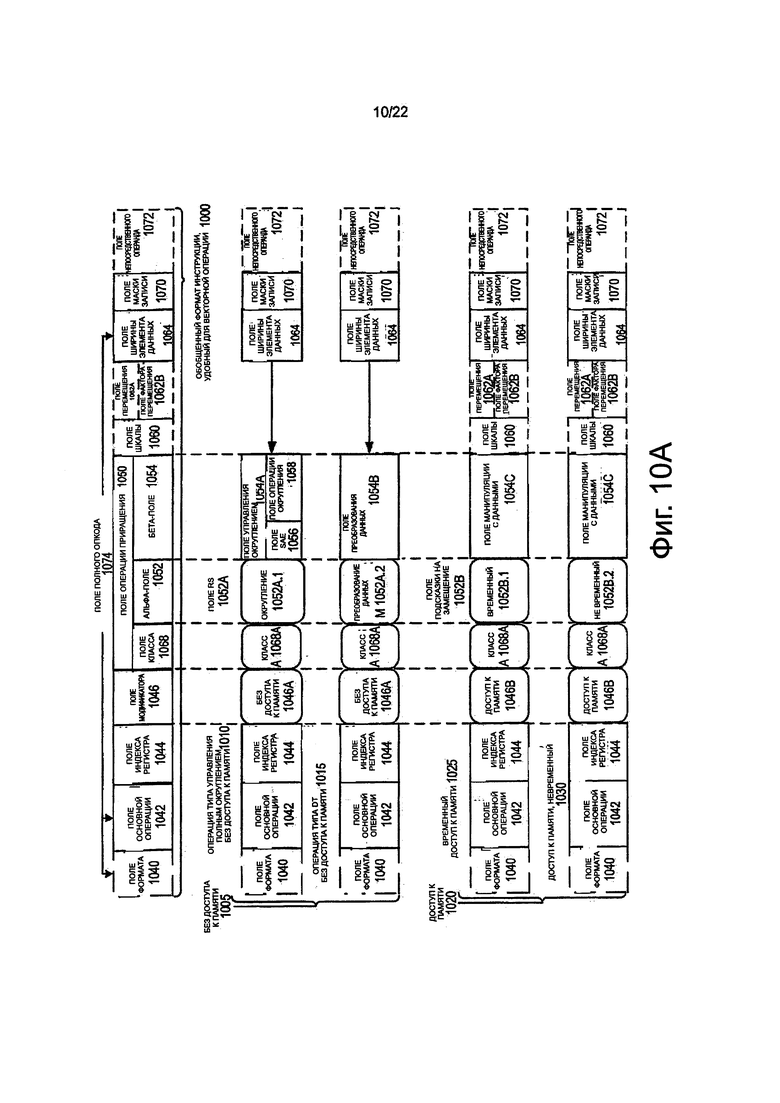

на фиг. 10А показана блок-схема, иллюстрирующая обобщенный формат инструкции, удобный для векторных операций, и его шаблоны инструкции класса А в соответствии с вариантами осуществления изобретения;

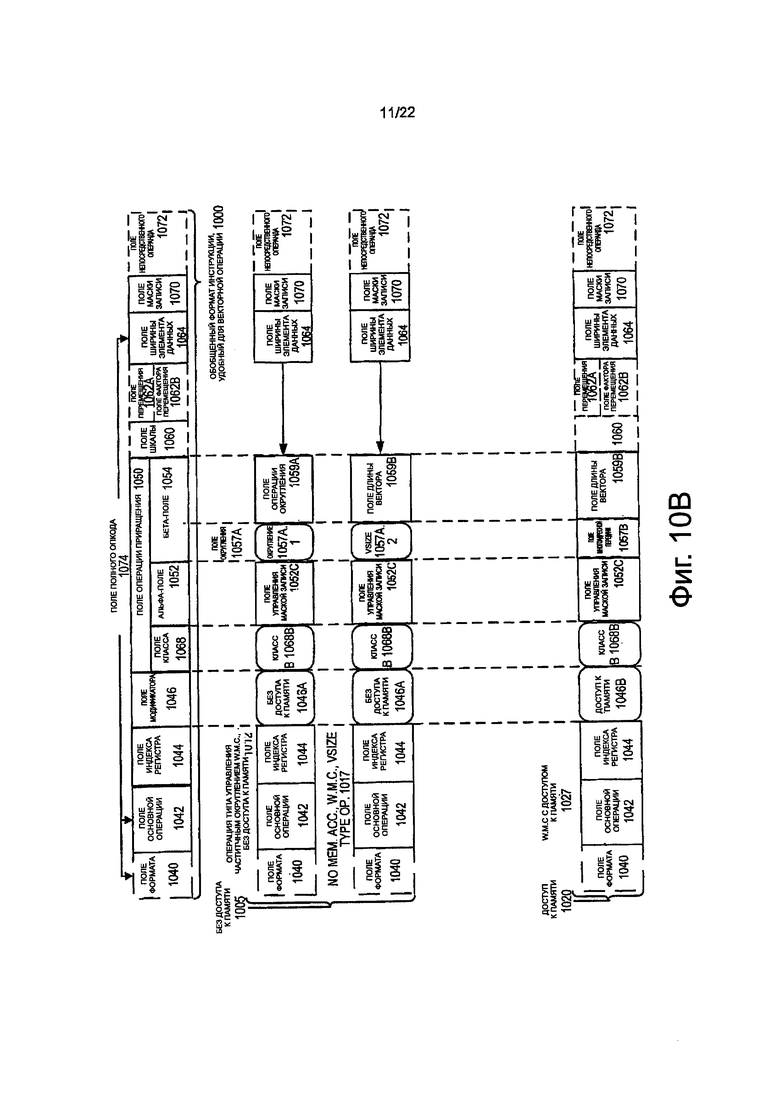

на фиг. 10В показана блок-схема, иллюстрирующая обобщенный формат инструкции, удобный для векторных операций, и его шаблоны инструкции класса В в соответствии с вариантами осуществления изобретения;

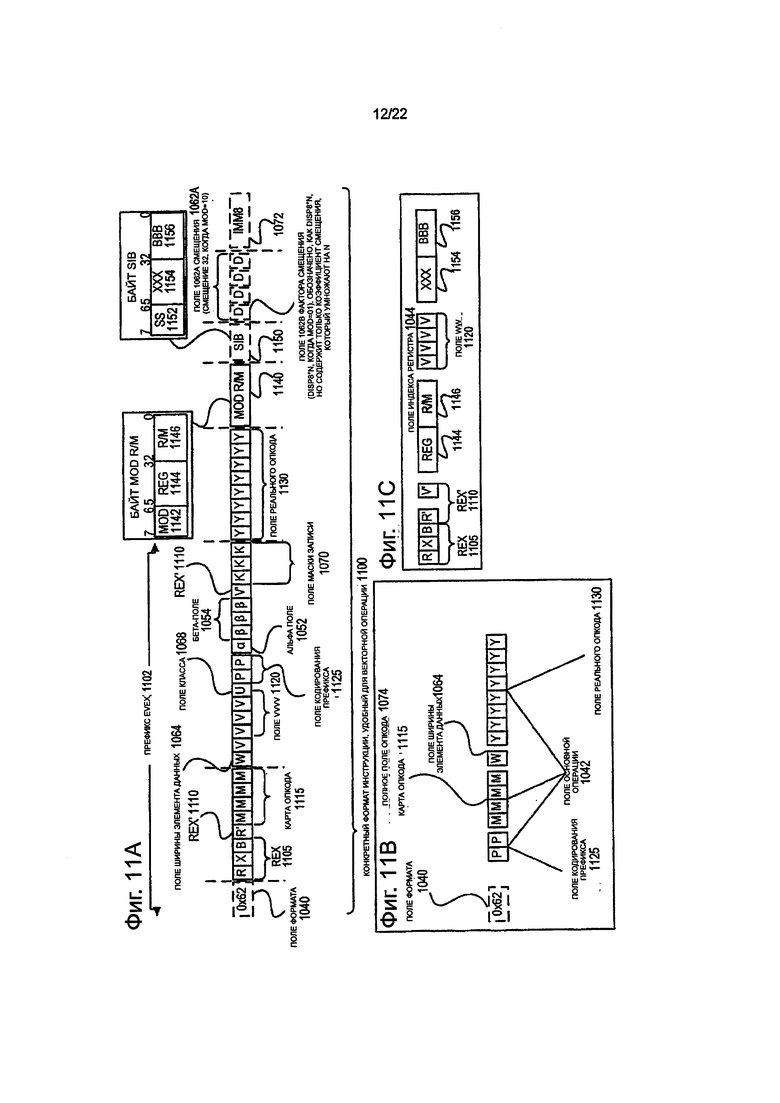

на фиг. 11А показана блок-схема, иллюстрирующая примерный конкретный формат инструкции, удобный для векторных операций, в соответствии с вариантами осуществления изобретения;

на фиг. 11В представлен конкретный формат инструкции, удобный для векторных операций, который определен в том смысле, что он определяет местоположение, размер, интерпретацию и порядок полей, а также значения для некоторых из этих областей;

на фиг. 11С показана блок-схема, иллюстрирующая поля конкретного формата инструкции, удобного для векторных операций, которые составляют поле индекса регистра в соответствии с одним вариантом выполнения изобретения;

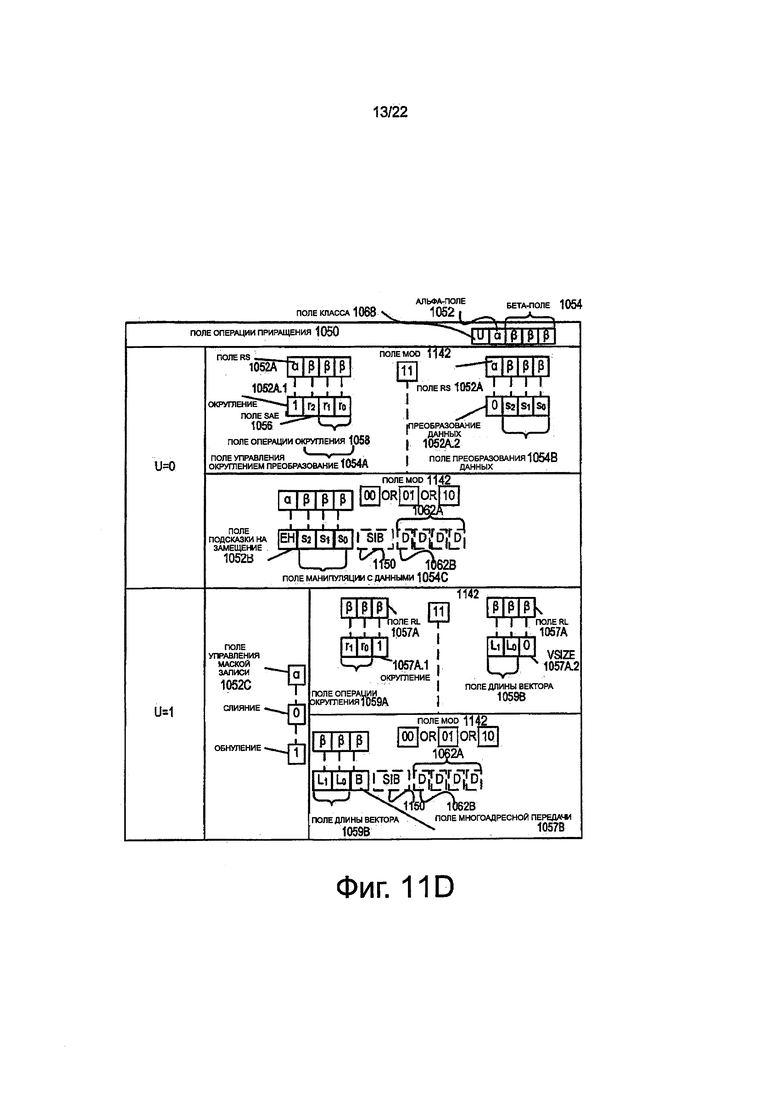

на фиг. 11D показана блок-схема, иллюстрирующая поля конкретного формата инструкции, удобного для векторных операций, которые составляют поле операции приращения в соответствии с одним вариантом выполнения изобретения;

на фиг. 12 показана блок-схема архитектуры регистра в соответствии с одним вариантом выполнения изобретения;

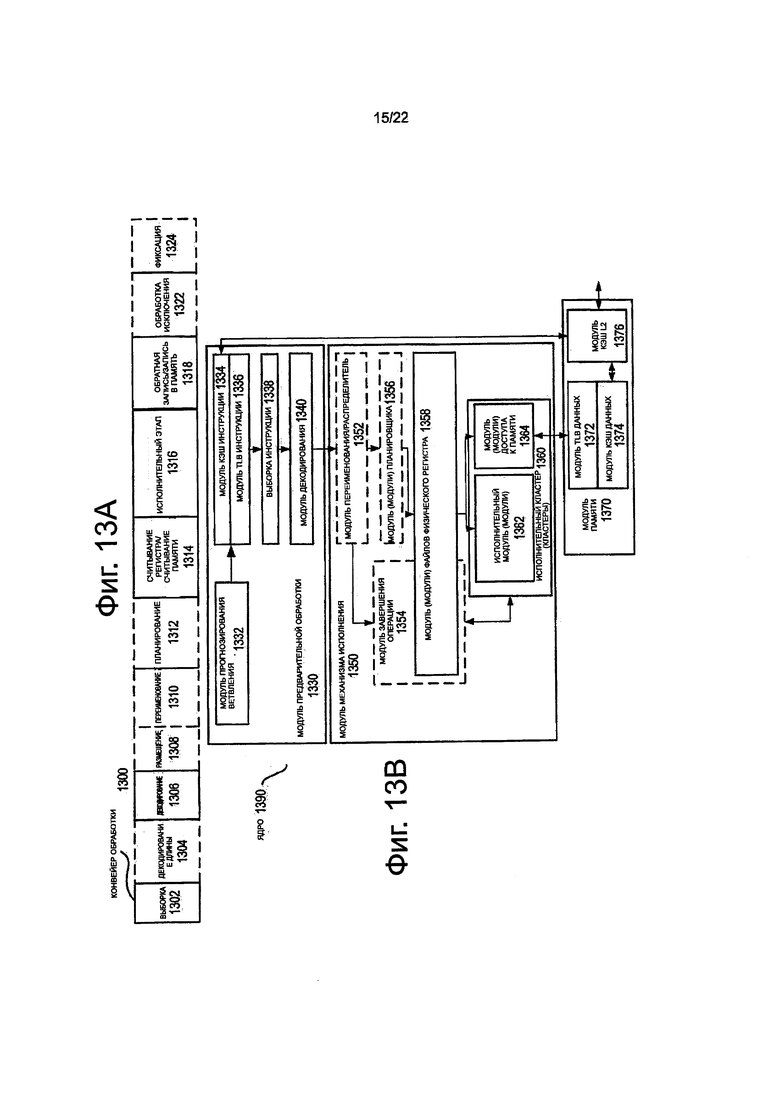

на фиг. 13А показана блок-схема, иллюстрирующая, как примерный конвейер, работающий по порядку, так и примерный конвейер обработки задачи/исполнения, работающий не порядку, с переименованием регистра, в соответствии с вариантами осуществления изобретения;

на фиг. 13В показана блок-схема, иллюстрирующая, как примерный вариант осуществления архитектуры ядра, работающей по порядку, так и пример архитектуры ядра задачи/исполнения не по порядку с переименованием регистра, которое должно быть включено в процессор, в соответствии с вариантами осуществления изобретения;

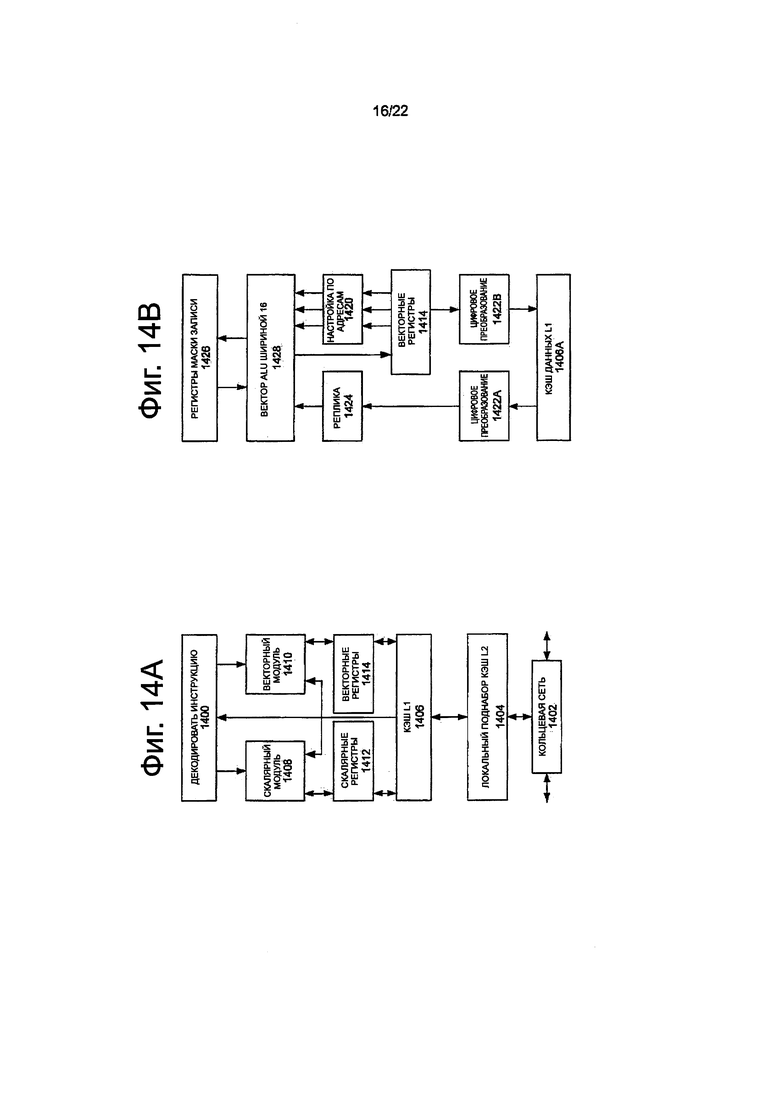

на фиг. 14А показана блок-схема ядра с одним процессором, вместе с его соединением с сетью взаимного соединения на кристалле и с его локальным поднабором кэш Уровня 2 (L2), в соответствии с вариантами осуществления изобретения;

на фиг. 14В показан расширенный вид в перспективе части ядра процессора по фиг. 14А, в соответствии с вариантами осуществления изобретения;

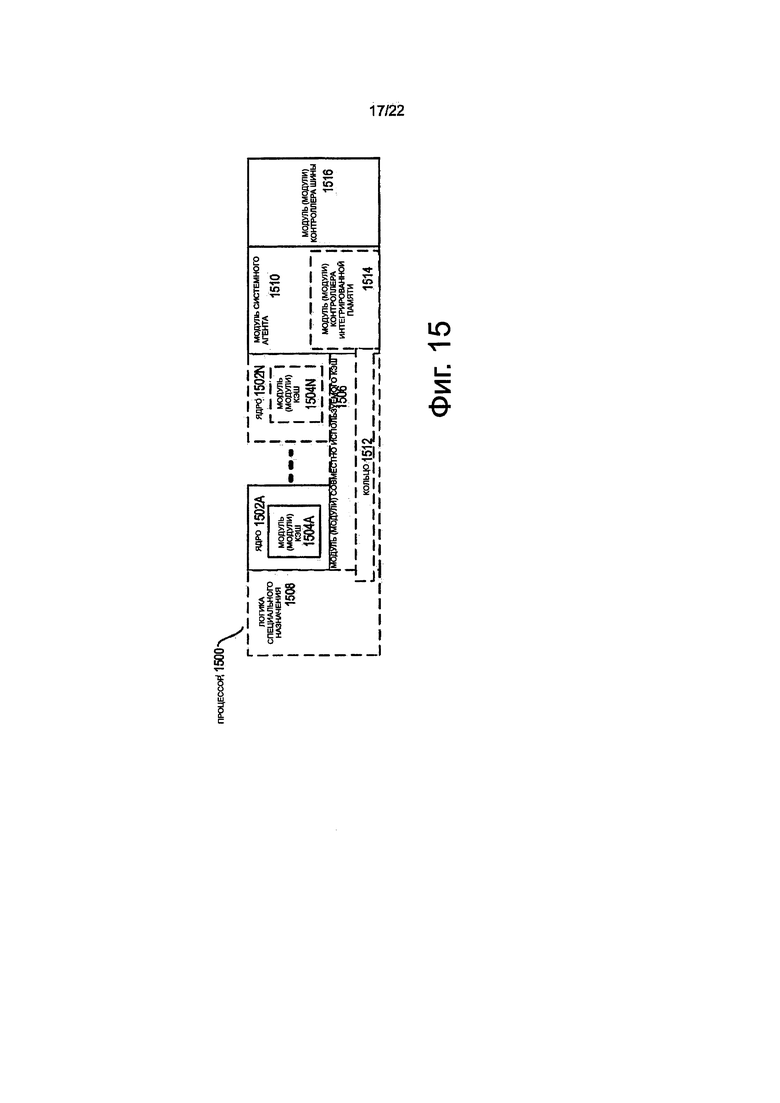

на фиг. 15 показана блок-схема процессора, который может иметь больше, чем одно ядро, может иметь интегрированный контроллер памяти и может иметь интегрированную графику, в соответствии с вариантами осуществления изобретения;

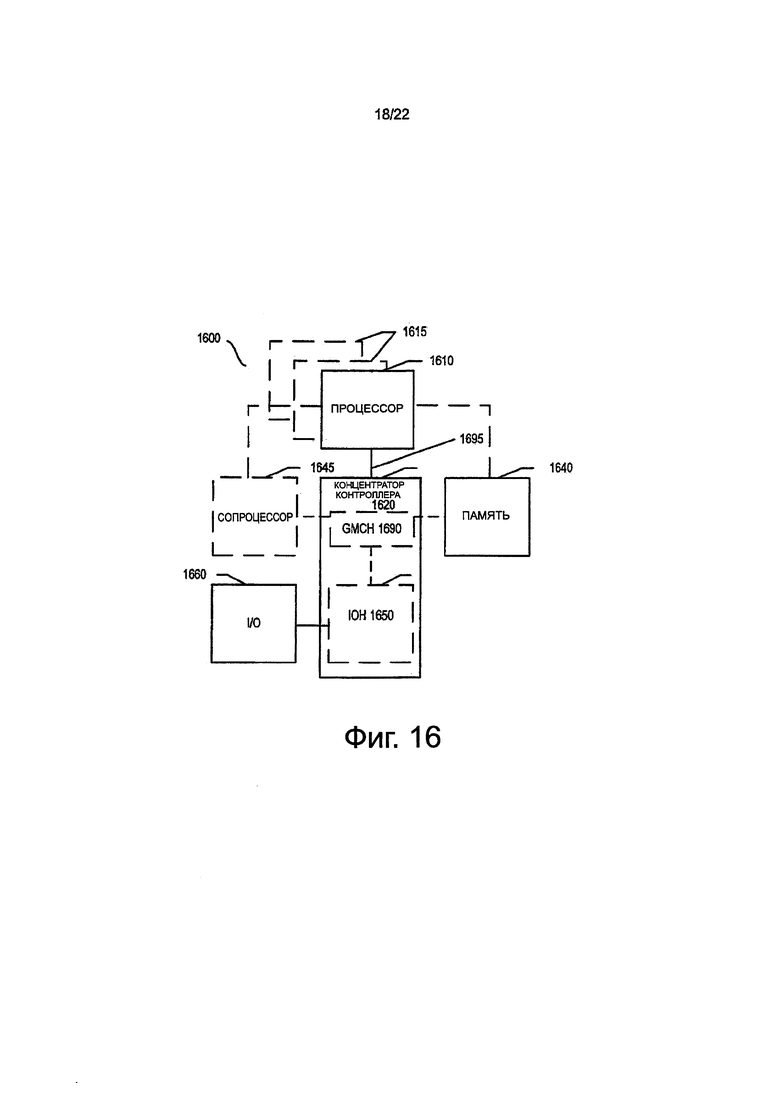

на фиг. 16 показана блок-схема системы в соответствии с одним вариантом осуществления настоящего изобретение;

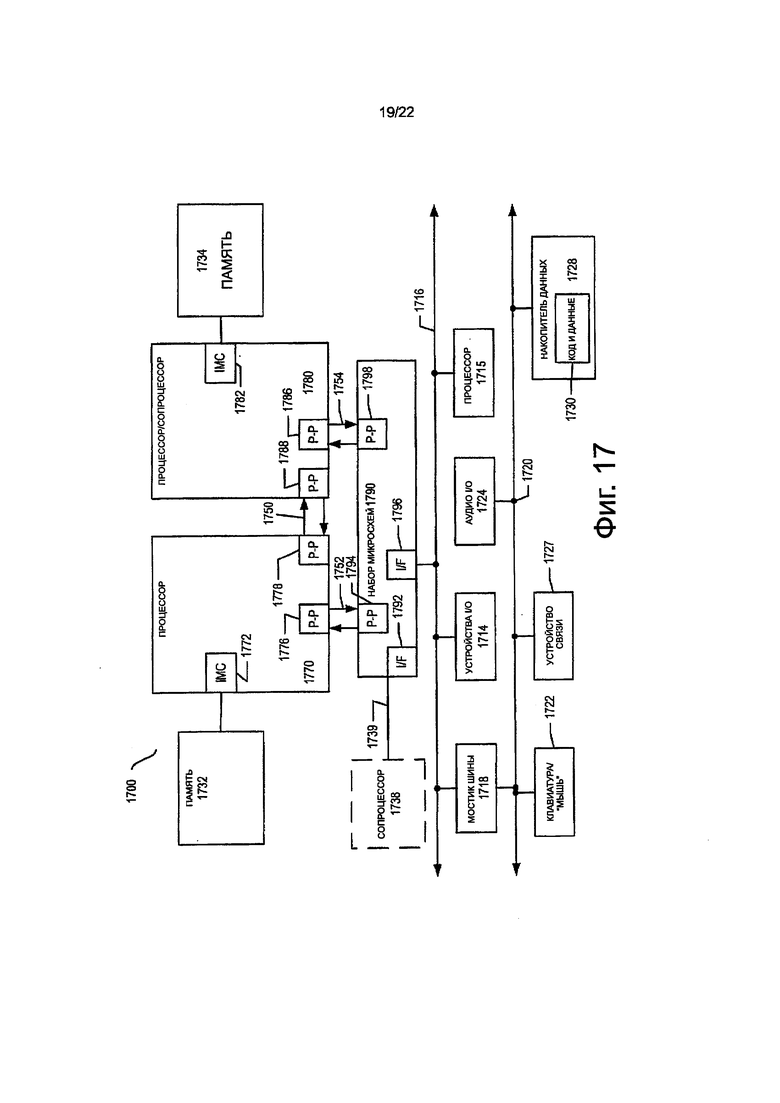

на фиг. 17 показана блок-схема первого, более конкретного примера системы, в соответствии с вариантом осуществления настоящего изобретение;

на фиг. 18 показана блок-схема второго, более конкретного примера системы, в соответствии с вариантом осуществления настоящего изобретение;

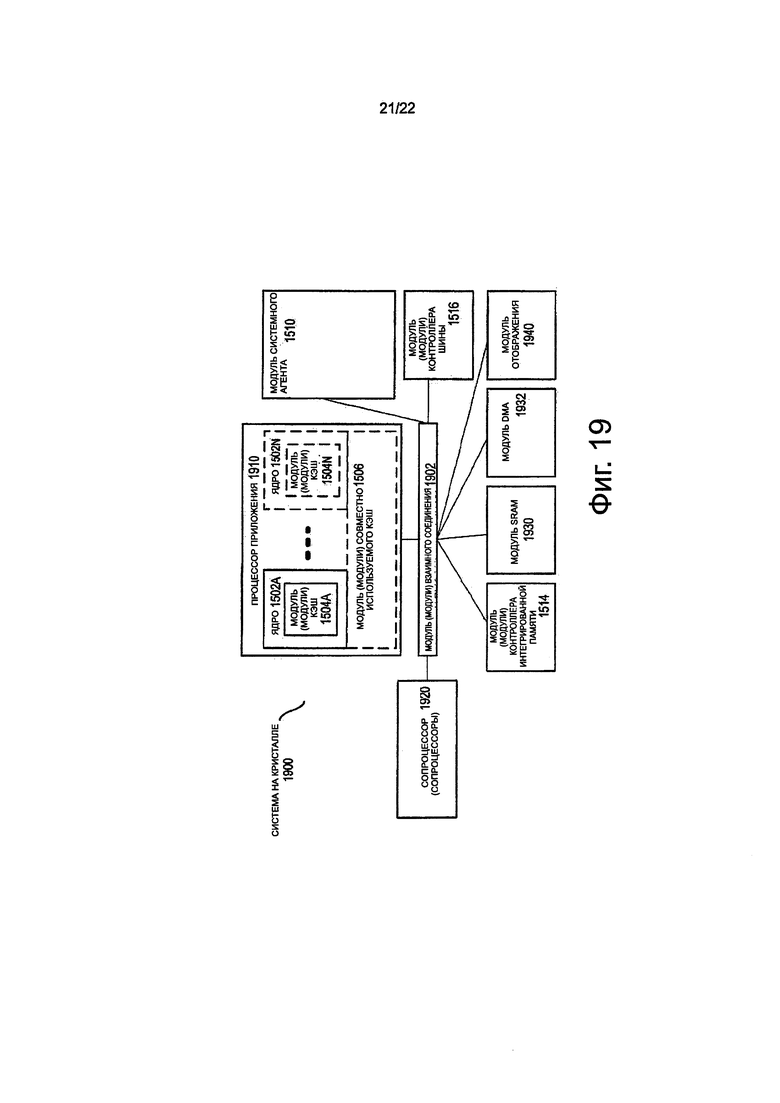

на фиг. 19 показана блок-схема SoC, в соответствии с вариантом осуществления настоящего изобретение;

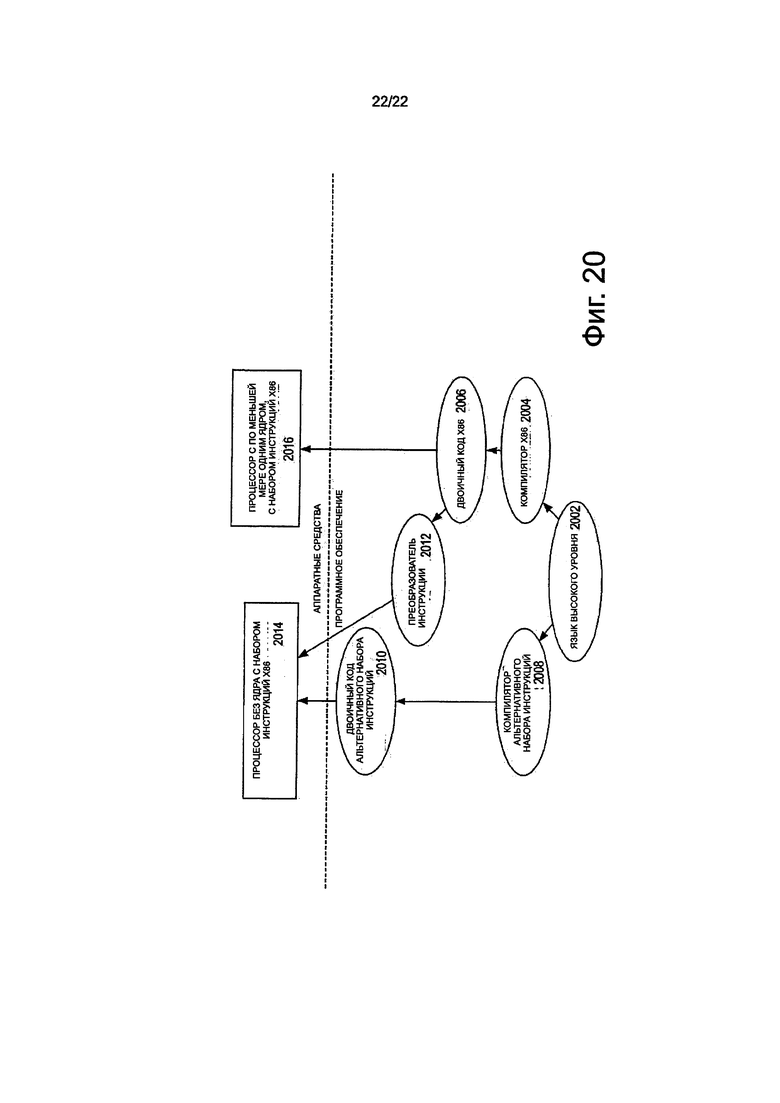

на фиг. 20 показана блок-схема, представляющая отличие от использования программного преобразователя инструкции для преобразования двоичных инструкций в наборе инструкций источников в двоичную инструкцию в целевом наборе инструкций, в соответствии с вариантами осуществления изобретения.

Осуществление изобретения

Здесь раскрыты инструкции, используемые для транскодирования точек кода переменной длины данных Unicode, процессоры для исполнения или выполнения инструкций, способы, выполняемые процессорами при исполнении или выполнении инструкций, и системы, в состав которых входит один или больше процессоров для исполнения или выполнения инструкций. В следующем описании, представлено множество конкретных деталей (например, операции/функции конкретной инструкции, комбинации инструкций, форматы кодирования, конфигурации процессора, последовательности операций и т.п.). Однако, варианты осуществления могут быть выполнены на практике без этих конкретных деталей. В других случаях хорошо известные схемы, структуры и технологии не были представлены подробно, чтобы исключить затруднения при понимании описания.

На фиг. 1 показана блок-схема варианта осуществления процессора 100. Процессор представляет вариант осуществления устройства обработки инструкции. В некоторых вариантах осуществления процессор может представлять собой процессор общего назначения (например, микропроцессор общего назначения, такого типа, который часто используется, как центральное процессорное устройство (CPU) в настольных компьютерах, переносных компьютерах и подобных компьютерах). В качестве альтернативы, процессор может представлять собой процессор специального назначения. Примеры соответствующих процессоров специального назначения включают в себя, но не ограничены этим, сетевые процессоры, процессоры передачи данных, криптографические процессоры, графические процессоры, сопроцессоры, встроенные процессоры, цифровые сигнальные процессоры (DSP) и контроллеры (например, микроконтроллеры), которые представляют собой только несколько примеров. Такие процессоры специального назначения также иногда называются аппаратными ускорителями, ускорителями специального назначения и т.п. Процессор может представлять собой любой из различных процессоров со сложным набором команд архитектуры процессора (CISC), различных процессоров с сокращенным набором команд (RISC), различных процессоров с командами большой длины (VLIW), различные гибриды или другие типы процессоров вообще.

Процессор имеет набор 102 инструкций. Инструкции набора инструкций представляют макроинструкции, инструкции языка ассемблера, инструкции машинного уровня или другие инструкции относительно высокого уровня или сигналы управления, в отличие от микроинструкций, микроопераций, или других инструкций относительно низкого уровня или сигналов управления, которые получают в результате декодирования инструкций более высокого уровня или сигналов управления.

В некоторых вариантах осуществления набор инструкций может включать в себя одну или больше инструкций 103, которые используются для транскодирования кодов переменной длины или точек кода для данных Unicode. В некоторых вариантах осуществления инструкции 103, в случае необходимости, включают в себя одну или больше упакованных инструкций 104 определения длины точки кода переменной длины. Упакованные инструкции 104 определения длины точки кода переменной длины могут иметь одну из характеристик, атрибутов или свойств, показанных и описанных дополнительно ниже на фигурах со ссылкой на фиг. 3-5. В некоторых вариантах осуществления инструкции 103, в случае необходимости, могут включать в себя одну или больше инструкций 106 выделения упакованных битов знака точки кода переменной длины (например, битов Unicode). Инструкции 106 выделения упакованных битов знака точки кода переменной длины (например, биты Unicode) могут иметь любую одну из характеристик, атрибутов или свойств, показанных и описанных дополнительно ниже со ссылкой на фиг. 2 и 6-9. В некоторых вариантах осуществления инструкции 103 могут, в случае необходимости, включать в себя, как одну или больше инструкций 104 определения длины точки кода упакованной переменной длины и одну или больше инструкций 106 выделения упакованных битов знака точки кода переменной длины (например, битов Unicode), хотя это и не требуется.

Процессор также включает в себя набор регистров 108 упакованных данных. Регистры упакованных данных, в общем, представляют места расположения на кристалле в накопителе процессора. Регистры упакованных данных работают для сохранения упакованных данных, векторных данных или данных SIMD. Инструкции из набора инструкций (например, инструкции 104 определения длины точки кода упакованной переменной длины и/или инструкции 106 выделения битов Unicode точки кода упакованной переменной длины), могут устанавливать регистры упакованных данных из набора 108 для идентификации операндов (например, операндов источника, операндов места назначения и т.д.). Таким образом, регистры упакованных данных могут быть видимыми для программных средств и/или программиста (возможно, могут быть воплощены с переименованием регистра). Такие регистры иногда называются архитектурно видимыми регистрами или архитектурными регистрами.

Процессор также включает в себя один или больше исполнительных модулей 110. Исполнительный модуль (модули) работают для исполнения или обработки необязательных инструкций 104 определения длины упакованной точки кода переменной длины и/или необязательных инструкций 106 выделения битов Unicode упакованной точки кода переменной длины. В некоторых вариантах осуществления исполнительный модуль (модули) может включать в себя определенную логику (например, определенную схему или другие аппаратные средства, потенциально в комбинации с одним или больше из встроенного программного обеспечения и программного обеспечения) для выполнения инструкций 104, 106.

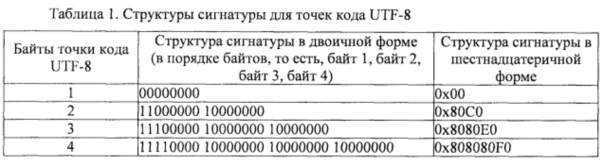

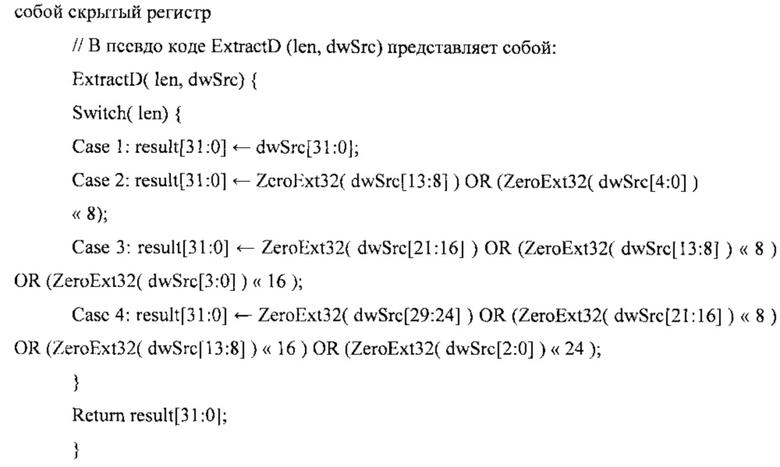

На фиг. 2 показана таблица характеристик 224 точек кода переменной длины UTF-8. В первом самом левом столбце представлен список множества байтов в точках кода переменной длины UTF-8. Первый ряд соответствует одному байту точек кода UTF-8, второй ряд соответствует двум байтам точек кода UTF-8, третий ряд соответствует трем байтам точек кода UTF-8, и четвертый ряд соответствует четырем байтам точек кода UTF-8. В будущем, возможно, что пять или еще шесть байтов точек кода UTF-8 могут стать более распространенными в UTF-8.

Во втором - четвертом столбцах представлен в виде списка формат из байтов переменной длины точек кода UTF-8. Формат в каждом байте представлен от положения младшего значащего бита справа до положения старшего значащего бита слева. Например, формат байта 1 одного байта точки кода UTF-8 представляет собой Оххххххх. Байт 2 следует после байта 1 (то есть, байт 2 является более значимым), байт 3 следует после байта 2, и байт 4 следует после байта 3. Для двухбайтной точки кода UTF-8 формат байта 1 представляет собой 10ххххх, и формат байта 2 представляет собой 10хххххх. Форматы точек кода UTF-8 из трех и четырех байтов являются такими, как представлено на иллюстрации. В этих форматах биты, которые представляют двоичные единицы (то есть, 1) и нули (то есть, 0) представляют биты 226 сигнатуры, тогда как символ "х" используется в тех битах, которые представляют биты 228 точек кода Unicode. Например, для формата UTF-8 из двух байтов, самые левые три старших значащих бита в байте 1 и самые левые два старших значащих бита в байте 2 представляют собой биты сигнатуры, тогда как все другие биты, представленные "х", представляют собой биты точки кода Unicode.

Биты 226 сигнатуры используются для определения длины точки кода UTF-8 (например, представляет ли она собой точку кода UTF-8 из одного байта, двух байтов, трех байтов или четырех байтов). Например, биты сигнатуры могут использоваться для определения контекста положения точки кода во входном потоке байтов, который может использоваться для определения идентичностей компонента байтов многобайтной точки кода UTF-8. Биты 228 точки кода Unicode можно использовать для определения, путем транскодирования, соответствующего знака Unicode или значения, которое кодировано или представлено точкой кода UTF-8. Таким образом, биты точки кода Unicode могут изменяться с одного знака Unicode на другой.

Точка однобайтового кода UTF-8 имеет один бит сигнатуры в бите 7 и семь битов точек кода Unicode в битах [6:0]. Точка двухбайтового кода UTF-8 имеет пять битов сигнатуры в битах [7:5] и [15:14] и одиннадцать битов точки кода Unicode в битах [4:0] и [13:8]. Точка в трехбайтовом коде UTF-8 имеет восемь битов сигнатуры в битах [7:4], [15:14] и [23:22], и шестнадцать битов точек кода Unicode в битах [3:0], [13:8] и [21:16]. Точка четырехбайтового кода UTF-8 имеет одиннадцать битов сигнатуры в битах [7:3], [15:14], [23:22] и [31:30]. Точка четырехбайтового кода UTF-8 имеет двадцать один бит точки кода Unicode в битах [2:0], [13:8], [21:16] и [29:24].

В соответствии с этим, в UTF-8 так же, как и в других стандартах, используемых для кодирования знаков Unicode, применяют кодирование переменной длины или точки кода (например, различные количества байтов для представления разных знаков Unicode). Кодирование переменной длины или точек кода обычно означает, что процессорам требуется транскодировать или по-другому обработать эти точки кода или потоки байтов в контексте положения, выведенном из одного или больше предыдущего байта (байтов). Такое свойство часто затрудняет выполнение такого транскодирования, используя операции с упакованными данными, векторные операции или операции SIMD. С одной стороны, вычислительные операции или манипуляции необходимые для транскодирования точки кода UTF-8, например, в 32-битное значение Unicode, обычно меняются в зависимости от длины точки кода UTF-8. В результате, границы разделений между точками кода переменной длины (например, точками кода одно, двух, трех и четырехбайтового кода UTF-8) обычно должны быть определены и должны соблюдаться во время обработки SIMD. Существующие наборы инструкций SIMD, в общем, являются неэффективными при удостоверении или определении переменных длин точек кода UTF-8 и других систем кодирования переменной длины. Улучшенные способы определения длины разных точек кода, например, через одиночные инструкции, специально разработанные с этой целью, могут иметь преимущество. Кроме того, гранулярная обработка бита внутри байта и между байтами с неустановившимися структурами от одного байта к следующему, применяемая при транскодировании UTF-8 или других точек кода переменной длины в другие форматы, обычно проявляет тенденцию быть трудновыполнимой в операциях с упакованными данными, в векторных операциях или в операциях SIMD. Улучшенные способы выполнения такой гетерогенной обработки внутри байта и между байтами, используемой во время транскодирования, например, через одиночные инструкции, специально разработанные с этой целью, могут иметь преимущества.

На фиг. 3 показана блок-схема варианта осуществления процессора 300, который во время работы выполняет или обрабатывает вариант осуществления инструкции определения длины точки упакованного кода переменной длины 304. Процессор 300, в случае необходимости, может иметь одну из характеристик или атрибутов процессора по фиг. 1. Например, процессор 300 может представлять собой процессор общего назначения, процессор специального назначения, может иметь архитектуру CISC, RISC, VLIW или другую архитектуру, и т.д. Для предотвращения усложнения описания, такие свойства, которые могут быть одинаковыми или аналогичными, не будут повторяться, а скорее описание будет стремиться к тому, чтобы подчеркивать разные или дополнительные свойства процессора по фиг. 3.

Процессор 300 может принимать инструкцию 304 определения длины точки упакованного кода переменной длины. Например, инструкция может быть принята из модуля выборки инструкции, из очереди инструкций и т.п. Инструкция может представлять макроинструкцию, инструкцию на уровне машинного кода, инструкцию языка ассемблера или другую инструкцию или сигнал управления из набора инструкций процессора. Инструкции могут иметь рабочий код или операционный код. Операционный код может представлять собой множество битов, или одно или больше полей, которые во время работы идентифицируют инструкцию и/или операцию, которая должна быть выполнена (например, операцию определения длины точки упакованного кода переменной длины). Инструкции также могут иметь биты или одно или больше полей для установления одного или больше источников и/или операндов назначения, как дополнительно поясняется ниже.

Представленный процессор включает в себя модуль 312 декодирования инструкции. Модуль декодирования инструкции может также называться модулем декодирования или декодером. Модуль декодирования может принимать и декодировать инструкции относительно высокого уровня или сигналы управления (например, макроинструкции, инструкции на уровне машинного кода, инструкции языка ассемблера и т.д.) и может выводить одну или больше микроинструкций, микроопераций, точек входа микрокода или другие инструкции относительно низкого уровня или сигналы управления, которые отражают, представляют и/или которые выведены из инструкций высокого уровня или сигналов управления. Одна или больше из инструкций низкого уровня или сигналов управления может быть воплощена инструкцией высокого уровня или сигналом управления через одну или больше операций низкого уровня (например, на уровне схемы или на уровне аппаратных средств). Модуль декодирования может быть осуществлен, используя всевозможные механизмы, логику или интегральные схемы, включающие в себя, но без ограничений, постоянные запоминающие устройства для микрокода (ROM), справочные таблицы, воплощения в виде аппаратных средств, массивы программируемой логики (PLA) и другие механизмы, логику или интегральные схемы, используемые для воплощения, модули декодирования, известные в области техники.

В других вариантах осуществления могут использоваться эмулятор инструкции, транслятор, морфер, интерпретатор или другая логика преобразования инструкции. Различные типы логики преобразования инструкции известны в области техники и могут быть воплощены в программных, аппаратных средствах, во встроенном программном обеспечении, или используя их комбинации. Логика преобразования инструкции может принимать инструкцию и может эмулировать, транслировать, выполнять трансформацию, интерпретировать или по-другому преобразовывать инструкцию в одну или больше соответствующие выведенные инструкции или сигналы управления. В других вариантах осуществления могут использоваться, как логика преобразования инструкции, так и модуль декодирования. Например, процессор может иметь логику преобразования инструкции для преобразования принимаемой инструкции машинного кода в одну или больше промежуточных инструкций, и модуль декодирования для декодирования одной или больше промежуточных инструкций в одной или больше инструкциях более низкого уровня, или сигналы управления, выполняемые собственными аппаратными средствами процессора (например, исполнительным модулем). Некоторые или все из логики преобразования инструкции могут быть расположены вне процессора, например, на отдельном кристалле и/или в памяти.

Процессор 300 также включает в себя набор регистров 308 упакованных данных. Каждый из регистров упакованных данных может представлять место расположения для накопителя на кристалле, который во время работы сохраняет упакованные данные, векторные данные или данные SIMD. Регистры упакованных данных могут быть воплощены по-разному в разных микроархитектурах, используя хорошо известные технологии, и не ограничены каким-либо определенным типом схемы. Различные типы регистров пригодны для этого. Примеры соответствующих типов регистров включают в себя, но не ограничены этим, специализированные физические регистры, динамически выделенные физические регистры с использованием переименования регистра, и их комбинацию.

Снова обращаясь к фиг. 3, исполнительный модуль 310 соединен с модулем 312 декодирования и с регистрами 308 упакованных данных. В качестве примера исполнительный модуль может включать в себя функциональный модуль, логический модуль, арифметический логический модуль, цифровую схему для выполнения логических и/или арифметических, и логических операций, и т.п. Исполнительный модуль может принимать одну или больше из декодированных или по-другому преобразованных инструкций или сигналы управления, которые представляют инструкцию 304 определения длины точки упакованного кода переменной длины и/или которые выведены из нее. Исполнительный модуль и/или процессор может включать в себя специфичную или конкретную логику (например, схему или другие аппаратные средства, потенциально скомбинированные со встроенным программным обеспечением и/или программным обеспечением), которая работает для выполнения операции определения длины точки упакованного кода переменной длины в ответ на и/или, как результат инструкции определения длины точки упакованного кода переменной длины (например, в ответ на одну или больше инструкций или сигналы управления, декодированные или по-другому выведенные из него).

В некоторых вариантах осуществления инструкция 304 определения длины точки упакованного кода переменной длины может в явном виде устанавливать (например, через одно или больше полей или набор битов), или по-другому обозначать (например, в скрытом виде обозначать), упакованные данные 314 первого источника. Упакованные данные первого источника могут иметь, по меньшей мере, две точки упакованного кода переменной длины знаков 315 Unicode. В одном конкретном варианте осуществления упакованные данные первого источника могут иметь часть потока непрерывно расположенных переменных точек кодов UTF-8 или кодирования для знаков Unicode, включающие в себя кодовые точки из одного байта, двух байтов, в случае необходимости, трех байтов и, в случае необходимости, четырех байтов, хотя объем изобретения не ограничен этим.

В некоторых вариантах осуществления инструкция определения длины точки упакованного кода переменной длины, в случае необходимости, может в явном виде устанавливать или по-другому обозначать упакованные данные 316 второго источника, хотя это и не требуется. Упакованные данные второго источника могут иметь, по меньшей мере, две структуры упакованной сигнатуры для разных точек кода переменной длины. В качестве альтернативы, вместо требования, чтобы инструкция обозначала упакованные данные второго источника, имеющие две или больше структур упакованной сигнатуры, эти две или больше структуры сигнатуры, в случае необходимости, могут быть сохранены в энергонезависимой памяти на кристалле, такой как, например, постоянное запоминающее устройство (ROM) на кристалле. В некоторых вариантах осуществления может присутствовать другая структура сигнатуры для каждой другой точки возможной длины кода в упакованных данных 314 первого источника. В некоторых вариантах осуществления могут присутствовать, по меньшей мере, две, в случае необходимости, три или, в случае необходимости, четыре или больше разных структур сигнатуры, в зависимости от конкретного подхода к кодированию, и каждая из которых соответствует другой точке кода переменной длины, возможного в упакованных данных 314 первого источника. Такие структуры сигнатуры могут быть, по существу, заранее определенными или могут представлять собой фиксированные значения.

В одном конкретном примерном варианте осуществления, в котором используется UTF-8, может присутствовать структура сигнатуры однобайтового UTF-8 для точки однобайтового кода UTF-8, структура сигнатуры двухбайтового UTF-8 для точки двухбайтового кода UTF-8, в случае необходимости, структура сигнатуры трехбайтового UTF-8 для точки трехбайтового кода UTF-8, и, в случае необходимости, структура сигнатуры четырехбайтового UTF-8 для точки четырехбайтового кода UTF-8, хотя объем изобретения не ограничен этим. Структуры битов сигнатуры, в случае необходимости, могут быть аналогичны тем, которые показаны и описаны выше со ссылкой на фиг. 2. Например, структура сигнатуры для точки однобайтового кода UTF-8 может иметь один бит сигнатуры в бите 7, структура сигнатуры для точки двухбайтового кода UTF-8 может иметь пять битов сигнатуры в битах [7:5] и [15:14], структура сигнатуры для точки трехбайтового кода UTF-8 может иметь восемь битов сигнатуры в битах [7:4], [15:14] и [23:22], и структура сигнатуры для точки четырехбайтового кода UTF-8 может иметь одиннадцать битов сигнатуры в битах [7:3], [15:14], [23:22] и [31:30].

В таблице 1, представленной ниже, перечислены примеры соответствующих структур сигнатуры, представленных в двоичном и шестнадцатеричном обозначениях для точек одно-четырехбайтового кода UTF-8.

В некоторых вариантах осуществления инструкции 304 определения длины точки упакованного кода переменной длины, в случае необходимости, могут иметь непосредственный операнд 318, хотя это и не требуется. Непосредственный операнд может иметь значения длины структур сигнатуры для разных точек кода переменной длины (например, которые представляют собой упакованные данные 316 второго источника). Каждое из значений длины может соответствовать разным структурам сигнатуры. Например, значения длины могут включать в себя или могут обозначать длину один байт, соответствующую структуре сигнатуры в один байт, длину два байта, соответствующую структуре сигнатуры два байта, в случае необходимости, длину три байта, соответствующую структуре сигнатуры три байта и, в случае необходимости, длину четыре байта, соответствующую структуре сигнатуры четыре байта. В других вариантах осуществления только два или только три разных значения длины могут потребоваться для конкретного воплощения. В качестве альтернативы, в других вариантах осуществления, вместо инструкции, для которой требуется непосредственный операнд, значения длины структур сигнатуры, в случае необходимости, могут быть предоставлены по-другому, например, путем сохранения в ROM на одном кристалле или в другой энергонезависимой памяти на кристалле. В качестве другого варианта выбора, значения длины, в случае необходимости, могут предоставляться другим явно установленным или неявно обозначенным операндом источника (например, могут быть предоставлены через скрытый регистр).

В некоторых вариантах осуществления инструкция определения длины точки упакованного кода переменной длины, в случае необходимости, может в явном виде устанавливать или по-другому обозначать место 320 назначения (например, место назначения сохранения), где полученные в результате упакованные данные должны быть сохранены в ответ на инструкцию 304. В некоторых вариантах осуществления полученные в результате упакованные данные могут включать в себя упакованные отрезки подтвержденных точек кода переменной длины или кодирование знаков 321 Unicode.

В некоторых вариантах осуществления исполнительный модуль может определять, соответствует ли часть данных из точек упакованного кода переменной длины знакам 315 Unicode любой из разных структур сигнатуры для разных точек 317 длины кода. Например, исполнительный модуль может сравнивать первый байт из точек упакованного кода UTF-8 переменной длины для знаков 315 Unicode с однобайтовой структурой 317 сигнатуры UTF-8, может сравнивать первые два байта из точек упакованного кода UTF-8 переменной длины знаков 315 Unicode с двухбайтовой структурой 317 сигнатуры UTF-8. В некоторых вариантах осуществления исполнительный модуль может также, в случае необходимости, сравнивать первые три байта из точек упакованного кода UTF-8 переменной длины знаков 315 Unicode с тремя байтами структуры 317 сигнатуры UTF-8 и может дополнительно, в случае необходимости, сравнивать первые четыре байта из точек упакованного кода UTF-8 переменной длины знаков 315 Unicode с четырьмя байтами структуры 317 сигнатуры UTF-8.

Если в определенной точке будет обнаружено соответствие, тогда можно предположить, что длина точки кода UTF-8 переменной длины или точки другого кода переменной длины из первых данных 314 источника была правильно определена. Это иногда называется в данной области техники подтверждением кодовой точки. В некоторых вариантах осуществления исполнительный модуль может затем сохранять подтвержденные или по-другому определенные значения длины для этих точек кода UTF-8 переменной длины или других точек кода в соответствующем положении в месте 320 назначения. Например, первый непрерывный трехбайтовый сегмент из первого источника 314 соответствует трехбайтовой структуре сигнатуры из второго источника 316, затем значение три может быть сохранено или по-другому обозначено в соответствующем положении в месте назначения для обозначения того, что соответствующая точка кода представляет собой точку трехбайтового кода. Такая обработка может повторяться для генерирования результата, который включает в себя упакованные значения длины всех удостоверенных точек кода переменной длины знаков 321 Unicode, которые могут быть удостоверены или по-другому определены в первом источнике 314.

Как показано, в некоторых вариантах осуществления, каждые из упакованных данных 314 первого источника, упакованных данных 316 второго источника и место 320 назначения могут представлять разные регистры упакованных данных. В качестве альтернативы, места расположения памяти или другие места расположения накопителя можно использовать для одного или больше из этих операндов. Например, точки упакованного кода переменной длины знаков 315 Unicode могут быть сохранены в определенном месте положения в памяти. Кроме того, один или больше операндов источников и/или мест назначения могут быть скрыты для инструкции, вместо их явного указания. В качестве другого варианта, один из операндов источника, в случае необходимости, может повторно использоваться в качестве операнда назначения, и полученные в результате упакованные данные могут быть записаны поверх упакованных данных источника. Хотя в некоторых случаях может быть желательно сохранить упакованные данные источника.

Для того, чтобы исключить усложнение описания, был представлен и описан относительно простой процессор 300. В других вариантах осуществления процессор, в случае необходимости, может включать в себя другие хорошо известные компоненты, которые можно видеть в процессорах. Примеры таких компонентов включают в себя, но без ограничений, модуль прогнозирования ветвлений, модуль выборки команды, кэш для инструкции и данных, буферы быстрого преобразования адреса для трансляции инструкции и данных, буферы упреждающей выборки, очереди микроинструкций, последовательности микроинструкций, модуль переименования регистра, модуль планировании инструкции, модули интерфейса шины, кэш второго или более высокого уровня, модуль устранения, другие компоненты, включенные в процессоры, и различные их комбинации. Существует буквально множество разных комбинаций и конфигураций компонентов в процессорах, и варианты осуществления не ограничены какой-либо конкретной их комбинацией или конфигурацией. Варианты осуществления могут быть включены в процессоры, которые имеют множество ядер, логические процессоры или механизмы исполнения, по меньшей мере, один из которых имеет исполнительную логику, действующую для выполнения варианта осуществления по инструкциям, раскрытым здесь.

На фиг. 4 показана блок-схема примерного варианта осуществления соответствующей операции 430 определения длины точки упакованного кода переменной длины для точек кода UTF-8 переменной длины. Операция может выполняться процессором или другим устройством обработки инструкции в ответ на и/или, как результат варианта осуществления инструкции определения длины точки упакованного кода переменной длины.

Инструкция может устанавливать или по-другому обозначать точки 415 упакованного кода UTF-8. Например, точки упакованного кода UTF-8 могут находиться в регистре упакованных данных или в определенном местоположении в памяти, установленном или по-другому обозначенном в инструкции. В представленном варианте осуществления точки упакованного кода UTF-8 имеют ширину 128 битов. В других вариантах осуществления, в случае необходимости, могут использоваться другие значения ширины такие как, например, 64 бита, 256 битов, 1024 бита или некоторые другие значения ширины. 128 битов являются достаточно широкими для размещения шестнадцати байтов. Шестнадцать байтов позволяют сохранять переменное количество точек кода UTF-8 переменной длины, например, каждый из которых имеет от одного до четырех байтов. В представленном примере три байта самого низкого порядка в битах [23:0] сохраняют точку 431 3-байтового кода UTF-8 для символа европейской денежной единицы (€). Четвертый байт в битах [31:24] содержит точку 432 1-байтового кода UTF-8 для знака доллар ($). Пятый и шестой байты в битах [47:32] содержат точку 433 2-байтового кода UTF-8 для знака цент (0). С седьмого по девятый байты в битах [71:48] также содержат точку 434 3-байтового кода UTF-8 для символа европейской валюты. Пятнадцатый и шестнадцатый байты в битах [127:112] содержат неполные два из трех байтов точки 435 3-х байтового кода UTF-8 для знака европейской валюты. Остальной третий байт не может попасть в пределы ограничения по ширине операнда 128-битных упакованных данных, и таким образом, только неполная часть символов представлена (например, в 128-битном регистре).

Инструкция может устанавливать или по-другому обозначать структуры упакованной сигнатуры для точек 417 кода UTF-8 разной длины. В некоторых вариантах осуществления инструкция может устанавливать регистр или другое местоположение в накопителе, имеющем структуры упакованной сигнатуры. В других вариантах осуществления структуры упакованной сигнатуры могут быть сохранены в ROM или в другой энергонезависимой памяти на кристалле. В представленном варианте осуществления показаны четыре разных структуры сигнатуры. В частности, первая структура 436 сигнатуры для однобайтовой точки кода UTF-8 сохранена в самом нижнем порядке 32-битного двойного слова в битах [31:0], вторая структура 437 сигнатуры для точки двухбайтового кода UTF-8 сохранена в следующем после самого низкого порядка 32-битного кодового слова в битах [63:32], третья структура 438 сигнатуры для точки трехбайтового кода UTF-8 сохранена в следующем 32-битном двойном слове самого высокого порядка в битах [95:64], четвертая структура 439 сигнатуры для точки четырехбайтового кода UTF-8 сохранена в 32-битном двойном слове самого высокого порядка в битах [127:96]. Первая структура сигнатуры может иметь нулевое расширение и может иметь в своем байте самого низкого порядка значение "00000000". Вторая структура сигнатуры может иметь нулевое расширение и может иметь в своих двух байтах самого низкого порядка значение "10000000 11000000". Третья структура сигнатуры может иметь нулевое расширение и может иметь в своих трех байтах самого низкого порядка значения "10000000 10000000 11100000". Четвертая структура сигнатуры может иметь нулевое расширение и может иметь в своих четырех байтах самого низкого порядка значения "10000000 10000000 10000000 11110000". Эти структуры сигнатуры, в случае необходимости, также могут быть размещены в любом другом порядке в пределах операндов. Также, в других вариантах осуществления можно использовать только две различные структуры сигнатуры (например, если предполагается использовать только точки одно- и двухбайтового кода UTF-8, но не предполагается использовать точки трех- или четырехбайтового кода UTF-8). Следует отметить, что установленные биты (то есть, бинарные биты) в структурах 417 сигнатуры также можно найти в тех же относительных положениях битов точек 415 кода UTF-8 для той же длины байтов. Например, структура сигнатуры для точки 437 двухбайтового кода UTF-8 имеет установленные биты только в битах [15:14] и [7], и точка 433 двухбайтового кода UTF-8 для знака цент, также имеет установленные биты в битах [15:14] и [7].

В некоторых вариантах осуществления инструкция может устанавливать или по-другому обозначать значения длины структур 419 сигнатуры. В этом варианте осуществления значения длины структур сигнатуры представляют собой один, два, три и четыре байта. В некоторых вариантах осуществления инструкция может иметь непосредственный операнд для предоставления этих значений длины. Например, в одном варианте осуществления, непосредственный операнд может представлять собой 8-битный непосредственный операнд, имеющий четыре 2-битных поля, каждое из которых обозначает одно из значений длины. В некоторых вариантах осуществления может использоваться так называемое соглашение "плюс один", в котором значение ноль в непосредственном операнде может использоваться, для обозначения 1 байта, значение один может использоваться для обозначения 2 байтов, значение два может использоваться для обозначения 3 байтов, и значение три может использоваться для обозначения 4 байтов, хотя это не требуется. Эти значения также, в случае необходимости, могут быть размещены в любых других порядках в пределах непосредственного операнда, если только каждый из них логически соответствует соответствующей структуре сигнатуры. В другом варианте осуществления два разных значения длины могут быть обозначены двумя 2-битными полями 4-битного непосредственного операнда. В других вариантах осуществления значения длины, в случае необходимости, могут быть сохранены в ROM или в другой энергонезависимой памяти на кристалле, вместо предоставления с использованием непосредственного операнда.

В ответ на и/или в результате инструкции, процессор может сравнивать байты из точек 415 упакованного кода UTF-8 с другими упакованными структурами сигнатуры для точек 417 кода UTF-8 разной длины. Например, первый байт в битах [7:0] точек 415 упакованного кода UTF-8 можно сравнивать со структурой 436 сигнатуры для точки 1-байтового кода UTF-8, и может быть определено, что они не соответствуют. Затем первые 2 байта в битах [15:0] точек 415 упакованного кода UTF-8 можно сравнивать со структурой 437 сигнатуры для точки 2-байтового кода UTF-8, и может быть определено, что они не соответствуют. Затем первые 3 байта в битах [23:0] точек 415 упакованного кода UTF-8 можно сравнивать со структурой 438 сигнатуры для точки 3-байтового кода UTF-8, и может быть определено, что они не соответствуют друг другу. Другими словами, может быть определено, что все установленные биты (то есть, двоичные) в структуре 438 сигнатуры также представляют собой установленные биты (то есть, двоичные) в точке 431 3-байтового кода UTF-8. Также можно определить, что биты [31:24] точек 415 упакованного кода UTF-8 представляют точку 1-байтового кода UTF-8 для знака 432 доллара, который соответствует структуре 436 сигнатуры для точки 1-байтового кода UTF-8. Также может быть определено, что биты [47-32] точек 415 упакованного кода UTF-8, которые представляют точку 2-байтового кода UTF-8 для знака 433 цент, соответствуют структуре 437 сигнатуры для точки 2-байтового кода UTF-8. Также может быть определено, что биты [71:48] точек 415 упакованного кода UTF-8, которые представляют точку 3-байтового кода UTF-8 для знака 434 европейской валюты, соответствуют структуре 438 сигнатуры для точки 3-байтового кода UTF-8. В представленном выше описании описан определенный порядок для выполнения этих сравнений, хотя следует понимать, что сравнения могут, в случае необходимости, быть выполнены в любом другом требуемом порядке, и что сравнения могут быть выполнены последовательно, параллельно или частично последовательно и частично параллельно.

Такие определения, что точки кода UTF-8 соответствуют структурам сигнатуры, представляют вариант осуществления для определения значения длины точек кода UTF-8. Значения, представляющие значения длины точек кода UTF-8, могут быть сохранены в упакованных значениях длины удостоверенных точек 421 кода UTF-8. Например, как показано, это может включать в себя сохранение значения, обозначающего длину из 3-байтов 440, соответствующую точке 431 3-байтового кода UTF-8 для первого возникновения символа евро, значение, обозначающее длину 1 байта 441, соответствующего точке 432 1-байтового кода UTF-8 для знака доллар, значение, обозначающее длину 2 байта 442, соответствующую точке 433 2-байтового кода UTF-8 для символа цент, и значение, обозначающее длину 3 байтов 443, соответствующую точке 434 3-байтового кода UTF-8 для второго возникновения символа европейской валюты. Как показано в некоторых вариантах осуществления, значения, представляющие значения длины, в случае необходимости, могут быть сохранены в тех же относительных положениях байта для байтов самого низкого порядка, соответствующих точек кода UTF-8, и все нули, в случае необходимости, могут быть сохранены в тех же относительных положениях байта или в любых более значимых байтах соответствующих точек кода UTF-8, хотя это и не требуется. В других вариантах осуществления, в случае необходимости, могут использоваться другие соглашения. Предпочтительно, такой формат проявляет тенденцию хорошего соответствия для кодирования переменной длины. Если относительно большое количество точек меньшего кода (например, точек 1 -байтового кода) будет включено во входной поток (то есть, первый источник), тогда большие значения длины могут быть сохранены в месте назначения. Например, вплоть до шестнадцати значений длины для шестнадцати соответствующих 1-байтовых знаков (например, точек кода UTF-8 для знаков ASCII) могут быть сохранены в месте назначения.

На фиг. 4 был представлен и описан определенный порядок компоновки байтов точек кода UTF-8. Однако, также возможны другие способы организации или размещения байтов в операндах или регистрах. Также пригодны любые известные обычные способы размещения байтов в точках кода UTF-8.

На фиг. 5 показана блок-схема последовательности операций варианта осуществления способа 550, выполняемого процессором и/или выполняемого в пределах процессора при обработке варианта осуществления инструкции определения длины точки упакованного кода переменной длины. В некоторых вариантах осуществления операция и/или способ на фиг. 5 могут быть выполнены процессором и/или в пределах процессоров, показанных на фиг. 1 и/или фиг. 3. Компоненты, свойства и конкретные дополнительные детали, описанные здесь для процессоров на фиг. 1 и/или фиг. 3 также, в случае необходимости, применяют для операций и/или способа на фиг. 5, который может быть выполнен в вариантах осуществления, используя и/или находясь в пределах таких процессоров. В качестве альтернативы, операции и/или способ по фиг. 5 могут быть выполнены с помощью и/или в пределах аналогичных или других процессоров, или другого устройства. Кроме того, процессоры на фиг. 1 и/или на фиг. 3 могут выполнять операции и/или способы, которые являются такими же как, аналогичными или другими, чем представлены на фиг. 5.

Способ включает в себя: принимают инструкция определения длины точки упакованного кода переменной длины, в блоке 551. В других аспектах инструкция может быть принята в процессоре или в его части (например, в модуле выборки инструкции, в модуле декодирования и т.д.). В различных аспектах инструкция может быть принята из источника, находящегося за пределами кристалла (например, из основной памяти, диска или через взаимное соединение), или из источника, находящегося на кристалле (например, из кэш инструкции). В некоторых вариантах осуществления инструкция определения длины точки упакованного кода переменной длины может в явном виде устанавливать или по-другому обозначать упакованные данные из первого источника, имеющие множество точек упакованного кода переменной длины, каждая из которых представляет знак, и может в явном виде устанавливать или по-другому обозначать местоположения назначения сохранения.

Полученные в результате упакованные данные могут быть сохранения в обозначенном местоположении сохранения назначения в ответ на и/или как результат инструкции определения длины точки упакованного кода переменной длины, в блоке 552. В некоторых вариантах осуществления полученные в результате упакованные данные могут включать в себя значения длины для каждой из множества точек упакованного кода переменной длины. В некоторых вариантах осуществления полученные в результате упакованные данные могут иметь любую из ранее описанных характеристик упакованных длин 321 на фиг. 3 и/или упакованных длин 421 на фиг. 4.

Для того, чтобы дополнительно иллюстрировать определенные концепции, рассмотрим подробный пример варианта осуществления инструкции определения длины точки упакованного кода переменной длины с пневмоником VPVLNCPCLSFL. Формат инструкции может представлять собой VPVLNCPCLSFL DEST, SRC1, SRC2, IMM8. DEST может представлять регистр мета назначения упакованных данных шириной 128 битов. SRC1 может представлять собой регистр упакованных данных шириной 128 битов из первого источника или места в памяти. SRC2 может представлять собой второй регистр упакованных данных шириной 128 битов из второго источника. IMM8 может представлять 8-битный непосредственный операнд.

SRC1 может сохранять часть потока UTF-8, представляющую кодированную последовательность байтов UTF-8. SRC2 может сохранять вплоть до четырех разных структур сигнатуры, соответствующих формату кодирования UTF-8 для каждого из четырех разных значений длины точек кода UTF-8 (например, один, два, три и четыре байта). Например, каждая из этих четырех разных структур сигнатуры может быть сохранена в различных элементах данных 32-битного двойного слова. IMM8 может включать в себя четыре 2-битных поля. Каждое 2-битное поле может представлять кодирование длины соответствующей структуры сигнатуры, например, в соглашении "один плюс", в котором единицу добавляют к длине, кодированной для определения фактической длины байта. Другой вариант осуществления описанной выше инструкции может исключать операнд SRC2 второго источника и непосредственный операнд IMM8, и, вместо этого, может предоставлять структуры сигнатуры, и их соответствующие значения длины через ROM или другую энергонезависимую память на кристалле.

Инструкция может использоваться для удостоверения и определения длины в байтах каждой удостоверенной точки кода UTF-8 из SRC1, и также для идентификации смещения первой неполной точки кода UTF-8 в SRC1. Это смещение может быть полезным для определения начала следующей части кода UTF-8 для обработки (например, с последующей инструкцией). Каждую точку кода из SRC1 можно сравнивать с, по меньшей мере, двумя и вплоть до четырех различными структурами сигнатуры, соответствующими разным значениям длины из SRC2. Если точка кода из SRC1 соответствует структуре сигнатуры из SRC2, тогда положение ведущего байта DEST может сохранять заданное значение длины точки кода, которая равна длине структуры сигнатуры и известной из IMM8 (например, один, два, три или четыре). Если определенная длина точки кода больше, чем единица, все следующие оставшиеся байты точки кода в DEST могут быть заполнены нулями (например, 00000000).

В некоторых вариантах осуществления, если ни одна из четырех структур сигнатуры в SRC2 не соответствует точке кода в SRC1, тогда соответствующий ведущий байт точки кода DEST может, в случае необходимости, быть заполнен всеми единицами (например, 11111111). Это необязательно, но может помочь для маркировки или обозначения недействительных или недостоверных точек кода. Это также может помочь для идентификации смещения первой неполной и/или недействительной точки кода UTF-8 в SRC1 (например, для обработки последующей инструкции). Например, в процессорах архитектуры Intel (ΙΑ), такая идентификация может быть выполнена при использовании инструкции PMOVMSKB. Например, результат PMOVMSKB может быть проверен, и младший значащий установленный бит результата PMOVMSKB может обозначать значение смещения первой неполной и/или недействительной точки кода UTF-8 в SRC1. Если результат PMOVMSKB, выполняемый DEST, равен нулю, тогда все 16 байтов во входном потоке UTF-8 могут рассматриваться, как действительные кодовые точки. В качестве альтернативы, некоторое другое соответствующее распознанное значение, помимо всех единиц (например, 11111111), в таких ситуациях, в случае необходимости, может быть сохранено в DEST. В других вариантах осуществления, в случае необходимости, могут использоваться более широкие или более узкие регистры. Например, в различных вариантах осуществления могут использоваться 64-битные, 256-битные, 512-битные или 1024-битные регистры для SRC1 и/или SRC2 и/или DEST.

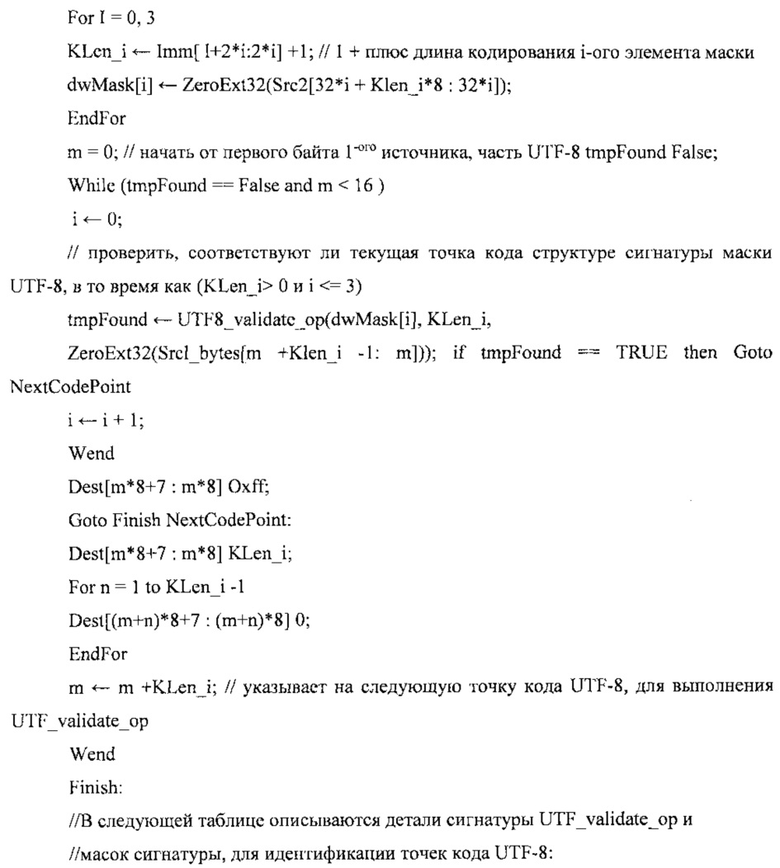

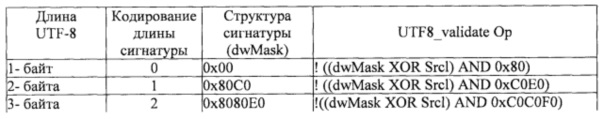

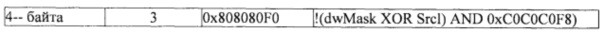

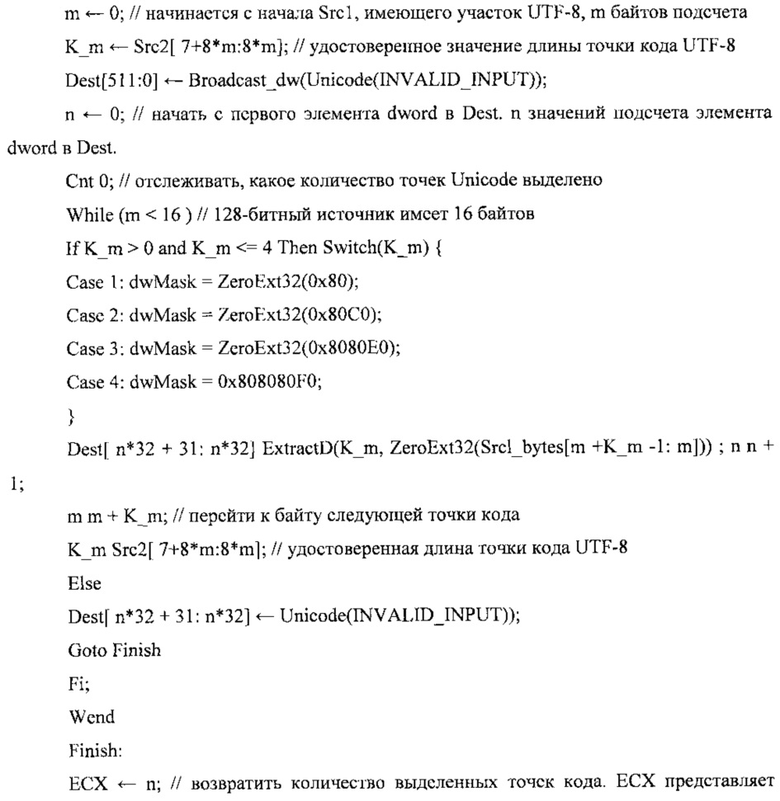

Следующий псевдокод представляет другой примерный вариант осуществления соответствующей инструкции определения длины точки упакованного кода переменной длины. В этом псевдокоде Src1 представляет первый источник, имеющий набор или последовательность точек кода UTF-8, Src2 представляет операнд второго источника, имеющий четыре сигнатуры для точек от одного до четырехбайтового кода UTF-8, Imm представляет 8-битный непосредственный операнд, и Dest представляет место назначения. ZeroExt32 представляет нулевое расширение для 32-битной функции.

На фиг. 6 показана блок-схема варианта осуществления процессора 600, который работает для исполнения или обработки варианта осуществления битов инструкции 606 выделения знака точки упакованного кода переменной длины (например, битов Unicode). Процессор 600, в случае необходимости, может иметь любую из характеристик или атрибутов процессора 100 по фиг. 1 и/или процессора 300 на фиг. 3. Например, процессор 600 может представлять собой процессор общего назначения, процессор специального назначения может иметь архитектуру CISC, RISC, VLIW или другую архитектуру, модуль декодирования может быть таким же или аналогичным, и т.д. Для того чтобы не усложнять описание, эти особенности, которые могут быть такими же или аналогичными, не будут повторяться, а скорее в описании просматривается тенденция разъяснять другие или дополнительные свойства процессора 600 на фиг. 6.

Процессор 600 может принимать инструкцию 606 в виде выделения битов знака точки упакованного кода переменной длины (например, биты Unicode). Биты Unicode, предназначенные для выделения, представляют те биты кодирования переменной длины, которые позволяют получить знак Unicode или его значение (например, знак Unicode может быть определен на основе только полного набора битов Unicode, предназначенного для выделения). Биты Unicode представляют вариант осуществления знака или битов данных, которые должны быть выделены, и другие варианты осуществления не ограничены битами Unicode. Инструкция может иметь код операции или опкод, который во время работы идентифицирует инструкцию и/или операцию для выполнения (например, операцию выделения битов Unicode точки упакованного кода переменной длины). Представленный процессор включает в себя модуль 612 декодирования инструкции, который может быть аналогичен или может быть таким же, как модуль 312 декодирования. Как описано ранее, в случае необходимости, может также использоваться логика преобразования инструкции. Процессор 600 также включает в себя набор регистров 608 упакованных данных, который может быть аналогичен или может быть таким же, как регистры 308 упакованных данных. Исполнительный модуль 610 соединен с модулем 312 декодирования и с регистрами 308 упакованных данных. Исполнительный модуль 610 может быть аналогичным или может быть таким же, как и исполнительный модуль 310. Исполнительный модуль и/или процессор может включать в себя определенную или конкретную логику (например, схему или другие аппаратные средства, потенциально скомбинированные со встроенным программным обеспечением и/или программным обеспечением), которое во время работы выполняет операцию выделения битов Unicode точки упакованного кода переменной длины в ответ на и/или в результате инструкции 606 (например, в ответ на одну или больше инструкций или декодированных сигналов управления или по-другому выведенных из инструкции 606).

В некоторых вариантах осуществления инструкция 304 выделения битов знака точки упакованного кода переменной длины (например, биты Unicode) может в явном виде устанавливать (например, через одно или больше полей или набор битов), или по-другому обозначать (например, обозначать в неявном виде), упакованные данные 614 первого источника. Упакованные данные первого источника могут иметь, по меньшей мере, две точки упакованного кода переменной длины в виде знаков 615 Unicode. В одном конкретном варианте осуществления упакованные данные первого источника могут иметь участок потока последовательных точек переменных кодов UTF-8 или могут составлять кодирование для знаков Unicode, включающих в себя однобайтовые, двухбайтовые, в случае необходимости, трехбайтовые и, в случае необходимости, четырехбайтовые кодовые точки, хотя объем изобретения не ограничен этим. В некоторых вариантах осуществления точки 615 упакованного кода переменной длины могут быть аналогичными или могут быть такими же, как и точки 315 упакованного кода переменной длины, используемые для инструкции 304 определения длины точки упакованного кода переменной длины по фиг. 3. Например, та же последовательность точек кода может вначале быть обработана инструкцией 304 на фиг. 3, и затем может быть обработана инструкцией 606 на фиг. 6.

В некоторых вариантах осуществления, инструкция выделения битов знака точки упакованного кода переменной длины (например, биты Unicode) может в явном виде устанавливать или по-другому обозначать упакованные данные 616 второго источника. В некоторых вариантах осуществления упакованные данные второго источника могут иметь две или больше упакованные длины точек удостоверенного кода переменной длины знаков 621 Unicode. Например, в некоторых вариантах осуществления упакованные длины точек удостоверенного кода переменной длины знаков 621 Unicode могут содержать два или больше значения, обозначающие значения длины двух или больше соответствующих точек кода UTF-8, как 1-байтовое, 2-байтовое, или, в случае необходимости, 3-байтовое или 4-байтовое (например, в вариантах осуществления, в которых используются 3-байтовые или 4-байтовые точки кода UTF-8). Например, в варианте осуществления, в котором используется UTF-8, значения упакованной длины точек удостоверенного кода переменной длины знаков Unicode 621 могут содержать значение (например, три), для обозначения длины 3 байта для соответствующей точки кода UTF-8, представляющей символ евро, значение (например, один), для обозначения длины 1 байт, для соответствующей точки кода UTF-8, представляющей знак доллар, и так далее.

В некоторых вариантах осуществления значения 621 упакованной длины могут представлять результат, сохраненный в ответ на вариант осуществления инструкции 104 выделения битов знака точки упакованного кода переменной длины (например, битов Unicode). Таким образом, в некоторых вариантах осуществления результат инструкции 104 может использоваться, как операнд источника инструкцией 606. Например, в некоторых вариантах осуществления, значения 621 упакованной длины могут быть аналогичны или могут быть такими же, как и значения 321 упакованной длины на фиг. 3 и/или значения 421 упакованной длины на фиг. 4. Любые из свойств и характеристик, описанных для значений 321 упакованной длины и/или значения 421 упакованной длины, также, в случае необходимости, применимы к значениям 621 упакованной длины. В качестве альтернативы, другие типы значений упакованной длины удостоверенных точек кода переменной длины знаков 621, в случае необходимости, можно использовать вместо этого, и они не ограничены генерированием инструкции 104 определения длины точки упакованного кода переменной длины. Некоторые варианты осуществления не ограничены знаками Unicode, а скорее могут использовать другие знаки или стандарты. Некоторые варианты осуществления не ограничены UTF-8, а скорее могут использовать другое кодирование переменной длины, помимо UTF-8.

В некоторых вариантах осуществления инструкция 606 выделения битов Unicode точки упакованного кода переменной длины, в случае необходимости, могут в явном виде устанавливать или по-другому обозначать место назначения 620 (например, место назначения накопителя), где полученные в результате упакованные данные должны быть сохранены в ответ на инструкцию 606. В качестве другой опции, один из источников можно повторно использовать, как место назначения, и данные источника могут быть перезаписаны результатом. В некоторых вариантах осуществления упакованные наборы выделенных битов 660 Unicode могут быть сохранены в месте назначения. Каждый набор выделенных упакованных битов Unicode может соответствовать разным соответствующим точкам кода переменной длины из первого источника 614. Каждый набор выделенных битов Unicode может включать в себя или может представлять те биты из соответствующих точек кода переменной длины, которые составляют значение Unicode или другое значение знака/символа. Набор выделенных битов Unicode может быть достаточным сам по себе для определения или транскодирования значения Unicode. В некоторых вариантах осуществления биты Unicode могут быть выделены путем логического вычитания, или по-другому удаления битов сигнатуры из соответствующих точек кода переменной длины, хотя объем изобретения не ограничен этим. Например, одна или больше логических операций может использоваться для удаления структуры сигнатуры из соответствующих точек кода переменной длины. В некоторых вариантах осуществления любая из ранее описанных структур сигнатуры может использоваться с этой целью. В других вариантах осуществления операция выделения отдельных битов на уровне бита может выполняться без таких логических операций, например, используя мультиплексоры и т.д. Следует понимать, что обработка выделения может перемещать, изменять компоновку, может перегруппировать, может выполнять конкатенацию или по-другому может манипулировать с выделенными битами Unicode различными, отличающимися друг от друга способами, если только инструкции и/или наборы инструкций, используемые для обработки выделенных битов Unicode, позволяют понять и использовать такие манипуляции. Без ограничения, такие упакованные наборы выделенных битов Unicode можно впоследствии обрабатывать одной или больше другими инструкциями для преобразования их в значения Unicode или другие форматы знаков.

Как показано, в некоторых вариантах осуществления, каждые из упакованных данных 614 первого источника упакованных данных 616 второго источника, и место 620 назначения могут представлять разный регистр упакованных данных. В качестве альтернативы, расположение в памяти или другие места расположения в накопителе можно использовать для одного или больше из таких операндов. Например, точки упакованного кода переменной длины для знаков 615 Unicode, в случае необходимости, вместо этого, могут быть сохранены в определенном месте расположения в памяти. Кроме того, один или больше операндов источников и/или мест назначения может, в случае необходимости, быть неявным для инструкции, вместо его явного установления. В качестве другого варианта, один из первого и второго операндов источника, в случае необходимости, можно повторно использовать, как операнд места назначения, и полученные в результате упакованные данные могут быть записаны поверх упакованных данных источника.

В некоторых вариантах осуществления количество выделенных 664 точек кода, в случае необходимости, могут также быть сохранены в ответ на и/или как результат инструкции 606 выделения битов Unicode точки упакованного кода переменной длины, хотя это и не требуется. Количество выделенных точек кода может представлять общее количество удостоверенных точек кода в первом операнде 614 источнике, для которого были выделены биты Unicode. Например, если первый операнд источника имеет шестнадцать удостоверенных 1-байтовых точек кода, тогда количество выделенных точек кода также может быть равно шестнадцати. В некоторых вариантах осуществления инструкция может в явном виде устанавливать или в неявном виде обозначать второе место 662 назначения, где количество выделенных точек 664 кода должно быть сохранено. Например, в одном варианте осуществления, инструкция может в неявном виде обозначать регистр общего назначения, хотя объем изобретения не ограничен этим.

На фиг. 7 показана блок-схема примерного варианта осуществления соответствующей операции 766 выделения битов Unicode точек упакованного кода UTF-8, для точек кода UTF-8. Операция может быть выполнена процессором или другим устройством обработки инструкции в ответ на и/или как результат примерного варианта осуществления инструкции выделения битов Unicode точки упакованного кода UTF-8.

Инструкция может устанавливать или по-другому обозначать точки 715 упакованного кода UTF-8. Например, точки упакованного кода UTF-8 могут находиться в регистре упакованных данных или в определенном местоположении памяти, которые установлены или по-другому обозначены инструкцией. В иллюстрируемом варианте осуществления операнд точек упакованного кода UTF-8 имеет ширину 128 битов. В других вариантах осуществления другие значения ширины, в случае необходимости, можно использовать, такие как, например, 64 бита, 256 битов, 1024 бита или некоторые другие значения ширины. Ширина 128 битов имеет шестнадцать байтов. Шестнадцать байтов позволяют сохранить переменное количество точек кода UTF-8 переменной длины, например, каждый из которых имеет от одного до двух байтов, от одного до трех байтов или от одного до четырех байтов, в зависимости от варианта осуществления. В представленном примере три байта самого низкого порядка в битах [23:0] содержат точку 731 3-байтового кода UTF-8 для символа европейской валюты (€). Четвертый байт в битах [31:24] содержит точку 732 1 - байтового кода UTF-8 для символа доллар ($). Пятый и шестой байты в битах [47:32] содержат точку 733 2-байтового кода UTF-8 для знака цент (0). В с седьмого по девятый байтах, в битах [71:48] также содержится точка 734 3-байтового кода UTF-8 для символа европейской валюты. В пятнадцатом и шестнадцатом байтах, в битах [127:112] содержатся неполные два из трех байтов точки 735 3-байтового кода UTF-8 для символа европейской валюты. Оставшийся третий байт не может быть установлен в пределах ограничения ширины 128-битов операнда, и поэтому только неполная часть символа присутствует (например, в 128-битном регистре). Конечно, здесь представлены исключительно примерные типы точек кода.

Инструкция также может устанавливать или по-другому обозначать упакованные значения длины удостоверенных точек 721 кода UTF-8. В представленном варианте осуществления операнд точек упакованного кода UTF-8 также имеет ширину 128 битов. В других вариантах осуществления другие значения ширины, в случае необходимости, могут использоваться, такие как, например, 64 бита, 256 битов, 1024 бита или некоторое другое значение ширины. Представленные значения 721 упакованной длины имеют значение, обозначающее длину 3 байта 740, соответствующую точке 731 3-байтового кода UTF-8 для первого возникновения символа евро, значение, обозначающее длину 1 байт 741, соответствующую точке 732 1-байтового кода UTF-8 для знака доллар, значение, обозначающее длину 2 байта, соответствую точке 742 2-байтового кода UTF-8 733 для символа цент, и значение, обозначающего длину 3 байта 743, соответствующее точке 734 3-байтового кода UTF-8 для второго возникновения символа европейской валюты. Как показано, в некоторых вариантах осуществления, значения, представляющие значения длины, в случае необходимости, могут быть сохранены в тех же относительных положениях байта для байтов самого низкого порядка соответствующих точек кода UTF-8, и все нули могут быть, в случае необходимости, сохранены в тех же относительных положениях байтов для любых более значимых байтов соответствующих точек кода UTF-8, хотя это и не требуется. В других вариантах осуществления, в случае необходимости, могут использоваться другие соглашения (например, нули могут быть сохранены в младшем значащем байте (байтах) и значения длины в старшем значащем байте и т.д.). Следует отметить, что в некоторых вариантах осуществления такое же количество байтов используется для упакованных значений 721 длины, как используется для соответствующих точек кода в точках 715 упакованного кода UTF-8 (например, три байта в каждом, два байта в каждом и т.д.).

В ответ на и/или как результат инструкции выделения битов Unicode точек упакованного кода UTF-8, наборы упакованных выделенных битов 760 Unicode могут быть сохранены в установленном или по-другому обозначенном месте назначения. Как показано, в некоторых вариантах осуществления, операнд назначения может представлять собой операнд шириной 512 битов (например, регистр шириной 512 битов, два регистра 256 битов, четыре регистра 128 битов и т.д.). В других вариантах осуществления, в случае необходимости, могут использоваться другие значения ширины. Каждый набор упакованных выделенных битов Unicode может соответствовать другой соответствующей точке кода переменной длины из точек 715 упакованного кода UTF-8. Каждый набор выделенных битов Unicode может включать в себя или может представлять собой те биты соответствующей точки кода переменной длины, которые сопоставляют значение Unicode или другое значение знака/символа. Набор выделенных битов Unicode может быть достаточен сам по себе для определения или транскодирования значения Unicode. В некоторых вариантах осуществления биты Unicode могут быть выделены путем логического вычитания или другого удаления битов сигнатуры и/или структур из соответствующих точек кода переменной длины, хотя объем изобретения не ограничен этим. Например, в некоторых вариантах осуществления, инструкция может обозначать две или больше структуры сигнатуры, соответствующая структура сигнатуры может быть выбрана на основе соответствующей информации длины из значений 721 упакованной длин, и одна или больше логических операций действия могут использоваться для удаления выбранной структуры сигнатуры из соответствующей точки кода переменной длины. Ранее описанные структуры сигнатуры являются соответствующими. В некоторых вариантах осуществления множество структур сигнатуры может быть сохранено в ROM или в другой энергонезависимой памяти на кристалле. В качестве альтернативы, инструкция может устанавливать или может обозначать операнд, имеющий множество структур сигнатуры. В других вариантах осуществления, вместо использования такой структуры сигнатуры, выделения на уровне бита могут быть выполнены аппаратными средствами, например, по линиям передачи, через мультиплексоры и т.д.

И снова обращаясь к фиг. 7, упакованные наборы выделенных битов 760 Unicode включают в себя первый набор выделенных битов 767 Unicode в битах [31:0], которые соответствуют точке 3-байтового кода UTF-8 для первого случая символа 731 евро, и второй набор выделенных битов 768 Unicode в битах [63:32], которые соответствует точке 1-байтового кода UTF-8 для знака 732 доллар. Наборы выделенных битов Unicode также включают в себя третий набор выделенных битов 769 Unicode в битах [95:64], которые соответствуют 2-байтовой точке кода UTF-8 для знака 733 цент, и четвертый набор выделенных битов 770 Unicode в битах [127:96], которые соответствуют 3-байтовой точке кода UTF-8 для второго случая знака 734 евро. На иллюстрации подчеркивание используется для того, чтобы представить, что биты сигнатуры или структуры сигнатуры, так, как они выглядят в точках 715 упакованного кода UTF-8, были удалены из упакованных наборов выделенных битов 731 Unicode. Таким образом, подчеркнутые установленные биты (то есть, двоичные), были преобразованы в подчеркнутые очищенные биты (то есть, двоичный ноль). Другие наборы выделенных битов Unicode также могут быть включены, если существуют другие действительные точки кода UTF-8 в точках 715 упакованного кода UTF-8. Например, вплоть до шестнадцати наборов выделенных битов Unicode, каждый из них сохранен в 32-битном элементе dword 512-битного операнда места назначения, могут быть сохранены в случае, когда упакованные точки 715 кода UTF-8 включают в себя шестнадцать 1-байтовых точек кода UTF. Как показано, в некоторых вариантах осуществления, остаточная ширина операнда назначения может содержать недействительные значения, которые могут представлять собой или могут не представлять собой заданные значения, распознаваемые соответствующими стандартами, как содержащие недействительное значение или недействительные данные (например, не распознанные значения знака Unicode).

На фиг. 8 показана блок-схема, иллюстрирующая соответствующие способы размещения или упорядочивания наборов выделенных битов Unicode в элементе упакованных данных, который может использоваться вариантами осуществления инструкциями/операциями выделения битов Unicode точки упакованного кода переменной длины. Здесь показана точка 3-байтового кода UTF-8 для символа 831 евро. В некоторых вариантах осуществления соответствующий набор выделенных битов Unicode может быть размещен или упорядочен в порядке 872 от младшего к старшему байтам в элементе данных упакованного результата и/или операнда места назначения. Это аналогично подходу, представленному и описанному выше со ссылкой на фиг. 7. В качестве альтернативы, в некоторых вариантах осуществления, соответствующий набор выделенных битов Unicode может быть размещен или упорядочен в порядке 874 от старшего к младшему байтам в элементе упакованного результата и/или операнда места назначения. В некоторых вариантах осуществления такой подход может помочь способствовать последующей обработке, будучи размещенным в формате, который хорошо подходит для определенных инструкций. Однако этот подход не требуется.

На фиг. 9 показана блок-схема последовательности операций варианта осуществления способа 978, выполняемого процессором и/или внутри процессора при обработке варианта осуществления инструкции выделения битов Unicode точки упакованного кода переменной. В некоторых вариантах осуществления операции и/или способ по фиг. 9 могут выполняться процессором и/или внутри процессора по фиг. 1 и/или по фиг. 6. Компоненты, свойства и конкретные необязательные детали, описанные здесь для процессоров на фиг. 1 и/или фиг. 6, также, в случае необходимости, применяются для операций и/или способа на фиг. 9, и эти варианты осуществления могут выполняться процессорами и/или внутри таких процессоров. В качестве альтернативы, операции и/или способ на фиг. 9 могут быть выполнены процессорами и/или внутри аналогичных или других процессоров или других устройств. Кроме того, процессоры на фиг. 1 и/или фиг. 6 могут выполнять операции и/или способы, которые являются такими же, как или аналогичными, или другими, чем те, которые показаны на фиг. 9.

Способ включает в себя: принимают инструкция выделения битов знака точки упакованного кода переменной длины в блоке 979. В различных аспектах инструкция может быть принята в процессоре или его части (например, в модуле выборки инструкции, модуле декодирования и т.д.). В различных аспектах инструкция может быть принята из источника, находящегося вне кристалла (например, из основной памяти, диска или через взаимное соединение), или из источника на кристалле (например, из кэш инструкции). В некоторых вариантах осуществления инструкция выделения битов знака точки упакованного кода переменной длины может в явном виде устанавливать или по-другому обозначать упакованные данные первого источника, имеющие множество точек упакованного кода переменной длины, каждый из которых представляет знак. Инструкция может также в явном виде устанавливать или по-другому обозначать упакованные данные второго источника, имеющие упакованные значения длины удостоверенных точек кода переменной длины из упакованных данных первого источника. Инструкция также может в явном виде устанавливать или по-другому обозначать место положения накопителя места назначения. Это включает в себя, в некоторых случаях, повторное использование одного из источников в качестве места назначения.

Получаемые в результате упакованные данные могут быть сохранены в обозначенном месте положения в накопителе места назначения в ответ на и/или в результате инструкции выделения битов знака точки упакованного кода переменной длины, в блоке 980. В некоторых вариантах осуществления получаемые в результате упакованные данные могут иметь наборы упакованных битов выделенного знака. Каждый набор выделенного знака может соответствовать другой одной из удостоверенных точек кода переменной длины из упакованных данных первого источника. В некоторых вариантах осуществления каждый набор выделенных битов знака может быть достаточным для определения знака, представленного точками кода переменной длины. В некоторых вариантах осуществления полученные в результате упакованные данные могут быть аналогичны или могут быть такими же, как и, в случае необходимости, могут иметь любую из характеристик или свойства упакованных наборов выделенных битов 660 по фиг. 6 и/или упакованных выделенных битов 760 Unicode по фиг. 7.

Для того, чтобы дополнительно иллюстрировать определенные концепции, рассмотрим подробный примерный вариант осуществления инструкции выделения битов Unicode точки упакованного кода UTF-8 с пневмоником VPVLNEXTRD. Формат инструкции может представлять собой VPVLNEXTRD DEST, SRC1, SRC2. DEST может представлять регистр упакованных данных назначения шириной 512 битов. SRC1 может представлять первый регистр упакованных данных источника шириной 128 битов или местоположение в памяти. SRC2 может представлять второй регистр упакованных данных источника шириной 128 битов. Таким образом, в некоторых вариантах осуществления DEST может быть, по меньшей мере, в четыре раза шире, чем каждый из SRC1 и SRC2. SRC1 может содержать часть потока UTF-8, представляющую кодируемую последовательность байта UTF-8. SRC2 может содержать упакованные значения длины, соответствующие удостоверенным точкам кода UTF-8 из SRC1.