Область техники, к которой относится изобретение

Настоящее изобретение относится, в общем, к архитектуре процессора компьютера и, более конкретно, к модулю сопроцессора кэша.

Уровень техники

Набор команд или структура набора команд (ISA) представляет собой часть архитектуры компьютера, относящуюся к программированию, и может содержать различные виды внутренних данных, команды, архитектуру регистров, режимы адресации, архитектуру памяти, обработку прерываний и особых ситуаций, а также внешний ввод и вывод (I/O). Следует отметить, что термин команда здесь обычно относится к макрокоманде, т.е. команде, направляемой в процессор для выполнения, в отличие от микрокоманды или микрооперации, являющихся результатом декодирования макрокоманд посредством декодера процессора.

Структура набора команд отличается от микроархитектуры, представляющей собой внутреннюю конструкцию процессора, реализующего структуру ISA. Процессоры с различными микроархитектурами могут использовать общий набор команд. Набор команд содержит один или более форматов команд. Конкретный набор команд определяет разнообразные поля (число битов, расположение битов) для спецификации, помимо всего прочего, операции, которую нужно выполнить, и операнд(ы), над которыми должна быть выполнена эта операция. Конкретную команду представляют с использованием конкретного формата команд, и эта команда определяет и операцию, и операнд(ы). Поток команд представляет собой определенную последовательность команд, где каждая команда в последовательности является событием команды в некоем формате команды.

Разного рода научные, финансовые приложения, автоматически векторизуемые приложения общего назначения, приложения RMS (распознавание, анализ и синтез)/визуальные и мультимедийные (например, 2D/3D графика, обработка изображения, сжатие/расширение видео, алгоритмы распознавания речи и манипуляции со звуком) приложения часто требуют, чтобы одна и та же операция была выполнена над большим числом элементов данных (именуется «параллелизмом данных»). Название «одна команда, множество данных» (SIMD) обозначает тип команд, в соответствии с которыми процессор выполняет одну и ту же операцию применительно к множеству объектов данных. Технология SIMD специально приспособлена для процессоров, способных разбивать биты в регистре на некоторое число элементов данных фиксированного размера, каждый из которых представляет отдельную величину. Например, биты в 64-битовом регистре могут быть определены как операнд-источник, работать с которым следует как с четырьмя отдельными 16-битовыми элементами данных, каждый из которых представляет отдельную 16-битовую величину. В качестве другого примера, биты в 256-битовом регистре могут быть определены как операнд-источник, работать с которым следует как с четырьмя отдельными 64-битовыми упакованными элементами данных (элементы данных размером со счетверенное слово (Q)), восемью отдельными 32-битовыми упакованными элементами данных (элементы данных размером со сдвоенное слово (D)), шестнадцатью отдельными 16-битовыми упакованными элементами данных (элементы данных размером в одно слово (W)) или тридцатью двумя отдельными 8-битовыми элементами данных (элементы данных размером в один байт (В)). Данные такого типа именуются данными упакованного типа (упакованными данными) или данными векторного типа (векторными данными), а операнды данных такого типа называются операндами упакованных данных или векторными операндами. Другими словами термином «объект упакованных данных» или «вектор» обозначают последовательность упакованных элементов, а операнды такого типа именуются операндами упакованных данных или векторными операндами. Другими словами, термин «упакованный объект данных» или «вектор» обозначает последовательность упакованных элементов данных; а операнд упакованных данных или векторный операнд является операндом-источником или операндом-адресатом для SIMD-команды (также называемой «команда для упакованных данных» или «векторная команда»).

Операция транспонирования является общеупотребительной элементарной операцией (примитивом) для векторного программного обеспечения. Хотя некоторые структуры наборов команд имеют команды для осуществления операции транспонирования, эти команды обычно производят перетасовку и перестановку, что требует дополнительных издержек, чтобы задать маски управления перетасовкой с использованием битов непосредственной адресации или с использованием отдельного векторного регистра, увеличивая тем самым нагрузку команд и увеличивая размеры. Кроме того, операции перетасовки в некоторых структурах наборов команд являются 128-битовыми операциями. В результате для осуществления операции полного транспонирования применительно к 256-битовому регистру или 512-битовому регистру (например) необходимо сочетание перетасовок и перестановок.

Программные приложения расходуют значительную долю времени на операции загрузки (LD) и сохранения (ST) в памяти, причем число операций загрузки обычно более чем вдвое превосходит число сохранений в памяти. Некоторые функции, требующие многочисленных операций загрузки и сохранения, почти не требуют вычислений - это, например, очистка памяти, копирование памяти, транспонирование; а другие используют незначительный объем вычислений - это например, вычисление скалярного произведения матриц, суммирование массивов и т.п. Каждая операция загрузки или операция сохранения требует использования ресурсов ядра (например, станций резервации (RS), буфера переупорядочения (ROB), буферов заполнения и т.п.).

Краткое описание чертежей

Настоящее изобретение иллюстрируется примером и не ограничивается прилагаемыми чертежами, на которых подобные позиционные обозначения присвоены аналогичным элементам и на которых:

фиг. 1 иллюстрирует пример выполнения команды транспонирования согласно одному из вариантов;

фиг. 2 иллюстрирует другой пример выполнения команды транспонирования согласно одному из вариантов;

фиг. 3 представляет логическую схему, иллюстрирующую пример операций транспонирования элементов данных в векторном регистре или в позиции памяти путем выполнения одной команды транспонирования согласно одному из вариантов;

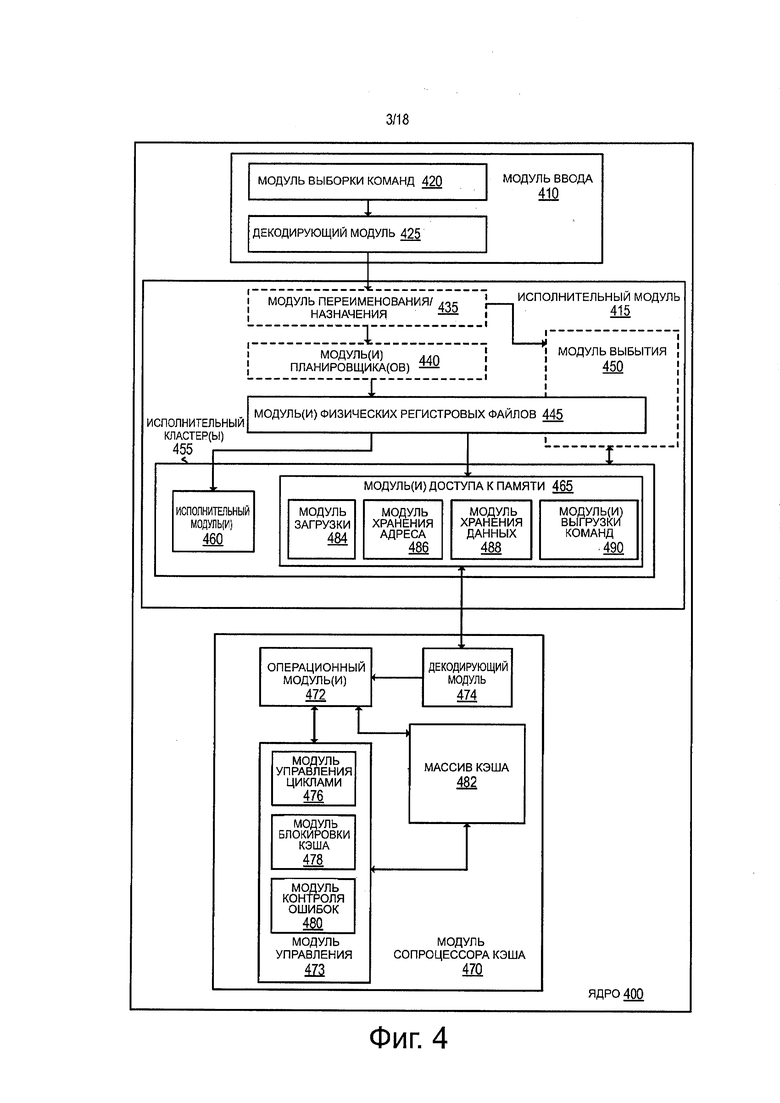

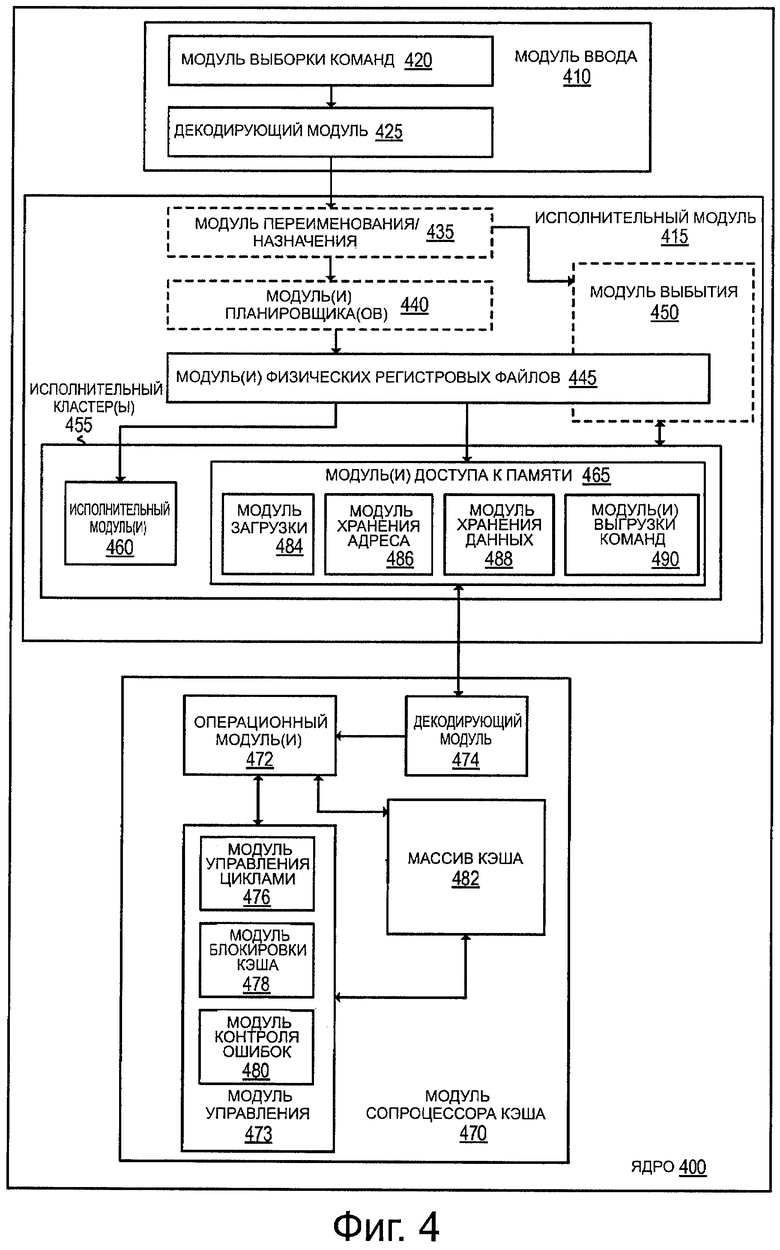

фиг. 4 представляет блок-схему, иллюстрирующую пример варианта ядра с архитектурой выполнения команд по порядку и пример ядра архитектуры с выдачей/выполнением команд не по порядку и переименованием регистров, содержащего пример модуля сопроцессора кэша, выполняющего команды, которые были выгружены, чтобы их не выполнял исполнительный кластер процессорного ядра, согласно одному из вариантов;

фиг. 5 представляет блок-схему, иллюстрирующую пример операций для выполнения выгруженной команды согласно одному из вариантов;

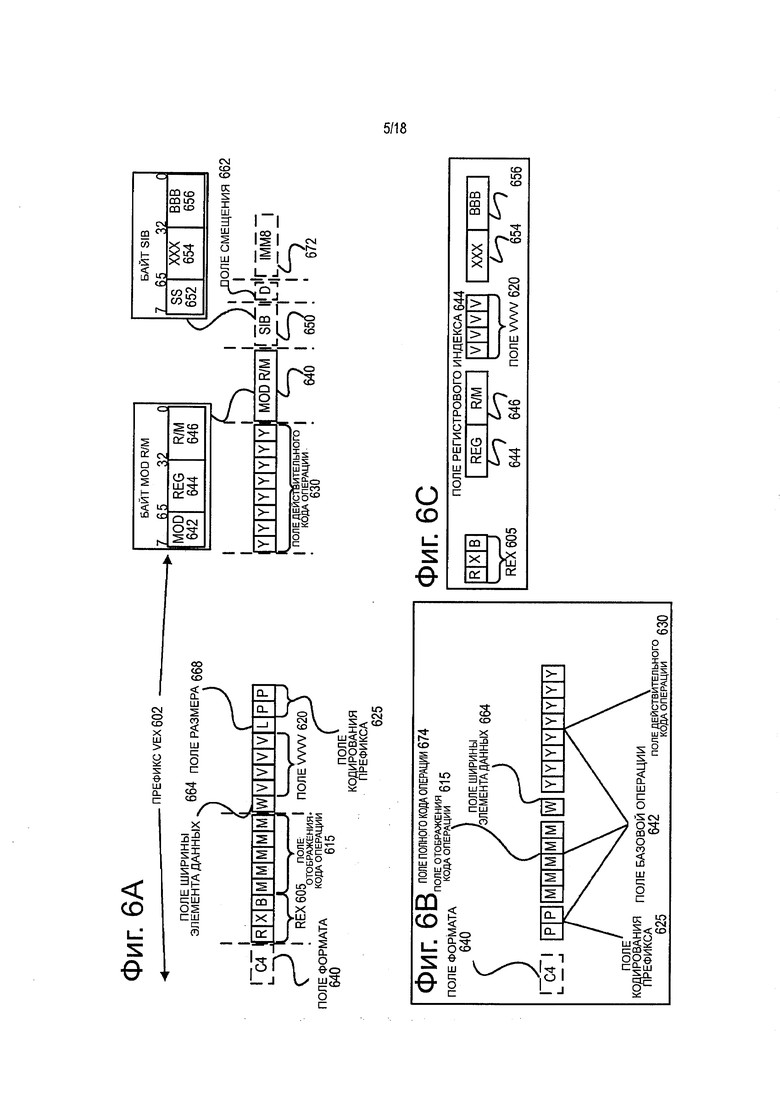

фиг. 6А иллюстрирует пример формата команды AVX, содержащего префикс VEX, поле кода операции реального режима, байт Mod R/M, байт SIB, поле смещения и IMM8 согласно одному из вариантов;

фиг. 6В показывает, какие поля из представленных на фиг. 6А составляют поле полного кода операции и поле базовой операции согласно одному из вариантов;

фиг. 6С показывает, какие поля из представленных на фиг. 6А составляют поле индекса регистра согласно одному из вариантов;

фиг. 7А представляет блок-схему, иллюстрирующую обобщенный удобный для работы с векторами формат команд и шаблон команд класса А в этом формате согласно вариантам настоящего изобретения;

фиг. 7В представляет блок-схему, иллюстрирующую обобщенный удобный для работы с векторами формат команд и шаблон команд класса В в этом формате согласно вариантам настоящего изобретения;

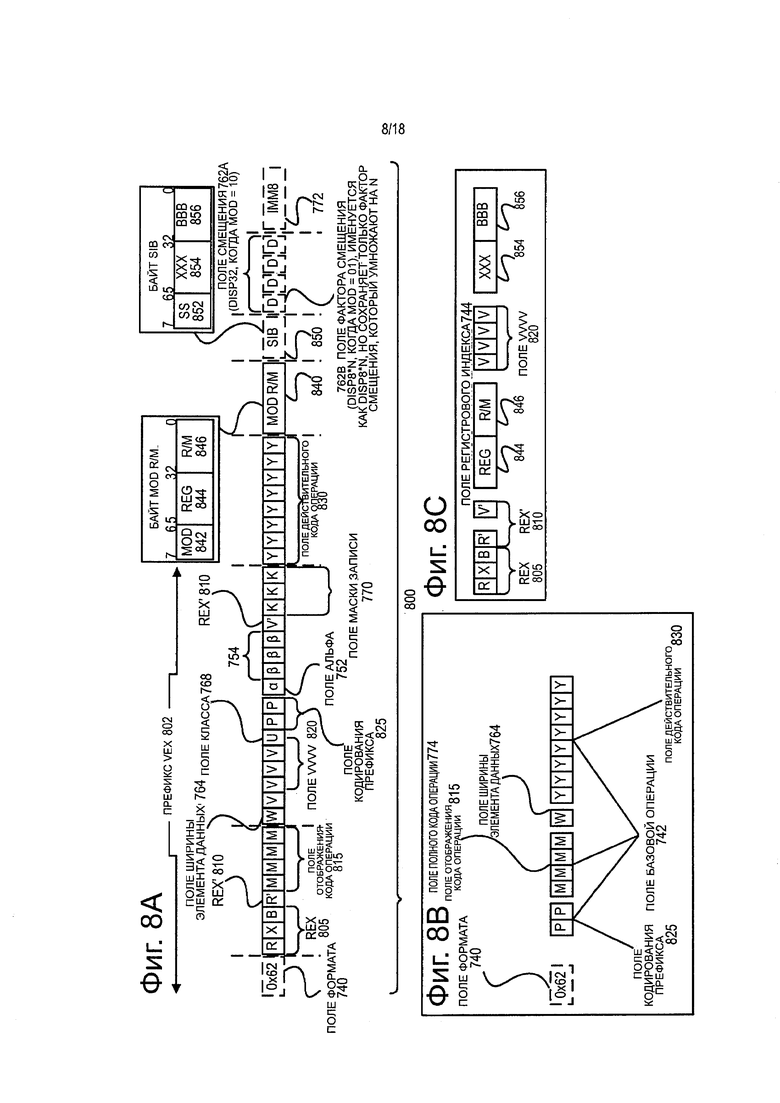

фиг. 8А представляет блок-схему, иллюстрирующую пример специального удобного для работы с векторами формата команд согласно вариантам настоящего изобретения;

фиг. 8В представляет блок-схему, иллюстрирующую поля показанного на фиг. 8А конкретного удобного для работы с векторами формата команд, составляющие поле полного кода операции согласно одному из вариантов настоящего изобретения;

фиг. 8С представляет блок-схему, иллюстрирующую поля конкретного удобного для работы с векторами формата команд, составляющие поле индекса регистра согласно одному из вариантов настоящего изобретения;

фиг. 8D представляет блок-схему, иллюстрирующую поля конкретного удобного для работы с векторами формата команд, составляющие поле дополнительной операции согласно одному из вариантов настоящего изобретения;

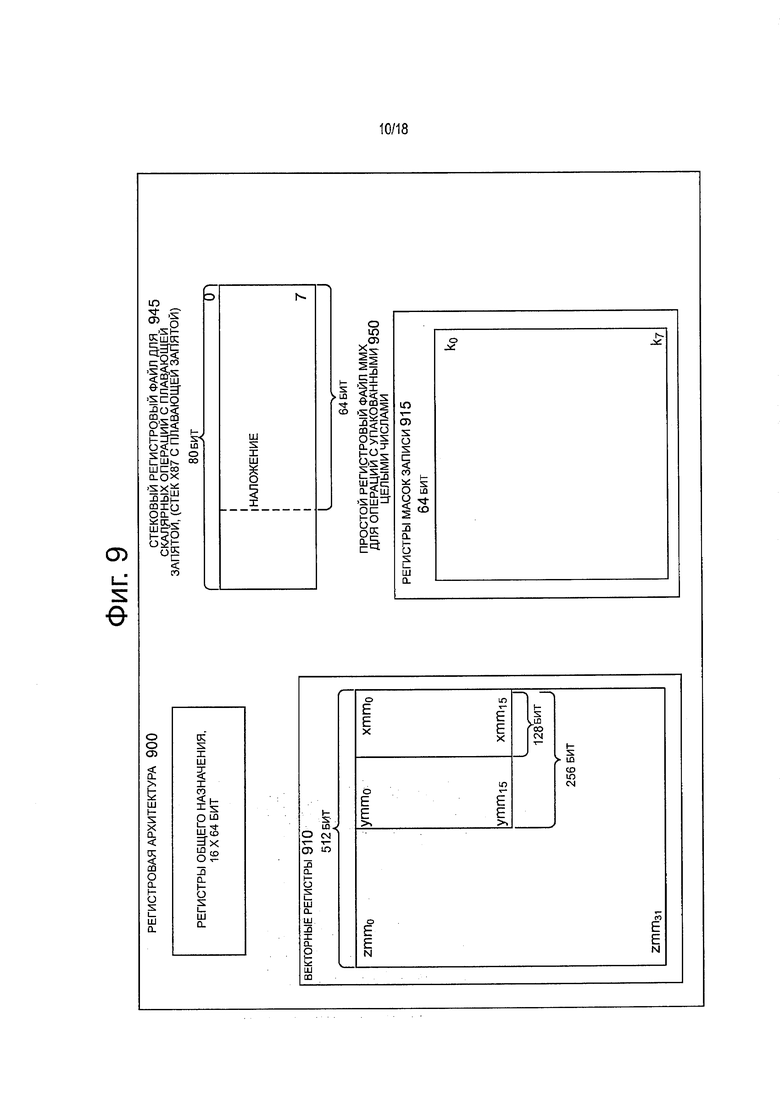

фиг. 9 представляет блок-схему регистровой архитектуры согласно одному из вариантов настоящего изобретения;

фиг. 10А представляет блок-схему, иллюстрирующую пример конвейера, выполняющего команды по порядку, и пример конвейера с выдачей данных/выполнением команд не по порядку и переименованием регистров согласно вариантам настоящего изобретения;

фиг. 10В представляет блок-схему, иллюстрирующую пример варианта ядра с архитектурой выполнения команд по порядку и пример ядра архитектуры с выдачей данных/выполнением команд не по порядку и переименованием регистров для включения в состав процессора согласно вариантам настоящего изобретения;

фиг. 11А представляет блок-схему одного ядра процессора вместе с его соединением с выполненной на кристалле соединительной схемой и с его локальным подмножеством кэша Уровня 2 (L2) согласно вариантам настоящего изобретения;

фиг. 11В представляет расширенное изображение части ядра процессора, показанного на фиг. 11А, согласно вариантам настоящего изобретения;

фиг. 12 представляет блок-схему процессора, который может иметь больше одного ядра, может иметь встроенный контроллер памяти и может иметь встроенную графику согласно вариантам настоящего изобретения;

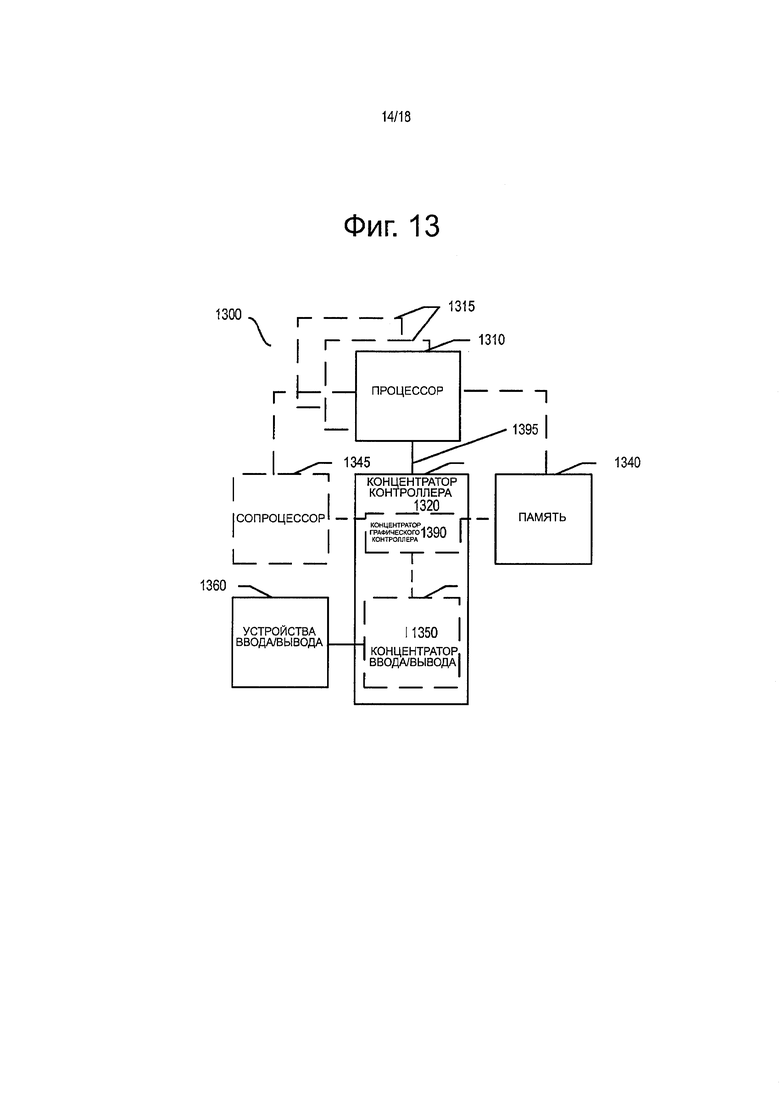

фиг. 13 представляет блок-схему системы согласно одному из вариантов настоящего изобретения;

фиг. 14 представляет блок-схему первого более конкретного примера системы согласно одному из вариантов настоящего изобретения;

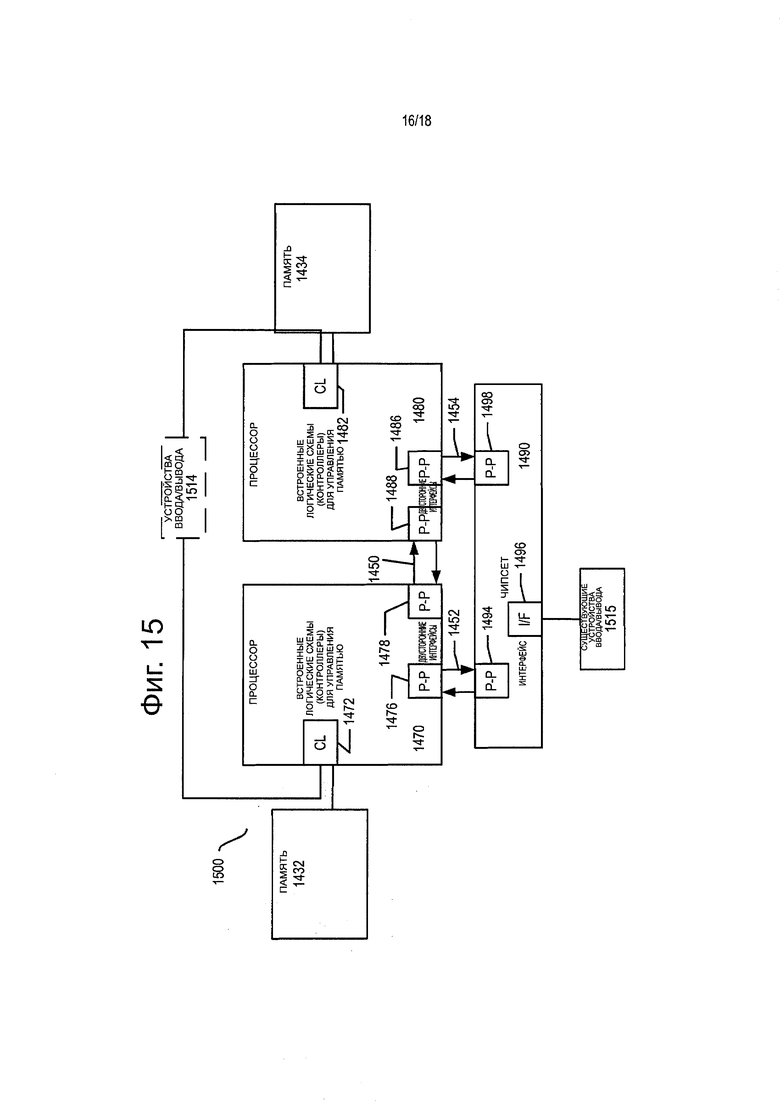

фиг. 15 представляет блок-схему второго более конкретного примера системы согласно одному из вариантов настоящего изобретения;

фиг. 16 представляет блок-схему «системы на кристалле» (SoC) согласно одному из вариантов настоящего изобретения; и

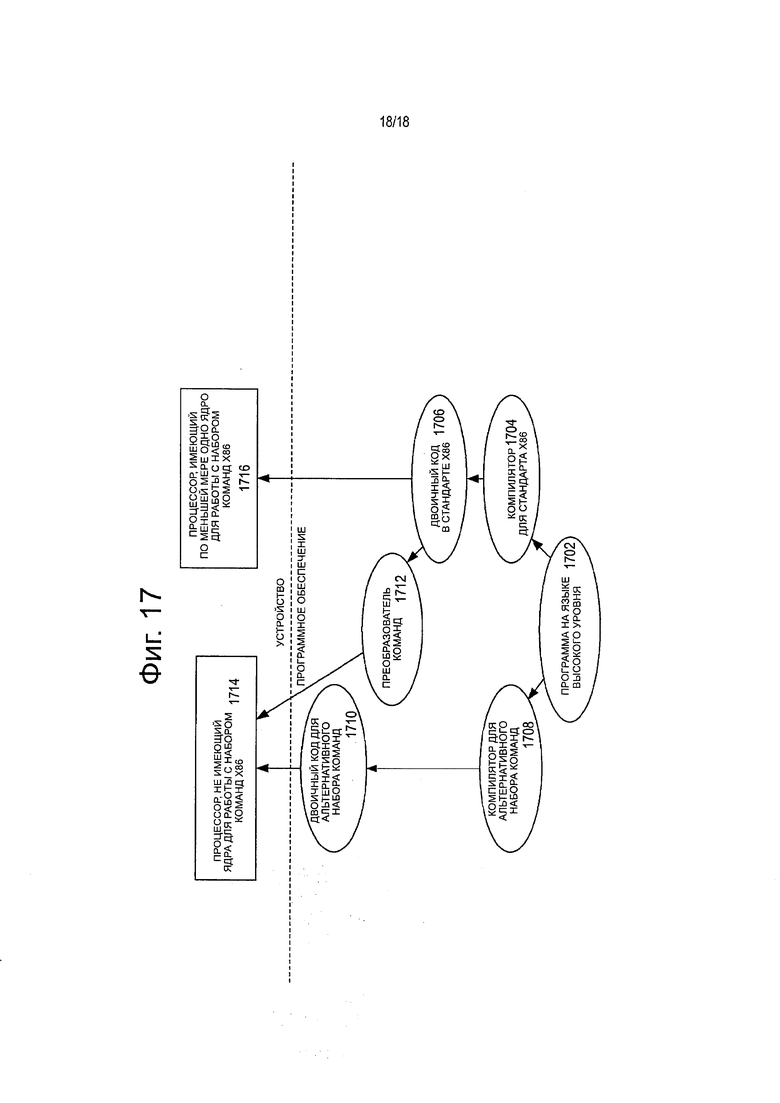

фиг. 17 представляет блок-схему сравнения использования программного преобразователя команд с целью преобразования двоичных команд из состава исходного набора команд в двоичные команды из состава целевого набора команд согласно вариантам настоящего изобретения.

Осуществление

В последующем описании приведены многочисленные конкретные детали. Однако понятно, что варианты настоящего изобретения могут быть практически реализованы и без этих конкретных деталей. В других случаях хорошо известные схемы, структуры и способы не были показаны подробно, чтобы не затруднять понимание настоящего описания.

Ссылки в настоящем описании на «один вариант», «некоторый вариант», «пример варианта» и т.п. означают, что описываемый вариант может иметь конкретный признак, структуру или характеристику, но каждый вариант совсем не обязательно содержит этот конкретный признак, структуру или характеристику. Более того, такая фраза совсем не обязательно относится к тому же самому варианту. Далее, когда конкретный признак, структура или характеристика описывается в связи с каким-либо вариантом, предполагается, что у специалиста в рассматриваемой области достаточно знаний, чтобы применить их в других вариантах, независимо от того, описано такое применение в явном виде или нет.

Команда транспонирования

Как подробно описано ранее, операцию транспонирования элементов традиционно выполняли в виде сочетания операций перетасовки и перестановки, что требует дополнительных издержек задания масок управления перетасовкой с использованием самих ближайших битов или с использованием отдельного векторного регистра, что увеличивает нагрузку и размер команд.

Варианты команды транспонирования (Transpose) подробно рассмотрены ниже, равно как и варианты, систем, архитектур, форматов команд и т.п., которые могут быть использованы для выполнения такой команды. Команда транспонирования содержит операнд, определяющий векторный регистр или позицию в памяти. При выполнении команды транспонирования процессор сохраняет элементы данных, записанные в определенном векторном регистре или позиции памяти, в порядке, обратном первоначальному порядку. Например, наиболее значимый («самый старший») элемент данных становится наименее значимым («самым младшим») элементом данных, наименее значимый элемент данных становится наиболее значимым элементом данных и т.д.

В некоторых вариантах, если команда определяет позицию в памяти, эта команда дополнительно содержит операнд, указывающий число элементов.

В некоторых вариантах, как будет подробно описано позднее, команду транспонирования выгружают для выполнения в модуле сопроцессора кэша.

Один из примеров этой команды выглядит так "Transpose [PS/PD/B/W/D/Q] Vector_Register/Memory", где параметр Vector_Register указывает векторный регистр (такой как 128, 256 или 512-битовый регистр), а параметр Memory указывает позиции в памяти. Участок "PS" команды обозначает скалярную плавающую запятую (4 байта). Участок "PD" команды указывает плавающую запятую для двойного формата (8 байт). Участок "В" обозначает байт, независимо от атрибута размера операнда. Участок "W" команды обозначает слово, независимо от атрибута размера операнда. Участок "D" команды обозначает сдвоенное слово, независимо от атрибута размера операнда. Участок "Q" команды обозначает счетверенное слово, независимо от атрибута размера операнда.

Определенный векторный регистр или позиция памяти является и источником, и адресатом операции. В результате выполнения команды транспонирования элементы данных, находящиеся в определенном векторном регистре или позиции памяти, сохраняют в порядке, обратном первоначальному порядку, в этом же определенном векторном регистре или позиции памяти.

Другой пример этой команды выглядит так "Transpose [PS/PD/B/W/D/Q] Memory, Num_Elements", где параметр Memory обозначает позиции в памяти, а параметр Num_Elements обозначает число элементов. В одном из вариантов команду такого вида выгружают и выполняют в модуле сопроцессора кэша.

Фиг. 1 иллюстрирует пример выполнения команды транспонирования согласно одному из вариантов. Команда 100 транспонирования содержит операнд 105. Эта команда 100 транспонирования принадлежит к структуре набора команд, и каждое «появление» такой команды 100 в потоке команд должно содержать величины в операнде 105. В этом примере операнд 105 определяет векторный регистр (такой как 128-, 256- или 512-битовый регистр). В качестве такого векторного регистра показан регистр zmm с 16 32-битовыми элементами данных; однако здесь могут быть использованы и другие размеры элементов данных и регистров, например, регистры xmm или ymm с 16-битовыми или 64-битовыми элементами данных.

Содержимое регистра, определенное операндом 105 (zmml), представлено, как показано на чертеже, 16 элементами данных. Фиг. 1 иллюстрирует регистр zmml до выполнения команды 100 транспонирования и после выполнения этой команды 100. Перед выполнением команды 100 транспонирования элемент данных с индексом 0 в регистре zmml сохраняет величину А, элемент данных с индексом 1 в регистре zmml сохраняет величину В, и т.д., так что последний элемент данных с индексом 15 в регистре zmml сохраняет величину Р. Выполнение команды 100 транспонирования вызывает пересохранение элементов данных, находившихся в регистре zmml, в этом же регистре, но в обратном порядке. Таким образом, элемент данных с индексом 0 в регистре zmml сохраняет величину Ρ (которая раньше находилась под индексом 15 в регистре zmml), элемент данных с индексом 1 сохраняет величину О (которая раньше находилась под индексом 14), и т.д., так что элемент данных с индексом 15 сохраняет величину А (которая раньше находилась под индексом 0).

Фиг. 2 иллюстрирует другой пример выполнения команды транспонирования. Команда 200 транспонирования содержит операнд 205 и операнд 210. Операнд 205 определяет позицию в памяти (в которой в этом примере хранится массив данных), а операнд 210 указывает число элементов (которое в этом примере равно 16). Перед выполнением команды 200 транспонирования элемент данных с индексом 0 в массиве сохраняет величину А, элемент данных с индексом 1 в массиве сохраняет величину В и т.д., а последний элемент данных с индексом 15 в массиве сохраняет величину Р. Выполнение команды 200 транспонирования вызывает пересохранение элементов данных, находившихся в массиве, в этом же массиве, но в обратном порядке относительно первоначального порядка. Таким образом, элемент данных с индексом 0 в массиве сохраняет величину Ρ (которая раньше находилась в массиве под индексом 15), элемент данных с индексом 1 сохраняет величину О (которая раньше находилась под индексом 14), и т.д., так что элемент данных с индексом 15 сохраняет величину А (которая раньше находилась под индексом 0).

Фиг. 3 представляет логическую схему, иллюстрирующую пример операций для транспонирования элементов данных в векторном регистре или в позиции памяти при выполнении одной команды транспонирования согласно одному из вариантов. На операции 310 процессор выбирает команду транспонирования (например, посредством модуля выборки в составе процессора). Эта команда транспонирования содержит операнд, определяющий векторный регистр или позицию в памяти. Специфицированный векторный регистр или позиция в памяти содержит несколько элементов данных, которые нужно транспонировать. Векторный регистр может, например, представлять собой регистр zmm, имеющий 16 32-битовых элементов данных; однако здесь могут быть использованы и другие размеры элементов данных и регистров, например, регистры xmm или ymm с 16-битовыми или 64-битовыми элементами данных.

Процесс переходит от операции 310 к операции 315, где процессор декодирует команду транспонирования. Например, в некоторых вариантах, процессор содержит аппаратный декодирующий модуль, куда поступает команда (например, от модуля выборки в составе процессор). В качестве декодирующего модуля могут быть использованы самые разнообразные и хорошо известные декодирующие модули. Например, такой декодирующий модуль может декодировать команду транспонирования и превратить ее в одну широкую микрокоманду. В качестве другого примера декодирующий модуль может декодировать команду транспонирования и превратить ее в несколько широких микрокоманд. Еще в одном примере, особенно хорошо подходящем для конвейерных систем, выполняющих команды не по порядку, декодирующий модуль может декодировать команду транспонирования и превратить ее в одну или несколько микроопераций, где каждая такая микрооперация может быть выдана и выполнена не по порядку (с изменением очередности). Кроме того, декодирующий модуль может быть реализован в составе одного или нескольких декодеров, причем каждый декодер может быть выполнен в виде программируемой логической матрицы (PLA), как это хорошо известно в технике. В качестве примера, конкретный декодирующий модуль может содержать: 1) управляющую логическую схему, направляющую различные макрокоманды в разные декодеры; 2) первый декодер, который может декодировать подмножество набора команд (но больше, чем это может делать каждый из второго, третьего и четвертого декодеров) и генерировать две микрооперации за один раз; 3) второй, третий и четвертый декодеры, каждый из которых может декодировать только подмножество всего набора команд и генерировать только одну микрооперацию за один раз; 4) ROM коммутатора микрокоманд, которое может декодировать только подмножество всего набора команд и генерировать четыре микрооперации за один раз; и 5) мультиплексорную логическую схему, получающую на входы микрокоманды от декодеров и от ROM коммутатора микрокоманд и определяющую, выходную команду какого из этих модулей поставить в очередь микроопераций. Другие варианты декодирующего модуля могут содержать больше или меньше декодеров, способных декодировать больше или меньше команд и подмножеств команд. Например, один вариант может содержать второй, третий и четвертый декодеры, каждый из которых может генерировать по две микрооперации за один раз; и может содержать ROM коммутатора микрокоманд, которое генерирует по восемь микроопераций за один раз.

Далее процедура переходит к операции 320, в ходе которой процессор выполняет команду транспонирования, вызывающую сохранение элементов данных, находящихся в некотором порядке в определенном векторном регистре или позиции памяти, в этом же определенном регистре или позиции памяти, но в порядке, обратном первоначальному порядку.

Команду транспонирования может автоматически генерировать компилятор, либо ее может закодировать вручную разработчик программного обеспечения. Выполнение описанной здесь команды транспонирования улучшает программируемость структуры набора команд и уменьшает число команд, снижая тем самым потребление энергии в ядре. Кроме того, выполнение команды транспонирования происходит, не требуя создания временного буфера для сохранения транспонированных элементов в памяти, в отличие от традиционных способов выполнения операции транспонирования, что уменьшает требования к размеру памяти. Кроме того, выполнение одной команды транспонирования проще, чем выполнение сложного набора перетасовок и перестановок, который раньше требовался для осуществления операций транспонирования.

Выгрузка команд для выполнения модулем сопроцессора кэша

Как подробно описано ранее, программные приложения могут содержать функции, обычно требующие выполнения некоторого числа операций загрузки и/или сохранения между исполнительным кластером процессорного ядра и модулем памяти (кэшем и памятью) компьютерной системы. Некоторые из этих функций почти не требуют вычислений, но могут потребовать большого числа операций загрузки и/или сохранения, таких как очистка памяти, копирование памяти и транспонирование. Другие функции, такие как вычисление скалярного произведения матриц и суммирование массивов требуют небольшого объема вычислений, но также могут потребовать большого числа операций загрузки и/или сохранения. Например, для выполнения операции транспонирования массива памяти этот массив памяти следует загрузить в регистр, ядро обратит порядок следования величин, после чего эти величины снова сохраняют в массиве памяти (эти этапы может потребоваться повторить несколько раз прежде, чем будет транспонирован весь массив памяти).

Варианты настоящего изобретения описывают модуль процессора кэша, выполняющий команды, выгруженные, чтобы не выполнять их посредством исполнительного кластера компьютерной системы. Например, некоторые функции управления памятью (такие как очистка памяти, копирование памяти, транспонирование и т.п.) выгружают, чтобы их не выполнял исполнительный кластер компьютерной системы, и выполняют непосредственно в модуле сопроцессора кэша (который может содержать данные, над которыми производятся операции). В качестве другого примера, команды, которые требуют проведения постоянной вычислительной операции в непрерывной области массива кэша в модуле сопроцессора кэша, могут быть выгружены в этот модуль сопроцессора кэша и выполнены им (например, скалярное произведение матриц, суммирование массивов и т.п.). Выгрузка этих команд в модуль сопроцессора кэша уменьшает число операций загрузки и сохранения между модулем процессора кэша и исполнительным кластером компьютерной системы, что уменьшает число команд, освобождает ресурсы исполнительного кластера (например, станций резервации (RS), буфера переупорядочения (ROB), буферов заполнения и т.п.), и тем самым позволяет исполнительному кластеру использовать эти ресурсы для выполнения других команд.

Фиг. 4 представляет блок-схему, иллюстрирующую пример варианта ядра с архитектурой выполнения команд по порядку и пример ядра архитектуры с выдачей/выполнением команд не по порядку и переименованием регистров, содержащего пример модуля сопроцессора кэша, выполняющего команды, которые были выгружены, чтобы их не выполнял исполнительный кластер процессорного ядра, согласно одному из вариантов. Прямоугольниками из сплошных линий на фиг. 4 обозначены компоненты конвейера с выполнением команд по порядку и ядра с выполнением команд по порядку, тогда как добавленные в качестве компоненты в прямоугольниках из штриховых линий обозначают компоненты конвейера и ядра архитектуры с выдачей/выполнением команд не по порядку и переименованием регистров. Поскольку аспект выполнения команд по порядку являются частью аспекта с выполнением команд не по порядку, далее будет описан аспект с выполнением команд не по порядку.

Как показано на фиг. 4, процессорное ядро 400 содержит модуль 410 ввода, соединенный с исполнительным модулем 415, который соединен с модулем 470 сопроцессора кэша. Процессорное ядро 400 может представлять собой компьютерное ядро с уменьшенным набором команд (RISC), ядро со сложным набором команд (CISC), ядро с очень длинным командным словом (VLIW), либо ядро гибридного или альтернативного типа. Еще в одном варианте ядро 400 может представлять собой ядро специального назначения, такое как, например, сетевое ядро или ядро связи, автомат сжатия, сопроцессорное ядро, ядро графического процессора общего назначения (GPGPU), графическое ядро или другое подобное ядро.

Входной модуль 410 содержит модуль 420 выборки команд, соединенный с декодирующим модулем 425. Этот декодирующий модуль 425 (или декодер) конфигурирован для декодирования команд и генерации на выходе одной или нескольких микроопераций, точек ввода микрокодов, микрокоманд, других команд или других сигналов управления, которые декодированы на основе, или как-то иначе отражают или выведены из исходных команд. Такой декодирующий модуль 425 может быть реализован с использованием разнообразных механизмов. К примерам подходящих механизмов относятся, не ограничиваясь этим, просмотровые таблицы, аппаратные реализации, программируемые логические матрицы (PLA), ROM микрокодов и т.п. В одном из вариантов, ядро 400 содержит ROM микрокодов или другой носитель, сохраняющий микрокоды для определенных макрокоманд (например, в декодирующем модуле 425 или, в ином случае, в модуле 410 ввода). Указанный декодирующий модуль 425 соединен с модулем 435 переименования/назначения в составе исполнительного модуля 415. Хотя на фиг. 1 это не показано, модуль 410 ввода может также содержать модуль прогнозирования ветвления, соединенный с модулем кэша команд, который в свою очередь соединен с буфером ассоциативной трансляции (TLB), связанным с модулем выборки команд 420.

Декодирующий модуль 425 также конфигурирован для определения, следует ли выгрузить какую-либо команду в модуль 470 сопроцессора кэша. В одном из вариантов, решение о выгрузке команды в модуль 470 сопроцессора кэша принимается динамически (во время выполнения программы) и зависит от архитектуры. Например, в одном из вариантов команда может быть выгружена, если ее длина в памяти больше длины кэш-линии (например, 64 байта) и если она кратна длине кэш-линии. В другом варианте решение о выгрузке команды в модуль 470 сопроцессора кэша может быть принято независимо от длины этой команды в памяти, а в зависимости от эффективности модуля 470 сопроцессора кэша.

В другом варианте при принятии решения о выгрузке команды в модуль 470 сопроцессора кэша может также учитываться сама команда. Иными словами, некоторые команды могут быть специально предназначены для выгрузки в модуль 470 сопроцессора кэша или по меньшей мере могут быть (допускают) выгружены в этот модуль 470 сопроцессора кэша. В качестве примера, такая команда может быть сформирована компьютером или написана разработчиком программного обеспечения на основе того, что такую команду было бы более эффективно выгрузить в модуль сопроцессора кэша.

Указанный исполнительный модуль 415 содержит модуль 435 переименования/назначения, соединенный с модулем 450 выбытия и группой из одного или более модулей планировщиков 440. Модули 440 планировщики представляют собой любое число различных планировщиков, включая станции резервации, центральное командное окно и т.п. Модули 440 планировщиков соединены с модулями 445 физических регистровых файлов. Каждый из этих модулей 445 физических регистровых файлов представляет один или более физических регистровых файлов, так что разные файлы сохраняют один или более различных типов данных, такие как скалярные целочисленные данные, скалярные данные с плавающей запятой, упакованные целочисленные данные, упакованные данные с плавающей запятой, векторные целочисленные данные, векторные данные с плавающей запятой, данные состояния (например, указатель команды, представляющий собой адрес следующей команды, которую нужно выполнить) и т.п. В одном из вариантов, модуль 445 физических регистровых файлов содержит модуль векторных регистров, модуль регистров масок записи и модуль скалярных регистров. Эти регистровые модули могут предоставлять архитектурные векторные регистры, регистры векторных масок и регистры общего назначения. На модули 445 физических регистровых файлов наложен модуль 450 выбытия для иллюстрации различных способов, которыми может быть реализовано переименование регистров и выполнение команд не по порядку (например, с использованием буфера(ов) переупорядочения и регистровых файлов выбытия; с использованием будущих файлов, буфера(ов) предыстории и регистровых файлов выбытия; с использованием карт регистров и пула регистров; и т.п.). Указанные модуль 450 выбытия и модули 445 физических регистровых файлов соединены с исполнительным кластером(ами) 455.

Исполнительный кластер(ы) 455 содержит группу из одного или более исполнительных модулей 460 и группу модулей 465 доступа к памяти. Исполнительные модули 455 могут осуществлять различные вычислительные операции (например, сдвиги, суммирование, вычитание, умножение) и над различными типами данных (например, скалярными данными с плавающей запятой, упакованными целочисленными данными, упакованными данными с плавающей запятой, векторными целочисленными данными, векторными данными с плавающей запятой). Модули 440 планировщиков, модули 445 физических регистровых файлов и исполнительные кластеры 455 показаны как, возможно, по несколько штук, поскольку в некоторых вариантах создают отдельные конвейеры для некоторых типов данных/операций (например, конвейер для скалярных целочисленных данных, конвейер для скалярных данных с плавающей запятой/упакованных целочисленных данных/упакованных данных с плавающей запятой/векторных целочисленных данных/векторных данных с плавающей запятой и/или конвейер доступа к памяти, так что каждый конвейер имеет свой собственный модуль планировщика, модуль физических регистровых файлов и/или исполнительный кластер - и в случае отдельного конвейера доступа к памяти реализованы некоторые варианты, в которых только исполнительный кластер этого конвейера имеет модули 465 доступа к памяти). Следует понимать, что при использовании раздельных конвейеров один или более из этих конвейеров могут использовать выдачу/выполнение не по порядку очередности, а остальные - в порядке очередности.

Группа модулей 465 доступа к памяти соединена с модулем 470 сопроцессора кэша. В одном из вариантов модуль 465 доступа к памяти содержит модуль 484 загрузки, модуль 486 адресов сохранения, модуль 488 сохранения данных и группу из одного или более модулей 490 выгрузки команд, осуществляющих выгрузку команд в модуль 470 сопроцессора кэша. Указанный модуль 484 загрузки выдает операции доступа для загрузки (которые могут иметь форму микроопераций загрузки) в модуль процессора кэша 470. Например, модуль 484 загрузки указывает адрес данных, которые нужно загрузить. Для выполнения операций сохранения используют модуль 486 адресов сохранения и модуль 488 сохранения данных. Здесь модуль 486 адресов сохранения задает адрес, а модуль 488 сохранения данных указывает данные, которые нужно записать в память. В некоторых вариантах, модули загрузки и модули адресов сохранения могут быть использованы либо в качестве модулей загрузки, либо в качестве модулей адресов сохранения.

Как описано ранее, программные приложения могут тратить значительное количество времени и ресурсов на выполнение операций загрузки и сохранения. Например, многие команды, такие как очистка памяти, копирование памяти и транспонирование, обычно требуют выполнения множества команд загрузки, вычисления и сохранения в исполнительных модулях исполнительного кластера ядра. Например, команду загрузки выдают для загрузки данных в регистр(ы), осуществляют вычисление и выдают команду сохранения, чтобы записать полученные в результате данные. Для полного выполнения команды могут потребоваться несколько итеративных циклов этих операций. Операции загрузки и сохранения также используют ширину полосы кэша и памяти, равно как и другие ресурсы ядра (например, станций RS, буфера ROB, буферов заполнения и т.п.).

Модуль(и) 490 выгрузки команд выдает команду(ы) в модуль 470 сопроцессора кэша с целью перенести («выгрузить») выполнение некоторых команд в модуль 470 сопроцессора кэша. Например, выполнение команд, которые обычно требуют значительного числа операций загрузки и/или сохранения, но при этом требуют незначительного (или вообще нулевого) объема вычислений, могут быть выгружены для выполнения прямо в модуль 470 сопроцессора кэша, чтобы уменьшить число операций загрузки и сохранения, которые в противном случае пришлось бы осуществить. Например, функция очистки памяти, функция копирования памяти и функция транспонирования обычно требуют выполнения большого числа операций загрузки и сохранения, но при этом связаны с незначительным (или даже нулевым) объемом вычислений. В одном из вариантов, выполнение этих функций может быть выгружено в модуль 470 сопроцессора кэша. В качестве другого примера в модуль 470 сопроцессора кэша могут быть для выполнения выгружены команды, для которых требуется постоянно выполнять одну и ту же операцию вычисления в непрерывной области данных. Примерами таких команд являются осуществление функций, таких как вычисление скалярного произведения матриц, вычисление суммы массивов и т.п.

Рассматриваемый модуль 470 сопроцессора кэша осуществляет операции с кэшем (например, кэш L1, кэш L2) для ядра 400 и обрабатывает выгруженные команды. Таким образом, модуль 470 сопроцессора кэша обрабатывает обращения для загрузки и обращения для сохранения аналогично тому, как это делает обычный модуль кэша, а также обрабатывает выгруженные команды. Декодирующий модуль 474 в составе модуля 470 сопроцессора кэша содержит логическую схему для декодирования выгруженных команд, а также запросов загрузки, адресов сохранения и запросов на сохранение данных. В одном из вариантов для декодирования каждого запроса используется отдельная управляющая проводная линия между каждым из модулей доступа к памяти и модулем 470 сопроцессора кэша. В другом варианте для уменьшения числа проводных линий используют группу из одного или более управляющих проводов между модулями 465 доступа к памяти и декодирующим модулем 474, управляемым одним или более мультиплексорами.

После декодирования запрошенной операции(й) операционные модули 472 из состава модуля 470 сопроцессора кэша выполняют эти операции. Например, операционный модуль(и) 472 содержит логическую схему для записи данных в массив 482 кэша (для операций сохранения) и считывания данных из массива 482 кэша (для операций загрузки), равно как из любых требуемых буферов. Например, если принят запрос загрузки, операционный модуль(и) 472 обращается в массив кэша по запрошенному адресу и выдает данные (в предположении, что эти данные находились в массиве 482 кэша). В качестве другого примера, если принят запрос сохранения, операционный модуль(и) 472 записывает запрошенные данные по запрашиваемому адресу.

Декодирующий модуль 474 определяет, какие операции должны быть произведены для выполнения выгруженной команды. В качестве примера, в варианте, где выгруженная команда является по существу невычислительной (например, очистка памяти, копирование памяти, транспонирование или другая функция, трансформирующая данные, не требуя вычислений), этот декодирующий модуль 474 определяет число операций загрузки и/или сохранения, которые должны осуществить операционные модули 472 для выполнения команды. Например, если принята команда очистки памяти, декодирующий модуль 474 может управлять операционными модулями 472 для осуществления некоторого числа операций сохранения (в зависимости от длины области памяти, которую нужно очистить) в массиве 482 кэша с целью приравнять запрошенные данные нулю (или другой величине). Таким образом, например, в модуль 470 сопроцессора кэша может быть выгружена только одна команда для осуществления этим модулем функции очистки памяти, не требуя, чтобы модули 465 доступа к памяти (модуль 486 адресов сохранения и модуль 488 сохранения данных) выдали множество запросов сохранения для завершения функции очистки памяти.

Операционные модули 472 при выполнении этих операций используют модуль 473 управления. Например, модуль 476 управления циклами в составе модуля 473 управления осуществляет управление циклами в массиве 482 кэша для выполнения операций, требующих циклов. В качестве примера, если декодирована команда очистки памяти, модуль 476 управления циклами осуществляет циклические проходы через массив 482 кэша несколько раз (в зависимости от размеров области памяти, которую нужно очистить), а операционные модули 472 очищают массив 482 соответственно. В одном из вариантов работа операционных модулей 472 ограничена обработкой в пределах размера кэш-линии и границы.

Модуль 473 управления содержит также модуль 478 блокирования кэша, осуществляющий блокирование области массива 482 кэша, обрабатываемой в текущий момент операционными модулями 472. Попадание в заблокированную область массива 482 кэша вызывает остановку попавшего в кэш процесса.

Модуль 473 управления содержит также модуль 480 контроля ошибок, предназначенный для сообщения об ошибках. Например, об ошибке, относящейся к обработке выгруженной команды, сообщают назад, в модуль 490 выгрузки команд, выдавший команду, которая привела либо к сбою выполнения команды, либо к записи кода ошибки в управляющем регистре. В одном из вариантов модуль 480 контроля ошибок сообщает об ошибке в модуль 490 выгрузки команд, выдавший выгруженную команду, когда в массиве 482 кэша нет данных. В одном из вариантов модуль 480 контроля ошибок сообщает об ошибке в модуль 490 выгрузки команд, выдавший выгруженную команду, когда имеет место состояние переполнения или недостаточного заполнения.

Хотя на фиг. 4 это не показано, модуль 470 сопроцессора кэша может быть также соединен с буфером ассоциативной трансляции (буфером преобразования адресов). Кроме того, модуль 470 сопроцессора кэша может быть соединен с кэшем уровня 2 и/или с основной памятью. Далее, модуль 473 управления может также содержать логическую схему слежения, контролирующую адресные шины для доступа к позициям памяти, которые были кэширование в массиве 482 кэша.

В некоторых вариантах выгруженные команды требуют вычислений (например, сдвига, суммирования, вычитания, умножения, деления). Например, вычислений требуют такие функции, как определение скалярного произведения матриц или суммирование массивов. В вариантах, где выгружаемые команды требуют вычислений, в одном из вариантов среди операционных модулей 472 присутствуют исполнительные модули (например, арифметическо-логические модули, модули для осуществления операций с плавающей запятой) для выполнения этих операций.

На фиг. 4 показано, что модуль 470 сопроцессора кэша реализован в кэше уровня 1. Однако в других вариантах этот модуль сопроцессора кэша может быть реализован в кэше другого уровня (например, в кэше уровня 2 или во внешнем кэше).

В одном из вариантов модуль 470 сопроцессора кэша реализован в виде дублирующей копии кэша уровня 1, где контент считывают из кэша уровня 1, блокируют, и вносят изменения в дублирующую копию. После завершения операций кэш-линии в кэше уровня 1 делают недействительными и разблокируют, а дублирующая копия имеет действительные данные.

В одном из вариантов выгруженная команда будет выдана, только если данные для этой команды уже находятся в кэше. В таком варианте приложение, генерирующее команду, обеспечивает наличие данных в кэше. В одном из вариантов ошибки кэш обрабатывают аналогично обычным, регулярным ошибки кэш. Например, после ошибки кэш обращаются в кэш следующего уровня или в основную память для доступа к нужным данным.

На фиг. 5 представлена логическая схема, иллюстрирующая пример операций для выполнения выгруженной команды согласно одному из вариантов. Схема на фиг. 5 будет рассмотрена со ссылками на пример архитектуры, показанный на фиг. 4. Однако следует понимать, что операции, представленные на фиг. 5, могут быть выполнены в вариантах, отличных от варианта, рассмотренного в связи с фиг. 4, а варианты, обсуждавшиеся в связи с фиг. 4, могут выполнять операции, отличные от операций, обсуждаемых со ссылками на фиг. 5.

На операции 510 происходит выборка команды. Эту выборку команды осуществляет, например, модуль 420 выборки команд. Затем процедура переходит к операции 515, на которой декодирующий модуль 425 из состава модуля 410 ввода декодирует команду и принимает решение, что ее следует выгрузить для выполнения в модуль 470 сопроцессора кэша. Например, команда может быть такого типа, какой специально предназначен для выгрузки в модуль 470 сопроцессора кэша. В качестве другого примера, рассматриваемая команда может допускать выгрузку, а ее длина в памяти может быть больше размера кэш-линии.

Затем процедура переходит к операции 520, на которой декодированную команду выдают в модуль 470 сопроцессора кэша. Например, команду в модуль 470 сопроцессора кэша выдают модули 490 выгрузки команд. Далее процедура переходит к операции 525, на которой декодирующий модуль 474 из состава модуля 470 сопроцессора кэша декодирует выгруженную команду. После этого процедура переходит к операции 530, и операционные модули 472 выполняют эту команду, как было описано раньше.

В одном из вариантов команду для каждой функции, которая должна быть выгружена, формулируют таким образом, чтобы она могла быть выдана в модуль 470 сопроцессора кэша для обработки. В качестве конкретного примера, команда транспонирования может быть выгружена и выполнена модулем 470 сопроцессора кэша. Например, команда транспонирования может иметь вид "TransposeO [PS/PD/B/W/D/Q] Memory, Num_Elements", где параметр Memory обозначает позицию в памяти, а параметр Num_Elements обозначает число элементов в этой позиции памяти. Эта команда транспонирования аналогична команде транспонирования, описанной ранее; однако код операции для этой команды "TransposeO" обозначает, что эта команда транспонирования подлежит выгрузке.

После обнаружения этой команды декодирующий модуль 425 определяет, что она должна быть выгружена в модуль 470 сопроцессора кэша, как было описано ранее. Соответственно, модуль 490 выгрузки команд выдает команду в модуль 470 процессора кэша вместе с передаваемыми в модуль 470 сопроцессора кэша начальным адресом в памяти и длиной команды (в одном из вариантов модуль адресов сохранения передает начальный адрес в памяти и длину в виде, упакованном в полезную нагрузку, от модуля 470 сопроцессора кэша).

Декодирующий модуль 474 декодирует команду и инициирует выполнение соответствующих операций посредством операционных модулей 472. Например, операционные модули 472 начинают с загрузки первой и последней кэш-линий из позиции памяти, указанной начальным адресом в памяти, в массив 482 кэша, осуществляют свопинг этих двух кэш-линий и затем переходят в направлении внутрь, пока не выберут всю длину из памяти. Таким образом, единственная команда транспонирования, выполняемая сразу модулем 470 сопроцессора кэша, уменьшает число команд загрузки и сохранения между исполнительным кластером и модулем сопроцессора кэша, равно как и сберегает ресурсы исполнительного модуля 415, которые могут быть использованы для выполнения других команд.

Выгрузка команд для выполнения их посредством модуля сопроцессора кэша позволяет более не выполнять относительно простые задания, связанные с памятью, (например) посредством исполнительных модулей процессорного ядра, тем самым уменьшая число команд и сберегая затраты энергии в ядре, уменьшая степень использования буферов и улучшая характеристики за счет уменьшения размеров кода и упрощения программирования. Таким образом, с точки зрения модуля 410 ввода и исполнительного модуля 415 можно выгрузить и выполнить посредством модуля 470 сопроцессора кэша единственную команду вместо выполнения длинной цепочки команд. Это позволяет исполнительному модулю 415 использовать свои ресурсы для решения более сложных вычислительных задач, сберегая тем самым ресурсы ядра, затраты энергии в ядре и улучшая характеристики.

Примеры форматов команд

Описанные здесь варианты команд могут быть реализованы в различных форматах. Примеры систем, архитектур и конвейеров будут подробно рассмотрены ниже. Различные варианты команд можно выполнять в системах, архитектурах и конвейерах подобного типа, не ограничиваясь только теми, которые будут подробно описаны здесь. В одном из вариантов такие примеры систем, архитектур и конвейеров, подробно обсуждаемые ниже, можно использовать для выполнения команд, которые не выгружены в модуль сопроцессора кэша, описанный выше.

Формат VEX команды

Кодирование в формате VEX дает возможность командам иметь больше двух операндов и позволяет векторным регистрам SIMD быть длиннее 128 бит. Использование префикса VEX дает синтаксис с тремя операндами (или более). Например, предшествующие команды с двумя операндами позволяли осуществлять операции типа А = А + В, где результат записывают на место операнда источника. Использование префикса VEX позволяет операндам выполнять неразрушающие операции, такие как А = В + С.

Фиг. 6А иллюстрирует пример формата AVX команды, содержащего поле 602 префикса VEX, поле 630 действительного кода операции, байт 640 Mod R/M, байт 650 SIB 650, поле 662 смещения и параметр 672 IMM8. Фиг. 6В иллюстрирует, какие поля из изображенных на фиг. 6А, составляют поле 664 полного кода операции и поле 642 базовой операции. Фиг. 6С иллюстрирует, какие поля из изображенных на фиг. 6А, составляют поле 644 индекса регистра.

Префикс 602 VEX (байты 0-2) кодирован в виде трех байтов. Первый байт является полем 640 формата (VEX байт 0, биты [7:0]), содержащим величину явного байта С4 (уникальная величина, используемая, чтобы отличать формат С4 команд). Второй и третий байты (VEX байты 1-2) содержат ряд битовых полей, предоставляющих специальные возможности. В частности, поле 605 REX (VEX байт 1, биты [7-5]) содержит битовое поле VEX.R (VEX байт 1, бит [7] - R), битовое поле VEX.X (VEX байт 1, бит [6] - X) и битовое поле VEX.B (VEX байт 1, бит [5] - В). Другие поля команд кодируют три младших бита регистровых индексов, как это известно в технике (rrr, ххх и bbb), так что Rrrr, Хххх и Bbbb могут быть получены путем добавления VEX.R, VEX.X и VEX.B. Поле 615 отображения кода операции (VEX байт 1, биты [4:0] - mmmmm) содержит контент для кодирования первого байта операционного кода в неявном виде. Поле 664 W (VEX байт 2, бит [7] - W) - представлено обозначением VEX.vvvv и описывает различные функции, зависящие от команды. Роль поля 620 VEX.vvvv (VEX байт 2, биты [6:3]-vvvv) может быть следующей: 1) VEX.vvvv кодирует первый регистровый операнд-источник, заданный в инвертированной (1s дополнение или дополнение до 1) форме и действительный для команд с 2 или более операндами-источниками; 2) VEX.vvvv кодирует регистровый операнд-адресат, определенный в форме дополнения до 1 для некоторых векторных сдвигов; или 3) VEX.vvvv не кодирует ни один операнд, поле зарезервировано и должно содержать 1111b. Если поле 668 размера VEX.L (VEX байт 2, бит [2]-L) = 0, это означает 128-битовый вектор; если VEX.L = 1, это означает 256-битовый вектор. Поле 625 кодирования префикса (VEX байт 2, бит [1:0]-рр) предоставляет дополнительные биты для поля базовой операции.

Поле 630 действительного кода операции (байт 3) известно также под названием байта кода операции. В этом поле определена часть кода операции.

Поле 640 MOD R/M (байт 4) содержит поле 642 MOD (биты [7-6]), поле 644 Reg (биты [5-3]) и поле 646 R/M (биты [2-0]). Роль поля 644 Reg может состоять в следующем: кодирование либо регистрового операнда-адресата, либо регистрового операнда-источника (rrr или Rrrr), или это поле нужно рассматривать как расширение кода операции и не следует использовать для кодирования какого-либо операнда команды. Роль поля 646 R/M может состоять в следующем: кодирование операнда команды, указывающего адрес в памяти, или кодирование либо регистрового операнда-адресата, либо регистрового операнда-источника.

Масштаб, Индекс, База (Scale, Index, Base (SIB)) - Поле 650 Масштаб Scale (байт 5) содержит параметр SS652 (биты [7-6]), который используется для генерирования адресов памяти. Содержание полей 654 SIB.xxx (биты [5-3]) и 656 SIB.bbb (биты [2-0]) было предварительно соотнесено с регистровыми индексами Хххх и Bbbb.

Поле 662 смещения 662 и поле 672 непосредственной адресации (IMM8) содержат адресные данные.

Пример кодирования в VEX

Обобщенный удобный для работы с векторами формат команд

Удобный для работы с векторами формат команд представляет собой формат команд, приспособленный для векторных команд (например, имеются определенные поля, определенные для векторных операций). Хотя в описанных здесь вариантах и векторные операции, и скалярные операции поддерживаются посредством указанного удобного для работы с векторами формата команд, альтернативные варианты используют только векторные операции этого удобного для работы с векторами формата команд.

Фиг. 7А-7В представляют блок-схемы, иллюстрирующие обобщенный удобный для работы с векторами формат команд шаблоны команд в этом формате согласно вариантам настоящего изобретения. Фиг. 7А представляет блок-схему, иллюстрирующую обобщенный удобный для работы с векторами формат команд и шаблоны команд класса А в этом формате согласно вариантам настоящего изобретения; тогда как фиг. 7В показывает блок-схему, иллюстрирующую обобщенный удобный для работы с векторами формат команд и шаблоны команд класса В в этом формате согласно вариантам настоящего изобретения. В частности, показан обобщенный удобный для работы с векторами формат 700 команд, для которого определены шаблоны команд класса А и класса В, так что обе группы шаблонов содержат шаблоны 705 команд без доступа к памяти и шаблоны 720 команд с доступом к памяти. Термин «обобщенный» в контексте рассматриваемого удобного для работы с векторами формата команд означает, что этот формат команд не привязан к какому-либо конкретному формату команд.

Тогда как здесь будут описаны варианты настоящего изобретения, в которых упомянутый удобный для работы с векторами формат команд поддерживает следующее: длину (или размер) векторного операнда 64 байт с шириной (или размером) элемента данных 32 бит (4 байта) или 64 бит (8 байт) (и, таким образом, вектор размером 64 байт содержит либо 16 элементов в размере двойного слова, либо, в качестве альтернативы, 8 элементов в размере учетверенного слова); длину (или размер) векторного операнда 64 байт с шириной (или размером) элемента данных 16 бит (2 байт) или 8 бит (1 байт); длину (или размер) векторного операнда 32 байт с шириной (или размером) элемента данных 32 бит (4 байт), 64 бит (8 байт), 16 бит (2 байт) или 8 бит (1 байт); и длину (или размер) векторного операнда 16 байт с шириной (или размером) элемента данных 32 бит (4 байт), 64 бит (8 байт), 16 бит (2 байт) или 8 бит (1 байт); альтернативные варианты могут поддерживать больше, меньше или другие размеры векторных операндов (например, векторные операнды размером 256 байт) с большей, меньшей или другой шириной элементов данных (например, ширина элемента данных 128 бит (16 байт)).

Шаблоны команд класса А, показанные на фиг. 7А, содержат: 1) в совокупность шаблонов 705 команд без доступа к памяти входят шаблоны 710 команд для операций управления с полным округлением и без доступа к памяти и шаблоны 715 команд для преобразования данных без доступа к памяти; и 2) в совокупность шаблонов 720 команд с доступом к памяти входят шаблоны 725 временных команд с доступом к памяти и шаблоны 730 не временных команд с доступом к памяти. Шаблоны команд класса В, показанные на фиг. 7 В, содержат: 1) в совокупность шаблонов 705 команд без доступа к памяти входят шаблоны 712 команд для операций управления с частичным округлением, управлением маской записи и без доступа к памяти и шаблоны 717 команд для операций vsize-типа (с переменным размером), управлением маской записи и без доступа к памяти; и 2) в совокупность шаблонов 720 команд с доступом к памяти входят шаблоны 727 команд управления маской записи и с доступом к памяти.

Обобщенный удобный для работы с векторами формат 700 команд содержит следующие поля, перечисленные ниже в порядке, показанном на фиг. 7А-7В.

Поле 740 формата - конкретная величина (величина идентификатора формата команды) в этом поле однозначно идентифицирует удобный для работы с векторами формат команд, и, таким образом, появление команд, имеющих этот в удобный для работы с векторами формат команд, в потоке команд. Поэтому указанное поле является опцией в том смысле, что оно не требуется при работе с наборами команд, имеющими только рассматриваемый обобщенный удобный для работы с векторами формат команд.

Поле 742 базовой операции - его содержание различает различные базовые операции.

Поле 744 индекса регистра - его содержание, непосредственно, или через генерирование адреса определяет местонахождение операнда-источника и операнда-адресата, будь они в регистрах или в памяти. Это поле содержит достаточное число битов, чтобы выбрать N регистров из регистрового файла размером P×Q (например, 32×512, 16×128, 32×1024, 64×1024). Хотя в одном из вариантов в эти N регистров могут входить до трех регистров-источников и один регистр-адресат, альтернативные варианты могут поддерживать большее или меньшее число регистров-источников и регистров-адресатов (например, могут поддерживать до двух источников, причем один из этих источников служит также адресатом, могут поддерживать до трех источников, причем один из этих источников служит также адресатом, могут поддерживать до двух источников и одного адресата).

Поле 746 модификатора - его содержание отличает появление команд в обобщенном формате векторных команд, определяющих доступ к памяти, от команд, которые этого не делают; иными словами, отличает шаблоны 705 команд без доступа к памяти от шаблонов 720 команд с доступом к памяти. Операции доступа к памяти осуществляют чтение и/или запись в иерархическую структуру памяти (в некоторых случаях указывают адреса источника и/или адресата с использованием величин, находящихся в регистрах), тогда как операции без доступа к памяти этого не делают (например, источник и адресаты являются регистрами). Тогда как в одном из вариантов это поле также выбирает между тремя разными способами вычислений адресов в памяти, альтернативные варианты могут поддерживать больше, меньше или другие способы вычисления адресов в памяти.

Поле 750 дополнительной операции - его содержание указывает, какую из множества разных операций следует выполнить в дополнение к базовой операции. Это поле зависит от контекста. В одном из вариантов настоящего изобретения это поле разделено на поле 768 класса, поле 752 альфа и поле 754 бета. Это поле 750 дополнительной операции позволяет выполнять общую группу операций в одной команде, а не в 2, 3 или 4 командах.

Поле 760 масштаба - его содержание позволяет масштабировать содержание поля индекса для генерирования адреса в памяти (например, для генерирования адреса по формуле 2масштаб · индекс + база (2scale · index + base)).

Поле 762А смещения - его содержание используется как часть генерирования адреса в памяти (например, для генерации адреса в памяти с использованием формулы 2масштаб · индекс + база + смещение (2scale · index + base + displacement)).

Поле 762В фактора смещения (отметим, что наложение поля 762А смещения непосредственно на поле 762В фактора смещения указывает, что используется одно или другое из этих полей) - его содержание используется как часть процедуры генерирования адреса; это поле задает фактор смещения, который должен быть масштабирован по размеру единицы доступа к памяти (N) - где N обозначает число байтов в единице данных при доступе к памяти (например, для генерирования адреса в памяти с использованием формулы 2масштаб · индекс + база + масштабированное смещение (2scale · index + base + scaled displacement)). Избыточные младшие биты игнорируются, так что содержание поля фактора смещения умножают на полный размер (N) операндов в памяти для генерирования окончательного смещения, которое должно быть использовано при вычислении эффективного адреса. Величину N определяет аппаратура процессора во время выполнения программы на основе поля 774 полного кода операции (будет здесь описано позднее) и поля 754С манипуляции данными. Поле 762А смещения и поле 762В фактора смещения являются опциями в том смысле, что эти поля не используются в шаблонах 705 команд без доступа к памяти и/или в других вариантах могут применяться только одно из этих двух полей или ни одного.

Поле 764 ширины элемента данных - его содержание указывает, какое из множества возможных значений ширины элементов данных следует использовать (в некоторых вариантах - для всех команд; в других вариантах - только для некоторых команд). Это поле является опцией в том смысле, что оно не требуется, если поддерживается только одно значение ширины элементов данных, и/или если поддержка различных значений ширины элементов данных осуществляется с использованием некоторых аспектов кодов операций.

Поле 770 маски записи - его содержание управляет, на основе позиций элементов данных, отражает ли позиция элемента данных в векторном операнде-адресате результат базовой операции и дополнительной операции. Шаблоны команд класса А поддерживают объединяющее маскирование при записи (merging-writemasking), а шаблоны команд класса В поддерживают и объединяющее, и обнуляющее маскирование при записи. В случае объединения векторные маски позволяют любую группу элементов в адресате защитить от обновления при выполнении любой операции (заданной посредством базовой операции и дополнительной операции); в другом варианте - сохраняет старую величину каждого элемента в адресате, когда соответствующий бит маски равен 0. Напротив, при обнулении векторные маски позволяют любую группу элементов адресата обнулить во время выполнения какой-либо операции (заданной посредством базовой операции и дополнительной операции); в одном из вариантов элемент адреса делают равным 0, когда соответствующий бит маски имеет значение 0. Подмножеством этой функции является способность управлять длиной вектора выполняемой операции (иными словами, модифицируется размер совокупности элементов от первого элемента до последнего); однако нет необходимости, чтобы модифицируемые элементы располагались последовательно один за другим. Таким образом, поле 770 маски записи позволяет выполнять частичные векторные операции, включая загрузки, сохранения, арифметические операции, логические операции и т.п. Хотя в описанных здесь вариантах настоящего изобретения содержание поля 770 маски записи выбирает из ряда регистров масок записи один регистр, содержащий маску записи, которую нужно использовать (и, таким образом, содержание поля маски записи косвенно указывает, что должно быть применено маскирование), альтернативные варианты вместо этого или в дополнение к этому допускают, чтобы содержание поля 770 маски записи прямо определяло маскирование, которое должно быть произведено.

Поле 772 непосредственной адресации - его содержание позволяет определить непосредственную адресацию. Это поле является опцией в том смысле, что его нет в реализации обобщенного удобного для работы с векторами формата, не поддерживающего непосредственную адресацию, и этого поля нет в командах, не использующих непосредственную адресацию.

Поле 768 класса - его содержание позволяет отличать различные классы команд. Применительно к фиг. 7А-В содержание этого поля осуществляет выбор между командами класса А и командами класса В. На фиг. 7А-В квадраты со скругленными углами использованы для индикации, что в этом поле присутствует конкретная величина (например, класс А 768А и класс В 768 В для поля класса 768 на фиг. 7А-В, соответственно).

Шаблоны команд класса А

В случае шаблонов 705 команд класса А без доступа к памяти поле 752 альфа интерпретируют как поле RS 752А, содержание которого различает, какой из разных типов дополнительных операций нужно выполнить (например, округление 752А.1 и преобразование данных 752А.2 определены, соответственно, для шаблонов команд 710 для операции типа округления и без доступа к памяти и для операции типа преобразования данных и без доступа к памяти), тогда как поле 754 бета различает, какую операцию определенного типа следует выполнить. В шаблонах 705 команд без доступа к памяти отсутствуют поле 760 масштаба, поле 762А смещение и поле 762В фактора смещения.

Шаблоны команд без доступа к памяти - Операции типа управления полным округлением

В шаблоне 710 команды операции типа управления полным округлением и без доступа к памяти поле 754 бета интерпретируют, как поле 754А управления округлением, содержание которого обеспечивает статическое округление. Тогда как в описываемых вариантах настоящего изобретения поле 754А управления округлением содержит поле 756 подавления всех исключений с плавающей запятой (SAE) и поле 758 управления операцией округления, альтернативные варианты могут поддерживать кодирование обоих этих принципов в одном и том же поле, либо иметь только один из этих принципов/полей (например, могут иметь только поле 750 управления операцией округления).

Поле 756 SAE - его содержание определяет, отключать или нет сообщения об особых ситуациях (событиях исключений); когда содержание поля 756 SAE указывает, что подавление включено, конкретная команда не сообщает о каких либо флагах исключений с плавающей запятой и не запускает какую-либо программу обработки исключений с плавающей запятой.

Поле 758 управления операцией округления - его содержание определяет, какую из групп операций округления выполнить (например, округление вверх, округление вниз, округление по отношению к нулю и округление до ближайшего целого). Таким образом, поле 758 управления операцией округления позволяет изменять режим округления от команды к команде. В одном из вариантов настоящего изобретения, в котором процессор содержит регистр для определения режимов округления, содержание поля 758 управления операцией округления превалирует над величиной, записанной в регистре.

Шаблоны команд без доступа к памяти - операция типа преобразования данных

В шаблоне 715 команды для операции типа преобразования данных без доступа к памяти поле 754 бета интерпретировано как поле 754В преобразования данных, содержание которого указывает, какое именно из ряда преобразований данных следует выполнить (например, не преобразовывать данные, преобразовать ссылки, передать в режиме широкого вещания).

В случае шаблона 720 команды класса А с доступом к памяти поле 752 альфа интерпретируют как поле 752В рекомендации вытеснения, содержание которого указывает, какую именно рекомендацию вытеснения следует использовать (на фиг. 7А, временное 752В.1 и не временное 752В.2, соответственно, определены для доступа к памяти, шаблон 725 временной команды с доступом к памяти и шаблон 730 не временной команды с доступом к памяти), тогда как поле 754 бета интерпретируют как поле 754С манипуляции данными, содержание которого указывает, какой именно из ряда видов операций манипуляции данными (также именуемых примитивами) следует выполнить (например, не манипулировать данными, передавать в режиме вещания, преобразовать источник вверх и преобразовать адресат вниз). Шаблоны 720 команд с доступом к памяти содержат поле 760 масштаба и, в качестве опции, поле 762А смещения или поле 762В масштаба смещения.

Команды векторной памяти осуществляют загрузку векторов из памяти и сохранение векторов в памяти с поддержкой преобразования. Как и в случае обычных векторных команд, команды векторной памяти передают данные из/в память по элементам данных, причем, передача каких именно элементов происходит, реально обнаруживается содержание векторной маски, выбранной в качестве маски записи.

Шаблоны команд с доступом к памяти - временные

Под временными данными понимают данные, которые вероятно будут использованы повторно достаточно скоро, чтобы получить выигрыш от кэширования. Это, однако, всего лишь рекомендация, так что разные процессоры могут реализовать ее различными способами, включая полное игнорирование такой рекомендации.

Шаблоны команд с доступом к памяти - не временные

Под не временными данными понимают данные, которые вероятно не будут использованы повторно достаточно скоро, чтобы получить выигрыш от кэширования в кэше уровня 1, и которым следует отдать приоритет при вытеснении. Это, однако, всего лишь рекомендация, так что разные процессоры могут реализовать ее различными способами, включая полное игнорирование такой рекомендации.

Шаблоны команд класса В

В случае шаблонов команд класса В поле 752 альфа интерпретируют в качестве поля 752С управления маской записи (Z), содержание которого указывает, должно ли маскирование при записи, управляемое эти полем 770 маски записи, быть объединяющим или обнуляющим.

В случае шаблонов 705 команд класса В без доступа к памяти часть поля 754 бета интерпретируют как поле RL 757А, содержание которого указывает, какой из различных типов дополнительных операций следует выполнить (например, округление 757А.1 и длина вектора (VSIZE) 757А.2, соответственно, определены для шаблона 712 команды типа операции управления частичным округлением, с управлением маской записи и без доступа к памяти, и для шаблона 717 команды типа операции установления длины вектора VSIZE, с управлением маской записи и без доступа к памяти), тогда как остальная часть поля 754 бета указывает, какую именно операцию определенного первой частью типа следуют выполнить. В шаблонах 705 команд без доступа к памяти отсутствуют поле 760 масштаба, поле 762А смещения и поле 762В масштаба смещения.

В шаблоне 710 команды типа операции управления частичным округлением с управлением маской записи и без доступа к памяти остальную часть поля 754 бета интерпретируют как поле 759А операции округления при отключенном сообщении о событиях исключения (конкретная команда не сообщает о каких-либо флагах исключений с плавающей запятой и не запускает какую-либо программу обработки исключений с плавающей запятой).

Поле 759А управления операцией округления - точно так же, как для поля 758 управления операцией округления, его содержание указывает, какую из групп операций округления следует выполнить (например, округление вверх, округление вниз, округление по отношению к нулю и округление до ближайшего целого). Таким образом, поле 759А управления операцией округления позволяет изменять режим округления от команды к команде. В одном из вариантов настоящего изобретения, в котором процессор содержит регистр для определения режимов округления, содержание поля 750 управления операцией округления превалирует над величиной, записанной в регистре.

В шаблоне 717 команды типа операции установления длины VSIZE вектора, с управлением маской записи и без доступа к памяти остальную часть поля 754 бета интерпретируют как поле 759В длины вектора, содержание которого указывает, какую из ряда возможных длин вектора данных нужно применить (например, 128, 256 или 512 байт).

В случае шаблона 720 команд класса В с доступом к памяти часть поля 754 бета интерпретируют как поле 757 В вещания, содержание которого указывает, следует ли выполнять операцию манипуляции с данными типа широкого вещания, тогда как остальную часть поля 754 бета интерпретируют как поле 759В длины вектора. Шаблоны 720 команд с доступом к памяти содержат поле 760 масштаба и могут в качестве опций содержать поле 762А смещения или поле 762В масштаба смещения.

Применительно к обобщенному удобному для работы с векторами формату 700 команд поле 774 полного кода операции содержит поле 740 формата, поле 742 базовой операции и поле 764 ширины элемента данных. Хотя показан один из вариантов, в котором поле 774 полного кода операции содержит все эти поля, в вариантах, которые не поддерживают все перечисленные поля, это поле полного кода операции содержит меньшее число полей. Указанное поле 774 полного кода операции предоставляет код операции.

Перечисленные поле 750 дополнительной операции, поле 764 ширины элемента данных и поле 770 маски записи позволяют определить эти характеристики для каждой команды в обобщенном удобном для работы с векторами формате команд.

Сочетание поля маски записи и поля ширины элемента данных создает типовые команды в том смысле, что они позволяют применять маску на основе ширины элементов данных.

Разнообразные шаблоны команд, относящихся к классу А и классу В, обладают преимуществами в различных ситуациях. В некоторых вариантах настоящего изобретения различные процессоры или различные ядра процессоров могут поддерживать только класс А, только класс В или оба класса. Например, обладающее высокими характеристиками ядро для выполнения операций не по порядку, предназначенное для вычислений общего назначения, может поддерживать только класс В, ядро, предназначенное для графических и/или научных (скоростных) вычислений, может поддерживать только класс А, а ядро, предназначенное и для вычислений общего назначения, и для графических и/или научных вычислений, может поддерживать оба класса (безусловно, ядро, имеющее некоторую смесь шаблонов и команд из обоих классов, но не все шаблоны и команды из обоих классов, находится в сфере охвата настоящего изобретения). Кроме того, один процессор может иметь несколько ядер, причем все ядра могут поддерживать один и тот же класс, либо разные ядра могут поддерживать различные классы. Например, в процессоре с раздельными графическими ядрами и ядрами общего назначения одно из графических ядер, предназначенное главным образом для графических и/или научных вычислений, может поддерживать только класс А, тогда как одно или несколько ядер общего назначения могут быть обладающими высокими характеристиками ядрами с выполнением операций не по порядку и переименованием регистров, предназначенными для вычислений общего назначения, и поддерживать только класс В. Другой процессор, не имеющий графического ядра, может содержать одно или несколько ядер общего назначения с выполнением операций по порядку или не по порядку, поддерживающих оба класса - и класс А и класс В. Безусловно, в различных вариантах настоящего изобретения признаки из одного класса могут быть также реализованы в другом классе. Программы, записанные на языке высокого уровня, могут быть приведены (например, непосредственно во время компиляции или статической компиляции) к разнообразным исполняемым формам, и в том числе: 1) форма, содержащая только команды класса(ов), поддерживаемого целевым процессором, который, как предполагается, будет выполнять эту программу; или 2) форма, содержащая альтернативные процедуры, написанные с использованием различных сочетаний команд из всех классов, и имеющая управляющий код, выбирающий процедуры для исполнения на основе команд, поддерживаемых процессором, который выполняет программу в текущий момент.

Пример специального удобного для работы с векторами формата команд

Фиг. 8 представляет блок-схему, иллюстрирующую пример специального удобного для работы с векторами формата команд согласно вариантам настоящего изобретения. На фиг. 8 показан специальный удобный для работы с векторами формат 800 команд, являющийся определенным в том смысле, что он определяет позиции, размеры, интерпретацию и порядок полей, равно как и значения для некоторых из этих полей. Такой определенный удобный для работы с векторами формат 800 команд может быть использован для расширения набора команд х86, вследствие чего некоторые поля аналогичны или совпадают с полями, используемыми в существующем наборе команд х86 или его расширении (например, AVX). Этот формат остается совместим с полем кодирования префикса, полем байта действительного кода операции, полем MOD R/M, полем SIB, полем смещения и полями непосредственной адресации в существующем наборе команд х86 с расширениями. Показаны изображенные на фиг. 7 поля, на которые отображаются поля, представленные на фиг. 8.

Следует понимать, что хотя варианты настоящего изобретения описаны со ссылками на определенный удобный для работы с векторами формат 800 команд в контексте обобщенного удобного для работы с векторами формата 700 команд в целях иллюстрации, настоящее изобретение не ограничивается определенным удобным для работы с векторами форматом 800 команд, за исключением случаев, где это оговорено отдельно. Например, обобщенный удобный для работы с векторами формат 700 команд рассматривает разнообразные возможные размеры различных полей, тогда как определенный удобный для работы с векторами формат 800 команд показан как имеющий поля конкретных размеров. В качестве конкретного примера, тогда как поле 764 ширины элементов данных показано в определенном удобном для работы с векторами формате 800 команд в виде однобитового поля, настоящее изобретение этим не ограничивается (иными словами, обобщенный удобный для работы с векторами формат 700 команд может иметь дело и с другими размерами поля 764 ширины элементов данных).

Обобщенный удобный для работы с векторами формат 700 команд содержит следующие поля, перечисленные ниже в порядке, показанном на фиг. 8А.

Префикс EVEX Prefix (байты 0-3) 802 - кодирован в форме четырех байтов.

Поле 740 формата (EVEX байт 0, биты [7:0]) - первый байт (EVEX байт 0) является полем 740 формата и содержит 0×62 (уникальное значение, используемое для указания удобного для работы с векторами формата команд в одном из вариантов настоящего изобретения).

Байты со второго по четвертый (EVEX байты 1-3) содержат ряд битовых полей, предоставляющих специальные возможности.

Поле 805 REX (EVEX байт 1, биты [7-5]) - содержит битовое поле EVEX.R (EVEX байт 1, бит [7] - R), битовое поле EVEX.X (EVEX байт 1, бит [6] - X) и 757 ВЕХ байт 1, бит[5] - В). Битовые поля EVEX.R, EVEX.X и EVEX.B выполняют такие же функции, как соответствующие битовые поля VEX, и кодированы с использованием формы дополнения до 1, т.е. ZMM0 кодировано как 1111В, ZMM15 кодировано как 0000 В. Другие поля команды кодируют младшие три бита регистровых индексов, как это известно в технике (rrr, XXX и bbb), так что Rrrr, Хххх и Bbbb могут быть получены путем суммирования EVEX.R, EVEX.X и EVEX.B.

Поле 710 REX′ - это первая часть поля 710 REX′ и представляет собой битовое поле EVEX.R′ (EVEX байт 1, бит [4] - R′), используемое для кодирования либо верхних 16, либо нижних 16 из расширенной группы 32 регистров. В одном из вариантов настоящего изобретения этот бит, вместе с другими, как указано ниже, сохраняется в формате инвертированного бита, чтобы отличить (в хорошо известном 32-битовом режиме х86) от команды BOUND, действительный код операции для которой равен 62, но не приемлет в поле MOD R/M (описано ниже) величины 11 в поле MOD; альтернативные варианты настоящего изобретения не сохраняют этот и другие биты, указанные ниже, в инвертированном формате. Величина 1 используется для кодирования нижних 16 регистров. Другими словами, параметр R′Rrrr посредство сочетания EVEX.R′, EVEX.R и другого RRR из других полей.

Поле 815 отображения кода операции (EVEX байт 1, биты [3:0] - mmmm) - его содержание кодирует ведущий байт кода операции в неявном виде (OF, OF 38 или OF 3).

Поле 764 ширины элемента данных (EVEX байт 2, бит [7] - W) - представлено записью EVEX.W. Параметр EVEX.W используется для задания степени разбиения (размера) типа данных (либо 32-битовый элемент данных, либо 64-битовый элемент данных).

Поле 820 EVEX.vvvv (EVEX байт 2, биты [6:3] - ww) - роль параметра EVEX.ww может состоять в следующем: 1) EVEX.vvvv кодирует первый операнд-источник регистра, заданный в инвертированной (дополнение до 1) форме и действительный для команд с 2 или более операндами-источниками; 2) EVEX.vvvv кодирует операнд-адресат регистра, заданный в форме дополнения до 1 для некоторых сдвигов вектора; или 3) EVEX.vvvv не кодирует ни один операнд, поле зарезервировано и должно содержать 1111b. Таким образом, поле 820 EVEX.vvvv кодирует 4 младших бита определяется первого регистра-источника, сохраненного в инвертированной (дополнение до 1) форме. В зависимости от команды дополнительное другое битовое поле EVEX используется для увеличения размера определителя до 32 регистров.

Поле 768 класса EVEX.U (EVEX байт 2, бит [2]-U) - если EVEX.U = 0, это означает класс А или EVEX.U0; если EVEX.U = 1, это означает класс В или EVEX.U1.

Поле 825 кодирования префикса (EVEX байт 2, биты [1:0]-рр) - предоставляет дополнительные для поля базовой операции. В дополнение к поддержке существующих команд SSE в формате префикса EVEX это поле имеет также преимущество сжатия префикса SIMD (вместо того, чтобы требовать байт для выражения префикса SIMD, префикс EVEX требует только 2 бита). В одном из вариантов для поддержки существующих команд SSE, использующих префикс SIMD, (66Н, F2H, F3H) и в существующем формате, и в формате префикса EVEX, такие существующие префиксы SIMD кодируют в поле кодирования префикса SIMD; и во время работы расширяют до формата существующих префиксов SIMD перед тем, как передать в матрицу PLA декодера (так что эта матрица PLA может обрабатывать и существующий формат, и формат EVEX этих существующих команд без модификации). Хотя более новые команды могут использовать содержание поля кодирования префикса EVEX непосредственно в качестве расширения кода операции, некоторые варианты расширяют аналогичным образом для согласованности, но позволяют задавать различные значения с использованием этих существующих префиксов SIMD. Альтернативный вариант может изменить конфигурацию матрицы PLA для поддержки кодирования 2-битового префикса SIMD, и потому не требует расширения.

Поле 752 альфа (EVEX байт 3, бит [7] - ЕН; известно так же, как EVEX.EH, EVEX.rs, EVEX.RL, EVEX.write mask control и EVEX.N; и обозначено α) - как было описано ранее, это поле зависит от контекста.

Поле 754 бета (EVEX байт 3, биты [6:4] - SSS, известно так же, как EVEX.s2-0, EVEX.r2-0, EVEX.rrl, EVEX.LL0, EVEX.LLB; также иллюстрировано посредством βββ) - как было описано ранее, это поле зависит от контекста.

Поле 710 REX′ - это остальная часть поля REX′ и представляет собой битовое поле EVEX.V (EVEX байт 3, бит [3] - V), которое может быть использовано для кодирования либо верхних 16, либо нижних 16 регистров из расширенной группы 32 регистров. Этот бит сохраняют в инвертированном формате. Величину 1 используют для кодирования нижних 16 регистров. Другими словами, VVVVV образовано сочетанием EVEX.V, EVEX.vvvv.

Поле 770 маски записи (EVEX байт 3, биты [2:0]-kkk) - его содержание задает индекс регистра в группе регистров маски записи, как описано ранее. В одном из вариантов настоящего изобретения специальная величина EVEX.kkk = 000 имеет специальный характер, предполагая, что для конкретной команды никакая маска записи не используется (это может быть реализовано различными способами, включая использование маски записи, в которой аппаратно заданы все единицы, или аппаратуру, обходящую маскирующую аппаратуру).

Поле 830 действительного кода операции (байт 4) также известно как байт кода операции. В этом поле определена часть кода операции.