Изобретение относится к классу носителей информации, используемых с машинами, по меньшей мере, частично предназначенными для переноса цифровой информации, отличающихся видом цифровой маркировки, например формой, характером, кодом.

Предлагаемое изобретение направлено на решение задачи повышения скорости записи и считывания данных на флэш-карту памяти, использующую последовательный интерфейс.

В различных устройствах, например цифровых фото- и видеокамерах, портативных компьютерах предусматривается использование внешнего носителя - флэш-карты - для хранения медиаданных и другой информации, принятых в настоящее время стандартов (Secure Digital, Secure Digital High Capacity и др.) Функциональные параметры указанных устройств, например частота кадров при фотосъемке, а также продолжительность работы от встроенного источника до повторной перезарядки определяется, в том числе, скоростью записи данных на установленную флэш-карту.

В существующих твердотельных устройствах хранения информации, содержащих в качестве носителя флэш-память, скорость обмена данными с внешним устройством определяется быстродействием встроенного микроконтроллера, выполняющего преобразование адресного пространства, организацию файловой системы, копирования и стирания, исправление ошибок данных и другие функции. При этом операции чтения блоков данных из памяти и записи в памяти являются наиболее ресурсоемкими.

Один из вариантов повышения скорости записи и считывания данных на флэш-карту заключается в применении в ее составе аппаратных контроллеров прямого доступа к памяти, позволяющих производить считывание и запись блоков данных во встроенную флэш-память без привлечения ядра микроконтроллера, тем самым существенно ускоряя процесс переноса информации. Это позволяет исключить операции копирования блоков данных между внешним устройством и флэш-памятью из программы встроенного контроллера. При этом системные шины процессора не занимаются, следовательно, снижаются требования к его быстродействию и производительности, что в конечном итоге приводит к общему снижению энергопотребления флэш-картой во время операций чтения и записи.

Известно устройство, описанное в [1], «Composite Compact Flash Card» (Объединенная компакт-флэш-карта), по схожести признаков и функциональному назначению схожее с предлагаемым изобретением и содержащее соединитель интерфейса Compact Flash (CF Interface Connector), контроллер (Controller), оперативное запоминающее устройство (ОЗУ, RAM), постоянное запоминающее устройство, (ПЗУ, ROM), схему управления слоями (Management Layer Circuit), блок флэш-памяти (Flash memory), блок обеспечения протокола (Protocol Layer), схему обнаружения переключателя (Switch Detecting Circuit), контактирующее устройство (Slot) и механический переключатель (Mechanical Switch), соединитель интерфейса Compact Flash, ОЗУ, ПЗУ, схема управления слоями, блок обеспечения протокола и схема обнаружения переключателя соединены с контроллером, блок флэш-памяти соединен с со схемой управления слоями, механический переключатель соединен со схемой обнаружения переключателя и контактирующим устройством, причем внешняя шина обмена данными объединенной компакт-флэш карты соединена с контроллером и является интерфейсом стандарта Compact Flash.

Основной недостаток объединенной компакт-флэш карты заключается в относительно низкой скорости обмена данными внешних устройств с флэш-памятью, входящей в ее состав, вследствие того, что все операции обмена данными выполняются последовательно контроллером.

Известно устройство, описанное в [2], «SD Memory Card For Extension Of Function», карта памяти стандарта SD (Secure Digital) с расширенной функцией, содержащее блок внешнего интерфейса (SD Card Interface), блок интерфейса флэш-памяти (Memory Interface), блок флэш-памяти (Flash memory), микропроцессор (Microprocessor), периферийный блок (Peripheral Module), ПЗУ (ROM), ОЗУ программ (RAM), блок кодирования (Encoding Module), блок интерфейса связи (Link Interface), адаптер контактной карты (Contact IC Card Adaptor), радиочастотный блок (RF Circuit) и антенный блок (Antenna Unit), причем блоки: внешнего интерфейса, интерфейса флэш-памяти, интерфейса связи, кодирования, а также ОЗУ программ, ПЗУ, периферийный блок и микропроцессор соединены между собой двунаправленной шиной данных, блок интерфейса флэш-памяти соединен с блоком флэш-памяти первой, а с блоком внешнего интерфейса - дополнительно восьмой двунаправленной шиной, блок интерфейса связи соединен девятой и десятой двунаправленными шинами с адаптером контактной карты и радиочастотным блоком соответственно, антенный блок соединен с блоком интерфейса связи одиннадцатой двунаправленной шиной, внешняя шина обмена данными устройства соединена с блоком внешнего интерфейса и является интерфейсом стандарта Secure Digital.

Недостатком данного устройства является то, что в нем не ставится и не решается задача повышения скорости считывания и записи данных во встроенную флэш-память носителя информации. Операции копирования блоков данных производятся последовательно контроллером без использования аппаратного прямого доступа к памяти.

По схожести признаков с предлагаемым изобретением и по схожести функционального назначения данное устройство выбрано за прототип.

Сущностью изобретения является съемный носитель информации, обладающий повышенной скоростью доступа внешнего устройства к встроенной флэш-памяти.

Сопоставительный анализ показывает, что предлагаемый носитель информации отличается тем, что устройство, содержащее признаки и связи прототипа: ОЗУ программ, ПЗУ, блок флэш-памяти, микропроцессор, а также соединенные с ним двунаправленной шиной данных блок внешнего интерфейса и блок интерфейса флэш-памяти, соединенный первой двунаправленной шиной с блоком флэш-памяти, а внешняя шина обмена данными носителя информации соединена с блоком внешнего интерфейса, дополнительно включает первый и второй контроллеры прямого доступа к памяти, коммутатор, первое и второе ОЗУ данных, а также ОЗУ физических секторов, причем первый контроллер прямого доступа к памяти соединен с блоком внешнего интерфейса второй, а с коммутатором - третьей двунаправленной шиной, коммутатор и ОЗУ физических секторов подсоединены к двунаправленной шине данных, первое и второе ОЗУ данных соединены с коммутатором соответственно четвертой и пятой двунаправленными шинами, второй контроллер прямого доступа к памяти соединен с коммутатором шестой, а с блоком интерфейса флэш-памяти - седьмой двунаправленной шиной, а микропроцессор, ОЗУ программ и ПЗУ соединены между собой двунаправленной шиной команд, причем коммутатор осуществляет переключение потоков данных между третьей, четвертой, пятой и шестой двунаправленными шинами.

Следовательно, носитель информации удовлетворяет критерию «новизна».

Сравнение с другими техническими решениями показывает, что предлагаемый носитель информации обладает признаками, позволяющими обеспечивать повышенную скорость доступа к памяти и экономию энергии источника питания внешнего устройства за счет организации в носителе прямого доступа к памяти и снижения производительности встроенного процессора.

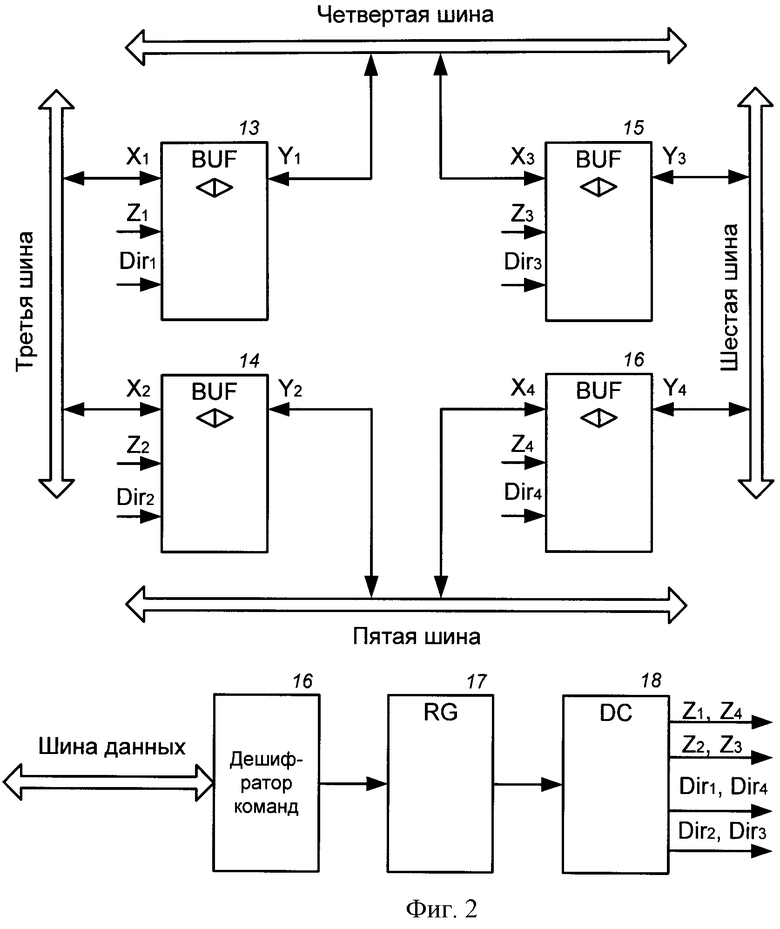

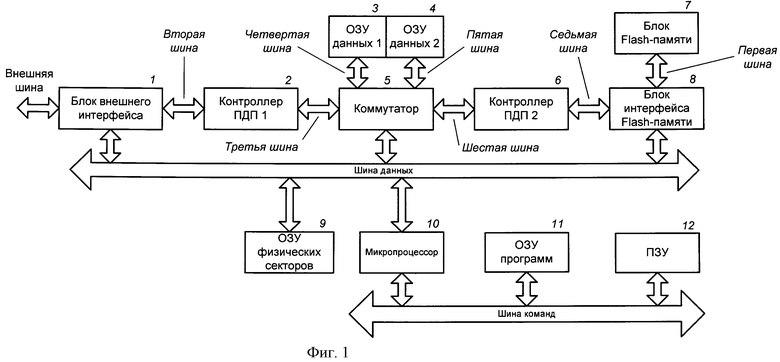

Изобретение поясняется следующими графическими материалами:

фиг.1 - структурная схема съемного носителя информации с повышенной скоростью доступа внешнего устройства к встроенной флэш-памяти;

фиг.2 - структурная схема коммутатора, входящего в состав съемного носителя информации.

Носитель информации с повышенной скоростью доступа содержит блок внешнего интерфейса 1, первый контроллер прямого доступа к памяти 2, ОЗУ данных: первое 3 и второе 4, коммутатор 5, второй контроллер прямого доступа к памяти 6, блок флэш-памяти 7, блок интерфейса флэш-памяти 8, ОЗУ физических секторов 9, микропроцессор 10, ОЗУ программ 11, ПЗУ 12, причем микропроцессор 10 соединен двунаправленной шиной данных с блоком внешнего интерфейса 1, коммутатором 5, ОЗУ физических секторов 9 и блоком интерфейса флэш-памяти 8, соединенным первой двунаправленной шиной с блоком флэш-памяти 7, первый контроллер прямого доступа к памяти 2 соединен с блоком внешнего интерфейса 1 второй, а с коммутатором 5 - третьей двунаправленной шиной, ОЗУ данных: первое 3 и второе 4 соединены с коммутатором 5 соответственно четвертой и пятой двунаправленными шинами, второй контроллер прямого доступа к памяти 6 соединен с коммутатором 5 шестой, а с блоком интерфейса флэш-памяти 8 - седьмой двунаправленной шиной, а микропроцессор 10, ОЗУ программ 11 и ПЗУ 12 соединены между собой двунаправленной шиной команд, внешняя шина обмена данными носителя информации соединена с блоком внешнего интерфейса 1.

Носитель информации с повышенной скоростью доступа работает следующим образом.

При функционировании носителя предусмотрено два основных режима: записи и считывания информации.

В режиме записи информации на носитель по внешней шине обмена данными с внешнего устройства поступает команда записи, после чего блок внешнего интерфейса 1 передает ответный сигнал готовности по упомянутой шине внешнему устройству, и далее команда записи по шине данных передается микропроцессору 10. Последний, получая упомянутую команду, передает по шине данных конфигурационные команды, переводящие блок внешнего интерфейса 1 в режим чтения пакетов входных данных с внешней шины, блок интерфейса флэш-памяти 8 - в режим записи данных в блок флэш-памяти 7, а коммутатор 5 - на передачу пакетов данных по соответствующим шинам в направлении от первого контроллера прямого доступа к памяти 2 к первому ОЗУ данных 3 и от второго ОЗУ данных 4 - к второму контроллеру прямого доступа к памяти 6.

При поступлении пакета данных с внешнего устройства последний принимается блоком внешнего интерфейса 1 по сигналу микропроцессора 10 и посредством первого контроллера прямого доступа к памяти 2 через коммутатор 5 записывается в первое ОЗУ данных 3.

После окончания цикла записи микропроцессором 10 вычисляется физический адрес пакета записываемых данных, который передается по шине данных блоку интерфейса флэш-памяти 8 и записывается в ОЗУ физических секторов 9. Далее по сигналу микропроцессора 10, передаваемому по шине данных, блок интерфейса флэш-памяти 8 осуществляет чтение записанного ранее пакета данных из второго ОЗУ данных 4 посредством второго контроллера прямого доступа к памяти 6 через коммутатор 5 и запись упомянутого пакета в блок флэш-памяти 7 по вычисленному физическому адресу. В то же время блок внешнего интерфейса 1 осуществляет чтение следующего пакета данных, поступающего по внешней шине. При поступлении очередного пакета данных с внешнего устройства процесс циклически повторяется.

Таким образом, запись текущего пакета из блока внешнего интерфейса 1 в первое ОЗУ данных 3 и запись предыдущего - из второго ОЗУ данных 4 в блок флэш-памяти 7 производится одновременно, посредством первого 2 и второго 6 контроллеров прямого доступа к памяти без участия микропроцессора 10 как переносчика данных.

В режиме считывания информации с носителя по внешней шине обмена данными с внешнего устройства поступает команда чтения, после чего блок внешнего интерфейса 1, как и в режиме записи, передает ответный сигнал готовности внешнему устройству, и далее команда чтения по шине данных передается микропроцессору 10. Последний, получая упомянутую команду, передает по шине данных конфигурационные команды, переводящие блок внешнего интерфейса 1 в режим записи пакетов входных данных на внешнюю шину, блок интерфейса флэш-памяти 8 - в режим чтения данных из блока флэш-памяти 7, а коммутатор 5 - на передачу пакетов данных по соответствующим шинам в направлении от второго контроллера прямого доступа к памяти 6 к второму ОЗУ данных 4 и от первого ОЗУ данных 3 - к первому контроллеру прямого доступа к памяти 2.

Микропроцессором 10 из ОЗУ физических секторов 9 извлекается физический адрес пакета считываемых данных, который передается по шине данных блоку интерфейса флэш-памяти 8. Последний по сигналу микропроцессора 10 посредством второго контроллера прямого доступа к памяти 6 считывает пакет данных из блока флэш-памяти 7 и через коммутатор 5 записывает его во второе ОЗУ данных 4.

После окончания цикла записи по сигналу микропроцессора 10, передаваемому по шине данных, блок внешнего интерфейса 1 осуществляет чтение записанного ранее пакета данных из первого ОЗУ данных 3 посредством первого контроллера прямого доступа к памяти 2 через коммутатор 5 и передачу упомянутого пакета на внешнюю шину носителя. В это же время блок интерфейса флэш-памяти 8 осуществляет чтение следующего пакета данных из блока флэш-памяти 7 и передачу его в направлении второго ОЗУ данных 4. Далее процесс считывания данных из флэш-памяти циклически повторяется.

Таким образом, считывание текущего пакета из блока флэш-памяти 7, запись во второе ОЗУ данных 4 и выдача предыдущего из первого ОЗУ данных 3 на внешнюю шину производится одновременно, посредством второго 6 и первого 2 контроллеров прямого доступа к памяти без участия микропроцессора 10 как переносчика данных. Последний выполняет только обработку команд внешнего устройства, выдачу по соответствующей шине конфигурационных команд и управляющих сигналов блокам-переносчикам данных, вычисление адреса чтения и записи пакета данных в блок флэш-памяти 7 и управление взаимодействием блоков, включенных в состав носителя информации. Благодаря низкой периодичности выполнения указанных функций - не чаще чем один раз за блок передаваемых данных - от микропроцессора 10 не требуется высокой производительности, и тактовая частота его может быть снижена, в отличие от тактовой частоты процессоров, используемых в прототипах и непосредственно участвующих в передаче байтов или слов информации.

Следовательно, предлагаемый носитель обладает признаками, позволяющими обеспечивать повышенную скорость доступа к памяти и экономию энергии источника питания внешнего устройства за счет организации в носителе прямого доступа к памяти и снижения производительности встроенного микропроцессора.

Оперативное запоминающее устройство программ 11 и постоянное запоминающее устройство 12 совместно обеспечивают выполнение программы микропроцессора 10.

Постоянное запоминающее устройство 12 предназначено для хранения программы микропроцессора 10 и может быть, например, однократно программируемым.

Оперативное запоминающее устройство программ 11 предназначено для временного хранения данных программы микропроцессора 10 и может быть статическим. В представленной реализации носителя объем ОЗУ программ составляет 32 кбайт.

Оперативное запоминающее устройство физических секторов 9 предназначено для временного хранения таблиц соответствия физических адресов блоков данных, записанных в блоке флэш-памяти логическим адресам записанной информации и может быть статическим.

Например, для флэш-памяти объемом 32 Гбайт объем данных, хранимых в ОЗУ физических секторов 9 составит 16×2048=32768 слов разрядностью 11 бит (2047=211). Наличие указанного запоминающего устройства позволяет сократить объем ОЗУ программ 11 микропроцессора 10.

Микропроцессор 10 предназначен для обработки команд внешнего устройства, выдачи конфигурационных команд и управляющих сигналов блокам-переносчикам данных, вычисление адресов чтения и записи пакетов данных в блок флэш-памяти 7 и управление взаимодействием блоков, включенных в состав носителя информации. В качестве микропроцессора может быть использован любой RISC-процессор, обладающий внешними шинами команд и данных, набором базовых арифметических и логических команд и прерываний, а также в составе других блоков удовлетворяющий требованиям быстродействия и потребления, предъявляемым к конкретной реализации носителя информации. Например, может быть использован микроконтроллер A Tmega 103 фирмы Atmel (США) [3].

Оперативные запоминающие устройства данных: первое 3 и второе 4 идентичны, могут быть статическими и предназначены для временного хранения пакетов считываемых и записываемых данных, Объем первого и второго ОЗУ данных определяется исходя из длины пакета и в представленной реализации носителя составляет 16 кбайт.

Блок флэш-памяти 7 является общеизвестным признаком, может быть, например, запоминающим устройством типа NAND-Flash. Блок предназначен для энергонезависимого хранения пакетов данных, записываемых в носитель. В представленной реализации носителя объем флэш-памяти составляет 32 Гбайт.

Первый 2 и второй 6 контроллеры прямого доступа к памяти идентичны и предназначены для побайтного чтения из блока памяти и записи пакетов информации в блока памяти. Контроллеры прямого доступа являются известными техническими устройствами и могут быть реализованы, например, в виде устройства [4] «DMA Controller» (Конртоллер прямого доступа к памяти) и состоять из секвенсора (Sequencer), счетчика циклов (CYC Counter), счетчика транзакций (TRN Counter), генератора адреса источника (SRC Address Counter), генератора адреса получателя (DST Address Counter), управляющего регистра, соединенных общей двунаправленной шиной, схемы арбитража (Arbitration Circuit), соединенной двенадцатой двунаправленной шиной с секвенсором (Sequencer), регистра циклов (CYC Register), соединенного со счетчиком циклов, регистра адресов источника (SRC Address Register), соединенного с генератором адреса источника, регистра адресов получателя (DST Address Register), соединенного с генератором адреса получателя, общая двунаправленная шина контроллера является его входной и выходной двунаправленной шиной обмена данными.

Для первого контроллера ПДП 2 выходная двунаправленная шина обмена данными соединена со второй и третьей двунаправленными шинами носителя информации. Для второго контроллера ПДП 6 выходная двунаправленная шина обмена данными соединена с шестой и седьмой двунаправленными шинами носителя информации.

Блок интерфейса флэш-памяти 8 предназначен для обеспечения функции обмена пакетами данных с блоком флэш-памяти 7. Блок интерфейса флэш-памяти 8 может быть реализован, например, в виде устройства, описанного в [5] «NAND Flash Controller and Data Exchange Method Between NAND Flash Memory and NAND Flash Controller» (Контроллер NAND-флэш памяти и метод обмена данными между контроллером NAND-флэш памяти и NAND-флэш памятью) и состоять из интерфейса входной шины (Bus Timing Interface), управляющего регистра (Control Register), контроллера логики (Logic Controller), буфера данных (Data Buffer Region), блока выбора канала (Channel Selector), блок синхронизации флэш-памяти (Flash Timing Generator), интерфейс входной шины соединен тринадцатой двунаправленной шиной с управляющим регистром, четырнадцатой двунаправленной шиной - с буфером данных и пятнадцатой двунаправленной шиной - с блоком выбора канала, контроллер логики соединен шестнадцатой двунаправленной шиной с буфером данных, семнадцатой двунаправленной шиной - с блоком выбора канала, управляющий регистр соединен с контроллером логики и с блоком выбора канала, соединенным восемнадцатой двунаправленной шиной с блоком синхронизации флэш-памяти, который содержит подсоединение к двунаправленной шине обмена данными с флэш-памятью, являющейся первой двунаправленной шиной носителя информации, а интерфейс входной шины содержит подсоединение к двунаправленной шине обмена данными, являющейся седьмой двунаправленной шиной носителя информации.

Коммутатор 5 предназначен для переключения потоков передачи данных в направлении от первого контроллера прямого доступа к памяти 2 к первому ОЗУ данных 3 последовательно по третьей и четвертой двунаправленным шинам и от ОЗУ данных 4 ко второму контроллеру прямого доступа к памяти 6 - последовательно по пятой и шестой двунаправленным шинам, если накопитель функционирует в режиме записи либо в обратном направлении - в режиме считывания. Коммутатор управляется по шине данных.

Коммутатор 5 работает по следующему алгоритму.

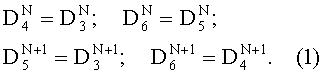

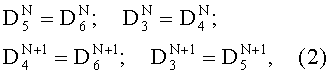

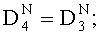

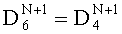

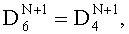

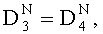

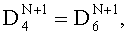

В режиме записи информации на носитель:

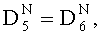

В режиме считывания информации с носителя:

где  - данные N-го пакета на k-й двунаправленной шине.

- данные N-го пакета на k-й двунаправленной шине.

Коммутатор 5 (фиг.2) может быть реализован, например, в виде устройства, состоящего из четырех двунаправленных буферов 13-16 с третьим (Z) состоянием, дешифратора команд процессора 17, регистра и двоичного дешифратора 18, вход данных X1 первого двунаправленного буфера с третьим состоянием 13 подсоединен к третьей двунаправленной шине, а его выход Y1 - к четвертой двунаправленной шине накопителя, вход данных Х2 второго двунаправленного буфера с третьим состоянием 14 подсоединен к третьей двунаправленной шине, а его выход Y2 - к пятой двунаправленной шине накопителя, вход данных Х3 третьего двунаправленного буфера с третьим состоянием 15 подсоединен к четвертой двунаправленной шине, а его выход Y3 - к шестой двунаправленной шине накопителя, вход данных Х4 четвертого двунаправленного буфера с третьим состоянием 16 подсоединен к пятой двунаправленной шине, а его выход Y4 - к шестой двунаправленной шине накопителя, дешифратор команд процессора 16 подсоединен к двунаправленной шине данных накопителя, выход дешифратора команд подсоединен ко входу данных регистра 17, выход которого соединен ко входу двоичного дешифратора 18, который содержит выходы Z1-Z4 и Dir1-Dir4, выходы Z1-Z4 двоичного дешифратора 18 каждый подсоединены к соответствующим входам выбора третьего состояния двунаправленных буферов с первого по четвертый 13-16, а выходы Dir1-Dir4 каждый - к соответствующим входам выбора направления указанных буферов.

Входы и выходы данных буферов с третьим состоянием с первого по четвертый 13-16 при подаче лог. «1» на входы выбора третьего состояния Z1-Z4 переходят в третье (Z) состояние, а подаче лог. «0» на указанные входы - в активное состояние, причем при подаче лог. «0» на входы выбора направления Dir1-Dir4, данные подаются на вход Xi i-го двунаправленного буфера с третьим состоянием (i=1…4), а снимаются с его выхода Yi. При подаче лог. «1» на входы выбора направления Dir1-Dir4, данные передаются через буферы с третьим состоянием в обратном направлении (от выхода Yi ко входу Xi).

Коммутатор 5 работает следующим образом.

При подаче микропроцессором 10 по шине данных команды записи или чтения информации на носитель и признака четности номера записываемого (считываемого) пакета N, на выходе дешифратора команд процессора 16 формируется соответствующее значение, которое записывается в регистр 17 и удерживается в нем до снятия команды. Двоичный дешифратор 18 по значению, содержащемуся в регистр 17, формирует двоичное кодовое слово, побитно подаваемое на входы выбора третьего состояния Z1-Z2 и входы выбора направления Dir1-Dir4 двунаправленных буферов с третьим состоянием с первого по четвертый 13-16, которые осуществляют коммутацию данных между соответствующими двунаправленными шинами.

Коммутация данных осуществляется в соответствии с формулами (1) и (2). Так, в режиме записи информации на носитель (1), для N-го пакета первый двунаправленный буфер с третьим состоянием 13 осуществляет передачу данных с третьей на четвертую, а четвертый двунаправленный буфер с третьим состоянием 16 - с пятой на шестую двунаправленную шину, а для N+1-го пакета - второй двунаправленный буфер с третьим состоянием 14 осуществляет передачу данных с третьей на пятую, а третий двунаправленный буфер с третьим состоянием 15 - с четвертой на шестую двунаправленную шину. В режиме чтения информации с носителя (2), для N-го пакета четвертый двунаправленный буфер с третьим состоянием 16 осуществляет передачу данных с шестой на пятую, а первый двунаправленный буфер с третьим состоянием 13 - с четвертой на третью двунаправленную шину, а для N+1-го пакета - третий двунаправленный буфер с третьим состоянием 15 осуществляет передачу данных с шестой на четвертую, а второй двунаправленный буфер с третьим состоянием 14 - с пятой на третью двунаправленную шину.

Двоичное кодовое слово дешифратора формируется в соответствии с таблицей, приведенной ниже.

Блок внешнего интерфейса 1 предназначен для обработки команд, поступающих носителю от внешнего устройства и выдачи команды процессору для запуска операции чтения или записи, а также двунаправленной передачи пакетов данных от внешнего интерфейса в первое и второе ОЗУ данных 3 и 4. Блок внешнего интерфейса 1 может функционировать, например, в стандарте «Secure Digital» и может быть реализован, например, в виде блока «SD Memory Controller», входящего в состав устройства «SD2.0 Memory Controller», описанного в [6] и состоящего из декодера команд (Cmd_Dec), второго дешифратора команд (Command Validator), генератора ответных команд (Resp_Gen), буфера (Buffer), приемопередатчика (Tx_Rx) и блока интерфейса процессора (CPU Interface), причем декодер команд, генератор ответных команд и приемопередатчик подсоединены к внешней двунаправленной шине обмена данными носителя информации, приемопередатчик подсоединен ко второй двунаправленной шине носителя информации, декодер команд соединен с дешифратором команд девятнадцатой двунаправленной шиной, буфер соединен с дешифратором команд и с блоком интерфейса процессора соответственно двадцатой и двадцать первой двунаправленными шинами, генератор ответных команд соединен с блоком интерфейса процессора двадцать второй двунаправленной шиной, а блок интерфейса процессора подсоединен к блок интерфейса процессора подсоединен к двунаправленной шине данных накопителя.

Источники информации

1. Патент US 7278583 B2 «Composite Compact Flash Card» от 09.10.2007 г.

2. Заявка US 2005/0224589 A1 «SD Memory Card For Extension Of Function» от 13.11.2005.

3. www.atmel.com/atmel/acrobat/doc2467.pdf.09451-AVR-02/07. ATMEL. 8-bit AVR Microcontroller with 128K Bytes In-System Programmable Flash. A Tmega 103. Official Datasheet.

4. Патент US 6728797 B2 «DMA Controller» от 27.04.2004.

5. Заявка US 2009/0094411 A1 «NAND Flash Controller and Data Exchange Method Between NAND Flash Memory and NAND Flash Controller» от 09.04.2009.

6. www.arasan.com/products/sd/SD-Mem-Ctrl-1-2-Flyer.pdf. Arasan «SD2.0 Memory Controller». Product Overview. Arasan Chip System Inc. Version 1.2b.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЬЮТЕРНАЯ СИСТЕМА | 2014 |

|

RU2579949C2 |

| УСТРОЙСТВО ПРЯМОГО ОТОБРАЖЕНИЯ АДРЕСОВ ДАННЫХ, РАСПОЛАГАЮЩИХСЯ ВО ВНЕШНЕМ ПОСЛЕДОВАТЕЛЬНОМ ПЗУ, В АДРЕСНОЕ ПРОСТРАНСТВО МИКРОПРОЦЕССОРНОГО ЯДРА, КОМПЬЮТЕРНАЯ СИСТЕМА И СПОСОБ ПЕРЕДАЧИ ДАННЫХ | 2014 |

|

RU2579942C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И ВЕДУЩЕЕ УСТРОЙСТВО | 2005 |

|

RU2348992C2 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ | 2009 |

|

RU2419139C1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Декодер контроллера твердотельного накопителя информации | 2021 |

|

RU2769562C1 |

| Способ передачи данных по шине, система связи для осуществления данного способа и устройство автоматической защиты для предотвращения аварийной ситуации на объекте управления | 2018 |

|

RU2705421C1 |

| УПРАВЛЯЮЩИЙ МОДУЛЬ | 2014 |

|

RU2569576C1 |

| ГИБРИДНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ЕДИНЫМ ИНТЕРФЕЙСОМ | 2007 |

|

RU2442211C2 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА ДЛЯ КОМПЬЮТЕРОВ ИНФОРМАЦИОННО-ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | 2006 |

|

RU2321055C2 |

Изобретение относится к носителям информации. Техническим результатом является обеспечение повышенной скорости доступа к памяти и экономии энергии источника питания внешнего устройства за счет организации в носителе прямого доступа к памяти и снижения производительности встроенного процессора. Съемный носитель информации с повышенной скоростью доступа содержит блок внешнего интерфейса, первый контроллер прямого доступа к памяти, первое и второе оперативные запоминающие устройства данных, коммутатор, второй контроллер прямого доступа к памяти, блок флэш-памяти, блок интерфейса флэш-памяти, оперативное запоминающее устройство физических секторов, микропроцессор, оперативное запоминающее устройство программ, постоянное запоминающее устройство. 2 ил., 1 табл.

Съемный носитель информации, содержащий оперативное запоминающее устройство программ, постоянное запоминающее устройство, блок флэш-памяти, микропроцессор, а также соединенные с ним двунаправленной шиной данных блок внешнего интерфейса и блок интерфейса флэш-памяти, соединенный первой двунаправленной шиной с блоком флэш-памяти, а внешняя шина обмена данными носителя информации соединена с блоком внешнего интерфейса, отличающийся тем, что он дополнительно содержит первый и второй контроллеры прямого доступа к памяти, коммутатор, первое и второе оперативные запоминающие устройства данных и оперативное запоминающее устройство физических секторов, причем первый контроллер прямого доступа к памяти соединен с блоком внешнего интерфейса второй, а с коммутатором - третьей двунаправленной шиной, коммутатор и оперативное запоминающее устройство физических секторов подсоединены к двунаправленной шине данных, первое и второе оперативные запоминающие устройства данных соединены с коммутатором соответственно четвертой и пятой двунаправленными шинами, второй контроллер прямого доступа к памяти соединен с коммутатором шестой, а с блоком интерфейса флэш-памяти - седьмой двунаправленной шиной, а микропроцессор, оперативное запоминающее устройство программ и постоянное запоминающее устройство соединены между собой двунаправленной шиной команд, причем коммутатор осуществляет переключение потоков данных между третьей, четвертой, пятой и шестой двунаправленными шинами по следующему алгоритму: в режиме записи информации на носитель

и

и

и в режиме считывания информации с носителя

и в режиме считывания информации с носителя

где

где  - данные N-го пакета на k-й двунаправленной шине.

- данные N-го пакета на k-й двунаправленной шине.

| US 7278583 B2, 09.10.2007 | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| Устройство для подъема длинных валов | 1947 |

|

SU71174A1 |

| RU 2008115025 A, 10.11.2009. | |||

Авторы

Даты

2013-01-20—Публикация

2011-11-18—Подача