Область техники

Заявленное решение относится к компьютерной технике, в частности к компьютерным системам с использованием внешней памяти для начальной загрузки системы применительно к недорогим компьютерным системам с расширенными функциональными возможностями.

Уровень техники

Известно решение по патенту США 6601167 В1 (приоритет от 14.01.2000), включающее в себя способ инициализации компьютерной системы, включающей процессор и память последовательного доступа с программой загрузки, хранящейся в ней, и соответствующую компьютерную систему для осуществления способа. Загрузчик в ответ на инициализацию компьютерной системы сначала управляет последовательным запоминающим устройством для чтения загрузочной программы, после чего управляет процессором для перехода к работе загрузочной программы в памяти последовательного доступа. Первая страница памяти программы начальной загрузки вызывает загрузочный код, который должен быть передан в оперативное запоминающее устройство (ОЗУ). Затем процессор переключается на код в ОЗУ, заставляет передать оставшуюся часть загрузочного кода из памяти последовательного доступа в ОЗУ и выполнить его. Недостатком данного решения является необходимость использования внутреннего ОЗУ даже для небольших компьютерных систем.

Известны другие решения, включающие в себя устройства загрузки с использованием NAND флэш-памяти, например, по патенту США 7849302 (приоритет от 10.04.2006), и способ получения команд загрузки из энергонезависимой памяти, например, техническое решение по патенту США 20068533448 (приоритет от 06.12.2010), которые могут быть реализованы путем обнаружения сигнала сброса, относящегося к устройству, и получения заранее определенной страницы данных из энергонезависимой области памяти в регистр, связанный с энергонезависимой памятью, при постраничном извлечении данных из энергонезависимой памяти, при этом сама страница данных включает в себя команды загрузки устройства. При получении команды на считывание данных, хранящихся в регистре, используют включенный в нее адрес, идентифицирующий местоположение одной или более команд в регистре. В результате из регистра извлекается одна или более команд для исполнения процессором. Эти команды включают в себя команды загрузки данных из регистра памяти во внутреннее ОЗУ. Недостатком решений по данному патенту является то, что данный патент подразумевает использование многосигнального интерфейса NAND Flash памяти, описанного в стандарте ONFI. Стоит также отметить, что данный патент подразумевает использование в качестве загрузочного ПЗУ исключительно NAND Flash память, что сужает круг устройств, которые можно использовать в качестве ПЗУ в соответствующих компьютерных системах.

Из заявки на получение патента США 2005/0108500 (приоритет от 18.11.2003), известно решение архитектуры загрузочной флэш-памяти, которая позволяет использовать не-адресуемую память NAND, которая будет использоваться в качестве загрузочной памяти в цифровых процессорных системах. NAND-память имеет более низкую стоимость и более высокую плотность и важна для реализации процессоров с низким энергопотреблением. В начале процедуры (последовательной) загрузки предварительно выбранный адрес передается в NAND флэш-память. Этот предварительно выбранный адрес совпадает с тем, который ожидает процессорное ядро в начале процесса загрузки. После завершения цикла выбранной длительности флэш-память NAND переходит к следующей последовательной ячейке памяти и, таким образом, выводит последовательность команд по линии передачи данных. Линии передачи данных из флэш-памяти NAND предоставляют собой линии входа для передачи данных процессорному ядру. Процессорное ядро во время загрузки компьютера получает новые загрузочные команды в тот момент времени, когда они выходят из NAND флэш-памяти. Недостатками данного решения является то, что заявленный метод загрузки предусматривает использование исключительно NAND Flash памяти, а для метода загрузки то, что в нем используется многосигнальный интерфейс между микропроцессором и микросхемой NAND Flash, что, во-первых, требует большого количества выводов микросхемы системы на кристалле (СнК), а во-вторых, требует наличия специализированного интерфейса устройства микропроцессора. Кроме того, данный подход может потребовать наличия внутреннего ОЗУ.

Известно также решение по заявке на получение патента США 2004/0230738 А1 (приоритет 29.10.2003) в виде устройства, позволяющего управлять исполнением команд непосредственно из последовательной флэш-памяти, и чип флэш-памяти с использованием этого устройства, при этом контроллер ПЗУ с определенным объемом хранения данных имеет доступ к ПЗУ для чтения целых страниц памяти, в которых хранятся требуемые данные, и может передавать необходимые данные основному управляющему модулю или исполнять их. Устройство включает в себя кэш-модуль для доступа к указанному адресу памяти ПЗУ в ответ на команду, полученную от управляющего модуля, и чтения или записи данных основным управляющим модулем, и контроллер ПЗУ с загрузчиком, позволяющим осуществлять загрузку путем чтения данных с ПЗУ с хранением загрузочных кодов в буфере и немедленной передачей загрузочных кодов в основной управляющий модуль по его требованию. Основным недостатком является обязательное наличие внутреннего ОЗУ.

Все известные решения объединяет то, что после включения питания микросхема СнК, содержащая микропроцессор (микропроцессорное ядро), начинает процедуру начальной инициализации, для чего микропроцессорное ядро начинает считывать и выполнять инструкции программы начальной инициализации с некоторого начального адреса в собственном адресном пространстве. Т.е. программа начальной инициализации располагается в загрузочном энергонезависимом постоянном запоминающем устройстве (ПЗУ), выполненном, например, по технологии Flash, или загрузочное ПЗУ реализуют в составе микросхемы, что требует наличия специального технологического процесса, делает процесс изготовления микросхемы дороже. При использовании другого более дешевого и распространенного варианта с применением внешней микросхемы загрузочного ПЗУ типа Flash для доступа к загрузочному ПЗУ параллельного типа требуется несколько десятков выводов микросхемы СнК, в том числе, выводы адреса, данных и управления.

Кроме того, для уменьшения необходимого количества выводов как СнК, так и микросхемы памяти, уменьшения размеров и снижения стоимости корпусов СнК и микросхем памяти, а следовательно, размеров и стоимости печатных плат компьютерных систем широко используются ПЗУ последовательного типа (например, формата SPI (последовательный периферийный интерфейс)) для хранения программы начальной инициализации, которые осуществляют передачу данных чтения и записи, управляющую и статусную информацию по однобитному последовательному каналу. В частности, микросхемы ПЗУ типа SPI используют три линии для приема и передачи данных:

- вход для тактирования передаваемых или принимаемых данных (Serial Clock);

- вход для передачи данных от контроллера к микросхеме (SI - Serial Input), по этой линии побитно передают адрес, данные для записи, и коды команд управления микросхемой;

- выход для передачи данных от микросхемы к контроллеру, по этой линии побитно передают читаемые данные, а также информацию о состоянии микросхемы (SO - Serial Output).

Для взаимодействия с ПЗУ такого типа требуется специальный контроллер, инициирующий операции чтения/записи/стирания и т.д. путем подачи специализированной последовательности команд. Недостатком такого рода решений является то, что содержимое последовательного ПЗУ прямо не отображается в адресном пространстве микропроцессорного ядра, что сильно влияет на сложность программного обеспечения.

Имеющиеся решения для работы с таким ПЗУ требуют наличия встроенного в микросхему СнК начального микроПЗУ и внутреннего загрузочного оперативного запоминающего устройства ОЗУ. В этом случае, после включения питания микропроцессорное ядро считывает и выполняет инструкции из микроПЗУ, результатом выполнения которых будет копирование программы начальной инициализации из последовательного ПЗУ во внутреннее загрузочное ОЗУ, после чего происходит передача управления на команду внутреннего загрузочного ОЗУ, что сказывается на быстродействии, сложности конструкции и, следовательно, стоимости системы.

Раскрытие изобретения

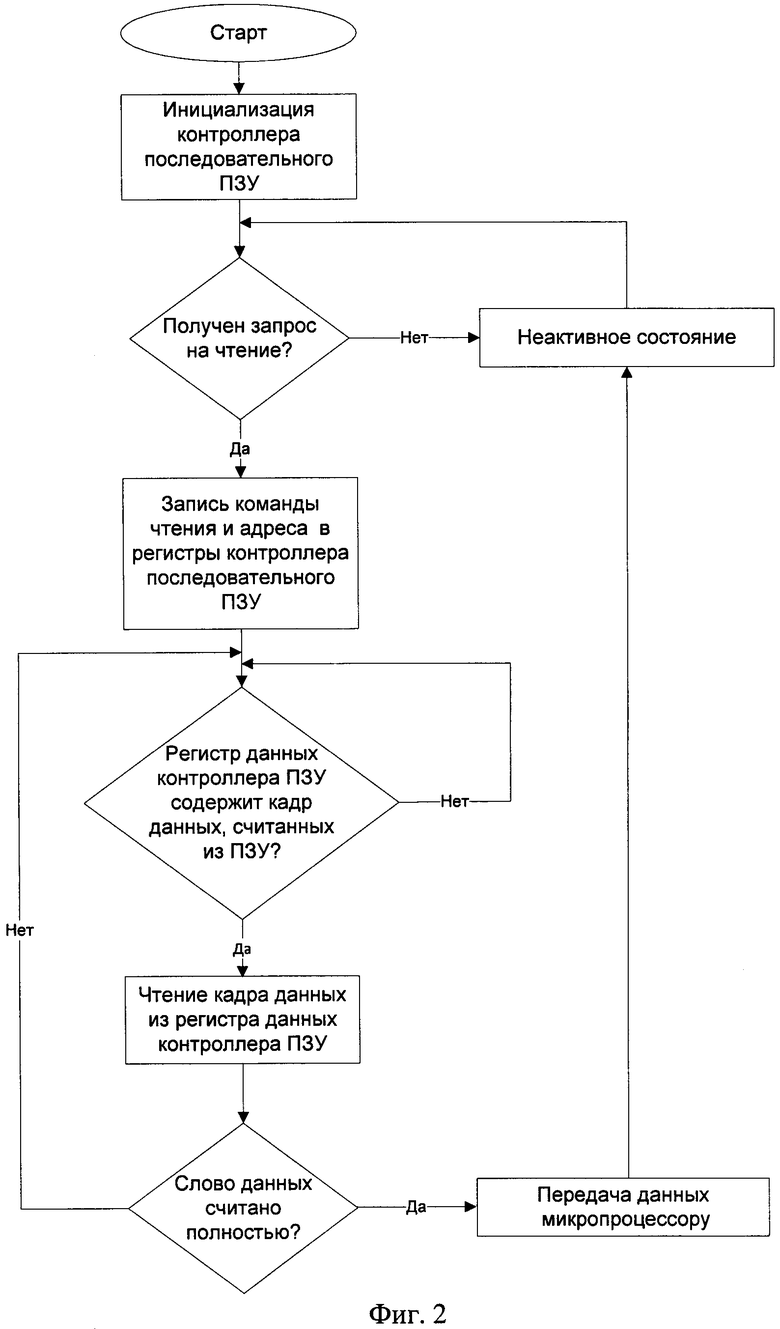

Для преодоления указанных недостатков и создания современной компьютерной системы с высокой вычислительной мощностью и расширенным функционалом, позволяющим работать с высокоскоростными внешними периферийными устройствами, удовлетворяя, таким образом, требованиям, предъявляемым к современным компьютерным системам, предлагается компьютерная система (фиг. 1), включающая в себя систему на кристалле (СнК) и внешнее последовательное ПЗУ; в свою очередь СнК включает в себя микропроцессор, включающий в себя, по меньшей мере, одно микропроцессорное ядро, контроллер внешнего последовательного ПЗУ для параллельной передачи слов данных, считанных из внешнего последовательного ПЗУ, расположенные между ними и связанные друг с другом устройство прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора и устройство внутренней коммутации. При этом устройство внутренней коммутации расположено между микропроцессором и устройством прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора. Устройство внутренней коммутации позволяет включить в состав СнК, по меньшей мере, одно интерфейсное устройство и, по меньшей мере, одно устройство внутренней памяти. Интерфейсные устройства позволяют СнК осуществлять взаимодействие с внешними по отношению к системе на кристалле периферийными устройствами, в т.ч. высокоскоростными, например, использовать в качестве оперативной памяти внешние микросхемы со встроенной динамической памятью, а также и производить вторую стадию загрузки из них посредством широко распространенных высокоскоростных и/или низкоскоростных протоколов приема/передачи данных. Устройства внутренней памяти позволяют дополнительно увеличить вычислительную мощность системы.

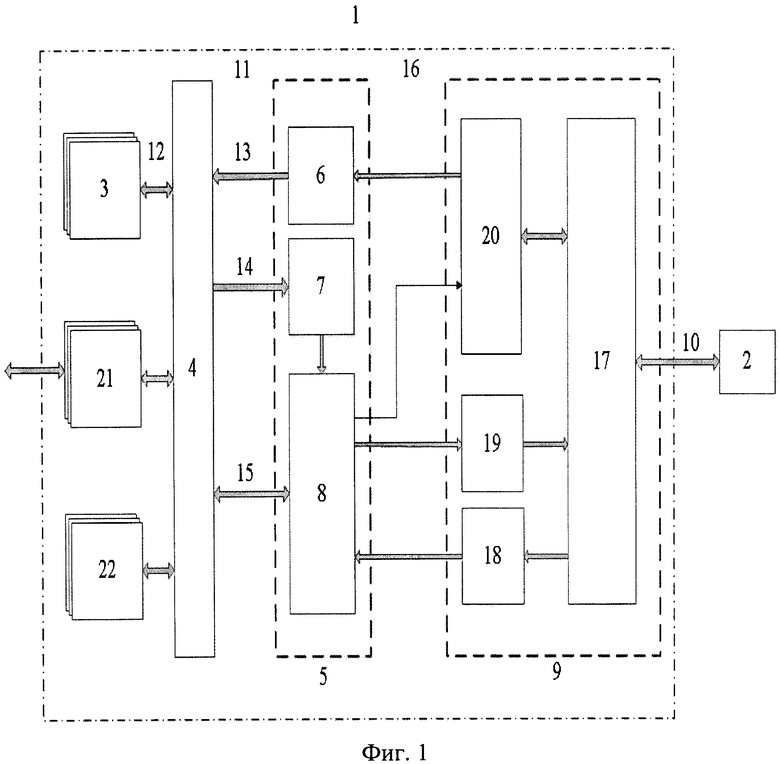

Устройство прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора работает по алгоритму, изображенному на фиг. 2. Оно включает в себя регистр считанных данных, регистр адреса и конечный автомат устройства прямого отображения адресов, производящий автоматические обращения к регистрам контроллера внешнего последовательного ПЗУ. Находясь между устройством коммутации и контроллером внешнего последовательного ПЗУ, оно преобразует запросы на чтение ПЗУ, поступающие от микропроцессора через устройство внутренней коммутации, в последовательность обращений к контроллеру внешнего последовательного ПЗУ. В результате работы контроллера получают набор слов данных, считанных из внешнего последовательного ПЗУ. Полученный набор слов передают по шине данных в микропроцессор через устройство внутренней коммутации, которое позволяет микропроцессору осуществлять высокоскоростное взаимодействие с другими устройствами системы на кристалле. Это взаимодействие осуществляется с использованием внутрисистемного интерфейса, поддерживаемого блоком внутренней коммутации при помощи наборов шин, где каждый из которых в свою очередь содержит три шины: шину адреса, шину управления и шину данных. Взаимодействие между устройством прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, и контроллером внешнего последовательного ПЗУ осуществляется посредством набора шин интерфейса, поддерживаемого контроллером внешнего последовательного ПЗУ, в соответствии с указанным выше алгоритмом (фиг. 2). Обмен данными между контроллером внешнего последовательного ПЗУ и самим ПЗУ производится посредством сигналов последовательного интерфейса. Для повышения вычислительной мощности в системе используется процессор, включающий, по меньшей мере одно ядро, а устройство внутренней коммутации позволяет включить в состав СнК, по меньшей мере, одно интерфейсное устройство и, по меньшей мере, одно устройство внутренней памяти. При этом интерфейсные устройства функционально обеспечивают взаимодействие системы с внешними периферийными устройствами, в т.ч. высокоскоростными, и могут, например, использовать в качестве оперативной памяти внешние микросхемы со встроенной динамической памятью, а также и производить вторую стадию загрузки из них посредством широко распространенных высокоскоростных и/или низкоскоростных протоколов приема/передачи данных. Включение устройств внутренней памяти также влияет на увеличение вычислительной мощности СнК. При этом имеет место упрощение конструкции за счет снижения числа контактов, снижаются требования к объему ОЗУ при возможности отказа от наличия в СнК внутренних загрузочного микроПЗУ и загрузочного ОЗУ, что в целом приводит также к снижению материалоемкости и, следовательно, к снижению стоимости микросхемы.

Использование в компьютерной системе устройства прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора позволяет осуществлять исполнение команд, располагающихся во внешнем последовательном ПЗУ (а в наилучшем варианте - исполнение начального кода загрузки компьютерной системы), благодаря тому, что в момент готовности к работе внешнего последовательного ПЗУ с компьютерной системы снимают сигнал сброса, производят автоматическую инициализацию одного или нескольких регистров управления контроллера внешнего последовательного ПЗУ с использованием конечного автомата устройства прямого отображения в адресное пространство микропроцессора адресов данных, располагающихся во внешнем последовательном ПЗУ, содержащем начальный код загрузки, и ожидают от микропроцессора поступления запросов на чтение, а при получении запроса на чтение и адреса от микропроцессора по шине управления и по шине адреса, соответственно, с использованием конечного автомата устройства прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора производят соответствующую запись в регистр данных и, возможно, в регистр управления контроллера внешнего последовательного ПЗУ, после этого с использованием конечного автомата устройства прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора выполняют чтение регистра данных контроллера внешнего последовательного ПЗУ до тех пор, пока полностью не считают слово данных, которое затем передают в микропроцессор по шине данных блока прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора для использования в микропроцессоре, до окончания получения запросов на чтение данных из ПЗУ. Несмотря на то, что основная часть обращений на чтение ПЗУ со стороны микропроцессора происходит во время загрузки, такие обращения могут поступать в течение всей работы компьютерной системы, что позволяет использовать внешнее последовательное ПЗУ в качестве источника данных и после загрузки.

Техническим результатом заявленного изобретения является создание компьютерной системы с оптимизированной возможностью выполнения программы инициализации из внешнего последовательного ПЗУ путем отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора сокращает число контактов, требуемых для подключения внешнего загрузочного ПЗУ к СнК, дает возможность отказа от использования внутренних загрузочных ОЗУ и ПЗУ, что экономит место на кристалле при одновременном обеспечении высокой вычислительной мощности и расширенных функциональных возможностей. Создание данной компьютерной системы расширяет арсенал современных компьютерных систем.

Описание чертежей

Решение проблемы и сущность заявленных технических решений могут быть пояснены с помощью следующих чертежей.

Фиг 1. Компьютерная система с системой на кристалле, содержащей микропроцессор, включающий одно или несколько микропроцессорных ядер, устройство прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора, устройство внутренней коммутации, интерфейсные устройства, устройства внутренней памяти и контроллер внешнего последовательного ПЗУ.

Фиг. 2. Алгоритм работы устройства прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора.

Осуществление изобретения

Компьютерная система (фиг. 1), состоящая из СнК (1) и внешнего последовательного ПЗУ (2), может быть осуществлена с использованием системы на кристалле, содержащей микропроцессор (3), включающий, по меньшей мере, одно микропроцессорное ядро; устройство внутренней коммутации (4), расположенное между микропроцессором (3) и устройством (5) прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ (2), в адресное пространство микропроцессора (3), включающего, по меньшей мере одно микропроцессорное ядро (т.е. микропроцессор (3) может быть как состоящим из одного ядра, так и быть многоядерным). Устройство (5) работает по алгоритму, изображенному на фиг. 2. Устройство (5) включает в себя регистр считанных данных (6), регистр адреса (7) и конечный автомат (8) устройства (5) прямого отображения адресов, производящий автоматические обращения к регистрам контроллера (9) внешнего последовательного ПЗУ (2). Находясь между устройством внутренней коммутации (4) и контроллером (9) внешнего последовательного ПЗУ (2), оно преобразует запросы на чтение ПЗУ (2), поступающие со стороны устройства внутренней коммутации (4) от микропроцессора (3), содержащего, по меньшей мере, одно микропроцессорное ядро, в последовательность обращений к контроллеру (9) внешнего последовательного ПЗУ (2), в результате чего получают набор слов данных, считанных из внешнего последовательного ПЗУ (2). Полученный набор слов передают в микропроцессор (3), содержащий, по меньшей мере, одно микропроцессорное ядро, через устройство внутренней коммутации (4), при этом устройство внутренней коммутации (4) позволяет микропроцессору (3), содержащему, по меньшей мере, одно микропроцессорное ядро, осуществлять высокоскоростное взаимодействие с другими устройствами системы на кристалле. Передача данных с устройства (5) прямого отображения адресов на устройство внутренней коммутации (4) и контроллер (9) происходит с использованием внутрисистемного интерфейса, поддерживаемого устройством внутренней коммутации (4), содержащим наборы шин (11) и (12), где каждый из которых в свою очередь содержит, по меньшей мере, три шины, как, например, в наборе (11) содержатся - шина адреса (13), шина управления (14) и шина данных (15). Устройство (5) взаимодействует с контроллером (9) внешнего последовательного ПЗУ (2) посредством набора шин интерфейса (16), поддерживаемого контроллером (9) внешнего последовательного ПЗУ (2), в соответствии с алгоритмом, описывающим работу блока прямого отображения адресов (фиг. 2). В качестве интерфейса (16) может быть использован интерфейс АМБА или любой специализированный интерфейс. Контроллер (9) внешнего последовательного ПЗУ (2) включает в себя конечный автомат (17) контроллера последовательного ПЗУ (2) и набор регистров, среди которых можно выделить, по меньшей мере, один регистр статуса (18), по меньшей мере, один регистр управления (19), по меньшей мере, один регистр данных (20). Обмен данными между контроллером (9) внешнего последовательного ПЗУ (2) и самим ПЗУ (2) производится посредством сигналов последовательного интерфейса (протокола) контроллера ПЗУ по однобитным последовательным каналам (10). При этом в начале работы компьютерной системы осуществляется передача начального кода загрузки компьютерной системы, располагающегося во внешнем последовательном ПЗУ (2), благодаря тому, что в момент готовности к работе внешнего последовательного ПЗУ (2) с компьютерной системы снимают сигнал сброса, производят автоматическую инициализацию одного или нескольких регистров управления контроллера (9) внешнего последовательного ПЗУ (2) с использованием конечного автомата устройства (8) прямого отображения в адресное пространство микропроцессора (3), содержащего, по меньшей мере, одно микропроцессорное ядро, адресов данных, располагающихся во внешнем последовательном ПЗУ (2), содержащем начальный код загрузки, и ожидают от микропроцессора (3), содержащего, по меньшей мере, одно микропроцессорное ядро, поступления запросов на чтение, а при получении запроса на чтение и адреса от микропроцессора (3), содержащего, по меньшей мере, одно микропроцессорное ядро, по шине управления и по шине адреса, соответственно, с использованием устройства внутренней коммутации (4) и конечного автомата (8) устройства (5) прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ (2), в адресное пространство микропроцессора (3), содержащего, по меньшей мере, одно микропроцессорное ядро, производят соответствующую запись в регистр данных (20) и, возможно, в регистр управления (19) контроллера (9) внешнего последовательного ПЗУ (2), после этого с использованием конечного автомата устройства (8) прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ (2), в адресное пространство микропроцессора (1) выполняют чтение регистра данных (20) контроллера внешнего последовательного ПЗУ (9) до тех пор, пока полностью не считают слово данных, которое затем передают в микропроцессор (3) через устройство внутренней коммутации (4) из устройства (5) прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ (2), в адресное пространство микропроцессора (3), включающего, по меньшей мере, одно микропроцессорное ядро, для использования в нем, до окончания получения запросов на чтение данных из ПЗУ (2). Несмотря на то, что основная часть обращений на чтение ПЗУ (2) со стороны микропроцессора (3), содержащего, по меньшей мере, одно микропроцессорное ядро, происходит во время загрузки (т.е. в адресное пространство микропроцессора отображаются адреса инструкций начального кода загрузки), такие обращения могут поступать в течение всего времени работы компьютерной системы, что позволяет использовать внешнее последовательное ПЗУ (2) в качестве источника данных и после загрузки.

Слова данных, считанные из внешнего последовательного ПЗУ (2), передаются по шине данных (15) в устройство коммутации (4) и далее в микропроцессор (3), включающий, по меньшей мере, одно микропроцессорное ядро. Таким образом, становится возможным, что микропроцессор (3), включающий, по меньшей мере, одно микропроцессорное ядро, способен производить чтение данных из внешнего по отношению к СнК последовательного ПЗУ (2) с помощью контроллера (9) внешнего последовательного ПЗУ (2), устройства (5) и блока внутренней коммутации (4). Взаимодействие устройства (5) с устройством внутренней коммутации (4) может производиться по любому внутрисистемному интерфейсу СнК, поддерживаемому блоком внутренней коммутации, например, АМВА/ОСР/и т.д. Обмен данными между устройством (5) прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора (3), включающего, по меньшей мере, одно микропроцессорное ядро, и контроллером (9) внешнего последовательного ПЗУ (2) может осуществляться в соответствии с любым протоколом, поддерживаемым контроллером (9) внешнего последовательного ПЗУ (2). Обмен данными контроллера (9) с внешним последовательным ПЗУ (2) производится по однобитным последовательным каналам (10). В компьютерной системе при работе устройства (5) прямого отображения адресов данных в качестве внешнего последовательного ПЗУ (2) может быть использована микросхема Flash памяти с последовательным интерфейсом, в качестве которого используют SPI интерфейс, а в качестве контроллера внешнего последовательного ПЗУ используют SPI контроллер. В состав СнК входят интерфейсные устройства (21) и устройства внутренней памяти (22). Наличие устройства внутренней коммутации (4) позволяет микропроцессору (3), включающему, по меньшей мере, одно микропроцессорное ядро, использовать интерфейсные устройства (22) при подключении высокоскоростных и низкоскоростных периферийных устройств с использованием внутрисистемного интерфейса (12), поддерживаемого устройством внутренней коммутации, например, АМВА/ОСР и т.п.

В качестве блока внутренней коммутации может быть использовано устройство внутренней коммутации, поддерживающее режим DMA (Direct Memory Access), при этом к компьютерной системе могут быть подключены через интерфейсные устройства дополнительные внешние периферийные устройства, позволяющие расширить функциональные возможности и вычислительные мощности этой системы. Внешние периферийные устройства, например, могут быть использованы для осуществления второй стадии загрузки, после окончания первой стадии, производящейся с использованием устройства (5) прямого отображения адресов из внешнего ПЗУ (2). Вторая стадия может осуществляться с использованием высокоскоростного протокола приема/передачи данных (например, SATA), при этом загрузочный код первой стадии обязательно должен включать в себя код инициализации всех задействованных во второй стадии загрузки устройств.

В качестве интерфейсных устройств в системе на кристалле (где устройства контроллеров являются интерфейсными устройствами, т.е. частью СнК) могут быть использованы:

- устройство контроллера Gigabit Ethernet;

- устройство контроллера 10 Gigabit Ethernet;

- устройство контроллера PCI (Peripheral component interconnect) и/или PCI Express;

- устройство контроллера SATA (Serial Advanced Technology Attachment);

- устройство контроллера DDR SDRAM (Double Data Rate Synchronous Dynamic Random Access Memory);

- устройство контроллера USB (Universal Serial Bus);

- устройства контроллеров низкоскоростных последовательных периферийных устройств.

В системе на кристалле дополнительно могут использоваться также такие интерфейсные устройства, как:

- устройство контроллера вывода видеоинформации;

- устройства контроллера ввода/вывода звуковой информации.

В качестве внутрисистемного интерфейса может быть использован интерфейс АМВА, ОСР и т.п. Блоки, входящие в состав контроллеров периферийных устройств, могут взаимодействовать друг с другом и посредством другого интерфейса, т.е. отличного от интерфейса блока коммутации.

Осуществление описанной компьютерной системы и соответствующего ей способа передачи данных (в т.ч. загрузки) с использованием устройства (5) прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ (2), в адресное пространство микропроцессора (3), содержащего, по меньшей мере, одно микропроцессорное ядро, благодаря использованию устройства внутренней коммутации (4) при подключении интерфейсных устройств (21) (по меньшей мере, одного) и устройств внутренней памяти (22) (по меньшей мере, одного) обеспечит следующие преимущества:

- исключение необходимости наличия в СнК внутренних блоков памяти, предназначенных для загрузки, - внутреннего загрузочного микроПЗУ и внутреннего ОЗУ, предназначенного для копирования кода загрузки;

- использование последовательного интерфейса (например, SPI) между СнК и микросхемой внешнего последовательного ПЗУ (5) (например, микросхемой Flash памяти), что уменьшает количество выводов СнК;

- возможность использования широкого спектра микросхем ПЗУ (5) (в частности, Flash памяти) за счет малого количества требований к данным микросхемам;

- упрощение программного доступа к данным в ПЗУ (5) за счет прямого отображения ПЗУ в адресное пространство микропроцессора (3), включающего, по меньшей мере, одно микропроцессорное ядро, и исключения, таким образом, необходимости подачи специальных команд для чтения ПЗУ (5).

Отсутствие известных технических решений, позволяющих обеспечить указанные выше преимущества, позволяет считать, что заявленное решение отвечает требованиям патентоспособности.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПРЯМОГО ОТОБРАЖЕНИЯ АДРЕСОВ ДАННЫХ, РАСПОЛАГАЮЩИХСЯ ВО ВНЕШНЕМ ПОСЛЕДОВАТЕЛЬНОМ ПЗУ, В АДРЕСНОЕ ПРОСТРАНСТВО МИКРОПРОЦЕССОРНОГО ЯДРА, КОМПЬЮТЕРНАЯ СИСТЕМА И СПОСОБ ПЕРЕДАЧИ ДАННЫХ | 2014 |

|

RU2579942C2 |

| УСТРОЙСТВО ШИФРОВАНИЯ ДАННЫХ (ВАРИАНТЫ), СИСТЕМА НА КРИСТАЛЛЕ С ЕГО ИСПОЛЬЗОВАНИЕМ (ВАРИАНТЫ) | 2015 |

|

RU2585988C1 |

| Сложно-функциональный блок для СБИС типа система на кристалле | 2018 |

|

RU2691886C1 |

| УПРАВЛЯЮЩИЙ МОДУЛЬ | 2014 |

|

RU2569576C1 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Многоканальное устройство управления шаговым двигателем | 1990 |

|

SU1789970A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в оптимизации выполнения программы инициализации из внешнего последовательного ПЗУ путем отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора. Компьютерная система включает в себя систему на кристалле и внешнее последовательное ПЗУ, причем система на кристалле включает в себя: микропроцессор, содержащий, по меньшей мере, одно микропроцессорное ядро; контроллер внешнего последовательного ПЗУ; устройство прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора; по меньшей мере, одно интерфейсное устройство; по меньшей мере, одно устройство внутренней памяти; и устройство внутренней коммутации, обеспечивающее взаимодействие между микропроцессором и остальными устройствами системы на кристалле; при этом устройство прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора содержит регистр считанных данных, регистр адреса и конечный автомат устройства прямого отображения адресов. 31 з.п. ф-лы, 2 ил.

1. Компьютерная система, характеризующаяся тем, что включает в себя систему на кристалле и внешнее последовательное ПЗУ,

при этом система на кристалле включает в себя:

микропроцессор, содержащий, по меньшей мере, одно микропроцессорное ядро;

контроллер внешнего последовательного ПЗУ;

устройство прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора; по меньшей мере, одно интерфейсное устройство; по меньшей мере, одно устройство внутренней памяти; и

устройство внутренней коммутации, обеспечивающее взаимодействие между микропроцессором и остальными устройствами системы на кристалле и находящееся между соединенным с контроллером внешнего последовательного ПЗУ устройством прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора и другими вышеназванными устройствами;

при этом названное устройство прямого отображения адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора содержит регистр считанных данных, регистр адреса и конечный автомат устройства прямого отображения адресов, позволяет осуществлять прямое отображение адресов данных, располагающихся во внешнем последовательном ПЗУ, в адресное пространство микропроцессора и преобразовывает запросы на чтение со стороны микропроцессора в последовательность обращений к контроллеру внешнего последовательного ПЗУ, а считанную из внешнего последовательного ПЗУ последовательность слов данных передает по шине данных из устройства отображения в микропроцессор через устройства внутренней коммутации, при этом устройство внутренней коммутации работает с микропроцессором и с каждым из устройств системы на кристалле с использованием внутрисистемного интерфейса, содержащего наборы шин, каждый из которых включает в себя, по меньшей мере, одну шину данных, по меньшей мере, одну шину адреса и, по меньшей мере, одну шину управления.

2. Компьютерная система по п. 1, отличающаяся тем, что при работе устройства прямого отображения адресов данных в качестве внешнего последовательного ПЗУ используют микросхему Flash памяти с последовательным интерфейсом.

3. Компьютерная система по п. 2, отличающаяся тем, что при работе устройства прямого отображения адресов данных в качестве последовательного интерфейса к внешнему последовательному ПЗУ используют SPI интерфейс, а в качестве контроллера внешнего последовательного ПЗУ используют SPI контроллер.

4. Компьютерная система по п. 1, отличающаяся тем, что устройство прямого отображения адресов данных выполнено с возможностью отображения в адресное пространство микропроцессора, содержащего, по меньшей мере, одно микропроцессорное ядро, адресов данных, являющихся инструкциями начального кода загрузки.

5. Компьютерная система по п. 2, отличающаяся тем, что устройство прямого отображения адресов данных выполнено с возможностью отображения в адресное пространство микропроцессора, содержащего, по меньшей мере, одно микропроцессорное ядро, адресов данных, являющихся инструкциями начального кода загрузки.

6. Компьютерная система по п. 3, отличающаяся тем, что устройство прямого отображения адресов данных выполнено с возможностью отображения в адресное пространство микропроцессора, содержащего, по меньшей мере, одно микропроцессорное ядро, адресов данных, являющихся инструкциями начального кода загрузки.

7. Компьютерная система по п. 4, отличающаяся тем, что устройство прямого отображения адресов данных выполнено с возможностью использования внешнего последовательного ПЗУ в качестве источника данных и после завершения чтения инструкций начального кода загрузки.

8. Компьютерная система по п. 5, отличающаяся тем, что устройство прямого отображения адресов данных выполнено с возможностью использования внешнего последовательного ПЗУ в качестве источника данных и после завершения чтения инструкций начального кода загрузки.

9. Компьютерная система по п. 6, отличающаяся тем, что устройство прямого отображения адресов данных выполнено с возможностью использования внешнего последовательного ПЗУ в качестве источника данных и после завершения чтения инструкций начального кода загрузки.

10. Компьютерная система по п. 1, отличающаяся тем, что контроллер внешнего последовательного ПЗУ включает в себя конечный автомат контроллера внешнего последовательного ПЗУ, регистр данных, по меньшей мере, один регистр управления и, по меньшей мере, один регистр адреса.

11. Компьютерная система по п. 2, отличающаяся тем, что контроллер внешнего последовательного ПЗУ включает в себя конечный автомат контроллера внешнего последовательного ПЗУ, регистр данных, по меньшей мере, один регистр управления и, по меньшей мере, один регистр адреса.

12. Компьютерная система по п. 3, отличающаяся тем, что контроллер внешнего последовательного ПЗУ включает в себя конечный автомат контроллера внешнего последовательного ПЗУ, регистр данных, по меньшей мере, один регистр управления и, по меньшей мере, один регистр адреса.

13. Компьютерная система по п. 1, отличающаяся тем, что микропроцессорные ядра образуют кластеры.

14. Компьютерная система по п. 2, отличающаяся тем, что микропроцессорные ядра образуют кластеры.

15. Компьютерная система по п. 3, отличающаяся тем, что микропроцессорные ядра образуют кластеры.

16. Компьютерная система по п. 4, отличающаяся тем, что микропроцессорные ядра образуют кластеры.

17. Компьютерная система по п. 5, отличающаяся тем, что микропроцессорные ядра образуют кластеры.

18. Компьютерная система по п. 6, отличающаяся тем, что микропроцессорные ядра образуют кластеры.

19. Компьютерная система по п. 7, отличающаяся тем, что микропроцессорные ядра образуют кластеры.

20. Компьютерная система по п. 8, отличающаяся тем, что микропроцессорные ядра образуют кластеры.

21. Компьютерная система по п. 9, отличающаяся тем, что микропроцессорные ядра образуют кластеры.

22. Компьютерная система по п. 1, отличающаяся тем, что в качестве устройства внутренней коммутации используют устройство внутренней коммутации, поддерживающее DMA (Direct Memory Access).

23. Компьютерная система по п. 2, отличающаяся тем, что в качестве устройства внутренней коммутации используют устройство внутренней коммутации, поддерживающее DMA (Direct Memory Access).

24. Компьютерная система по п. 3, отличающаяся тем, что в качестве устройства внутренней коммутации используют устройство внутренней коммутации, поддерживающее DMA (Direct Memory Access).

25. Компьютерная система по п. 10, отличающаяся тем, что в качестве устройства внутренней коммутации используют устройство внутренней коммутации, поддерживающее DMA (Direct Memory Access).

26. Компьютерная система по п. 11, отличающаяся тем, что в качестве устройства внутренней коммутации используют устройство внутренней коммутации, поддерживающее DMA (Direct Memory Access).

27. Компьютерная система по п. 12, отличающаяся тем, что в качестве устройства внутренней коммутации используют устройство внутренней коммутации, поддерживающее DMA (Direct Memory Access).

28. Компьютерная система по любому из пунктов пп. 1-27, отличающаяся тем, что в качестве устройства внутренней памяти используют память типа SRAM (Static Random Access Memory).

29. Компьютерная система по любому из пунктов п. 1-27, отличающаяся тем, что в качестве устройства внутренней памяти используют память типа ROM (Read Only Memory).

30. Компьютерная система по п. 1-27, отличающаяся тем, что в качестве внутрисистемного интерфейса используют интерфейс типа АМВА.

31. Компьютерная система по п. 1-27, отличающаяся тем, что в качестве внутрисистемного интерфейса используют интерфейс ОСР.

32. Компьютерная система п. 1-27, отличающаяся тем, что в качестве интерфейсного устройства используют устройство контроллера Gigabit Ethernet, или устройство контроллера PCI (Peripheral component interconnect), или устройство контроллера PCI Express или SATA (Serial Advanced Technology Attachment), или устройство контроллера DDR SDRAM (Double Data Rate Synchronous Dynamic Random Access Memory), или устройство контроллера USB (Universal Serial Bus), или устройства контроллеров низкоскоростных последовательных периферийных устройств, или устройство контроллера вывода видеоинформации, или устройства контроллера ввода/вывода звуковой информации.

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| KR 1020070081597 A, 17.08.2007 | |||

| US 6601167 B1, 29.07.2003 | |||

| US 7237105 B2, 26.06.2007 | |||

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПОДДЕРЖАНИЯ УПОРЯДОЧЕНИЯ ТРАНЗАКЦИЙ И РАЗРЕШЕНИЯ КОНФЛИКТНЫХ СИТУАЦИЙ В МОСТОВОЙ СХЕМЕ ШИН | 1995 |

|

RU2182356C2 |

Авторы

Даты

2016-04-10—Публикация

2014-09-30—Подача