Область техники

Изобретение относится к электронной технике и может использоваться при разработке полупроводниковых КМОП (комплементарных металл-окисел-полупроводник) микросхем для создания схем дифференциальных радиочастотных и СВЧ (сверхвысокочастотных) аттенюаторов с широкой полосой частот, требуемым шагом ослабления, малыми фазовыми искажениями и повышенным уровнем линейности сигнала.

Предшествующий уровень техники

Аттенюаторы СВЧ, выполненные на основе полупроводниковых приборов, широко используются в технике СВЧ, особенно многоразрядные аттенюаторы СВЧ с дискретным изменением затухания, которые представляют собой каскадное соединение нескольких разрядов, каждый из которых представляет собой П- или Т-образное соединение резисторов, замыкаемых ключами в соответствии с поданным цифровым кодом.

Из уровня техники известны также способы построения аналоговых электронных аттенюаторов, выполненных по КМОП технологии. Аналоговый аттенюатор - это электронное устройство, позволяющее ослаблять входной сигнал по непрерывному закону.

Известен аналоговый аттенюатор, построенный на основе схемы истокового повторителя [1]. В схеме стоки двух полевых МОП транзисторов p-типа подключены на землю, а истоки подключены к источнику тока. На затвор первого транзистора подается входной сигнал (Vin), на затвор второго подается постоянное напряжение, управляющее величиной ослабления (Vbias). Выход снимается со стоков МОП транзисторов.

Принцип работы указанного аналогового аттенюатора состоит в том, что изменение сопротивления второго транзистора приводит к изменению коэффициента передачи схемы.

Известен источник [2], в котором представлен дифференциальный вариант аналогового аттенюатора на основе истокового повторителя. По сравнению с однополярным аттенюатором в дифференциальном напряжение на затворы управляющих транзисторов подается через RC-фильтр. При этом управляющий сигнал с неинвертирующего входа подается на транзистор, регулирующий величину ослабления сигнала с инвертированного входа. Такое включение позволяет подавлять синфазную составляющую входного сигнала.

Известные аттенюаторы обладают следующими недостатками: узкий диапазон рабочих частот, узкий динамический диапазон, сложность построения и большие потери многоразрядных аттенюаторов ввиду использования фиксированного управляющего напряжения.

Раскрытие изобретения

Техническим результатом, на достижение которого направлено заявленное изобретение, является расширение функциональных возможностей аттенюаторов, выполненных по КМОП технологии, снижение потерь при прямом прохождении сигнала, увеличение динамического диапазона, расширение полосы рабочих частот, уменьшение фазовых искажений при переключении уровня аттенюации.

Указанный технический результат достигается тем, что заявленный интегральный аттенюатор содержит генератор дифференциального сигнала, звенья, состоящие из параллельно включенных управляемых МОП транзисторов n- и p- типа, блок управления и нагрузку, кроме того, неинвертирующая пара звеньев, состоящих из МОП транзисторов n- и p-типа соединена с генератором дифференциального сигнала и нагрузкой напрямую, а инвертирующая пара звеньев, состоящих из МОП транзисторов n- и p- типа, соединена с генератором дифференциального сигнала и нагрузкой перекрестно; где регулировка сопротивлений МОП транзисторов, входящих в звенья, осуществляется блоком управления, при этом сопротивление одной пары звеньев МОП транзисторов возрастает, а другой падает.

При построении переключателя используются дифференциальные мостовые схемы построения, которые позволяют, во-первых, уменьшить влияние паразитных индуктивностей, связанных с общей шиной и, во-вторых, используя эффект компенсации (уменьшение сигнала за счет сложения с сигналом противоположной полярности), обеспечить ослабление сигнала без использования каскадного соединения аттенюаторов с фиксированной величиной ослабления. Для увеличения динамического диапазона используется параллельное включение МОП транзисторов n- и p-типов. Цифровое управление предложенным аттенюатором может быть обеспечено за счет блока управления, преобразующего цифровые коды в требуемые значения напряжений смещения транзисторов.

Краткое описание чертежей

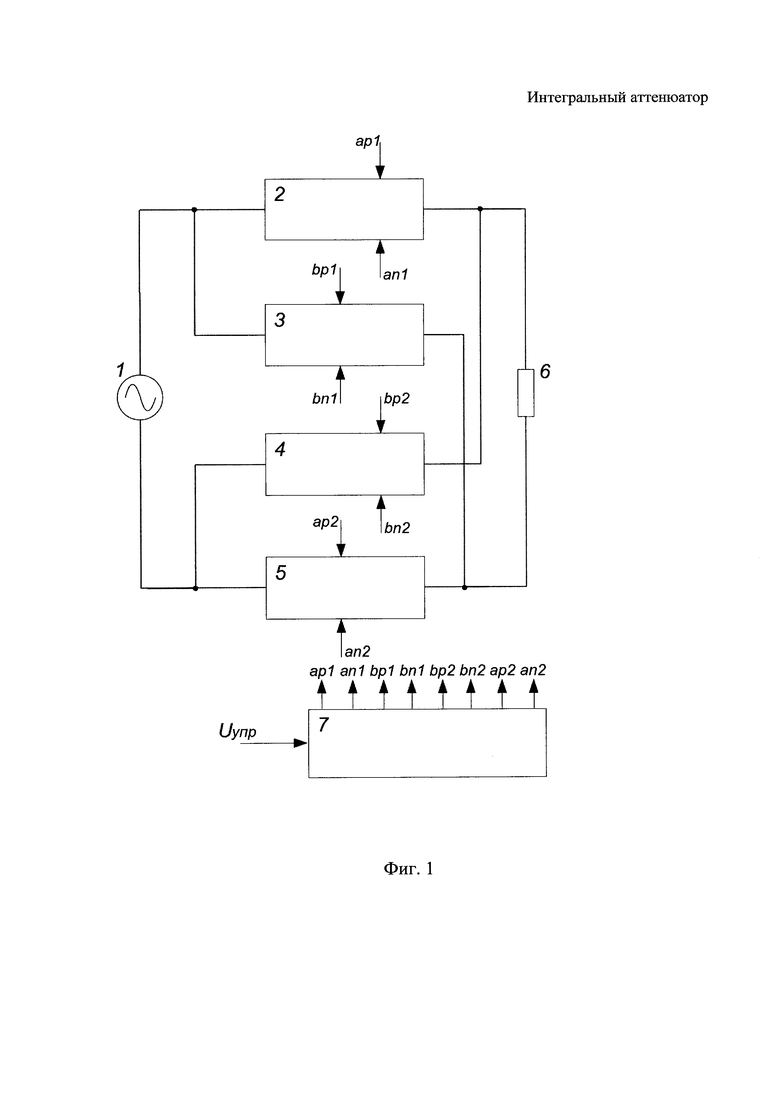

Сущность полезной модели поясняется чертежом, где на фиг. 1 представлена блок-схема аттенюатора, выполненного на МОП структурах, где:

1 - генератор дифференциального сигнала;

2, 3, 4, 5 - звенья, состоящие из параллельного соединения МОП транзисторов n- и p-типа;

6 - нагрузка;

7 - блок управления.

Блок управления преобразует внешние сигналы управления в требуемые уровни смещения. Параллельное соединение в каждом звене МОП транзисторов n- и p-типа обеспечивает лучшую линейность передачи сигнала по сравнению с использованием транзисторов одного типа. При равенстве сопротивлений проходных звеньев 2 и 5 сопротивлениям компенсирующих звеньев 3 и 4 происходит максимальное ослабление сигнала. При максимальном открывании транзисторов проходных звеньев, т.е. минимальном сопротивлении проходных звеньев и соответствующем увеличении сопротивления компенсирующих звеньев обеспечивается прямое прохождение сигнала с минимальными потерями. При правильном выборе комплексных импедансов звеньев, когда импеданс звеньев 2 и 5 растет пропорционально уменьшению импеданса звеньев 3 и 4, обеспечивается согласование с источником сигнала во всем диапазоне регулировки коэффициента передачи.

Управление величиной сопротивления МОП транзисторов помимо подачи непрерывных значений на управляющие выводы может осуществляться и цифровым способом, при этом транзисторы с каналом n-типа управляются сигналами от блока цифрового управления: an1, an2, bn1, bn2, а МОП транзисторы p-типа сигналами: ap1, ар2, bp1, bp2 соответственно.

Осуществление изобретения

Работа устройства осуществляется следующим образом.

В блок-схеме, представленной на фиг. 1, сигнал от генератора дифференциального сигнала 1 поступает на звенья 2-5, которые управляются от блока управления 7 таким образом, что при открывании МОП транзисторов в звеньях 2 и 5 МОП транзисторы в звеньях 3 и 4 закрываются. При одинаковом сопротивлении всех звеньев сигнал на нагрузке 6 будет минимальный, и наоборот, при минимальном сопротивлении звеньев 2 и 5 и максимальном сопротивлении звеньев 3 и 4 потери сигнала на выходе будут наименьшими. Таким образом, изменяя внутри звеньев сопротивления МОП транзисторов потенциалом на их затворах, можно осуществлять регулирование выходного сигнала с требуемым шагом. При условии, что произведение сопротивлений звеньев с уменьшающимся и с увеличивающимся сопротивлениями будут равны, можно достичь согласование сигнала с источником и нагрузкой 6. Регулировка осуществляется блоком управления 7, который может управляться как аналоговым сигналом, так и цифровым (при использовании в блоке управления 7 цифроаналогового преобразователя - ЦАП), обеспечивая плавную (аналоговую) или дискретную (цифровую) регулировку ослабления сигнала.

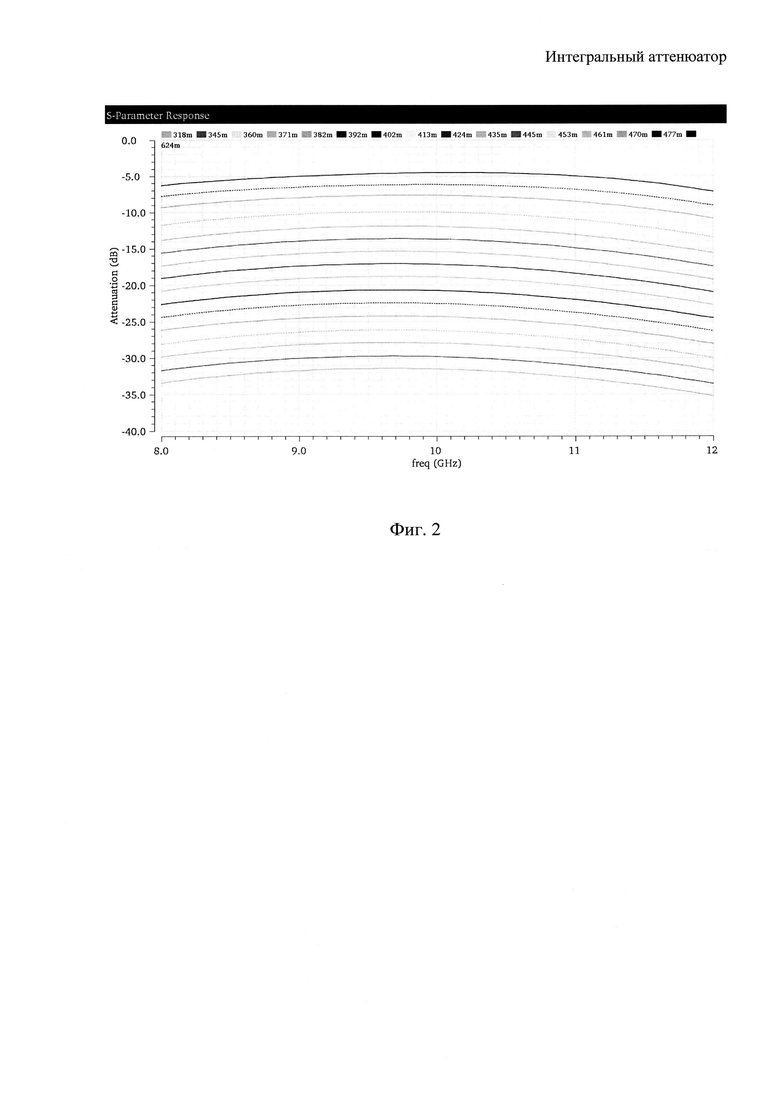

На фиг. 2 в качестве примера представлено семейство кривых, показывающее изменение сигнала аттенюатором при различных кодах ЦАП в широком диапазоне частот.

Результаты, полученные при использовании КМОП технологического процесса с минимальными размерами 0,25 мкм, приведены в Таблице 1.

Значения приведенных параметров значительно лучше ранее полученных для сопоставимых КМОП технологических процессов.

Интегральный аттенюатор реализован в виде монолитной КМОП интегральной микросхемы на одном кристалле.

Источники информации

1. Т.Н. Тео, Low-Power Digitally Controlled CMOS Source Follower Variable Attenuator, IEEE ISCAS 2007, New Orleans, LA, 27-30 May 2007.

2. Патент на изобретение. US №0295594. Source Follower Attenuator / T.H. Тео, опубл. 25.10.2010.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный аттенюатор с дискретным управлением | 2022 |

|

RU2792262C1 |

| ИНТЕГРАЛЬНЫЙ ПЕРЕКЛЮЧАТЕЛЬ | 2024 |

|

RU2835384C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КМОП КОМПАРАТОР НАПРЯЖЕНИЯ | 1992 |

|

RU2019913C1 |

| Высокочастотный фазовращатель на МОП-транзисторах | 2015 |

|

RU2607673C1 |

| ИСТОЧНИК ЭЛЕКТРИЧЕСКОГО СИГНАЛА, ПРОПОРЦИОНАЛЬНОГО АБСОЛЮТНОЙ ТЕМПЕРАТУРЕ | 1993 |

|

RU2115099C1 |

| ПОЛУПРОВОДНИКОВАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 1991 |

|

RU2104601C1 |

| ЭЛЕКТРОННОЕ РЕЛЕ С ТРАНСФОРМАТОРНОЙ РАЗВЯЗКОЙ И С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ ПО ТОКУ И ПЕРЕГРЕВА ЭЛЕКТРОННОГО КЛЮЧА | 2008 |

|

RU2380828C1 |

| ИНТЕГРАЛЬНЫЙ ГРАДИЕНТНЫЙ МАГНИТОТРАНЗИСТОРНЫЙ ДАТЧИК | 2010 |

|

RU2453947C2 |

| ЭЛЕКТРОННОЕ РЕЛЕ С ТРАНСФОРМАТОРНОЙ РАЗВЯЗКОЙ И С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ ПО ТОКУ | 2008 |

|

RU2360358C1 |

| ИНТЕГРАЛЬНЫЙ МАГНИТОТРАНЗИСТОРНЫЙ ДАТЧИК С ЦИФРОВЫМ ВЫХОДОМ | 2009 |

|

RU2437185C2 |

Использование: для создания схем дифференциальных аттенюаторов для работы в СВЧ диапазоне. Сущность изобретения заключается в том, что интегральный аттенюатор содержит генератор дифференциального сигнала, звенья, состоящие из параллельно включенных управляемых МОП транзисторов n- и p-типа, блок управления и нагрузку, кроме того, неинвертирующая пара звеньев, состоящих из МОП транзисторов n- и p-типа, соединена с генератором дифференциального сигнала и нагрузкой напрямую, а инвертирующая пара звеньев, состоящих из МОП транзисторов n- и p-типа соединена с генератором дифференциального сигнала и нагрузкой перекрестно; где регулировка сопротивлений МОП транзисторов, входящих в звенья, осуществляется блоком управления, при этом сопротивление одной пары звеньев МОП транзисторов возрастает, а другой падает. Технический результат: обеспечение возможности расширения функциональных возможностей аттенюаторов, выполненных по КМОП технологии, снижения потерь при прямом прохождении сигнала, увеличения динамического диапазона, расширения полосы рабочих частот, уменьшения фазовых искажений при переключении уровня аттенюации. 2 ил., 1 табл.

Интегральный аттенюатор, содержащий генератор дифференциального сигнала, звенья, состоящие из параллельно включенных управляемых МОП транзисторов n- и p-типа, блок управления и нагрузку, отличающийся тем, что неинвертирующая пара звеньев, состоящих из МОП транзисторов n- и p-типа соединена с генератором дифференциального сигнала и нагрузкой напрямую, а инвертирующая пара звеньев, состоящих из МОП транзисторов n- и p-типа соединена с генератором дифференциального сигнала и нагрузкой перекрестно; где регулировка сопротивлений МОП транзисторов, входящих в звенья, осуществляется блоком управления, при этом сопротивление одной пары звеньев МОП транзисторов возрастает, а другой падает.

| US 20100295594 A1, 25.11.2010 | |||

| JP 2014241554 A, 25.12.2014 | |||

| US 4438415 A1, 20.03.1984 | |||

| ИНТЕГРАЛЬНЫЙ АТТЕНЮАТОР СВЧ-СИГНАЛА | 2010 |

|

RU2408114C1 |

| Прибор для записи углов наклона | 1957 |

|

SU115125A1 |

Авторы

Даты

2018-01-25—Публикация

2016-11-01—Подача