Изобретение относится к электронной технике и может использоваться в радиолокации при разработке полупроводниковых КМОП (комплементарных металл-окисел-полупроводник) микросхем для создания схем дифференциальных радиочастотных и СВЧ переключателей с широкой полосой частот, минимальными потерями, высокой изоляцией и повышенным уровнем линейности сигнала.

Переключатели радиочастотного сигнала, выполненные на основе полупроводниковых приборов, широко используются в технике СВЧ, особенно в антенно-фидерный трактах при переключении на прием или передачу сигнала. Полупроводниковые переключатели обладают следующими характеристиками: высоким быстродействием, малыми потерями, высокой изоляцией, широкой полосой рабочих частот сигнала и высоким уровнем мощности передаваемого сигнала. В активно-фазированных антенных решетках существует необходимость в использовании нескольких антенн при одном источнике входного сигнала, для этого применяется переключатель один в четыре.

Известно устройство переключения сигнала высокого уровня мощности, где используются p-i-n диоды, которые переключают однополярный сигнал. При этом увеличиваются потери сигнала при прохождении через переключатель. Недостатком является отсутствие возможности высокоскоростного переключения дифференциального сигнала между четырьмя выходами /1/.

Известен также переключатель дифференциального сигнал, где используются катушки индуктивности для подавления паразитного сигнал и согласования с нагрузкой. Однако, при этом включении низкое быстродействие при переключении между каналами и большая занимаемая площадь на пластине /2/.

В ближайшем аналоге взятым за прототип используется дифференциальная мостовая схема МОП транзисторов для переключения между двумя выходными каналами /3/. Применяется схемотехническое решение компенсации паразитного сигнала, тем самым, обеспечивается широкая полоса рабочих частот. Однако, указанное устройство не может применяться для переключения мощности высокого уровня между четырьмя дифференциальными выходами. Это связано с тем, что используются только транзисторы n-типа. Переключатель основан на структуре один в два (Single Port Duble Throu - SPDT), что накладывает ограничения на количество переключаемых выходных сигналов и при этом отсутствует цифровое управление при переключении.

Задачей изобретения является увеличение мощности и быстродействия передаваемого или принимаемого сигнала между четырьмя антеннами, с возможностью цифрового управления, при сохранении минимальных потерь, максимальной изоляции и широкой полосы рабочих частот.

Интегральный переключатель, содержащий два дифференциальных ключа, соединенные общим входом, состоящие из неинвертирующих МОП транзисторов и инвертирующих МОП транзисторов, связанные таким образом, что неинвертирующие транзисторы соединены с источником дифференциального сигнала и нагрузкой напрямую, а инвертирующие транзисторы соединены с источником дифференциального сигнала и нагрузкой перекрестно, отличающийся тем, что добавлены еще два дифференциальных ключа параллельно - исходным двум, и параллельно n-типа транзисторам в ключах введены транзисторы р-типа таким образом, что стоки р-типа транзисторов соединены с истоками n-канальных транзисторов, а истоки р-типа транзисторов соединены со стоками n-канальных транзисторов, также введен цифровой блок таким образом, что входы первого, второго, третьего и четвертого дифференциальных ключей соединены с выходом блока управления, вход первого дифференциального ключа соединен с входом второго дифференциального ключа, входом третьего дифференциального ключа и входом четвертого дифференциального ключа, а также выходы первого, второго, третьего и четвертого дифференциальных ключей соединены с нагрузкой (7), нагрузкой (8), нагрузкой (9) и нагрузкой (10) соответственно.

Интегральный переключатель реализован в виде монолитной КМОП интегральной микросхемы на одном кристалле и содержит четыре дифференциальных ключа, соединенные общим входом, состоящие из неинвертирующих комплементарных пар МОП транзисторов и инвертирующих комплементарных пар МОП транзисторов, связанные таким образом, что неинвертирующая пара комплементарных транзисторов соединена с источником дифференциального сигнала и нагрузкой напрямую, а инвертирующая пара комплементарных транзисторов соединена с источником дифференциального сигнала и нагрузкой перекрестно, что обеспечивает высокий уровень мощности принимаемого или передаваемого сигнала по одному из четырех каналов в зависимости от сигнала управления.

При построении переключателя используются дифференциальные мостовые схемы, с применением n- и р-типа транзисторов, которые позволяют за счет использования эффекта компенсации обеспечивать минимальные потери, максимальную изоляцию и высокий уровень мощности сигнала. Параллельное соединение МОП транзисторов n- и р-типа в каждом переключателе обеспечивает высокий уровень линейности передачи или приема сигнала по сравнению с использованием транзисторов одного типа.

Цифровое управление предложенным переключателем обеспечивается за счет применения блока управления, которые преобразует цифровой код в требуемые уровни значений напряжения для переключения транзисторов. Цифровой сигнал на n- и р-типа транзисторов подается в противофазе.

Предложенную схему переключателя можно представить как дифференциальное соединение источника входных сигналов и нагрузки через четыре дифференциальных ключа соединенных общим входом и имеющих четыре различных выхода. В каждом ключе две пары комплементарных МОП транзисторов напрямую соединены с источником и инвертированы с нагрузкой, а другая пара комплементарных МОП транзисторов напрямую соединена с нагрузкой и инвертирована с источником. Применение комплементарной пары транзисторов позволяет увеличить мощность и быстродействие переключения между каналами при использовании на прием или передачу сигнала. Ширина n- и р-типа транзисторов выполнены с одинаковой шириной канала. Одинаковая площадь комплементарной пары позволяет сохранить минимальные потери и максимальную изоляцию в широком диапазоне рабочих частот сигнала. Переключение между каналами обеспечивается цифровым блоком управления.

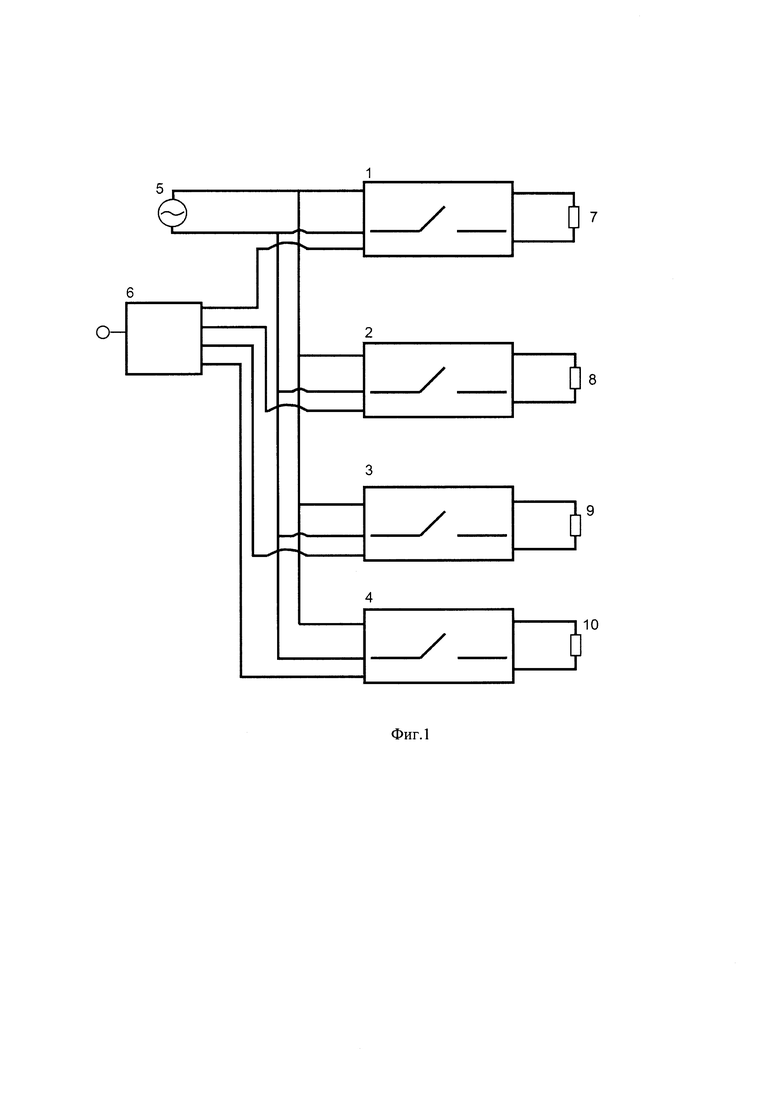

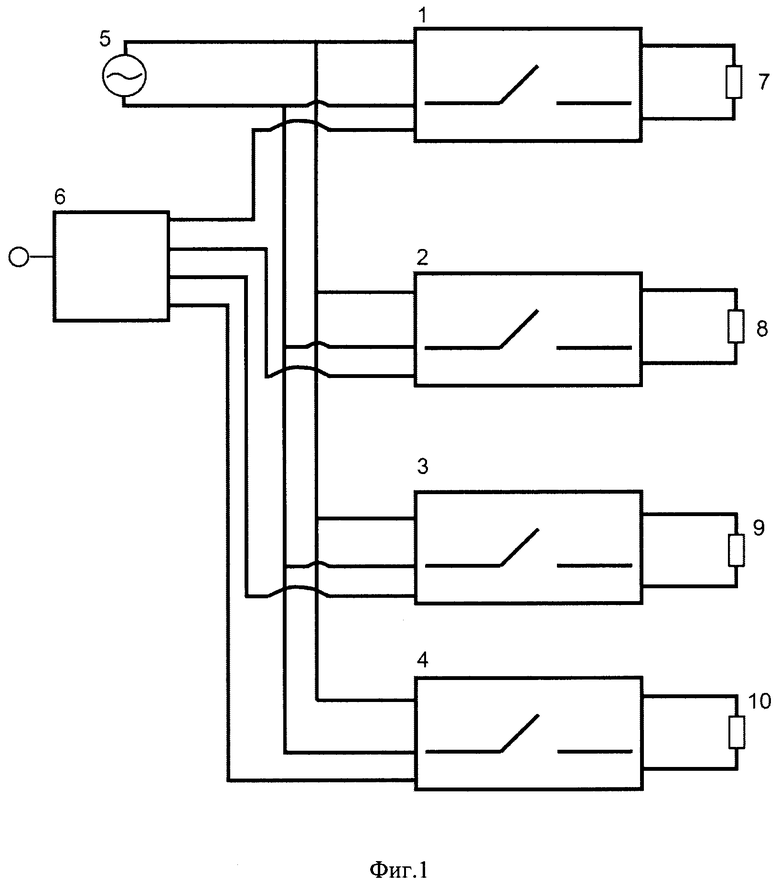

Сущность изобретения поясняется чертежами, где на Фиг. 1 представлена блок-схема переключателя, выполненного на дифференциальных ключах по Фиг. 2, где:

5 - источник дифференциального сигнала;

1, 2, 3, 4 - дифференциальные ключи;

6 - блок управления;

7, 8, 9, 10 - нагрузка.

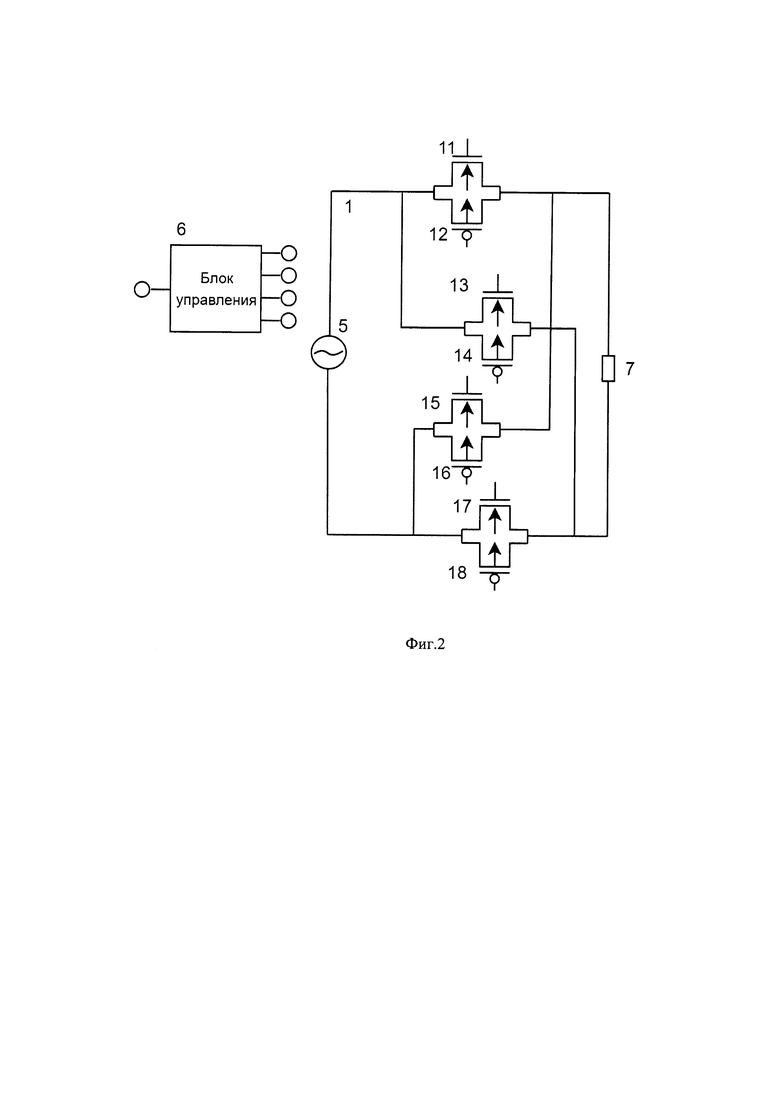

На Фиг. 2 представлена схема дифференциального ключа в данном случае 1, выполненного на комплементарных МОП транзисторах, где:

5 - источник дифференциального сигнала;

11, 17 - неинвертирующие транзисторы n-типа;

12, 18 - неинвертирующие транзисторы р-типа;

13, 15 - инвертирующие транзисторы n-типа;

14, 16 - инвертирующие транзисторы р-типа;

7 - нагрузка;

6 - блок управления.

Работа интегрального переключателя осуществляется следующим образом. В схеме на Фиг. 2, неинвертирующие транзисторы n-типа 11, 17 и неинвертирующие транзисторы р-типа 12, 18 образуют комплементарную пару в виде ключа для управления полезным сигналом, поступающим с источника дифференциального сигнала 5. Инвертирующие транзисторы n-типа 13, 15 и инвертирующие транзисторы р-типа 14, 16 образуют комплементарную пару в виде ключа для управления паразитным сигналом, поступающим с источника 5 в закрытом состоянии. Управление происходит путем подачи необходимого уровня напряжения с цифрового блока управления 6 на затворы транзисторов 11, 12, 13, 14, 15, 16 17.

В схеме, представленной на Фиг. 1, сигнал от источника дифференциального сигнала 5 поступает одновременно на все четыре дифференциальных ключа. В зависимости от управляющего сигнала три ключа 2, 3, 4 находятся в закрытом состоянии, один ключ 1 в открытом. Состояние ключей 1, 2, 3, 4 зависит от поданного от цифрового блока управления 6, соответствующего уровня напряжения. При этом в открытом состоянии (на Фиг. 2) инвертирующие и неинвертирующие цепи, которые управляются от блока управления 6, таким образом, что комплементарная пары МОП транзисторов 11, 17 и 12, 18 находятся в открытом положении, а комплементарная пара МОП транзисторов 13, 15 и 14, 16 находится в закрытом положении. Полезный сигнал через открытые комплементарные пары МОП транзисторов 11, 17 и 12, 18 будет поступать на нагрузку 7. Ширина затворов комплементарных пар МОП транзисторов 13, 15 и 14, 16, компенсирующих сигнал, выбирается таким образом, чтобы получить максимальное ослабление паразитного сигнала. Применение транзисторов n- и р-типа позволяет получить высокий уровень мощности принимаемого или передаваемого сигнала. В закрытом состоянии паразитный сигнал через комплементарные пары МОП транзисторов 11, 17 и 12, 18, которые находятся в закрытом положении, поступает на нагрузку 7. Сигнал, равный по величине паразитному сигналу и противоположный полярности через комплементарные пары компенсирующих МОП транзисторов 13, 15 и 14, 16, также поступает на нагрузку 7. Паразитный и компенсирующий сигналы, поступающие на нагрузку 7, вычитаются и, тем самым, обеспечивается высокий уровень изоляции.

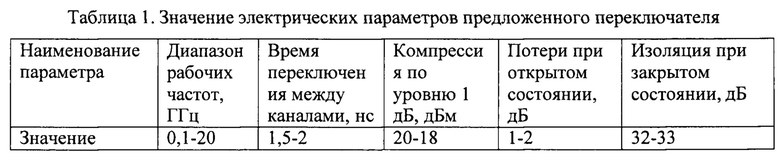

Результаты, полученные при использовании КМОП технологического процесса с минимальными размерами 0,09 мкм приведены в Таблице 1.

Значения приведенных параметров мощности и быстродействия переключения между каналами лучше ранее полученных результатов на дифференциальных переключателях (у прототипа) при сохранении минимальных потерь в открытом состоянии и максимальной изоляции в закрытом состоянии в широком диапазоне частот, тем самым, решается задача с быстродейственным переключением мощного сигнала между четырьмя выходами.

Источники информации:

1. Патент Китая № CN 114024540 А.

2. Патент №2454758.

3. Патент №2601172 - прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегральный аттенюатор с дискретным управлением | 2022 |

|

RU2792262C1 |

| Интегральный аттенюатор | 2016 |

|

RU2642538C1 |

| ПЕРЕКЛЮЧАТЕЛЬ С ВЫСОКОЙ ИЗОЛЯЦИЕЙ | 2015 |

|

RU2601172C2 |

| ПОЛУПРОВОДНИКОВАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 1991 |

|

RU2104601C1 |

| Усилитель заряда | 1983 |

|

SU1148003A1 |

| ДРАЙВЕР ПОЛУПРОВОДНИКОВОГО ЛАЗЕРА | 1999 |

|

RU2172514C2 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ | 1991 |

|

RU2010361C1 |

| Устройство для управления четырехфазным двигателем переменного тока | 1983 |

|

SU1138918A2 |

| Преобразователь логических уровней | 1990 |

|

SU1812634A1 |

Изобретение относится к электронной технике. Техническим результатом является расширение функциональных возможностей переключателей, увеличение мощности и быстродействия сигнала между четырьмя каналами, с возможностью цифрового управления, при сохранении минимальных потерь, максимальной изоляции и широкой полосы рабочих частот. Он достигается тем, что в схему переключателя введены четыре дифференциальных ключа, соединенные общим входом и имеющие четыре различных выхода, состоящие из неинвертирующих комплементарных пар МОП-транзисторов и инвертирующих комплементарных пар МОП-транзисторов. При этом параллельно n-типа транзисторам в ключах введены транзисторы р-типа, также введен цифровой блок таким образом, что входы первого, второго, третьего и четвертого дифференциальных ключей соединены с выходом блока управления, вход первого дифференциального ключа соединен с входом второго дифференциального ключа, входом третьего дифференциального ключа и входом четвертого дифференциального ключа, а также выходы дифференциальных ключей соединены с нагрузками соответственно. 2 ил., 1 табл.

Интегральный переключатель, содержащий два дифференциальных ключа, соединенные общим входом, состоящие из неинвертирующих МОП-транзисторов и инвертирующих МОП-транзисторов, связанные таким образом, что неинвертирующие транзисторы соединены с источником дифференциального сигнала и нагрузкой напрямую, а инвертирующие транзисторы соединены с источником дифференциального сигнала и нагрузкой перекрестно, отличающийся тем, что добавлены еще два дифференциальных ключа параллельно исходным двум, и параллельно n-типа транзисторам в ключах введены транзисторы р-типа таким образом, что стоки р-типа транзисторов соединены с истоками n-канальных транзисторов, а истоки р-типа транзисторов соединены со стоками n-канальных транзисторов, также введен цифровой блок таким образом, что входы первого, второго, третьего и четвертого дифференциальных ключей соединены с выходом блока управления, вход первого дифференциального ключа соединен с входом второго дифференциального ключа, входом третьего дифференциального ключа и входом четвертого дифференциального ключа, а также выходы первого, второго, третьего и четвертого дифференциальных ключей соединены с нагрузкой (7), нагрузкой (8), нагрузкой (9) и нагрузкой (10) соответственно.

| Интегральный аттенюатор | 2016 |

|

RU2642538C1 |

| ПЕРЕКЛЮЧАТЕЛЬ С ВЫСОКОЙ ИЗОЛЯЦИЕЙ | 2015 |

|

RU2601172C2 |

| Высоковольтный транзисторный переключатель | 1983 |

|

SU1129736A2 |

| US 20140184309 A1, 03.07.2014. | |||

Авторы

Даты

2025-02-25—Публикация

2024-04-11—Подача