Область техники, к которой относится изобретение

Описанные здесь варианты осуществления изобретения в общем касаются системы памяти, в которой контроллер памяти обменивается информацией по одному каналу или шине с несколькими модулями памяти, расположение выводов которых совместимо с разъемами, связанными с каналом и контроллером памяти.

Уровень техники

Контроллер памяти управляет потоком данных по некоторому устройству сопряжения или шине между процессором и одним или более модулями памяти. Контроллер памяти содержит логическую схему, нужную для чтения из модуля памяти и записи в модуль памяти и обновления данных, сохраненных в DRAM, и контроллер памяти выполнен как отдельная интегральная микросхема. Контроллер памяти поддерживает протокол, используемый множеством модулей памяти, связанных с каналом, такой как протокол синхронного динамического оперативного запоминающего устройства (SDRAM) удвоенной скорости передачи данных третьего поколения (DDR3) объединенного инженерного совета по электронным устройствам (JEDEC).

До использования сопряжения с памятью, контроллер памяти должен настроить модули памяти для работы, что делают путем регулировки момента времени, когда контроллер памяти будет активироваться для выборки считанных данных из модулей памяти. Контроллер памяти управляет устройством выравнивания сигнала, таким как устройство фазовой интерполяции, с целью выработки информации по фазе синхронизации и устройство выравнивания сигнала реагирует на сигналы управления фазой и эталонные сигналы, обладающие различными определенными фазами, что нужно для выравнивания сигнала выборки данных для выборки считанных данных центр в центр, где считанные данные будут переданы, или окно данных.

Краткое описание чертежей

Варианты осуществления изобретения описаны в качестве примера со ссылками на приложенные чертежи, которые выполнены не в масштабе и на которых аналогичные ссылочные позиции обозначены одинаковыми элементами.

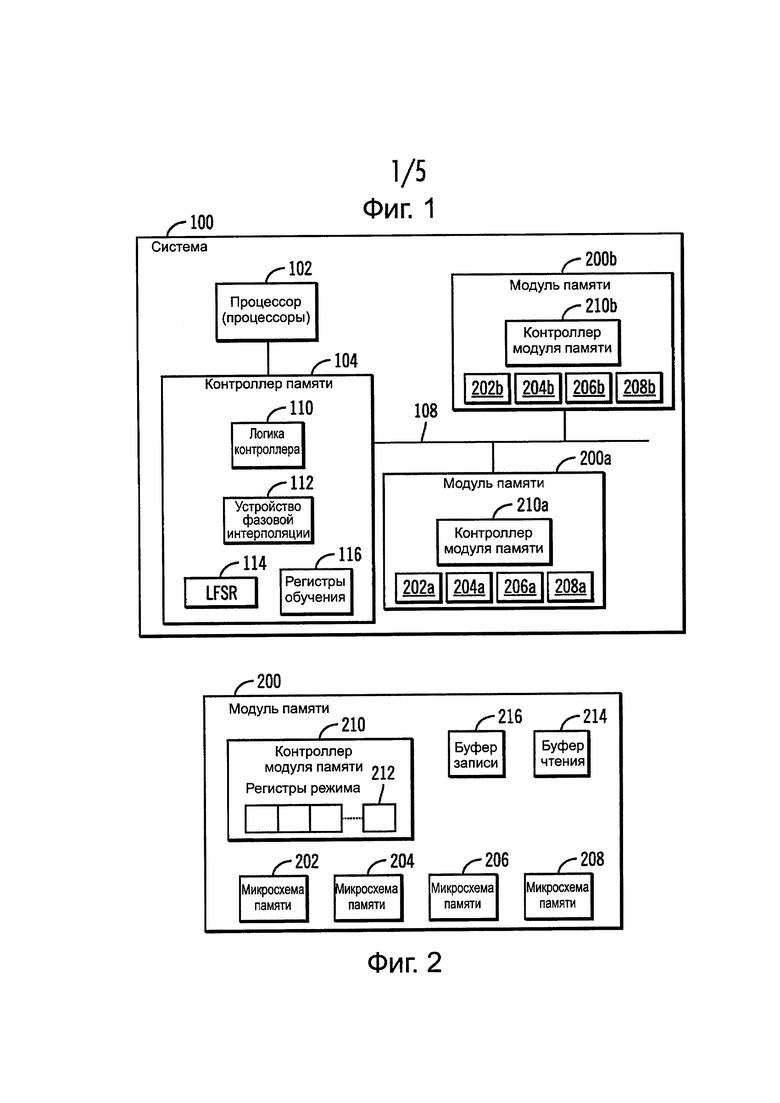

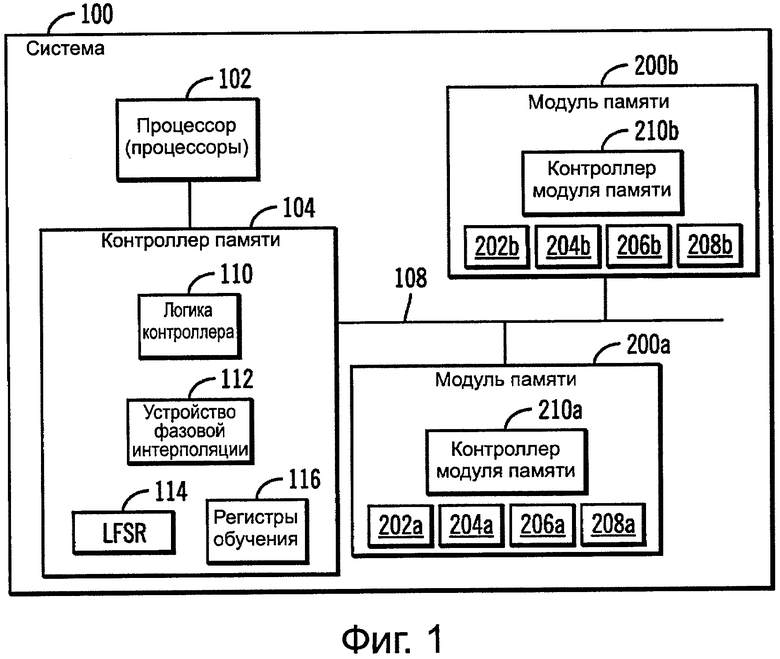

Фиг. 1 - вид, показывающий один вариант осуществления системы, содержащей систему памяти;

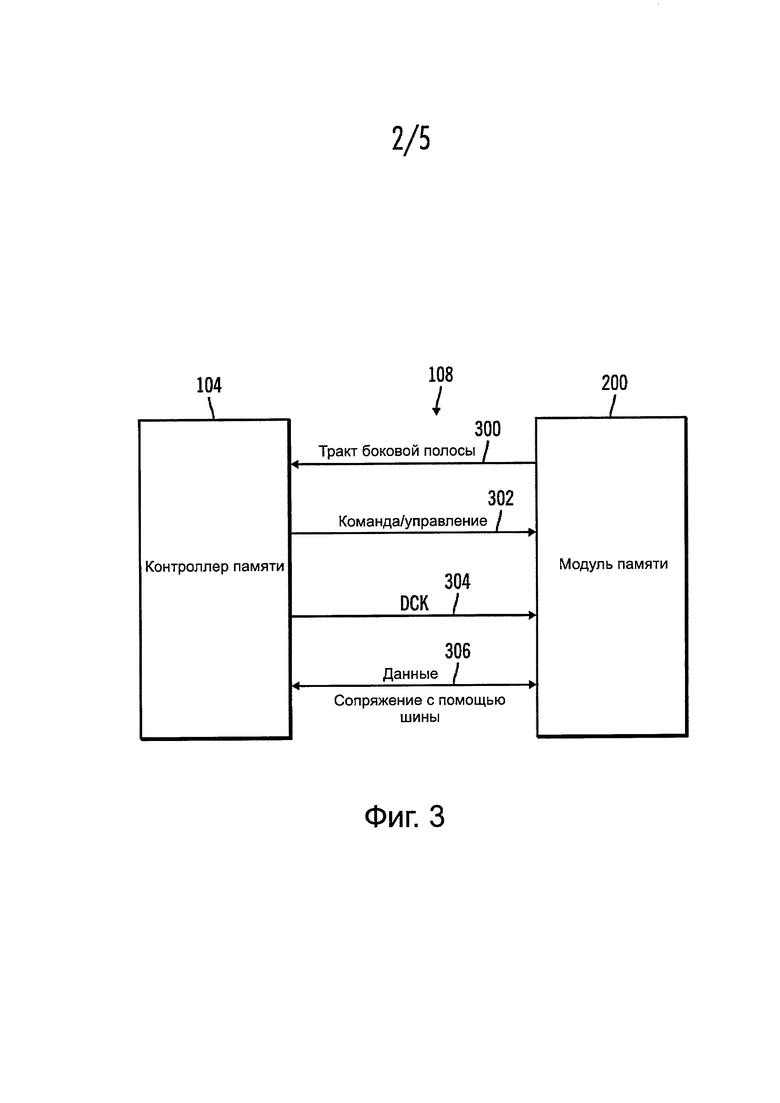

фиг. 2 - вид, показывающий один вариант осуществления модуля памяти;

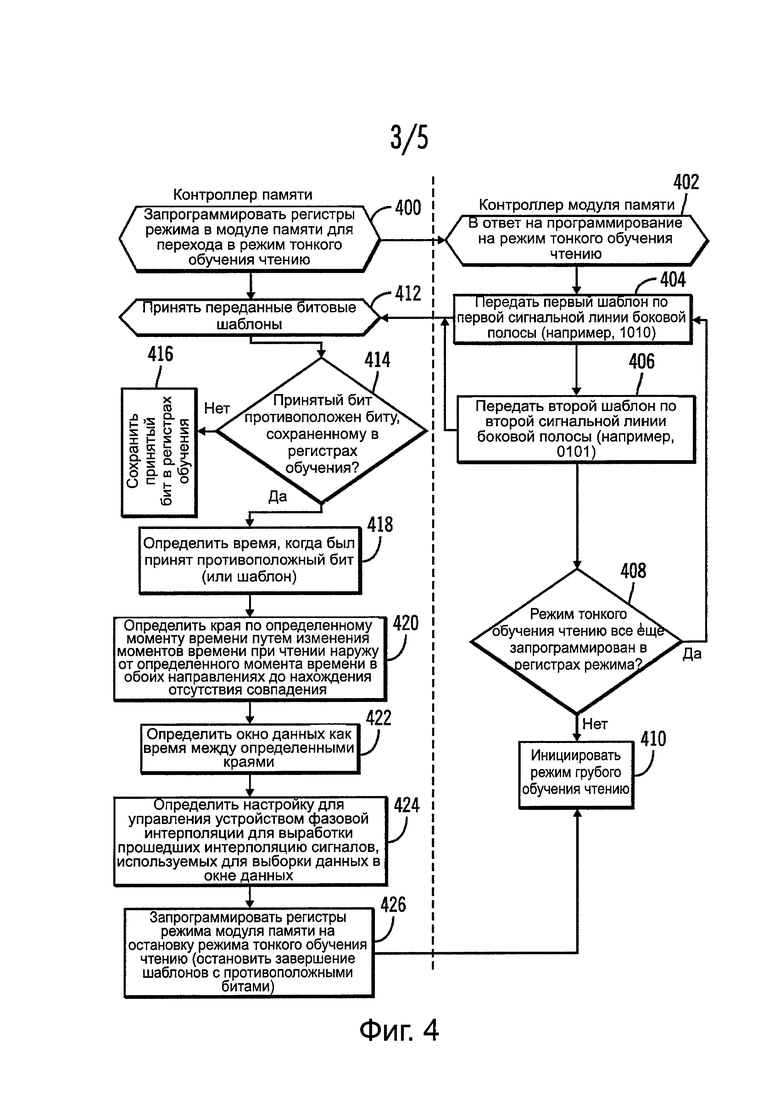

фиг. 3 - вид, показывающий один вариант осуществления сопряжения контроллера памяти и модуля памяти с помощью шины;

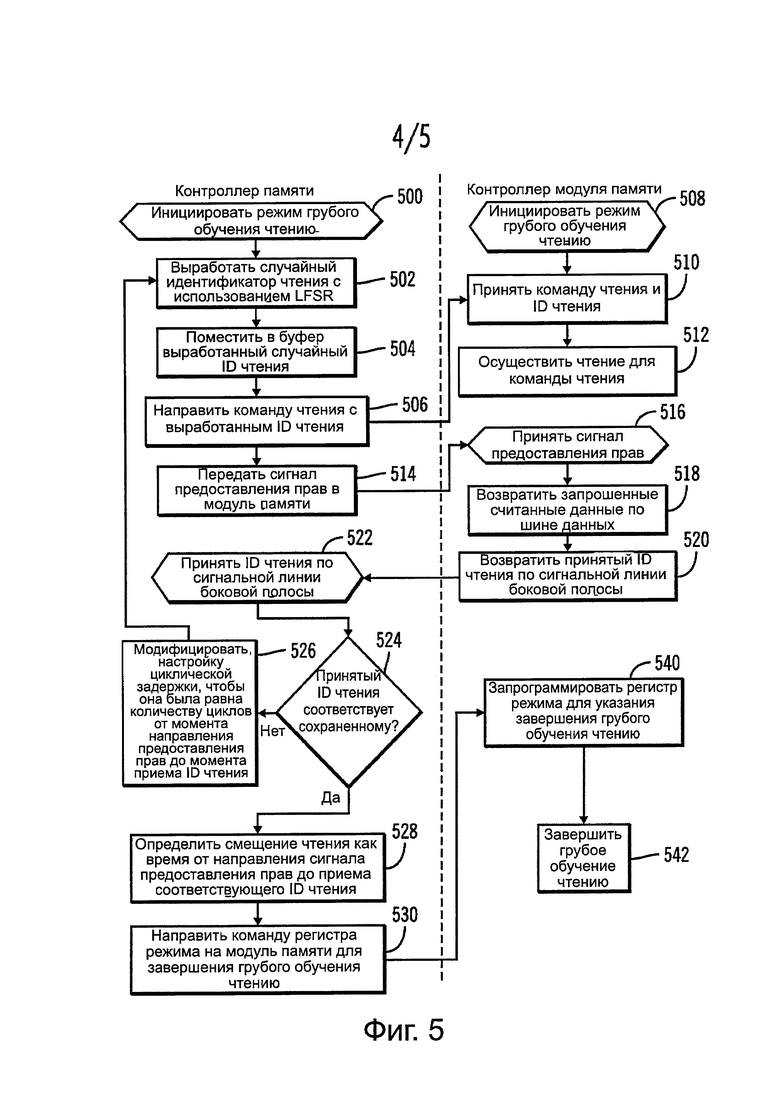

фиг. 4 - вид, показывающий один вариант осуществления операций для выполнения тонкого обучения чтению с целью регулировки устройства фазовой интерполяции для выработки сигнала выборки;

фиг. 5 - вид, показывающий один вариант осуществления операций для выполнения грубого обучения чтению с целью определения смещения чтения, при котором принимают считанные данные;

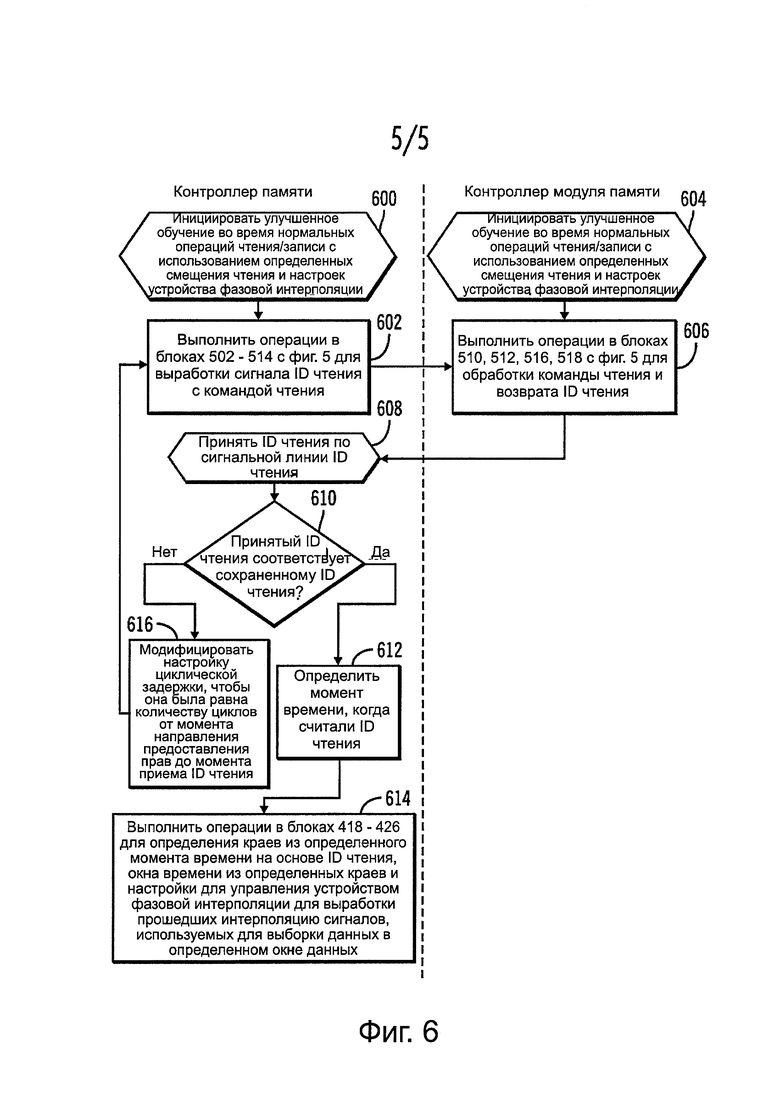

фиг. 6 - вид, показывающий один вариант осуществления операций для выполнения обучения устройства фазовой интерполяции во время нормальных операций чтения.

Описание вариантов осуществления изобретения

Что касается сопряжения памяти, модуль памяти передает стробирующие сигналы с сигналами данных на контроллер памяти, где контроллер памяти обрабатывает стробирующие сигналы с целью определения, когда включить устройства приема и считать данные.

Далее контроллер памяти может использовать другие процедуры для определения, когда осуществлять выборку считанных данных для чтения, такие как использование устройства фазовой интерполяции.

В описанных вариантах осуществления изобретения предложены технологии для осуществления тонкого обучения чтению, за которым следует грубое обучение чтению и далее улучшенное обучение чтению для регулировки устройства фазовой интерполяции во время нормальных операций чтения. В описанных вариантах осуществления изобретения предложен тракт сигнала боковой полосы для модуля памяти для возвращения сигналов, использованных контроллером памяти для регулировки устройства фазовой интерполяции. Далее, контроллер памяти предоставляет шаблоны сигналов модуля памяти, которые модуль памяти возвращает через тракт боковой полосы по шине, который отделен от линий данных и линий команд шины, для контроллера памяти с целью использования для определения времени смещения чтения, показывающего, когда включить устройства приема для осуществления выборки возвращенных считанных данных.

В последующем описании для обеспечения более глубокого понимания настоящего изобретения приведено большое количество конкретных деталей, таких как реализации логики, коды операций, средства определения операндов, реализации разделения/совместного использования/дублирования ресурсов, типы и взаимосвязи системных компонентов и логические альтернативы разделения/объединения. Тем не менее, специалистам в рассматриваемой области следует понимать, что настоящее изобретение может быть реализовано без подобных конкретных деталей. В других примерах структуры управления, схемы уровня логических элементов и полные последовательности команд программного обеспечения не показаны подробно, чтобы сделать изобретение более понятным. С помощью приведенных описаний специалисты в рассматриваемой области могут реализовать соответствующие функциональные возможности без проведения лишних экспериментов.

В этом описании слова «один вариант осуществления», «вариант осуществления», «пример варианта осуществления» и так далее показывают, что описанный вариант осуществления изобретения может содержать конкретный признак, структуру или характеристику, но каждый вариант осуществления не обязательно содержит конкретный признак, структуру или характеристику. Более того, такие фразы не обязательно относятся к одному и тому же варианту осуществления изобретения.

В приведенном ниже описании и формуле изобретения могут быть использованы термины «связанный» и «соединенный», а также их производные. Надо понимать, что эти термины не являются синонимами. «Связанный» используют для указания на то, что два или более элементов, которые могут быть в непосредственном физическом или электрическом контакте друг с другом или могут не быть в непосредственном физическом или электрическом контакте друг с другом, взаимодействуют друг с другом.

«Соединенный» используют для указания на установление соединения между двумя или более элементами, которые связаны друг с другом. Определенные варианты осуществления изобретения касаются электронных устройств памяти. Варианты осуществления изобретения содержат как устройства, так и способы образования электронных устройств.

На фиг. 1 показан некоторый вариант осуществления вычислительной системы 100, содержащей один или более процессоров 102, контроллер 104 памяти и несколько модулей 200а, 200b памяти, которые обычно установлены на материнской плате. Процессоры 102 могут содержать центральный процессор, многоядерный процессор. Контроллер 104 памяти в ответ на запросы о доступе к памяти от процессоров 102 взаимодействует с несколькими модулями 200а, 200b памяти по шине 108, так же называемой каналом, сопряжением с помощью шины и так далее, при этом оба модуля 200а, 200b памяти отдельно и независимо друг от друга соединены с одной и той же шиной 108. Контроллер 104 памяти может содержать логическую схему 110 контроллера, включающую в себя код или логику, выполняемую для осуществления операций; устройство 112 фазовой интерполяции для приема сигналов времени ввода и выработки прошедшего интерполяцию сигнала выборки, выровненного с окном данных принятого сигнала считанных данных; регистр (LFSR) 114 сдвига с линейной обратной связью для выработки случайных идентификаторов чтения, используемых на фазах грубого и улучшенного обучения чтению; и регистры 116 обучения для хранения значений, использованных во время операций обучения.

В варианте осуществления изобретения с фиг. 1 модули 200a, 200b памяти установлены в разъемы или гнезда памяти на материнской плате системы 100. Модули 200а, 200b памяти могут содержать модули памяти одного или разных типов, расположение контактов которых совместимо с расположением контактов в разъемах памяти на материнской плате. Далее модули памяти могут поддерживать одинаковые или разные протоколы памяти, такие как протокол удвоенной скорости передачи данных четвертого поколения (DDR4) и дополнительные протоколы. Хотя показаны только два модуля 200а, 200b памяти, может присутствовать несколько модулей памяти.

Каждый из модулей 200а, 200b памяти содержит микросхемы 202а, 204а, 206а, 208а и 202b, 204b, 206b, 208b памяти соответственно на одной или обеих сторонах модулей 200а, 200b памяти для хранения данных. Микросхемы памяти, например, микросхемы DRAM, расположенные на одной или обеих сторонах пакета 200а, 200b модулей памяти, содержат элементы хранения, в которых хранят данные, используемые процессором 102.

Каждый модуль 200а, 200b памяти может содержать контроллер 210а, 210b модуля памяти для согласования управления памятью и операций доступа с контроллером 104 памяти. Контроллер 104 памяти содержит логическую схему, такую как логическая схема 110, для управления операциями обучения чтению, операциями чтения и записи и операциями управления памятью для модулей 200а, 200b памяти, соединенных с шиной 108, и управления сопряжением процессора 102 с модулями 200а, 200b памяти. Контроллер 104 памяти и/или модули 200а, 200b памяти могут быть объединены с процессором 102 или могут быть реализованы в логической схеме, отдельной от процессора 102 на материнской плате системы 100, показанной на фиг. 1.

Материнская плата системы 100 может содержать разъем памяти, совместимый с микросхемами памяти различных типов, чтобы позволить модулям 200а, 200b памяти различных типов, поддерживающим устройства памяти различных типов с различными протоколами памяти, до тех пор, пока модули 200а, 200b памяти различных типов совместимы с расположением контактов в разъемах памяти.

В одном варианте осуществления изобретения модули 200а, 200b памяти могут содержать модули памяти одного или разных типов синхронного динамического оперативного запоминающего устройства двойной скорости передачи данных (DDR SDRAM), таких как LPDDR, модули памяти с двухрядным расположением микросхем (DIMM), таких как безбуферные DIMM (UDIMM), модуль памяти (LRDIMM) с двухрядным расположением микросхем и уменьшенной нагрузкой, малогабаритный модуль памяти (SODIMM) с двухрядным расположением микросхем и так далее. Модули 200а, 200b памяти могут реализовать различные формы памяти, в том числе, помимо прочего, NAND (флеш) память, ферроэлектрическое оперативное запоминающее устройство (FeTRAM), энергонезависимую память на основе нанопроволоки, трехмерную (3D) перекрестную память, такую как память (РСМ) на фазовых переходах, магниторезистивное оперативное запоминающее устройство (MRAM), MRAM с переносом спинового момента (STT) и так далее.

На фиг. 2 показаны дополнительные подробности некоторого варианта осуществления модуля 200 памяти, такого как модули 200а, 200b памяти, как модуля, содержащего контроллер 210 модуля памяти, который осуществляет операции модуля памяти и взаимодействия с контроллером 104 памяти. Модуль 200 памяти может содержать регистры 212 режима в контроллере 210 модуля памяти, которые содержат данные, которые могут быть сконфигурированы с использованием команды установки (MRS) режима регистра, буфер 214 чтения и буфер 216 записи для буферизации чтения и записи данных для микросхем 202, 204, 206, 208 памяти. Буферы 214, 216 могут быть выполнены в контроллере 210 модуля памяти или в схеме, внешней по отношению к контроллеру 210 модуля памяти из модуля 200 памяти. В других вариантах осуществления изобретения регистры 212 режима могут быть реализованы в микросхемах 202, 204, 206, 208 памяти.

Код или логика, реализуемая контроллером 210 модуля памяти, и операции контроллера 104 памяти могут быть реализованы в виде считываемого компьютером кода, загруженного в память и выполняемого процессором, или может быть закодирована аппаратным образом, например, в специализированной интегральной схеме (ASIC), программируемой пользователем вентильной матрице (FPGA) и так далее.

Логика или код описанных вариантов осуществления изобретения может быть реализована на считываемом машиной носителе информации, содержащем устройство, включающее в себя электрические и другие аппаратные элементы для хранения выполняемых машиной команд. Считываемый машиной носитель может содержать, помимо прочего, флеш-память, оптические диски, постоянное запоминающее устройство (CD-ROM) из компакт-дисков, постоянное запоминающее устройство из универсальных цифровых/видео дисков (DVD), стираемое программируемое постоянное запоминающее устройство (EPROM), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM), магнитные или оптические карты и другие считываемые машиной носители, подходящие для хранения электронных команд.

В альтернативных вариантах осуществления логика или код описанных вариантов осуществления изобретения могут быть реализованы в носителе передачи сигнала.

На фиг. 3 показан некоторый вариант осуществления линий 108 сопряжения с помощью шины между контроллером 104 памяти и модулем 200 памяти, содержащих тракт 300 боковой полосы, включающий в себя линии боковой полосы; сигнальные линии 302 команд и управления, по которым контроллер 104 памяти передает команды в модуль 200 памяти; дифференциальный входной сигнал (DCLK) 304 синхронизации от контроллера 104 памяти до модуля 200 памяти, чтобы модуль 200 памяти использовал для выборки адреса и сигналов управления по линиям 302 команды/управления; и линии 306 данных, по которым передают считываемые и записываемые данные между контроллером 104 памяти и модулем 200 памяти. Дополнительные линии шины могут быть предусмотрены для других целей.

Тракт 300 боковой полосы содержит одну или более сигнальных линий для передачи дополнительной информации, которую контроллер 104 памяти может использовать для обучения и других целей, и в ответ на сигналы управления от контроллера 104 памяти. Например, контроллер 104 памяти может направить сообщение предоставления прав в модуль 200 памяти в ответ на прием уведомления о чтении, что может привести к тому, что модуль 200 памяти направит сигнал идентификатора (ID) чтения по тракту 300 боковой полосы до направления данных. Модуль 200 памяти может использовать тракт 300 боковой полосы для передачи ID чтения, который ранее передан контроллером 104 памяти с запросом на чтение, и в ответ модуль 200 памяти может возвратить ID чтения по тракту 300 боковой полосы без обработки, например, фильтрации, интерполяции и т.д. Далее, в определенных вариантах осуществления изобретения тракт 300 боковой полосы может содержать пары сигналов синхронизации в модуле 200 памяти.

В одном варианте осуществления изобретения тракт 300, который передает ID чтения назад в контроллер 104 памяти, передает сигналы на частоте команд, а не частоте синхронизации. В одном варианте осуществления изобретения тракт 300 боковой полосы может быть предназначен для передачи синхронизации и передачи шаблона синхронизации, который является двойным периодом входного сигнала (DCLK) синхронизации 304. Модуль 200 памяти может передавать сигналы и принимать ID чтения, как часть сигнала управления, по тракту 300 боковой полосы до передачи считанных данных. Эти сигналы ID чтения могут передавать пакет данных с конкретным временным взаимоотношением относительно сигнала управления, такого как сигнал предоставления прав. Это временное взаимоотношение может изменяться в некотором диапазоне, в зависимости от задержек модуля памяти и канала. В определенных вариантах осуществления изобретения модуль 200 памяти может не передавать тактовый импульс с пакетом данных, так что контроллер 104 памяти осуществляет тонкое обучение чтению с целью обучения задержкам выборки сигнала ID чтения для выравнивания по центру сигнального окна ID чтения с целью получения низкой частоты появления ошибочных битов. Сигналы ID чтения могут быть переданы на половине частоты шины данных, но эти скорости тем не менее могут достигать 1600 MTps.

На фиг. 4 показан некоторый вариант операций, осуществляемых логической схемой 110 контроллера памяти и логической схемой 202 модуля памяти с целью предоставления возможности логической схеме ПО контроллера памяти вместе с модулем 200 памяти осуществить тонкое обучение чтению устройства 112 фазовой интерполяции для обеспечения выравнивания прошедших интерполяцию сигналов выборки в окне данных. Тонкое обучение чтению может быть инициировано во время опробования шины 108 при загрузке системы 100. Для инициирования тонкого обучения чтению логическая схема ПО контроллера памяти передает команду (в блоке 400) для программирования регистров 212 режима в модуле 200 памяти с целью начала режима тонкого обучения чтению. В ответ на запись в регистры 212 режима с целью указания на режим тонкого обучения чтению, контроллер 210 модуля памяти передает (в блоках 404 и 406) первый шаблон по первой боковой сигнальной линии тракта 300 боковой полосы и второй шаблон по второй сигнальной линии, отличной от первой сигнальной линии, тракта 300 боковой полосы. Первый и второй шаблоны могут содержать сигналы синхронизации, содержащие противоположные значения, такие как 1010 и 0101. В определенных вариантах осуществления изобретения шаблоны синхронизации могут обладать периодом, равным двум периодам DLCK 304 сигнала синхронизации, и могут обладать некоторой частотой в сигнальной линии 302 команды/управления, отличной от частоты 304 синхронизации. Сигналы, такие как 1010 и 0101, в отдельных сигнальных линиях тракта 300 боковой полосы могут не совпадать по фазе или могут совпадать по фазе. Далее переданные в блоках 404 и 406 шаблоны могут быть переданы в непрерывном режиме по отдельным линиям тракта 300 боковой полосы.

После передачи битов первого и второго шаблонов, если (в блоке 408) регистры 212 режима продолжают указывать режим тонкого обучения чтению, то управление возвращается в блок 404 для продолжения передачи шаблонов, обладающих противоположными значениями. Если (в блоке 408) режим тонкого обучения закончен, то может начаться (в блоке 410) фаза грубого обучения чтению.

При приеме (в блоке 412) логической схемой 110 контроллера памяти переданного битового шаблона, если (в блоке 414) принятый бит не является противоположным значением для бита, сохраненного в регистрах 116 обучения, 0 в отличие от 1 или 1 в отличие от нуля, то принятый бит сохраняют (в блоке 416) в регистрах 116 обучения. Если (в блоке 414) значение принятого бита является противоположным относительно значения сохраненного бита, то выполняют (в блоке 418) определение времени приема для противоположного бита (или шаблона). Далее логическая схема 110 контроллера памяти определяет (в блоке 422) края по определенному моменту времени, что делают путем изменения моментов времени для чтения, то есть смещают наружу от определенного момента времени в обоих направлениях до нахождения совпадения, когда края окна данных определены в каждом направлении от определенного момента времени, в который был принят противоположный битовый шаблон. Далее определяют (в блоке 422) окно данных как время между моментами времени краев. В одном варианте осуществления изобретения края окна данных определяют путем изменения моментов времени устройства 112 фазовой интерполяции с целью смещения наружу от определенного окна данных в каждом направления для нахождения точки, в которой нет совпадения.

На основе этих сигналов моментов времени, выполняют определение (в блоке 424) установки для управления устройством 112 фазовой интерполяции с целью выработки прошедших интерполяцию сигналов, используемых для выборки данных в определенном окне данных. После обучения устройства 112 фазовой интерполяции с целью выработки прошедших интерполяцию сигналов для выборки в окне данных между краями, логическая схема 110 контроллера памяти записывает (в блоке 426) в регистр 212 режима из модуля 200 памяти с целью остановки тонкого обучения чтению, чтобы контроллер модуля памяти прекратил направлять шаблоны противоположных битов по тракту 300 боковой полосы.

В некоторых вариантах осуществления изобретения обнаружение переходов между выборкой 1 и 0 и наоборот указывает на время чтения данных, которые могут содержать окно данных, края или считанные данные между краев. Эти операции обучения могут требовать четырех битов результата обучения для захвата четности/нечетности на сигнал. Два бита могут быть использованы если только захватывают нечетность или четность. Устройство 112 фазовой интерполяции выполнено для выработки прошедшей интерполяцию выборки для чтения данных в середине между границами окна данных.

В описанном выше варианте осуществления изобретения бит шаблона сравнивают с целью определения определенного момента времени, в который начинают смещать края окна данных. В альтернативном варианте осуществления изобретения контроллер 110 памяти может сравнивать не только бит, а может сравнивать весь шаблон (например, 0101, 1010), так что окно данных определяют в блоках 414 и 418 в момент времени, когда обнаруживают противоположное для сохраненного шаблона, а не только для одного бита. Далее, в таких вариантах осуществления изобретения, когда сравнивают целый шаблон, в блоке 416 в регистрах 116 обучения сохраняют целый шаблон, а не только один бит.

На фиг. 5 показан некоторый вариант операций, осуществляемых логической схемой 110 контроллера памяти и логической схемой 202 модуля памяти с целью предоставить возможность логической схеме 110 контроллера памяти вместе с модулем 200 памяти осуществить грубое обучение чтению контроллера 104 памяти для определения смещения или времени ожидания до того, как контроллер 104 памяти активирует чтение данных после сигнала предоставления прав, направленного для возобновления чтения данных. При запуске (в блоке 500) грубого обучения чтению логическая схема 110 контроллера памяти вырабатывает (в блоке 502) случайный ID чтения с использованием LFSR 114. Выработанный ID чтения помещают в буфер (в блоке 504) в регистрах 116 обучения. Логическая схема 110 контроллера памяти направляет (в блоке 506) команду чтения с выработанным ID чтения в модуль 200 памяти. Пока контроллер 210 модуля памяти работает в режиме грубого обучения чтению (в блоке 508) при приеме (в блоке 510) команды чтения и ID чтения контроллер 210 модуля памяти выполняет команду чтения (в блоке 512).

После направления команды чтения с ID чтения (в блоке 506) логическая схема 110 контроллера памяти передает (в блоке 514) сигнал предоставления прав в модуль 200 памяти по сопряжению 108 с помощью шины. При приеме (в блоке 516) сигнала предоставления прав запрошенные данные возвращают (в блоке 518) по шине 306 данных и принятый ID чтения возвращают (в блоке 520) по тракту 300 боковой полосы. Сигнал ID чтения возвращают в пакетном режиме. В определенных вариантах осуществления изобретения ID чтения возвращают сначала, до считанных данных, по тракту 300 боковой полосы. Таким образом, контроллер 210 модуля памяти возвращает ID чтения в контроллер 104 памяти без фильтрации или интерпретации данных. В определенных вариантах осуществления изобретения логическая схема 110 контроллера памяти может предоставить сигнал предоставления прав без ожидания уведомления (АСК) от модуля 200 памяти для команды чтения.

При приеме контроллером 104 памяти (в блоке 522) ID чтения по тракту 300 боковой полосы, логическая схема 110 контроллера памяти определяет (в блоке 524), соответствует ли принятый ID чтения переданному ID чтения, сохраненному в регистрах 116 обучения. Если (по ответвлению НЕТ блока 524) нет соответствия, то логическая схема 110 контроллера памяти модифицирует (в блоке 526) настройку циклической задержки, чтобы она была равна количеству циклов от того, когда направили предоставление прав, до того, когда приняли ID чтения. Настройка циклической задержки является грубой временной настройкой момента времени, когда логическая схема 110 контроллера памяти пытается считать данные, и это время грубой циклической задержки или время уровня цикла регулируют в блоке 526 до тех пор, пока время не станет соответствовать моменту времени приема ID чтения, или настройка двухсторонней задержки от момента времени установления предоставления прав. Из блока 526 управление переходит назад на блок 502 для непрерывной выработки случайных ID чтения для грубого обучения чтению до тех пор, пока не появится соответствие. Если (в блоке 524) направленный и принятый ID чтения соответствуют, то логическая схема 110 контроллера памяти определяет (в блоке 526) смещение чтения как разность времен от направления сигнала предоставления прав до приема соответствующего ID чтения. После определения смещения чтения логическая схема 110 контроллера памяти может направить (в блоке 530) команду регистра режима в модуль 200 памяти для определения грубого обучения чтению. Контроллер 210 модуля памяти программирует (в блоке 540) регистры 212 режима после приема команды на завершение (в блоке 542) грубого обучения чтению.

Тонкое обучение чтению вырабатывает настройки для управления устройством 112 фазовой интерполяции с целью выработки прошедшего интерполяцию сигнала выборки для чтения в окне данных, когда передают считанные данные, а результатом грубого обучения чтению является смещение чтения, которое используют для определения того, когда начинать прием считанных данных после установки сигнала предоставления прав. После тонкого и грубого обучения чтению можно начать операции нормального чтения с использованием определенных настроек устройства 112 фазовой интерполяции и смещения чтения.

На фиг. 6 показан некоторый вариант осуществления операций, выполняемых логической схемой 110 контроллера памяти и логической схемой 202 модуля памяти с целью выполнения улучшенного обучения чтению во время операций нормального чтения для дополнительного улучшения настроек устройства 112 фазовой интерполяции, используемых для выработки сигнала выборки, используемого для выборки сигнала считанных данных. После начала (в блоке 600) улучшенного обучения во время операций чтения/записи с использованием определенных настроек устройства фазовой интерполяции и смещения чтения, логическая схема 110 контроллера памяти осуществляет (в блоке 602) операции в блоках 502-514 с фиг. 5 для выработки и передачи сигнала ID чтения с командой чтения. При нахождении в режиме улучшенного обучения во время операций чтения/записи (в блоке 604), контроллер 210 модуля памяти осуществляет (в блоке 606) операции в блоках 510, 512, 516, 518 с фиг. 5 с целью обработки принятой команды чтения и возврата ID чтения по тракту 300 боковой полосы.

При приеме контроллером 104 памяти (в блоке 608) ID чтения по тракту 300 боковой полосы, если (в блоке 610) принятый ID чтения соответствует переданному ID чтения, сохраненному в регистрах 116 обучения, то определяют (в блоке 612) момент времени, когда был считан ID чтения. Далее логическая схема 110 контроллера памяти осуществляет (в блоке 614) операции в блоках 418-426 с целью определения краев из определенного времени ID чтения, окна времени из определенных краев и настройки для управления устройством фазовой интерполяции для выработки прошедших интерполяцию сигналов, используемых для выборки данных в определенном окне данных. Эти операции для регулировки устройства 112 фазовой интерполяции с использованием случайно выработанных ID чтения выполняют непрерывно для определения границ окна данных и повторного центрирования настроек устройства 112 фазовой интерполяции с более агрессивными и реалистичными шаблонами в форме случайно выработанных ID чтения, что противоположно повторяющимся противоположным шаблонам, используемым во время тонкого обучения чтению.

Если (по ответвлению НЕТ блока 610) нет соответствия, то логическая схема 110 контроллера памяти модифицирует (в блоке 616) настройку циклической задержки, чтобы она была равна количеству циклов от того, когда направили предоставление прав, до того, когда приняли ID чтения. Настройка циклической задержки является грубой временной настройкой того, когда логическая схема 110 контроллера памяти пытается считать данные и это время грубой циклической задержки или время уровня цикла регулируют в блоке 526 до тех пор, пока время не станет соответствовать тому, когда принимают ID чтения, или настройка кругового ожидания от того, когда устанавливают предоставление прав. Из блока 616 управление переходит назад на блок 602 для непрерывной выработки случайных ID чтения для улучшенного тонкого обучения до тех пор, пока не появится соответствие.

Описанные варианты осуществления изобретения позволяют проводить обучение сигналов ID чтения боковой полосы по линии 300 ID чтения с целью достижения низкой частоты появления ошибочных битов в шине 100. Описанное обучение чтению эффективно в том плане, что при нем достигают выборки, отцентрированной в окне относительно шаблона выборки. Описанные варианты осуществления изобретения могут дополнительно вырабатывать шаблоны высокого напряжения в шине 300 ID чтения, что нужно для определения границ наихудшего случая.

Следует понимать, что ссылки в этом описании на «один вариант осуществления изобретения» или «некоторый вариант осуществления изобретения» означают, что конкретный признак, структура или характеристика, описанная в связи с вариантом осуществления настоящего изобретения, содержится, по меньшей мере, в одном варианте осуществления настоящего изобретения. Следовательно, это подчеркивается и следует понимать, что две или более ссылок на «один вариант осуществления изобретения» или «некоторый вариант осуществления изобретения» или «альтернативный вариант осуществления изобретения» в различных частях этого описания не обязательно касаются одного и того же варианта осуществления изобретения. Более того, конкретные признаки, структуры или характеристики могут быть объединены подходящим образом в одном или более вариантах осуществления изобретения.

Аналогично, следует понимать, что в приведенном выше описании вариантов осуществления изобретения различные признаки иногда сгруппированы вместе в одном варианте осуществления изобретения, чертеже или описании изобретения, что сделано с целью упрощения описания, для помощи в понимании одного или нескольких различных аспектов изобретения. Тем не менее, этот способ описания не нужно интерпретировать как отражающий намерение показать, что объект патентования требует больше признаков, чем точно перечислено в каждом пункте формулы изобретения. В отличие от сказанного, как отражает приведенная ниже формула изобретения, аспекты изобретения расположены не во всех признаках единственного описанного выше варианта осуществления изобретения. Таким образом, формула изобретения, приведенная после подробного описания, настоящим заявлением явно встроено в приведенное подробное описание.

Описанные операции контроллера 104 памяти и модулей 200 памяти могут быть реализованы как способ, устройство или считываемый компьютером носитель с использованием стандартных технологий программирования и/или машиностроения, что делается для выработки программного, программно-аппаратного или аппаратного обеспечения или любой их комбинации. Описанные операции могут быть реализованы в виде кода или логики, которые поддерживаются в «считываемом компьютером носителе» и которые могут непосредственно выполнять функции, или, когда процессор может считывать и выполнять код со считываемого компьютером носителя. Считываемый компьютером носитель содержит, помимо прочего, по меньшей мере, одно из следующего: электронную схему, материалы для хранения, неорганические материалы, органические материалы, биологические материалы, корпус, оболочку, покрытие и аппаратное обеспечение. Считываемый компьютером носитель может содержать, помимо прочего, магнитный носитель (например, накопители на жестких дисках, флоппи-диски, ленту и так далее), оптические носители (CD-ROM, DVD, оптические диски и так далее), энергозависимые и энергонезависимые устройства хранения (например, EEPROM, ROM, PROM, RAM, DRAM, SRAM, флеш-память, встроенное программное обеспечение, программируемые логические схемы и так далее), твердотельные устройства (SSD) и так далее. Считываемый компьютером носитель может дополнительно содержать цифровые логические схемы, реализованные аппаратно (например, интегральную микросхему, программируемое логическое устройство, программируемую вентильную матрицу (FPGA), программируемую пользователем вентильную матрицу (FPGA), специализированную интегральную схему (ASIC) и так далее). Также код, реализующий описанные операции, может быть реализован в «сигналах передачи», где сигналы передачи могут распространяться в пространстве или по среде передачи, такой как оптическое волокно, медный провод и так далее. Сигналы передачи, в которые закодированы код или логика, могут дополнительно содержать беспроводной сигнал, спутниковую передачу, радиоволны, инфракрасные сигналы, сигналы по технологии Bluetooth и так далее. Программный код, встроенный в считываемый компьютером носитель, может быть передан как сигналы передачи от станции передачи или компьютера до станции приема или компьютера. Считываемый компьютером носитель не содержит исключительно сигналы передачи. Специалистам в рассматриваемой области ясно, что можно предложить много модификаций этой конфигурации, не выходя за границы объема настоящего изобретения и изготавливаемый продукт может содержать подходящий носитель информации, известный в технике.

Примеры

Приведенные ниже примеры касаются дополнительных вариантов осуществления изобретения.

Пример 1 является устройством, связанным, по меньшей мере, с одним модулем памяти по шине и содержащим: сопряжение с помощью шины, по меньшей мере, для одного модуля памяти; логическую схему контроллера памяти, которая при работе осуществляет операции, эти операции включают в себя следующее: программируют модуль памяти с целью запуска режима обучения, в котором модуль памяти передает непрерывные битовые шаблоны по тракту боковой полосы сопряжения с помощью шины; принимают битовые шаблоны по сопряжению с помощью шины; определяют из принятых битовых шаблонов переход значений в битовом шаблоне с целью определить окно данных между определенными переходами значений; и определяют настройку с целью управления устройством фазовой интерполяции для выработки прошедших интерполяцию сигналов, используемых для выборки данных в рамках определенного окна данных.

В примере 2 объект из примера 1 может дополнительно содержать то, что операции дополнительно включают в себя следующее: программируют модуль памяти с целью завершения режима обучения и направляют битовые шаблоны в ответ на определение окна данных и настройки с целью управления устройством фазовой интерполяции.

В примере 3 объект из примера 1 может дополнительно содержать то, что определение из принятых битовых шаблонов синхронизации перехода включает в себя следующее: сохраняют считанное значение из битового шаблона в регистре; и определяют, соответствует ли следующее считанное значение из последующей передачи битового шаблона считанному значению в регистре, при этом окно данных определяют между краями двух считанных значений, которые соответствуют значениям, сохраненным в регистре.

В примере 4 объект из примера 1 может дополнительно содержать следующее: битовые шаблоны содержат первый непрерывный битовый шаблон по тракту боковой полосы сопряжения с помощью шины, используемого для сигналов идентификатора чтения, и второй непрерывный битовый шаблон по тракту боковой полосы, при этом первый и второй непрерывные битовые шаблоны обладают противоположными значениями.

В примере 5 объект из примера 4 может дополнительно содержать следующее: первый непрерывный битовый шаблон направляют по первой сигнальной линии идентификатора чтения и первый непрерывный битовый шаблон содержит непрерывный 1010 шаблон и при этом второй непрерывный битовый шаблон направляют по второй сигнальной линии идентификатора чтения и второй непрерывный битовый шаблон содержит непрерывный 0101 шаблон.

В примере 6 объект из примера 5 может дополнительно содержать следующее: первый и второй непрерывные битовые шаблоны чередуются между 0 и 1 каждый Тактовый интервал с целью создания шаблона синхронизации с периодом, который в два раза больше периода тактового интервала сопряжения с помощью шины.

В примере 7 объект из примера 1 может дополнительно содержать следующее: сопряжение с помощью шины включает в себя линии команд, по которым передают команды, линии данных, по которым передают данные, и сигнальные линии идентификаторов чтения, при этом битовые шаблоны передают по сигнальным линиям идентификаторов чтения на частоте команд, которая меньше частоты синхронизации.

В примере 8 объект из примера 1 может дополнительно содержать то, что операции дополнительно включают в себя следующее: в ответ на определение настройки для управления устройством фазовой интерполяции, направляют в модуль памяти команду чтения с идентификатором чтения; принимают считанные данные из модуля памяти, в том числе возвращенный идентификатор чтения; и определяют смещение чтения в ответ на определение того, что возвращенный идентификатор чтения соответствует идентификатору чтения, направленному с командой чтения, при этом смещение чтения используют для определения того, когда начинать выборку считанных данных в окне данных с использованием определенной настройки для устройства фазовой интерполяции.

Пример 9 является устройством, связанным, по меньшей мере, с одним модулем памяти по шине и содержащим: сопряжение с помощью шины, по меньшей мере, для одного модуля памяти; логическую схему контроллера памяти, которая при работе осуществляет операции грубого обучения чтению, эти операции включают в себя следующее: направляют в модуль памяти команду чтения и идентификатор чтения; принимают из модуля памяти по сопряжению с помощью шины считанные данные и принятый идентификатор чтения; и определяют смещение чтения в ответ на определение того, что принятый идентификатор чтения от модуля памяти включает в себя идентификатор чтения, направленный с командой чтения, при этом смещение чтения используют для определения того, когда начать выборку данных в окне принятых считанных данных.

В примере 10 объект из примера 9 может дополнительно содержать то, что операции дополнительно включают в себя следующее: в ответ на определение того, что принятый идентификатор чтения не соответствует идентификатору чтения, направленному с командой чтения, осуществляют, по меньшей мере, одну итерацию выработки нового идентификатора чтения для включения его в новую команду чтения, направляемую в модуль памяти, что делают до определения смещения чтения в ответ на принятые из модуля памяти считанные данные, содержащие выработанный новый идентификатор чтения.

В примере 11 объект из примера 10 может дополнительно содержать регистр (LFSR) сдвига с линейной обратной связью, используемый для выработки идентификатора чтения и новых идентификаторов чтения для обеспечения случайных значений идентификаторов чтения.

В примере 12 объект из примера 9 может дополнительно содержать следующее: грубое обучение чтению завершают в ответ на принятый идентификатор чтения, содержащий идентификатор чтения, направленный с командой чтения.

В примере 13 объект из примера 9 может дополнительно содержать следующее: идентификатор чтения является причиной того, что модуль памяти зацикливает идентификатор чтения, когда возвращает считанные данные в ответ на команду чтения.

В примере 14 объект из примера 9 может дополнительно содержать следующее: идентификатор чтения передают из модуля памяти по тракту боковой полосы.

В примере 15 объект из примера 8 может дополнительно содержать следующее: сопряжение с помощью шины включает в себя линии команд, по которым передают команды, линии данных, по которым передают данные, и сигнальные линии идентификаторов чтения, при этом модуль памяти возвращает идентификатор чтения по сигнальным линиям идентификаторов чтения.

В примере 16 объект из примера 15 может дополнительно содержать то, что идентификатор чтения возвращают из модуля памяти по сигналам синхронизации.

В примере 17 объект из примера 9 может дополнительно содержать то, что упомянутые операции дополнительно включают в себя следующее: направляют в модуль памяти сигнал предоставления прав после направления команды чтения, при этом модуль памяти направляет сигнал идентификатора чтения в ответ на сигнал предоставления прав, при этом смещение чтения измеряет время, когда доставляют данные после направления сигнала предоставления прав.

Пример 18 является устройством, связанным, по меньшей мере, с одним модулем памяти по шине и содержащим: сопряжение с помощью шины, по меньшей мере, для одного модуля памяти; устройство фазовой интерполяции; логическую схему контроллера памяти, которая при работе осуществляет операции грубого обучения чтению, эти операции включают в себя следующее: используют идентификатор чтения, возвращенный из модуля памяти по тракту боковой полосы сопряжения с помощью шины, который не совпадает с сигнальными линиями команд и данных сопряжения с помощью шины, что делают для определения смещения чтения, при котором осуществляют выборку считанных данных по сопряжению с помощью шины; и при использовании смещения чтения для определения, когда начинать выборку данных в окне считанных данных, что осуществляют следующим образом: направляют команду чтения с идентификатором чтения в модуль памяти; принимают принятый идентификатор чтения из модуля памяти по тракту боковой полосы сопряжения с помощью шины; в ответ на определение того, соответствует ли принятый идентификатор чтения идентификатору чтения, направленному с командой чтения: определяют окно данных как то, куда считали принятый идентификатор чтения; и определяют настройку для управления устройством фазовой интерполяции с целью выработки прошедших интерполяцию сигналов, используемых для выборки данных в определенном окне данных, в котором считан принятый идентификатор чтения.

В примере 19 объект из примера 18 может дополнительно содержать то, что использование идентификатора чтения для определения смещения чтения включает в себя следующее: направляют команду чтения с идентификатором чтения в модуль памяти; принимают считанные данные и принятый идентификатор чтения из модуля памяти по сопряжению с помощью шины, при этом принятый идентификатор чтения принимают по тракту боковой полосы сопряжения с помощью шины; определяют смещение чтения как время, когда принятые считанные данные соответствуют идентификатору чтения, направленному с командой чтения.

В примере 20 объект из примера 18 может дополнительно содержать регистр (LFSR) сдвига с линейной обратной связью, используемый для выработки идентификаторов чтения во время грубого обучения чтению и при использовании смещения чтения для определения того, когда начать выборку данных в окне данных.

Пример 21 является считываемым компьютером носителем, связанным, по меньшей мере, с одним модулем памяти по сопряжению с помощью шины с шиной, при этом считываемый компьютером носитель реализует логику, при выполнении которой осуществляют операции, включающие в себя следующее: программируют модуль памяти с целью запуска режима обучения, в котором модуль памяти передает непрерывные битовые шаблоны по тракту боковой полосы сопряжения с помощью шины; принимают битовые шаблоны по сопряжению с помощью шины; определяют из принятых битовых шаблонов переход значений в битовом шаблоне с целью определить окно данных между определенными переходами значений; и определяют настройку с целью управления устройством фазовой интерполяции для выработки прошедших интерполяцию сигналов, используемых для выборки данных в рамках определенного окна данных.

В примере 22 объект из примера 21 может дополнительно содержать следующее: битовые шаблоны содержат первый непрерывный битовый шаблон по тракту боковой полосы сопряжения с помощью шины, который используют для сигналов идентификатора чтения, и второй непрерывный битовый шаблон по тракту боковой полосы, при этом первый и второй непрерывные битовые шаблоны обладают противоположными значениями.

В примере 23 объект из примера 18 может дополнительно содержать то, что операции дополнительно включают в себя следующее: в ответ на определение настройки для управления устройством фазовой интерполяции, направляют в модуль памяти команду чтения с идентификатором чтения; принимают считанные данные из модуля памяти, в том числе возвращенный идентификатор чтения; и определяют смещение чтения в ответ на определение того, что возвращенный, идентификатор чтения соответствует идентификатору чтения, направленному с командой чтения, при этом смещение чтения используют для определения того, когда начинать выборку считанных данных в окне данных с использованием определенной настройки для устройства фазовой интерполяции.

Пример 24 является считываемым компьютером носителем, связанным, по меньшей мере, с одним модулем памяти по сопряжению с помощью шины с шиной, при этом считываемый компьютером носитель реализует логику, при выполнении которой осуществляют операции, включающие в себя следующее: направляют в модуль памяти команду чтения и идентификатор чтения; принимают из модуля памяти по сопряжению с помощью шины считанные данные и принятый идентификатор чтения; и определяют смещение чтения в ответ на определение того, что принятый идентификатор чтения от модуля памяти включает в себя идентификатор чтения, направленный с командой чтения, при этом смещение чтения используют для определения того, когда начать выборку данных в окне принятых считанных данных.

В примере 25 объект из примера 24 может дополнительно содержать то, что операции дополнительно включают в себя следующее: в ответ на определение того, что принятый идентификатор чтения не соответствует идентификатору чтения, направленному с командой чтения, осуществляют, по меньшей мере, одну итерацию выработки нового идентификатора чтения для включения его в новую команду чтения, направляемую в модуль памяти, что делают до определения смещения чтения в ответ на принятые из модуля памяти считанные данные, содержащие выработанный новый идентификатор чтения.

Пример 26 является способом обучения устройства сопряжения с шиной, связанной, по меньшей мере, с одним модулем памяти по сопряжению с помощью шины и содержащим следующее: программируют модуль памяти с целью запуска режима обучения, в котором модуль памяти передает непрерывные битовые шаблоны по тракту боковой полосы сопряжения с помощью шины; принимают битовые шаблоны по сопряжению с помощью шины; определяют из принятых битовых шаблонов переход значений в битовом шаблоне с целью определить окно данных между определенными переходами значений; и определяют настройку с целью управления устройством фазовой интерполяции для выработки прошедших интерполяцию сигналов, используемых для выборки данных в рамках определенного окна данных.

В примере 27 объект из примера 26 может дополнительно содержать следующее: битовые шаблоны содержат первый непрерывный битовый шаблон по тракту боковой полосы сопряжения с помощью шины, используемый для сигналов идентификатора чтения, и второй непрерывный битовый шаблон по тракту боковой полосы, при этом первый и второй непрерывные битовые шаблоны обладают противоположными значениями.

В примере 28 объект из примеров 26 и 27 может дополнительно содержать следующее: считываемый компьютером носитель содержит код, при выполнении которого машина осуществляет способ из любого примера 26 или 27.

Пример 29 является способом обучения устройства сопряжения с шиной, связанной, по меньшей мере, с одним модулем памяти по сопряжению с помощью шины и содержащим следующее: направляют в модуль памяти команду чтения и идентификатор чтения; принимают из модуля памяти по сопряжению с помощью шины считанные данные и принятый идентификатор чтения; и определяют смещение чтения в ответ на определение того, что принятый идентификатора чтения от модуля памяти включает в себя идентификатор чтения, направленный с командой чтения, при этом смещение чтения используют для определения того, когда начать выборку данных в окне принятых считанных данных.

В примере 30 объект из примера 29 может дополнительно содержать то, что операции дополнительно включают в себя следующее: в ответ на определение того, что принятый идентификатор чтения не соответствует идентификатору чтения, направленному с командой чтения, осуществляют, по меньшей мере, одну итерацию выработки нового идентификатора чтения для включения его в новую команду чтения, направляемую в модуль памяти, что делают до определения смещения чтения в ответ на принятые из модуля памяти считанные данные, содержащие выработанный новый идентификатор чтения.

Пример 31 является устройством, связанным, по меньшей мере, с одним модулем памяти по шине и содержащим следующее: средство программирования модуля памяти с целью запуска режима обучения, в котором модуль памяти передает непрерывные битовые шаблоны по тракту боковой полосы сопряжения с помощью шины; средство приема битовых шаблонов по сопряжению с помощью шины; средство определения из принятых битовых шаблонов перехода значений в битовом шаблоне с целью определить окно данных между определенными переходами значений; и средством определения настройки с целью управления устройством фазовой интерполяции для выработки прошедших интерполяцию сигналов, используемых для выборки данных в рамках определенного окна данных.

В примере 32, объект из примера 31 может дополнительно содержать средство программирования модуля памяти с целью завершения режима обучения и направления битовых шаблонов в ответ на определение окна данных и настройки с целью управления устройством фазовой интерполяции.

В примере 33, объект из примера 31 может дополнительно содержать то, что средство определения из принятых битовых шаблонов синхронизации перехода содержит: средство сохранения считанного значения из битового шаблона в регистре; и средство определения, соответствует ли следующее считанное значение из последующей передачи битового шаблона считанному значению в регистре, при этом окно данных определяют между краями двух считанных значений, которые соответствуют значениям, сохраненным в регистре.

В примере 34 объект из примера 31 может дополнительно содержать средство направления команды чтения с идентификатором чтения в модуль памяти в ответ на определение настройки для управления устройством фазовой интерполяции; средство приема считанных данных из модуля памяти, в том числе возвращенный идентификатор чтения; и средство определения смещения чтения в ответ на определение того, что возвращенный идентификатор чтения соответствует идентификатору чтения, направленному с командой чтения, при этом смещение чтения используют Для определения того, когда начинать выборку считанных данных в окне данных с использованием определенной настройки для устройства фазовой интерполяции.

В примере 35 объект из примера 34 может дополнительно содержать средство осуществления, по меньшей мере, одной итерации выработки нового идентификатора чтения для включения его в новую команду чтения, направляемую в модуль памяти, что делают до определения смещения чтения в ответ на принятые из модуля памяти считанные данные, содержащие выработанный новый идентификатор чтения, в ответ на определение того, что принятый идентификатор чтения не соответствует идентификатору чтения, направленному с командой чтения.

В примере 36 объект из примера 31 может дополнительно содержать средство использования идентификатора чтения, возвращенного из модуля памяти по тракту боковой полосы сопряжения с помощью шины, который не совпадает с сигнальными линиями команд и данных из сопряжения с помощью шины, что делают для определения смещения чтения, при котором осуществляют выборку считанных данных по сопряжению с помощью шины; и средство использования смещения чтения для определения, когда начинать выборку данных в окне данных из считанных данных, что осуществляют следующим образом: направляют команду чтения с идентификатором чтения в модуль памяти; принимают принятый идентификатор чтения из модуля памяти по тракту боковой полосы сопряжения с помощью шины; в ответ на определение, соответствует ли принятый идентификатор чтения идентификатору чтения, направленному с командой чтения: определяют окно данных как то, куда считали принятый идентификатор чтения; и определяют настройку для управления устройством фазовой интерполяции с целью выработки прошедших интерполяцию сигналов, используемых для выборки данных в определенном окне данных, в котором считан принятый идентификатор чтения.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЧУВСТВИТЕЛЬНЫЙ К ЗАДЕРЖКЕ БУФЕР ТРАНЗАКЦИИ ДЛЯ СВЯЗИ С КВИТИРОВАНИЕМ | 2014 |

|

RU2598594C2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ДАННЫХ С ВОЗМОЖНОСТЬЮ ОСУЩЕСТВЛЕНИЯ ВЗАИМОДЕЙСТВИЯ С OpenFlow КОНТРОЛЛЕРОМ | 2014 |

|

RU2584471C1 |

| УСТРОЙСТВО И СПОСОБ РЕАЛИЗАЦИИ ИНТЕРФЕЙСА ВЫСОКОСКОРОСТНОЙ ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2353066C2 |

| УСТРОЙСТВО, СИСТЕМА И СПОСОБ УЛУЧШЕНИЯ КОРРЕКЦИИ ЗАДАВАЕМЫМ АППАРАТУРОЙ АЛГОРИТМОМ | 2014 |

|

RU2580404C2 |

| ФИЗИЧЕСКИЙ УРОВЕНЬ ВЫСОКОПРОИЗВОДИТЕЛЬНОГО МЕЖСОЕДИНЕНИЯ | 2013 |

|

RU2579140C1 |

| ФИЗИЧЕСКИЙ УРОВЕНЬ ВЫСОКОПРОИЗВОДИТЕЛЬНОГО МЕЖСОЕДИНЕНИЯ | 2013 |

|

RU2599971C2 |

| ЗВЕНО СВЯЗИ МНОГОКРИСТАЛЬНОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ | 2013 |

|

RU2656732C2 |

| ИНТЕРФЕЙС С ВЫСОКОЙ СКОРОСТЬЮ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2371872C2 |

| СПОСОБ УПРАВЛЕНИЯ ДИАЛОГОМ И СИСТЕМА ПОНИМАНИЯ ЕСТЕСТВЕННОГО ЯЗЫКА В ПЛАТФОРМЕ ВИРТУАЛЬНЫХ АССИСТЕНТОВ | 2020 |

|

RU2759090C1 |

| СПОСОБ И УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ И СПОСОБ И УСТРОЙСТВО ОТПРАВКИ ДАННЫХ | 2019 |

|

RU2787887C2 |

Группа изобретений относится к вычислительной технике и может быть использована для обучения чтению контроллера памяти. Техническим результатом является повышение эффективности обучения чтению. Устройство содержит устройство сопряжения шины, по меньшей мере, с одним модулем памяти; логическую схему контроллера памяти, которая при работе выполнена с возможностью осуществления операций, причем операции включают в себя программирование модуля памяти для запуска режима обучения, в котором модуль памяти передает непрерывные битовые шаблоны по тракту боковой полосы устройства сопряжения шины; прием битовых шаблонов по устройству сопряжения шины; определение из принятых битовых шаблонов перехода значений в битовом шаблоне для определения окна данных между определенными переходами значений; и определение настройки для управления устройством фазовой интерполяции для выработки прошедших интерполяцию сигналов, используемых для выборки данных в пределах определенного окна данных. 3 н. и 17 з.п. ф-лы, 6 ил.

1. Устройство для обучения чтению контроллера памяти, содержащее:

устройство сопряжения шины по меньшей мере с одним модулем памяти;

логическую схему контроллера памяти, которая при работе выполнена с возможностью осуществления операций, причем операции включают в себя:

программирование модуля памяти для запуска режима обучения, в котором модуль памяти передает непрерывные битовые шаблоны по тракту боковой полосы устройства сопряжения шины;

прием битовых шаблонов по устройству сопряжения шины;

определение из принятых битовых шаблонов перехода значений в битовом шаблоне для определения окна данных между определенными переходами значений; и

определение настройки для управления устройством фазовой интерполяции для выработки прошедших интерполяцию сигналов, используемых для выборки данных в пределах определенного окна данных.

2. Устройство по п. 1, в котором операции дополнительно включают в себя программирование модуля памяти для завершения режима обучения и отправки упомянутых битовых шаблонов в ответ на определение окна данных и упомянутой настройки для управления устройством фазовой интерполяции.

3. Устройство по п. 1, в котором определение перехода из принятых тактовых битовых шаблонов включает в себя:

сохранение считанного значения из битового шаблона в регистре; и

определение, соответствует ли следующее считанное значение из последующей передачи битового шаблона считанному значению в регистре, при этом окно данных определяют между краями двух считанных значений, которые соответствуют значениям, сохраненным в регистре.

4. Устройство по п. 1, в котором битовые шаблоны содержат первый непрерывный битовый шаблон по тракту боковой полосы устройства сопряжения шины, используемый для сигналов идентификатора чтения, и второй непрерывный битовый шаблон по тракту боковой полосы, при этом первый и второй непрерывные битовые шаблоны обладают противоположными значениями.

5. Устройство по п. 4, в котором первый непрерывный битовый шаблон отправляется по первой сигнальной линии идентификатора чтения и содержит непрерывный шаблон 1010, а второй непрерывный битовый шаблон отправляется по второй сигнальной линии идентификатора чтения и содержит непрерывный шаблон 0101.

6. Устройство по п. 5, в котором первый и второй непрерывные битовые шаблоны чередуются между 0 и 1 каждый тактовый интервал для создания тактового шаблона с периодом, в два раза большим периода тактового интервала устройства сопряжения шины.

7. Устройство по п. 1, в котором устройство сопряжения шины включает в себя командные линии, по которым передаются команды, линии данных, по которым передаются данные, и сигнальные линии идентификатора чтения, при этом битовые шаблоны передаются по сигнальным линиям идентификатора чтения на частоте команд, меньшей тактовой частоты.

8. Устройство по п. 1, в котором операции дополнительно включают в себя:

отправку, в ответ на определение настройки для управления устройством фазовой интерполяции, команды чтения с идентификатором чтения в модуль памяти;

прием считанных данных из модуля памяти, в том числе возвращенного идентификатора чтения; и

определение смещения чтения в ответ на определение, что возвращенный идентификатор чтения соответствует идентификатору чтения, отправленному с командой чтения, при этом смещение чтения используется для определения времени начала выборки считанных данных в окне данных с использованием определенной настройки для устройства фазовой интерполяции.

9. Устройство по п. 8, в котором устройство сопряжения шины включает в себя командные линии, по которым передаются команды, линии данных, по которым передаются данные, и сигнальные линии идентификатора чтения, при этом модуль памяти выполнен с возможностью возврата идентификатора чтения по сигнальным линиям идентификатора чтения.

10. Устройство по п. 9, характеризующееся тем, что выполнено с возможностью возврата идентификатора чтения из модуля памяти на сигналах синхронизации.

11. Устройство для обучения чтению контроллера памяти, содержащее:

устройство сопряжения шины по меньшей мере с одним модулем памяти;

логическую схему контроллера памяти, которая при работе выполнена с возможностью осуществления операций грубого обучения чтению, причем операции включают в себя:

отправку в модуль памяти команды чтения и идентификатора чтения;

прием из модуля памяти по устройству сопряжению шины считанных данных и принятого идентификатора чтения; и

определения смещения чтения в ответ на определение, что принятый идентификатор чтения от модуля памяти включает в себя идентификатор чтения, отправленный с командой чтения, при этом смещение чтения используется для определения времени начала выборки данных в окне данных принятых считанных данных.

12. Устройство по п. 11, в котором операции дополнительно включают в себя осуществление в ответ на определение, что принятый идентификатор чтения не соответствует идентификатору чтения, отправленному с командой чтения, по меньшей мере одной итерации выработки нового идентификатора чтения для включения его в новую команду чтения, отправляемую в модуль памяти, пока не будет определено смещения чтения в ответ на принятые из модуля памяти считанные данные, содержащие выработанный новый идентификатор чтения.

13. Устройство по п. 12, дополнительно содержащее регистр (LFSR) сдвига с линейной обратной связью, используемый для выработки идентификатора чтения и новых идентификаторов чтения для обеспечения случайных значений идентификаторов чтения.

14. Устройство по п. 11, характеризующееся тем, что выполнено с возможностью завершения грубого обучения чтению в ответ на принятый идентификатор чтения, содержащий идентификатор чтения, отправленный с командой чтения.

15. Устройство по п. 11, в котором идентификатор чтения вызывает закольцовывание модулем памяти идентификатора чтения при возврате считанных данных в ответ на команду чтения.

16. Устройство по п. 11, в котором идентификатор чтения передается из модуля памяти по тракту боковой полосы.

17. Устройство по п. 11, в котором операции дополнительно включают в себя отправку в модуль памяти сигнала предоставления прав после отправки команды чтения, при этом модуль памяти выполнен с возможностью отправки сигнала идентификатора чтения в ответ на сигнал предоставления прав, при этом смещение чтения определяется временем поступления данных после отправки сигнала предоставления прав.

18. Устройство для обучения чтению контроллера памяти, содержащее:

устройство сопряжения шины по меньшей мере с одним модулем памяти;

устройство фазовой интерполяции;

логическую схему контроллера памяти, которая при работе выполнена с возможностью осуществления операций грубого обучения чтению, причем операции включают в себя:

использование идентификатора чтения, возвращенного из модуля памяти по тракту боковой полосы устройства сопряжения шины, отдельному от командных линий и линий сигналов данных устройства сопряжения шины, для определения смещения чтения, при котором осуществляется выборка считанных данных устройства сопряжения шины; и

выполнение при использовании смещения чтения для определения времени начала выборки данных в окне данных считанных данных:

отправки команды чтения с идентификатором чтения в модуль памяти;

приема принятого идентификатора чтения из модуля памяти по тракту боковой полосы устройства сопряжения шины;

в ответ на определение, соответствует ли принятый идентификатор чтения идентификатору чтения, отправленному с командой чтения:

определения окна данных в качестве окна данных, в котором считан принятый идентификатор чтения; и

определения настройки для управления устройством фазовой интерполяции для выработки прошедших интерполяцию сигналов, используемых для выборки данных в определенном окне данных, в котором считан принятый идентификатор чтения.

19. Устройство по п. 18, в котором использование идентификатора чтения для определения смещения чтения включает в себя:

отправку команды чтения с идентификатором чтения в модуль памяти;

прием из модуля памяти по устройству сопряжения шины считанных данных и принятого идентификатора чтения, при этом принятый идентификатор чтения принимается по тракту боковой полосы сопряжения с помощью шины;

определение смещение чтения как момента времени, в который принятые считанные данные соответствуют идентификатору чтения, отправленному с командой чтения.

20. Устройство по п. 18, дополнительно содержащее регистр (LFSR) сдвига с линейной обратной связью, используемый для выработки идентификаторов чтения во время грубого обучения чтению и, при использовании смещения чтения, для определения времени начала выборки данных в окне данных.

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| US 7107424 B1, 12.09.2006 | |||

| СПОСОБ И УСТРОЙСТВО ДЛЯ НЕЯВНОЙ ПРЕДВАРИТЕЛЬНОЙ ЗАРЯДКИ ДИНАМИЧЕСКОЙ ОПЕРАТИВНОЙ ПАМЯТИ (DRAM) | 2004 |

|

RU2331118C2 |

Авторы

Даты

2018-02-02—Публикация

2014-07-29—Подача