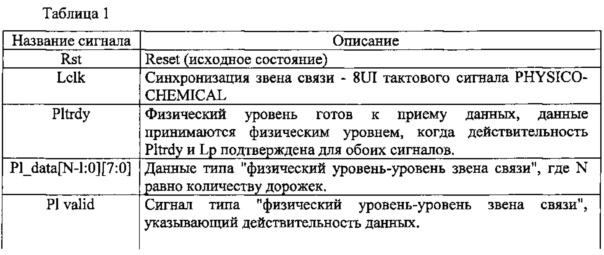

Область техники, к которой относится изобретение

Настоящее раскрытие относится к компьютерной системе и, в частности (но не исключительно), к межсоединениям типа "точка-точка".

Уровень техники

Прогресс в области технологии полупроводников и разработки логических схем позволил увеличить количество логических элементов, которые могут присутствовать в устройствах интегральных схем. Как следствие, конфигурации компьютерных систем прошли эволюцию от одиночных или многочисленных интегральных схем в системе до многоядерного, многоцепочечного аппаратурного обеспечения и многочисленных логических процессоров, присутствующих в индивидуальных интегральных схемах, а также других интерфейсов, интегрированных внутри таких процессоров. Процессор или интегральная схема обычно содержит одиночный кристалл физического процессора, где кристалл процессора может содержать множество ядер, цепочек аппаратурного обеспечения, логических процессоров, интерфейсов, памяти, концентраторов контроллеров и т.д.

В результате повышения возможности размещения большей вычислительной мощности в меньших корпусах интегральных схем, возросла популярность малогабаритных компьютерных устройств. Количество смартфонов, планшетов, ультратонких ноутбуков и другого оборудования пользователя возросло экспоненциально. Однако, такие более малогабаритные устройства опираются на серверы как для хранения данных, так и для сложной обработки, которая превышает форм-фактор. Следовательно, спрос на компьютерном рынке на высокопроизводительные устройства (то есть, на серверное пространство) также вырос. Например, в модемных серверах обычно существует не только одиночный процессор с множеством ядер, но также и многочисленные физические процессоры (также упоминаемые как многочисленные сокеты), чтобы повысить вычислительную мощность. Но поскольку вычислительная мощность растет вместе с ростом количества устройств в компьютерной системе, связь между сокетами и другими устройствами становится более критичной.

Фактически, межсоединения выросли из более традиционных многоточечных шин, которые имеют дело прежде всего с электрическими соединениям, чтобы полностью развивать архитектуры межсоединений, облегчающих быстрое соединение. К сожалению, поскольку потребность в будущих процессорах растет с более высокими скоростями, соответствующие потребности накладываются на возможности существующих архитектур межсоединений.

Краткое описание чертежей

Фиг. 1 - вариант осуществления компьютерной системы, содержащей архитектуру межсоединений.

Фиг. 2 - вариант осуществления архитектуры межсоединений, содержащей многоуровневый набор.

Фиг. 3 - вариант осуществления запроса или пакета, который должен формироваться или приниматься в рамках архитектуры межсоединений.

Фиг. 4 - вариант осуществления пары передатчика и приемника для архитектуры межсоединений.

Фиг. 5 - вариант осуществления многокристального корпуса интегральной схемы.

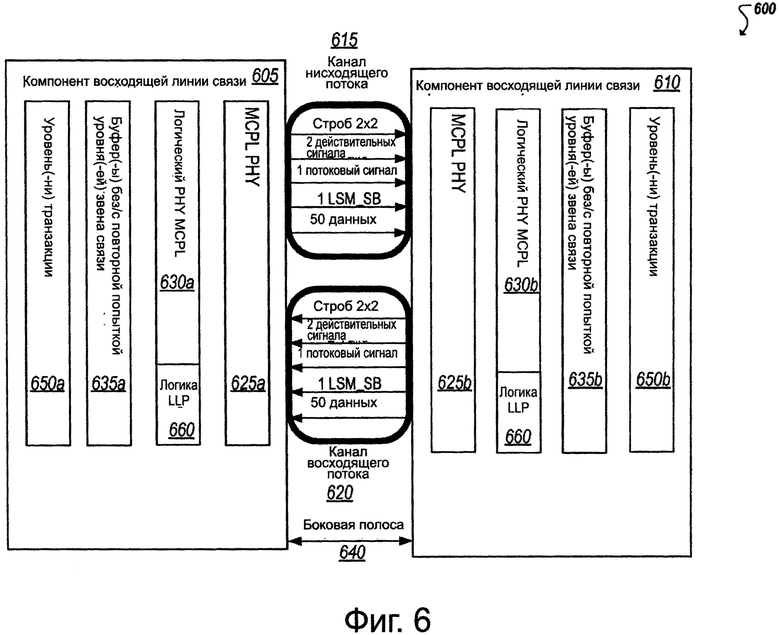

Фиг. 6 - упрощенная блок-схема звена связи многокристального корпуса интегральной схемы (MCPL).

Фиг. 7 - пример сигнализации в примерной MCPL.

Фиг. 8 - упрощенная блок-схема дорожки для передачи данных в примерной MCPL.

Фиг. 9 - упрощенная блок-схема примерных технологий подавления перекрестных помех в варианте осуществления MCPL.

Фиг. 10 - упрощенная схема примерных компонент подавления перекрестных помех в варианте осуществления MCPL.

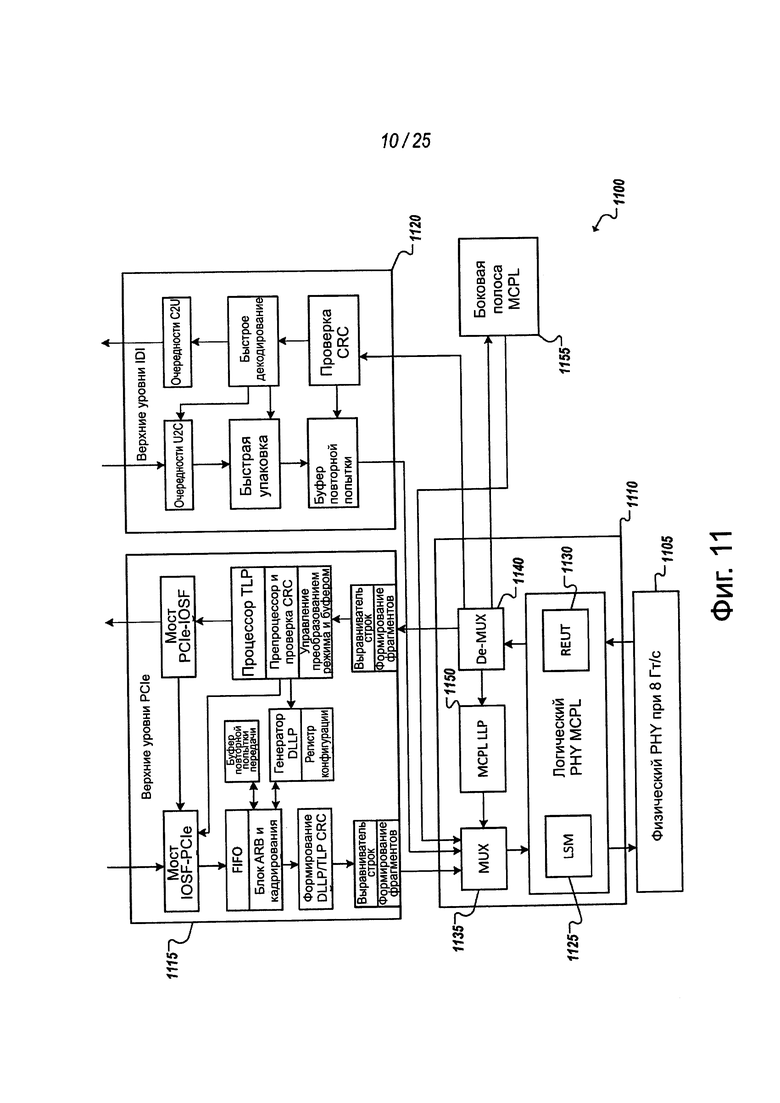

Фиг. 11 - упрощенная блок-схема MCPL.

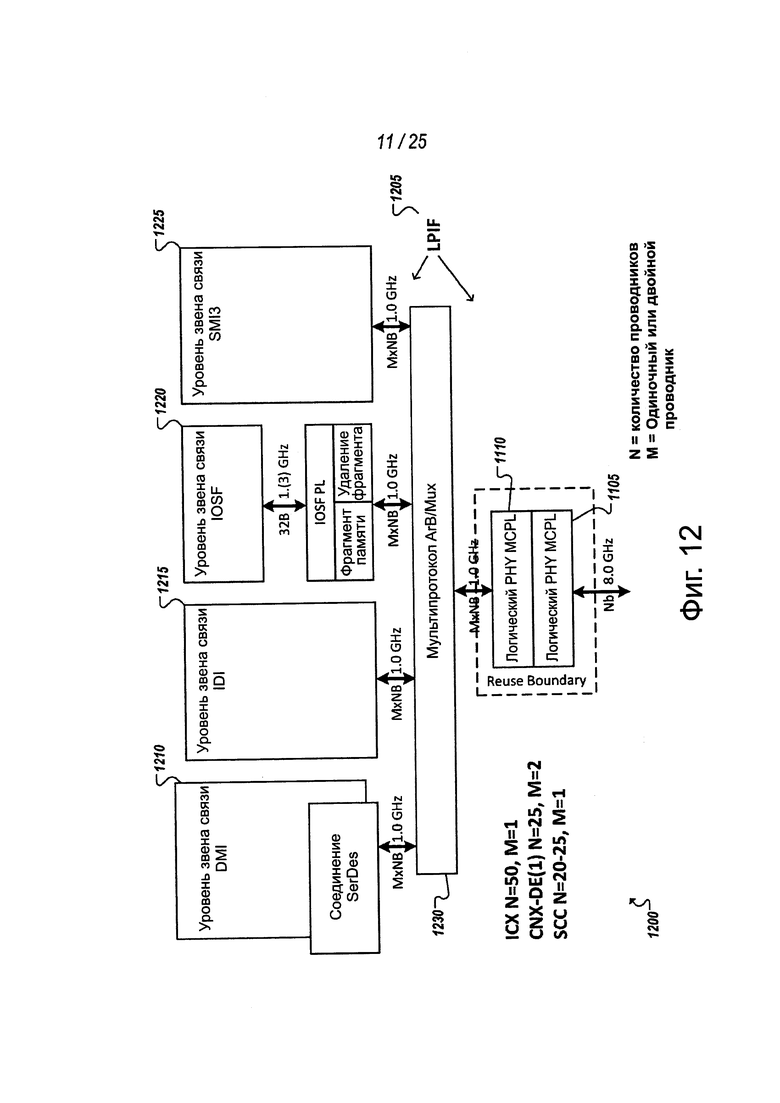

Фиг. 12 - упрощенная блок-схема MCPL, взаимодействующей с логикой верхнего уровня по многочисленным протоколам, использующим логический интерфейс PHY (LPIF).

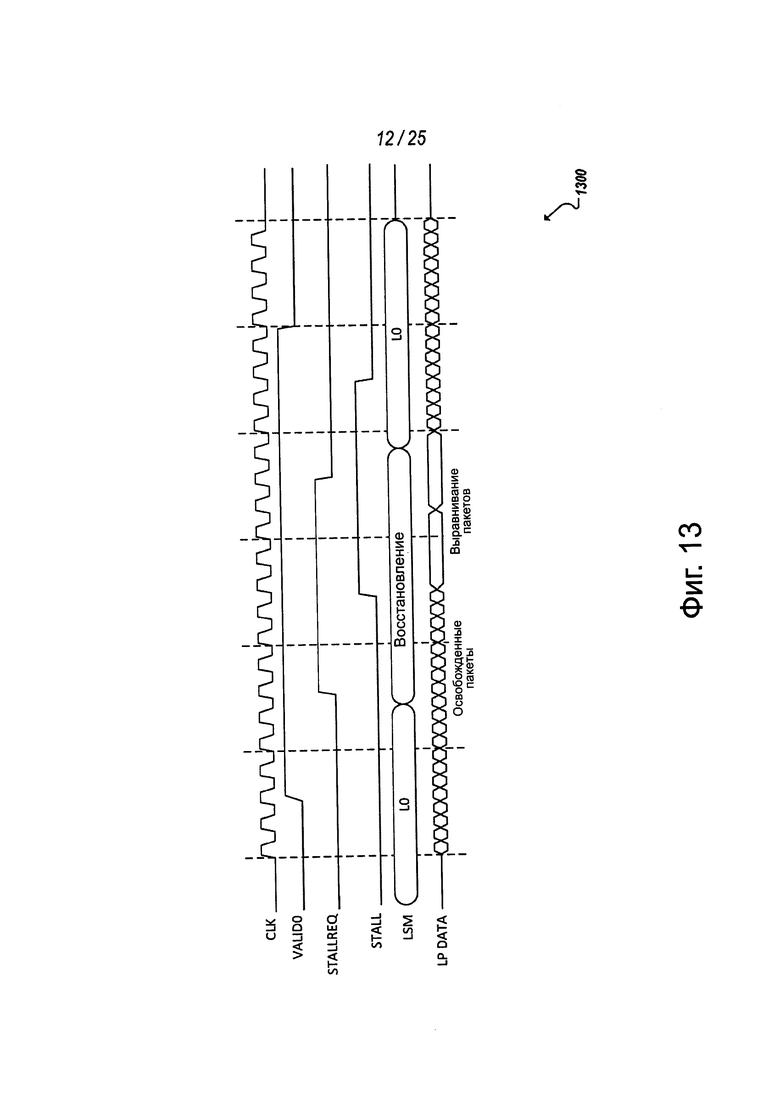

Фиг. 13 - пример сигнализации примерной MCPL в сочетании с восстановлением звена связи.

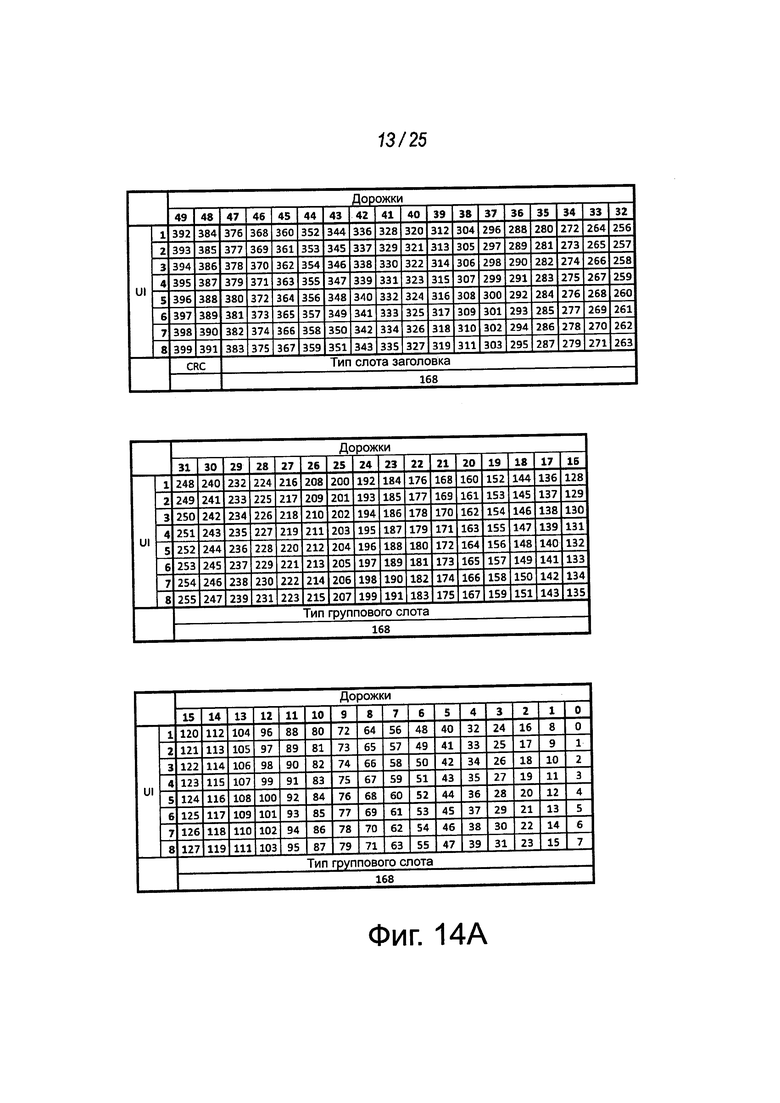

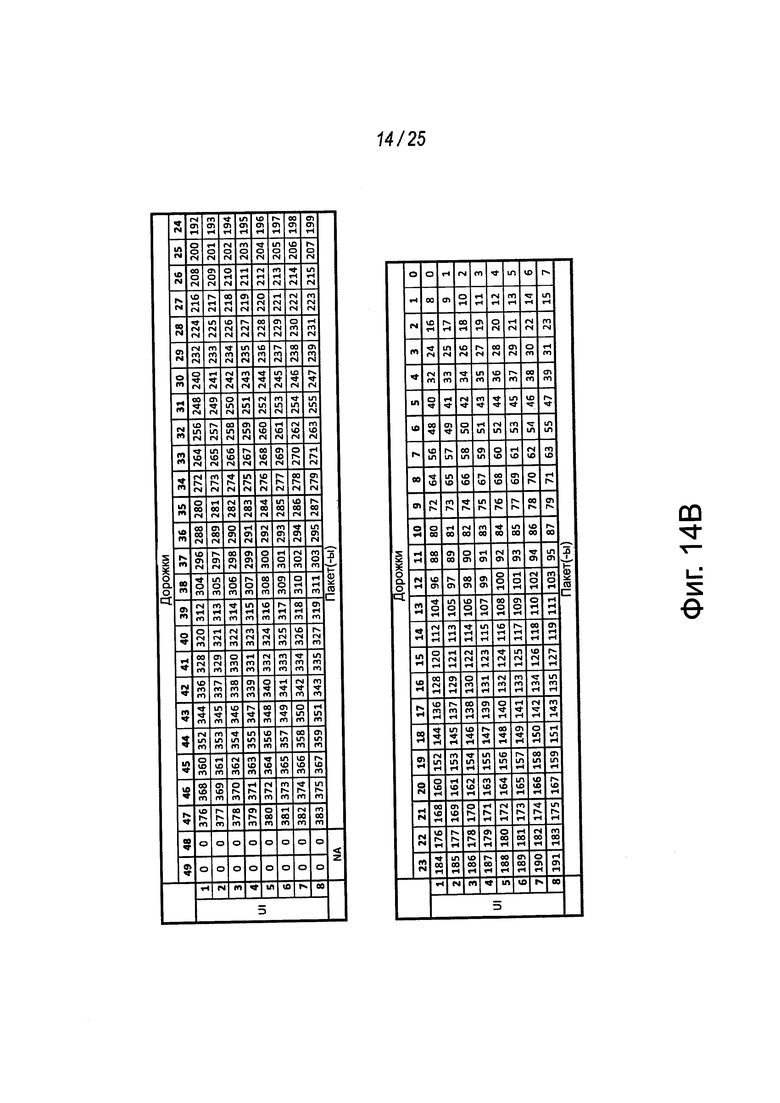

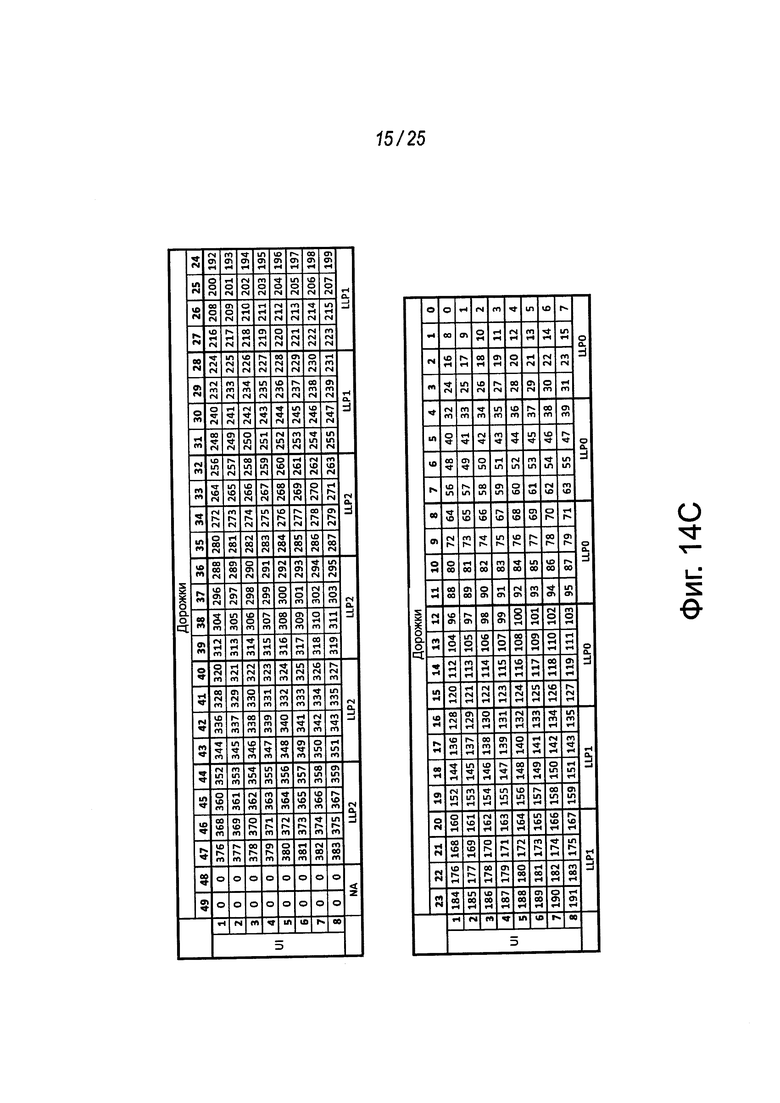

Фиг. 14А-14С - примерные битовые отображения данных на дорожках примерной MCPL.

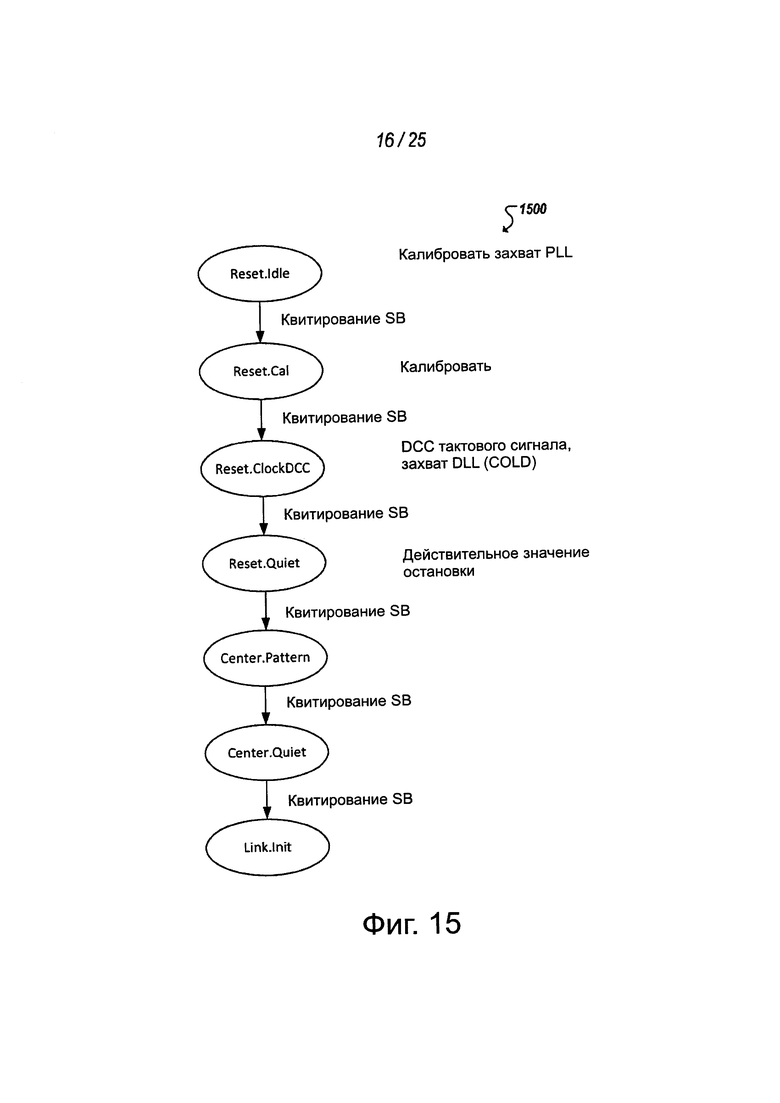

Фиг. 15 - участок примерного конечного автомата звена связи.

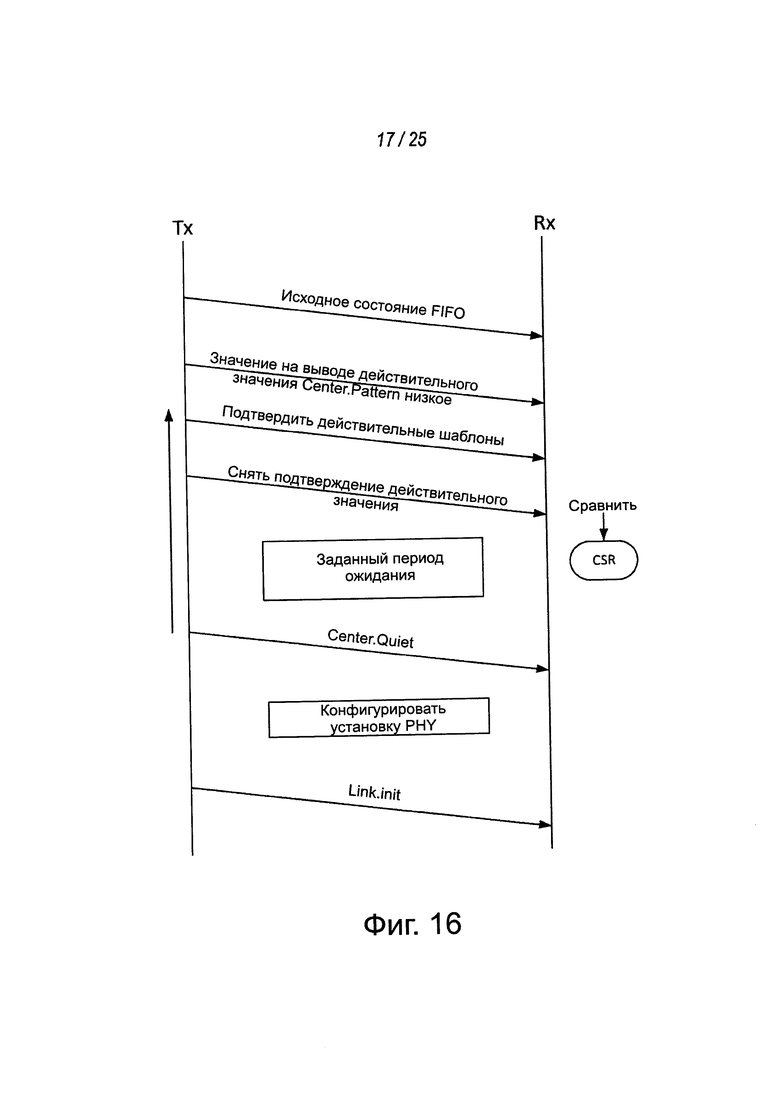

Фиг. 16 - поток, связанный с примерной центровкой звена связи.

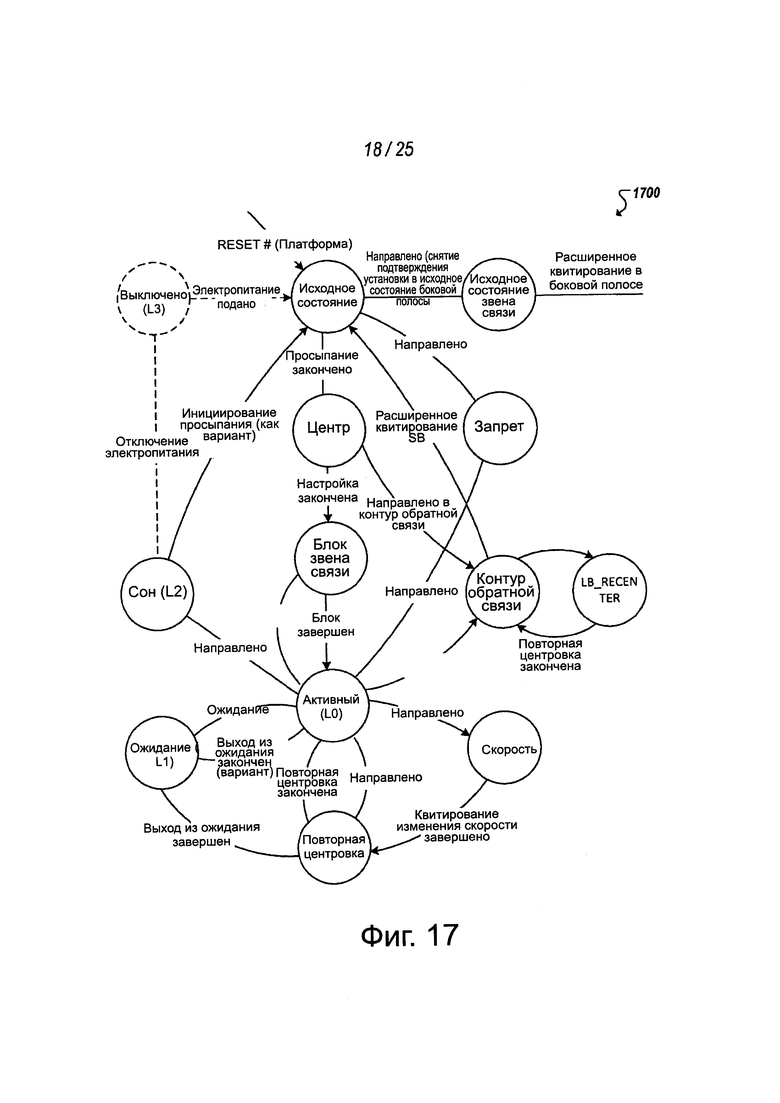

Фиг. 17 - примерный конечный автомат звена связи.

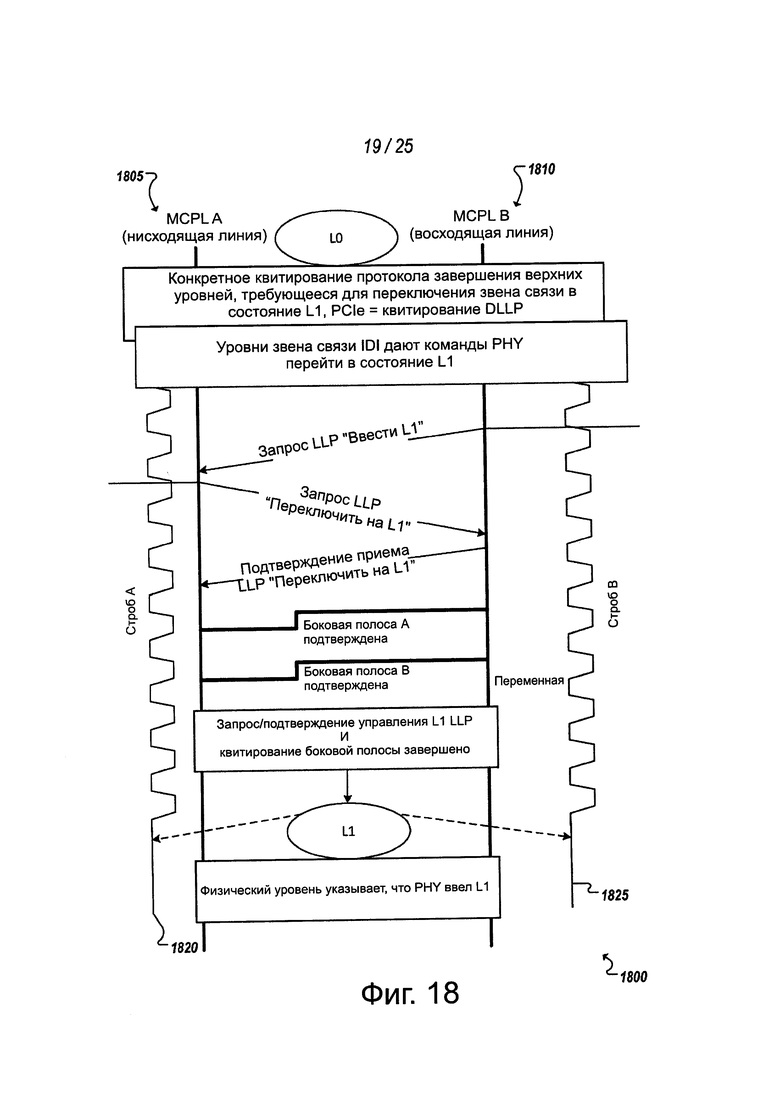

Фиг. 18 - сигнализация для ввода состояния низкого энергопотребления.

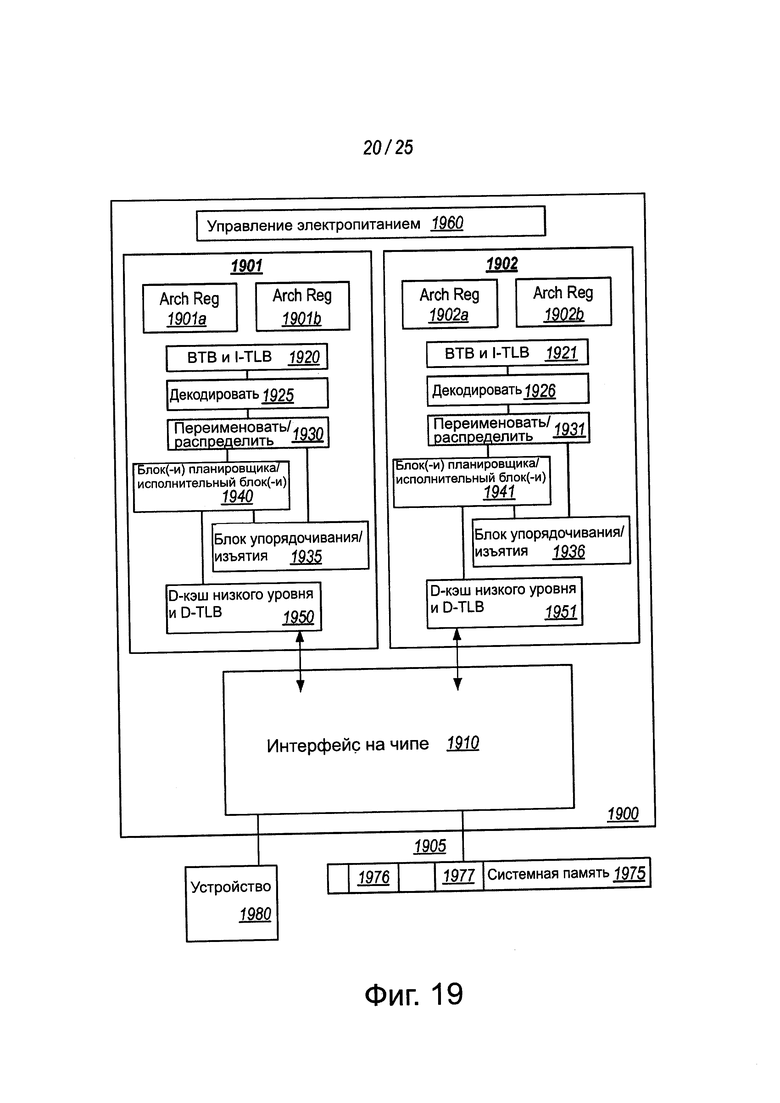

Фиг. 19 - вариант осуществления блок-схемы компьютерной системы, содержащей многоядерный процессор.

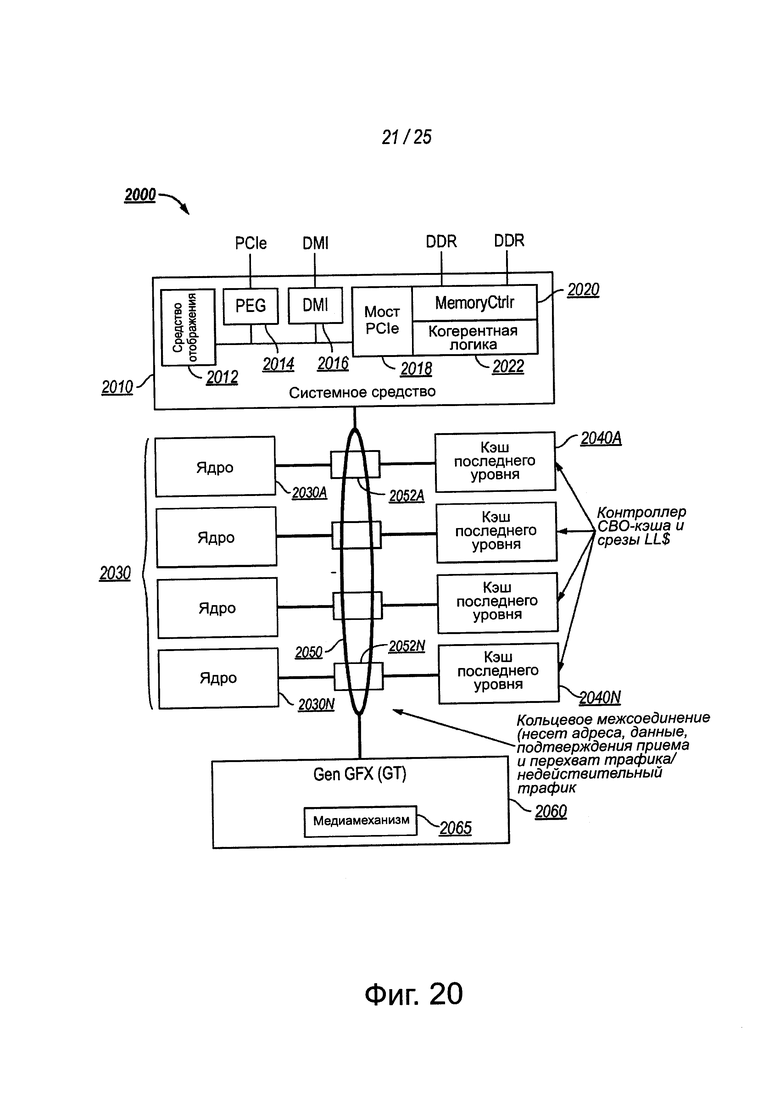

Фиг. 20 - другой вариант осуществления блок-схемы компьютерной системы, содержащей многоядерный процессор.

Фиг. 21 - вариант осуществления блок-схемы процессора.

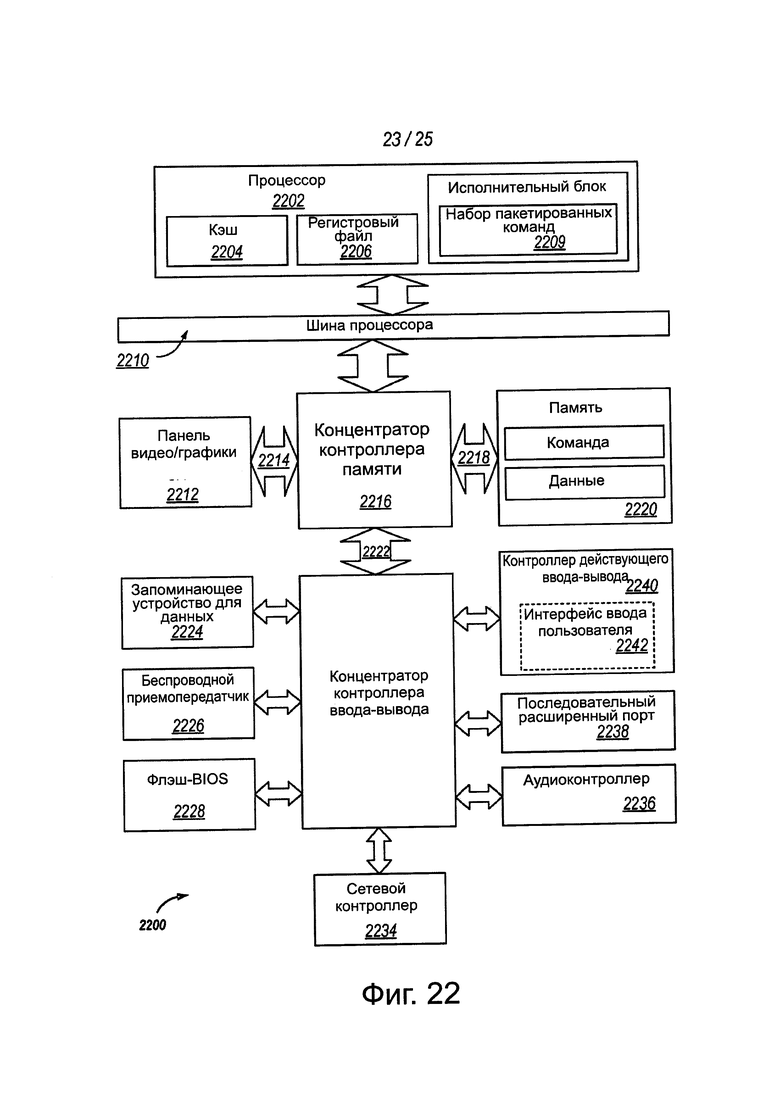

Фиг. 22 - другой вариант осуществления блок-схемы компьютерной системы, содержащей процессор.

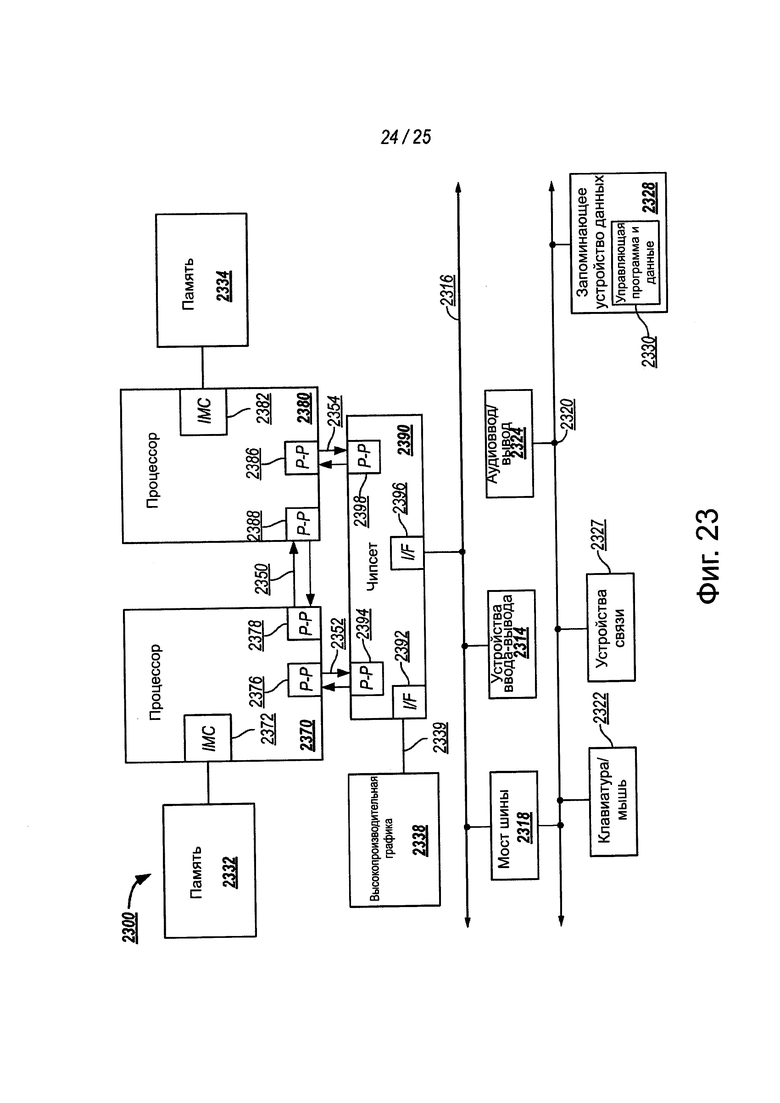

Фиг. 23 - вариант осуществления блока компьютерной системы, содержащей многочисленные процессоры.

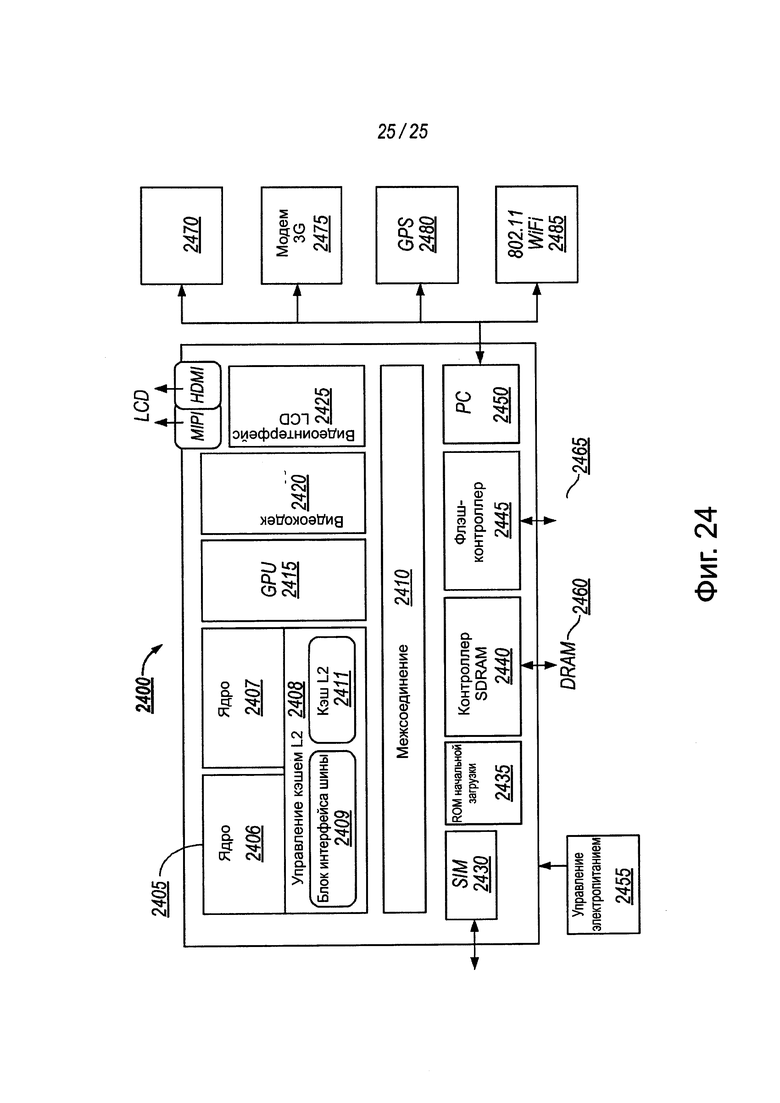

Фиг. 24 - примерная система, реализуемая как система на чипе (SoC).

Схожие ссылочные номера и обозначения на различных чертежах указывают схожие элементы.

Подробное описание

В последующем описании излагаются многочисленные конкретные подробности, такие как примеры конкретных типов процессоров и системных конфигураций, конкретного аппаратурного обеспечения, конкретных архитектурных и микроархитектурных подробностей, конкретных конфигураций регистров, конкретных типов команд, конкретных системных компонент, конкретных результатов измерений/максимумов, конкретных стадий и работы процессорного конвейера и т.д., чтобы обеспечить полное понимание настоящего изобретения. Специалистам в данной области техники должно быть, однако, очевидным, что эти конкретные подробности нет необходимости использовать для практической реализации настоящего изобретения. В других случаях, известные компоненты или способы, такие как конкретные и альтернативные архитектуры процессоров, конкретные логические схемы/управляющие программы для описанных алгоритмов, конкретная встроенная управляющая программа, конкретная взаимосвязанная операция, конкретные логические конфигурации, конкретные производственные технологии и материалы, конкретные реализации компиляторов, конкретное выражение алгоритмов в управляющей программе, конкретные технологии/логика отключения электропитания и стробирования и другие конкретные операционные подробности компьютерной системы не были описаны подробно, чтобы избежать излишнего запутывания настоящего изобретения.

Хотя последующие варианты осуществления могут быть описаны со ссылкой на энергосбережение и эффективность использования энергии в конкретных интегральных схемах, таких как компьютерные платформы или микропроцессоры, к другим типам интегральных схем и логических устройств применимы другие варианты осуществления. Схожие технологии и принципы вариантов осуществления, описанные здесь, могут быть применены к другим типам схем или полупроводниковых устройств, которые также могут извлечь выгоду из улучшенного использования энергии и энергосбережения. Например, раскрытые варианты осуществления не ограничиваются настольными компьютерными системами или Ultrabooks™. Они могут также использоваться в других устройствах, таких как карманные устройства, планшеты, другие тонкие ноутбуки, устройства с системами на чипе (SOC) и встраиваемые применения. К некоторым примерам карманных устройств относятся сотовые телефоны, устройства, работающие по интернет-протоколу, цифровые фотоаппараты, персональные цифровые секретари (PDA) и карманные персональные компьютеры. Встраиваемые применения обычно содержат микроконтроллер, цифровой сигнальный процессор (DSP), систему на чипе, сетевые компьютеры (NetPC), цифровые приемники, сетевые концентраторы, переключатели глобальной сети (WAN) или любую другую систему, способную выполнять представленные ниже функции и операции. Кроме того, описанные здесь устройство, способы, и системы не ограничивается физическими компьютерными устройствами, а могут также относиться к оптимизации программного обеспечения для энергосбережения и эффективности использования электропитания. Как станет совершенно очевидным в приведенном ниже описании, описанные здесь варианты осуществления способов, устройств и систем (неважно, со ссылкой на аппаратурные средства, встроенное программное обеспечение, программное обеспечение или их комбинации), являются жизненно важными для будущей "зеленой технологии", сбалансированной с требуемыми рабочими характеристиками.

По мере прогресса компьютерных систем, содержащиеся в них компоненты становятся все более сложными. В результате сложность архитектуры межсоединений и связей между компонентами также возрастает, чтобы обеспечить удовлетворение требований к ширине полосы для оптимальной работы составляющих компонент. Дополнительно, различные сегменты рынка требуют различных вариантов архитектур межсоединений для удовлетворения потребностей рынка. Например, серверы требуют более высокопроизводительных рабочих характеристик, тогда как мобильная экосистема иногда способна пожертвовать общей производительностью в целях экономии электропитания. К тому же, единственной целью большинства связных структур является обеспечение максимально возможных рабочих характеристик при максимальной экономии потребляемой мощности. Ниже обсуждается множество межсоединений, которые потенциально могут извлечь выгоду из описанных здесь вариантов изобретения.

Одна из связных архитектур межсоединений содержит экспресс-архитектуру межсоединений периферийных компонент (Peripheral Component Interconnect (PCI) Express (PCIe)). Первичная цель PCIe состоит в том, чтобы позволить компонентам и устройствам, получаемым от различных поставщиков, взаимодействовать в открытой архитектуре, перекрывая многочисленные сегменты рынка: клиенты (настольные и мобильные компьютеры), серверы (стандартные и внутренние предприятий) и встроенные устройства и устройства связи. PCI Express является высокопроизводительным межсоединением ввода-вывода общего назначения, предназначенным для широкого разнообразия будущих компьютерных и связных платформ. Некоторые атрибуты PCI, такие как модель использования, архитектура загрузки и хранения и интерфейсы программного обеспечения поддерживались во всех версиях, хотя предшествующие реализации с параллельной шиной были заменены хорошо масштабируемым, полностью последовательным интерфейсом. Более свежие версии PCI Express обладают преимуществом перспективы для соединений "точка-точка", технологии на основе переключений и пакетированного протокола, чтобы предоставить новые уровни рабочих характеристик и функций. Управление электропитанием, Power Management (управление электропитанием), Quality Of Service (QoS) (качество обслуживания), поддержка Hot-Plug/Hot-Swap ("горячего" подключения/"горячей" замены), Data Integrity (целостность данных) и Error Handling (обработка ошибок) являются лишь некоторыми из перспективных функций, поддерживаемых PCI Express.

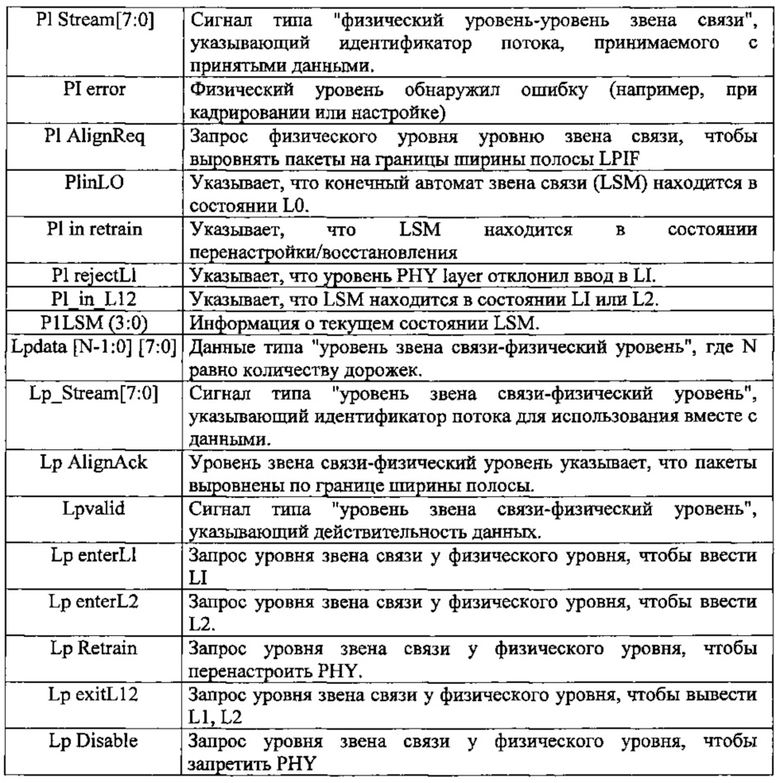

На фиг. 1 показан вариант осуществления связной структуры, состоящей из звеньев связи "точка-точка", которые связывают между собой набор компонент. Система 100 содержит процессор 105 и системную память 110, связанные с концентратором 115 контроллера. Процессор 105 содержит любой элемент обработки, такой как микропроцессор, ведущий процессор, встроенный процессор, сопроцессор или другой процессор. Процессор 105 соединяется с концентратором 115 контроллера через шину внешнего интерфейса (FSB) 106. В одном из вариантов осуществления FSB 106 является последовательным межсоединением "точка-точка", как описано ниже. В другом варианте осуществления, линия 106 звена связи содержит архитектуру последовательных дифференциальных межсоединений, совместимую с различными стандартами межсоединений.

Системная память 110 содержит любое устройство памяти, такое как оперативная память (RAM), энергонезависимая память (NV) или другая память, доступная устройствам в системе 100. Системная память 110 соединяется с концентратором 115 контроллера через интерфейс 116 памяти. Примерами интерфейса памяти являются интерфейс памяти с двойной скоростью передачи данных (DDR), двухканальный интерфейс памяти DDR и интерфейс динамической памяти RAM (DRAM).

В одном из вариантов осуществления концентратор 115 контроллера является корневым концентратором, корневым комплексом или корневым контроллером в иерархии межсоединений для экспресс-межсоединений периферийных компонент (PCIe или PCIE). Примерами концентратора 115 контроллера являются чипсет, концентратор контроллера памяти (МСН), северный мост, концентратор контроллера межсоединений (ICH), южный мост и корневой контроллер/концентратор. Часто термин "чипсет" относится к двум физически раздельным концентраторам контроллеров, то есть, к концентратору контроллера памяти (МСН), связанному с концентратором контроллера межсоединений (ICH). Заметим, что существующие системы часто содержат МСН, интегрированный с процессором 105, тогда как контроллер 115 должен осуществлять связь с устройствами ввода-вывода способом, подобным описанному ниже. В некоторых вариантах осуществления, как вариант, дополнительно поддерживается одноранговая маршрутизация через корневой комплекс 115.

Здесь концентратор 115 контроллера связывается с переключателем/мостом 120 через последовательное звено 119 связи. Модули 117 и 121 ввода-вывода, которые могут также упоминаться как интерфейсы/порты 117 и 121, содержат/осуществляют стек многоуровневого протокола, чтобы обеспечивать передачу между концентратором контроллера 115 и переключателем 120. В одном из вариантов осуществления с переключателем 120 способны связываться многочисленные устройства.

Переключатель/мост 120 маршрутизирует пакеты/сообщения от устройства 125 по восходящий линии, то есть, вверх по иерархии в направлении корневого комплекса к концентратору 115 контроллера, и по нисходящей линии, то есть, вниз по иерархии в направлении от корневого контроллера корня, от процессора 105 или системной памяти 110 к устройству 125. Выключатель 120 в одном из вариантов осуществления относится к логической сборке многочисленных виртуальных устройств мостов типа "от PCI к PCI". Устройство 125 содержит любое внутреннее или внешнее устройство или компонент, которые должны связываться с электронной системой, такой как устройство ввода-вывода, контроллер сетевого интерфейса (NIC), расширительная плата, аудиопроцессор, сетевой процессор, жесткий диск, запоминающее устройство, ROM на CD/DVD, монитор, принтер, "мышь", клавиатура, маршрутизатор, мобильное запоминающее устройство, устройство Firewire, устройство универсальной последовательной шины (USB), сканер и другие устройства ввода-вывода. Часто на жаргоне PCIe устройство упоминается как конечная точка. Хотя это специально не показано, устройство 125 может содержать PCIe к мосту PCI/PCI-X, чтобы поддерживать устройства PCI действующей или другой версии. Устройства конечной точки в PCIe часто классифицируются как действующие, PCIe или интегрированные конечные точки корневого комплекса.

Графический ускоритель 130 также связывается с концентратором 115 контроллера через последовательную линию 132 связи. В одном из вариантов осуществления графический ускоритель 130 связывается с МСН, который связывается с ICH. Переключатель 120 и, соответственно, устройство 125 ввода-вывода затем связывается с ICH. Модули 131 и 118 ввода-вывода должны также реализовывать стек многоуровневого протокола, чтобы осуществлять связь между графическим ускорителем 130 и концентратором 115 контроллера. Подобно МСН, обсуждавшемуся выше, графический контроллер или графический ускоритель 130 сам по себе может интегрироваться в процессор 105.

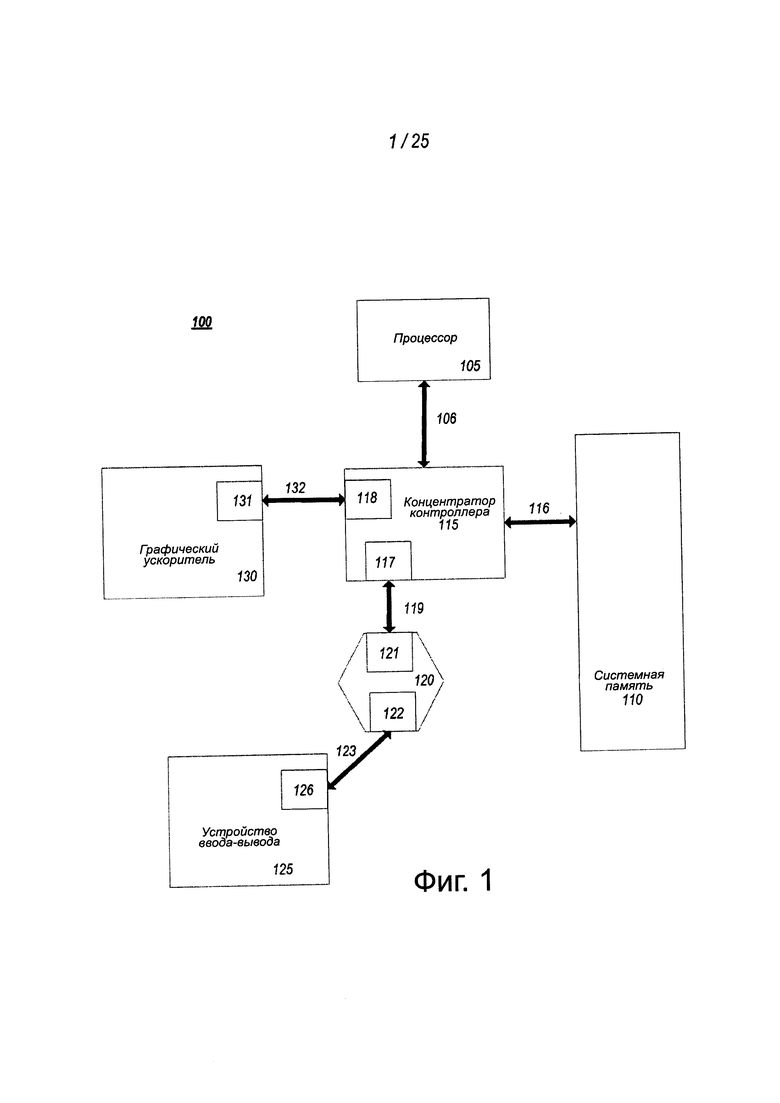

На фиг. 2 показан вариант осуществления стека многоуровневого протокола. Стек 200 многоуровневого протокола содержит любую форму стека многоуровневой связи, такую как стек Quick Path Interconnect (QPI), стек PCIe, стек высокопроизводительных компьютерных межсоединений или другой многоуровневый стек. Хотя обсуждение далее на фиг. 1-4 делает ссылку только на стек PCIe, те же самые концепции могут быть применены к другим стекам межсоединений. В одном из вариантов осуществления стек 200 является стеком протокола PCIe, содержащим уровень 205 транзакции, уровень 210 звена связи для передачи данных и физический уровень 220. Интерфейс, такой как интерфейс 117, 118, 121, 122, 126 и 131 на фиг. 1, может быть представлен как стек 200 протокола связи. Представление в виде стека протокола связи может также упоминаться как модуль или интерфейс, осуществляющий/содержащий стек протокола.

PCI Express использует пакеты для передачи информации между компонентами. Пакеты формируются на уровне 205 транзакции и на уровне 210 звена передачи данных, чтобы переносить информацию от передающего компонента к приемному компоненту. По мере того, как переданные пакеты проходят через другие уровни, они обогащаются дополнительной информацией, необходимой для обработки пакетов на этих уровнях. На приемной стороне происходит обратный процесс и пакеты получают преобразованными из их представления на физическом уровне 220 в представление на уровне звена 210 связи для передачи данных и, окончательно, (для пакетов уровня транзакции) в форму, которая может обрабатываться на уровне 205 транзакции приемного устройства.

Уровень транзакции

В одном из вариантов осуществления уровень 205 транзакции должен обеспечивать интерфейс между ядром обработки устройства и межсоединительной архитектурой, такой как уровень 210 звена связи для передачи данных и физический уровень 220. В этом отношении первичная ответственность уровня 205 транзакции заключается в сборке и разборке пакетов (то есть, пакетов уровня транзакции или TLP). Уровень 205 трансляции обычно руководит управлением потока кредит-база для TLP. PCIe осуществляет транзакции с разделением, то есть, транзакции с запросом и ответом, разделенными во времени, позволяя звену связи в то время, когда целевое устройство собирает данные для ответа, передавать другой трафик.

Кроме того, PCIe использует управлением потоком кредит-база. В этой схеме устройство рекламирует начальный объем кредита для каждого из приемных буферов на уровне 205 транзакции. Внешнее устройство на противоположном конце линии связи, такое как концентратор 115 контроллера, показанный на фиг. 1, подсчитывает количество кредитов, использованных каждым TLP. Транзакция может передаваться, если транзакция не превышает кредитный лимит. После получения ответа объем кредита восстанавливается. Преимущество кредитной схемы состоит в том, что время ожидания возврата кредита не влияет на рабочие характеристики при условии, что не возникает кредитный лимит.

В одном из вариантов осуществления четыре адресных пространства транзакции содержат адресное пространство конфигурации, адресное пространство памяти, адресное пространство ввода/вывода и адресное пространство сообщения. Транзакции пространства памяти содержат один или более запросов считывания и запросов записи, чтобы передавать данные в местоположение отображенной памяти и от него. В одном из вариантов осуществления транзакции пространства памяти способны использовать два различных адресных формата, например, формат короткого адреса, такой как 32-разрядный адрес, или формат длинного адреса, такой как 64-разрядный адрес. Транзакции пространства конфигурации используются для доступа к пространству конфигурации устройств PCIe. Транзакции в пространстве конфигурации содержат запросы считывания и запросы записи. Транзакции пространства сообщения (или, просто сообщения) определяются для поддержки внутриполосной передачи между средствами PCIe.

Поэтому в одном из вариантов осуществления, уровень 205 транзакции собирает заголовок/полезную нагрузку пакета 206. Формат для текущего заголовка/полезной нагрузки пакета может быть найден в технических требованиях PCIe на веб-сайте технических требований PCIe.

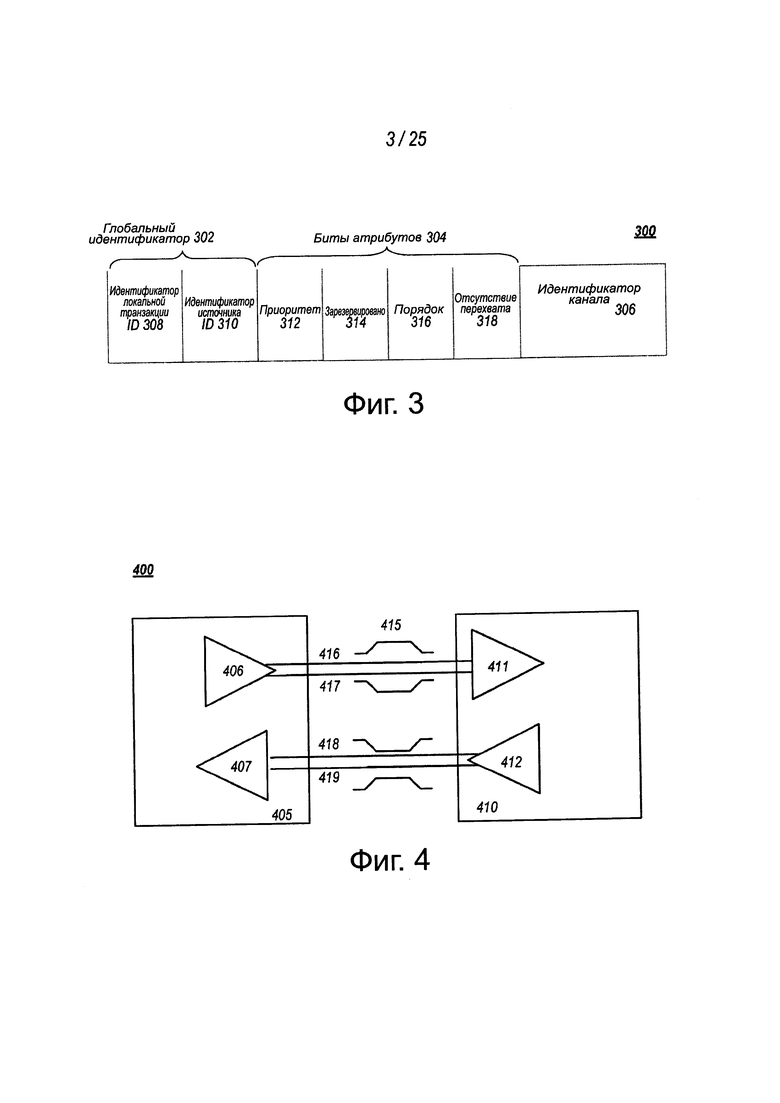

Сразу обращаемся к фиг. 3, где показан вариант осуществления дескриптора транзакции PCIe. В одном из вариантов осуществления дескриптор 300 транзакции является механизмом переноса информацию о транзакции. В этом отношении дескриптор 300 транзакции поддерживает идентификацию транзакции в системе. Другое потенциальное использование содержит модификации слежения за упорядочиванием транзакции по умолчанию и ассоциации транзакции с каналами.

Дескриптор 300 транзакции содержит поле 302 глобального идентификатора, поле 304 атрибутов и поле 306 идентификатора. В показанном примере поле 302 глобального идентификатора изображается содержащим локальное поле 308 идентификатора транзакции и поле 310 идентификатора источника. В одном из вариантов осуществления глобальный идентификатор 302 транзакции является уникальным для всех исходящих запросов.

В соответствии с одной из реализаций, локальное поле 308 идентификатора транзакции является полем, формируемым средством запроса, и оно уникально для всех исходящих запросов, которые требуют завершения для данного запрашивающего средства. Дополнительно, в этом примере, идентификатор 310 источника однозначно идентифицирует средство запросчика внутри иерархии PCIe. Соответственно, вместе с ID 310 источника локальное поле 308 идентификатора транзакции обеспечивает глобальную идентификацию транзакции внутри области иерархии.

Поле 304 атрибутов определяет характеристики и зависимости транзакции. В этом отношении, поле 304 атрибутов потенциально используется для предоставления дополнительной информации, позволяющей модификацию обработки транзакции по умолчанию. В одном из вариантов осуществления поле 304 атрибутов содержит поле 312 приоритетов, зарезервированное поле 314, поле 316 упорядочивания и поле 318 отсутствия перехвата. Здесь субполе 312 приоритета может быть модифицировано инициатором, чтобы назначить приоритет транзакции. Зарезервированное поле 314 атрибутов оставляется зарезервированным на будущее или используется согласно назначению поставщиком. Возможные модели использования, использующие приоритет или атрибуты безопасности, могут реализовываться, используя резервное поле атрибутов.

В этом примере поле 316 атрибутов упорядочивания используется для предоставления дополнительной информации, транспортирующей тип упорядочивания, который может модифицировать правила упорядочивания, действующие по умолчанию. Согласно одной примерной реализации, атрибут "0" упорядочивания обозначает, что должны применяться правила упорядочивания по умолчанию, а атрибут "1" упорядочивания обозначает упрощенное упорядочивание, при котором записи могут пропускаться в одном и том же направлении, а завершения считывания могут пропускать записи в том же самом направлении. Поле 318 атрибута перехвата используется для определения, перехватываются ли транзакции. Как показано на чертеже, поле 306 идентификатора канала идентифицирует канал, с которым связывается транзакция.

Уровень линии связи

Уровень 210 звена связи, также упоминаемый как уровень 210 связи для передачи данных, действует как промежуточный этап между уровнем 205 транзакции и физическим уровнем 220. В одном варианте осуществления ответственность уровня 210 звена связи для передачи данных обеспечивает достоверный механизм для обмена пакетами уровня транзакции (TLP) между двумя компонентами линии связи. Одна сторона уровня 210 звена связи для передачи данных принимает TLP, собранные уровнем 205 транзакции, применяет идентификатор 211 последовательности пакетов, то есть, количество идентификаций или количество пакетов, вычисляет и применяет код обнаружения ошибки, то есть, CRC 212, и представляет модифицированные TLP на физический уровень 220 для передачи через физический уровень на внешнее устройство.

Физический уровень

В одном из вариантов осуществления физический уровень 220 содержит логический субблок 221 и электрический субблок 222, чтобы физически передавать пакет внешнему устройству. Здесь логический субблок 221 ответственен за "цифровые" функции физического уровня 221. В этом отношении, логический субблок содержит секцию передачи для подготовки исходящей информации к передаче физическим субблоком 222 и секцию приемника для идентификации и подготовки принятой информации перед пропусканием ее на уровень 210 звена связи.

Физический блок 222 содержит передатчик и приемник. Передатчик снабжен логическим субблоком 221 с символами, которые передатчик переводит в последовательную форму и передает внешнему устройству. На приемник от внешнего устройства подаются переведенные в последовательную форму символы и приемник преобразует принятые сигналы в битовый поток. Битовый поток переводится обратно из последовательной формы в параллельную и подается на логический субблок 221. В одном из вариантов осуществления используется код передачи 8b/10b, где передаются/принимаются десятиразрядные символы. Здесь, специальные символы используются, чтобы кадрировать пакет с получением кадров 223. Кроме того, в одном из примеров, приемник также обеспечивает тактовые сигналы символов, восстанавливаемые из входящего последовательного потока.

Как указано выше, хотя уровень 205 транзакции, уровень 210 звена связи и физический уровень 220 обсуждаются со ссылкой на конкретный вариант осуществления стека протокола PCIe, стек многоуровневого протокола этим не ограничивается. Фактически, может присутствовать/осуществляться любой многоуровневый протокол. Как пример, порт/интерфейс, который представляется в качестве многоуровневого протокола, содержит: (1) первый уровень, на котором собираются пакеты, то есть, уровень транзакции; второй уровень, на котором устанавливается последовательная форма пакетов, то есть, звена связи; и третий уровень для передачи пакетов, то есть, физический уровень. В качестве конкретного примера, используется многоуровневый протокол интерфейса по общепринятому стандарту (common standard interface, CSI).

Далее на фиг. 4 показан вариант осуществления последовательной связной структуры PCIe типа "точка-точка". Хотя на чертеже показан вариант осуществления последовательной линии связи PCIe типа "точка-точка", последовательное звено связи типа "точка-точка" этим не ограничивается, поскольку оно содержит любой путь передачи сигнала для передачи последовательных данных. В показанном варианте осуществления основное звено связи PCIe содержит две низковольтные, дифференцированно запускаемые сигнальные пары: передающая пара 406/411 и приемная пара 412/407. Соответственно, устройство 405 содержит передающую логику 406 для передачи данных на устройство 410 и приемную логику 407 для приема данных от устройства 410. Другими словами, в звене связи PCIe содержатся два пути передачи, то есть, пути 416 и 417, и два пути приема, то есть, пути 418 и 419.

Термин "путь передачи" относится к любому пути передачи данных, такому как линия передачи, медная линия, оптическая линия, канал беспроводной связи, линия инфракрасной связи или другой канал связи. Соединение между двумя устройствами, такими как устройство 405 и устройство 410, упоминается как звено связи, такое как звено 415 связи. Звено связи может поддерживать одну дорожку - каждая дорожка представляет набор дифференциальных сигнальных пар (одна пара для передачи, одна пара для приема). Чтобы определить ширину полосы пропускания, звено связи может объединять множество дорожек, обозначенные как xN, где N - любая поддерживаемая ширина звена связи, такая как 1, 2, 4, 8, 12, 16, 32, 64 или шире.

Термин "дифференциальная пара" относится к двум путям передачи, таким как линии 416 и 417, для передачи дифференциальных сигналов. Как пример, когда линия 416 переключается с низковольтного уровня на высоковольтный уровень, то есть, формируется нарастающий фронт, линия 417 переключается с высокого логического уровня на низкий логический уровень, то есть, формируется ниспадающий фронт. Дифференциальные сигналы потенциально демонстрируют лучшие электрические характеристики, такие как лучшая целостность сигнала, то есть, перекрестная связь, положительный/отрицательный выброс напряжения, звон и т.д. Это позволяет получить лучшее временное окно, дающее возможность более высоких частот передачи.

На фиг. 5 показана упрощенная блок-схема 500 примерной многокристальной интегральной схемы 505, содержащей два или более чипов или кристаллов, (например, 510, 515) соединенных для осуществления связи, используя примерное звено 520 связи многокристальной интегральной схемы (MCPL). Хотя на фиг. 5 показан пример из двух (или более) кристаллов, которые соединяются, используя примерную MCPL 520, следует понимать, что принципы и функции, описанные здесь в отношении реализаций MCPL, могут применяться среди потенциально возможных других примеров к любому межсоединению или звену связи, соединяющим кристалл (например, 510) и другие компоненты, содержащие два или более кристаллов (например, 510, 515), соединяя кристалл (или чип) с другим, находящимся вне кристалла компонентом, соединяя кристалл с другим устройством или находящимся вне корпуса интегральной схемы кристаллом (например, 505), соединяя кристалл с корпусом BGA интегральной схемы реализуя временное соединение на керамической подложке (POINT),.

Обычно, многокристальная интегральная схема (например, 505) может быть электронной интегральной схемой, где многочисленные интегральные схемы (IC), полупроводниковые кристаллы или другие дискретные компоненты (например, 510, 515) помещены на объединяющую подложку (например, кремниевую или другую полупроводниковую подложку), облегчая использование объединенных компонент в качестве единого компонента (например, как бы большей интегральной схемы). В некоторых случаях крупные компоненты (например, кристаллы 510, 515) сами могут быть системными интегральными схемами, такими как системы на чипе (SoC), многопроцессорные чипы или другие компоненты, которые содержат многочисленные компоненты (например, 525-530 и 540-545) на устройстве, например, на едином кристалле (например, 510, 515). Многокристальные интегральные схемы 505 могут обеспечивать гибкость при построении сложных и изменяемых систем из потенциально возможных многочисленных дискретных компонент и систем. Например, из числа множества примеров, каждый из кристаллов 510, 515 может изготавливаться или как-либо иначе поставляться двумя различными предприятиями, а кремниевая подложка 505 интегральной схемы может обеспечиваться третьим предприятием. Дополнительно, кристаллы и другие компоненты внутри многокристальной интегральной схемы 505 сами могут содержать межсоединение или другие связные структуры (например, 535, 550), обеспечивая инфраструктуру для связи между компонентами (например, 525-530 и 540-545) внутри устройства (например, 510, 515, соответственно). Различные компоненты и межсоединения (например, 535, 550) могут потенциально поддерживать или использовать многие различные протоколы. Дополнительно, связь между кристаллами (например, 510, 515) потенциально может содержать транзакции между различными компонентами на кристаллах по многочисленным различным протоколам. Разработка механизмов обеспечения связи между чипами (или кристаллами) многокристальной интегральной схемы может быть многообещающей, когда традиционные решения, использующие узкоспециализированные, дорогостоящие и специализированные для интегральной схемы решения, основанные на конкретных сочетаниях компонент (и требуемых транзакциях), целесообразны для взаимных соединений.

Примеры, системы, алгоритмы, устройства, логика и функции, описанные в рамках настоящих технических требований могут решать, по меньшей мере, некоторые из идентифицированных выше проблем, потенциально включая и многие другие, неявно упомянутые здесь. Например, в некоторых реализациях могут обеспечиваться широкая полоса пропускания, низкая мощность, интерфейс с малой задержкой, чтобы соединять ведущее устройство (например, центральный процессор) или другое устройство с сопутствующим чипом, который находится в той же самой интегральной схеме, что и ведущее устройство. Такое звено связи многокристальной интегральной схемы (MCPL) может поддерживать многочисленные варианты корпуса интегральной схемы, многочисленные протоколы ввода-вывода, а также характеристики надежности, доступности и удобства обслуживания (RAS). Дополнительно, физический уровень (PHY) может содержать электрический уровень и логический уровень и может поддерживать более протяженные длины каналов, в том числе, длины канала до приблизительно 45 мм, а в некоторых случаях и более. В некоторых реализациях примерная MCPL может работать на высоких скоростях передачи данных, в том числе, на скоростях, превышающих 8-10 Гб/с.

В одной из примерных реализаций MCPL электрический уровень PHY может улучшать традиционные решения многоканальных межсоединений (например, многоканальный ввод-вывод DRAM), увеличивая скорость передачи данных и конфигурацию канала, например, посредством многочисленных функций, таких как, например, среди прочих потенциально возможных примеров, регулируемое окончание промежуточного канала, активное подавление маломощных перекрестных помех, схемная избыточность, коррекция и выравнивание рабочего цикла на каждый бит, линейное кодирование и выравнивание передатчиков.

В одной из примерных реализаций MCPL может быть осуществлен логический уровень PHY, который может дополнительно помочь (например, функции электрического уровня) в повышении скорости передачи данных и расширении конфигурации канала, в то же время также позволяя межсоединение для маршрутизации многочисленных протоколов через электрический уровень. Такие реализации могут обеспечивать и определять модульный общий физический уровень, который является протокольно агностическим и спроектирован для работы с потенциально любым существующим или будущим протоколом межсоединений.

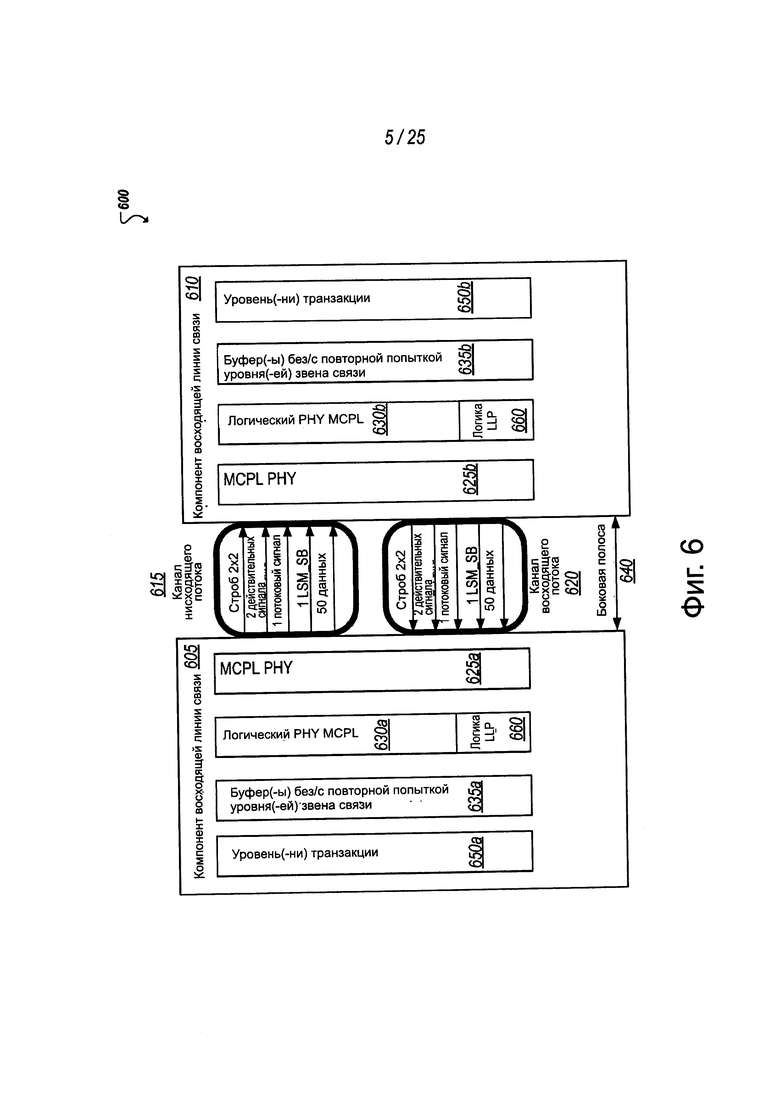

На фиг. 6 представлена упрощенная блок-схема 600, показывающая, по меньшей мере, часть системы, содержащую примерную реализацию звена связи многокристальной интегральной схемы (MCPL). MCPL может быть осуществлена, используя физические электрические соединения (например, провода, реализуемые как дорожки), соединяющие первое устройство 605 (например, первый кристалл, содержащий один или более субкомпонент) со вторым устройством 610 (например, вторым кристаллом, содержащим один или более других субкомпонент). В конкретном примере, показанном на высокоуровневом представлении схемы 600, все сигналы (в каналах 615, 620) могут быть однонаправленными и дорожки могут обеспечиваться для сигналов данных, чтобы иметь как восходящую, так и нисходящую передачу данных. Хотя блок-схема 600 на фиг. 6 относится к первому компоненту 605 как к восходящему компоненту, а ко второму компоненту 610 как к нисходящему компоненту, и физические дорожки MCPL используются при передаче данных в качестве нисходящего канала 615 и используются при приеме данных (от узла 610) в качестве восходящего канала 620, следует понимать, что MCPL между устройствами 605, 610 может использоваться каждым из устройств, чтобы передавать и принимать данные между устройствами.

В одной из примерных реализаций MCPL может обеспечивать физический уровень (PHY), содержащий электрический PHY 625а, b (или, все вместе, 625) MCPL и исполняемую логику, осуществляющую логический PHY 630а, b (или, все вместе, 630) MCPL. Электрический, или физический PHY 625 может обеспечивать физическое соединение, через которое передаются данные между устройствами 605, 610. Компоненты и логика формирования сигнала могут быть осуществлены в сочетании с физическим уровнем PHY 625, чтобы установить для звена связи возможности передачи данных с высокой скоростью и конфигурации канала, которые в некоторых приложениях могут содержать плотно сгруппированные физические соединения на длинах приблизительно 45 мм или более. Логический PHY 630 может содержать логику для облегчения синхронизации, управления состоянием звена связи (например, для уровней 635а, 635b звена связи) и мультиплексирования протокола между потенциально многочисленными различными протоколами, используемые для связи по MCPL.

В одной из примерных реализаций физический PHY 625 может содержать для каждого канала (например, 615, 620) набор дорожек для передачи данных, по которым могут передаваться данные внутри полосы. В этом конкретном примере в каждом восходящем и нисходящем каналах 615, 620 обеспечиваются 50 дорожек для данных, хотя может использоваться и любое другое количество дорожек, разрешенное ограничениями по расположению и энергетике, требуемыми приложениями, ограничениями на устройство и т.д. Каждый канал может дополнительно содержать одну или более выделенных дорожек для строб-сигнала или синхронизации, канального сигнала, одну или более выделенных дорожек для действительного сигнала для канала, одну или более выделенных дорожек для потокового сигнала и одну или более выделенных дорожек для управления конечным автоматом звена связи или сигналом боковой полосы. В числе других примеров, физический PHY может дополнительно содержать звено 640 связи боковой полосы, которое в некоторых примерах может быть двунаправленным более низкочастотным звеном связи управляющего сигнала, используемым для координации переходных состояний и других атрибутов MCPL, соединяющей устройства 605, 610.

Как отмечено выше, многочисленные протоколы могут поддерживаться, используя реализацию MCPL. Конечно, многочисленные, независимые уровни 650а, 650b транзакции могут обеспечиваться в каждом устройстве 605, 610. Например, каждое устройство 605, 610, среди прочих, может поддерживать и использовать два или более протоколов, таких как PCI, PCIe, QPI, Intel In-Die Interconnect (IDI). IDI является когерентным протоколом, используемый на кристалле для связи между ядрами, кэшами последнего уровня (Last Level Caches (LLC)), памятью, графикой и контроллерами ввода-вывода. Другие протоколы могут также поддерживаться, в том числе протокол Ethernet, протоколы Infiniband и другие протоколы на основе связной структуры PCIe. Среди других примеров, также может использоваться объединение логического PHY и физического PHY в качестве межсоединения "кристалл-кристалл", чтобы соединить SerDes PHY (PCIe, Ethernet, Infiniband или другой высокоскоростной SerDes) на одном кристалле с его верхними уровнями, которые осуществляются на другом кристалле.

Логический PHY 630 может поддерживать мультиплексирование между этими многочисленными протоколами на MCPL. Например, выделенная дорожка для потока может использоваться для подтверждения кодированного потокового сигнала, который идентифицирует, какой протокол должен примениться к данным, переданным, по существу, одновременно по дорожкам для данных канала. Дополнительно, логический PHY 630 может использоваться, чтобы согласовать различные типы изменений переходных состояний звена связи, которые различные протоколы могут поддерживать или запрашивать. В некоторых случаях, сигналы LSMSB, переданные по выделенному дорожке LSMSB канала, могут использоваться вместе со звеном 640 связи боковой полосы, чтобы передать и согласовать переходные состояния звена связи между устройствами 605, 610. Дополнительно, настройка звена связи, обнаружение ошибок, обнаружение искажений, устранение искажений и другие функциональные возможности традиционных межсоединений могут заменяться или управляться, частично используя логический PHY 630. Например, действительные сигналы, переданные по одной или более выделенным дорожкам для действительного сигнала в каждом канале, помимо других примеров, могут использоваться для сигнализации о деятельности звена связи, обнаружения искажения, ошибок звена связи и реализации других функций. В частном примере на фиг. 6, многочисленные дорожки для действительного сигнала обеспечиваются по каждому каналу. Например, дорожки для данных внутри канала могут быть связаны или кластеризованы (физически и/или логически), и дорожка для действительного сигнала может обеспечиваться для каждой группы. Дополнительно, в качестве других примеров могут обеспечиваться многочисленные стробируемые дорожки, в некоторых случаях, также чтобы обеспечить выделенный стробированный сигнал для каждого кластера во множестве кластеров дорожек для данных в канале.

Как отмечено выше, логический PHY 630 может использоваться для согласования и управления сигналами управления звена связи, передаваемыми между устройствами, соединенными посредством MCPL. В некоторых реализациях логический PHY 630 может содержать логику 660 формирования пакетов уровня звена (LLP) связи, которая может использоваться для передачи сообщений управления на уровне звена связи через MCPL (то есть, в полосе). Такие сообщения могут передаваться по дорожкам данных канала, с помощью дорожки потокового сигнала, идентифицирующего, что данные являются сообщениями типа "уровень звена-уровень звена", такими, как, например, данные управления уровня звена связи. Сообщения уровня звена связи, позволяющие использовать модуль 660 LLP, помимо других функций уровня звена связи, могут помочь при согласовании и выполнении передачи состояний уровня звена связи, управлении электропитанием, закольцовывании, запрете, повторной центровке, скремблировании между уровнями 635а, 635b звена связи устройств 605, 610, соответственно.

На фиг. 7 показана схема 700, представляющая примерную передачу сигналов, используя набор дорожек (например, 615, 620) в конкретном канале примерной MCPL. В примере на фиг. 7 два кластера из двадцати пяти (25) дорожек для данных обеспечиваются для пятидесяти (50) общих дорожек для передачи данных в канале. На чертеже показана часть дорожек, тогда как другие (например, DATA [4-46] и вторая дорожка строб-сигнала (STRB)) для удобства показа конкретного примера не показаны (например, такие как сигналы с избыточностью). Когда физический уровень находится в активном состоянии (например, электропитание не выключено или находится в режиме низкого потребления (например, в состоянии L1)), дорожки строб-сигнала (STRB) могут сопровождаться синхронным тактовым сигналом. В некоторых реализациях данные могут передаваться как на нарастающем фронте, так и на ниспадающем фронте строб-сигнала. Каждый фронт (или половина тактового цикла) может устанавливать границу единичного интервала (UI). Соответственно, в этом примере, бит (например, 705), может передаваться по каждому дорожке, позволяя передавать байт каждые 8UI. Период 710 времени байта может быть определен как 8UI или время для передачи байта по одиночной дорожке из числа дорожек для данных (например, DATA [0-49]).

В некоторых реализациях действительный сигнал, переданный по одному или более выделенным действительным сигнальным каналам (например, VALIDO, VALID1), может служить опережающим индикатором для приемного устройства, чтобы идентифицировать, когда подтверждается (высокий уровень), для приемного устройства или приемника, что в течение следующего периода времени, такого период 710 времени байта, данные передаются от передающего устройства или источника по дорожкам для данных (например, DATA[0-49]). Альтернативно, когда действительный сигнал имеет низкий уровень, источник указывает приемнику, что приемник не должен передавать данные по дорожкам для данных в течение следующего периода времени. Соответственно, когда логический PHY приемника обнаруживает, что действительный сигнал не подтвержден (например, на дорожках VALID0 и VALID1), приемник может игнорировать любые данные, которые обнаруживаются на дорожках для данных (например, DATA [0-49]) во время следующего периода времени. Например, шум перекрестных помех или другие биты могут появляться на одной или более дорожках для данных, когда источник, в действительности, не передает данных. На основании действительного сигнала низкого уровня или неподтвержденного в течение предыдущего периода времени (например, периода времени предыдущего байта), приемник может решить, что в течение последующего периода времени дорожки для данных должны игнорироваться.

Данные, переданные по каждой из дорожек MCPL, могут быть строго выровнены со строб-сигналом. Период времени может быть определен, основываясь на строб-сигнале, таком как период времени байта, и каждый из этих периодов может соответствовать определенному окну, в котором сигналы должны передаваться по дорожкам для данных (например, DATA[0-49]), дорожкам для действительного сигнала (например, VALID1, VALID2) и дорожке для потокового сигнала (например, STREAM). Соответственно, выравнивание этих сигналов может позволить идентификацию, что действительный сигнал в предыдущем окне периода времени применяется к данным в последующем окне периода времени, и что потоковый сигнал применяется к данным в том же самом окне периода времени. Потоковый сигнал может быть кодированным сигналом (например, 1 байтом данных для окна периода времени байта), который кодируется, чтобы идентифицировать протокол, применяемый к данным, передаваемым во время того же самого окна периода времени.

Для иллюстрации, в конкретном примере на фиг. 7 определено окно периода времени байта. Действительный сигнал подтверждается в окне n (715) периода времени перед тем, как какие-либо данные будут введены в дорожки для данных DATA[0-49]. В следующем окне n+1 (720) периода времени данные передаются по меньшей мере по некоторым из дорожек для данных. В данном случае, данные передаются по всем пятидесяти дорожкам для данных в течение времени n+1 (720). Поскольку действительный сигнал был подтверждена для длительности предыдущего окна n (715) периода времени, устройство приемника может проверить данных, принятые по дорожкам для данных DATA[0-49] во время окна n+1 (720) периода времени. Дополнительно, опережающий характер действительного сигнала во время окна n (715) периода времени позволяет приемному устройству подготовиться к входящим данным. Продолжая пример на фиг. 7, действительный сигнал остается подтвержденным (на VALID1 и VALID2) в течение длительности окна n+1 (720) периода времени, заставляя устройство приемника ожидать данные, переданные по дорожкам для данных DATA[0-49] во время окна n+2 (725) периода времени. Если действительный сигнал будет оставаться подтвержденным в течение окна n+2 (725) периода времени, устройство приемника может дополнительно ожидать приема (и обработки) дополнительных данных, передаваемых сразу после окна n+3 (730) периода времени. В примере, показанном на фиг. 7, однако, подтверждение действительного сигнала снимается в течение длительности окна n+2 (725) периода времени, указывая устройству приемника, что никакие данные не будут передаваться в течение окна n+3 (730) периода времени и что любые биты, обнаруженные на дорожках для данных DATA[0-49] в течение окна n+3 (730) периода времени должны игнорироваться.

Как отмечено выше, для каждого канала могут поддерживаться многочисленные действительные дорожки и дорожки строб-сигнала. Помимо прочих преимуществ, при сохранении простоты схемы и синхронизации среди кластеров это может помочь в части относительно длинных физических дорожек, соединяющих два устройства. В некоторых реализациях набор дорожек для данных может быть объединен кластеры дорожек для данных. Например, в примере, показанном на фиг. 7, дорожки для данных DATA[0-49] могут быть объединены в два кластера по двадцать пять дорожек и каждый кластер может иметь выделенную дорожку для действительного сигнала и стробируемого сигнала. Например, дорожка для действительного сигнала VALID1 может быть связана с дорожками для данных DATA[0-24], а дорожка для действительного сигнала VALID2 может быть связана с дорожкой для данных DATA[25-49]. Сигналы на каждой "копии" действительных дорожек и дорожек для строб-сигнала для каждого кластера могут быть идентичными.

Как описано выше, данные STREAM на дорожке для потокового сигнала могут использоваться для указания принимающему логическому PHY, какой протокол должен применяться к соответствующим данным, передаваемым по дорожкам для данных DATA[0-49]. В примере на фиг. 7 потоковый сигнал передается по STREAM в течение того же самого окна периода времени, что и данные по дорожкам для данных DATA[0-49], чтобы указать протокол данных для дорожек для данных. В альтернативных реализациях, помимо других потенциальных изменений, потоковый сигнал может передаваться в течение предыдущего окна такого периода времени, как для соответствующих действительных сигналов. Однако, продолжая пример на фиг. 7, потоковый сигнал 735 передается во время окна n+1 (720) периода времени, которое кодируется, чтобы указать протокол (например, PCIe, PCI, IDI, QPI, и т.д.), который должен примениться к битам, передаваемым по дорожкам для данных DATA[0-49] в течение окна n+1 (720) периода времени. Аналогично, другой потоковый сигнал 740 может быть передан в течение последующего окна n+2 (725) периода времени, чтобы указать протокол, который применяется к битам, передаваемым по дорожкам для данных DATA[0-49] во время окна n+2 (725) периода времени, и так далее. В некоторых случаях, таких как в примере на фиг. 7, (где оба потоковых сигнала 735, 740 имеют одно и то же кодирование, двоичный FF), данные в последовательных окнах периода времени (например, n+1 (720) и n+2 (725)) могут принадлежать одному и тому же протоколу. Однако в других случаях данные в последовательных окнах периода времени (например, n+1 (720) и n+2 (725)) могут происходить от различных транзакции, к которым должны применяться разные протоколы, и потоковые сигналы (например, 735, 740), помимо других примеров, могут кодироваться соответственно, чтобы идентифицировать различные протоколы, применяемые к последовательным байтам данных на дорожках для данных (например, DATA[0-49]).

В некоторых реализациях для MCPL может быть определено состояние низкого энергопотребления или ожидания. Например, когда ни одно из устройств на MCPL не передает данные, физический уровень (электрический и логический) MCPL может переходить в состояние ожидания или низкого энергопотребления. Например, как показано на фиг. 7, в окне n-2 (745) периода времени MCPL находится в спокойном состоянии или состоянии ожидания и строб-сигнал выключен, чтобы экономить электроэнергию. MCPL может переключаться из режима низкого энергопотребления или режима ожидания, подавая строб-сигнал в окне n-1 периода времени окна периода времени (например, 705). Строб-сигнал может завершить передачу преамбулы (например, чтобы помочь запустить и синхронизовать каждую из дорожек канала, а также устройство приемника), начиная строб-сигнал перед любой другой сигнализацией по другим нестробированным дорожкам. После этого окна n-1 (705) периода времени действительный сигнал может быть подтвержден в окне n (715) периода времени, чтобы уведомить приемник, что предстоит появление данных в следующем окне n+1 (720) периода времени, как обсуждалось выше.

MCPL может повторно войти в состояние низкого энергопотребления или ожидания (например, состояние LI) после обнаружения условий ожидания на дорожках для действительных сигналов, дорожках для данных и/или других дорожках канала MCPL. Например, не может быть обнаружена никакая сигнализация, начинающаяся в окне n+3 (730) периода времени, и далее. Логика на источнике или на устройстве приемника, среди прочих примеров и принципов, может инициировать переход обратно в состояние низкого энергопотребления, ведущее снова (например, окно n+5 (755) периода времени) к строб-сигналу, вводящему режим ожидания или низкого энергопотребления (в том числе те, которые обсуждаются здесь позже).

Электрические характеристики физического PHY среди прочих признаков могут содержать одну или более асимметричную сигнализацию, синхронизацию на половинной частоте, согласование канала межсоединений, а также транспортную задержку на чипе для передатчика (источника) и приемника (приемник), оптимизированную защиту от электростатического разряда (ESD), емкость контактных площадок. Дополнительно MCPL может осуществляться, чтобы достигнуть более высокой скорости передачи данных (например, приближающейся к 16 Гб/с) и характеристик эффективности использования энергии, чем при традиционных решениях для ввода-вывода интегральных схем.

На фиг. 8 показан участок упрощенной блок-схемы 800, представляющий часть примерной MCPL. Схема 800, показанная на фиг. 8, содержит представление примерной дорожки 805 (например, дорожки для данных, дорожки для действительного сигнала или дорожки для потокового сигнала) и логики 810 формирования тактового сигнала. Как показано в примере на фиг. 8, в некоторых реализациях, логика 810 формирования тактового сигнала может быть осуществлена как дерево синхронизации, чтобы распространять сформированный тактовый сигнал каждому блоку, реализующему каждую дорожку примерной MCPL, такую как дорожка 805 для данных. Дополнительно может обеспечиваться схема 815 восстановления синхронизации. В некоторых реализациях, вместо обеспечения отдельной схемы восстановления синхронизации для каждой дорожки, по которой распространяется сигнал синхронизации, что является общепринятым, по меньшей мере, в некоторых традиционных архитектурах межсоединений ввода-вывода, может обеспечиваться единая схема восстановления синхронизации для кластера из множества дорожек. Конечно, отдельная дорожка для строба и сопутствующая схема восстановления синхронизации, которые применяются в примерных конфигурациях, показанных на фиг. 6 и 7, могут быть обеспечены для каждого кластера из двадцати пяти дорожек для данных.

Продолжая обращаться к фиг. 8, в некоторых реализациях, по меньшей мере, дорожки для данных, дорожки для потокового сигнала и дорожки для действительного сигнала могут заканчиваться на промежуточном канале к регулируемому напряжению больше нуля (земле). В некоторых реализациях напряжение на промежуточном канале пути может регулироваться до Vcc/2. В некоторых реализациях для каждого кластера дорожек может обеспечиваться единый регулятор 825 напряжения. Например, при применении в примерах, показанных на фиг. 6 и 7, среди других потенциально возможных примеров первый регулятор напряжения может обеспечиваться для первого кластера из двадцати пяти дорожек для данных, а второй стабилизатор напряжения может обеспечиваться для остального кластера из двадцати пяти дорожек для данных. В некоторых случаях, среди других примеров, примерный регулятор 825 напряжения может быть осуществлен как линейный регулятор, схема с переключаемой емкостью. В некоторых реализациях, среди других примеров, линейный регулятор может быть снабжен аналоговым контуром обратной связи или цифровым контуром обратной связи.

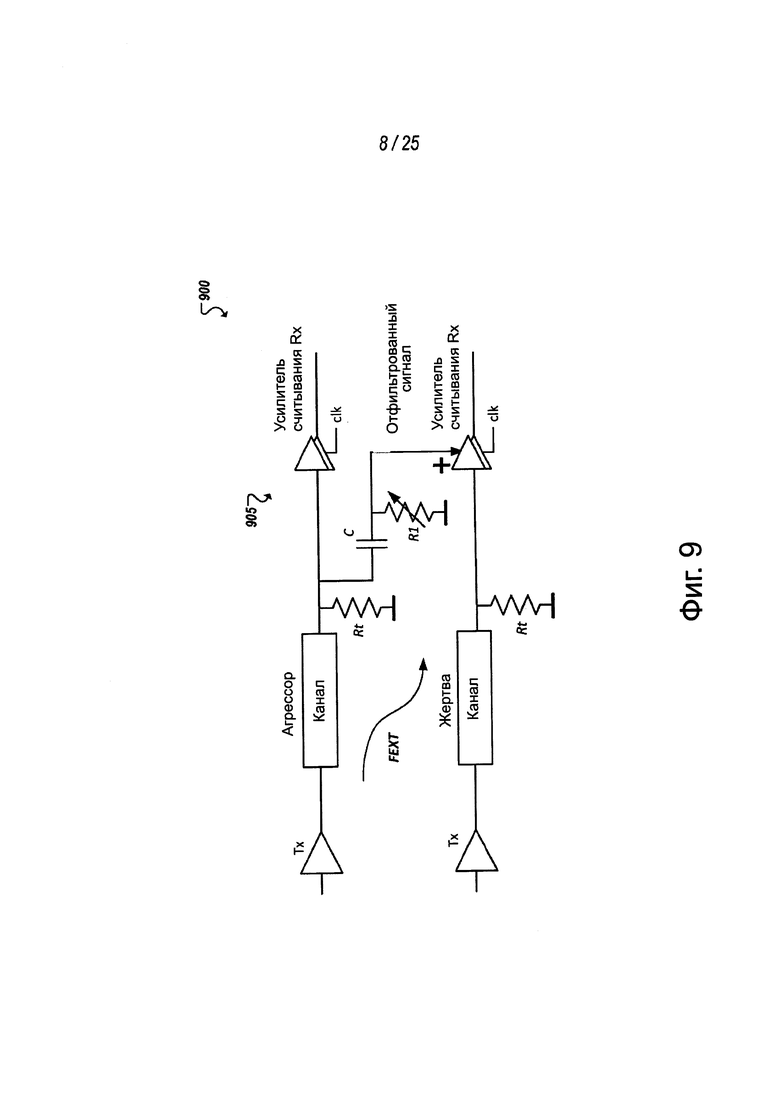

В некоторых реализациях для примерной MCPL может также обеспечиваться схема подавления перекрестных помех. В некоторых случаях компактный характер длинных проводов MCPL может создавать перекрестные помехи между дорожками. Для решения этих и других проблем может реализовываться логика подавления перекрестных помех. Например, в одном из примеров, показанных на фиг. 9-10, перекрестные помехи могут быть значительно уменьшены с помощью примерной активной схемы пониженного энергопотребления, такой как показано на схемах 900 и 1000. Например, в примере на фиг. 9 взвешенный, прошедший фильтр верхних частот сигнал "агрессора" может быть добавлен к сигналу "жертвы" (то есть, сигналу, подвергающемуся перекрестным помехам со стороны агрессора). Каждый сигнал может рассматриваться как жертва перекрестных помех от любого другого сигнала в звене связи и может сам быть агрессором в отношении другого сигнала в той степени, в которой он является источником перекрестных помех. Такой сигнал может создаваться и снижать перекрестные помехи на дорожке жертвы более, чем на 50%, благодаря производному характеру перекрестных помех на звене связи. Сигнал агрессора, прошедший низкочастотный фильтр, как показано в примере на фиг. 9, может формироваться при прохождении через высокочастотный RC-фильтр (реализуемый, например, с помощью С и R1), который создает отфильтрованный сигнал, который должен добавляться, используя схему 905 суммирования (например, чувствительный усилитель приемника).

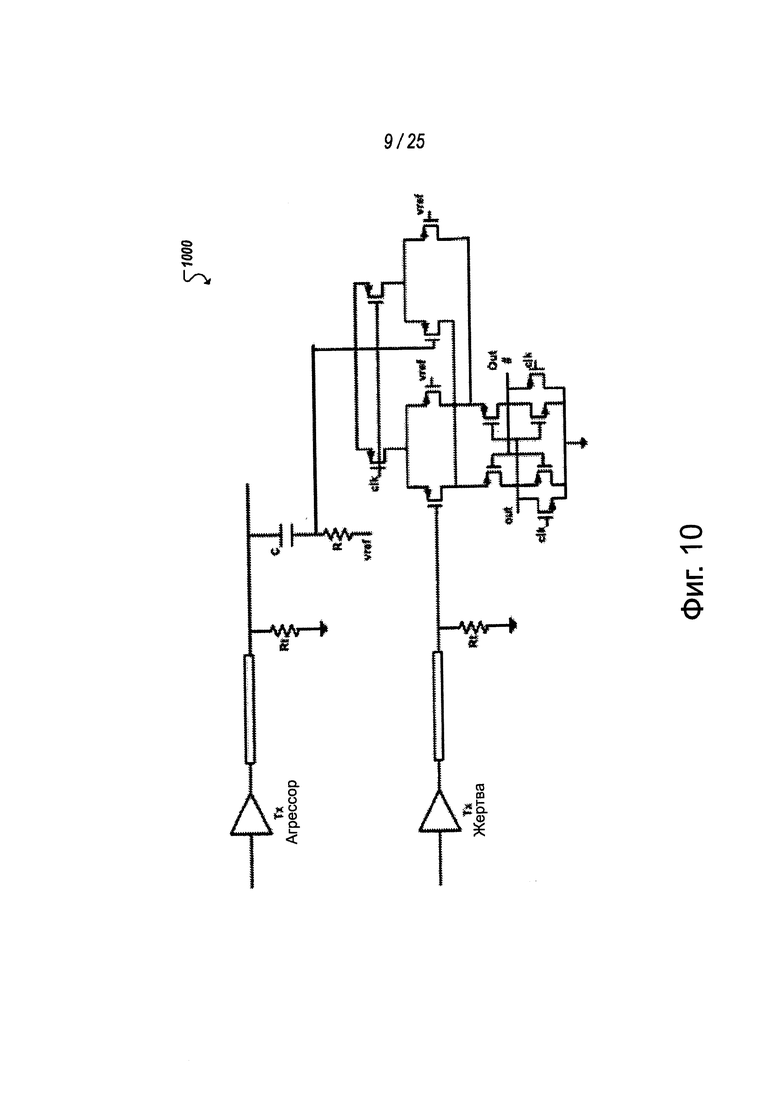

Реализации, подобные описанным в примере на фиг. 9, могут быть особенно удобными решениями для такого приложения, как MCLP, поскольку схема может быть реализована с относительно низкими непроизводительными потерями, как показано в схеме на фиг. 10, где поясняется примерная схема на транзисторном уровне, показанная и описанная в примере на фиг. 9. Следует понимать, что представления на фиг. 9 и 10 являются упрощенными представлениями и фактическая реализация может содержать многочисленные экземпляры схем, показанных на фиг. 9 и 10, чтобы разместить схему подавления перекрестных помех среди и между дорожками звена связи. В качестве примера, помимо прочих примеров, в звене связи с тремя дорожками (например, дорожки 0-2) схема, подобная описанной в примерах на фиг. 9 и 10, может обеспечиваться между дорожкой 0 и дорожкой 1, между дорожкой 0 и дорожкой 2, между дорожкой 1 и дорожкой 0, между дорожкой 1 и дорожкой 2, между дорожкой 2 и дорожкой 0, между дорожкой 2 и дорожкой 1 и т.д., основываясь на геометрии и расположении дорожек.

Дополнительные функции могут осуществляться на физическом уровне PHY примерной MCPL. Например, ответвление приемника может вносить существенную погрешность и в некоторых случаях ограничивать поле допуска напряжения ввода-вывода. Избыточность схемы может использоваться для улучшения чувствительности приемника. В некоторых реализациях избыточность схемы может быть оптимизирована, чтобы решать проблему среднеквадратического отклонения устройств выборки данных, используемых в MCPL. Например, может обеспечиваться примерное устройство выборки данных, приспособленное к требованию утроенного (3) среднеквадратичного отклонения. В примерах на фиг. 6 и 7, например, имелось два (2) устройства выборки данных, которые должны использоваться для каждого приемника (например, для каждой дорожки), сто (100) устройств выборки должны использоваться для пятидесяти (50) дорожек MCPL. В этом примере вероятность, что одна из дорожек приемника (RX) не соответствует требованию утроенного среднеквадратичного отклонения, составляет 24%. Может обеспечиваться генератор опорного напряжения чипа для установления верхней границы отклонения и перехода на следующее устройство выборки данных в приемнике, если обнаруживается, что другое устройство из числа устройств выборки превышает границу. Однако, если в каждом приемнике должны использоваться четыре (4) устройства выборки данных (то есть, вместо двух в этом примере), приемник будет давать отказ, только если три из четырех устройств выборки перестанут работать. Для MCPL с пятьюдесятью дорожками, как в примерах на фиг. 6 и 7, добавление этой дополнительной избыточности схемы может существенно снизить частоту отказов с 24% до менее чем 0,01%.

В других дополнительных примерах, при очень высоких скоростях передачи данных, коррекция цикла загрузки на бит (DCC) и устранение искажений могут использоваться, чтобы увеличить базовую линию на DCC кластера, и устранить искажения для улучшения поля допуска звена связи. Вместо исправления для всех случаев, как в традиционных решениях, в некоторых реализациях может быть использована цифровая реализация с низким энергопотреблением, которая воспринимает и корректирует выбросы, при которых дорожка ввода-вывода может перестать работать. Например, может выполняться глобальная настройка дорожек, чтобы идентифицировать проблемные дорожки внутри кластера. Эти проблемные дорожки могут затем планироваться для синхронизации по каждой дорожке, чтобы достигнуть высоких скоростей передачи данных, поддерживаемых MCPL.

В некоторых примерах MCPL, как вариант, могут также осуществляться дополнительные функции, чтобы улучшить показатели производительности физического звена связи. Например, может обеспечиваться линейное кодирование. Хотя для инверсии (DBI) шины данных постоянного тока (DC) могут быть разрешены нагрузки на промежуточном пути, как описано выше и описание которых не приводится, DBI переменного тока (АС) все еще могут использоваться, чтобы снизить динамическую мощность. Также может использоваться более сложное кодирование, чтобы исключить наихудший случай разности единиц и нулей, чтобы, помимо примеров с другими преимуществами, уменьшить, например, потребность в приводе регулятора на промежуточном пути, а также предельный шум при переключении ввода-вывода. Дополнительно, как вариант, может также осуществляться коррекция передатчиков. Например, на очень высоких скоростях передачи данных вносимые потери для канала внутри корпуса интегральной схемы могут быть значительными. Весовая коррекция передатчиков с двумя ответвлениями (выполняемая, например, во время начальной последовательности включения электропитания) может в некоторых случаях быть достаточной, чтобы смягчить некоторые из прочих таких проблем.

На фиг. 11 представлена упрощенная блок-схема 1100, показывающая пример логический PHY примерной MCPL. Физический 1105 PHY может соединяться с кристаллом, который содержит логический PHY 1110 и дополнительную логику, поддерживающую уровень звена связи MCPL. Кристалл в этом примере может дополнительно содержать логику для поддержки многочисленных различных протоколов на MCPL. Например, в примере на фиг. 11, логика 1115 PCIe может обеспечиваться также, как логика 1120 IDI, так что помимо потенциально возможных многочисленных других примеров кристаллы могут соединяться, используя PCIe или IDI на одной и той же MCPL, соединяющей два кристалла, в том числе, в примерах, где через MCPL поддерживаются более двух протоколов или протоколов, отличных от PCIe и IDI. Различные протоколы, поддерживаемые среди кристаллов, могут предложить различные уровни обслуживания и функции.

Логический PHY уровень 1110 может содержать логику 1125 управления конечным автоматом звена связи, чтобы согласовать изменения состояния звена связи согласно запросам логики верхнего уровня кристалла (например, полученными по PCIe или IDI). Логический PHY 1110 может дополнительно содержать тестирование звена связи и отладку логики (например, 1130) и некоторых реализаций. Как отмечено выше, пример MCPL может поддерживать управляющие сигналы, передаваемые между кристаллами по MCPL, чтобы облегчить функции агностики протокола, высокопроизводительные характеристики и энергопотребление (помимо других примерных функций) MCPL. Например, логический PHY 1110 может поддерживать формирование и передачу, а также прием и обработку действительных сигналов, потоковых сигналов и сигналов боковой полосы LSM в сочетании с передачей и приемом данных по выделенным дорожкам для данных, как описано в примерах выше.

В некоторых реализациях логика мультиплексирования (например, 1135) и демультиплексирования (например, 1140) может быть включена или как-либо иначе быть доступна для логического уровня 1110 PHY. Например, логика мультиплексирования (например, 1135) может использоваться для идентификации данных (например, введенных в качестве пакетов, сообщений и т.д.), которые должны передаваться через MCPL. Логика 1135 мультиплексирования может идентифицировать протокол, управляющий данными, и формировать потоковый сигнал, который кодируется, чтобы идентифицировать протокол. Например, в одном из примеров реализации, потоковый сигнал может кодироваться как байт из двух шестнадцатеричных символов (например, IDI: FFh; PCIe: FOh; LLP: AAh; в боковой полосе: 55h; и т.д.) и может передаваться в течение того же самого окна (например, окна периода времени байта) данных, управляемого идентифицированным протоколом. Аналогично, логика 1140 демультиплексирования может использоваться для интерпретации входящих потоковых сигналов, чтобы декодировать потоковый сигнал и идентифицировать протокол, который должен применяться к данным, принимаемым одновременно с потоковым сигналом по дорожкам для данных. Логика 1140 демультиплексирования может затем применять (или обеспечивать) обработку уровня звена связи, специфичную для протокола, и заставлять данные обрабатываться соответствующей логикой протокола (например, логикой 1115 PCIe или логикой 1120 IDI).

Логический уровень 1110 PHY может дополнительно содержать логику 1150 пакетов уровня звена связи, которая может использоваться для управления различными функциями звена связи, в том числе, задачами управления электропитанием, контуром обратной связи, запретом, повторной центровкой, скремблированием и т.д. Логика 1150 LLP, помимо прочих функций, может облегчить сообщения типа "уровень звена связи-уровень звена связи" по MCLP. Данные, соответствующие сигнализации LLP, могут быть также идентифицированы потоковым сигналом, переданным по выделенной дорожке для потокового сигнала, который кодируется, чтобы идентифицировать, что дорожки данных являются дорожками для данных LLP. Логики (например, 1135, 1140) мультиплексирования и демультиплексирования могут также использоваться для формирования и интерпретации потоковых сигналов, соответствующие трафику LLP, а также, чтобы заставить такой трафик обрабатываться соответствующей логикой кристалла (например, логикой 1150 LLP). Аналогично, поскольку некоторые реализации MCLP могут содержать, среди других примеров, выделенную боковую полосу (например, боковую полосу 1155 и поддерживающую логику), такую как асинхронный и/или более низкочастотный канал боковой полосы.

Логика 1110 логического уровня PHY 1110 может дополнительно содержать логику управления конечным автоматом звена связи, которая может формировать и принимать (и использовать) сообщение управления состоянием звена связи по выделенной дорожке боковой полосы LSM. Например, дорожка боковой полосы LSM, помимо других потенциально возможных примеров, может использоваться для выполнения квитирования, предшествующего состоянию моделирования звена связи, выхода из состояний управления электропитанием (например, состояния LI). Сигнал боковой полосы LSM может быть асинхронным сигналом, в котором он не выравнивается с данными, действительным сигналом и потоковыми сигналами звена связи, а вместо этого, помимо других примеров, соответствует изменениям состояния сигнализации и выравниванию конечного автомата звена связи между двумя кристаллами или чипами, соединенными звеном связи. Обеспечение выделенной дорожки боковой полосе LSM, помимо других выгод, показанных на примерах, в некоторых примерах позволяет исключить схемы бесшумной настройки и приемные схемы обнаружения аналогового переднего фронта (AFE).

На фиг. 12 показана упрощенная блок-схема 1200, показывающая другое представление логики, используемой при осуществлении MCPL. Например, логический уровень 1110 PHY обеспечивается с помощью определенной логического интерфейса PHY (LPIF) 1205, через который любой из множества различных протоколов (например, PCIe, IDI, QPI и т.д.) 1210, 1215, 1220, 1225 и режимов сигнализации (например, в боковой полосе) может взаимодействовать с физическим уровнем примерной MCPL. В некоторых реализациях логика 1230 мультиплексирования и арбитража может также обеспечиваться как уровень, отдельный от логического уровня 1110 PHY. В одном из примеров LPIF 1205 может обеспечиваться в качестве интерфейса с любой из сторон от этого уровня 1230 MuxArb. Логический уровень 1110 PHY может сопрягаться с физическим уровнем PHY (например, аналоговым передним фронтом (AFE) 1105 MCPL PHY) через другой интерфейс.

LPIF может отделить PHY (логический и электрический/аналоговый) от верхних уровней (например, 1210, 1215, 1220, 1225), так. чтобы мог быть реализован совершенно другой PHY после LPIF, прозрачного для верхних уровней. Это может помочь при стимулировании модульности и повторного использования при проектировании, поскольку, помимо прочего, верхние уровни могут оставаться нетронутыми, когда обновляется базовая технология сигнализации PHY. Дополнительно, LPIF может определить множество сигналов, разрешающих мультиплексирование/ демультиплексирование, управление LSM, обнаружение и обработку ошибок и другие функциональные возможности логического PHY. Например, в таблице 1 обобщается, по меньшей мере, часть сигналов, которые могут быть определены для примера LPIF:

Как видно в таблице 1, в некоторых реализациях механизм выравнивания может обеспечиваться через квитирование AlignReq/AlignAck. Например, когда физический уровень входит в состояние восстановления, некоторые протоколы могут терять кадрирование пакета. Выравнивание пакетов может быть исправлено, например, чтобы гарантировать правильную идентификацию кадрирования посредством уровня звена связи. Дополнительно, как показано на фиг. 13, физический уровень может подтвердить сигнал StallReq, когда вводит восстановление, так что уровень звена связи подтверждает сигнал Stall, когда новый выровненный пакет готов для передачи. Логика физического уровня может сделать выборку как Stall, так и Valid, чтобы определить, выровнены ли пакеты. Например, физический уровень может продолжать запускать trdy, чтобы освобождать пакеты уровня звена связи, пока выборки Stall и Valid не будут подтверждены, помимо других потенциально возможных реализаций, в том числе, других альтернативных реализаций, использующих Valid, чтобы помочь при выравнивании пакетов.

Для сигналов на MCPL могут определяться различные допуски для сбоев. Например, допуски для сбоев могут быть определены для действительных сигналов, потоковых сигналов, LSM боковой полосы, низкочастотной боковой полосы пакетов уровня связи и других типов сигналов. Допуски для сбоев для пакетов, сообщений и других данных, переданных по выделенным дорожкам для данных MCPL, могут быть основаны на конкретном протоколе, управляющем данными. В некоторых реализациях среди других потенциально возможных примеров могут обеспечиваться механизмы обнаружения и обработки ошибок, такие как контроль циклическим избыточным кодом (CRC), буферы повторения. В качестве примеров, для пакетов PCIe, переданных по MCPL, 32-разрядный CRC может быть использован для пакетов уровня транзакции PCIe (TLP) (с гарантированной доставкой (например, через механизм воспроизведения)), и 16-разрядный CRC может быть использован для пакетов уровня звена связи PCIe (которые могут быть построены так, что имеют потери (например, когда воспроизведение не применяется)). Дополнительно, для символов кадрирования PCIe для идентификатора символа может быть определено особое расстояние Хемминга (например, расстояние Хемминга равное четырем (4)); также, помимо прочих примеров, могут использоваться четность и 4-разрядный CRC. Для пакетов IDI, с другой стороны, может использоваться 16-разрядный CRC.

В некоторых реализациях допуски сбоев могут определяться для пакетов уровня звена связи (link layer packet, LLP), которые содержат требование перехода действительного сигнала с низкого уровня на высокий (то есть, с 0 на 1) (например, чтобы помочь в подтверждении бита и блокировки символа). Дополнительно, в одном из примеров, для передачи может быть определено конкретное количество последовательных, идентичных LLP и ответы могут ожидаться на каждый запрос, с повторным запросом запросчика после перерыва, отведенного на ответ, помимо других определенных характеристик, которые могут использоваться в качестве основы определения отказов в данных LLP на MCPL. В дополнительных примерах допуск для отказов может обеспечиваться для действительного сигнала, например, посредством расширения действительного сигнала на все окно периода времени, или символа (например, поддерживая высокий уровень действительного сигнала восьми UI). Дополнительно, помимо прочих примеров, ошибки или отказы в потоковых сигналах могут предотвращаться, поддерживая расстояние Хемминга для значений кодирования потокового сигнала.

Реализации логического PHY могут содержать обнаружение ошибок, отчет об ошибках и логику обработки ошибок. В некоторых реализациях логический PHY примерной MCPL, помимо прочего, может содержать логику для обнаружения ошибок нарушения кадрирования уровня PHY (например, на дорожках для действительных значений и дорожках для потоковых сигналов), ошибок на боковой полосе (например, связанных с переходами состояний LSM), ошибок в LLP (например, которые являются критичными к переходам состояний LSM). Некоторые обнаружения/устранения ошибок, помимо прочего, могут делегироваться логике верхнего уровня, такой как логика PCIe, адаптированная для обнаружения конкретных для PCIe ошибок.

В случае ошибок нарушения кадрирования, в некоторых реализациях один или более механизмов могут обеспечиваться через логику обработки ошибок. Ошибки нарушения кадрирования могут обрабатываться, основываясь на используемом протоколе. Например, в некоторых реализациях уровни звена связи могут информироваться об ошибках, чтобы запустить повторную попытку. Нарушение кадрирование может также вызывать повторное выравнивание нарушения кадрирования логического PHY. Дополнительно, помимо прочего, может выполняться повторное центровка логического PHY и блокировка символа/окна может быть осуществлена повторно. Центровка в некоторых примерах может содержать PHY перемещение фазы тактового сигнала приемника к оптимальной точке, чтобы обнаружить входящие данные. "Оптимальный", в этом контексте, может относиться к тому, где имеется наибольшее поле для шумов и дрожания тактового сигнала. Повторная центровка может содержать упрощенные функции центровки, выполняемые, среди прочего, например, когда PHY выходит из состояния низкого энергопотребления.

Другие типы ошибок могут использовать другие способы обработки ошибок. Например, ошибки, обнаруженные в боковой полосе, могут фиксироваться через механизм задержки соответствующего состояния (например, LSM). Ошибка может регистрироваться и конечный автомат звена связи может затем переключаться состояние Reset. LSM может оставаться в состоянии Reset до тех пор, пока от программного обеспечения не будет принята команда перезапуска. В другом примере ошибки LLP, такие как ошибки пакета управления звена связи, могут быть обработаны с помощью механизма блокировки по времени, который может снова запустить последовательность LLP, если подтверждается, что последовательность LLP не принята.

На фиг. 14А-14С показаны представления примерных битовых отображений на дорожках для данных примерного MCPL для различных типов данных. Например, примерный MCPL может содержать пятьдесят дорожек для данных. На фиг. 14А показано первое битовое отображение примерных 16-байтовых слотов в первом протоколе, таком как IDI, которые могут передаваться по дорожкам для данных внутри символа или окна длиной 8UI. Например, внутри определенного окна длиной 8UI могут передаваться три 16-байтовых слота, в том числе, слот заголовка. В этом примере остаются два байта данных и эти остающиеся два байта могут использоваться битами CRC (например, в дорожках DATA[48] и DATA[49]).

В другом примере на фиг. 14В показан второе примерное битовое отображение данных пакета PCIe, передаваемых по этим пятидесяти дорожкам для данных примерной MCPL. В примере на фиг. 14В 16-байтовые пакеты (например, пакеты PCIe уровня транзакции (TLP) или уровня звена передачи данных (DLLP)) могут передаваться через MCPL. В окне длиной 8UI могут быть отправлены три пакета с остающимися двумя байтами с левой стороны ширины полосы, остающимися неиспользованными внутри окна. Символы кадрирования могут содержаться в этих символах и использоваться для определения местоположения начала и конца каждого пакета. В одном из примеров PCIe кадрирование, используемое в примере на фиг. 14В, может быть таким же, как те символы, которые реализуются для PCIe в 8GT/с.

В еще одном примере на фиг. 14С показано примерное битовое отображение пакетов типа "звено-звено" (например, пакетов LLP), передаваемых через примерную MCPL. LLP могут иметь длину 4 байта каждый и каждый LLP (например, LLPO, LLP1, LLP2 и т.д.) может передаваться четыре раза друг за другом в соответствии с допуском на отказ и обнаружением ошибок внутри примерной реализации. Например, отказ при приеме четырех следующих подряд идентичных LLP может указывать на ошибку. Дополнительно, как для других типов данных, отказ в приеме VALID в продолжающемся временном окне или символа может также указывать на ошибку. В некоторых случаях LLP могут иметь фиксированные слоты. Дополнительно, в этом примере, помимо прочего, неиспользуемые или "запасные" биты в периоде времени байта могут приводить в результате к логическим нулям, передаваемым по двум из пятидесяти дорожек (например, DATA [48-49]).

На фиг. 15 упрощенная схема 1400 переключений конечного автомата звена связи показана вместе с квитированием в боковой полосе, используемым между переключениями состояния. Например, состояние Reset.Idle (например, где выполняется калибровка захвата контура фазовой автоподстройки (PLL)) может переключаться через квитирование в боковой полосе в состояние Reset. Cal (например, при дополнительной калибровке звена связи). Состояние Reset. Cal может переключаться через квитирование в боковой полосе в состояние Reset.ClockDCC (например, где может выполняться коррекция рабочего цикла (DCC) и захват в контуре (DLL) с задержкой захвата). Дополнительное квитирование может выполняться на переходе из состояния Reset.ClockDCC в состояние Reset.Quiet (например, чтобы снять состояние Valid). Чтобы помочь в выравнивании сигнализации на дорожках MCPL, дорожки могут центроваться через состояние Center. Pattern.

В некоторых реализациях, как показано в примере на фиг. 16, во время состояния Center.Pattem передатчик может формировать шаблоны настройки или другие данные. Приемник может формировать свою схему приемника, например, для приема таких шаблонов настройки, устанавливая положение фазового интерполятора и положение vref и устанавливая компаратор. Приемник может непрерывно сравнивать принятые шаблоны с ожидаемыми шаблонами и сохранять результат в регистре. После того, как один набор шаблонов завершен, приемник может давать приращение установке фазового интерполятора, поддерживая vref одним и тем же. Процесс формирования и сравнения испытательного шаблона может продолжаться и новые результаты сравнения могут сохраняться в регистре с помощью процедуры, непрерывно проходящей через все значения фазового интерполятора и через все значения vref. Состояние Center.Quiet может быть введено, когда процесс формирования шаблонов и сравнения полностью закончен. После центрировки дорожек через состояния через Center.Pattem и Center Quiet звена связи, квитирование в боковой полосе (например, используя сигнал боковой полосы LSM на выделенной дорожке боковой полосы LSM звена связи) может быть облегчено, чтобы перейти в состояние Link.Init для инициализации MCPL и разрешения передачи данных через MCPL.

Возвращаясь на мгновение к обсуждению фиг. 15, как отмечено выше, квитирования в боковой полосе могут использоваться для облегчения переключений конечного автомата звена связи между кристаллами или чипами в многокристальной интегральной схеме. Например, сигналы на дорожках в боковой полосе LSM MCPL могут использоваться для синхронизации переключений конечного автомата в кристалле. Например, когда удовлетворяются условия выхода из состояния (например, Reset.Idle), сторона, удовлетворившая эти условия, может подтвердить на своей внешней дорожке LSM SB сигнал в боковой полосе LSM и ожидать от другого удаленного кристалла, когда он достигнет того же самого состояния и подтвердит сигнал в боковой полосе LSM на его дорожке LSM SB. Когда оба сигнала LSM SB подтверждаются, конечный автомат звена связи каждого соответствующего кристалла может переключаться в следующее состояние (например, в состояние Reset.Cal). Можно определить минимальное время перекрытия, в течение которого оба сигналы LSM SB должны поддерживаться подтвержденными до состояния перехода. Дополнительно, может быть определено минимальное время в состоянии покоя, после которого подтверждение LSM SB снимается, чтобы позволить точное обнаружение переключения. В некоторых реализациях каждое переключение конечного автомата звена связи может быть обусловлено и облегчено такими квитированиями LSM SB.