Область техники, к которой относится изобретение

Настоящее раскрываемое изобретение относится в общем к области компьютерных разработок, а более конкретно - к разработке программного обеспечения, включающей в себя координацию взаимозависимых систем с ограничениями.

Уровень техники

Успехи в обработке полупроводников и логическом проектировании позволили увеличить количество логических схем, которое может находиться на устройствах с интегральными схемами. Как следствие этого, конфигурации компьютерных систем эволюционировали от единственной или множественных интегральных схем в системе до множественных ядер, множественных аппаратных потоков обработки и множественных логических процессоров, находящихся на отдельных интегральных схемах, равно как и других интерфейсах, интегрируемых в пределах таких процессоров. Процессор или интегральная схема обычно содержат один физический кристалл процессора, причем этот кристалл процессора может включать в себя любое количество ядер, аппаратных потоков обработки, логических процессоров, интерфейсов, памяти, концентраторов-контроллеров и так далее.

В результате большей возможности вмещать больше вычислительной мощности в меньших по размеру корпусах, выросла популярность малых вычислительных устройств. Количество смартфонов, планшетных компьютеров, ультратонких ноутбуков и другого пользовательского оборудования росло по экспоненте. Однако эти меньшие по размеру устройства полагаются в отношении как хранения данных, так и сложной обработки данных, которая выходит за рамки возможностей этого форм-фактора, на серверы. Следовательно, спрос на рынке высокопроизводительных вычислений (то есть на серверное пространство) также увеличился. Например, в современных серверах обычно имеется не только одиночный процессор с множественными ядрами, но также и множественные физические процессоры (также именуемые как множественные панельки) для увеличения вычислительной мощности. Но по мере того как вместе с количеством устройств в вычислительной системе растут возможности по обработке данных, все более критически важной становится связь между панельками и другими устройствами.

В сущности, межсоединения проделали путь от более традиционных многоотводных шин, которые главным образом имели дело с электрической связью, до архитектур межсоединения, в их полном расцвете, которые облегчают быстрый обмен данными. К сожалению, поскольку от будущих процессоров требуется потреблять данные с еще более высокими скоростями, то соответствующее требование предъявляется и к возможностям существующих архитектур межсоединений.

Краткое описание чертежей

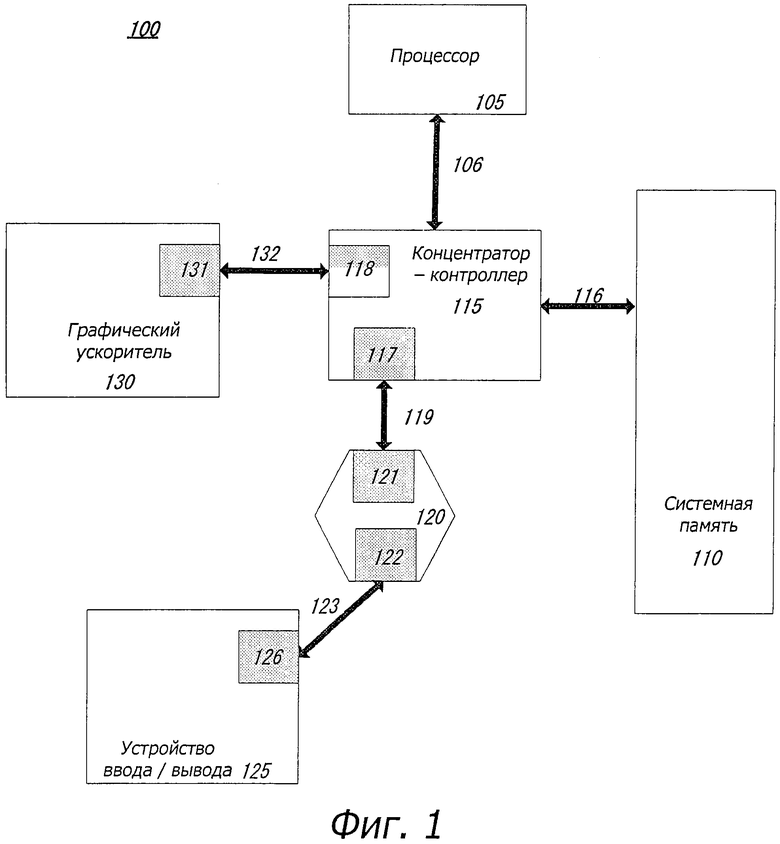

На фиг. 1 проиллюстрирована упрощенная структурная схема системы, включающая в себя двухточечное межсоединение последовательной передачи данных, подсоединяющее устройства ввода-вывода в вычислительной системе в соответствии с одним вариантом реализации изобретения;

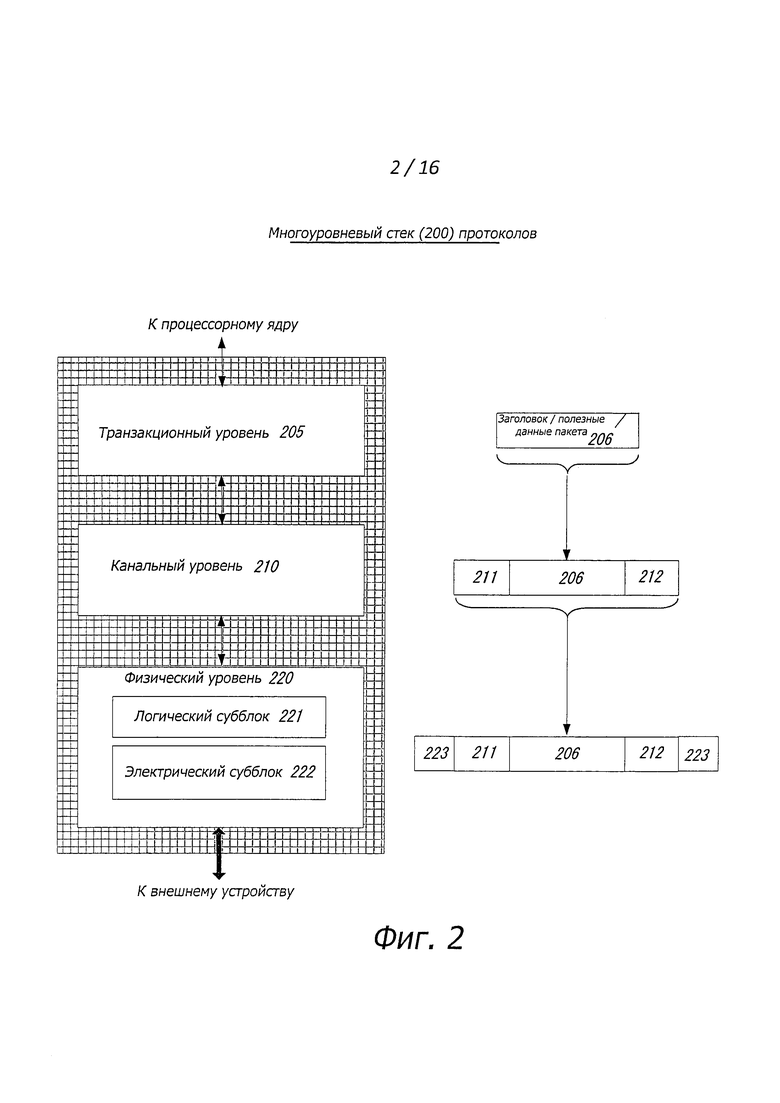

На фиг. 2 проиллюстрирована упрощенная блок-схема многоуровневого стека протоколов, соответствующего одному варианту реализации изобретения;

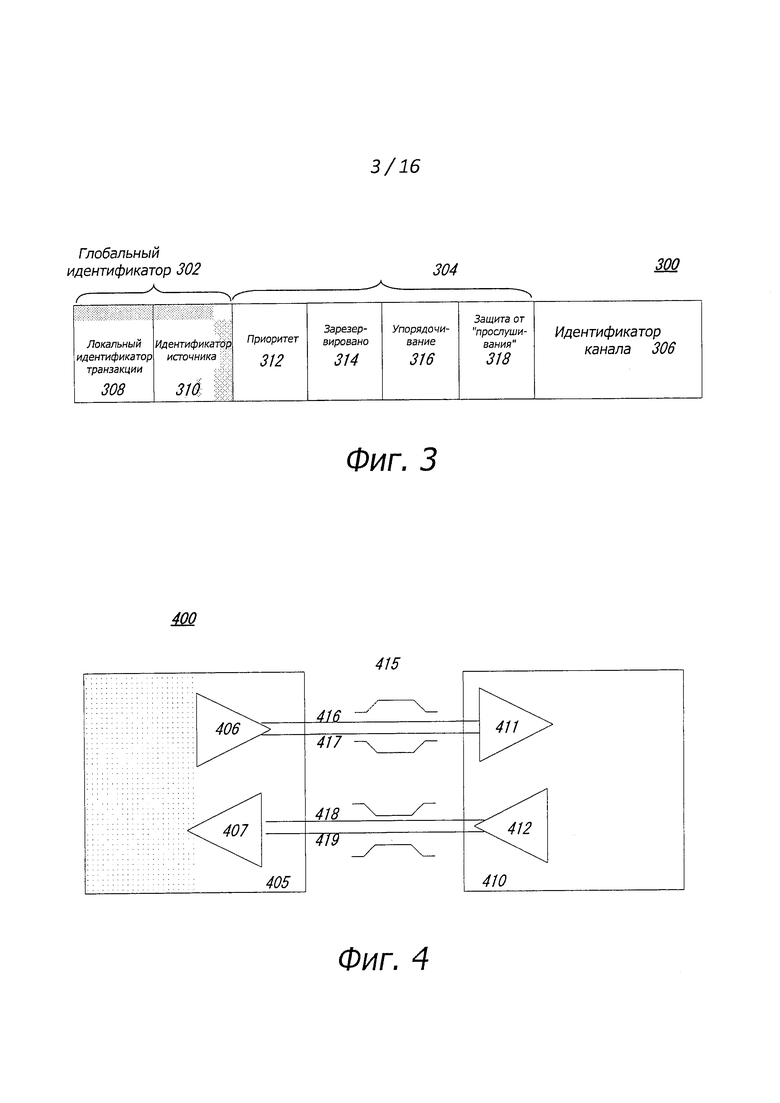

На фиг. 3 проиллюстрирован вариант реализации описателя транзакции.

На фиг. 4 проиллюстрирован вариант реализации двухточечного канала последовательной передачи данных.

На фиг. 5 проиллюстрированы варианты реализации возможных конфигураций системы высокопроизводительных межсоединений (HPI-межсоединений).

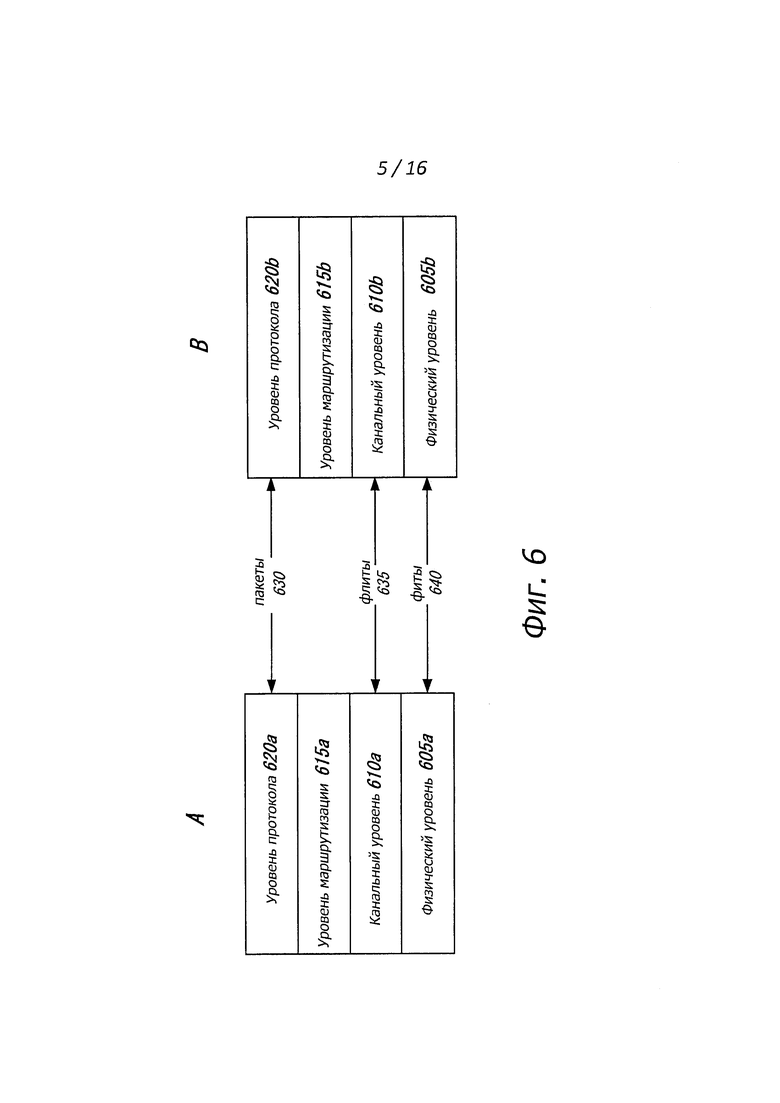

На фиг. 6 проиллюстрирован вариант реализации многоуровневого стека протоколов, связанного с HPI-межсоединением.

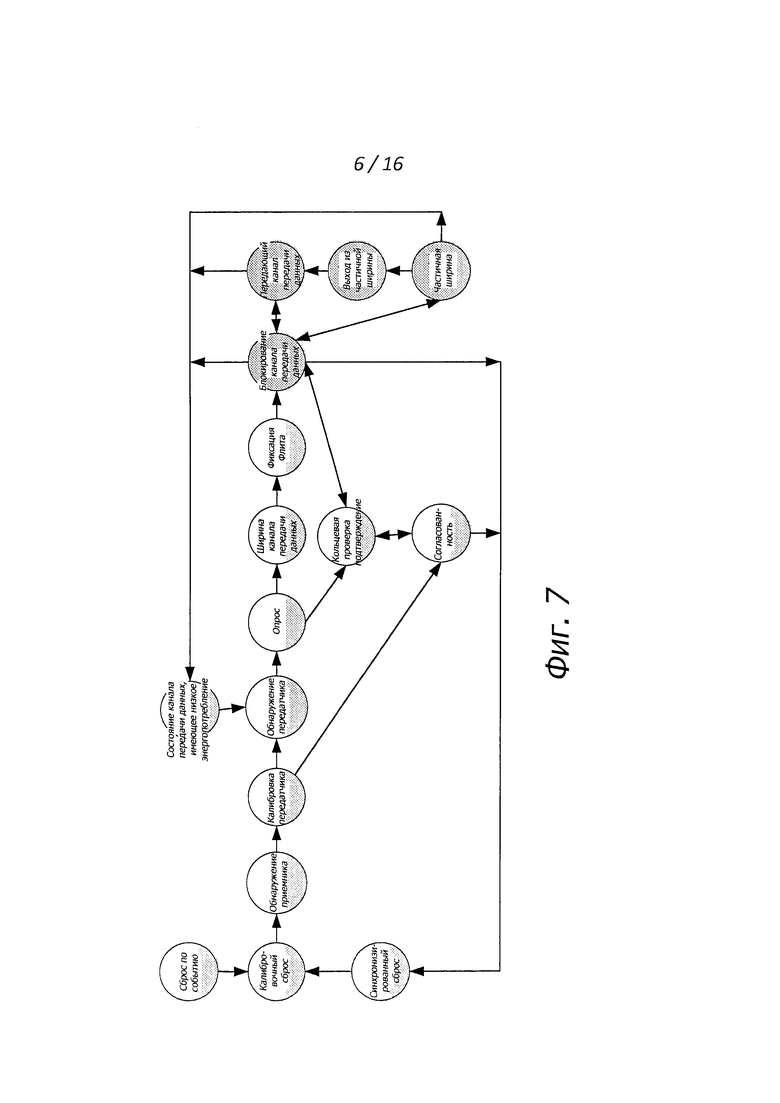

На фиг. 7 проиллюстрировано представление приводимого в качестве примера конечного автомата.

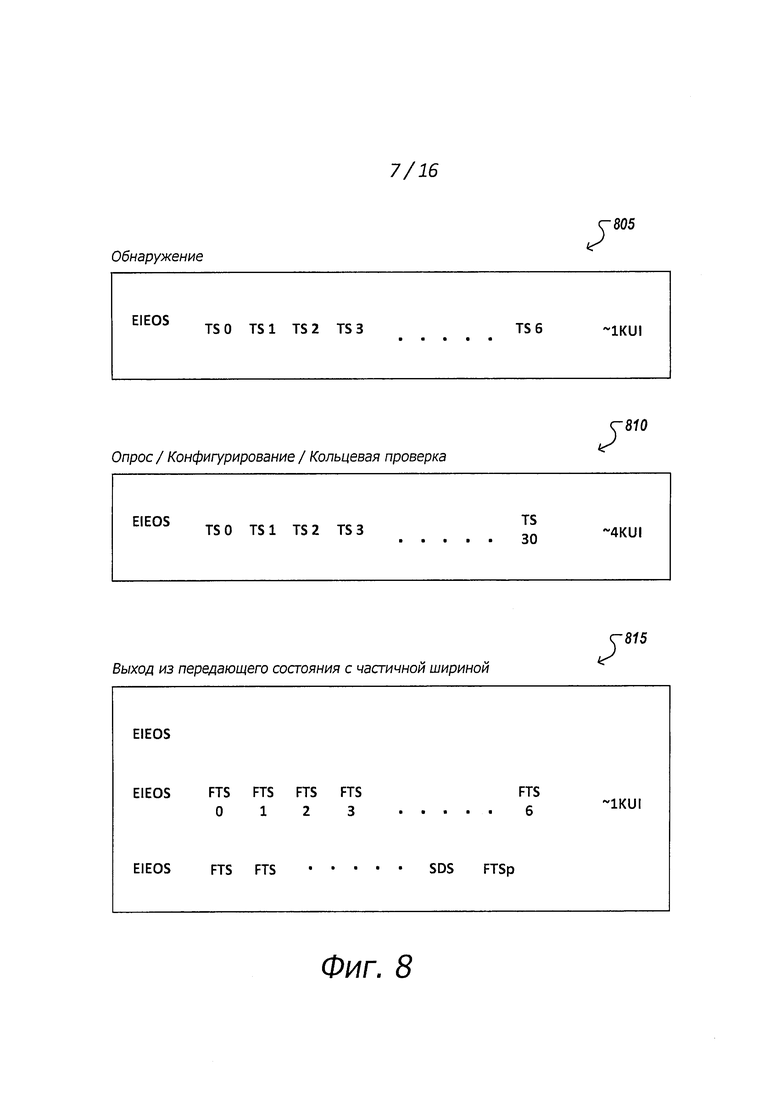

На фиг. 8 проиллюстрированы приводимые в качестве примера управляющие надпоследовательности.

На фиг. 9 проиллюстрирована схема последовательности операций, представляющая приводимое в качестве примера вхождение в передающее состояние с частичной шириной.

На фиг. 10 проиллюстрировано представление приводимого в качестве примера флита, отправленного по приводимому в качестве примера каналу передачи данных, имеющему двадцать путей передачи данных.

На фиг. 11 проиллюстрировано представление приводимого в качестве примера флита, отправленного по приводимому в качестве примера каналу передачи данных, имеющему восемь путей передачи данных.

На фиг. 12 проиллюстрирован вариант реализации структурной схемы для вычислительной системы, включающей в себя многоядерный процессор.

На фиг. 13 проиллюстрирован другой вариант реализации структурной схемы для вычислительной системы, включающей в себя многоядерный процессор.

На фиг. 14 проиллюстрирован вариант реализации структурной схемы для процессора.

На фиг. 15 проиллюстрирован другой вариант реализации структурной схемы для вычислительной системы, включающей в себя процессор.

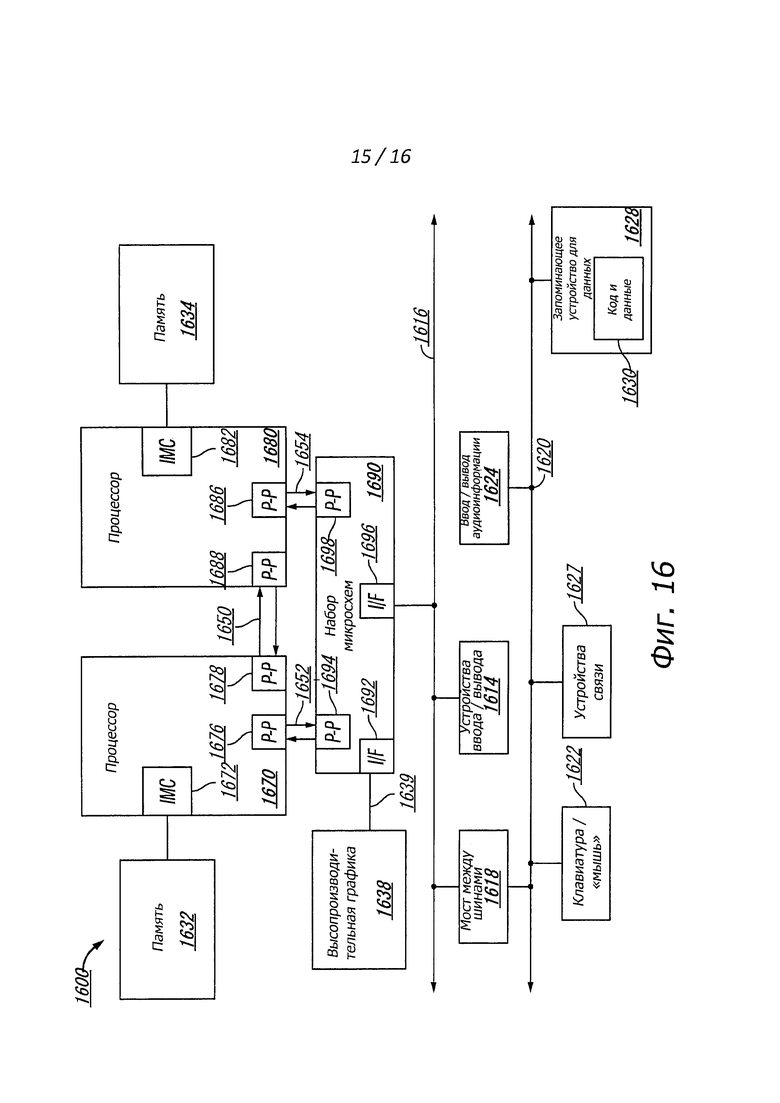

На фиг. 16 проиллюстрирован вариант реализации блока для вычислительной системы, включающей в себя множественные сокеты процессоров.

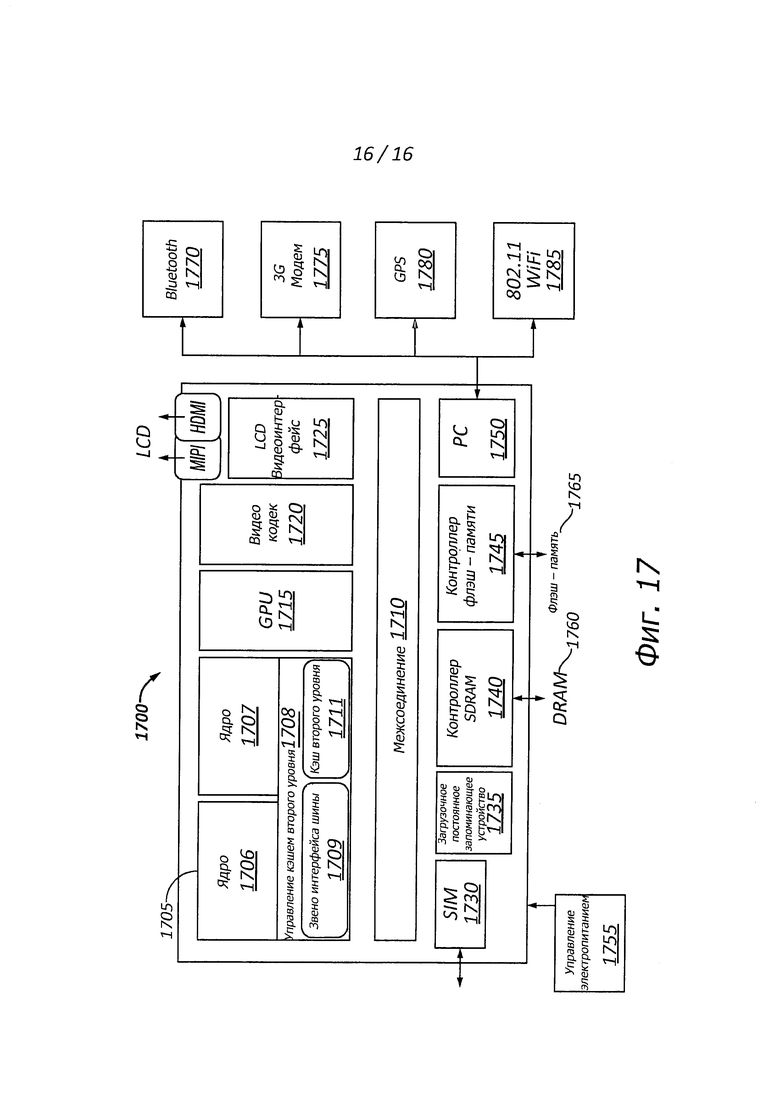

На фиг. 17 проиллюстрирован другой вариант реализации структурной схемы для вычислительной системы.

Одинаковые ссылочные позиции и обозначения на различных чертежах указывают одинаковые элементы.

Подробное описание изобретения

В нижеследующем описании, в целях обеспечения глубокого понимания настоящего изобретения, приводятся многочисленные конкретные подробности, такие как примеры конкретных типов процессоров и конфигураций системы, конкретных конструкций аппаратных средств, конкретных подробностей архитектуры и микроархитектуры, конкретных конфигураций регистров, конкретных типов команд, конкретных компонентов системы, конкретных стадий процессорного конвейера, конкретных слоев внутрисхемных соединений, конкретных конфигураций пакетов/транзакций, конкретных наименований транзакций, обменов данными по конкретным протоколам, конкретных ширин канала передачи данных, конкретных реализаций и функционирования и так далее. Однако специалисту в данной области техники может быть очевидно, что эти конкретные подробности не обязательно должны использоваться для осуществления на практике предмета настоящего раскрываемого изобретения. В других случаях, во избежание излишне затемнения сути настоящего раскрываемого изобретения, не приводится очень детализированное описание известных компонентов или способов, таких как специальные и альтернативные архитектуры процессора, конкретные логические схемы/код для описанных алгоритмов, конкретный микропрограммный код, функционирование межсоединений нижнего уровня, конкретные логические конфигурации, конкретные технологии изготовления и материалы, конкретные реализации компилятора, конкретное выражение алгоритмов в коде, конкретные технология/логика выключения и отпирания и другие подробности функционирования компьютерной системы.

Хотя нижеследующие варианты реализации изобретения могут быть описаны в отношении сохранения энергии, энергетической эффективности, эффективности обработки данных и так далее в специальных интегральных схемах, таких как в вычислительных платформах или микропроцессорах, другие варианты реализации изобретения применимы к другим типам интегральных схем и логических устройств. Технологии и идеи, аналогичные описанным здесь вариантам реализации изобретения, могут быть применены к другим типам схем или полупроводниковых устройств, которые также могут получить пользу от таких характеристик. Например, раскрытые варианты реализации изобретения не ограничены компьютерной системой сервера, настольными компьютерными системами, портативными компьютерами, компьютерами Ultrabooks™ (сверхтонкими "ноутбуками"), но могут также использоваться в других устройствах, таких как карманные устройства, "смартфоны", планшетные компьютеры, другие тонкие "ноутбуки", устройства "систем, встроенных в кристалл" (SOC-систем) и встраиваемые варианты применения. Некоторые примеры карманных устройств включают в себя сотовые телефоны, устройства, поддерживающие интернет-протокол, цифровые фотокамеры, персональные цифровые секретари (PDA) и карманные персональные компьютеры. Здесь, технологии, аналогичные высокопроизводительному межсоединению могут быть применены для того, чтобы повысить производительность (или даже сберечь энергию) в межсоединении с низким энергопотреблением. Встроенные варианты применения обычно включают в себя микроконтроллер, процессор цифровой обработки сигналов (DSP-процессор), внутрикристальную систему, сетевые компьютеры (NetPC (сетевые персональные компьютеры)), телевизионные абонентские приставки, сетевые концентраторы, коммутаторы глобальной сети (WAN) или любую другую систему, которая может выполнять функции и операции, описываемые ниже. Кроме того, описываемые здесь аппараты, способы и системы не ограничены физическими вычислительными устройствами, но могут также относиться к программным оптимизациям для энергосбережения и эффективности. Как можно легко понять из приводимого ниже описания, варианты реализации способов, аппаратов и систем, описываемых здесь (будь то в отношении аппаратных средств, программно-аппаратных средств, программных средств или их сочетания), могут рассматриваться как существенно важные для будущего "зеленой технологии", сбалансированного с соображениями производительности.

По мере развития вычислительных систем компоненты этих систем становятся более сложными. Архитектура межсоединений для сопряжения компонентов и обмена данными между ними также усложняется таким образом, чтобы обеспечивать удовлетворение потребности в ширине полосы пропускания для оптимального функционирования компонентов. Кроме того, различным сегментам рынка требуются, для удовлетворения соответствующего рынка, различные аспекты архитектуры межсоединений. Например, серверам требуется более высокая производительность, в то время как в экосистеме мобильных устройств иногда можно пожертвовать общей производительностью ради сбережения энергии. Тем не менее, единая цель большинства структур заключается в том, чтобы обеспечить максимально возможную производительность при максимальном сбережении энергии. Кроме того, описываемый здесь предмет изобретения может потенциально принести пользу большому разнообразию различных межсоединений.

В соответствии с одним или более принципами, описываемыми здесь среди других примеров, потенциально может быть усовершенствована, среди других примеров, архитектура структуры межсоединения PCIe (Скоростное межсоединение PCI (межсоединение периферийных компонентов)) и архитектура структуры межсоединения QuickPath (межсоединением QPI (Межсоединением тракта быстрой передачи данных)). Например, основная цель межсоединения PCIe заключается в том, чтобы позволить компонентам и устройствам от различных поставщиков взаимодействовать в открытой архитектуре, охватывая множественные сегменты рынка; клиентов (настольные компьютеры и мобильные устройства), серверы (стандартные серверы и серверы предприятий) и встроенные устройства и устройства связи. Межсоединение PCI Express (Скоростное межсоединение периферийных компонентов) представляет собой высокопроизводительное межсоединение ввода-вывода общего назначения, определенное для широкого круга будущих платформ вычисления и связи. Некоторые атрибуты межсоединения PCI, такие как его модели использования, архитектура загрузки-хранения и программируемые интерфейсы, были сохранены при пересмотрах этого стандарта, тогда как существовавшие ранее реализации параллельной шины были заменены значительно расширяемым полностью последовательным интерфейсом. Более свежие версии межсоединения PCI Express используют достижения в области двухточечных межсоединений, технологии на основе переключателя, и пакетизированный протокол для того, чтобы предоставить новые уровни производительности и функциональных возможностей. Среди некоторых из усовершенствованных функциональных возможностей, поддерживаемых межсоединением PCI Express имеются: администрирование энергопотребления, качество обслуживания (QoS), поддержка Hot-Plug/Hot-Swap (подключения устройств без выключения системы/смены устройств без выключения системы), обеспечение целостности данных и обработка ошибок. Хотя основное обсуждение в данном описании относится к новой архитектуре высокопроизводительного межсоединения (HPI-межсоединения), аспекты описываемого здесь изобретения могут быть применены к другим архитектурам межсоединений, таким как PCIe - совместимой архитектуре, QPI - совместимой архитектуре, MIPI - совместимой архитектуре, высокопроизводительной архитектуре или другой известной архитектуре межсоединения.

Обратимся к фиг. 1, на которой проиллюстрирован вариант реализации структуры, составленной из двухточечных каналов передачи данных, которые соединяют между собой некоторый набор компонентов. Система (100) включает в себя процессор (105) и системную память (110), сопряженные с концентратором-контроллером (115). Процессор (105) может включать в себя любой процессорный элемент, такой как микропроцессор, главный процессор, встроенный процессор, сопроцессор или другой процессор. Процессор (105) сопряжен с концентратором-контроллером (115) через управляющую шину (FSB-шину) (106). В одном варианте реализации изобретения FSB-шина (106) представляет собой двухточечное межсоединение последовательной передачи данных, которое описывается ниже. В другом варианте реализации изобретения канал (106) передачи данных включает в себя последовательную, дифференциальную архитектуру межсоединения, которая совместима со стандартом дифференциального межсоединения.

Системная память (110) включает в себя любое запоминающее устройство, такое как оперативное запоминающее устройство (RAM), энергонезависимое (NV) запоминающее устройство или другое запоминающее устройство, доступное для устройств в системе (100). Системная память (110) сопряжена с концентратором-контроллером (115) через интерфейс (116) памяти. Примеры интерфейса памяти включают в себя интерфейс (DDR) памяти с удвоенной скоростью передачи данных, двухканальный интерфейс памяти с удвоенной скоростью передачи данных и интерфейс памяти динамического оперативного запоминающего устройства (DRAM).

В одном варианте реализации изобретения концентратор-контроллер (115) может включать в себя корневой концентратор, корневой комплекс или корневой контроллер, такие как в иерархии межсоединения PCIe. Примеры концентратора-контроллера (115) включают в себя набор микросхем, концентратор-контроллер (МСН) памяти, "северный мост", концентратор-контроллер (ICH) межсоединения, "южный мост" и корневой концентратор-контроллер. Часто термин "набор микросхем" относится к двум физически отдельным концентраторам-контроллерам, например, к концентратору-контроллеру (МСН) памяти, сопряженному с концентратором-контроллером (ICH) межсоединения. Отметим, что имеющиеся в настоящее время системы часто включают в себя концентратор-контроллер (МСН) памяти, интегрированный с процессором (105), в то время как контроллер (115) должен поддерживать связь с устройствами ввода-вывода способом, аналогичным тому, что описан ниже. В некоторых вариантах реализации изобретения, посредством корневого комплекса (115) дополнительно поддерживается одноранговая маршрутизация.

Здесь, концентратор-контроллер (115) сопряжен с переключателем/мостом (120) через канал (119) последовательной передачи данных. Модули (117) и (121) ввода/вывода, которые могут также упоминаться как интерфейсы/порты (117) и (121), могут включать в себя/реализовывать многоуровневый стек протоколов для обеспечения связи между концентратором-контроллером (115) и переключателем (120). В одном варианте реализации изобретения, с переключателем (120) способны сопрягаться множественные устройства.

Переключатель/мост (120) осуществляет маршрутизацию пакетов/сообщений от устройства (125) по восходящему потоку (данных), то есть вверх по иерархии по направлению к корневому комплексу, к концентратору-контроллеру (115), и по нисходящему потоку (данных), то есть вниз по иерархии в направлении от корневого контроллера, от процессора (105) или системной памяти (110) к устройству (125). Переключатель (120), в одном варианте реализации изобретения, упоминается как логический узел множественных виртуальных мостовых устройств "PCI-c-PCI". Устройство (125) включает в себя любое внутреннее или внешнее устройство или компонент, подлежащий сопряжению с электронной системой, такое как устройство ввода/вывода, сетевой интерфейсный контроллер (NIC-контроллер), расширительная плата, процессор обработки звукового сигнала, сетевой процессор, накопитель на жестких магнитных дисках, запоминающее устройство, CD/DVD ROM (постоянное запоминающее устройство на компакт-дисках/универсальных цифровых дисках), монитор, принтер, "мышь", клавиатура, маршрутизатор, портативное запоминающее устройство, устройство Firewire, устройство с универсальной последовательной шиной (USB-шиной), сканер и другие устройства ввода/вывода. Часто в терминологии стандарта PCIe, такого рода устройство упоминается как "конечная точка". Устройство (125) может включать в себя, хотя это особо и не показано, мост (например, мост от PCIe к PCI/PCI - X) для поддержания преемственности или других версий устройств или структур межсоединения, поддерживаемых такими устройствами.

С концентратором-контроллером (115) через канал (132) последовательной передачи данных может также быть сопряжен графический ускоритель (130). В одном варианте реализации изобретения, графический ускоритель (130) сопряжен с концентратором-контроллером (МСН) памяти, который сопряжен с концентратором-контроллером (ICH) межсоединения. Переключатель (120), и, соответственно устройство ввода/вывода (125), в таком случае сопрягаются с концентратором-контроллером (ICH) межсоединения. Модули ввода-вывода (131) и (118) должны также реализовывать многоуровневый стек протоколов для поддержания связи между графическим ускорителем (130) и концентратором-контроллером (115). Аналогично тому, что было сказано выше в отношении концентратора-контроллера (МСН) памяти, сам графический контроллер или графический ускоритель (130) может быть интегрирован в процессор (105).

Обратимся к фиг. 2, на которой проиллюстрирован вариант реализации многоуровневого стека протоколов. Многоуровневый стек (200) протоколов может включать в себя любую форму многоуровневого стека протоколов связи, такую как стек QPI, стек PCIe, стек для межсоединения следующего поколения для высокопроизводительного вычисления (HPI-стек) или другой многоуровневый стек. В одном варианте реализации изобретения, стек (200) протоколов может включать в себя транзакционный уровень (205), канальный уровень (210) и физический уровень (220). Интерфейс, такой как интерфейсы (117), (118), (121), (122), (126) и (131), показанные на фиг. 1, могут быть представлены как стек (200) протоколов связи. Представление в виде стека протоколов связи может также упоминаться как модуль или интерфейс, реализующий/включающий в себя стек протоколов.

Для обмена информацией между компонентами могут использоваться пакеты. Пакеты могут быть сформированы на транзакционном уровне (205) и уровне (210) канала передачи данных для того, чтобы переносить информацию от передающего компонента к принимающему компоненту. Поскольку передаваемые пакеты проходят через другие уровни, то они дополняются дополнительной информацией, используемой для обработки пакетов на этих уровнях. На стороне приема происходит обратный процесс, и пакеты преобразуются из их представления физического уровня (220) в представление уровня канала передачи данных и, наконец (для пакетов транзакционного уровня), в форму, которая может быть обработана на транзакционном уровне (205) принимающего устройства.

В одном варианте реализации изобретения, транзакционный уровень (205) может обеспечивать интерфейс между ядром обработки данных в устройстве и архитектурой межсоединения, такой как уровень (210) канала передачи данных и физический уровень (220). Отметим в этой связи, что основная обязанность транзакционного уровня (205) может включать в себя сборку и разборку пакетов (то есть пакетов транзакционного уровня или TLP-пакетов). Трансляционный уровень (205) может также администрировать управление потоками для TLP-пакетов, основанное на "кредитах" (разрешениях на передачу некоторого количества данных). В некоторых вариантах осуществления изобретения могут, среди других примеров, использоваться "разделенные" транзакции, то есть транзакции с запросом и ответом, разделенными временем, что позволяет каналу передачи данных передавать другой трафик в то время, пока целевое устройство собирает данные для ответа.

Управление потоками, основанное на "кредитах", может быть использовано для того, чтобы реализовывать виртуальные каналы и сети, использующие эту структуру межсоединения. В одном примере, устройство может объявлять некоторое начальное количество "кредитов" для каждого из приемных буферов на транзакционном уровне (205). Внешнее устройство на противоположном конце канала передачи данных, такое как концентратор-контроллер (115), показанный на фиг. 1, может подсчитывать количество "кредитов", потребляемое каждым TLP-пакетом. Транзакция может быть передана в том случае, если транзакция не превышает предел "кредитов". После получения ответа количество "кредита" восстанавливается. Один пример преимущества, среди других потенциальных преимуществ, такой схемы с "кредитами" заключается в том, что время задержки возвращения "кредита" не влияет на производительность, при том условии, что предел "кредитов" не нарушен.

В одном варианте реализации изобретения, четыре транзакционных адресных пространства могут включать в себя адресное пространство конфигурации, адресное пространство памяти, адресное пространство ввода/вывода и адресное пространство сообщений. Транзакции пространства памяти включают в себя один или более запросов чтения и запросов записи для передачи данных в отображенные в памяти места. В одном варианте реализации изобретения, транзакции пространства памяти способны использовать два различных формата адреса, например, короткий формат адреса, такой как 32-разрядный адрес, или длинный формат адреса, такой как 64-разрядный адрес. Транзакции пространства конфигурации могут быть использованы для того, чтобы получать доступ к пространству конфигурации различных устройств, подсоединяемых к межсоединению. Транзакции в отношении пространства конфигурации могут включать в себя запросы чтения и запросы записи. Транзакции пространства сообщений (или просто сообщения) могут также быть определены таким образом, чтобы поддерживать внутриполосную связь между агентами межсоединения. Следовательно, в одном приводимом в качестве примера варианте реализации, транзакционный уровень (205) может осуществлять сборку заголовка/полезных данных (206) пакета.

Быстро рассмотрим фиг. 3, на которой проиллюстрирован приводимый в качестве примера вариант реализации дескриптора пакета транзакционного уровня. В одном варианте реализации изобретения, дескриптор (300) транзакции может представлять собой механизм для передачи информации о транзакции. В этом отношении отметим, что дескриптор (300) транзакции поддерживает идентификацию транзакций в системе. Другие потенциальные варианты использования включают в себя отслеживание изменений упорядочивания транзакции по умолчанию и ассоциативную привязку транзакции к каналам. Например, дескриптор (300) транзакции может включать в себя поле (302) глобального идентификатора, поле (304) атрибутов и поле (306) идентификатора канала. В проиллюстрированном примере поле (302) глобального идентификатора изображено содержащим поле (308) локального идентификатора транзакции и поле (310) идентификатора источника. В одном варианте реализации изобретения, глобальный идентификатор (302) транзакции является уникальным для всех невыполненных запросов.

В соответствии с одним вариантом осуществления изобретения, поле (308) локального идентификатора транзакции представляет собой поле, сгенерированное запрашивающим агентом, и может быть уникальным для всех невыполненных запросов, которые требуют своего завершения для этого запрашивающего агента. Кроме того, в этом примере, идентификатор (310) источника уникальным образом определяет запрашивающего агента в пределах иерархии межсоединений. Соответственно, вместе с идентификатором (310) источника, поле (308) локального идентификатора транзакции обеспечивают глобальную идентификацию транзакции в пределах домена иерархии.

Поле (304) атрибутов определяет характеристики и связи транзакции. В этом отношении отметим, что поле (304) атрибутов потенциально используется для того, чтобы предоставлять дополнительную информацию, которая позволяет изменять обработку транзакций по умолчанию. В одном варианте реализации изобретения, поле (304) атрибутов включает в себя поле (312) приоритета, зарезервированное поле (314), поле (316) упорядочивания и поле (318) защиты от "прослушивания". Здесь, подполе (312) приоритета может быть изменено инициатором для задания приоритета транзакции. Зарезервированное поле (314) атрибутов оставлено зарезервированным для будущего использования или использования, определенного поставщиком оборудования. С использованием зарезервированного поля (314) атрибутов могут быть воплощены возможные модели использования, использующие приоритет или атрибуты секретности.

В этом примере, поле (316) атрибута упорядочивания используется для предоставления дополнительной информации, сообщающей тип упорядочивания, который может изменять правила упорядочивания по умолчанию. В соответствии с одним примером варианта осуществления изобретения, атрибут упорядочивания, составляющий "0", означает то, что должны быть применены правила упорядочивания по умолчанию, тогда как атрибут упорядочивания, составляющий "1", означает смягченное упорядочивание, при котором записи могут обгонять записи в том же самом направлении, а завершения чтения могут обгонять записи в том же самом направлении. Поле (318) атрибута "прослушивания" используется для определения того, не "прослушиваются" ли транзакции. Как показано на фигуре, поле (306) идентификатора канала идентифицирует канал, с которым связана транзакция.

Возвращаясь к обсуждению фиг. 2, отметим, что канальный уровень (210), также именуемый как уровень (210) канала передачи данных, может действовать в качестве промежуточной стадии между транзакционным уровнем (205) и физическим уровнем (220). В одном варианте реализации изобретения, обязанность уровня (210) канала передачи данных заключается в обеспечении надежного механизма для обмена пакетами транзакционного уровня (TLP-пакетами) между двумя компонентами по каналу передачи данных. Одна сторона уровня (210) канала передачи данных принимает TLP-пакеты, собранные на транзакционном уровне (205), применяет идентификатор (211) последовательности пакетов, то есть идентификационный номер или номер пакета, вычисляет и применяет код обнаружения ошибок, то есть циклический избыточный код (212), и представляет измененные TLP-пакеты на физический уровень (220) для передачи на физическом уровне внешнему устройству.

В одном примере, физический уровень (220) включает в себя логический субблок (221) и электрический субблок (222) для физической передачи пакета на внешнее устройство. Здесь, логический субблок (221) ответствен за "цифровые" функции физического уровня (221). В этом отношении отметим, что логический субблок может включать в себя секцию передатчика, предназначенную для подготовки исходящей информации к передаче физическим субблоком (222), и секцию приемника, предназначенную для идентификации и подготовки принятой информации перед передачей ее на канальный уровень (210).

Физический блок (222) включает в себя передатчик и приемник. Логический субблок (221) снабжает передатчик символами, которые трансмиттер преобразовывает в последовательную форму и передает на внешнее устройство. Приемник снабжается преобразованными в последовательную форму символами, поступающими от внешнего устройства, и преобразовывает принятые сигналы в поток битов. Поток битов преобразуется из последовательной формы в параллельную и подается на логический субблок (221). В одном приводимом в качестве примера варианте реализации изобретения используется код передачи 8 битов / 10 битов, при котором передаются/принимаются десятибитовые символы. При этом для того чтобы кадрировать пакет кадрами (223) используются специальные символы. В дополнение к этому, в одном примере приемник также обеспечивает синхронизацию символа, восстанавливаемую из поступающего последовательного потока данных.

Как было сказано выше, хотя в отношении конкретного варианта реализации стека протоколов (такого как стек протоколов стандарта PCIe) рассмотрены транзакционный уровень (205), канальный уровень (210) и физический уровень (220), многоуровневый стек (200) протоколов этим не ограничен. Фактически, любой многоуровневый протокол может быть включен сюда/реализован и наделен обсуждаемыми здесь признаками. В качестве примера, порт/интерфейс, который представлен как многоуровневый протокол, может включать в себя: (1) первый уровень для сборки пакетов, то есть транзакционный уровень; второй уровень для создания последовательности пакетов, то есть канальный уровень; и третий уровень для передачи пакетов, то есть физический уровень. В качестве конкретного примера используется многоуровневый протокол высокопроизводительного межсоединения, который описан в данном описании.

Обратимся далее к фиг. 4, на которой проиллюстрирован приводимый в качестве примера вариант реализации структуры двухточечного канала последовательной передачи данных. Двухточечный канал последовательной передачи данных может включать в себя любой тракт передачи данных, предназначенный для передачи последовательно передаваемых данных. В показанном варианте реализации изобретения, канал передачи данных может включать в себя две сигнальные пары низкого напряжения с дифференциальным возбуждением: передающую пару (406)/(411) и принимающую пару (412)/(407). Соответственно, устройство (405) включает в себя передающую логическую схему (406) для передачи данных на устройство (410) и принимающую логическую схему (407) для приема данных от устройства (410). Другими словами, в состав некоторых вариантов осуществления канала передачи данных входят два передающих тракта, то есть тракты (416) и (417), и два принимающих тракта, то есть тракты (418) и (419).

Термин "тракт передачи данных" относится к любому тракту для передачи данных, такому как линия передачи данных, медная линия, оптическая линия, канал беспроводной связи, канал связи в инфракрасном диапазоне или другой тракт связи. Соединение между двумя устройствами, такими как устройство (405) и устройство (410), именуется как канал передачи данных, такой как канал (415) передачи данных. Канал передачи данных может поддерживать один путь передачи данных - каждый путь передачи данных представляет набор дифференциальных сигнальных пар (одна пара для передачи, одна пара для приема). Для масштабирования ширины полосы пропускания канал передачи данных может объединять множественные пути передачи данных, обозначаемые как xN, где N представляет собой любую поддерживаемую ширину канала передачи данных, такую как 1, 2, 4, 8, 12, 16, 32, 64 или шире.

Дифференциальная пара может относиться к двум трактам передачи данных, таким как линии (416) и (417), для передачи разностных сигналов. В качестве примера, когда линия (416) переключается с низкого уровня напряжения на высокий уровень напряжения, то есть при нарастающем фронте, линия (417) переводится с высокого логического уровня на низкий логический уровень, то есть на падающий фронт. Разностные сигналы потенциально демонстрируют лучшие электрические характеристики, такие как лучшая целостность сигнала, то есть перекрестное взаимодействие, "выброс" напряжения вверх/вниз, "звон", среди других приводимых в качестве примера преимуществ. Это делает возможным лучшее окно синхронизации, которое делает возможным более высокие частоты передачи.

В одном варианте реализации изобретения предлагается новое высокопроизводительное межсоединение (HPI-межсоединение). HPI-межсоединение может включать в себя кэш - когерентное основанное на канале передачи данных межсоединение следующего поколения. В качестве одного примера, HPI-межсоединение может быть использовано на высокопроизводительных вычислительных платформах, таких как рабочие станции или серверы, включая сюда системы, где для соединения процессоров, ускорителей, устройств ввода/вывода и тому подобного обычно используются протокол PCIe (Скоростного межсоединения периферийных компонентов) или другой протокол межсоединения. Однако HPI-межсоединение этим не ограничено. Вместо этого, HPI-межсоединение может быть использовано в любой из описываемых здесь систем или платформ. Кроме того, отдельные разработанные идеи могут быть применены к другим межсоединениям и платформам, таким как PCIe, MIPI, QPI и так далее.

Для поддержания множественных устройств, в одном приводимом в качестве примера варианте осуществления изобретения, HPI-межсоединение может включать в себя агностика архитектуры набора команд (то есть HPI-межсоединение может быть реализовано во множественных различных устройствах). В другом сценарии HPI-межсоединение может также быть использовано для подсоединения высокопроизводительных устройств ввода/вывода, а не только процессоров или ускорителей. Например, высокопроизводительное устройство стандарта PCIe может быть подсоединено к HPI-межсоединению через соответствующий мост преобразования (то есть из HPI в PCIe). Кроме того, каналы передачи данных HPI-межсоединения могут быть использованы многими устройствами, основанными на HPI-межсоединении, такими как процессорами, различными способами (например, звездами, кольцами, многоугольниками и так далее). На фиг. 5 проиллюстрированы приводимые в качестве примера варианты осуществления множественных потенциальных многосортных конфигураций. Двухсокетная конфигурация (505), как изображено на фигуре, может включать в себя два HPI-канала передачи данных (канала передачи данных по HPI-межсоединению); однако в других вариантах осуществления изобретения может использоваться один HPI-канал передачи данных. Для более крупных топологий может быть использована любая конфигурация до тех пор, пока может быть присвоен идентификатор (ID) и есть некоторая форма виртуального тракта, среди других дополнительных признаков или заменяющих признаков. Как показано на фигуре, в одном примере, четырехсокетная конфигурация (510) имеет HPI-канал передачи данных, идущий от каждого процессора к другому. Но на восьмисокетном варианте осуществления изобретения, который показан на конфигурации (515), не каждый сокет напрямую соединен друг с другом через HPI-канал передачи данных. Однако если между процессорами существует некоторый виртуальный тракт или канал, то эта конфигурация поддерживается. Диапазон поддерживаемых процессоров включает в себя 2-32 в собственном домене. Более высокие количества процессоров могут быть достигнуты, среди других примеров, посредством использования множественных доменов или других межсоединений между контроллерами узлов.

Архитектура HPI-межсоединения включает в себя определение многоуровневую архитектуру протоколов, включающую в себя, в некоторых примерах, уровни протоколов (когерентный, некогерентный и, по желанию, другие основанные на памяти протоколы), уровень маршрутизации, канальный уровень и физический уровень. Кроме того, HPI-межсоединение может, среди других примеров, дополнительно включать в себя расширения, связанные с администраторами энергопотребления (такими как звенья управления энергопотреблением (PCU-звенья)), конструкцией для тестирования и отладки (DFT-конструкцией), устранением неисправностей, регистрами, безопасностью. На фиг. 5 проиллюстрирован вариант реализации приводимого в качестве примера многоуровневого стека протоколов HPI-межсоединения. В некоторых вариантах осуществления изобретения, по меньшей мере, некоторые из уровней, проиллюстрированных на фиг. 5, могут быть необязательными. Каждый уровень имеет дело со своим собственным уровнем гранулярности или кванта информации (уровень протокола (605 а, b) - с пакетами, (630), канальный уровень (610 а, b) - с флитами (flit) (635), а физический уровень (605 а, b) - с фитами (phit) (640)). Отметим, что пакет, в некоторых вариантах реализации изобретения, может, основываясь на варианте осуществления, включать в себя неполные флиты, единственный флит или множественные флиты.

В качестве первого примера, ширина фита (640) включает в себя отображение "1 в 1" ширины канала передачи данных на биты (например, 20-битовая ширина канала передачи данных включает в себя фит, составляющий 20 битов, и так далее). Флиты могут иметь больший размер, такой как 184, 192 или 200 битов. Отметим, что если фит (640) имеет ширину 20 битов, а размер флита (635) составляет 184 бита, то для того чтобы передать один флит (635), требуется дробное количество фитов (640) (например, среди других примеров, 9, 2 фитов с 20 битами - для передачи 184-битового флита (635), или 9, 6 при 20 битах - для передачи 192-битового флита). Отметим, что ширина основного канала передачи данных на физическом уровне может варьироваться. Например, количество путей передачи данных, приходящихся на одно направление, может включать в себя 2, 4, 6, 8, 10, 12, 14, 16, 18, 20, 22, 24 и так далее. В одном варианте реализации изобретения, канальный уровень (610 а, b) способен вкладывать в один флит множественные части различных транзакций, и в этот флит могут быть вложены один или множество заголовков (например, 1, 2, 3, 4). В одном примере, HPI-межсоединение разделяет заголовки на соответствующие сегменты для того, чтобы сделать возможными множественные сообщения в флите, предназначенные для различных узлов.

Физический уровень (605 а, b), в одном варианте реализации изобретения, может быть ответственным за быструю передачу информации в физической среде (электрической или оптической и так далее). Физический канал передачи данных может быть двухточечным между двумя объектами канального уровня, такими как уровень (605 а) и (605 b). Канальный уровень (610 а, b) может отделить физический уровень (605 а, b) от верхних уровней и предоставляет возможность надежно передавать данные (равно как и запросы) и администрировать управлением потоками данных между двумя напрямую связанными объектами. Канальный уровень может также быть ответственным за виртуализацию физического канала передачи данных во множественные виртуальные каналы и классы сообщений. Уровень (620 а, b) протокола полагается на канальный уровень (610 а, b) в том, чтобы отображать сообщения протокола на соответствующие классы сообщений и виртуальные каналы перед передачей их на физический уровень (605 а, b) для передачи по физическим каналам передачи данных. Канальный уровень (610 а, b) может поддерживать множественные сообщения, такие как, среди других примеров, запрос, "прослушивание", ответ, обратная запись, некогерентных данных.

Физический уровень (605 а, b) (или PHY-уровень) HPI - межсоединения может быть реализован выше электрического уровня (то есть электрических проводов, соединяющих два компонента) и ниже канального уровня (610 а, b), как это проиллюстрировано на фиг. 6. Физический уровень и соответствующая логика может постоянно находиться на каждом агенте и соединяет канальные уровни на двух агентах (А и В), отделенных друг от друга, (например на устройствах по обеим сторонам канала передачи данных). Местный и удаленный электрические уровни соединены посредством физических сред (например, проводов, проводников, оптической среды и так далее). Физический уровень (605 а, b) в одном варианте реализации изобретения имеет две большие фазы: инициализацию и работу. Во время инициализации соединение непрозрачно по отношению к канальному уровню, и передача сигналов может включать в себя сочетание синхронизированных состояний и событий установления связи. Во время работы, соединение прозрачно по отношению к канальному уровню, и передача сигналов осуществляется на скорости, при этом все пути передачи данных работают вместе как один канал передачи данных. Во время фазы работы, физический уровень транспортирует флиты от агента А агенту В и от агента В агенту А. Это соединение также именуется как канал передачи данных и отделяет некоторые физические аспекты, включая среды, ширину и скорость, от канальных уровней, обмениваясь при этом флитами и данными управления/состояния текущей конфигурации (например, ширины) с канальным уровнем. Фаза инициализации включает в себя младшие фазы, например, опрос, конфигурацию. Фаза работы также включает в себя младшие фазы (например, состояния с администрированием энергопотребления в канале передачи данных).

В одном варианте реализации изобретения, канальный уровень (610 а, b) может быть реализован таким образом, чтобы обеспечивать надежную передачу данных между двумя протоколами или объектами маршрутизации. Канальный уровень может отделять физический уровень (605 а, b) от уровня (620 а, b) протокола, и может быть ответственным за управление потоками данных между двумя агентами (А, В) протокола, и предоставлять сервисы виртуальных каналов уровню протокола (классы сообщений) и уровню маршрутизации (виртуальные сети). Интерфейс между уровнем (620 а, b) протокола и канальным уровнем (610 а) обычно может находиться на пакетном уровне. В одном варианте реализации изобретения, самая малая порция передачи на канальном уровне именуется как флит (flit) с некоторым указанным количеством битов, таким как 192 бита или некоторого другого достоинства. Канальный уровень (610 а, b) полагается на физический уровень (605 а, b) в том, чтобы вместить порцию (фит) передачи на физическом уровне (605 а, b) в порцию (флит) передачи на канальном уровне (610 а, b). В дополнение к этому, канальный уровень (610 а, b) может быть логически разделен на две части, отправитель и приемник. Пара "отправитель/приемник" на одном объекте может быть соединена с парой "приемник/отправитель" на другом объекте. Управление потоками данных часто выполняется на основе как флита, так и пакета. Обнаружение и исправление ошибок также потенциально выполняется на основе уровня флита.

В одном варианте реализации изобретения уровень (615 а, b) маршрутизации может обеспечить гибкий и распределенный способ маршрутизации HPI-транзакций (транзакций HPI-межсоединения) от источника до пункта назначения. Схема является гибкой, поскольку алгоритмы маршрутизации для множественных топологий могут быть указаны посредством программируемых таблиц маршрутизации в каждом маршрутизаторе (программирование в одном варианте реализации изобретения выполняется посредством программно-аппаратных средств, программных средств или их сочетания). Функциональные возможности маршрутизации могут быть распределенными; маршрутизация может быть выполнена посредством ряда этапов маршрутизации, при этом каждый этап маршрутизации определяется посредством просмотра таблицы в маршрутизаторах либо в источнике, промежуточном звене, либо в пункте назначения. Поиск в источнике может быть использован для того, чтобы ввести HPI-пакет (пакет HPI-межсоединения) в структуру HPI-межсоединения. Поиск в промежуточном маршрутизаторе может быть использован для того, чтобы маршрутизировать HPI-пакет от входного порта до выходного порта. Поиск в порту пункта назначения может быть использован для того, чтобы задавать пункт назначения агента HPI-протокола. Отметим, что уровень маршрутизации, в некоторых вариантах осуществления изобретения, может быть тонким, поскольку таблицы маршрутизации и, следовательно, алгоритмы маршрутизации, конкретно не определены техническими требованиями. Это делает возможным гибкость и разнообразие моделей использования, включающих в себя гибкие архитектурные топологии платформ, определяемые при реализации системы. Уровень (615 а, b) маршрутизации полагается на канальный уровень (610 а, b) в обеспечении использования до трех (или более) виртуальных сетей (VN), в одном примере - двух беступиковых виртуальных сетей (VN 0) и (VN 1) с несколькими классами сообщений, определенными в каждой виртуальной сети. На канальном уровне может быть определена совместно используемая адаптивная виртуальная сеть (VNA), но эта адаптивная сеть не может быть непосредственно раскрыта в концепциях маршрутизации, поскольку каждый класс сообщений и виртуальная сеть, могут иметь выделенные ресурсы и гарантированное лидирующее развитие, среди других признаков и примеров.

В некоторых вариантах осуществления, HPI-межсоединение может использовать встроенную синхронизацию. Синхронизирующий сигнал может быть встроен в данные, передаваемые с использованием этого межсоединения. При синхронизирующем сигнале, встроенном в данные, могут быть опущены особые и специально выделенные пути передачи синхронизирующего сигнала. Это может быть полезным, например, поскольку это может позволить выделить большее количество штырьковых контактов в устройстве для передачи данных, особенно в системах, где пространство для штырьковых контактов пользуется большим спросом.

Канал передачи данных может быть установлен между двумя агентами с обеих сторон межсоединения. Агент, отправляющий данные, может быть локальным агентом, а агент, принимающий данные, может быть удаленно расположенным агентом. Оба агента для управления различными аспектами канала передачи данных могут использовать конечные автоматы. В одном варианте реализации изобретения, тракт передачи данных на физическом уровне может передавать флиты с канального уровня на электрический внешний интерфейс. Тракт управления, в одном варианте осуществления изобретения, включает в себя конечный автомат (также именуемый как конечный автомат обучения канала передачи данных или тому подобное). Действия конечного автомата и выходы из состояний могут зависеть от внутренних сигналов, таймеров, внешних сигналов или другой информации. На самом деле, некоторые из состояний, такие как несколько состояний инициализации, могут иметь таймеры для предоставления значения времени ожидания для выхода из некоторого состояния. Отметим, что термин "обнаруживать" в некоторых вариантах реализации изобретения, относится к обнаружению события на обеих ветвях пути передачи данных; но не обязательно одновременно. Однако, в других вариантах реализации изобретения, термин "обнаружить" относится к обнаружению события агентом ссылки. Термин "противодребезговый", в качестве одного примера, относится к устойчивому установлению уровня сигнала. В одном варианте реализации изобретения, HPI-межсоединение поддерживает работу в случае нефункционирующих путей передачи данных. Здесь, в специальных состояниях пути передачи данных могут быть освобождены.

Состояния, определенные в конечном автомате, могут, среди других категорий и подкатегорий, включать в себя состояния сброса, состояния инициализации и рабочие состояния. В одном примере, некоторые состояния инициализации могут иметь вторичный таймер, который используется для того, чтобы выйти из состояния на некотором времени ожидания (по существу аварийное завершение вследствие неудачи в достижении прогресса в состоянии). Аварийное завершение может включать в себя обновление значения регистров, таких как регистра состояния. Некоторые состояния могут также иметь первичный таймер (первичные таймеры), которые используются для синхронизации основных функций в состоянии. Другие состояния могут быть определены, среди других примеров, таким образом, чтобы внутренние или внешние сигналы (такие как протоколы установления связи) переводили транзакцию из состояния в другое состояние.

Конечный автомат может также поддерживать отладку на одном этапе, фиксацию параметров системы при аварийном прекращении инициализации и использование тестеров. При этом выходы из состояний могут быть отложены/задержаны до тех пор, пока не будут готовы программные средства отладки. В некотором случае, выход может быть отложен/задержан до вторичного времени ожидания. Действия и выходы, в одном варианте реализации изобретения, могут быть основаны на обмене обучающими последовательностями. В одном варианте реализации изобретения, конечный автомат ссылки должен работать в локальном домене часов агента, и переход из одного состояния в следующее должно совпадать с границей обучающей последовательности. Для отражения текущего состояния могут быть использованы регистры состояний.

На фиг. 7 проиллюстрировано представление, по меньшей мере, части конечного автомата, используемого агентами на одном приводимом в качестве примера HPI-межсоединении. Следует понимать, что состояния, включенные в состав таблицы состояний, приведенной на фиг. 7, включают в себя неисчерпывающий перечень возможных состояний. Например, некоторые переходы не приводятся для того, чтобы упростить схему. Кроме того, некоторые состояния могут быть объединены, разделены или опущены, в то время как другие могли бы быть добавлены. Такие состояния могут включать в себя:

Состояние сброса по событию: наступает при событии "теплого" или "холодного" сброса. Восстанавливает значения "по умолчанию". Инициализирует счетчики (например, счетчики синхронизации). Может выйти в другое состояние, такое как другое состояние сброса.

Синхронизированное состояние сброса: синхронизированное состояние для внутриполосного сброса. Может приводить в действие предварительно определенный электрический упорядоченный набор (EOS-набор), так что удаленные приемники способны обнаружить этот EOS-набор и также войти в состояние синхронизированного сброса. Приемник имеет пути передачи данных, поддерживающие электрические настройки. Может осуществляться выход на агента для калибровочное состояния сброса.

Калибровочное состояние сброса: калибровка без передачи сигналов по путям передачи данных (например, состояние калибровки приемника) или выключения драйверов. Может быть некоторое предварительно заданное количество времени в состоянии, основанном на таймере. Может задавать рабочую скорость. Может действовать в качестве состояния ожидания, когда порт не разблокирован. Может включать в себя минимальное время пребывания (в этом состоянии). Может происходить основанное на конструкции подготовка приемника к работе или отключение расстройки. Может осуществляться выход в состояние обнаружения приемника после некоторого времени ожидания и/или завершения калибровки.

Состояние обнаружение приемника: обнаружение присутствия приемника на пути (путях) передачи данных. Может осуществляться поиск завершения работы приемника (например, введения отбоя приемника). Может осуществлять выход в калибровочное состояние сброса после установки некоторого указанного значения или когда другое указанное значение не установлено. Если приемник обнаружен или время ожидания достигнуто, то может осуществляться выход в состояние калибровки передатчика.

Состояние калибровки передатчика: для калибровок передатчика. Может представлять собой синхронизированное состояние, выделенное для калибровок передатчика. Может включать в себя передачу сигналов по пути передачи данных. Может непрерывно приводить в действие EOS-набор, такой как электрический упорядоченный набор выхода из простоя (EIEOS-набор). Когда калибровка выполнена, или при истечении времени на таймере может осуществляться выход в состояние согласованности. Если истекло значение счетчика или прошло вторичное время ожидания, то может осуществляться выход в состояние обнаружения передатчика.

Состояние обнаружения передатчика: определяется правильность передачи сигналов. Может представлять собой состояние установления связи, при котором агент завершает действия и осуществляет выход в следующее состояние, основываясь на сигналах удаленного агента. Правильность передачи сигналов из передатчика может определять приемник. Приемник, в одном варианте реализации изобретения, осуществляет поиск сигнала обнаружения "пробуждения", и если тот подвергся противодребезговой обработке на одном или более путях передачи данных, то ищет его на других путях передачи данных. Передатчик порождает сигнал обнаружения. В ответ на завершение противодребезговой обработки для всех путей передачи данных и/или времени ожидания или, если противодребезговая обработка на всех путях передачи данных не завершена и есть время ожидания, может осуществляться выход в состояние опроса. При этом один или более контрольных путей передачи данных могут бодрствовать для противодребезговой обработки сигнала пробуждения. И если они свободны от дребезжания, тогда другие пути передачи данных потенциально являются свободными от дребезжания. Это может сделать возможным сбережение энергии в состояниях низкого энергопотребления.

Состояние опроса: приемник настраивает, инициализирует буфер сдвига и захватывает биты/байты (например, идентифицирует границы символов). Пути передачи данных могут быть выровнены. В ответ на подтверждающее сообщение удаленный агент может вызвать выход в следующее состояние (например, состояние ширины канала передачи данных). Опрос может дополнительно включать в себя синхронизацию обучающей последовательности посредством синхронизации по EOS-набору и заголовку обучающей последовательности. Расфазировка между путями передачи данных на удаленном передатчике может быть покрыта на первой длине для максимальной скорости и второй длине для медленной скорости. Выравнивание может быть выполнено в медленном режиме, так же как и в рабочем режиме. Приемник может иметь специальный максимум для выравнивания расфазировки между путями передачи данных, такой как 8, 16 или 32 интервалов расфазировки. Действия приемника могут включать в себя фиксацию времени задержки. Действия приемника, в одном варианте реализации изобретения, могут быть завершены при успешном выравнивании действующей карты путей передачи данных. Успешное установление связи может быть достигнуто, в одном примере, тогда, когда некоторое количество следующих друг за другом заголовков обучающих последовательностей приняты с подтверждениями, и некоторое количество обучающих последовательностей с подтверждением переданы после того, как приемник завершил свои действия.

Состояние ширины канала передачи данных: агент поддерживает связь с окончательной картой путей передачи данных, ведущей к удаленному передатчику. Приемник принимает информацию и декодирует ее. Приемник может записать сконфигурированную карту путем передачи данных в структуру после контрольной точки предшествующего значения карты путей передачи данных во второй структуре. Приемник может также ответить подтверждением ("АСК"). Может инициировать внутриполосный сброс. В качестве одного примера, первое состояние внутриполосного сброса. В одном варианте реализации изобретения, выход в следующее состояние, такое как состояние конфигурации флита, выполняется в ответ на это подтверждение. Кроме того, перед входом в состояние с низким энергопотреблением, если частота появления сигнала обнаружения пробуждения падает ниже некоторого указанного значения (например, 1 на каждое количество единичных интервалов (UI-интервалов), такое как 4 тысячи единичных интервалов), то также может быть сгенерирован сигнал сброса. Приемник может сохранять текущую и предшествующую карту путей передачи данных. Передатчик может использовать различные группы путей передачи данных, основываясь на обучающих последовательностях, имеющих различные значения. Карта путей передачи данных, может, в некоторых вариантах реализации изобретения, не изменять некоторые регистры состояния.

Состояние конфигурации фиксации флита: вхождение в него осуществляется передатчиком, но это состояние считается покинутым (то есть, режим вторичного времени ожидания), когда как передатчик, так и приемник осуществили выход в состояние блокирования канала передачи данных или другое состояние канала передачи данных. Выход передатчика в состояние канала передачи данных, в одном варианте реализации изобретения, включает в себя границу начала последовательности данных (SDS) и обучающей последовательности (TS-последовательности) после получения сигнала планетарного выравнивания. При этом выход приемника может основываться на приеме SDS от удаленного передатчика. Это состояние может быть мостом от агента к состоянию канала передачи данных. Приемник идентифицирует SDS. Приемник может осуществить выход в состояния блокирования канала передачи данных (BLS-состояние) (или окно управления), если SDS принято после того, как инициализирован дескремблер. Если имеет место время ожидания, то выход может быть в состояние сброса. Передатчик управляет путями передачи данных посредством сигнала конфигурации. Выход передатчика может быть выполнен в сброс, BLS-состояние или другие состояния, основываясь на условиях или временах ожидания.

Передающее состояние канала передачи данных: состояние канала передачи данных. Флиты отправляются удаленному агенту. Может быть введено из состояния блокирования канала передачи данных и возвращается в состояние блокирования канала передачи данных при некотором событии, таком как время ожидания. Передатчик передает флиты. Приемник принимает флиты. Также может осуществляться выход в состояние канала передачи данных, имеющее низкое энергопотребление. В некоторых вариантах осуществления изобретения, передающее состояние канала передачи данных (TLS-состояние) может упоминаться как состояние L0.

Состояние блокирования канала передачи данных: состояние канала передачи данных. Передатчик и приемник работают объединенным образом. Может представлять собой синхронизированное состояние, в течение которого флиты канального уровня удерживаются, в то время как информация физического уровня передается удаленному агенту. Может осуществляться выход в состояние канала передачи данных, имеющее низкое энергопотребление (или другое состояние канала передачи данных, основанное на конструкции). Состояние блокирования канала передачи данных (BLS-состояние), в одном варианте реализации изобретения, имеет место периодически. Этот период именуется как интервал BLS-состояния и может быть синхронизирован, равно как и может различаться между медленной скоростью и рабочей скоростью. Отметим, что канальный уровень может периодически быть блокирован от отправки флитов, так чтобы могла быть отправлена управляющая последовательность физического уровня, имеющая некоторую длину, такая как в течение передающего состояния канала передачи данных или передающего состояния канала передачи данных, имеющего частичную ширину. В некоторых вариантах осуществления изобретения, состояние блокирования канала передачи данных (BLS-состояние) может упоминаться как состояние L0-управления, или состояние L0c.

Состояние канала передачи данных, имеющее частичную ширину: состояние канала передачи данных. Может сберегать энергию благодаря вхождению в состояние с частичной шириной. В одном варианте реализации изобретения асимметричная частичная ширина относится к каждому направлению двунаправленного канала передачи данных, имеющего различные ширины, которые могут поддерживаться в некоторых конструкциях. Пример инициатора, такого как передатчик, отправляющего указание частичной ширины, для вхождения в состояние канала передачи данных, имеющее частичную ширину, показан в примере, приведенном на фиг. 14. При этом указание частичной ширины отправляют, передавая по каналу передачи данных, имеющему первую ширину, для перехода этого канала передачи данных к передаче со второй, новой шириной. Несоответствие может привести к сбросу. Отметим, что скорости не могут быть изменены, но ширина может. Следовательно, флиты потенциально отправляются с различными ширинами. Может быть логически аналогичным передающему состоянию канала передачи данных; и все же, поскольку ширина меньше, то может потребоваться большее время для передачи флитов. Может осуществляться выход в другие состояния канала передачи данных, такие как состояние канала передачи данных, имеющее низкое энергопотребление, - на основе некоторых принятых и отправленных сообщений, или выход из передающего состояния канала передачи данных, имеющего частичную ширину, или из состояния блокирования канала передачи данных, основанный на других событиях. В одном варианте реализации изобретения, передающий порт может выключать бездействующие пути передачи данных в шахматном порядке для того, чтобы обеспечить лучшую целостность сигнала (то есть уменьшение шума). При этом, во время периодов, в которые изменяется ширина канала передачи данных, может использоваться флиты, способные не подвергаться повторной передаче, такие как нулевые флиты. Соответствующий приемник может отбрасывать эти нулевые флиты и выключать бездействующие пути передачи данных в шахматном порядке, так же как и записывать в одну или несколько структур текущую и предшествующую карту путей передачи данных. Отметим, что состояние и связанный с ним регистр состояния могут оставаться неизменными. В некоторых вариантах осуществления изобретения передающее состояние канала передачи данных, имеющее частичную ширину, может упоминаться как частичное состояние L0 или состояние L0p.

Состояние выхода из передающего состояния канала передачи данных, имеющего частичную ширину: выход из состояния с частичной шириной. В некоторых вариантах осуществления изобретения может использовать или может не использовать состояние блокирования канала передачи данных. Передатчик инициирует выход, в одном варианте реализации изобретения, отправляя комбинации выхода из состояния с частичной шириной по бездействующим путям передачи данных для того, чтобы осуществить "обучение" и выравнивание для этих путей. В качестве одного примера, комбинация выхода начинается с EIEOS набора, который обнаруживают и освобождают от дребезжания, для сигнализирования о том, что путь передачи данных готов начать вхождение в полное передающее состояние канала передачи данных, и может заканчиваться сигналом SDS или быстрой обучающей последовательностью (FTS-последовательностью) на бездействующих путях передачи данных. Любой сбой во время последовательности выхода (действия приемника, такие как выравнивание, не завершенные до времени ожидания) останавливают передачу флитов канальному уровню, и заявляют сброс, который обрабатывается посредством осуществления сброса канала передачи данных при следующем возникновении состояния блокирования канала передачи данных. SDS может также задавать скремблеру/дескремблеру на путях передачи данных надлежащие значения.

Состояние канала передачи данных, имеющее низкое энергопотребление: является состоянием с низким энергопотреблением. В одном варианте реализации изобретения, оно имеет более низкое энергопотребление, чем состояние канала передачи данных, имеющее частичную ширину, поскольку передача сигналов в этом варианте реализации изобретения прекращается на всех путях передачи данных и в обоих направлениях. Для запроса состояния канала передачи данных, имеющего низкое энергопотребление, передатчики могут использовать состояние блокирования канала передачи данных. При этом, приемник может декодировать запрос и ответить подтверждением (АСК) или отрицательным квитированием (NAK); в ином случае может быть запущен сброс. В некоторых вариантах осуществления изобретения, состояние канала передачи данных, имеющее низкое энергопотребление, может упоминаться как состояние L1.

В некоторых вариантах осуществления изобретения, переходы из одного состояния в другое состояние могут быть облегчены таким образом, чтобы позволить обходить состояния, например, в случае, когда действия состояний, осуществляемые в этих состояниях, такие как некоторые калибровки и конфигурирования, были уже выполнены. Результаты и конфигурации предшествующего состояния канала передачи данных могут быть сохранены и повторно использоваться в последующих инициализациях и конфигурациях канала передачи данных. Вместо того, чтобы повторять такие конфигурации и действия состояний, соответствующие состояния можно обойти. Однако, традиционные системы, осуществляющие обходы состояний, часто воплощают сложные конструкции и дорогие переходы с оценкой. Вместо того, чтобы использовать традиционный обход, в одном примере, HPI-межсоединение может использовать короткие таймеры в некоторых состояниях, таких как те, в которых действия состояния не должны повторяться. Это, среди других потенциальных преимуществ, может потенциально сделать возможным более однородные и синхронизированные переходы конечного автомата.

В одном примере, контроллер, основанный на программном обеспечении, (например, через внешнюю точку управления для физического уровня) может сделать возможным короткий таймер для одного или более конкретных состояний. Например, для состояния, для которого действия были уже выполнены и сохранены, состояние может быть сокращено во времени для того, чтобы облегчить быстрый выход из этого состояния в следующее состояние. Однако если действие предшествующего состояния не удалось или не может быть применено в пределах короткой продолжительности таймера, то может быть выполнен выход из состояния. Далее, контроллер может блокировать короткий таймер, например, когда действия состояния должны быть выполнены снова. Длинный, или задаваемый по умолчанию, таймер может быть установлен для каждого соответствующего состояния. Если конфигурационные действия в состоянии не могут быть завершены в пределах длинного таймера, то может произойти выход из состояния. Длинный таймер может быть установлен на некоторую разумную продолжительность для того, чтобы позволить завершение действий состояния. В противоположность этому, короткий таймер может быть значительно более коротким, что в некоторых случаях, делает невозможным выполнение действий состояния без повторного обращения, среди других примеров, к ранее выполненным действиям состояния.

В некоторых вариантах осуществления HPI-межсоединения, могут быть определены надпоследовательности, причем каждая надпоследовательность соответствует соответствующему состоянию или входу в соответствующее состояние / выходу из него. Надпоследовательность может включать в себя повторяющуюся последовательность наборов данных и символов. Эти последовательности в некоторых случаях могут повторяться, среди других примеров, до завершения состояния или перехода из одного состояния в другое состояние, или сообщения о соответствующем событии. В некоторых случаях, повторяющаяся последовательность надпоследовательности может повторяться в соответствии с некоторой определенной частотой, такой как определенное количество единичных интервалов (UI-интервалов). Единичный интервал (UI) может соответствовать интервалу времени для передачи одного бита по пути передачи данных в канале передачи данных или системе. В некоторых вариантах осуществления изобретения, повторяющаяся последовательность может начинаться с электрически упорядоченного набора (EOS-набора). Соответственно, можно ожидать, что экземпляр EOS-набора будет повторяться в соответствии с некоторой предварительно заданной частотой. Такие упорядоченные наборы могут быть реализованы, среди других примеров, как определенные 16-байтовые коды, которые могут быть представлены в шестнадцатеричном формате. В одном примере, EOS-набор надпоследовательности может представлять собой электрический упорядоченный набор простоя (или EIEIOS-набор). В одном примере, EIEOS-набор может напоминать низкочастотный синхронизирующий сигнал (например, предварительно заданное количество повторения шестнадцатеричных символов FF00 или FFF000 и так далее). За EOS-набором может следовать некоторый предварительно заданный набор данных, такой как некоторое предварительно заданное количества обучающих последовательностей или других данных. Такие надпоследовательности могут быть использованы, среди других примеров, при переходах из одного состояния в другое состояние, включающих в себя переходы из одного состояния в другое состояние канала передачи данных, так же как и при инициализации.

Как было представлено выше, инициализация, в одном варианте реализации изобретения, может быть выполнена первоначально на медленной скорости, вслед за чем следует инициализация на быстрой скорости. Инициализация на медленной скорости использует для регистров и таймеров значения "по умолчанию". После этого программные средства используют канал передачи данных на медленной скорости для настройки регистров, таймеров и электрических параметров и очищают калибровочные семафоры для того, чтобы проложить путь для инициализации на быстрой скорости. В качестве одного примера, инициализация может состоять из таких состояний или задач, как сброс, обнаружение, опрос и конфигурирования, среди потенциально других состояний или задач.

В одном примере, блокирующая управляющая последовательность канального уровня (то есть, состояние блокирования канала передачи данных (BLS-состояние) или состояние L0c) может включать в себя синхронизированное состояние, в течение которого флиты канального уровня, удерживаются, в то время как информация PHY-уровня передается удаленному агенту. При этом передатчик и приемник могут запустить таймер управляющей последовательности блокирования. И после истечения времени таймеров, передатчик и приемник могут выйти из состояния блокирования и могут предпринять другие действия, такие как выход в сброс, выход в другие состояния канала передачи данных (или другое состояние), включающие в себя состояния, которые позволяют отправку флита по этому каналу передачи данных.

В одном варианте реализации изобретения, может быть обеспечено "обучение" канала передачи данных и оно может включать в себя отправку одного или больше скремблированных обучающих последовательностей, упорядоченных наборов и управляющих последовательностей, таких как в связи с определенной надпоследовательностью. Символ обучающей последовательности может включать в себя одно или более из числа: заголовка, зарезервированных участков, целевого времени задержки, номера пары, код карты физических путей передачи данных опорный путь передачи данных или группа путей передачи данных, и состояния инициализации. В одном варианте реализации изобретения, заголовок, среди других примеров, может быть отправлен с подтверждением или отрицательным квитированием. В качестве примера, обучающие последовательности могут быть отправлены как часть надпоследовательностей и могут быть скремблированы.

В одном варианте реализации изобретения, упорядоченные наборы и управляющие последовательности не скремблируются или сдвигаются и передаются одинаковым образом, одновременно и полностью по всем путям передачи данных. Правильный прием упорядоченного набора может включать в себя проверку по меньшей мере части упорядоченного набора (или всего упорядоченного набора для частичных упорядоченных наборов). Упорядоченные наборы могут включать в себя электрически упорядоченный набор (EOS-набор), такой как электрический упорядоченный набор простоя (EIOS-набор) или EIEOS-набор. Надпоследовательность может включать в себя начало последовательности данных (SDS) или Быструю обучающую последовательность (FTS-последовательность). Такие наборы и управляющие надпоследовательности могут быть предварительно заданными и могут иметь любую структуру или шестнадцатеричное представление, так же как и любую длину. Например, упорядоченные наборы и надпоследовательности могут иметь длину, составляющую 8 байтов, 16 байтов или 32 байта и так далее. FTS-последовательность, в качестве примера, может дополнительно использоваться для быстрого захвата бита во время выхода из передающего состояния канала передачи данных, имеющего частичную ширину. Отметим, что формирование определение FTS-последовательности может быть по пути передачи данных и может использовать повернутую версию FTS-последовательности.

Надпоследовательности, в одном варианте реализации изобретения, могут включать в себя введение EOS-набора, такого как EIEOS-набор, в поток обучающей последовательности. Когда начинается передача сигналов, электропитание путей передачи данных, в одном варианте осуществления изобретения, включается в шахматном порядке. Однако это может в результате привести к тому, что начальные надпоследовательности будут выглядеть усеченными в приемнике на некоторых путях передачи данных. Надпоследовательности могут быть повторены, однако, через короткие интервалы времени (например, приблизительно одну тысячу единичных интервалов (или ~1 KUI)). Обучающие надпоследовательности могут дополнительно использоваться для одного или более из числа: выравнивания конфигурирования, и для сообщения объекта инициализации, карты путей передачи данных и так далее. EIEOS-набор может использоваться, среди других примеров, для одного или более из числа: перевода пути передачи данных из неактивного в активное состояние, отбора хороших путей передачи данных, идентификации границ символа и TS-последовательности (обучающей последовательности).

Обратимся к фиг. 8, на которой показаны представления приводимых в качестве примера надпоследовательностей. Например, может быть определена приводимая в качестве примера надпоследовательность (805) обнаружения. Надпоследовательность (805) обнаружения может включать в себя повторяющуюся последовательность, состоящую из единственного EIEOS-набора (или другого EOS-набора) сопровождаемого некоторым предварительно заданным количеством экземпляров некоторой конкретной обучающей последовательности (TS-последовательности). В одном примере, EIEOS-набор может быть передан, непосредственно сопровождаемым семью повторенными экземплярами TS-последовательности. Когда последние из семи TS-последовательностей отправлены, EIEOS может быть отправлен снова сопровождаемый семью дополнительными экземплярами TS-последовательности и так далее. Эта последовательность может повторяться в соответствии с некоторой конкретной предварительно заданной частотой. В примере, приведенном на фиг. 8, EIEOS-набор может повторно появляться на путях передачи данных приблизительно один раз на каждую тысячу UI-интервалов (~1 KUI) сопровождаемый остальной частью надпоследовательности (805) обнаружения. Приемник может контролировать пути передачи данных на присутствие повторения надпоследовательности (805) обнаружения, и после проверки надпоследовательности (705) может прийти к заключению о том, что удаленный агент присутствует, был добавлен (например, подключен без выключения системы) на путях передачи данных, "пробудился" или повторно инициализируется и так далее.

В другом примере, может быть определена другая надпоследовательность (810) для указания условия или состояния опроса, конфигурирования или кольцевой проверки. Как и в случае с примером надпоследовательности (805) обнаружения, пути передачи данных канала передачи данных могут контролироваться приемником для такого рода надпоследовательности (810) опроса/конфигурирования/кольцевой проверки для того, чтобы идентифицировать состояние опроса, состояние конфигурирования или состояние или условия кольцевой проверки. В одном примере, надпоследовательности (810) опроса/конфигурирования/кольцевой проверки может начинаться с EIEOS-набора, сопровождаемого некоторым предварительно заданным количеством повторенных экземпляров некоторой TS-последовательности. Например, в одном примере EIEOS-набор может сопровождаться тридцатью одним (31) экземпляром TS-последовательности, при этом EIEOS-последовательность повторяется приблизительно каждые четыре тысячи UI-интервалов (например, ~4 KUI).

Кроме того, в другом примере, может быть определена надпоследовательность (815) выхода из передающего состояния с частичной шириной (PWTS-состояния). В одном примере, надпоследовательность выхода из PWTS-состояния может включать в себя начальный EIEOS-набор для повторения с целью предварительно подготовить пути передачи данных заранее, перед отправкой первой полной последовательности в надпоследовательности. Например, последовательность, подлежащая повторению в надпоследовательности (815), может начинаться с EIEOS-набора (для повторения приблизительно один раз каждые 1 тысяча UI-интервалов). Кроме того, могут быть использованы быстрые обучающие последовательности (FTS-последовательности) вместо других обучающих последовательностей (TS-последовательностей), причем FTS-последовательности, сконфигурированные таким образом, чтобы содействовать в более быстром захвате бита, захвате байта и выравнивании. В некоторых вариантах осуществления изобретения, FTS-последовательность может быть разложена на составные части, чтобы далее содействовать в возвращении бездействующих путей передачи данных в активное состояние настолько быстро и безущербно, насколько это возможно. Как и в случае с другими надпоследовательностями, предшествующими входу в передающее состояние канала передачи данных, надпоследовательность (815) может быть прервана и закончена посредством отправки начала последовательности данных (SDS). Кроме того, может быть отправлена частичная FTS-последовательность (FTSp-последовательность) для содействия в синхронизации новых путей передачи данных с активными путями передачи данных, как, например, позволяя, среди других примеров, вычитать биты (или добавлять) к FTSp-последовательности.

Надпоследовательности, такие как надпоследовательность (705) обнаружения и надпоследовательность (710) опроса/конфигурирования/кольцевой проверки, и так далее потенциально могут быть отправлены, по существу, во время инициализации или повторной инициализации канала передачи данных. Приемник, после приема и обнаружения конкретной надпоследовательности может, в некоторых случаях, ответить, осуществив эхопередачу той же самой надпоследовательности на передатчик по путям передачи данных. Прием и проверка конкретной надпоследовательности передатчиком и приемником могут служить в качестве установления связи для подтверждения состояния или условия, сообщенного через надпоследовательность. Например, такое установление связи (например, с использованием надпоследовательности (705) обнаружения) может быть использовано для того, чтобы идентифицировать повторную инициализацию канала передачи данных. В другом примере, такое установление связи может быть использовано, среди других примеров, для того, чтобы указать конец электрического сброса или состояния малого энергопотребления, что в результате приводит к тому, что соответствующие пути передачи данных восстанавливаются. Конец электрического сброса может быть идентифицирован, например, из установления связи между трансмиттером и приемником каждый из которых передает надпоследовательность (705) обнаружения.

В другом примере, пути передачи данных могут контролироваться на надпоследовательности и могут использовать эти надпоследовательности в связи с отбором путей передачи данных для обнаружения, "пробуждения", выходов из состояний и входов в них, среди других событий. Предварительно заданная и предсказуемая природа и форма надпоследовательностей могут, кроме того, использоваться для того, чтобы выполнять такие задачи инициализации как захват бита, захват байта, устранение "дребезжания", дескремблирование, выравнивание, адаптация, фиксирования времени задержки, устанавливая, согласованные запаздывания и другие потенциальные варианты использования. Действительно, пути передачи данных могут, по существу, непрерывно контролироваться на такие события, что ускоряет способность системы реагировать на такие условия и обрабатывать их.