Область техники, к которой относится изобретение

Настоящее раскрытие, в общем, относится к области электроники. Более конкретно, некоторые варианты осуществления изобретения, в общем, относятся к отображению адреса встроенного кода коррекции ошибки (ЕСС).

Уровень техники

В различные электронные устройства может быть встроена технология памяти. При использовании памяти в некоторых электронных устройствах, например смартфонах и планшетных компьютерах, используются большие объемы, но такие варианты осуществления являются чувствительными к стоимости, в которых издержки, состоящие в добавлении битов кода коррекции ошибки (ЕСС) к памяти, являются неприемлемыми. Устройства с большими объемами могут использоваться на других рынках электронных устройств, например, в пространстве серверных продуктов. Однако такие рынки, в свою очередь, требуют высокой надежности от запоминающих устройств, что делает необходимыми использование ЕСС в устройствах памяти.

В соответствии с этим технологии по воплощению ЕСС в запоминающих устройствах с большим объемом памяти могут найти применение.

Краткое описание чертежей

Подробное описание изобретения представлено со ссылкой на приложенные чертежи. На чертежа представленная слева цифра (цифры) номера ссылочной позиции обозначает фигуру, на которой впервые появляется номер ссылочной позиции. Использование одних и тех же номеров ссылочных позиций на разных фигурах обозначает аналогичные или идентичные элементы.

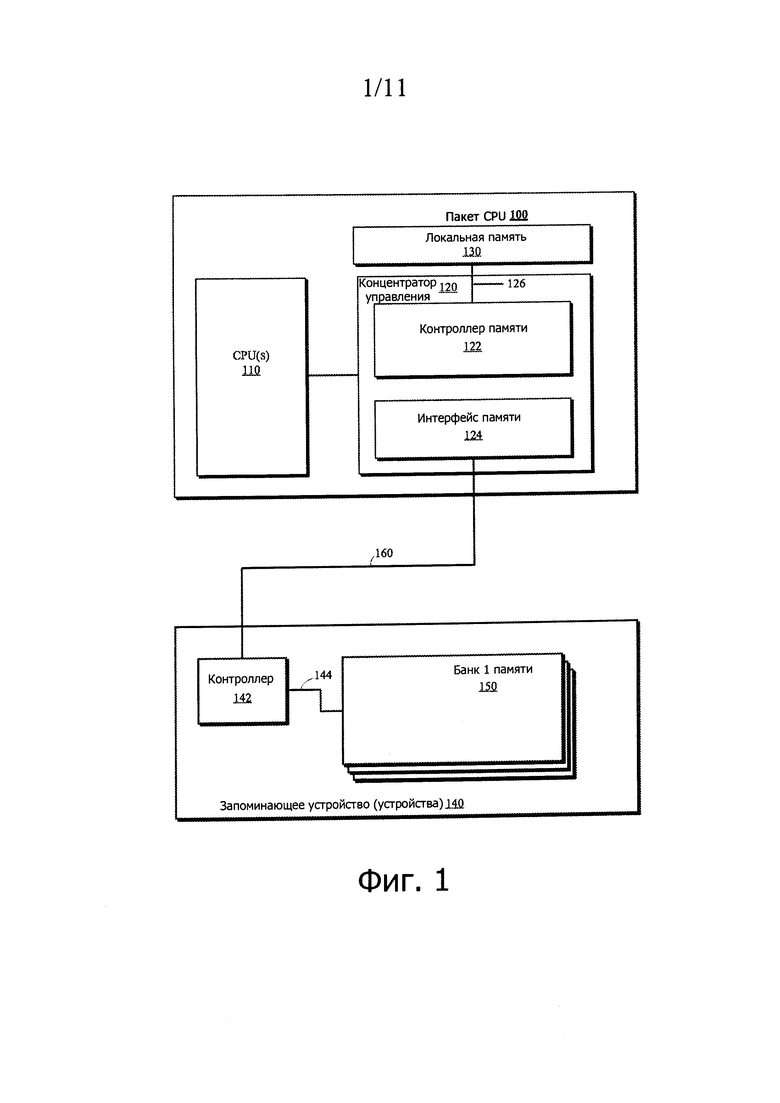

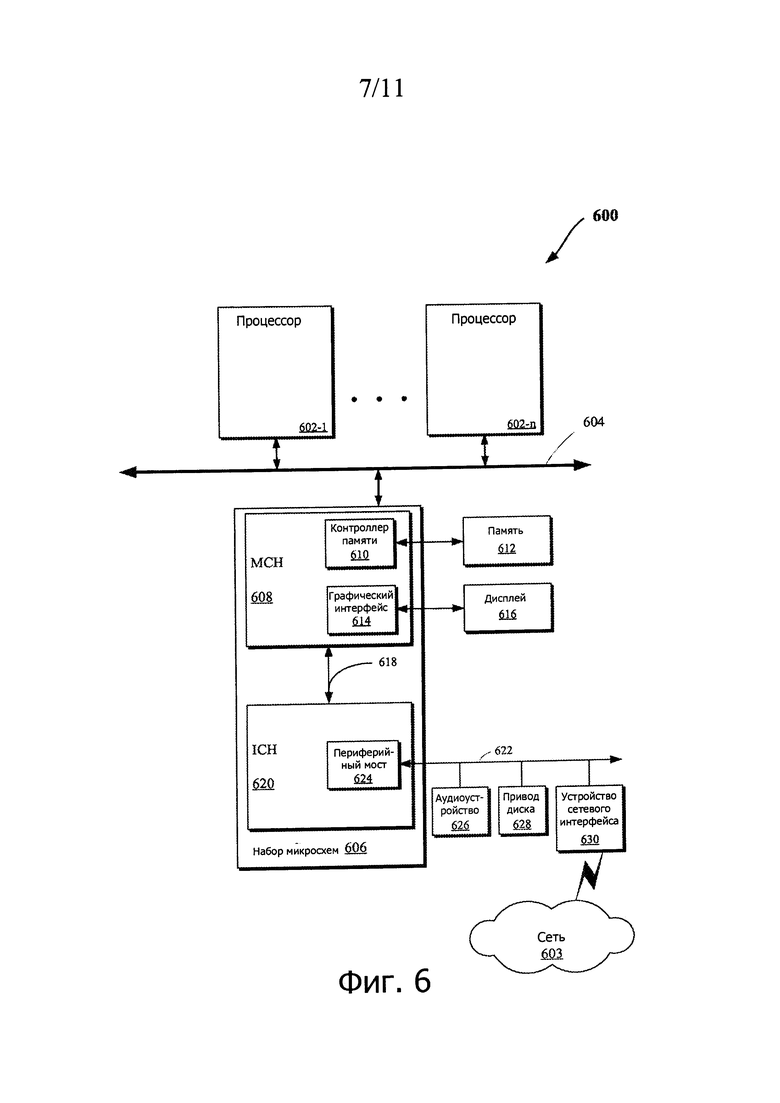

На фиг. 1 схематично показана блок-схема, иллюстрирующая компоненты устройства для воплощения отображения адреса встроенного ЕСС в соответствии с описанными здесь различными вариантами осуществления.

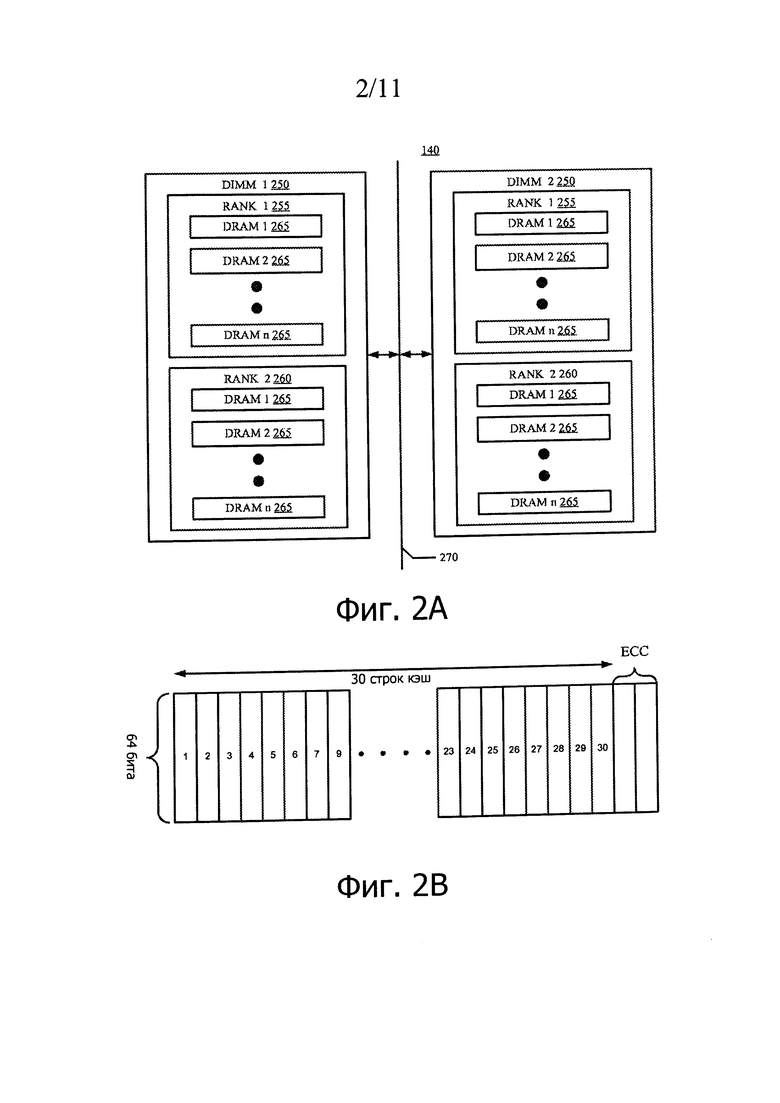

На фиг. 2А схематично показана блок-схема примерной памяти, которая может быть адаптирована для воплощения отображения адреса встроенного ЕСС, в соответствии с различными вариантами осуществления, описанными здесь.

На фиг. 2В схематично представлена иллюстрация страницы памяти в соответствии с описанными здесь различными вариантами осуществления.

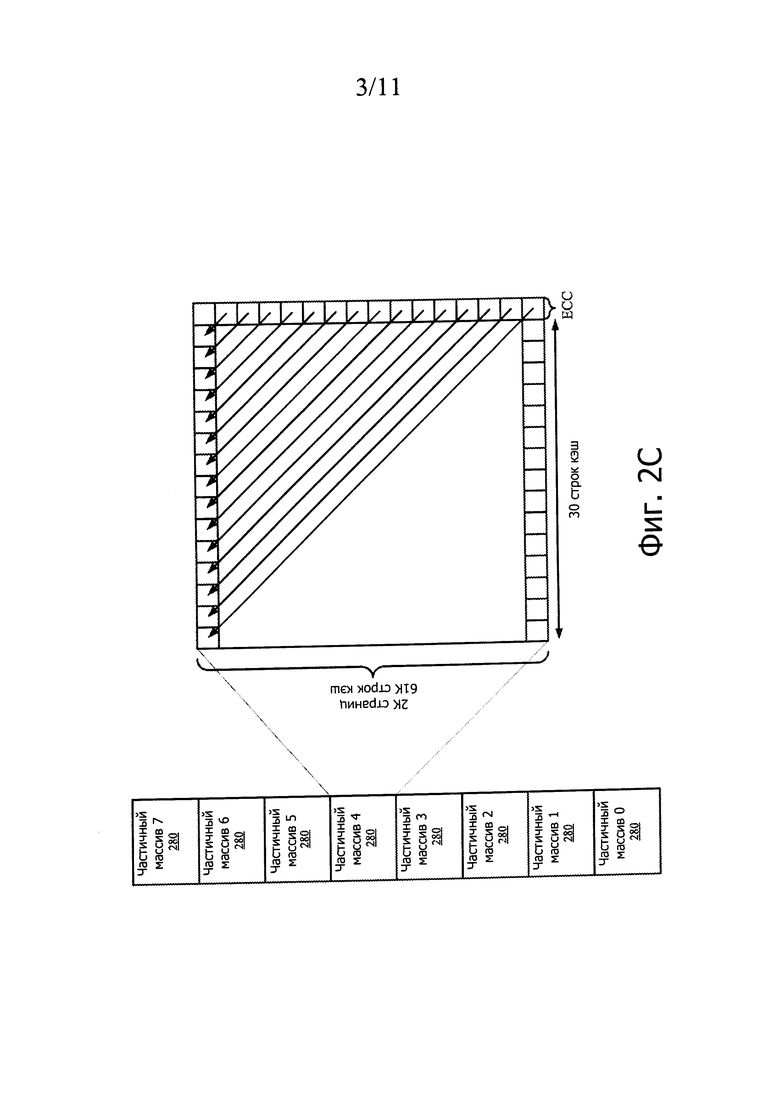

На фиг. 2С схематично представлена иллюстрация схемы отображения памяти в соответствии с описанными здесь различными вариантами осуществления.

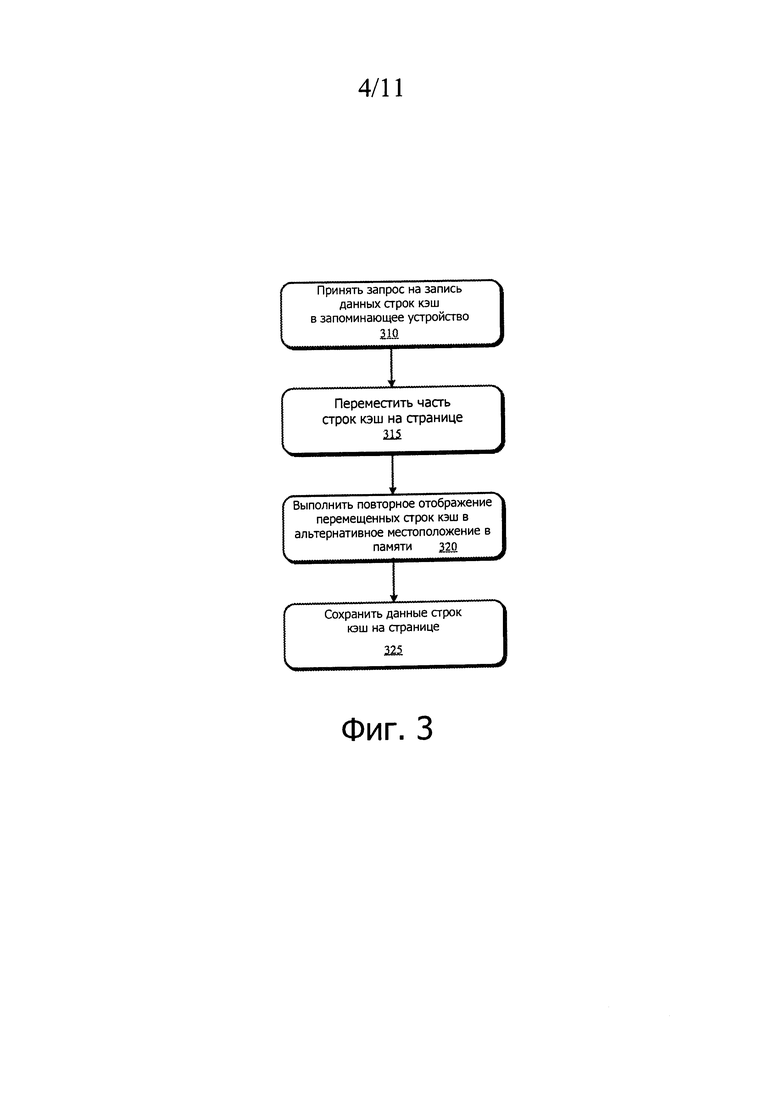

На фиг. 3-4 показана блок-схема последовательности операций, иллюстрирующая операции в способе для воплощения отображения адреса встроенного ЕСС, в соответствии с описанными здесь различными вариантами осуществления.

На фиг. 5 показана схематичная иллюстрация схемы отображения памяти для отображения адреса встроенного ЕСС, в соответствии с описанными здесь различными вариантами осуществления.

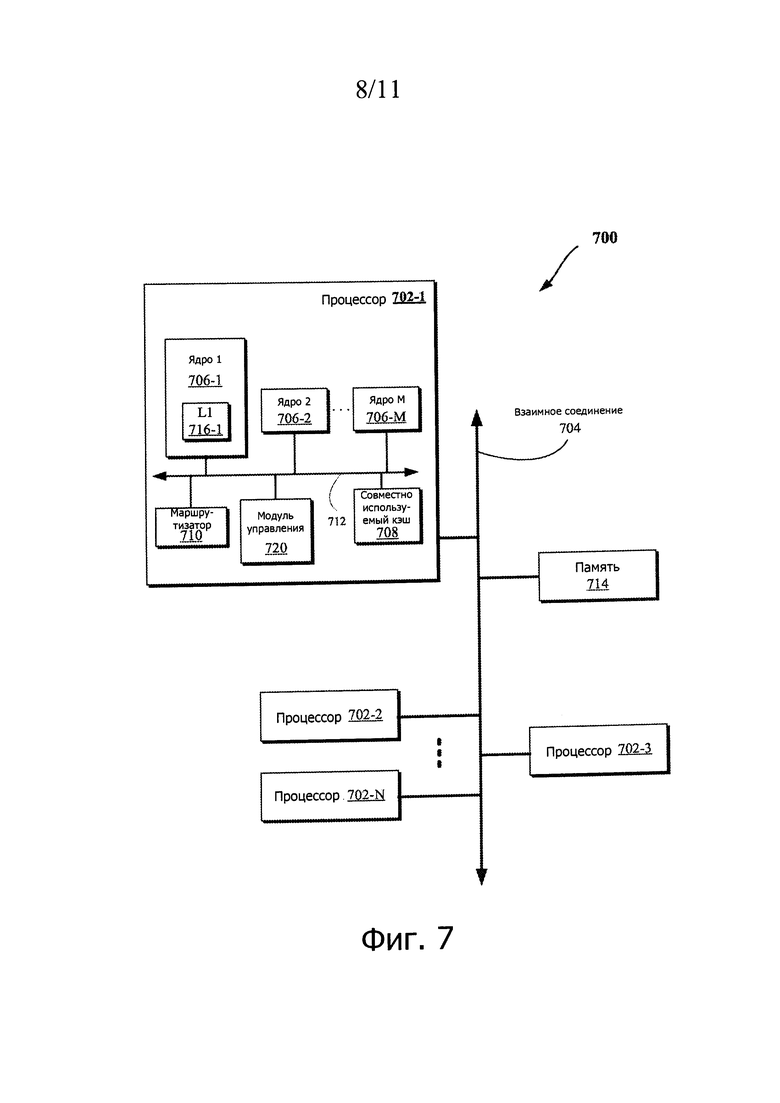

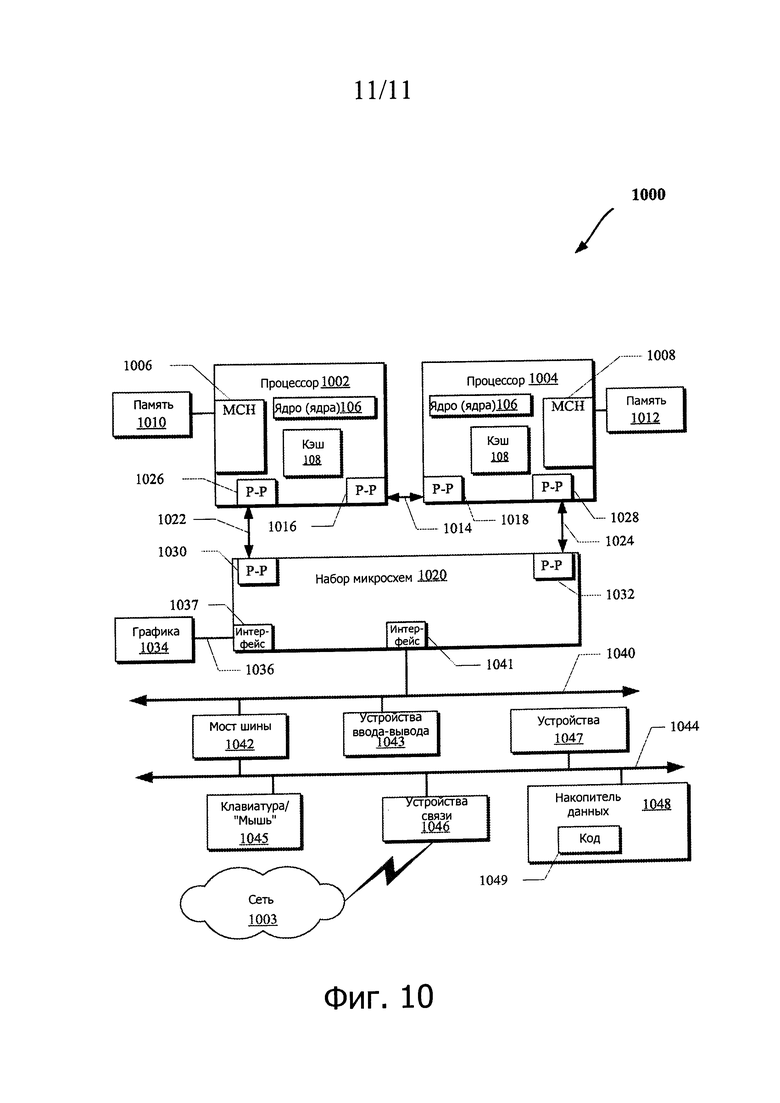

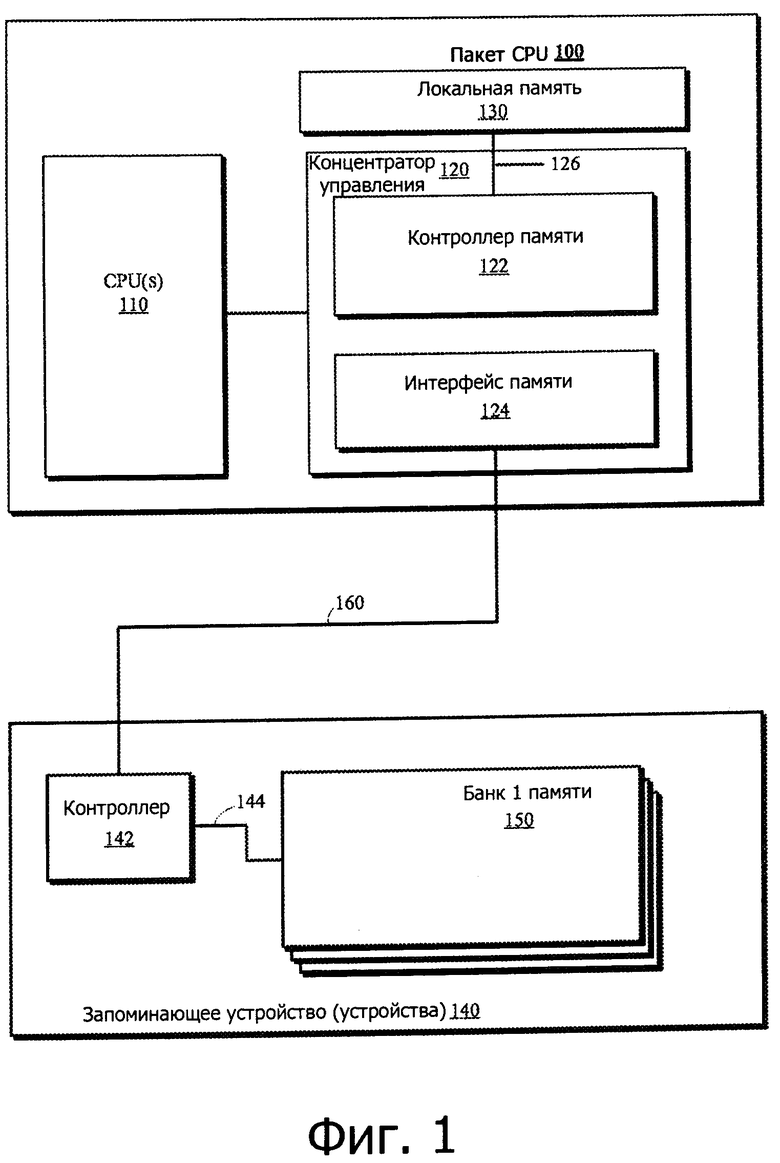

На фиг. 6-10 схематично показана иллюстрация блок-схемы электронных устройств, которые могут быть адаптированы для воплощения администрирования памятью ЕСС, в соответствии с описанными здесь различными вариантами осуществления.

Подробное описание изобретения

В следующем описании, различные конкретные детали представлены по порядку для обеспечения полного понимания различных вариантов осуществления. Однако различные варианты осуществления изобретения могут быть выполнены без этих конкретных деталей. В других случаях хорошо известные способы, процедуры, компоненты и схемы не были описаны подробно с тем, чтобы не усложнять конкретные варианты осуществления изобретения. Кроме того, различные аспекты вариантов осуществления изобретения могут быть выполнены, используя различные средства, такие как интегрированные полупроводниковые схемы ("аппаратные средства"), считываемые компьютером инструкции, организованные в виде одной или больше программ ("программное обеспечение"), или некоторые комбинации аппаратных средств и программного обеспечения. С целью данного раскрытия, ссылка на "логику" должна означать либо аппаратные средства, программное обеспечение, или некоторую их комбинацию.

Здесь описаны технологии для отображения битов ЕСС на участок запоминающего устройства (например, на динамическое оперативное запоминающее устройство (DRAM)), которое не включает в себя специально выделенную емкость для ЕСС. В различных вариантах осуществления биты ЕСС для любой заданной линии кэш могут быть размещены на той же странице DRAM (или в том же ряду), что и линия кэш. Это позволяет использовать общую команду активации DRAM как для доступа к данным линии кэш, так и для доступа к данным ЕСС, экономя, таким образом, электроэнергию и уменьшая задержку. Компоновка данных ЕСС на странице может быть размещена так, чтобы увеличить частоту успешных обращений к странице, которые могут совместно использовать один и тот же блок битов данных ЕСС, считываемых для первой линии кэш. Кроме того, линии кэш, которые смещены так, чтобы освободить пространство для битов данных ЕСС, перемещены на альтернативную страницу DRAM вместе с битами данных ЕСС, необходимых для защиты перемещенной линии кэш.

В некоторых вариантах осуществления блоки линии кэш могут быть отображены на физическое пространство DRAM таким образом, что, при использовании совместно с контроллером памяти, это обеспечивает возможность уменьшения потребления энергии в режиме ожидания. Если данные, необходимые для поддержки режимов низкого уровня потребления питания могут быть выделены в малый участок DRAM, тогда возможно перевести оставшуюся часть DRAM в состояние, аналогичное отключенному питанию, используя технологии частичного собственного обновления массива (PASR).

Описанные здесь технологии могут быть предусмотрены в различных электронных устройствах (например, включая в себя серверы, настольные компьютеры, ноутбуки, смартфоны, планшетные компьютеры, портативные игровые консоли и т.д.), которые могут включать в себя систему памяти, содержащую множество кристаллов DRAM, обычно собранных в виде модуля памяти с двусторонним расположением микросхем (DIMM). В некоторых вариантах осуществления логика может быть воплощена в контроллере памяти, который должен быть интегрирован в электронном устройстве. В качестве альтернативы, логика может быть воплощена на уровне DIMM для управления операциями для множества DRAM в DIMM.

На фиг. 1 схематично представлена иллюстрация в виде блок-схемы компонентов электронного устройства, которые могут быть адаптированы для воплощения отображения адреса встроенного ЕСС в соответствии с описанными здесь различными вариантами осуществления. На фиг. 1, в некоторых вариантах осуществления, корпус 100 центрального процессорного устройства (CPU), которое может содержать одно или больше CPU 110, соединен с концентраторов 120 управления. Концентратор 120 управления содержит контроллер 122 памяти и интерфейс 124 памяти. Контроллер 122 памяти соединен через шину 120 с локальной памятью 130.

Интерфейс 124 памяти соединен с одним или больше удаленными запоминающими устройствами 140, используя шину 160 передачи данных. Запоминающее устройство 140 может содержать контроллер 142 и один или больше сегментов 150 памяти. В различных вариантах осуществления сегменты 150 памяти могут быть воплощены, используя один или больше модулей памяти с двухрядным расположением микросхем (DIMM), соединенных с каналом 144 памяти, который обеспечивает канал передачи данных с контроллером 142. Конкретная конфигурация сегмента (сегментов) 150 памяти в запоминающем устройстве (устройствах) 140 не является критичной.

В различных вариантах осуществления запоминающее устройство (устройства) 140 может быть воплощено, как система памяти, использующая один или больше модулей памяти DRAM. На фиг. 2А схематично представлена блок-схема примерного запоминающего устройства (устройств) 140, которое может быть адаптировано для воплощения администрирования памятью ЕСС, в соответствии с различными вариантами осуществления, описанными здесь. Что касается фиг. 2А, в некоторых вариантах осуществления запоминающее устройство (устройства) 140 может содержать один или больше модулей памяти с двусторонним расположением микросхем (DIMM) 250, соединенных с каналом 270 памяти, который обеспечивает соединение для обмена данными с контроллером 142 памяти. В варианте осуществления, представленном на фиг. 2А, каждая DIMM содержит первый ряд 255 и второй ряд 260, каждый из которых включает в себя множество модулей 265 DRAM. Для специалиста в данной области техники будет понятно, что запоминающее устройство (устройства) 140 может содержать больше или меньше DIMM 250 и больше или меньше рядов на DIMM. Кроме того, некоторые электронные устройства (например, смартфоны, планшетные компьютеры и т.п.), могут содержать более простые системы памяти, содержащие одно или больше DRAM.

На фиг. 2В схематично представлена иллюстрация страницы памяти, которая может быть сохранена в DRAM 265. В некоторых вариантах осуществления каждая страница размером 2048 байт памяти содержит 30 линий кэш данных, каждая из которых имеет размер 64 байта и содержит 4 байта данных ЕСС на линию кэш. Таким образом, 1920 байт из 2048 байт используются для данных, и остальные выделены для данных ЕСС и метаданных. В некоторых вариантах осуществления данные ЕСС сохранены в конце страницы, как представлено на фиг. 2В.

В некоторых вариантах осуществления 64В линия кэш и 32 байта данных ЕСС могут быть переданы через один и тот же канал данных. Длина пакета BL8 может использоваться для считывания линии кэш, в то время как BL4 может использоваться для считывания данных ЕСС.

Как описано выше, в некоторых вариантах осуществления, по меньшей мере, один из контроллера 122 памяти или контроллера 142 в запоминающем устройстве (устройствах) 140 включает в себя логику для воплощения операций отображения адреса встроенного ЕСС. Операции отображения адреса ЕСС, воплощенные контроллером 122 памяти и/или контроллером 142, будут описаны со ссылкой на фиг. 3-5. На фиг. 3 иллюстрируются операции записи по линии кэш, которые могут быть воплощены, по меньшей мере, одним из контроллера 122 памяти или контроллера 142 в запоминающем устройстве (устройствах) 140 для воплощения отображения адреса встроенного ЕСС. Другие операции, такие как считывание линии кэш, запись ЕСС и считывание ЕСС, имеют аналогичные потоки. На фиг. 3, при выполнении операции 310, контроллер 122 памяти или контроллер 142 принимают запрос на запись данных линии кэш в локальную память 130 или на страницу запоминающего устройства 140.

При операции 320 смещенные линии кэш повторно отображают на альтернативное местоположение в памяти. Как показано на фиг. 2С, в некоторых вариантах осуществления запоминающее устройство разделено на множество частичных массивов 280, и смещенные линии кэш повторно отображены на вершину частичного массива, на которую направлена операция записи. При операции 325 данные линии кэш сохраняют на странице памяти.

Как показано на фиг. 2С, полученная в результате память является структурированной таким образом, что каждый частичный массив включает в себя как данные, так и всю информацию ЕСС, необходимую для защиты данных в частичном массиве. Таким образом, каждый частичный массив может быть независимо переведен в состояние низкого потребления энергии, используя логику самостоятельного обновления частичного массива (PASR), уменьшая, таким образом, потребление энергии запоминающим устройством 140.

Дополнительные аспекты операций отображения памяти описаны со ссылкой на фиг. 4-5. Что касается фиг. 4-5, когда поступает запрос на доступ к памяти, адрес хост-системы отображается на карту адреса линейного банка DRAM на основе выбранной страницы и на основе политики перемежения.

Если при выполнении операции 415 не все старшие значащие биты адреса в столбце представляют собой единицы, тогда применяется стандартное отображение адреса, и управление переходит к операции 420. Если при операции 420 запрос не является запросом для доступа к линии кэш, тогда управление переходит к операции 425, и применяется стандартное отображение линии кэш. В отличие от этого, если при выполнении операции 420 запрос к памяти направлен на доступ к ЕСС, тогда управление переходит к операции 430, и генерируется стандартная адресация ЕСС.

И снова, возвращаясь к операции 415, если все старшие значащие биты адреса линейного банка представляют единицы, тогда применяется альтернативное отображение, и управление переходит к операции 440. Если при операции 440 запрос к памяти направлен на доступ к линии кэш, тогда управление переходит к операции 445 и применяется альтернативное отображение линии кэш. В отличие от этого, если при выполнении операции 440 запрос к памяти направлен на доступ к ЕСС, тогда управление переходит к операции 450, и генерируется альтернативная адресация ЕСС.

На фиг. 5 иллюстрируется конкретный вариант осуществления для запоминающего устройства с размером страницы 2048 байт и 8 разделами. В этом примере 4 старшие значащие биты адреса колонки используются для определения, используется ли при доступе к линии кэш или ЕСС стандартное или альтернативное отображение. На этой иллюстрации также показано стандартное и альтернативное отображение для доступа к линии кэш и доступа к ЕСС. На этой иллюстрации дополнительно показано, как выполняют манипуляции со стандартно и альтернативно отображенными адресами для определения местоположения одного из восьми блоков линии кэш с ассоциированным ЕСС, в одном из восьми разделов DRAM. В этом примере старшие значащие три бита адреса ряда используются DRAM, для выбора раздела.

Как описано выше, в некоторых вариантах осуществления электронное устройство может быть воплощено как компьютерная система. На фиг. 6 показана блок-схема компьютерной системы 600, в соответствии с вариантом осуществления изобретения. Компьютерная система 600 может включать в себя один или больше из центрального процессорного устройства (устройств) (CPU) 602 или процессоров, которые сообщаются через сеть 604 взаимного соединения (или через шину). Процессоры 602 могут включать в себя процессор общего назначения, сетевой процессор (который обрабатывает данные, передаваемые через компьютерную сеть 603), или другие типы процессоров (включая в себя процессор компьютера с сокращенным набором команд (RISC) или компьютера со сложным набором команд (CISC)). Кроме того, процессоры 602 могут иметь конструкцию из одного или множества ядер. В процессорах 602 с конструкцией с множеством ядер могут быть интегрированы разные типы ядер процессора на одном кристалле интегральной схемы (IC). Кроме того, процессоры 602 с конструкцией с множеством ядер могут быть воплощены, как симметричные или асимметричные мультипроцессоры. В варианте осуществления, один или больше из процессоров 602 может быть таким же или может быть аналогичным процессорам 102 на фиг. 1. Например, один или больше из процессоров 602 может включать в себя модуль 120 управления, описанный со ссылкой на фиг. 1-3. Кроме того, операции, описанные со ссылкой на фиг. 3-5, могут быть выполнены одним или больше компонентами системы 600.

Набор 606 микросхем также может быть передан через сеть 604 взаимного соединения. Набор 606 микросхем может включать в себя концентратор 608 управления памятью (МСН). МСН 608 может включать в себя контроллер 610 памяти, который сообщается с памятью 612 (которая может быть такой же или аналогичной, как и память 130 на фиг. 1). Память 412 может содержать данные, включая в себя последовательности инструкций, которые могут исполняться CPU 602, или любым другим устройством, включенным в компьютерную систему 600. В одном варианте осуществления изобретения память 612 может включать в себя одно или больше из устройств энергонезависимого накопителя (или памяти), таких как оперативное запоминающее устройство (RAM), динамическое RAM (DRAM), синхронное DRAM (SDRAM), статическое RAM (SRAM) или другие типы устройств накопителей. Также может использоваться энергонезависимая память, такая как жесткий диск. Дополнительные устройства могут сообщаться через сеть 604 взаимного соединения, такую как множество CPU и/или множество экземпляров системной памяти.

МСН 608 также может включать в себя графический интерфейс 614, который сообщается с устройством 616 дисплея. В одном варианте осуществления изобретения графический интерфейс 614 может сообщаться с устройством 616 дисплея через ускоренный графический порт (AGP). В варианте осуществления изобретения дисплей 616 (такой как дисплей с плоской панелью) может сообщаться с графическим интерфейсом 614, например, через преобразователь сигнала, который транслирует цифровое представление изображения, сохраненного в устройстве накопителя, таком как видеопамять или системная память, в сигналы дисплея, которые интерпретируются и отображаются дисплеем 616. Сигналы дисплея, формируемые устройством дисплея, могут проходить через различные устройства управления перед их интерпретацией и последующим отображением на дисплее 616.

Интерфейс 618 концентратора может обеспечивать возможность сообщаться для МСН 608 и концентратора 620 управления вводом/выводом (ICH). ICH 620 может обеспечивать интерфейс для устройства (устройств) I/O, которые сообщаются с компьютерной системой 600. ICH 620 может сообщаться с шиной 622 через периферийный мост (или контроллер) 624, такой как мост межсоединения периферийных компонентов (PCI), контроллер универсальной последовательной шины (USB) или другие типы периферийных мостов или контроллеров. Мост 624 может обеспечивать путь для передачи данных между CPU 602 и периферийными устройствами. Могут использоваться другие типы топологии. Кроме того, множество шин могут сообщаться с ICH 620, например, через множество мостов или контроллеров. Кроме того, другое периферийное оборудование, которое сообщается с ICH 620, может включать в себя, в различных вариантах осуществления изобретения, привод (приводы) жесткого диска со встроенным интерфейсом накопителя (IDE) или интерфейсом малых компьютерных систем (SCSI), порт (порты) USB, клавиатуру, "мышь", параллельный порт (порты), последовательный порт (порты), привод (приводы) гибких дисков, поддержку цифрового устройства вывода (например, цифровой видеоинтерфейс (DVI)) или другие устройства.

Шина 622 может сообщаться с аудиоустройством 626, одним или больше приводом (приводами) 628 диска и устройством 630 сетевого интерфейса (которые сообщаются с компьютерной сетью 603). Другие устройства могут сообщаться через шину 622. Кроме того, различные компоненты (такие как устройство 630 сетевого интерфейса) могут сообщаться с МСН 608 в некоторых вариантах осуществления изобретения. Кроме того, процессор 602 и один или больше других компонентов, описанных здесь, могут быть скомбинированы для формирования одной микросхемы (например, для обеспечения Системы на кристалле (SOC)). Кроме того, графический ускоритель 616 может быть включен в МСН 608 в других вариантах осуществления изобретения.

Кроме того, компьютерная система 600 может включать в себя энергозависимую и/или энергонезависимую память (или накопитель). Например, энергонезависимая память может включать в себя один или больше из следующих: постоянное запоминающее устройство (ROM), программируемое ROM (PROM), стираемое PROM (EPROM), электрически стираемое EPROM (EEPROM), привод диска (например, 628), гибкий диск, ROM на компакт-диске (CD-ROM), цифровой универсальный диск (DVD), память типа флэш, магнитооптический диск или другие типы энергонезависимых считываемых устройством носителей информации, которые позволяют сохранять электронные данные (например, включая в себя инструкции).

На фиг. 7 иллюстрируется блок-схема компьютерной системы 700, в соответствии с вариантом осуществления изобретения. Система 700 может включать в себя один или больше процессоров 702-1 - 702-N (в общем, называются здесь "процессорами 702" или "процессором 702"). Процессоры 702 могут сообщаться через сеть взаимного соединения или шину 704. Каждый процессор может включать в себя различные компоненты, некоторые из которых описаны для ясности только со ссылкой на процессор 702-1. В соответствии с этим, каждый из остальных процессоров 702-2 - 702-N может включать в себя одинаковые или аналогичные компоненты, описанные со ссылкой на процессор 702-1.

В варианте осуществления процессор 702-1 может включать в себя одно или больше ядер 706-1 - 706-М процессора (здесь называются "ядрами 706" или, в более общем случае, "ядром 706"), совместно используемый кэш 708, маршрутизатор 710 и/или логику, или модуль 720 управления процессором. Ядра 706 процессора могут быть воплощены на одном кристалле интегральной микросхемы (IC). Кроме того, кристалл может включать в себя один или больше совместно используемых и/или частных кэш (таких как кэш 708), шин или взаимных соединений (таких как шина или сеть 712 взаимного соединения), контроллеры памяти или другие компоненты.

В одном варианте осуществления маршрутизатор 710 может использоваться для обмена данными между различными компонентами процессора 702-1 и/или системы 700. Кроме того, процессор 702-1 может включать в себя больше, чем один маршрутизатор 710. Кроме того, множество маршрутизаторов для 710 могут сообщаться друг с другом, для обеспечения маршрутизации данных между различными компонентами внутри или за пределами процессора 702-1.

Совместно используемый кэш 708 может содержать данные (например, включая в себя инструкции), которые используются одним или больше компонентами процессора 702-1, такие как ядра 706. Например, совместно используемый кэш 708 может локально содержать в кэш данные, содержащиеся в памяти 714, для более быстрого доступа компонентами процессора 702. В варианте осуществления кэш 708 может включать в себя кэш среднего уровня (такой как уровень 2 (L2), уровень 3 (L3), уровень 4 (L4) или другие уровни кэша), кэш последнего уровня (LLC), и/или их комбинации. Кроме того, различные компоненты процессора 702-1 могут сообщаться с совместно используемым кэш 708 напрямую через шину (например, шину 712) и/или контроллер памяти, или концентратор. Как показано на фиг. 7, в некоторых вариантах осуществления, одно или больше ядер 706 может включать в себя кэш 716-1 уровня 1 (LI) (обычно называется здесь "кэш 716 L1"). В одном варианте осуществления модуль 720 управления может включать в себя логику для воплощения операций, описанных выше со ссылкой на контроллер 122 памяти на фиг. 2.

На фиг. 8 иллюстрируется блок-схема частей ядра 706 процессора и других компонентов компьютерной системы, в соответствии с вариантом осуществления изобретения. В одном варианте осуществления стрелки, показанные на фиг. 8, иллюстрируют направление потока инструкций через ядро 706. Одно или больше ядер процессора (таких как ядро 706 процессора) могут быть воплощены на одном кристаллике интегральной схемы (или в микросхеме), такой, как описано со ссылкой на фиг. 7. Кроме того, кристалл может включать в себя один или больше совместно используемых и/или частных кэш (например, кэш 708 по фиг. 7), взаимных соединений (например, взаимных соединений 704 и/или 112 на фиг. 7), модулей управления, контроллеров памяти или других компонентов.

Как представлено на фиг. 8, ядро 706 процессора может включать в себя модуль 802 выборки, предназначенный для выборки инструкций (включая в себя инструкции с условными переходами) для исполнения ядром 706. Выборка инструкции может осуществляться из любых устройств накопителя, таких как память 714. Ядро 706 также может включать в себя модуль 804 декодирования для декодирования выбранных инструкций. Например, модуль 804 декодирования может декодировать выбранную инструкцию во множество uop (микроопераций).

Кроме того, ядро 706 может включать в себя модуль 806 планирования. Модуль 806 планирования может выполнять различные операции, ассоциированные с сохранением декодируемых инструкций (например, принятых из модуля 804 декодирования), пока инструкции не будут готовы для выдачи, например, до тех пор, пока все исходные значения декодируемой инструкции не станут доступными. В одном варианте осуществления модуль 806 планирования может планировать и/или вырабатывать (или подавать) декодируемые инструкции в исполнительный модуль 808 для исполнения. Исполнительный модуль 808 может выполнять выданные инструкции после их декодирования (например, модулем 804 декодирования) и их выдачи (например, модулем 806 планирования). В одном варианте осуществления исполнительный модуль 808 может включать в себя более чем один исполнительный модуль. Исполнительный модуль 808 также может выполнять различные арифметические операции, такие как суммирование, вычитание, умножение и/или деление, и может включать в себя один или больше арифметических-логических модулей (ALU). В одном варианте осуществления сопроцессор (не показан) может выполнять различные арифметические операции совместно с исполнительным модулем 808.

Кроме того, исполнительный модуль 808 может исполнять инструкции не по порядку. Следовательно, ядро 706 процессора может представлять собой ядро процессора, работающее не по порядку, в одном варианте осуществления. Ядро 706 также может включать в себя модуль 810 завершения операции. Модуль 810 завершения операции может завершать исполняемые инструкции после их выполнения. В варианте осуществления завершение выполняемых инструкций может привести к тому, что состояние процессора может привести к такому состоянию процессора, в котором завершено выполнение инструкций, физические регистры, используемые для инструкций, будут освобождены и т.д.

Ядро 706 также может включать в себя модуль 714 шины для обеспечения возможности обмена данными между компонентами ядра 706 процессора и другими компонентами (такими как компоненты, описанные со ссылкой на фиг. 8) через одну или больше шин (например, шины 804 и/или 812). Ядро 706 также может включать в себя один или больше регистров 816 для сохранения данных, доступ к которым осуществляется различными компонентами ядра 706 (такими, как значения, относящиеся к установкам состояния потребления энергии).

Кроме того, хотя на фиг. 7 иллюстрируется модуль 720 управления, соединенный с ядром 706 через взаимное соединение 812, в различных вариантах осуществления, модуль 720 управления может быть расположен в любом другом месте, таком, как внутри ядра 706, соединенным с ядром через шину 704, и т.д.

В некоторых вариантах осуществления, один или больше из компонентов, описанных здесь, могут быть воплощены как устройство системы на кристалле (SOC). На фиг. 9 иллюстрируется блок-схема корпуса SOC, в соответствии с вариантом осуществления. Как представлено на фиг. 9, SOC 902 включает в себя одно или больше ядер 920 центрального процессорного устройства (CPU), одно или больше из ядер 930 графического процессорного устройства (GPU), интерфейс 940 ввода/вывода (I/O), и контроллер 942 памяти. Различные компоненты корпуса SOC 902 могут быть соединены взаимным соединением или шиной, так, как описано здесь со ссылкой на другие фигуры. Кроме того, корпус 902 SOC может включать в себя большее или меньшее количество компонентов, таких, как описаны здесь со ссылкой на другие фигуры. Кроме того, каждый компонент корпуса 902 SOC может включать в себя один или больше других компонентов, например, как описано со ссылкой на другие представленные здесь фигуры. В одном варианте осуществления корпус 902 SOC (и его компоненты) представлены на одном или больше кристалле интегральной схемы (IC), например, которые установлены в одном полупроводниковом устройстве.

Как показано на фиг. 9, корпус 902 SOC соединен с памятью 960 (которая может быть аналогична или может быть такой же, как память, описанная здесь со ссылкой на другие фигуры), через контроллер 942 памяти. В варианте осуществления память 960 (или ее часть) может быть интегрирована в корпусе 902 SOC.

Интерфейс 940 I/O может быть соединен с одним или больше устройствами ввода 970 I/O, например, через взаимное соединение и/или шину, такую, как описано здесь со ссылкой на другие фигуры. Устройство (устройства) 970 I/O может включать в себя одно или больше из клавиатуры, "мыши", сенсорной панели, дисплея, устройства захвата изображения/видеоизображения (такого как камера или видеокамера/устройство видеозаписи), сенсорный экран, громкоговоритель и т.п.

На фиг. 10 иллюстрируется компьютерная система 1000, которая расположена в конфигурации из "точки-в-точку", (PtP), в соответствии с вариантом осуществления изобретения. В частности, на фиг. 10 показана система, в которой процессоры, память и устройства ввода/вывода взаимно соединены с помощью множества интерфейсов из "точки-в-точку". Операции, описанные со ссылкой на фиг. 2, могут выполняться одним или больше компонентами системы 1000.

Как представлено на фиг. 10, система 1000 может включать в себя несколько процессоров, из которых только два, процессоры 1002 и 1004, показаны для ясности. Процессоры 1002 и 1004 каждый может включать в себя локальный концентратор 1006 и 1008 контроллера памяти (МСН), для того, чтобы обеспечивать возможность связи с памятью 1010 и 1012. МСН 1006 и 1008 может включать в себя контроллер 120 памяти и/или логику 125 по фиг. 1 в некоторых вариантах осуществления.

В варианте осуществления процессор 1002 и 1004 может представлять собой один из процессоров 702, описанных со ссылкой на фиг. 7. Процессоры 1002 и 1004 могут выполнять обмен данными с интерфейсом 1014 из точки в точку (PtP), используя схему 1016 и 1018 интерфейса PtP, соответственно. Кроме того, процессоры 1002 и 1004 каждый может выполнять обмен данными с набором 1020 микросхем через индивидуальные интерфейсы 1022 и 1024 PtP, используя схему 1026, 1028, 1030 и 1032 интерфейса из "точки-в-точку". Набор 1020 микросхем дополнительно может выполнять обмен данными с графической схемой 1034 с высокой производительностью через графический интерфейс 1036 высокой производительности, например, используя схему 1037 интерфейса PtP.

Как показано на фиг. 10, одно или больше из ядер 106 и/или кэш 108 на фиг. 1 могут быть размещены в пределах процессоров 902 и 904. Другие варианты осуществления изобретения, однако, могут присутствовать в других схемах, логических модулях или устройствах в системе 900 на фиг. 9. Кроме того, другие варианты осуществления изобретения могут быть распределены в нескольких схемах, логических модулях или устройствах, представленных на фиг. 9.

Набор 920 микросхем может сообщаться с шиной 940, используя схему 941 интерфейса PtP. Шина 940 может иметь одно или больше устройств, которые связываются с нею, такие как мост 942 шины и устройства 943 I/O. Через шину 944 мост 943 шины может связываться с другими устройствами, такими как клавиатура/"мышь" 945, устройства 946 передачи данных (такие как модемы, устройства сетевого интерфейса или другие устройства передачи данных, которые могут сообщаться с компьютерной сетью 803), аудиоустройством I/O и/или устройством 948 - накопителем данных. Устройство 948 - накопитель данных (которое может представлять собой привод жесткого диска или твердотельное устройство на основе флеш NAND) может содержать код 949, который может быть выполнен процессорами 902 и/или 904.

Следующие примеры относятся к дополнительным вариантам осуществления.

Пример 1 направлен на электронное устройство, содержащее процессор и логику управления памятью для приема запроса для доступа к данным в запоминающем устройстве, в котором данные отображаются на страницу памяти, содержащую множество линий кэш, перемещения, по меньшей мере, части из множества линий кэш для того, чтобы встроить информацию кода коррекции ошибки в данные, повторного отображения части из множества линий кэш в другое местоположение в памяти и получить доступ к данным и информации кода коррекции ошибки на странице памяти.

В Примере 2, предмет изобретения по Примеру 1, в случае необходимости, может включать в себя шину данных, в которой данные и информацию кода коррекции ошибки передают по шине данных.

В Примере 3, предмет изобретения по любому из Примеров 1-2, в случае необходимости, может включать в себя логику для повторного отображения информации кода коррекции ошибки, ассоциированный с множеством линий кэш в другое местоположения в памяти.

В Примере 4 предмет изобретения по любому одному из Примеров 1-3 может быть выполнен таким образом, что запоминающее устройство разделяют на множество частичных массивов, и запрос на запись направляют в выбранный частичный массив, и запоминающее устройство дополнительно содержит логику для повторного отображения части множества линий кэш в заданное местоположение в выбранном частичном массиве.

В Примере 5, предмет изобретения по любому одному из Примеров 1-4 может быть скомпонован таким образом, что заданное местоположение соответствует верхней части выбранного частичного массива.

В Примере 6, предмет изобретения по любому одному из Примеров 1-3, в случае необходимости, может включать в себя логику для отключения питания, для выбранного частичного массива.

В Примере 7 предмет изобретения по любому одному из Примеров 1-6 может быть скомпонован таким образом, что запрос на доступ к данным в запоминающем устройстве представляет собой запрос на запись, и данные, и код коррекции ошибки сохранены на той же странице памяти.

В Примере 8 предмет изобретения по любому одному из Примеров 1-6 может быть скомпонован таким образом, что запрос на доступ к данным в устройстве памяти представляет собой запрос на считывание, и данные, и код коррекции ошибки получают из одной и той же страницы памяти.

Пример 9 представляет собой логику, содержащую контроллер памяти для приема запроса на доступ к данным в устройстве памяти, в котором данные отображают на странице памяти, содержащей множество линий кэш, перемещения, по меньшей мере, части из множества линий кэш для того, чтобы встроить информацию кода коррекции ошибки в данные, повторного отображения части из множества линий кэш в другое местоположение в памяти и получают доступ к данным и к информации кода коррекции ошибки на странице памяти.

В Примере 10, предмет изобретения по Примеру 9, в случае необходимости, может включать в себя шину данных, в которой данные и информацию кода коррекции ошибки передают по шине данных.

В Примере 11, предмет изобретения по любому из Примеров 9-10, в случае необходимости, может включать в себя логику для повторного отображения информации кода коррекции ошибки, ассоциированную с множеством линий кэш, в другое местоположение в памяти.

В Примере 12, предмет изобретения по любому одному из Примеров 9-11 может быть скомпонован таким образом, что запоминающее устройство разделено на множество частичных массивов, и запрос на запись направляют в выбранный частичный массив, и запоминающее устройство дополнительно содержит логику для повторного отображения части множества линий кэш в заданное местоположение в выбранном частичном массиве.

В Примере 13 предмет изобретения любого из Примеров 9-12 может быть расположен так, что, заданное местоположение соответствует главному блоку выбранного частичного массива.

В Примере 14 предмет изобретения по любому одному из Примеров 9-13, в случае необходимости, может включать в себя логику для отключения питания для выбранного частичного массива.

В Примере 15 предмет изобретения по любому одному из Примеров 9-14 может быть скомпонован таким образом, что запрос на доступ к данным в устройстве памяти представляет собой запрос на запись, и данные, и код коррекции ошибок сохраняют на одной и той же странице памяти.

В Примере 16 предмет изобретения по любому одному из Примеров 9-15 может быть скомпонован таким образом, что запрос на доступ к данным в устройстве памяти представляет собой запрос на считывание, и данные, и код коррекции ошибки получают из одной и той же страницы памяти.

Пример 17 направлен на устройство, содержащее запоминающее устройство, имеющее одну или больше ячеек памяти, логику управления памятью для приема запроса на доступ к данным в запоминающем устройстве, в котором данные отображают на страницу памяти, содержащую множество линий кэш, перемещения, по меньшей мере, части из множества линий кэш, для того, чтобы встроить информацию кода коррекции ошибки в данные, повторного отображения части из множества линий кэш в другое местоположение в памяти, и получения доступа к данным и информации кода коррекции ошибки на странице памяти.

В Примере 18 предмет изобретения по Примеру 17 может, в случае необходимости, включать в себя шину данных, в котором данные и информацию кода коррекции ошибки передают по шине данных.

В Примере 19 предмет изобретения по любому одному из Примеров 17-18, в случае необходимости, может включать в себя логику для повторного отображения информации кода коррекции ошибки, ассоциированной с множеством линий кэш в другое местоположение в памяти.

В Примере 20, предмет изобретения по любому одному из Примеров 17-19 может быть скомпонован таким образом, что запоминающее устройство разделено на множество частичных массивов, и запрос на запись направляют в выбранный частичный массив, и дополнительно содержащее логику для повторного отображения части множества линий кэш в заданное местоположение в выбранном частичном массиве.

В Примере 21 предмет изобретения по любому одному из Примеров 17-20 может быть скомпонован таким образом, что заданное местоположение соответствует верхней части выбранного частичного массива.

В Примере 22 предмет изобретения по любому одному из Примеров 17-21, в случае необходимости, может включать в себя логику для отключения питания для выбранного частичного массива.

В Примере 23 предмет изобретения по любому одному из Примеров 17-22 может быть скомпонован таким образом, что запрос на доступ к данным в устройстве памяти представляет собой запрос на запись, и данные, и код коррекции ошибки содержатся на одной и той же странице в памяти.

В Примере 24, предмет изобретения по любому одному из Примеров 17-23 может быть скомпонован таким образом, что запрос на доступ к данным в устройстве памяти представляет собой запрос на считывание, и данные, и код коррекции ошибки получают из одной и той страницы в памяти.

Пример 25 направлен на способ, основанный на процессоре, для отображения данных в запоминающем устройстве, содержащий: принимают, в устройстве обработки запрос на доступ к данным в запоминающем устройстве, в котором данные отображают на страницу памяти, содержащую множество линий кэш, перемещают, по меньшей мере, часть из множества линий кэш, для того, чтобы встроить информацию кода коррекции ошибки с данными, выполняют повторное отображение части из множества линий кэш в другое местоположение в памяти, и осуществляют доступ к данным и информации кода коррекции ошибки на странице памяти.

В примере 26, данные и информацию кода коррекции ошибки по п. 25 передают вместе по одной шине данных.

В Примере 27 предмет изобретения по любому одному из Примеров 25-26, в случае необходимости, может включать в себя: выполняют повторное отображение информации кода коррекции ошибки, ассоциированный с множеством линий кэш в другое местоположение в памяти.

В Примере 28 предмет изобретения по любому одному из Примеров 25-27, в случае необходимости, может включать в себя компоновку, в которой запоминающее устройство разделено на множество частичных массивов, и запрос на запись направляют в выбранный частичный массив, и дополнительно содержащий: выполняют повторное отображение части из множества линий кэш в заданное местоположение в выбранном частичном массиве.

В Примере 29 предмет изобретения по любому одному из Примеров 25-28, в случае необходимости, может включать в себя компоновку, в которой заданное местоположение соответствует верхней части выбранного частичного массива.

В Примере 30, предмет изобретения по любому одному из Примеров 25-27, в случае необходимости, может включать в себя отключение питания в выбранном частичном массиве.

В различных вариантах осуществления изобретения описанные здесь операции, например, со ссылкой на фиг. 1-9, могут быть воплощены, как аппаратные средства (например, схема), программное обеспечение, встроенное программное обеспечение, микрокод или их комбинации, которые могут быть предоставлены, как компьютерный программный продукт, например, включающий в себя вещественный (например, непереходный) считываемый устройством или считываемый компьютером носитель информации, на котором сохранены инструкции (или программные процедуры), используемые для программирования компьютера, для выполнения описанной здесь обработки. Кроме того, термин "логика" может включать в себя, в качестве примера, программное обеспечение, аппаратные средства или комбинацию программного обеспечения и аппаратных средств. Считываемый устройством носитель информации может включать в себя устройство - накопитель, такое как описано здесь.

Ссылка в описании на "один вариант осуществления" или "вариант осуществления" означает, что определенное свойство, структура или характеристика, описанная в связи с вариантом осуществления, могут быть включены в по меньшей мере один вариант осуществления. Появление фразы "в одном варианте осуществления" в различных местах в описании может относиться или может не относиться во всех случаях к одному и тому же варианту осуществления.

Кроме того, в описании и в формуле изобретения могут использоваться термины "включенный" и "соединенный", вместе с их производными. В некоторых вариантах осуществления изобретения термин "соединенный" может использоваться для обозначения того, что два или больше элементов находятся в прямом физическом или электрическом контакте друг с другом. Термин "подключенный" может означать, что два или больше элемента находятся в прямом физическом или электрическом контакте. Однако, термин "подключенный" может также означать, что два или больше элемента могут не находиться в прямом контакте друг с другом, но могут все еще содействовать или взаимодействовать друг с другом.

Таким образом, хотя варианты осуществления изобретения были описаны с использованием терминологии, специфичной для описания структурных свойств и/или методологических действий, следует понимать, что заявленный предмет изобретения может не быть ограничен описанными конкретными свойствами или действиями. Скорее, конкретные свойства и действия раскрыты, как форма примера воплощения заявленного предмета изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЕНИЕ ВРЕМЕНЕМ ОБРАЩЕНИЯ К ПАМЯТИ | 2014 |

|

RU2618938C2 |

| ГИБРИДНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2627100C2 |

| ОПРЕДЕЛЕНИЕ ФОРМАТОВ ТРАНСЛЯЦИИ ДЛЯ ФУНКЦИЙ АДАПТЕРА ВО ВРЕМЯ ВЫПОЛНЕНИЯ | 2010 |

|

RU2556418C2 |

| ТРАНСЛЯЦИЯ АДРЕСОВ ВВОДА-ВЫВОДА В АДРЕСА ЯЧЕЕК ПАМЯТИ | 2010 |

|

RU2547705C2 |

| ОБНАРУЖЕНИЕ И СМЯГЧЕНИЕ ВРЕДА ОТ ЗЛОУМЫШЛЕННОГО ВЫЗОВА ЧУВСТВИТЕЛЬНОГО КОДА | 2015 |

|

RU2665897C2 |

| ОТЛОЖЕННАЯ ОЧИСТКА БУФЕРОВ БЫСТРОГО ПРЕОБРАЗОВАНИЯ АДРЕСОВ | 2004 |

|

RU2361267C2 |

| ПРЕДСТАВЛЕНИЕ ФИЛЬТРАЦИИ НАБЛЮДЕНИЯ, АССОЦИИРОВАННОЙ С БУФЕРОМ ДАННЫХ | 2013 |

|

RU2608000C2 |

| ПЕРЕРАСПРЕДЕЛЕНИЕ СЕГМЕНТОВ ПАМЯТИ ДЛЯ РЕШЕНИЯ ПРОБЛЕМЫ ФРАГМЕНТАЦИИ | 2013 |

|

RU2666241C2 |

| КОМАНДЫ СОХРАНЕНИЯ/СОХРАНЕНИЯ БЛОКА ДАННЫХ ДЛЯ СВЯЗИ С АДАПТЕРАМИ | 2010 |

|

RU2522314C1 |

| ЗВЕНО СВЯЗИ МНОГОКРИСТАЛЬНОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ | 2013 |

|

RU2656732C2 |

Группа изобретений относится к области электроники и может быть использована для отображения адреса встроенного кода коррекции ошибки (ЕСС). Техническим результатом является экономия электроэнергии и уменьшение задержки доступа к данным. Устройство содержит процессор и логическую схему управления памятью, выполненную с возможностью приема запроса на доступ к данным в запоминающем устройстве, причем данные отображены на страницу памяти, содержащую множество строк кэш; смещения по меньшей мере части из множества строк кэш для встраивания в данные информации ЕСС; повторного отображения упомянутой части из множества строк кэш в другое местоположение в памяти и доступа к данным и информации ЕСС на странице памяти, при этом запоминающее устройство разделено на множество частичных массивов; запрос на запись направлен в выбранный частичный массив, логическую схему, выполненную с возможностью повторного отображения упомянутой части из множества строк кэш в заданное местоположение в выбранном частичном массиве, причем указанный частичный массив дополнительно содержит указанную информацию ЕСС, причем заданное местоположение соответствует верхней части указанного частичного массива. 3 н. и 15 з.п. ф-лы, 12 ил.

1. Электронное устройство для отображения адреса встроенного кода коррекции ошибки (ЕСС), причем электронное устройство не включает в себя выделенную емкость для ЕСС, при этом электронное устройство содержит:

процессор и

логическую схему управления памятью, выполненную с возможностью:

приема запроса на доступ к данным в запоминающем устройстве, причем данные отображены на страницу памяти, содержащую множество строк кэш;

смещения по меньшей мере части из множества строк кэш для встраивания в данные информации кода коррекции ошибки;

повторного отображения упомянутой части из множества строк кэш в другое местоположение в памяти и

доступа к данным и информации кода коррекции ошибки на странице памяти,

при этом

запоминающее устройство разделено на множество частичных массивов;

запрос на запись направлен в выбранный частичный массив, при этом

электронное устройство дополнительно содержит логическую схему, выполненную с возможностью

повторного отображения упомянутой части из множества строк кэш в заданное местоположение в выбранном частичном массиве, причем указанный частичный массив дополнительно содержит указанную информацию кода коррекции ошибки,

причем заданное местоположение соответствует верхней части указанного частичного массива.

2. Электронное устройство по п. 1, дополнительно содержащее шину данных, причем данные и информация кода коррекции ошибки передаются по шине данных.

3. Электронное устройство по п. 1, дополнительно содержащее логическую схему, выполненную с возможностью повторного отображения информации кода коррекции ошибки, связанной с упомянутым множеством строк кэш, в другое местоположение в памяти.

4. Электронное устройство по п. 1, дополнительно содержащее логическую схему, выполненную с возможностью отключения питания для выбранного частичного массива.

5. Электронное устройство по п. 1, в котором:

запрос на доступ к данным в запоминающем устройстве представляет собой запрос на запись и

данные и код коррекции ошибки хранятся на одной и той же странице памяти.

6. Электронное устройство по п. 1, в котором:

запрос на доступ к данным в запоминающем устройстве представляет собой запрос на считывание и

данные и код коррекции ошибки извлекаются из одной и той же страницы памяти.

7. Контроллер памяти, содержащий логическую схему, выполненную с возможностью:

приема запроса на доступ к данным в запоминающем устройстве, причем данные отображены на страницу памяти, содержащую множество строк кэш;

смещения по меньшей мере части из множества строк кэш для встраивания информации кода коррекции ошибки;

повторного отображения упомянутой части из множества строк кэш в другое местоположение в памяти и

доступа к данным и информации кода коррекции ошибки на странице памяти,

при этом

запоминающее устройство разделено на множество частичных массивов;

запрос на запись направлен в выбранный частичный массив;

при этом контроллер памяти дополнительно содержит логическую схему, выполненную с возможностью повторного отображения упомянутой части из множества строк кэш в заданное местоположение в выбранном частичном массиве, причем указанный частичный массив дополнительно содержит указанную информацию кода коррекции ошибки,

причем заданное местоположение соответствует верхней части выбранного частичного массива.

8. Контроллер памяти по п. 7, дополнительно содержащий шину данных, причем данные и информация кода коррекции ошибки передаются по шине данных.

9. Контроллер памяти по п. 7 дополнительно содержащий логическую схему, выполненную с возможностью повторного отображения информации кода коррекции ошибки, связанной с упомянутым множеством строк кэш, в другое местоположение в памяти.

10. Контроллер памяти по п. 7, дополнительно содержащий логическую схему, выполненную с возможностью отключения питания для выбранного частичного массива.

11. Контроллер памяти по п. 7, в котором:

запрос на доступ к данным в запоминающем устройстве представляет собой запрос на запись и

данные и код коррекции ошибок хранятся на одной и той же странице памяти.

12. Контроллер памяти по п. 7, в котором:

запрос на доступ к данным в запоминающем устройстве представляет собой запрос на считывание; и

данные и код коррекции ошибки извлекаются из одной и той же страницы памяти.

13. Устройство для отображения адреса встроенного кода коррекции ошибки (ЕСС), причем устройство не включает в себя выделенную емкость для ЕСС, при этом устройство содержит:

запоминающее устройство, имеющее одну или более ячеек памяти;

логическую схему управления памятью, выполненную с возможностью:

приема запроса на доступ к данным в запоминающем устройстве, причем данные отображены на страницу памяти, содержащую множество строк кэш;

смещения по меньшей мере части из множества строк кэш для встраивания информации кода коррекции ошибки;

повторного отображения упомянутой части из множества строк кэш в другое местоположение в памяти и

доступа к данным и информации кода коррекции ошибки на странице памяти,

при этом

запоминающее устройство разделено на множество частичных массивов,

запрос на запись направлен в выбранный частичный массив;

при этом устройство дополнительно содержит логическую схему, выполненную с возможностью

повторного отображения упомянутой части множества строк кэш в заданное местоположение в выбранном частичном массиве, причем указанный частичный массив дополнительно содержит указанную информацию кода коррекции ошибки,

причем заданное местоположение соответствует верхней части выбранного частичного массива.

14. Устройство по п. 13, дополнительно содержащее шину данных, причем данные и информация кода коррекции ошибки передаются по шине данных.

15. Устройство по п. 13, дополнительно содержащее логическую схему, выполненную с возможностью повторного отображения информации кода коррекции ошибки, связанной с упомянутым множеством строк кэш, в другое местоположение в памяти.

16. Устройство по п. 13, дополнительно содержащее логическую схему, выполненную с возможностью отключения питания для выбранного частичного массива.

17. Устройство по п. 13, в котором:

запрос на доступ к данным в запоминающем устройстве представляет собой запрос на запись и

данные и код коррекции ошибки хранятся на одной и той же странице в памяти.

18. Устройство по п. 13, в котором:

запрос на доступ к данным в запоминающем устройстве представляет собой запрос на считывание и

данные и код коррекции ошибки извлекаются из одной и той же страницы в памяти.

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| US 6427188 B1, 30.07.2002 | |||

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ФАЙЛАМИ | 2004 |

|

RU2349955C2 |

Авторы

Даты

2018-02-12—Публикация

2014-06-24—Подача