Область техники, к которой относится изобретение

Раскрытые варианты осуществления, в общем, относятся к псевдодвухпортовой памяти.

УРОВЕНЬ ТЕХНИКИ

Двухпортовая память в типичном варианте имеет два порта и массив ячеек памяти. Обращение к массиву памяти может одновременно осуществляться с обоих портов при условии, что ячейки памяти, обращение к которым осуществляется с одного порта, не являются теми же ячейками памяти, обращение к которым осуществляется с другого порта. Общий тип ячейки памяти, используемой в такой двухпортовой памяти, включает в себя восемь полевых транзисторов (FET). Четыре транзистора связаны между собой так, чтобы сформировать два инвертора с перекрестными обратными связями. Первый узел D данных ячейки памяти - это узел на линии вывода первого из инверторов и линии ввода второго из инверторов. Второй узел DN данных ячейки памяти - это узел на линии вывода второго из инверторов и линии ввода первого из инверторов. Предусмотрено два входных транзистора, подключенных к первому узлу D данных. Первый входной транзистор предусмотрен так, что первая разрядная шина B1 выборочно может быть подключена к первому узлу D данных. Второй входной транзистор предусмотрен так, что вторая разрядная шина B2 выборочно может быть подключена к первому узлу D данных. Аналогично, предусмотрено два входных транзистора, подключенных ко второму узлу DN данных. Первый входной транзистор предусмотрен так, что линейка B1N первой разрядной шины может быть подключена ко второму узлу DN. Второй входной транзистор предусмотрен так, что линейка B2N второй разрядной шины может быть подключена ко второму узлу DN. Первая разрядная шина B1 и линейка B1N первой разрядной шины составляют пару разрядной шины и служат для подключения адресуемой ячейки памяти к первому из двух портов двухпортовой памяти. Вторая разрядная шина B2 и линейка B2N второй разрядной шины составляют пару разрядной шины и служат для подключения адресуемой ячейки памяти ко второму из двух портов двухпортовой памяти.

Ячейки памяти в однопортовой памяти в типичном варианте включают в себя только шесть транзисторов. Как и в случае ячейки с восемью транзисторами, четыре транзистора формируют структуру инвертора с перекрестными обратными связями. Вместо двух пар входных транзисторов в качестве ячейки с восемью транзисторами, тем не менее, ячейка с шестью транзисторами имеет только одну пару входных транзисторов. Первый входной транзистор предусмотрен для выборочного подключения первого узла D данных инверторов с перекрестными обратными связями к разрядной шине B. Второй входной транзистор предусмотрен для выборочного подключения второго узла DN данных инверторов с перекрестными обратными связями к линейке BN разрядной шины. Ячейка памяти с шестью транзисторами в типичном варианте занимает только примерно наполовину меньше области интегральной микросхемы, чем ячейка с восемью транзисторами, когда два типа ячеек памяти изготавливаются с помощью одного и того же процесса.

Чтобы использовать преимущество ячейки памяти с шестью транзисторами меньшего размера, зачастую используется запоминающее устройство, называемое псевдодвухпортовой памятью. В одном примере псевдодвухпортовая память имеет один массив памяти, при этом каждая ячейка памяти массива - это ячейка памяти с шестью транзисторами, которая может быть выборочно подключена к одной паре разрядных шин (например, разрядной шине B и линейке BN разрядной шины). Массив памяти работает как однопортовая память в том, что за один раз выполняется только одно обращение к памяти.

Тем не менее, псевдодвухпортовая память имитирует двухпортовую память в том, что она имеет два порта. В одном примере псевдодвухпортовая память имеет схему, иногда называемую мультиплексором с временной задержкой (TDM). Один входной синхронизирующий сигнал принимается в псевдодвухпортовой памяти, и этот один входной синхронизирующий сигнал используется для того, чтобы защелкивать входной адрес считывания, входной адрес записи и значение входных данных. Передний фронт входного синхронизирующего сигнала используется для того, чтобы инициировать операцию считывания с помощью входного адреса считывания. Операция считывания выполняется. После этого возникает задний фронт входного синхронизирующего сигнала. TDM использует задний фронт входного синхронизирующего сигнала для того, чтобы инициировать операцию записи. Входной адрес записи используется для того, чтобы адресовать массив памяти в ходе операции записи, а данные, записанные в массив памяти, являются входным значением данных. Хотя две операции с памятью выполняются в одном такте входного синхронизирующего сигнала, две операции памяти фактически выполняются одна за другой. Тем не менее, извне псевдодвухпортовой памяти, как кажется, псевдодвухпортовая память разрешает два обращения к массиву памяти одновременно или практически одновременно.

Автор изобретения установил, что количество времени, требуемое для того, чтобы выполнить первую операцию считывания из памяти, может быть не равно количеству времени, требуемому для того, чтобы выполнить вторую операцию записи в память. Использование традиционного подхода TDM замедляет общее время обращения к памяти, поскольку относительное количество времени, доступное для двух операций, определяется временем, когда передний фронт такта выполняется, и времени, когда задний фронт такта выполняется. Например, если синхронизирующий сигнал имеет низкий уровень в течение такого же времени, что и высокий в такте (т.е. синхронизирующий сигнал имеет продолжительность включения 50/50), то одинаковое количество времени должно быть разрешено для выполнения как более быстрой операции считывания, так и более медленной операции записи. Результат - количество потерянного времени, которое начинается после того, как операция считывания выполнена, и завершается при заднем фронте синхронизирующего сигнала.

Традиционный подход TDM иногда замедляет общее время обращения к памяти не только в ситуациях, когда относительное количество времени, требуемое для того, чтобы выполнить два обращения к памяти, не совпадает с продолжительностью включения синхронизирующего сигнала, но традиционный подход TDM также может приводить к тому, что общее время обращения к памяти меньше, чем было бы в противном случае за счет использования заднего фронта синхронизирующего сигнала, чтобы инициировать операции. Может быть дрожание фазы при продолжительности включения синхронизирующего сигнала, так что синхронизация заднего фронта синхронизирующего сигнала изменяется от такта к такту. Если схема оптимизирована для работы в режиме одной продолжительности включения синхронизирующего сигнала, то она в типичном варианте не оптимизирована для работы в режиме другой продолжительности включения синхронизирующего сигнала. Запас времени в типичном варианте встраивается в схему так, что схема двухпортовой памяти должна работать корректно во всех режимах продолжительности включения синхронизирующего сигнала. Этот запас времени переводится в потерянное время при определенных режимах работы, в которых для надлежащей работы не требуется запаса времени. Максимальная тактовая частота псевдодвухпортовой памяти, следовательно, задается так, чтобы быть меньше, чем она могла бы быть, когда нет такого запаса времени.

Несмотря на то что псевдодвухпортовая память, описанная выше, имеет один входной синхронизирующий сигнал, в некоторых вариантах применения должно быть желательным для псевдодвухпортовой памяти иметь первый порт, который синхронизирован с первым входным синхронизирующим сигналом, и второй порт, который синхронизирован со вторым входным синхронизирующим сигналом. Посредством предоставления двух отдельных входных синхронизирующих импульсов использование одного порта может быть сделано во многом независимым от использования другого порта. Посредством задания этих двух портов более независимыми, использование псевдодвухпортовой памяти может быть упрощено.

В свете вышеописанного, требуется усовершенствованная псевдодвухпортовая память, которая не использует как передний, так и задний фронт одного и того же входного синхронизирующего сигнала, чтобы управлять упорядочением двух операций с памятью, которая также имеет два отдельных порта, при этом каждый порт имеет собственный входной синхронизирующий импульс.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Псевдодвухпортовая память имеет первый порт, второй порт и массив ячеек памяти с шестью транзисторами. Первый порт (например, порт только для считывания) включает в себя линию ввода синхронизирующего импульса для приема первого синхронизирующего сигнала. Второй порт (например, порт только для записи) включает в себя линию ввода синхронизирующего импульса для приема второго синхронизирующего сигнала.

Первое обращение к памяти (например, операция обращения для считывания из памяти) массива инициируется передним фронтом первого синхронизирующего сигнала, принимаемого по линии ввода синхронизирующих импульсов первого порта. Второе обращение к памяти (например, операция обращения для записи в память) массива инициируется в ответ на передний фронт второго синхронизирующего сигнала, принимаемого по линии ввода синхронизирующих импульсов второго порта. Если передний фронт второго синхронизирующего сигнала возникает в течение первого периода времени (например, когда первый синхронизирующий сигнал переходит к высокому уровню или в течение следующего количества времени, когда первый синхронизирующий сигнал высокий), то второе обращение к памяти инициируется практически сразу же после завершения первого обращения к памяти. С другой стороны, если передний фронт второго синхронизирующего сигнала возникает позднее в течение второго периода времени (например, в ходе последующего периода времени, когда первый синхронизирующий сигнал низкий), то инициирование второго обращения к памяти не следует сразу после завершения первого обращения к памяти, а вместо этого задерживается до второго переднего фронта первого синхронизирующего сигнала. Когда второй передний фронт первого синхронизирующего сигнала инициирует третью операцию обращения к памяти через первый порт, вторая операция обращения памяти осуществляется после третьей операции обращения к памяти.

Один пример схемы, которая обнаруживает, когда возникает передний фронт второго синхронизирующего сигнала, относительно первого синхронизирующего сигнала, и которая инструктирует задержу инициирования второго обращения к памяти, если такая задержка применима, описан в разделе подробного описания ниже. Схема включает в себя мультиплексор с временной задержкой, который принимает синхронизирующий сигнал считывания для первого обращения к памяти (операции считывания) и синхронизирующий сигнал записи для второго обращения к памяти (операции записи). Мультиплексор с временной задержкой выводит управляющий сигнал, который определяет то, что массив ячеек памяти адресован для первого обращения к памяти или адресован для второго обращения к памяти. Схема дополнительно включает в себя схему подавителя синхронизирующих импульсов записи. Если передний фронт второго синхронизирующего сигнала возникает слишком поздно (когда первый синхронизирующий сигнал низкий) для того, чтобы мультиплексор с временной задержкой работал надлежащим образом при инициировании второй операции обращения к памяти сразу после уже инициированной первой операции обращения к памяти, то схема подавителя синхронизирующих импульсов записи подавляет синхронизирующий сигнал записи, подаваемый в мультиплексор с временной задержкой, тем самым, задерживая инициирование второй операции обращения к памяти до окончания второго переднего фронта первого синхронизирующего сигнала.

В отличие от традиционной двухпортовой памяти, где задний фронт входного синхронизирующего импульса используется ко времени, когда второе обращение к памяти начинается, длительность первого и второго обращений к памяти в новой двухпортовой памяти, раскрытой в данном патентном документе, не зависит от того, когда возникает задний фронт синхронизирующего сигнала. Вместо этого, длительность первого обращения к памяти во многом зависит от задержки на распространение (например, задержки, вводимой посредством схемы одноразового срабатывания). Длительность второго обращения к памяти во многом зависит от задержки на распространение (например, задержки на распространение через случайную логику и/или задержки, введенной посредством схемы одноразового срабатывания). Отношение количества времени, выделяемого первому обращению к памяти, к количеству времени, выделяемому второму обращению к памяти, может корректироваться на стадии проектирования псевдодвухпортовой памяти посредством корректировки отношений и величин задержек на распространение. Отношение количества времени, выделяемого первому обращению к памяти, к количеству времени, выделяемому второму обращению к памяти, практически не зависит от продолжительности включения либо первого синхронизирующего сигнала, либо второго синхронизирующего сигнала.

Дополнительные варианты осуществления аппаратных средств, дополнительные способы и дополнительные детали поясняются в подробном описании ниже. Данная сущность не означает то, чтобы задавать изобретение. Изобретение задается посредством формулы изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

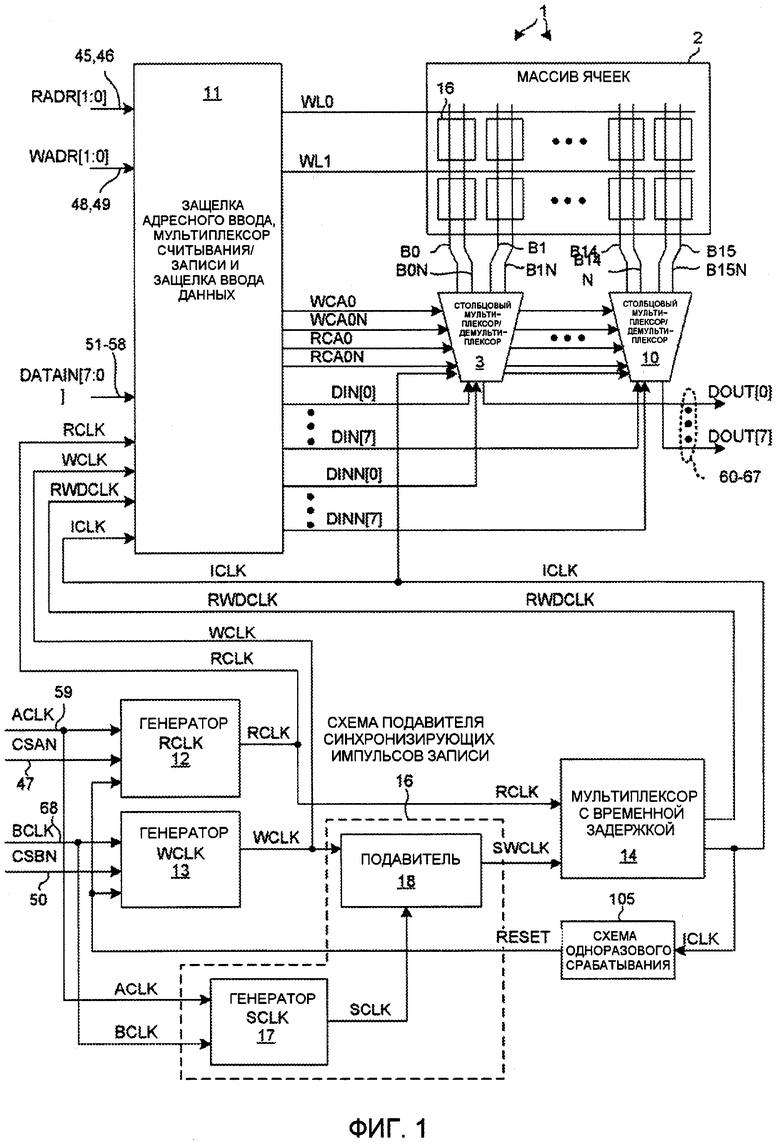

Фиг.1 - блок-схема высокого уровня псевдодвухпортового запоминающего устройства 1 в соответствии с одним вариантом осуществления.

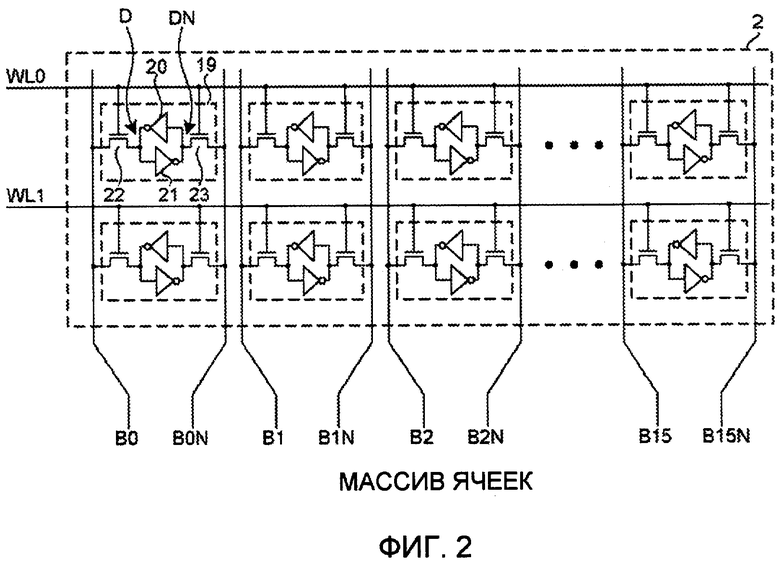

Фиг.2 - более подробная схема массива 2 памяти по фиг.1.

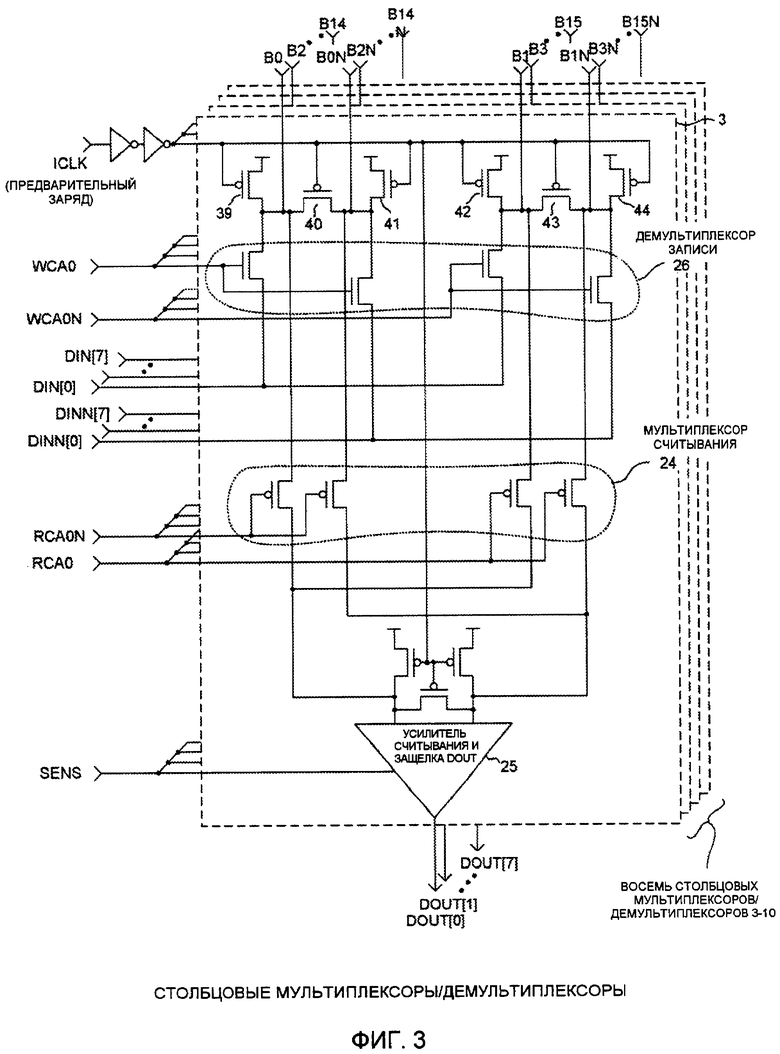

Фиг.3 - более подробная схема восьми столбцовых мультиплексоров/демультиплексоров 3-10 по фиг.1.

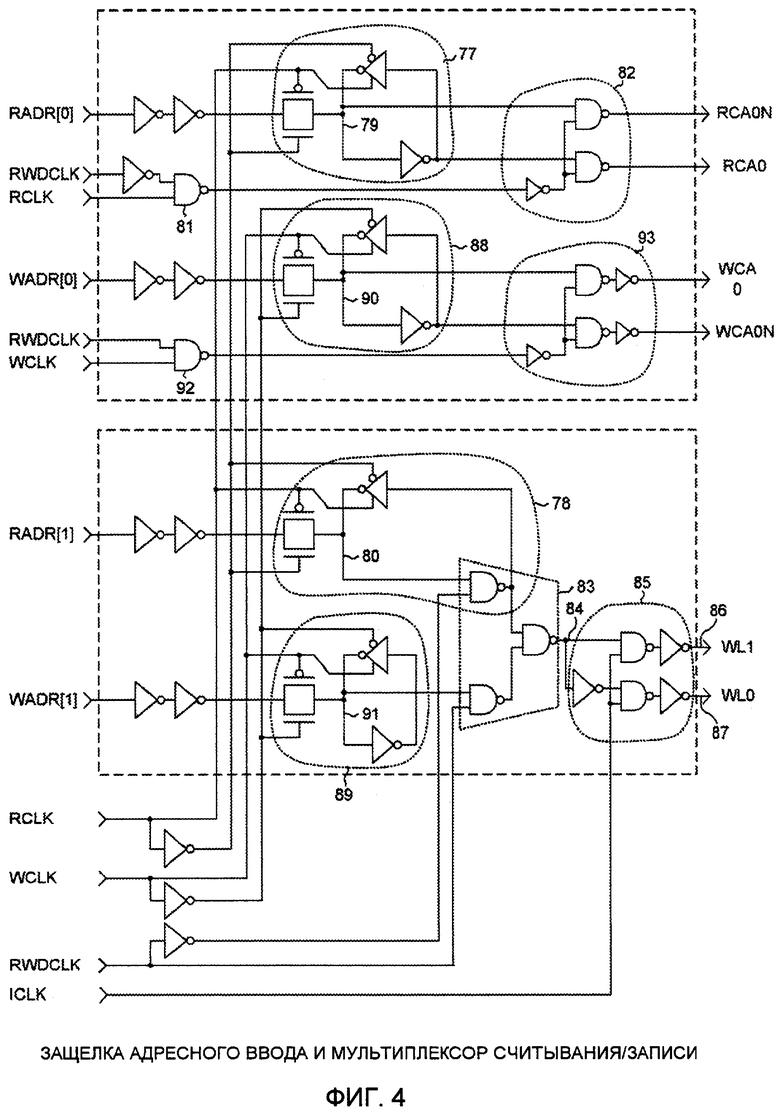

Фиг.4 - более подробная схема защелки ввода адреса и блока мультиплексора считывания/записи для блока 11 по фиг.1.

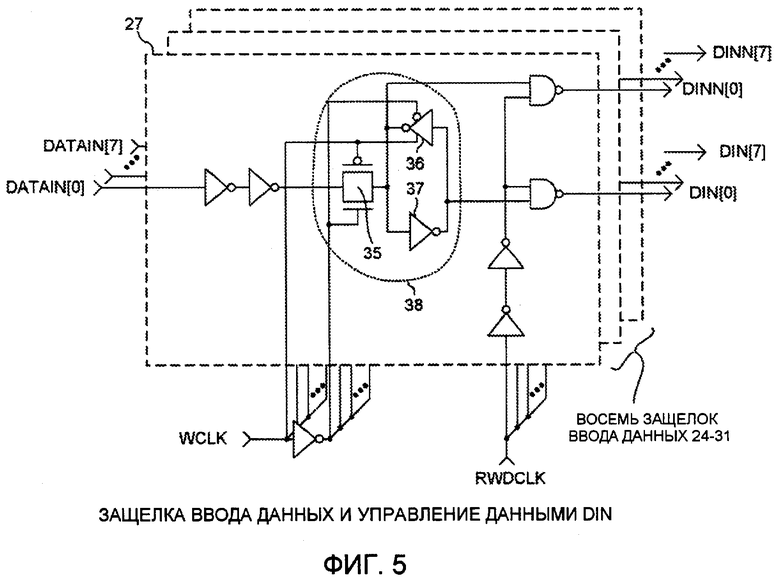

Фиг.5 - более подробная схема блока защелки ввода данных для блока 11 по фиг.1.

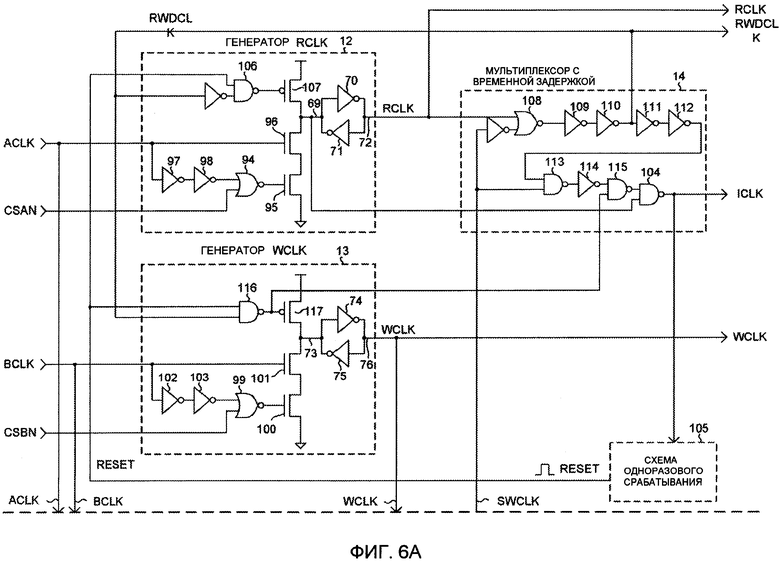

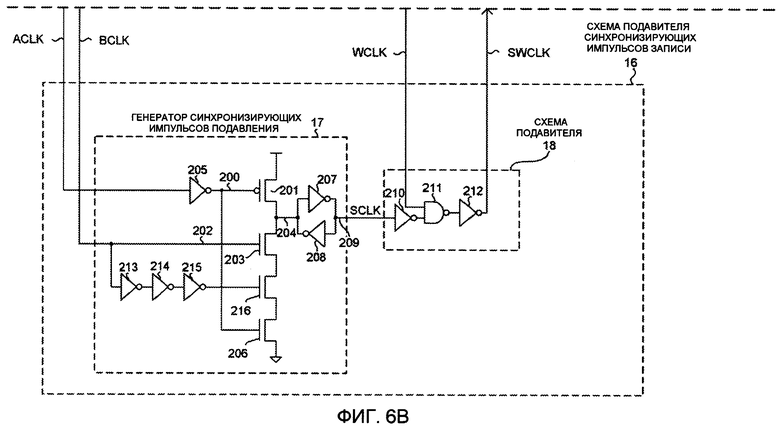

Фиг.6A и 6B - более подробная схема для схемы 12 генератора синхронизирующих импульсов считывания, схемы 13 генератора синхронизирующих импульсов записи, схемы 14 мультиплексора с временной задержкой и схемы 16 подавителя синхронизирующих импульсов записи и схемы 105 одноразового срабатывания по фиг.1.

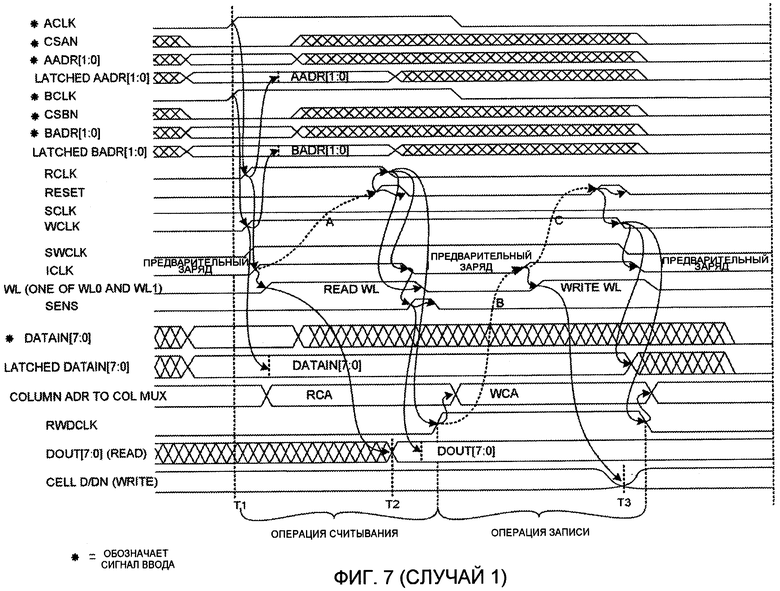

Фиг.7 - диаграмма формы сигнала, которая иллюстрирует первый сценарий (случай 1) работы псевдодвухпортового запоминающего устройства 1 по фиг.1-6.

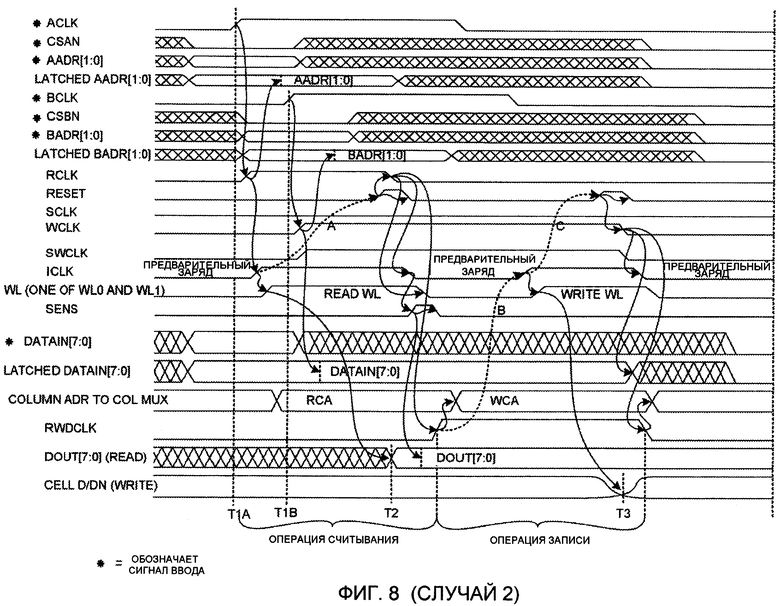

Фиг.8 - диаграмма формы сигнала, которая иллюстрирует второй сценарий (случай 2) работы псевдодвухпортового запоминающего устройства 1 по фиг.1-6.

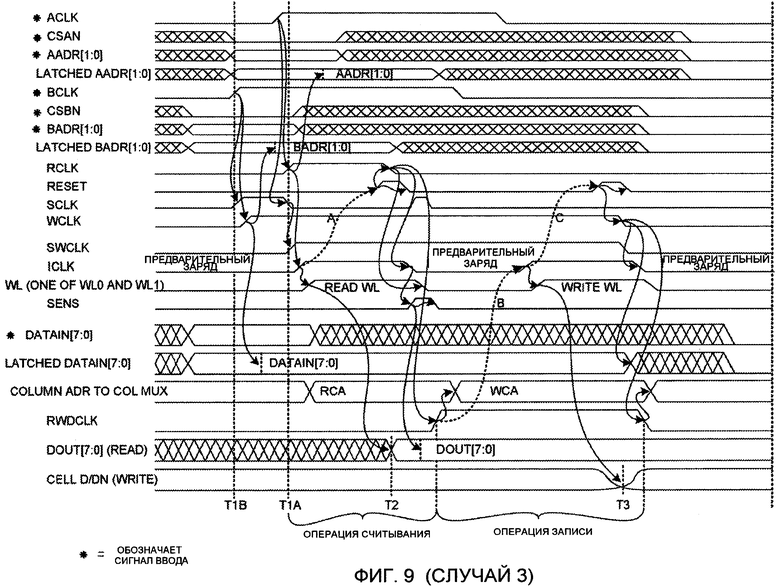

Фиг.9 - диаграмма формы сигнала, которая иллюстрирует третий сценарий (случай 3) работы псевдодвухпортового запоминающего устройства 1 по фиг.1-6.

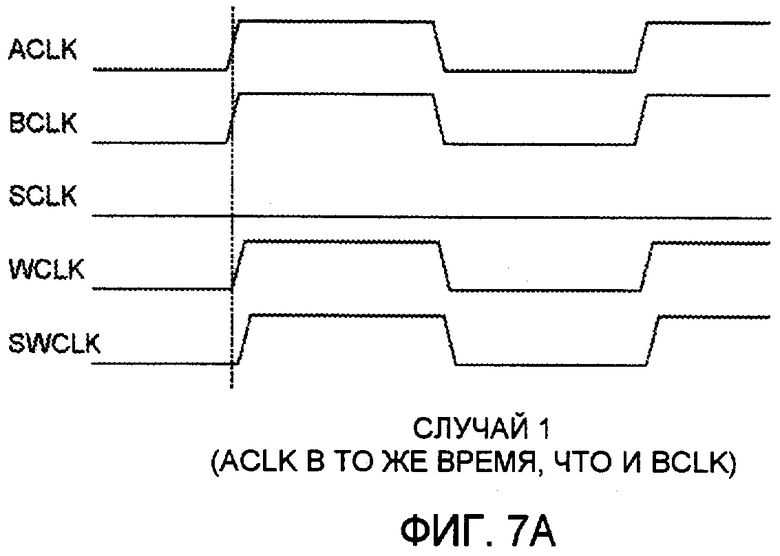

Фиг.7A - упрощенная схема формы сигнала первого сценария (случай 1).

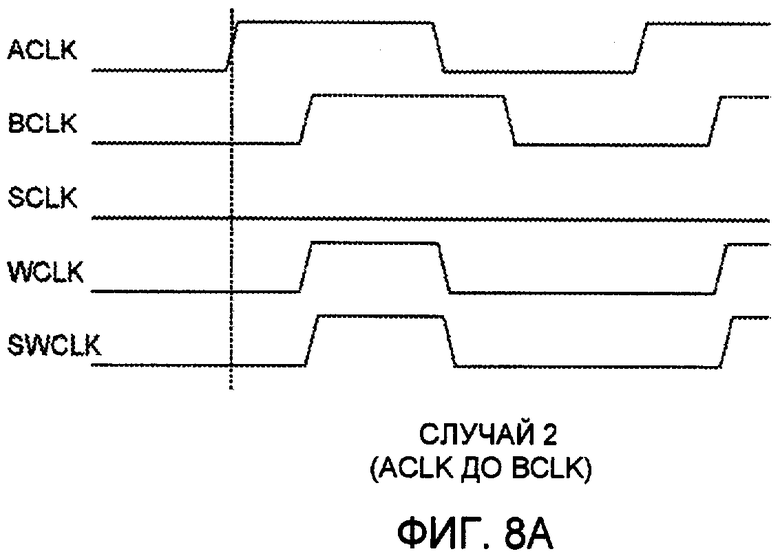

Фиг.8A - упрощенная схема формы сигнала второго сценария (случай 2).

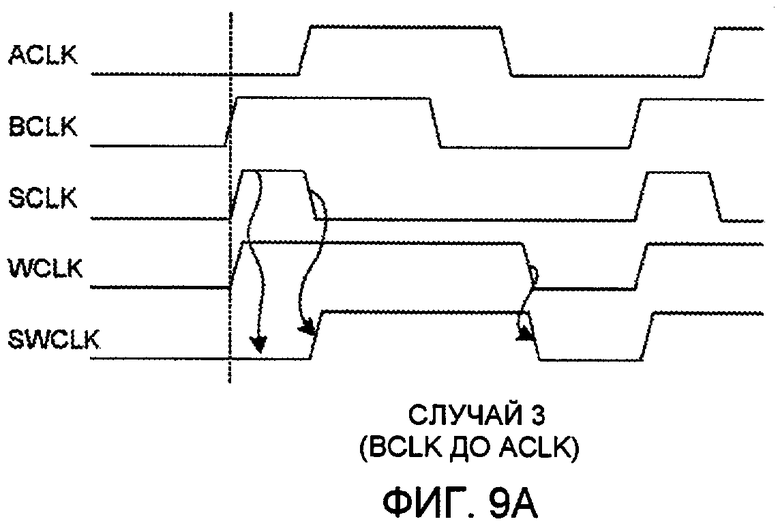

Фиг.9A - упрощенная схема формы сигнала третьего сценария (случай 3).

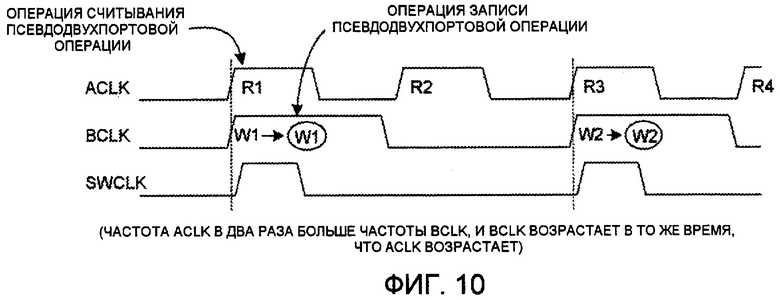

Фиг.10 - упрощенная схема формы сигнала первого примера, где частота ACLK выше частоты BCLK, но BCLK возрастает в то же время, когда возрастает и ACLK.

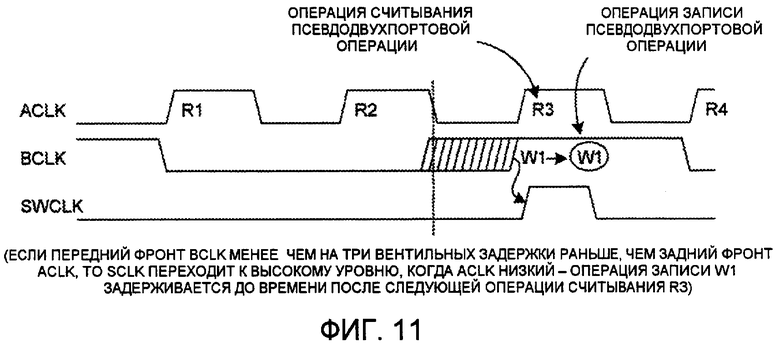

Фиг.11 - упрощенная схема формы сигнала второго примера, где частота BCLK возрастает в течение времени, когда ACLK имеет низкий уровень.

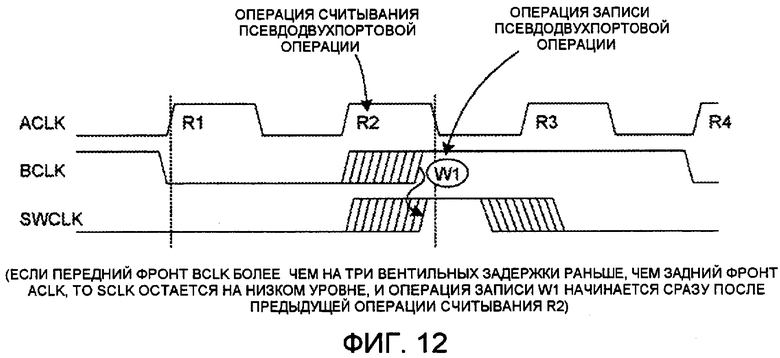

Фиг.12 - упрощенная схема формы сигнала третьего примера, где частота BCLK возрастает в течение времени, когда ACLK имеет высокий уровень.

ПОДРОБНОЕ ОПИСАНИЕ

Фиг.1 - это блок-схема высокого уровня псевдодвухпортового запоминающего устройства 1 в соответствии с одним вариантом осуществления. Запоминающее устройство 1 включает в себя массив 2 ячеек статической оперативной памяти. В проиллюстрированном примере массив 2 включает в себя две строки ячеек памяти, при этом каждая строка включает в себя шестнадцать ячеек памяти. Помимо массива 2 запоминающее устройство 1 включает в себя набор из восьми столбцовых мультиплексоров/демультиплексоров 3-10. Проиллюстрированы только первый и восьмой столбцовый мультиплексор/демультиплексор 3 и 10. Запоминающее устройство 1 также включает в себя защелку адресного входа, мультиплексор считывания/записи и схему 11 типа "защелка" ввода данных, схему 12 генератора синхронизирующих импульсов считывания, схему 13 генератора синхронизирующих импульсов записи, схему 14 мультиплексора с временной задержкой, схему 15 одноразового срабатывания и схему 16 подавителя синхронизирующих импульсов записи. Схема 16 подавителя синхронизирующих импульсов записи включает в себя схему 17 генератора синхронизирующих импульсов подавления и схему 18 подавителя. Схема в блоках 3-15 является управляющей схемой, которая управляет обращением к массиву 2.

Фиг.2 - это более подробная схема массива 2 памяти. Каждая из ячеек памяти является ячейкой памяти с шестью транзисторами. Ссылка с номером 19 идентифицирует ячейку памяти в верхнем левом углу массива. Четыре транзистора ячейки 19 памяти соединены между собой, чтобы сформировать пару инверторов 20 и 21 с перекрестными обратными связями. Первый узел D данных ячейки 19 памяти подключен к линии вывода инвертора 20 и подключен к линии ввода инвертора 21. Второй узел DN данных ячейки 19 памяти подключен к линии вывода инвертора 21 и подключен к линии ввода инвертора 20. Первый входной транзистор 22 предусмотрен таким образом, что узел D данных может быть выборочно подключен к вертикально идущей разрядной шине B0. Второй входной транзистор 23 предусмотрен таким образом, что узел DN данных может быть выборочно подключен к вертикально идущей разрядной шине B0N. Как проиллюстрировано, пары разрядных шин B0 и B0N, B1 и B1N,..., B15 и B15N идут через массив в вертикальном измерении. Например, пары разрядных шин B0 и B0N идут вертикально через левый крайний столбец ячеек памяти. Суффикс "N" в данной нотации указывает "не" или дополнение сигнала, имеющего такое же название сигнала, без суффикса "N". Пара числовых шин WL0 и WL1 идет через массив в горизонтальном направлении. Числовая шина WL0 подключена к затворам входных транзисторов различных ячеек памяти верхней строки ячеек памяти массива. Числовая шина WL1 подключена к затворам входных транзисторов различных ячеек памяти нижней строки ячеек памяти массива.

Фиг.3 - это более подробная схема восьми столбцовых мультиплексоров/демультиплексоров 3-10 по фиг.1. Каждый столбцовый мультиплексор/демультиплексор имеет две пары линий разрядной шины. Столбцовый мультиплексор/демультиплексор 3, к примеру, имеет линии, которые подключены к первой паре разрядных шин B0 и B0N, а также имеет линии, которые подключены ко второй паре разрядных шин B1 и B1N. Две пары разрядных шин проиллюстрированы, идущие сверху вниз в столбцовом мультиплексоре/демультиплексоре 3 на фиг.3.

Каждый столбцовый мультиплексор/демультиплексор принимает адрес RCA0 столбца считывания и его дополнение RCA0N. В ходе операции считывания одна из двух пар разрядных шин мультиплексируется посредством мультиплексора 24 на разностную пару линий ввода усилителя 25 считывания. То, какая именно из двух пар разрядных шин, определяется посредством значений RCA0 и RCA0N. Усилитель 25 считывания включает в себя защелку, которая защелкивает значение, выводимое на линию вывода данных столбцового мультиплексора/демультиплексора. Защелка является прозрачной, когда входной сигнал SENS имеет низкий уровень, и защелка защелкивается при переходе сигнала SENS от низкого. Линии DOUT[0:7] вывода данных запоминающего устройства 1 - это линии вывода данных восьми столбцовых мультиплексоров/демультиплексоров 3-10, соответственно.

Каждый столбцовый мультиплексор/демультиплексор также принимает внутренний синхронизирующий сигнал ICLK. Сигнал ICLK является сигналом предварительного заряда, который инструктирует предварительный заряд разрядных шин, когда ICLK имеет низкий уровень. Сигнал ICLK подробнее описывается ниже.

Каждый столбцовый мультиплексор/демультиплексор также принимает адрес WCA0 столбца записи и его дополнение WCA0N. Каждый столбцовый мультиплексор/демультиплексор также принимает входное значение данных, находящихся в защелке, и его дополнение. Первый столбцовый мультиплексор/демультиплексор 3, к примеру, принимает входное значение DIN[0] данных, находящихся в защелке, и его дополнение DINN[0]. В ходе операции записи входные значения DIN[0] и DINN[0] данных демультиплексируются посредством демультиплексора 26 на одну из двух пар разрядных шин, которые подключены к столбцовому мультиплексору/демультиплексору 3. Конкретная пара разрядных шин определяется посредством адреса WCA0 столбца записи и его дополнения WCA0N. Соответственно, в ходе операции считывания данные проходят из выбранной пары разрядных шин, через мультиплексор 24, через усилитель 25 считывания и на линию DOUT[0] вывода данных столбцового мультиплексора/демультиплексора 3. В ходе операции записи данные проходят из линий DIN[0] и DINN[0] ввода данных, через демультиплексор 26 и в выбранную пару разрядных шин B0 и B0N или B1 и B1N.

Фиг.4 - это более подробная схема типа "защелка" ввода адреса и узла мультиплексора считывания/записи для блока 11 по фиг.1. Схема по фиг.4 защелкивает поступающий двухбитовый адрес RADR[1:0] считывания, а также защелкивает поступающий двухбитовый адрес WADR[1:0] записи. Схема по фиг.4 выводит значения WL1 и WL0 числовых шин, значения RCA0 и RCA0N адресов столбцов считывания и значения WCA0 и WCA0N адресов столбцов записи.

Фиг.5 - это более подробная схема узла защелки ввода данных для блока 11 по фиг.1. Как проиллюстрировано, имеет восемь идентичных защелок 27-34 ввода данных, которые организованы параллельно таким образом, что они защелкивают восьмибитовое входное значение DATAIN[7:0] данных и выводят восьмибитовое значение DIN[7:0] данных, находящихся в защелке, и его дополнение DINN[7:0]. Синхронизирующий сигнал WCLK записи используется для того, чтобы защелкивать поступающее входное значение DATAIN[7:0] данных в восьми защелках ввода данных. Каждая защелка ввода данных является прозрачной, когда синхронизирующий сигнал WCLK записи имеет низкий уровень, и защелкивается, когда синхронизирующий сигнал WCLK записи переходит от низкого к высокому уровню. В защелке 27 ввода данных транзисторы, составляющие пропускной логический элемент 35, и инверторы 36 и 37 с перекрестными обратными связями вместе формируют прозрачную защелку 38. Цифровое значение, сохраненное в защелке ввода данных, а также дополнение сохраненного цифрового значения подаются на линии DIN[0] и DINN[0] данных защелки ввода данных, когда декодирующий синхронизирующий сигнал RWDCLK считывания/записи подтверждается высоким сигналом. С другой стороны, если сигнал RWDCLK имеет низкий уровень, то оба сигнала на линиях DIN[0] и DINN[0] вывода принудительно становятся высокими.

Фиг.6 - это более подробная схема 12 генератора синхронизирующих импульсов считывания, схемы 13 генератора синхронизирующих импульсов записи, схемы 14 мультиплексора с временной задержкой, схемы 15 одноразового срабатывания и схемы 16 подавителя синхронизирующих импульсов записи по фиг.1. Схема по фиг.6 выводит синхронизирующий сигнал RCLK считывания, синхронизирующий сигнал WCLK записи, внутренний синхронизирующий сигнал ICLK и синхронизирующий сигнал RWDCLK декодирования считывания/записи.

Работа псевдодвухпортового запоминающего устройства 1 описана ниже в связи со схемами формы сигнала по фиг.7-9. Фиг.7 - это схема формы сигнала первого сценария (случая 1), при котором передние фронты входного синхронизирующего сигнала ACLK для первого порта и входного синхронизирующего сигнала BCLK для второго порта возникают одновременно. Фиг.8 - это схема формы сигнала второго сценария (случая 2), при котором передний фронт входного синхронизирующего сигнала ACLK для первого порта предшествует переднему фронту входного синхронизирующего сигнала BCLK для второго порта. Фиг.9 - это схема формы сигнала третьего сценария (случая 3), при котором передний фронт входного синхронизирующего сигнала ACLK для второго порта предшествует переднему фронту входного синхронизирующего сигнала BCLK для первого порта. Названия сигналов, предваряемые на фиг.7-9 звездочкой, являются внешне предоставляемыми входными сигналами, которые предоставляются в псевдодвухпортовое запоминающее устройство 1.

Первоначально синхронизирующий сигнал ICLK имеет низкий уровень, как проиллюстрировано на фиг.7. ICLK подается в столбцовые мультиплексоры/демультиплексоры 3-10, проиллюстрированные на фиг.3. Когда ICLK имеет низкий уровень, P-канальные транзисторы 39-41 и 42-44 в каждом из столбцовых мультиплексоров/демультиплексоров являются токопроводящими. Все пары разрядных шин, следовательно, предварительно заряжены, чтобы подавать напряжение VCC. Этот предварительный заряд разрядных шин является первоначальным режимом.

Поскольку операция считывания должна быть выполнена, двухбитовый адрес RADR[1:0] считывания помещается в две линии 45 и 46 ввода адреса считывания псевдодвухпортовой памяти 1, и сигнал CSAN выборки при считывании подтверждается на линии 47 ввода псевдодвухпортовой памяти 1. Поскольку операция записи также должна быть выполнена, двухбитовый адрес WADR[1:0] записи помещается в две линии 48 и 49 ввода адреса записи псевдодвухпортовой памяти 1, и сигнал CSBN выборки при записи подтверждается на линии 50 ввода псевдодвухпортовой памяти 1. Восьмибитовое значение DATAIN[7:0] данных, которое должно быть записано в ходе операции записи, подается на восемь линий 51-58 ввода данных псевдодвухпортовой памяти 1. Линии 45 и 46 ввода адреса считывания, линия 59 ввода синхронизирующих импульсов считывания и линии 60-67 вывода данных составляют первый порт (порт только для считывания) псевдодвухпортового запоминающего устройства 1. Линии 48 и 49 ввода адреса записи, линия 68 ввода синхронизирующих импульсов записи и линии 51-58 ввода данных составляют второй порт (порт только для записи) псевдодвухпортового запоминающего устройства 1.

После того как информация по линиям 45-58 и 68 ввода установлена на период времени, первый входной синхронизирующий сигнал ACLK на линии 47 ввода и второй входной синхронизирующий сигнал BCLK на линии 50 ввода переходят к высокому уровню одновременно в момент времени T1 (см. фиг.7).

Когда первый входной синхронизирующий сигнал ACLK переходит к высокому уровню, значение сигнала CSAN выборки при считывании защелкивается в защелку схемы 12 генератора RCLK по фиг.6. Если CSAN имеет низкий уровень, то напряжение в узле 69 защелки опускается до земли и защелкивается посредством инверторов 70-71 с перекрестными обратными связями. Если CSAN имеет высокий уровень, то напряжение в узле 69 должно остаться в предыдущем защелкнутом состоянии. Как показывает диаграмма формы сигнала по фиг.7, CSAN имеет низкий уровень в ранее описанном примере работы. Цифровой низкий сигнал, следовательно, защелкивается в узле 69. Цифровой высокий сигнал, следовательно, защелкивается в узле 72. Цифровое значение в узле 72 - это значение синхронизирующего сигнала RCLK считывания. Синхронизирующий сигнал RCLK считывания, следовательно, переходит к высокому уровню, как проиллюстрировано на фиг.7.

Аналогично, синхронизирующий сигнал CSBN выборки при записи защелкивается в защелке генератора 13 синхронизирующих импульсов записи по фиг.6. Если CSBN имеет низкий уровень, то напряжение в узле 73 опускается до земли и защелкивается посредством инверторов 74-75 с перекрестными обратными связями. Если CSBN имеет высокий уровень, то напряжение в узле 73 остается в предыдущем защелкнутом состоянии. Как показывает диаграмма формы сигнала по фиг.7, CSBN имеет низкий уровень в ранее описанном примере работы. Цифровой низкий сигнал, следовательно, защелкивается в узле 73, а цифровой высокий сигнал защелкивается в узле 76. Цифровое значение в узле 76 - это значение синхронизирующего сигнала WCLK записи. Синхронизирующий сигнал WCLK записи, следовательно, переходит к высокому уровню, как проиллюстрировано на фиг.7.

В форме сигнала на фиг.7 и ACLK, и BCLK изначально являются цифровыми низкими сигналами. Поскольку ACLK является низким сигналом, цифровой высокий сигнал присутствует в узле 200 генератора 17 синхронизирующих импульсов подавления по фиг.6. P-канальный транзистор 201, следовательно, является нетокопроводящим. Поскольку BCLK был на низком уровне, цифровой низкий сигнал присутствует в узле 202 генератора 17 синхронизирующих импульсов подавления по фиг.6. N-канальный транзистор 203, следовательно, является нетокопроводящим. Следовательно, узел 204 остается защелкнутым, чтобы сохранять свое предыдущее цифровое значение. Когда ACLK переходит к высокому уровню, как проиллюстрировано на фиг.7, инвертор 205 подтверждает цифровой низкий сигнал в узле 200, тем самым инструктируя P-канальному транзистору 201 быть токопроводящим и инструктируя N-канальному транзистору 206 быть нетокопроводящим. Следовательно, узел 204 улучшается до цифрового высокого сигнала. Инверторы 207 и 208 с перекрестными обратными связями защелкиваются, так что напряжение в узле 209 является цифровым низким сигналом. Напряжение в узле 209 является синхронизирующим сигналом SCLK подавления. Пока ACLK является цифровым высоким сигналом, защелка генератора 17 синхронизирующих импульсов подавления удерживается в этом состоянии, вне зависимости от значения BCLK. Отметим на фиг.7, что сигнал SCLK является цифровым низким сигналом в момент времени T1 и остается цифровым низким сигналом после этого.

Защелка ввода адреса по фиг.4 включает в себя пару защелок 77 и 78 для защелкивания двух значений RADR[0] и RADR[1] бита адреса считывания, соответственно. Защелки 77 и 78 являются прозрачными, когда сигнал RCLK имеет низкий уровень, и защелкиваются на переднем фронте RCLK. Следовательно, значение RADR[0] защелкивается в узле 79 в защелке 77 на переднем фронте RCLK. Следовательно, значение RADR[1] защелкивается в узле 80 в защелке 78 на переднем фронте RCLK.

В момент времени T1 на диаграмме формы сигнала по фиг.7 RCLK имеет низкий уровень и еще не перешел к высокому уровню. Поэтому защелка 77 является прозрачной. Следовательно, RADR[0] присутствует в узле 79. Поскольку RCLK имеет низкий уровень, логический элемент 81 И-НЕ выводит цифровой высокий сигнал. Логическая схема 82, следовательно, подтверждает, что RCA0 и RCA0N имеют высокий уровень. Поскольку RCA0 и RCA0N имеют высокий уровень и приводят P-канальные транзисторы демультиплексоров записи в столбцовых мультиплексорах/демультиплексорах по фиг.3, демультиплексоры записи отключаются, и разрядные шины не подключаются к линиям ввода усилителей считывания столбцовых мультиплексоров/демультиплексоров. Демультиплексор записи отключается, поскольку операция, которая должна быть выполнена следом - это операция считывания.

В момент времени T1 на диаграмме формы сигнала по фиг.7 RCLK имеет низкий уровень, и защелка 78 прозрачная. Следовательно, RADR[1] присутствует в узле 80. Поскольку RWDCLK является цифровым низким сигналом, как проиллюстрировано на фиг.7, защелкнутое значение RADR[1] в узле 80 (см. фиг.4) предоставляется через мультиплексор 83 в узел 84. Поскольку ICLK имеет низкий уровень, логическая схема 85 блокирует сигнал на узле 84 от вывода на линии 86 и 87 вывода числовых шин. Цифровые низкие сигналы имеются на линиях 86 и 87 вывода числовых шин. Поскольку входные транзисторы ячеек памяти по фиг.4 являются N-канальными транзисторами, низкие сигналы в WL0 и WL1 не допускают токопроводности каких-либо входных транзисторов в массиве 2.

Защелка ввода адреса по фиг.4 дополнительно включает в себя вторую пару защелок 88 и 89 для защелкивания двух значений WADR[0] и WADR[1] бита адреса записи, соответственно. Защелки 88 и 89 являются прозрачными, когда сигнал WCLK имеет низкий уровень, и защелкиваются на переднем фронте WCLK. Следовательно, значение WADR[0] защелкивается в узле 90 в защелке 88 на переднем фронте WCLK. Следовательно, значение WADR[1] защелкивается в узле 91 в защелке 89 на переднем фронте WCLK.

В момент времени T1 на диаграмме формы сигнала по фиг.7 WCLK имеет низкий уровень и еще не перешел к высокому уровню. Поэтому защелка 88 является прозрачной. Следовательно, WADR[0] присутствует в узле 90. Поскольку WCLK имеет низкий уровень, логический элемент 92 И-НЕ выводит цифровой высокий сигнал. Логическая схема 93, следовательно, принудительно задает WCA0 и WCA0N низкими. Поскольку WCA0 и WCA0N имеют высокий уровень и приводят N-канальные транзисторы демультиплексоров в столбцовых мультиплексорах/демультиплексорах по фиг.3, демультиплексоры отключаются, и разрядные шины не подключаются к линиям DIN[7:0] и DINN[7:0] ввода данных столбцовых мультиплексоров/демультиплексоров.

В момент времени T1 на диаграмме формы сигнала по фиг.7 WCLK имеет низкий уровень, и защелка 89 прозрачная. Следовательно, WADR[1] присутствует в узле 91. Поскольку RWDCLK является цифровым низким сигналом, как проиллюстрировано на фиг.7, значение в узле 91 не предоставляется через мультиплексор 83 в узел 84.

В момент времени T1 ICLK имеет низкий уровень. Транзисторы 39-44 в столбцовых мультиплексорах/демультиплексорах 3-10 поэтому являются токопроводящими. Разрядные шины каждой пары разрядных шин соединены вместе и подключены к питающему напряжению VCC. Следовательно, как говорят, разрядные шины предварительно заряжаются.

Далее внешне подаваемый первый входной синхронизирующий сигнал ACLK и внешне подаваемый второй входной синхронизирующий сигнал BCLK переходят к высокому уровню. Два синхронизирующих сигнала ACLK и BCLK переходят к высокому уровню одновременно.

До перехода сигнала ACLK, сигнал ACLK был цифровым низким сигналом. CSAN был цифровым низким сигналом, как указано посредством формы сигнала по фиг.7. Логический элемент 94 ИЛИ-НЕ по фиг.6, следовательно, подавал цифровой высокий сигнал на затвор N-канального транзистора 95. Когда ACLK переходит к высокому уровню, высокий сигнал присутствует на затворе N-канального транзистора 96. Оба N-канальных транзистора 96 и 95, следовательно, являются токопроводящими в течение короткого периода времени до тех пор, пока цифровой высокий сигнал ACLK не распространится через инверторы 97 и 98 и логический элемент 94 ИЛИ-НЕ, чтобы принудительно сделать напряжение на затворе N-канального транзистора 95 низким. Напряжение в узле 69, следовательно, моментально понижается до нуля через транзисторы 96 и 95. Напряжение в узле 69 тем самым защелкивается до цифрового низкого сигнала, а напряжение в узле 72 защелкивается до цифрового высокого сигнала. Это проиллюстрировано в форме сигнала по фиг.7 посредством перехода от низкого уровня к высокому сигнала RCLK.

Подобное происходит в WCLK-генераторе 13. До перехода от низкого уровня к высокому сигнала BCLK, CSAB был цифровым низким сигналом, как указано посредством формы сигнала по фиг.7. Логический элемент 99 ИЛИ-НЕ по фиг.6, следовательно, подавал цифровой высокий сигнал на затвор N-канального транзистора 100. Когда BCLK переходит к высокому уровню, высокий сигнал присутствует на затворе N-канального транзистора 101. Оба N-канальных транзистора 101 и 100, следовательно, являются токопроводящими в течение короткого периода времени до тех пор, пока цифровой высокий сигнал CLK не распространится через инверторы 102 и 103 и логический элемент 99 ИЛИ-НЕ, чтобы принудительно сделать напряжение на затворе N-канального транзистора 100 низким. Напряжение в узле 73, следовательно, моментально понижается до нуля через транзисторы 101 и 100. Напряжение в узле 73 тем самым защелкивается до цифрового низкого сигнала, а напряжение в узле 76 защелкивается до цифрового высокого сигнала. Это проиллюстрировано в форме сигнала по фиг.7 посредством перехода от низкого уровня к высокому сигнала WCLK.

Когда RCLK переходит к высокому уровню, защелки 77 и 78 по фиг.4 защелкивают значения RADR[0] и RADR[1] адреса считывания в узлы 79 и 80, соответственно. Это проиллюстрировано на форме сигнала, помеченной LATCHED AADR[1:0] на фиг.7, посредством вертикальной пунктирной линии. Поскольку RCLK имеет высокий уровень, а RWDCLK имеет низкий уровень, логический элемент 81 И-НЕ выводит цифровой низкий сигнал. Логическая схема 82, следовательно, не задает RCA0 и RCA0N высокими по уровню, как раньше. Значение RADR[0] в защелке для узла 79 выводится как RCA0, а его дополнение выводится как RCA0N. Значения адресов столбцов считывания подаются в столбцовые мультиплексоры/демультиплексоры 3-10 при подготовке к предстоящей операции считывания. Это представлено на фиг.7 посредством формы сигнала, помеченной как COLUMN ADR TO COL MUX. Как видно на фиг.3, адреса RCA0 и RCA0N столбцов считывания инструктируют мультиплексору 24 считывания выбрать одну из пар разрядных шины и подключить выбранную пару к линиям ввода усилителя 25 считывания.

Когда WCLK переходит к высокому уровню, защелки 88 и 89 по фиг.4 защелкивают значения WADR[0] и WADR[1] адреса считывания в узлы 90 и 91, соответственно. Это проиллюстрировано на форме сигнала, помеченной LATCHED BADR[1:0] на фиг.7, посредством вертикальной пунктирной линии. Поскольку сигнал RWDCLK является цифровым высоким сигналом, тем не менее логический элемент 92 ИЛИ-НЕ по фиг.4 продолжает выводить цифровой высокий сигнал, и логическая схема 93 продолжает принудительно направлять значения WCA0 и WCA0N адресов столбцов низкого уровня к их неактивным состояниям. Значение WADR[1] адреса, которое зафиксировано в узле 91, блокируется от вывода в числовую шину WL, поскольку RWDCLK является цифровым низким сигналом и выбирает верхнюю линию ввода мультиплексора 83.

Возвращаясь к фиг.6, переход от высокого уровня к низкому в узле 69 подается на нижнюю линию ввода логического элемента 104 И-НЕ. Логический элемент 104 И-НЕ, следовательно, обнаруживает, что внутренний синхронизирующий сигнал ICLK имеет высокий уровень. Это представлено на фиг.7 посредством перехода от низкого уровня к высокому сигнала ICLK. Когда ICLK переходит к высокому уровню, предварительный заряд разрядных шин массива 2 прекращается. Транзисторы 39-44 предварительного заряда по фиг.3 становятся нетокопроводящими при подготовке к предстоящей операции считывания.

Когда ICLK переходит к высокому уровню, логическая схема 85 по фиг.4 более не задает принудительно цифровой логический уровень низким для сигналов в обеих числовых шинах. Фиксируемое в защелке значение адреса RADR[1] считывания в узле 80, следовательно, выводится на линию 86 вывода числовой шины WL1. Дополнение значения адреса считывания выводится на линию 87 вывода числовой шины WL0. Следовательно, цифровой высокий сигнал присутствует на одной из числовых шин WL0 и WL1. Это представлено в форме сигнала по фиг.7 посредством перехода от низкой к высокой форме сигнала, помеченной как WL (ONE OF WL0 AND WL1). Как видно на фиг.2, высокое значение в числовой шине инструктирует всем входным транзисторам всех ячеек памяти ассоциативно связанной строки шестнадцати ячеек памяти стать токопроводящими. Одно полное шестнадцатибитовое значение выводится из массива 2 в восемь столбцовых мультиплексоров/демультиплексоров. Восемь столбцовых мультиплексоров 3-10 выбирают одно восьмибитовое значение, чтобы вывести на линии вывода данных памяти на основе значений RCA0 и RCA0N адресов считывания. Дифференциальные напряжения на выбранных парах разрядных шин соединяются через столбцовые мультиплексоры/демультиплексор и на линии ввода усилителей считывания столбцовых мультиплексоров/демультиплексоров. Результирующее восьмибитовое значение выводится на линии 60-67 вывода запоминающего устройства 1. Вывод восьмибитового значения данных проиллюстрирован на фиг.7 в момент времени T2 в форме сигнала, помеченной DOUT[7:0](READ).

Обращаясь к фиг.6, схема 105 одноразового срабатывания обнаруживает переход от низкого уровня к высокому сигнала ICLK. После задержки схема 105 одноразового срабатывания выводит высокий импульс сигнала RESET. Это проиллюстрировано на фиг.7 посредством первого высокого импульса в форме сигнала, помеченной RESET. На фиг.7 пунктирная стрелка, помеченная A, представляет задержку, вводимую посредством схемы 105 одноразового срабатывания.

Пульсирующий высокий сигнал RESET инструктирует RCLK перейти к низкому уровню, поскольку высокое значение RESET присутствует на верхней линии ввода логического элемента 106 И-НЕ по фиг.6. RDWCLK является цифровым низким сигналом, так что цифровой высокий сигнал также присутствует на нижней линии ввода логического элемента 106 И-НЕ. Логический элемент 106 И-НЕ, следовательно, выводит цифровой низкий сигнал, тем самым инструктируя P-канальному транзистору 107 стать токопроводящим. Узел 69 переводится к высокому уровню, поскольку 69 соединен с VCC через транзистор 107. Сигнал RCLK в узле 72, следовательно, переходит к низкому уровню. Это проиллюстрировано на фиг.7 посредством перехода от низкого уровня к высокому формы сигнала RCLK. Следовательно, видно, что мультиплексор 14 с временной задержкой и схема 105 одноразового срабатывания функционируют вместе для того, чтобы очистить сигнал RCLK до низкого уровня в конце операции считывания.

Цифровой высокий сигнал присутствует на верхней линии ввода логического элемента 104 И-НЕ на фиг.6. Следовательно, ICLK имеет низкий уровень. Когда напряжение в узле 86 переходит к высокому уровню, цифровой высокий сигнал также присутствует на нижней линии ввода логического элемента 104 И-НЕ. Логический элемент 104 И-НЕ, следовательно, выводит цифровой низкий сигнал. Это проиллюстрировано на фиг.7 посредством перехода от низкого уровня к высокому формы сигнала RCLK. Транзисторы 39-44 предварительного заряда в столбцовых мультиплексорах/демультиплексорах, следовательно, повторно делаются токопроводящими, чтобы начать операцию предварительного заряда для предстоящей операции записи.

До того как вывод данных из запоминающего устройства может быть изменен вследствие предварительного заряда, сигнал SENS считывания подается в защелку усилителей считывания в столбцовых мультиплексорах/демультиплексорах. Переход от низкого уровня к высокому сигнала SENS вызывает защелкивание защелок в столбцовых мультиплексорах/демультиплексорах и сохранение значения данных, которые являются считываемыми, на линиях 60-67 вывода запоминающего устройства 1. Схема одноразового срабатывания (не показана) формирует сигнал SENS и посылает импульсы сигнала SENS до высокого уровня по заднему фронту сигнала ICLK, когда RWDCLK имеет низкий уровень. Защелкивание выходных данных считается окончанием операции считывания.

Переход RCLK к низкому уровню, когда WCLK является цифровым высоким сигналом, инструктирует цифровому низкому сигналу присутствовать на обеих линиях ввода логического элемента 108 ИЛИ-НЕ в мультиплексоре 14 с временной задержкой по фиг.6. Логический элемент 108 ИЛИ-НЕ, следовательно, выводит цифровой высокий сигнал. Этот сигнал распространяется через инверторы 109 и 110. Следовательно, RWDCLK переходит к высокому уровню, как проиллюстрировано на фиг.7 посредством перехода от низкого уровня к высокому в форме сигнала, помеченной RWDCLK.

Возвращаясь к фиг.4, переход от низкого уровня к высокому сигнала RWDCLK инструктирует значениям адресов записи выводиться из защелки ввода адреса по фиг.4. Высокий RWDCLK инструктирует цифровому низкому присутствовать на верхней линии ввода логического элемента 81 И-НЕ. Логический элемент 81 ИЛИ-НЕ, следовательно, выводит цифровой высокий сигнал. Это инструктирует логической схеме 82 принудительно присваивать RCA0 и RCA0N цифровые высокие значения. Принудительное задание RCA0 и RCA0N высокими инструктирует мультиплексору 24 считывания в столбцовых мультиплексорах/демультиплексорах по фиг.3 не подключать разрядные шины к усилителям считывания.

Возвращаясь к фиг.4, высокий RWDCLK инструктирует логическому элементу 92 И-НЕ выводить цифровой высокий сигнал. Следовательно, логическая схема 93 более не блокирует значение WADR[0] адреса записи, зафиксированное в защелке 88 от вывода в WCA0 и WCA0N. Значение WADR[0] адреса столбца записи, следовательно, передается через логическую схему 93 в демультиплексор 26 записи в столбцовом мультиплексоре/демультиплексоре по фиг.3. Входные значения данных по DIN[7:0] и DINN[7:0], следовательно, передаются через демультиплексор записи столбцовых мультиплексоров/демультиплексоров в выбранный набор из восьми пар разрядных шин. То, какой набор из восьми пар выбирается, определяется посредством значений WCA0 и WCA0N. На фиг.3 значения данных передаются через демультиплексор записи и в массив 2 памяти с тем, чтобы значения данных могли быть записаны в строку ячеек памяти, идентифицированную посредством значений WL0 и WL1 адресов числовых шин.

Возвращаясь к фиг.6, переход от низкого уровня к высокому RWDCLK продолжает распространяться через инверторы 111 и 112 и на верхнюю линию ввода логического элемента 113 И-НЕ. Поскольку SCLK является цифровым низким сигналом, инвертор 210 в схеме 18 подавления выводит цифровой высокий сигнал на нижнюю линию ввода логического элемента 211 И-НЕ. Поскольку WCLK является цифровым высоким сигналом, логический элемент 211 И-НЕ выводит цифровой низкий сигнал, и инвертор 212 подтверждает, что сигнал SWCLK имеет высокий уровень. Соответственно, когда SCLK имеет низкий уровень, синхронизирующий импульс WCLK записи стробируется через схему 18 подавления и выводится как SWCLK.

Поскольку цифровой высокий сигнал SWCLK присутствует на нижней линии ввода логического элемента 113 И-НЕ в мультиплексоре 14 с временной задержкой, переход от низкого уровня к высокому на верхней линии ввода логического элемента 113 И-НЕ инструктирует логическому элементу 113 И-НЕ выводить цифровой низкий сигнал, который инвертирован посредством инвертора 114. Цифровой высокий сигнал, следовательно, подтверждается на верхней линии ввода логического элемента 115 И-НЕ. Цифровой высокий сигнал уже присутствует на нижней линии ввода логического элемента 115 И-НЕ вследствие низкого значения сигнала RESET, инструктируя логическому элементу 116 схемы 13 генератора WCLK выводить цифровой высокий сигнал. Следовательно, логический элемент 115 И-НЕ выводит цифровой низкий сигнал, тем самым инструктируя логическому элементу 104 И-НЕ подтверждать ICLK на высоком уровне. Эта задержка на распространения от переднего фронта RWDCLK к переднему фронту ICLK показана на фиг.7 посредством пунктирной стрелки, помеченной B. Передний фронт ICLK сигнала завершает предварительный заряд операции записи.

Возвращаясь к фиг.4, передний фронт ICLK подается в логическую схему 85. Следовательно, логическая схема 85 более не задает WL0 и WL1 на низком уровне, а вместо этого дает возможность вывода значения WADR[1] адреса записи в узле 84 на линию 86 вывода числовой шины WL1. Значение адреса записи, которое защелкнуто в узле 91, мультиплексируется в узле 84 вследствие того, что значение RWDCLK является цифровым высоким сигналом в ходе операции записи. Результат заключается в том, что значение WADR[1] адреса записи выводится на линию 86 вывода WL1, а его дополнение выводится на линию 87 вывода WL0. Это проиллюстрировано на фиг.7 посредством перехода к форме сигнала, помеченной WL (ONE OF WL0 AND WL1).

Значения WADR[0] и WADR[1] адресов записи, следовательно, используются для того, чтобы адресовать массив 2 памяти в ходе операции записи. Это представлено на фиг.7 посредством метки WCA, которая отображается в форме сигнала, помеченной как COLUMN ADR TO COL MUX. Данные в восьми адресуемых ячейках памяти могут переключаться в момент времени T3, как проиллюстрировано на фиг.7.

Возвращаясь к фиг.6, переход от низкого уровня к высокому ICLK повторно обнаруживается посредством схемы 105 одноразового срабатывания. После задержки, представленной на фиг.7 посредством пунктирной стрелки, помеченной C, схема 105 одноразового срабатывания выводит высокий импульс сигнала RESET. Высокий импульс сигнала RESET подтверждается на верхней линии ввода логического элемента 116 И-НЕ. Поскольку RWDCLK имеет высокий уровень, имеются цифровые высокие сигналы на обеих линиях ввода логического элемента 116 И-НЕ. Логический элемент 116 И-НЕ приводит цифровой низкий сигнал в затворе P-канального транзистора 117, тем самым защелкивая цифровой высокий сигнал в узле 73 схемы 13 WCLK-генератора. Сигнал WCLK в узле 76, следовательно, переходит к низкому уровню. Это проиллюстрировано на фиг.7 посредством перехода от высокого к низкому уровню формы сигнала WCLK. Мультиплексор 14 с временной задержкой и схема 105 одноразового срабатывания, следовательно, вместе вызывают сброс сигнала WCLK до низкого уровня в конце операции записи.

Переход WCLK к низкому уровню инструктирует логическому элементу 221 И-НЕ в схеме 18 подавителя выводить цифровой высокий сигнал. Инвертор 212, следовательно, принудительно переводит SWCLK к низкому уровню. WCLK, следовательно, стробируется через схему 18 подавителя, поскольку сигнал SCLK подавления находится на низком уровне.

Переход SWCLK к низкому уровню инструктирует логическому элементу 113 И-НЕ в мультиплексоре 14 с временной задержкой выводить цифровой высокий сигнал. Инвертор 114 выводит цифровой низкий сигнал, тем самым инструктируя логическому элементу 115 И-НЕ выводить цифровой высокий сигнал. Поскольку RCLK является цифровым низким сигналом, напряжение в узле 69 схемы 12 RCLK-генератора является цифровым высоким сигналом. Имеются цифровые высокие сигналы на обеих линиях ввода логического элемента 104 И-НЕ, тем самым инструктируя логическому элементу 104 И-НЕ подтверждать ICLK на низком уровне. Это проиллюстрировано на фиг.7 посредством второго перехода от высокого уровня к низкому сигнала RCLK.

Переход SWCLK к низкому уровню также инструктирует цифровому высокому сигналу присутствовать на нижней линии ввода логического элемента 108 ИЛИ-НЕ по фиг.6. Логический элемент 108 ИЛИ-НЕ выводит цифровой низкий сигнал, который распространяется через инверторы 109 и 110, тем самым инструктируя RWDCLK переходить к низкому уровню на конец операции записи. Это проиллюстрировано на фиг.7 посредством перехода от высокого к низкому уровню формы сигнала, помеченной RWDCLK. В этой точке инициируется предварительный заряд-разрядные шины массива 2 памяти для последующей операции обращения к памяти.

Следовательно, обнаружено, что псевдодвухпортовое запоминающее устройство 1 выполняет операцию считывания, после которой следует операция записи. Окончание операции считывания и начало операции записи не зависят от заднего фронта входного синхронизирующего сигнала. Вместо этого асинхронные задержки на распространение через логическую схему и схему одноразового срабатывания используются для того, чтобы синхронизировать управляющие сигналы, требуемые для того, чтобы выполнять первую операцию записи, предварительно заряжать разрядные шины памяти и выполнять вторую операцию записи. Периоды времени задержки A, задержки B и задержки C могут быть увеличены или уменьшены в ходе конструирования запоминающего устройства, чтобы изменить относительный интервал времени, которое предоставляется для операции считывания, в сравнении с операцией записи.

Фиг.7A - это упрощенная схема формы сигнала для случая 1. Задний фронт ACLK и BCLK совпадает. SCLK остается на низком уровне и никогда не переходит к высокому уровню. Схема 18 подавителя по фиг.6, следовательно, всегда передает значение WCLK так, чтобы быть значением SWCLK. Сигнал SWCLK подается в мультиплексор 14 с временной задержкой вместо WCLK. Мультиплексор 14 с временной задержкой, следовательно, принимает RCLK и SWCLK (которые имеют такую же синхронизацию, что и WCLK) и формирует сигнал RWDCLK с временной задержкой, с тем чтобы выполнять операцию считывания после операции записи.

В вышеописанном сценарии должна быть выполнена и операция считывания, и операция записи. В сценарии, в котором должна быть выполнена только операция считывания, RCLK должен быть защелкнут на высоком уровне, RWDCLK должен быть принудительно переведен на низкий уровень для операции считывания, схема 105 одноразового срабатывания затем должна сбросить RCLK на низкий уровень, но CLK не должен быть защелкнут на высоком уровне. Следовательно, RWDCLK не должен быть принудительно переведен на высокий уровень в конце операции считывания, и не должно быть второй операции считывания.

Аналогично, в сценарии, в котором только операция записи должна быть выполнена, WCLK должен быть защелкнут на высоком уровне, но RCLK не должен быть защелкнут на высоком уровне. Следовательно, RWDCLK должен быть принудительно переведен на высокий уровень для операции записи, схема 105 одноразового срабатывания после этого должна сбросить WCLK на низкий уровень по окончании операции считывания, но не должно быть второй операции с памятью.

Рассмотрим ситуацию, при которой WCLK защелкнут на высоком уровне, когда RCLK еще не защелкнут на высоком уровне. Мультиплексор 14 с временной задержкой должен подтверждать высокий уровень RWDCLK для операции записи, и операция записи должна быть инициирована так, как описано выше, в режиме, при котором операция записи должна быть выполнена, но операция считывания не должна быть выполнена. Если RCLK затем защелкнут на высоком уровне (как в случае 3) в случае попытки считывания с первого порта, то логический элемент 108 в мультиплексоре 14 с временной задержкой должен выводить цифровой низкий сигнал, низкий сигнал должен распространяться через инверторы 109 и 110, и RWDCLK должен быть подтвержден как на низком уровне. Подтверждение низкого уровня RWDCLK до завершения операции записи, тем не менее, может вызывать некорректное функционирование псевдодвухпортового запоминающего устройства. Генератор 17 синхронизирующих импульсов подавления и схема 18 подавителя предотвращают такую ситуацию посредством подавления подтверждения высокого уровня WCLK, как он представляется в мультиплексор 14 с временной задержкой (WCLK представляется в мультиплексор 14 с временной задержкой как SWCLK), до тех пор, пока сигнал RCLK не перешел к высокому уровню. Подавление WCLK таким образом предотвращает некорректное функционирование, которое в ином случае произошло бы, если бы RCLK был подтвержден вскоре после того, как инициирована операция записи.

Фиг.8 - это схема формы сигнала, которая иллюстрирует работу псевдодвухпортового запоминающего устройства 1 в случае 2. В случае 2 первый входной синхронизирующий сигнал ACLK, который подается в первый порт памяти, подтверждается высоким уровнем сначала в момент времени T1A. Значения CSAN и AADR[1:0], следовательно, защелкиваются в памяти вскоре после момента времени T1A. Второй входной синхронизирующий сигнал BCLK, который подается на второй порт памяти, подтверждается через некоторое время после времени T1B. Значения CSBN и BADR[1:0], DATAIN[7:0], следовательно, защелкиваются в памяти вскоре после момента времени T1B.

Поскольку операция считывания должна осуществляться до операции записи, раннее возрастание ACLK инструктирует подтверждение RCLK. RCLK, в свою очередь, инициирует операцию считывания до переднего фронта BCLK. Когда операция считывания завершена, как определено посредством задержки A на распространение и последующего заднего фронта RCLK, мультиплексор 14 с временной задержкой по фиг.6 подтверждает RWDCLK, чтобы инициировать операцию записи. Синхронизирующий сигнал WCLK записи, который подтвержден в это время, стробируется через схему 18 подавителя и подается в мультиплексор 14 с временной задержкой в форме SWCLK. Когда операция считывания завершена, мультиплексор 14 с временной задержкой, следовательно, может инициировать операцию записи.

Фиг.8A - это упрощенная схема формы сигнала для случая 2. Передний фронт ACLK предшествует переднему фронту BCLK. SCLK остается на низком уровне и никогда не переходит к высокому уровню. Схема 18 подавителя по фиг.6, следовательно, никогда не подавляет WCLK. WCLK стробируется через схему 18 подавителя и подается в мультиплексор 14 с временной задержкой как SWCLK. Поскольку сигнал SWCLK записи присутствует в мультиплексоре 14 с временной задержкой в то время, когда операция считывания выполнена, мультиплексор 14 с временной задержкой может инициировать операцию записи таким же образом, как и в случае 1.

Фиг.9 - это схема формы сигнала, которая иллюстрирует работу псевдодвухпортового запоминающего устройства 1 в случае 3. В случае 3 второй входной синхронизирующий сигнал BCLK, который подается во второй порт памяти, подтверждается сначала в момент времени T1A. Значения CSBN и BADR[1:0], DATAIN[7:0] для операции записи, следовательно, защелкиваются в памяти вскоре после момента времени T1B. Первый входной синхронизирующий сигнал ACLK, который подается на первый порт памяти, подтверждается через некоторое время после времени T1A. Значения CSAN и AADR[1:0] для операции считывания, следовательно, защелкиваются в памяти вскоре после момента времени T1A.

Поскольку операция записи должна осуществляться после операции считывания, раннее возрастание BCLK не может быть разрешено для того, чтобы подтвердить высокий уровень SWCLK, с тем, чтобы операция записи была инициирована. Синхронизирующий импульс SCLK подавления, следовательно, подтверждается на высоком уровне в течение начального периода (приблизительно между временем T1B и временем T1A) до тех пор, пока синхронизирующий импульс ACLK считывания не перейдет к высокому уровню. В течение этого начального периода SCLK подавляет синхронизирующий импульс записи, который подается в мультиплексор 14 с временной задержкой (синхронизирующий импульс WCLK записи подается в мультиплексор 14 с временной задержкой как SWCLK). Подавление SWCLK в ходе этого начального периода предотвращает инициирование посредством мультиплексора 14 с временной задержкой операции записи до операции считывания.

Формирование синхронизирующего импульса SCLK подавления поясняется в связи с фиг.6. ACLK в это время имеет низкий уровень. Следовательно, инвертор 205 выводит цифровой высокий сигнал в узел 200. P-канальный транзистор 201 поэтому является нетокопроводящим, а N-канальный транзистор 206 является токопроводящим. BCLK первоначально имеет низкий уровень, а затем переходит к высокому уровню. Поэтому инверторы 213-215 первоначально выводят цифровой высокий сигнал в затвор N-канального транзистора 216. Следовательно, транзистор 216 первоначально является проводящим, но узел 204 не подключен к земле, поскольку N-канальный транзистор 203 является нетокопроводящим. Когда BCLK переходит к высокому уровню, напряжение в узле 202 переходит к высокому уровню, тем самым делая N-канальный транзистор 203 токопроводящим. Тем не менее, для высокого сигнала в узле 202 необходимо время на то, чтобы распространиться через инверторы 213-215, чтобы принудительно перевести затвор N-канального транзистора 216 к низкому уровню и отключить транзистор 216. Следовательно, в течение короткого периода времени после переднего фронта BCLK все три N-канальных понижающих транзистора 203, 216 и 206 являются токопроводящими, и узел 204 на мгновение подключается к потенциалу земли. Мгновенное подключение к потенциалу земли защелкивает цифровой низкий сигнал в узле 204. Синхронизирующий импульс SCLK подавления в узле 209, следовательно, подтверждается на высоком уровне. Это проиллюстрировано на фиг.9 посредством переднего фронта формы сигнала, помеченной SCLK.

Даже если WCLK возрастает на короткое время после момента времени T1B, высокое значение синхронизирующего импульса SCLK подавления подавляет синхронизирующий сигнал SWCLK записи, подаваемый в мультиплексор 14 с временной задержкой. Это состояние продолжается до тех пор, пока входной синхронизирующий сигнал ACLK для порта считывания не перейдет к высокому уровню. Когда ACLK переходит к высокому уровню, инвертор 205 выводит цифровой низкий сигнал в узел 200. P-канальный повышающий транзистор 201 становится токопроводящим, и узел 204 защелкивается и поддерживается на высоком уровне. Следовательно, SCLK защелкивается и поддерживается на низком уровне, тем самым завершая начальный период времени, когда синхронизирующий импульс SCLK подавления подтверждается. Передние фронты RCLK и SWCLK, следовательно, представляются в мультиплексор 14 с временной задержкой практически одновременно.

Фиг.9A - это упрощенная схема формы сигнала для случая 3. Передний фронт ACLK предшествует переднему фронту ACLK. Передний фронт BCLK, когда ACLK имеет низкий уровень, инструктирует защелке в генераторе 17 синхронизирующих импульсов подавления по фиг.6 защелкнуть цифровой низкий сигнал в узле 204, тем самым защелкивая синхронизирующий сигнал SCLK подавления на высоком уровне. Схема 18 подавителя по фиг.6, следовательно, подавляет SWCLK и поддерживает SWCLK на низком уровне в течение времени, когда SCLK имеет высокий уровень. Когда ACLK переходит к высокому уровню, цифровой высокий сигнал защелкивается в узле 204 генератора 17 синхронизирующих импульсов, тем самым защелкивая SCLK на низком уровне. Поэтому SWCLK более не поддерживается на низком уровне посредством схемы 18 подавителя. Значение синхронизирующего импульса WCLK записи является значением SWCLK для оставшихся операций считывания и записи. Мультиплексор 14 с временной задержкой и схема 105 одноразового срабатывания инициируют операцию считывания и затем операцию записи, как в случаях 1 и 2.

Фиг.10 - это упрощенная схема формы сигнала, иллюстрирующая работу псевдодвухпортовой памяти 1 в случае, когда ACLK имеет более высокую частоту, чем BCLK. Первый передний фронт ACLK возникает в то же время, что и первый передний фронт BCLK. Это ситуация по фиг.7. Первая операция записи следует после первой операции считывания. В случае по фиг.10 нет переднего фронта BCLK в течение времени второго переднего фронта ACLK. Второй передний фронт ACLK на фиг.10, следовательно, приводит ко второй операции считывания. В примере третий передний фронт ACLK возникает в то же время, что и второй передний фронт BCLK. Это ситуация по фиг.7. Вторая операция записи следует после третьей операции считывания.

Фиг.11 - это упрощенная схема формы сигнала, иллюстрирующая работу псевдодвухпортовой памяти 1 в случае, когда передний фронт BCLK возникает в первое время в ходе части низкого уровня ACLK. Передний фронт BCLK инструктирует подтверждение SCLK, тем самым подавляя SWCLK до третьего переднего фронта ACLK. Следовательно, операция записи задерживается до времени после третьей операции считывания.

Фиг.12 - это упрощенная схема формы сигнала, иллюстрирующая работу псевдодвухпортовой памяти 1 в случае, когда передний фронт BCLK возникает более чем за три вентильных задержки до заднего фронта ACLK. BCLK, следовательно, возрастает в течение времени, когда ACLK имеет высокий уровень. В этом случае ACLK имеет высокий уровень и удерживает узел 204 повышенным до VCC, когда передний фронт BCLK пытается моментально понизить узел 204 до земли. Поскольку N-канальный транзистор 206 является нетокопроводящим, узел 204 не понижается до земли, и SCLK не защелкивается на высоком уровне. Поэтому SWCLK не подавляется в течение начального периода. Следовательно, SWCLK проиллюстрирован переходящим к высокому уровню вскоре после того, как BCLK переходит к высокому уровню. Это инструктирует операции записи выполняться сразу после второй операции считывания. Вторая операция считывания в форме сигнала по фиг.12 является операцией считывания, обусловленной вторым передним фронтом ACLK.

Периоды времени задержки A, задержки B и задержки C могут быть увеличены или уменьшены в ходе конструирования запоминающего устройства, чтобы изменить относительную пропорцию времени, которое предоставляется для операции считывания, в сравнении с операцией записи. Окончание операции считывания может перекрывать начало операции записи по времени. В некоторых реализациях запоминающего устройства операции считывания может предоставляться больше времени, чем операции записи. В других реализациях операции записи может предоставляться больше времени, чем операции считывания. Проблемы, ассоциативно связанные с инициированием операции записи с помощью заднего фронта внешнего синхронизирующего сигнала, где задний фронт имеет нежелательно большую величину дрожания фазы, исключаются, поскольку задний фронт внешне подаваемого синхронизирующего сигнала не используется для того, чтобы завершать первую операцию считывания и/или начинать вторую операцию записи.

Хотя определенные конкретные варианты осуществления описаны выше в иллюстративных целях, настоящее изобретение не ограничено ими. Управляющая схема псевдодвухпортовой памяти может быть использована в вариантах осуществления, где первой операцией обращения к памяти является операция записи, а второй операцией обращения к памяти является операция считывания, где первой операцией обращения к памяти является операция записи и второй операцией обращения к памяти является операция записи, и где первой операцией обращения к памяти является операция считывания и второй операцией обращения к памяти является операция считывания. Следовательно, различные модификации, адаптации и комбинации различных признаков описанных конкретных вариантов осуществления могут быть использованы на практике без отступления от области применения изобретения, изложенной в формуле изобретения.

Изобретение относится к вычислительной технике, а именно к псевдодвухпортовой памяти. Техническим результатом является возможность управления упорядочением двух операций с памятью, имеющей два отдельных порта, каждый из которых имеет собственный входной синхронизирующий импульс. Псевдодвухпортовая память содержит первый порт, второй порт и массив ячеек памяти с шестью транзисторами. Первое обращение к памяти инициируется посредством переднего фронта первого синхронизирующего сигнала (ACLK), принимаемого по первому порту. Второе обращение к памяти инициируется в ответ на передний фронт второго синхронизирующего сигнала (BCLK), принимаемого по второму порту. Если передний фронт второго синхронизирующего сигнала возникает в первом периоде времени, то второе обращение к памяти инициируется сразу после завершения первого обращения к памяти псевдодвухпортовым способом. Если передний фронт второго синхронизирующего сигнала возникает позднее во втором периоде времени, то второе обращение к памяти задерживается до времени после второго переднего фронта первого синхронизирующего сигнала. Длительность первого и второго обращений к памяти не зависит от тактов синхронизирующих сигналов. Способ описывает работу данного устройства. 5 н. и 32 з.п. ф-лы, 12 ил.

1. Псевдодвухпортовая память, содержащая:

массив ячеек памяти, при этом каждая ячейка памяти массива представляет собой ячейку памяти с шестью транзисторами;

первый порт, содержащий первое множество линий ввода адреса и линий ввода синхронизирующих импульсов, при этом первый переход от низкого уровня к высокому первого входного синхронизирующего сигнала на линии ввода синхронизирующих импульсов первого порта вызывает защелкивание адреса в первом множестве линий ввода адреса в псевдодвухпортовой памяти и инициирует первое обращение к памяти массива ячеек памяти; и

второй порт, содержащий второе множество линий ввода адреса и линию ввода синхронизирующих импульсов, при этом:

в первом случае: переход от низкого уровня к высокому второго входного синхронизирующего сигнала на линии ввода синхронизирующих импульсов второго порта в течение первого периода времени вызывает защелкивание адреса по второму множеству линий ввода адреса в псевдодвухпортовой памяти и вызывает инициирование второго обращения к памяти массива ячеек памяти после завершения первого обращения к памяти и до второго перехода от низкого уровня к высокому первого входного синхронизирующего сигнала, и

во втором случае: переход от низкого уровня к высокому второго входного синхронизирующего сигнала на линии ввода синхронизирующих импульсов второго порта в течение второго периода времени вызывает задержку второго обращения к памяти массива ячеек памяти до времени после второго перехода от низкого уровня к высокому первого входного синхронизирующего сигнала, причем окончание первого периода времени совпадает с началом второго периода времени, и при этом второе обращение к памяти задерживают посредством задержки, вносимой элементом временной задержки.

2. Псевдодвухпортовая память по п.1, в которой первый входной синхронизирующий сигнал переходит к высокому уровню при первом переходе от низкого уровня к высокому, затем остается на высоком уровне в течение первого интервала времени, далее переходит к низкому уровню, затем остается на низком уровне в течение второго интервала времени, и после этого переходит к высокому уровню при втором переходе от низкого уровня к высокому первого входного синхронизирующего сигнала, причем первый переход от низкого уровня к высокому первого входного синхронизирующего сигнала совпадает с началом первого периода времени, и при этом первый период времени совпадает с первым интервалом времени.

3. Псевдодвухпортовая память по п.1, в которой первый входной синхронизирующий сигнал имеет продолжительность включения, и в которой первое обращение к памяти имеет определенную длительность, причем определенная длительность первого обращения к памяти не зависит от продолжительности включения первого входного синхронизирующего сигнала.

4. Псевдодвухпортовая память по п.1, в которой первый порт представляет собой порт только для считывания, а второй порт представляет собой порт только для записи.

5. Псевдодвухпортовая память по п.1, в которой в первом случае обращение к памяти инициируется сразу после завершения первого обращения к памяти.

6. Псевдодвухпортовая память по п.1, в которой второе обращение к памяти включает в себя начальный период предварительного заряда и последующий период, в течение которого информация записывается в ячейки памяти массива.

7. Псевдодвухпортовая память по п.1, дополнительно содержащая:

мультиплексор с временной задержкой, который имеет линию ввода синхронизирующего сигнала считывания, линию ввода подавленного синхронизирующего сигнала записи и линию вывода управляющего сигнала, при этом линия вывода управляющего сигнала мультиплексора с временной задержкой передает управляющий сигнал, который определяет то, адресован ли массив ячеек памяти для первого обращения к памяти или для второго обращения к памяти;

генератор синхронизирующих импульсов считывания, который имеет линию ввода и линию вывода, причем первый входной синхронизирующий сигнал присутствует на линии ввода, при этом линия вывода подключена к линии ввода синхронизирующего сигнала считывания мультиплексора с временной задержкой;

генератор синхронизирующих импульсов записи, который имеет линию ввода и линию вывода, причем второй входной синхронизирующий сигнал присутствует на линии ввода; и

схему подавителя синхронизирующих импульсов записи, имеющую первую линию ввода, вторую линию ввода, третью линию ввода и линию вывода, причем первый входной синхронизирующий сигнал присутствует на первой линии ввода, второй входной синхронизирующий сигнал присутствует на второй линии ввода, третья линия ввода подключена к линии вывода генератора синхронизирующих импульсов записи, линия вывода подключена к линии ввода подавленного синхронизирующего сигнала мультиплексора с временной задержкой, при этом схема подавителя синхронизирующих импульсов записи либо передает сигнал по третьей линии ввода в линию вывода, либо подавляет сигнал на третьей линии ввода от передачи в линию вывода, и при этом схема подавителя синхронизирующих импульсов подавляет сигнал на третьей линии ввода от передачи в линию вывода во втором случае в течение периода времени, начиная с перехода от низкого уровня к высокому второго входного синхронизирующего сигнала и заканчивая вторым переходом от низкого уровня к высокому первого входного синхронизирующего сигнала.

8. Псевдодвухпортовая память по п.1, в которой элемент временной задержки содержит мультиплексор с временной задержкой.

9. Псевдодвухпортовая память по п.1, в которой первый период времени начинается в момент первого перехода от низкого уровня к высокому первого входного синхронизирующего сигнала, и в которой первый период времени заканчивается в момент перехода от высокого уровня к низкому первого входного синхронизирующего сигнала.

10. Псевдодвухпортовая память по п.1, в которой второй период времени начинается до первого перехода от низкого уровня к высокому первого входного синхронизирующего сигнала.

11. Способ обращения к псевдодвухпортовой памяти, содержащий этапы, на которых:

принимают первый синхронизирующий сигнал по линии ввода синхронизирующего сигнала первого порта псевдодвухпортовой памяти, при этом первый входной синхронизирующий сигнал переходит к высокому уровню при первом переходе от низкого уровня к высокому, затем остается на высоком уровне в течение первого интервала времени, затем переходит к низкому уровню при переходе от высокого к низкому уровню, затем остается на низком уровне в течение второго интервала времени и затем переходит к высокому уровню при втором переходе от низкого уровня к высокому;

принимают второй синхронизирующий сигнал по линии ввода синхронизирующего сигнала второго порта псевдодвухпортовой памяти;

выполняют первую операцию обращения к памяти в ответ на первый переход от низкого уровня к высокому первого синхронизирующего сигнала, при этом первая операция обращения к памяти инициализируется в течение первого интервала времени, причем первая операция обращения к памяти является обращением к массиву ячеек псевдодвухпортовой памяти, при этом каждая из ячеек памяти является ячейкой памяти с шестью транзисторами, и при этом первая операция обращения к памяти имеет первую длительность, причем первая длительность не зависит от первого интервала времени; и

выполняют вторую операцию обращения к памяти в ответ на переход от низкого уровня к высокому второго синхронизирующего сигнала, при этом вторая операция обращения к памяти является обращением к массиву ячеек псевдодвухпортовой памяти, причем вторая операция обращения к памяти инициализируется сразу после завершения первой операции обращения к памяти, если переход от низкого уровня к высокому второго синхронизирующего сигнала осуществляется в первом периоде времени, и причем вторая операция обращения к памяти не инициализируется немедленно после завершения первого обращения к памяти, а вместо этого инициализируется после второго перехода от низкого уровня к высокому первого синхронизирующего сигнала, если переход от низкого уровня к высокому второго синхронизирующего сигнала осуществляется во втором периоде времени, и при этом вторую операцию обращения к памяти инициируют после задержки, вносимой элементом временной задержки, при этом окончание первого периода времени совпадает с началом второго периода времени.

12. Способ по п.11, в котором первый период времени такой же, что и первый интервал времени, когда первый синхронизирующий сигнал остается на высоком уровне, и в котором второй период времени такой же, что и второй интервал времени.

13. Способ по п.11, в котором первый порт представляет собой порт только для считывания, а второй порт представляет собой порт только для записи.

14. Способ по п.11, в котором переход от высокого уровня к низкому первого синхронизирующего сигнала не используется для того, чтобы управлять тем, когда первая операция обращения к памяти завершается, и в котором переход от высокого уровня к низкому первого синхронизирующего сигнала не используется для того, чтобы управлять тем, когда вторая операция обращения к памяти инициируется.

15. Способ по п.11, в котором вторая операция обращения к памяти включает в себя начальный период предварительного заряда и последующий период, в течение которого информация записывается в ячейки памяти массива.

16. Способ по п.11, дополнительно содержащий этапы, на которых:

устанавливают защелку в генераторе синхронизирующих импульсов считывания при первом переходе от низкого уровня к высокому первого синхронизирующего сигнала, причем защелка выводит синхронизирующий сигнал считывания;

устанавливают защелку в генераторе синхронизирующих импульсов записи при переходе от низкого уровня к высокому второго синхронизирующего сигнала, причем защелка выводит синхронизирующий сигнал записи;

пропускают синхронизирующий сигнал записи через схему подавителя, причем схема подавителя выводит подавленный синхронизирующий сигнал записи, при этом подавленный синхронизирующий сигнал записи идентичен синхронизирующему сигналу записи, если входной синхронизирующий сигнал подавления не подтверждается, и при этом подавленный синхронизирующий сигнал записи подавляется, если входной синхронизирующий сигнал подавления подтверждается;

устанавливают защелку в генераторе синхронизирующих импульсов подавления, когда первый синхронизирующий сигнал имеет высокий уровень, и сбрасывают защелку в генераторе синхронизирующих импульсов подавления, если второй синхронизирующий сигнал переходит к высокому уровню, когда первый синхронизирующий сигнал имеет низкий уровень, при этом генератор синхронизирующих импульсов подавления выводит входной синхронизирующий сигнал подавления в схему подавления, при этом входной синхронизирующий сигнал подавления является высоким, если защелка в генераторе синхронизирующих импульсов подавления установлена, причем входной синхронизирующий сигнал подавления является низким, если защелка в генераторе синхронизирующих импульсов подавления сброшена;

принимают синхронизирующий сигнал считывания и подавленный синхронизирующий сигнал записи в мультиплексоре с временной задержкой, причем мультиплексор с временной задержкой выводит управляющий сигнал, который определяет то, адресован ли массив ячеек памяти для первой операции обращения к памяти или адресован для второй операции обращения к памяти.

17. Способ по п.16, дополнительно содержащий этапы, на которых:

выводят сигнал предварительного заряда из мультиплексора с временной задержкой, при этом сигнал предварительного заряда имеет первый переход в ходе первой операции обращения к памяти, сигнал предварительного заряда имеет второй переход в ходе второй операции обращения к памяти;

используют схему одноразового срабатывания для того, чтобы сформировать первый импульс сброса в ответ на первый переход сигнала предварительного заряда, при этом первый импульс сброса очищает защелку в генераторе синхронизирующих импульсов считывания; и

используют схему одноразового срабатывания для того, чтобы сформировать второй импульс сброса в ответ на второй переход сигнала предварительного заряда, при этом второй импульс сброса очищает защелку в генераторе синхронизирующих импульсов записи.

18. Способ по п.11, в котором элемент временной задержки содержит мультиплексор с временной задержкой.

19. Способ по п.11, в котором первый период времени начинается в момент первого перехода от низкого уровня к высокому первого синхронизирующего сигнала, и в котором первый период времени заканчивается в момент перехода от высокого уровня к низкому первого синхронизирующего сигнала.

20. Способ по п.11, в котором второй период времени начинается до первого перехода от низкого уровня к высокому первого синхронизирующего сигнала.

21. Память, содержащая:

массив ячеек памяти, при этом каждая ячейка памяти массива представляет собой ячейку памяти с шестью транзисторами;

первый порт, содержащий первое множество линий ввода адреса и линию ввода синхронизирующих импульсов, причем первый синхронизирующий сигнал присутствует на линии ввода синхронизирующих импульсов первого порта, при этом первый синхронизирующий сигнал переходит к высокому уровню при первом переходе от низкого уровня к высокому, затем остается на высоком уровне в течение первого интервала времени, затем переходит к низкому уровню при переходе от высокого к низкому уровню, затем остается на низком уровне в течение второго интервала времени и затем переходит к высокому уровню при втором переходе от низкого уровня к высокому;

второй порт, содержащий второе множество линий ввода адреса и линию ввода синхронизирующих импульсов, причем второй синхронизирующий сигнал присутствует на линии ввода синхронизирующих импульсов второго порта; и