Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны компараторы двоичных чисел (см., например, рис. 6-20 на с. 288 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974), которые выполняют распознавание отношений х1=х2, х1>х2, х1<х2, где х1=x1(n-1)…х10, х2=x2(n-1)…x20 - n-разрядные двоичные числа, задаваемые двоичными сигналами х10, …, х1(n-1), х20, …, х2(n-1) ∈ {0,1}, причем сигналы х1(n-j), х2(n-j) ( ) подаются на упомянутые компараторы в j-й момент времени, а сигналы x1(n-1) и xi0 (

) подаются на упомянутые компараторы в j-й момент времени, а сигналы x1(n-1) и xi0 ( ) определяют значения соответственно старшего и младшего разрядов числа xi.

) определяют значения соответственно старшего и младшего разрядов числа xi.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных компараторов двоичных чисел, относится сложная структура, обусловленная имеющимися пересечениями соединений и тем, что цена по Квайну структуры, в частности упомянутого аналога равна 18.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип компаратор двоичных чисел (патент РФ №2393526, кл. G06F 7/02, 2010 г.), который содержит элемент НЕ, элемент И, элементы ИЛИ, элементы задержки и выполняет распознавание отношений х1=х2, х1>х2, х1<х2, где х1=x1(n-1)…х10, х2=x2(n-1)…x20 - n - разрядные двоичные числа, задаваемые двоичными сигналами х10, …, х1(n-1), х20, …, х2(n-1) ∈ {0,1}, причем сигналы х1(n-j), х2(n-j) ( ) подаются на соответствующие входы прототипа в j-й момент времени, а сигналы хi(n-1), хi0(n-j) (

) подаются на соответствующие входы прототипа в j-й момент времени, а сигналы хi(n-1), хi0(n-j) ( ) определяют значения соответственно старшего и младшего разрядов числа xi.

) определяют значения соответственно старшего и младшего разрядов числа xi.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится сложная структура, обусловленная тем, что в прототипе имеются пересечения соединений и цена по Квайну структуры прототипа равна 16.

Техническим результатом изобретения является упрощение структуры за счет устранения пересечений соединений и уменьшения ее цены по Квайну при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в компараторе двоичных чисел, содержащем элемент НЕ, элемент И, два элемента ИЛИ и два элемента задержки, причем вход i-го ( ) элемента задержки подключен к i-му выходу компаратора двоичных чисел, особенность заключается в том, что в него дополнительно введены два мажоритарных элемента, выход i-го элемента задержки, i-й вход и выход элемента И соединены соответственно с первым, вторым входами i-го мажоритарного элемента и входом элемента НЕ, подключенного выходом к третьему входу i-го мажоритарного элемента, выход и второй вход которого соединены соответственно с входом i-го элемента задержки и выходом i-го элемента ИЛИ, подключенного первым и вторым входами соответственно к выходу i-го элемента задержки и i-му входу компаратора двоичных чисел.

) элемента задержки подключен к i-му выходу компаратора двоичных чисел, особенность заключается в том, что в него дополнительно введены два мажоритарных элемента, выход i-го элемента задержки, i-й вход и выход элемента И соединены соответственно с первым, вторым входами i-го мажоритарного элемента и входом элемента НЕ, подключенного выходом к третьему входу i-го мажоритарного элемента, выход и второй вход которого соединены соответственно с входом i-го элемента задержки и выходом i-го элемента ИЛИ, подключенного первым и вторым входами соответственно к выходу i-го элемента задержки и i-му входу компаратора двоичных чисел.

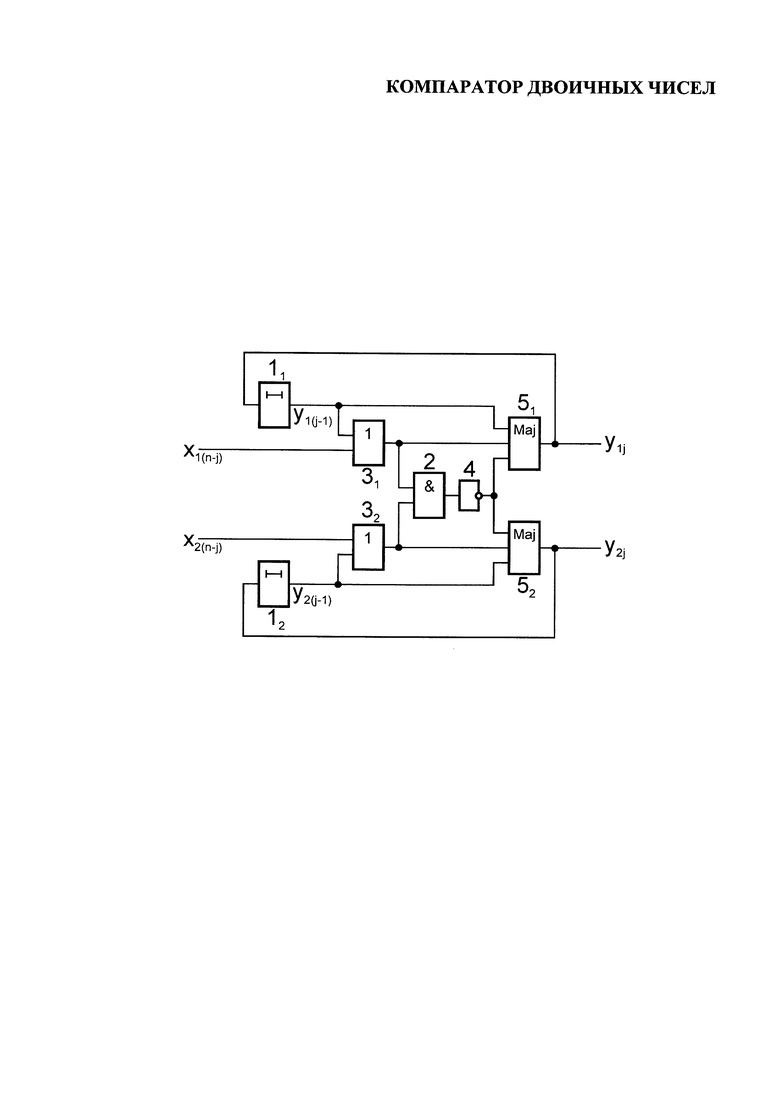

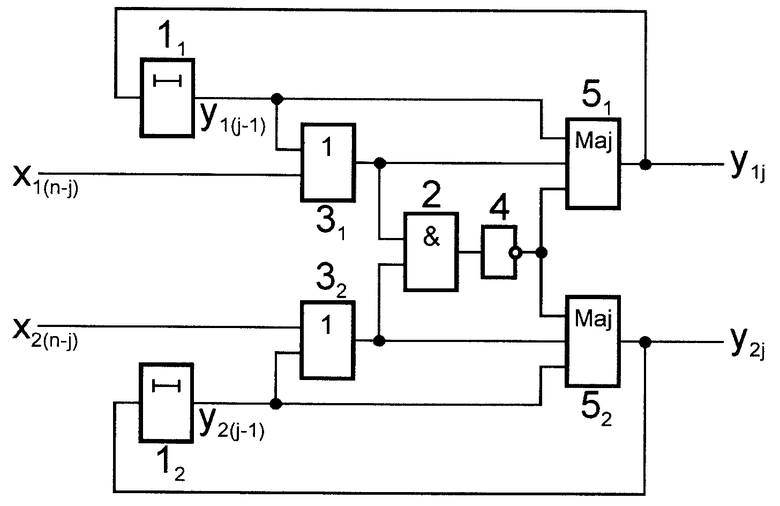

На чертеже представлена схема предлагаемого компаратора двоичных чисел.

Компаратор двоичных чисел содержит два элемента задержки 11, 12, элемент И 2, два элемента ИЛИ 31, 32, элемент НЕ 4, два мажоритарных элемента 51, 52, причем выход элемента 1i ( ), i-й вход и выход элемента 2 соединены соответственно с первым, вторым входами элемента 5i и входом элемента 4, подключенного выходом к третьему входу элемента 5i, выход и второй вход которого соединены соответственно с входом элемента 1i и выходом элемента 3i, подключенного первым и вторым входами соответственно к выходу элемента 1i и i-му входу компаратора двоичных чисел, i-й выход которого соединен с выходом элемента 5i.

), i-й вход и выход элемента 2 соединены соответственно с первым, вторым входами элемента 5i и входом элемента 4, подключенного выходом к третьему входу элемента 5i, выход и второй вход которого соединены соответственно с входом элемента 1i и выходом элемента 3i, подключенного первым и вторым входами соответственно к выходу элемента 1i и i-му входу компаратора двоичных чисел, i-й выход которого соединен с выходом элемента 5i.

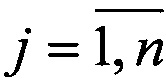

Работа предлагаемого компаратора двоичных чисел осуществляется следующим образом. На его первый и второй входы в j-й ( ) момент времени подаются соответственно двоичные сигналы х1(n-j) ∈ {0,1} и х2(n-j) ∈ {0,1}, которые задают значения (n-j)-х разрядов подлежащих сравнению n-разрядных двоичных чисел х1=x1(n-1)…х10 и х2=x2(n-1)…x20. Здесь сигналы xi(n-1) и xi0 (

) момент времени подаются соответственно двоичные сигналы х1(n-j) ∈ {0,1} и х2(n-j) ∈ {0,1}, которые задают значения (n-j)-х разрядов подлежащих сравнению n-разрядных двоичных чисел х1=x1(n-1)…х10 и х2=x2(n-1)…x20. Здесь сигналы xi(n-1) и xi0 ( ) определяют значения соответственно старшего и младшего разрядов числа xi. Сигнал на выходе элемента задержки 1, в j-й момент времени равен сигналу, который действовал на его входе в (j-1)-й момент времени, a yi0=0 (в качестве элемента задержки может быть использован D-триггер). Тогда сигналы на первом, втором выходах предлагаемого компаратора будут определяться выражениями

) определяют значения соответственно старшего и младшего разрядов числа xi. Сигнал на выходе элемента задержки 1, в j-й момент времени равен сигналу, который действовал на его входе в (j-1)-й момент времени, a yi0=0 (в качестве элемента задержки может быть использован D-триггер). Тогда сигналы на первом, втором выходах предлагаемого компаратора будут определяться выражениями

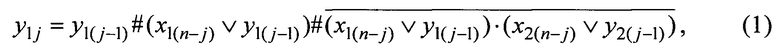

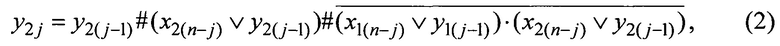

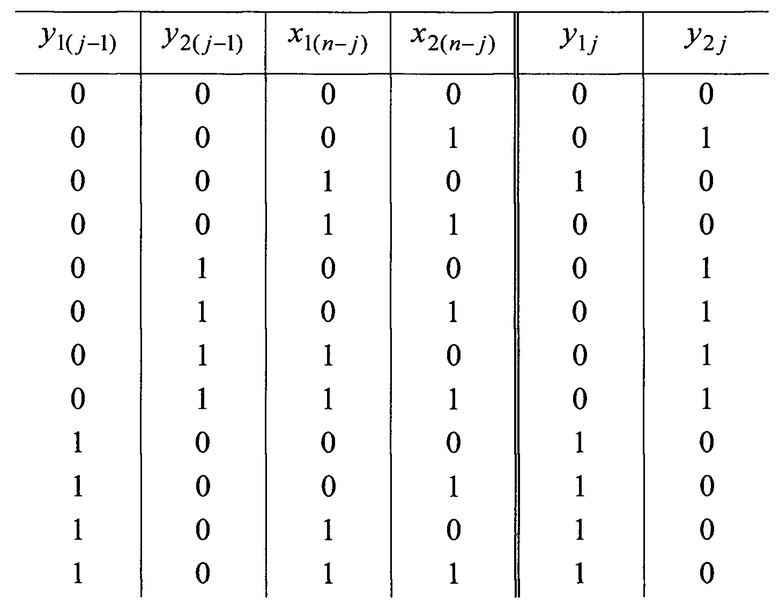

где y10=y20=0; ∨, ⋅, -, # есть символы операций ИЛИ, И, НЕ, Maj, причем а1#а2#a3=а1⋅а2∨a1⋅а3∨а2⋅а3. В представленной ниже таблице приведены значения реализуемых выражениями (1), (2) функций на всех возможных наборах значений их аргументов.

Анализ данных, приведенных в таблице, позволяет заключить, что: 1) если y1(j-1)=y2(j-1)=0 и х1(n-j)=х2(n-j), то y1j=y2j=0; 2) если y1(j-1)=y2(j-1)=0 и х1(n-j)>х2(n-j) (y1(j-1)=y2(j-1)=0 и х1(n-j)<х2(n-j)), то y1j=1 и y2j=0 (y1j=0 и y2j=1); 3) если y1(j-1)=1 и y2{j-1)=0 (y1(j-1)=0 и y2(j-1)=1), то y1j=1 и y2j=0 (y1j=0 и j2j=1). Таким образом, когда х1=х2 либо x1>х2 либо х1<х2 соответственно получим y1n=y2n=0 либо y1n=1, y2n=0 либо y1n=0, y2n=1. При этом в предлагаемом компараторе отсутствуют пересечения соединений и цена по Квайну структуры предлагаемого компаратора равна 15.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый компаратор двоичных чисел имеет более простую по сравнению с прототипом структуру и выполняет распознавание отношений х1=х2, х1>х2, x1<х2, где х1=x1(n-1)…x10, х2=x2(n-1)…x20 - n-разрядные двоичные числа, задаваемые двоичными сигналами x10, … х1(n-1), x20, … x2(n-1) ∈ {0,1}, причем сигналы х1(n-j), х2(n-j) ( ) подаются на соответствующие входы предлагаемого компаратора в j-й момент времени, а сигналы хi(n-1) и xi0 (

) подаются на соответствующие входы предлагаемого компаратора в j-й момент времени, а сигналы хi(n-1) и xi0 ( ) определяют значения соответственно старшего и младшего разрядов числа xi.

) определяют значения соответственно старшего и младшего разрядов числа xi.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2393526C2 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2020 |

|

RU2757832C1 |

| ПАРАЛЛЕЛЬНЫЙ ДЕШИФРАТОР УПРАВЛЯЕМОЙ ТРАНСПОЗИЦИИ ИНФОРМАЦИИ, ХРАНИМОЙ В ПЕРСОНАЛЬНОЙ ЭВМ | 2008 |

|

RU2390049C1 |

| УСТРОЙСТВО СОРТИРОВКИ ДВОИЧНЫХ ЧИСЕЛ | 2011 |

|

RU2445678C1 |

| УСТРОЙСТВО УПРАВЛЯЕМОЙ ПЕРЕСТАНОВКИ ИНФОРМАЦИИ, ХРАНИМОЙ В ЭВМ | 2009 |

|

RU2405187C1 |

| УСТРОЙСТВО СОРТИРОВКИ ДВОИЧНЫХ ЧИСЕЛ | 2005 |

|

RU2300136C1 |

| МНОГОВХОДОВЫЙ ОДНОРАЗРЯДНЫЙ СУММАТОР | 1992 |

|

RU2047216C1 |

| СПОСОБ ФОРМИРОВАНИЯ КЛЮЧА ШИФРОВАНИЯ/ДЕШИФРОВАНИЯ | 2005 |

|

RU2295199C1 |

| СПОСОБ ФОРМИРОВАНИЯ КЛЮЧА ШИФРОВАНИЯ/ДЕШИФРОВАНИЯ | 2018 |

|

RU2684492C1 |

| СПОСОБ ФОРМИРОВАНИЯ КЛЮЧА ШИФРОВАНИЯ/ДЕШИФРОВАНИЯ | 2018 |

|

RU2695050C1 |

Изобретение относится к компараторам двоичных чисел. Технический результат заключается в упрощении структуры за счет устранения пересечений соединений. Компаратор двоичных чисел содержит два элемента задержки (l1, l2), элемент И (2), два элемента ИЛИ (31, 32), элемент НЕ (4), два мажоритарных элемента (51, 52). 1 табл., 1 ил.

Компаратор двоичных чисел, содержащий элемент НЕ, элемент И, два элемента ИЛИ и два элемента задержки, причем вход i-го  элемента задержки подключен к i-му выходу компаратора двоичных чисел, отличающийся тем, что в него дополнительно введены два мажоритарных элемента, выход i-го элемента задержки, i-й вход и выход элемента И соединены соответственно с первым, вторым входами i-го мажоритарного элемента и входом элемента НЕ, подключенного выходом к третьему входу i-го мажоритарного элемента, выход и второй вход которого соединены соответственно с входом i-го элемента задержки и выходом i-го элемента ИЛИ, подключенного первым и вторым входами соответственно к выходу i-го элемента задержки и i-му входу компаратора двоичных чисел.

элемента задержки подключен к i-му выходу компаратора двоичных чисел, отличающийся тем, что в него дополнительно введены два мажоритарных элемента, выход i-го элемента задержки, i-й вход и выход элемента И соединены соответственно с первым, вторым входами i-го мажоритарного элемента и входом элемента НЕ, подключенного выходом к третьему входу i-го мажоритарного элемента, выход и второй вход которого соединены соответственно с входом i-го элемента задержки и выходом i-го элемента ИЛИ, подключенного первым и вторым входами соответственно к выходу i-го элемента задержки и i-му входу компаратора двоичных чисел.

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2361266C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2393526C2 |

| US 7103624 B2, 05.09.2006 | |||

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2006 |

|

RU2300131C1 |

| КОМПАРАТОР ДВОИЧНЫХ ЧИСЕЛ | 2005 |

|

RU2300132C1 |

Авторы

Даты

2018-03-30—Публикация

2017-04-04—Подача