Изобретение относится к кодирующим устройствам помехоустойчивого кода, обеспечивающего восстановление передаваемой по каналу связи информации после ее искажений под действием помех.

Известен формирователь кода (см. патент РФ №2509414 от 30.07.2012 «Формирователь кольцевого кода» авторов Гончарова С.Н., Мартынова А.П., Новикова А.В., Фомченко В.Н., Шишкина Г.И., МПК Н03М 7/02, опубликован в Б.И. №7: от 10.03.2014), содержащий последовательно-параллельный сдвигающий регистр, входы параллельной записи разрядов которого, начиная со второго, соединены с соответствующими информационными входами устройства, начиная с последнего разряда, вход управления последовательно-параллельным режимом регистра соединен с управляющим входом устройства, входы синхронизации и общего сброса соединены соответственно с тактовым входом и входом сброса устройства, выходы последнего и предпоследнего разрядов регистра соединены с входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, введены элемент ИЛИ-НЕ и второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом параллельной записи первого разряда регистра, а входы - с входами параллельной записи второго и старшего разрядов регистра, входы элемента ИЛИ-НЕ соединены с тактовым входом и входом сброса устройства, а выход является тактовым выходом устройства, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом последовательной записи регистра, выход последнего разряда которого является информационным выходом устройства. На выходе устройства производится формирование систематического кода, в котором информационные элементы занимают левую часть кодовой комбинации, а проверочные элементы - правую.

Недостатком устройства является то, что при передаче многобитной посылки на входе данного устройства информацию необходимо делить на n-кратное количество пакетов данных  , что, в свою очередь, приводит к увеличению времени передачи. Так же еще одним из существенных недостатков является низкая устойчивость к помехам длительностью более трех бит.

, что, в свою очередь, приводит к увеличению времени передачи. Так же еще одним из существенных недостатков является низкая устойчивость к помехам длительностью более трех бит.

Технический результат, на достижение которого направлено заявляемое изобретение, заключается в повышении помехоустойчивости и уменьшении времени передачи многобитных посылок.

Для достижения технического результата в формирователе кода, содержащем первый последовательно-параллельный регистр, первый и второй выходы которого соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а информационный вход является информационным входом формирователя кода, новым является то, что дополнительно введены счетный триггер, первый и второй элементы И, мультиплексор и второй последовательно-параллельный регистр, выход которого соединен с первыми входами первого и второго элементов И, выходы которых являются соответственно информационным и тактовым выходами формирователя кода, тактовый вход счетного триггера является тактовым входом формирователя кода и соединен со вторым входом второго элемента И, управляющий вход счетного триггера является управляющим входом формирователя кода и соединен со входом сброса второго последовательно-параллельного регистра, вход данных которого является входом разрешения Е формирователя кода, а тактовый вход соединен со входом выбора адреса мультиплексора, с выходом счетного триггера и тактовым входом первого последовательно-параллельного регистра, третий выход которого соединен со вторым входом мультиплексора, первый вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Указанная совокупность существующих признаков позволяет повысить помехоустойчивость посредством сдвига проверочного бита на 4 разряда в право и уменьшении времени передачи многобитных посылок за счет повышения помехозащищенности.

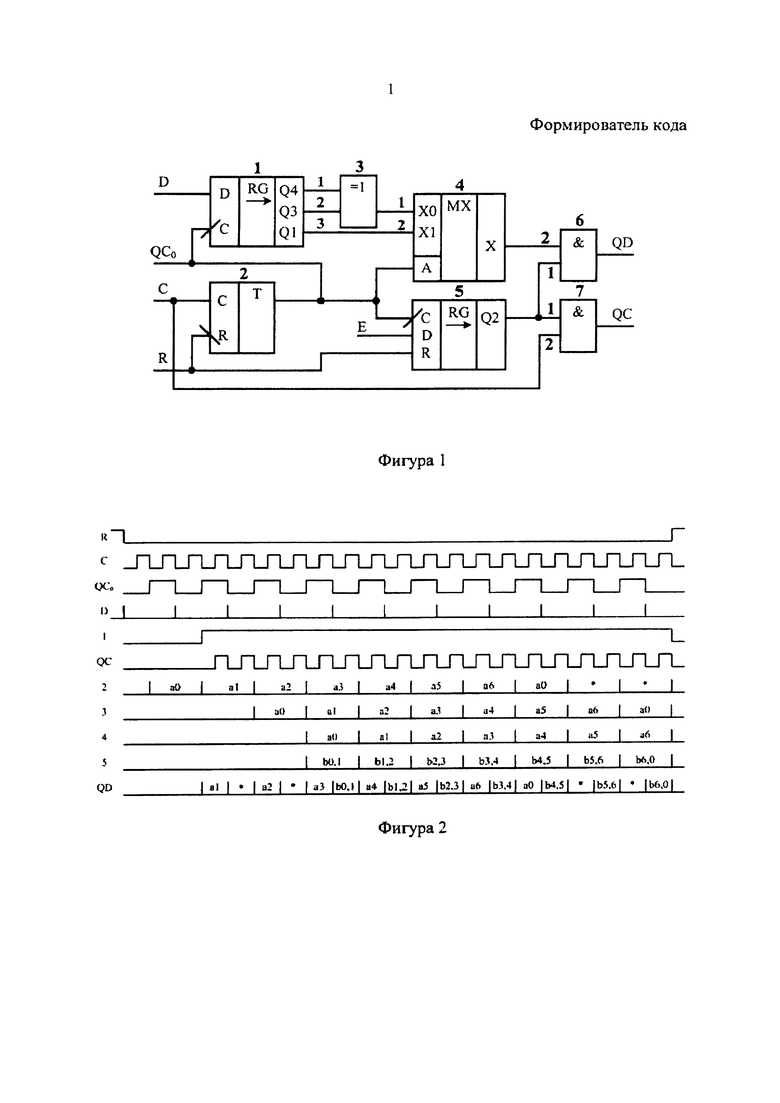

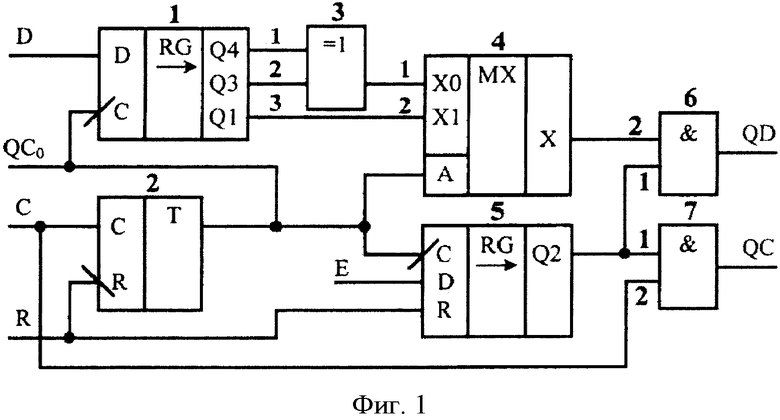

На фиг. 1 представлена схема формирователя кода, на фиг. 2 представлена временная диаграмма сигналов в характерных точках схемы.

Формирователь кода (см. фиг. 1) содержит первый последовательно-параллельный регистр 1, первый и второй выходы которого соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, а информационный вход является информационным входом формирователя кода, счетный триггер 2, первый 6 и второй 7 элементы И, мультиплексор 4 и второй последовательно-параллельный регистр 5, выход которого соединен с первыми входами первого 6 и второго 7 элементов И, выходы которых являются соответственно информационным и тактовым выходами формирователя кода. Тактовый вход счетного триггера 2 является тактовым входом формирователя кода и соединен со вторым входом второго 7 элемента И, управляющий вход счетного триггера 2 является управляющим входом формирователя кода и соединен со входом сброса второго последовательно-параллельного регистра 5, вход данных которого является входом разрешения Е формирователя кода, а тактовый вход соединен со входом выбора адреса мультиплексора 4, с выходом счетного триггера 2 и тактовым входом первого последовательно-параллельного регистра 1, третий выход которого соединен со вторым входом мультиплексора 4, первый вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3.

Формирователь кода работает следующим образом. При включении питания счетный триггер 2 и второй последовательно-параллельный регистр 5 удерживаются в исходном состоянии внешним сигналом по R-входу устройства. На выходах QC и QD выходным сигналом второго последовательно-параллельного регистра 5 задается уровень логического "0". На D-вход первого последовательно-параллельного регистра 1 подается информационный элемент а0.

Работа устройства разрешается после снятия удерживающего сигнала на R-входе. При этом на С-вход начинают поступать тактовые импульсы, которые отрицательным фронтом переключают счетный триггер 2, формируя положительные управляющие импульсы. Период повторения управляющих импульсов, начиная с положительного фронта, будем считать тактовым интервалом. Выходные сигналы триггера 2, поступающие на С-вход первого последовательно-параллельного регистра 1, положительным фронтом обеспечивают запись входной информации в первый последовательно-параллельный регистр 1, а отрицательным фронтом - смену информации на D-входе устройства с аi на аi+1.

Положительным фронтом второго управляющего импульса после окончания первого тактового интервала на выходе второго последовательно-параллельного регистра 5 устанавливается уровень логической "1", разрешающий прохождение сигналов на выходы QC и QD формирователя кода.

К моменту срабатывания второго последовательно-параллельного регистра 5 на выходе Q1 первого последовательно-параллельного регистра 1 формируется информационный элемент a1, на выходах Q3 и Q4, а следовательно, и на выходе логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 - произвольные сигналы. На втором тактовом интервале во время действия положительного управляющего импульса на выход мультиплексора 4 и далее на выход QD проходит информационный элемент a1, а после окончания импульса - произвольный сигнал, который не будет восприниматься дешифратором.

В начале третьего тактового интервала на выходе Q1 первого последовательно-параллельного регистра 1 устанавливается информационный элемент а2, а на выходе Q3 - информационный элемент а0, на выходе Q4, а следовательно, и на выходе элемента "исключающее ИЛИ" 3 - произвольные сигналы. Поэтому в третьем тактовом интервале во время действия положительного управляющего импульса на выход мультиплексора 5 и далее на выход QD проходит информационный элемент а2, а после окончания импульса - произвольный сигнал, который не будет восприниматься дешифратором.

В начале четвертого тактового интервала на выходе Q1 первого регистра 1 устанавливается информационный элемент а3, на выходе Q3 - информационный элемент а1, на выходе Q4 - информационный элемент а0. Следовательно, на выходе элемента "исключающее ИЛИ" 3 формируется проверочный элемент b0,1. Поэтому в четвертом тактовом интервале во время действия положительного управляющего импульса на выход мультиплексора 4 и далее на выход QD проходит информационный элемент а3, а после окончания импульса - проверочный элемент b0,1.

Далее во время тактовых интервалов с 5 по 8 будут сформированы аналогичным образом следующие элементы: a4, b1,2, a5, b2,3, a6, b3,4, а0, b4,5.

В начале девятого тактового интервала на выходе Q1 первого регистра устанавливается произвольное состояние, на выходе Q3 - информационный элемент а6, на выходе Q4 - информационный элемент a5. Следовательно, на выходе элемента "исключающее ИЛИ" 3 формируется проверочный элемент b5.6. Поэтому в девятом тактовом интервале во время действия положительного управляющего импульса на выход мультиплексора 4 и далее на выход QD проходит произвольный сигнал, который не будет восприниматься дешифратором, а после окончания импульса - проверочный элемент b5.6.

В начале десятого тактового интервала на выходе Q1 первого регистра 1 устанавливается произвольное состояние, на выходе Q3 - информационный элемент а0, на выходе Q4 - информационный элемент а6. Следовательно, на выходе элемента "исключающее ИЛИ" 3 формируется проверочный элемент b6.0. Поэтому в десятом тактовом интервале во время действия положительного управляющего импульса на выход мультиплексора 4 и далее на выход QD проходит произвольный сигнал, который не будет восприниматься дешифратором, а после окончания импульса - проверочный элемент b6.0. На этом работа формирователя заканчивается. Формируемые на выходе QC тактовые импульсы информационных и проверочных элементов располагаются во второй половине соответствующих временных интервалов.

Был изготовлен макет заявляемого устройства, который подтвердил его работоспособность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ КОДА ХЭММИНГА | 2013 |

|

RU2526769C1 |

| Устройство для кодирования цифровой информации циклическими кодами | 1986 |

|

SU1336255A1 |

| ФОРМИРОВАТЕЛЬ КОЛЬЦЕВОГО КОДА | 2012 |

|

RU2509414C1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ ИНФОРМАЦИОННЫХ СВОЙСТВ ТЕСТА | 1991 |

|

RU2068580C1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

Изобретение относится к кодирующим устройствам помехоустойчивого кода, обеспечивающего восстановление передаваемой по каналу связи информации после ее искажений под действием помех. Технический результат – повышение помехоустойчивости и уменьшение времени передачи многобитных посылок. Формирователь кода содержит первый и второй последовательно-параллельные регистры сдвига, счетный триггер, мультиплексор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй элементы И. 2 ил.

Формирователь кода, содержащий первый последовательно-параллельный регистр, первый и второй выходы которого соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а информационный вход является информационным входом формирователя кода, отличающийся тем, что дополнительно введены счетный триггер, первый и второй элементы И, мультиплексор и второй последовательно-параллельный регистр, выход которого соединен с первыми входами первого и второго элементов И, выходы которых являются соответственно информационным и тактовым выходами формирователя кода, тактовый вход счетного триггера является тактовым входом формирователя кода и соединен со вторым входом второго элемента И, управляющий вход счетного триггера является управляющим входом формирователя кода и соединен со входом сброса второго последовательно-параллельного регистра, вход данных которого, является входом разрешения Е формирователя кода, а тактовый вход соединен со входом выбора адреса мультиплексора, с выходом счетного триггера и тактовым входом первого последовательно-параллельного регистра, третий выход которого соединен со вторым входом мультиплексора, первый вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

| ФОРМИРОВАТЕЛЬ КОЛЬЦЕВОГО КОДА | 2012 |

|

RU2509414C1 |

| ФОРМИРОВАТЕЛЬ КОДА ХЭММИНГА | 2013 |

|

RU2526769C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1990 |

|

RU2036556C1 |

| СПОСОБ СОВМЕСТНОГО АРИФМЕТИЧЕСКОГО И ПОМЕХОУСТОЙЧИВОГО КОДИРОВАНИЯ | 2015 |

|

RU2629455C2 |

| ДЕШИФРАТОР КОЛЬЦЕВЫХ КОДОВ С ИСПРАВЛЕНИЕМСТИРАНИЙ | 0 |

|

SU299846A1 |

| ДЕШИФРАТОР КОЛЬЦЕВЫХ КОДОВ | 0 |

|

SU263994A1 |

| US 6898322 B2, 24.05.2005. | |||

Авторы

Даты

2018-06-22—Публикация

2017-08-17—Подача