Изобретение относится к цифровой магнитной записи и может быть использовано для уменьшения времени преобразования, исправления ошибок во внешних запоминающих устройствах микро-ЭВМ и персональных компьютеров.

Изобретение может быть использовано и для исправления ошибок в канале связи, использующем недвоичные сигналы.

Известно устройство, в котором запись информации на магнитный носитель осуществляется трехуровневым кодом, который позволяет стереть ранее записанную информацию без применения специальной стирающей головки. Восстановление исходного трехуровневого сигнала осуществляется с помощью пикового детектора и компаратора с четырьмя уровнями срабатывания.

Однако помехоустойчивость системы записи-воспроизведения является невысокой, а использование троичного сигнала не позволяет повысить плотность записи более чем в 1,5 раза.

Известно устройство для троичной цифровой магнитной записи, в котором в непрерывную последовательность стирающего сигнала вводятся вставки положительной и отрицательной полярности, доводящие носитель до насыщения.

Устройство позволяет повысить плотность цифровой магнитной записи в 1,5 раза, однако время преобразования, а также плотность и помехоустойчивость записи-воспроизведения невысоки.

Известно устройство для цифровой магнитной записи-воспроизведения, в котором для повышения плотности цифровой магнитной записи в 2,0 раза используется пятиричный Triplex сигнал.

Однако при высоком времени преобразования помехоустойчивость записи-воспроизведения невысока вследствие низкой избыточности.

Известно устройство, в котором для повышения плотности цифровой магнитной записи в 2,0 раза используется семиричный сигнал.

Однако помехоустойчивость записи-воспроизведения невысоки, так как аналог не позволяет исправлять ошибки.

Известно устройство, принятое за прототип, для преобразования дискретных сигналов, в котором для повышения помехоустойчивости и информативности используется двоично-пятиричное преобразование. Устройство-прототип содержит преобразователь сигнала в биполярный сигнал, анализатор веса, конвертор полярности импульсов, мультиплексер, логический переключатель, состоящий из выпрямителя, пяти элементов ИЛИ, пяти инверторов, трех сумматоров, двух ключей, причем вход устройства подключен к преобразователю двоичного сигнала, старшие разряды которого подключены к соответствующим входам анализатора веса и к первым входам конвертора полярности импульсов, выходы которого соединены с соответствующими первыми входами мультиплексора, выход мультиплексора подключен к выходу устройства, младшие разряды преобразователя двоичного сигнала в биполярный сигнал подключен к соответствующим информационным входам логического переключателя, выход анализатора веса соединен с управляющими входами логического переключателя, первый информационный вход логического переключателя соединен через второй инвертор с первым информационным выходом логического переключателя, с первым входом первого ключа, с первыми входами первого, четвертого и пятого элементов ИЛИ и через третий и четвертый инверторы подключен соответственно к первым входам второго и третьего элементов ИЛИ, второй информационный вход логического переключателя соединен с первым входом второго ключа, с третьим информационным выходом логического переключателя и через выпрямитель с вторыми входами первого, второго, третьего, четвертого и пятого элементов ИЛИ и через первый инвертор с первым информационным выходом логического переключателя, выход первого элемента ИЛИ подключен к третьему выходу логического переключателя, первый управляющий вход логического переключателя подключен к второму входу первого ключа и к первому управляющему выходу логического переключателя, выходы второго и третьего элементов ИЛИ соединены с первым и вторым информационными входами логического переключателя, выходы четвертого и пятого элементов ИЛИ подключены к входам третьего сумматора, выход которого через пятый инвертор соединен с третьим информационным выходом логического переключателя.

Устройство-прототип (при его несомненной работоспособности) обладает существенными недостатками переход от двоичного сигнала к пятиричному приводит к снижению помехоустойчивости записи, при этом для прохождения информации на выход нужен сигнал разрешения конвертора полярности импульсов, который формируется на выходе анализатора веса, после нахождения веса данного блока и эта операция повторяется в каждом блоке, за счет этого время преобразования существенно увеличивается, что приводит к снижению быстродействия ЭВМ.

Очевидным решением указанных проблем является использование некоторого пятиричного корректирующего кода, позволяющего компенсировать снижение помехоустойчивости. Использование любого известного систематического пятиричного кода на заданной длине требует введения дополнительных проверочных символов. Это хотя и позволяет частично компенсировать снижение помехоустойчивости, однако при этом увеличивается время преобразования, снижается удельная скорость информации, а следовательно и плотность цифровой магнитной записи. Применение же нелинейных пятиричных кодов позволяет исправлять одиночные ошибки без снижения удельной скорости информации, т.е. без снижения плотности цифровой магнитной записи. Однако, при этом, реализация такого устройства возможна только с использованием памяти очень большого объема, что существенно увеличивает время преобразования и усложняет систему цифровой магнитной записи. Таким образом, очевидные пути устранения недостатков устройства-прототипа не позволяет достичь требуемого положительного эффекта.

Целью предлагаемого изобретения является уменьшение времени преобразования, при одновременном повышении помехоустойчивости преобразования без снижения плотности цифровой магнитной записи.

Достижение поставленной цели позволяет повысить надежность цифровой магнитной записи без уменьшения объема информации, записанный на магнитный носитель. При этом быстродействие процесса запись-воспроизведение, а следовательно, и быстродействие ЭВМ будет повышено.

С этой целью в устройство-прототип, содержащее преобразователь двоичного сигнала, информационный вход которого является информационным входом устройства, логический переключатель, выходы которого подключены к первым информационным входам параллельно последовательного преобразователя, выходы которого являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью уменьшения времени преобразования и повышения помехоустойчивости устройства без снижения плотности цифровой магнитной записи, в устройство введены блок управления и 36-разрядный буферный регистр, преобразователь двоичного сигнала выполнен в виде двоично-семиричного преобразователя, логический переключатель выполнен на семи сумматорах по модулю два, входы и выходы которых являются соответственно входами и выходами логического переключателя, синхровход преобразователя двоичного сигнала объединен со входом блока управления и является входом синхронизации устройства, первый и второй выходы блока управления подключены к первому и второму управляющим входам преобразователя двоичного сигнала, выходы которого подключены к информационным входам 36-разрядного буферного регистра, выходы которого подключены к соответствующим входам логического переключателя и вторым информационным входам параллельно-последовательного преобразователя, третий выход блока управления подключен к управляющему входу 36-разрядного буферного регистра и первому управляющему входу параллельно-последовательного преобразователя, второй управляющий вход которого соединен с четвертым выходом блока управления, состоящего из умножителя частоты на два, делителя частоты на восемь, делителя частоты на девять, двух делителей частоты на четыре, делителя частоты на три, двух RS-триггеров, формирователя импульсов, элемента задержки, двух элементов ИЛИ, четырех инверторов и элемента И, вход умножителя частоты на два объединен со входом умножителя частоты на восемь и является входом блока управления, выход делителя частоты на восемь подключен к S-входу первого триггера и к входу первого инвертора, выход которого является первым выходом блока управления, выход умножителя частоты на два подключен к входу второго инвертора, выход которого соединен с первыми входами делителя частоты на девять, делителя частоты на три, первого делителя частоты на четыре и входом элемента задержки, выход которого подключен к первым входам первого и второго элементов ИЛИ, выходы которых являются соответственно вторым и четвертым выходами блока управления, выход делителя частоты на девять подключен непосредственно к R-входу первого триггера и через последовательно соединенные третий инвертор, второй делитель частоты на четыре и формирователь импульсов к третьему выходу блока управления и входу четвертого инвертора, выход которогоо подключен к первому входу элемента И, выход которого соединен с вторым входом первого делителя частоты на четыре, выход которого подключен к второму входу элемента И и S-входу второго триггера, выход которого соединен с вторым входом второго элемента ИЛИ и вторым входом делителя частоты на три, выход которого подключен к R-входу второго триггера, выход первого триггера подключен к вторым входам первого элемента ИЛИ и делителя частоты на девять.

Сущность предлагаемого изобретения заключается в том, что введение указанных элементов в совокупности с их связями позволяет уменьшить время преобразования за счет того, что задержка вводится только в первоначальный момент времени сигналом разрешения, подаваемым на введенный буферный регистр, и только для синхронизации, а также осуществлять исправление ошибок при записи-воспроизведении семиричным сигнралом. Поскольку переход от пятиричной записи к семиричной приводит к незначительному снижению помехоустойчивости, а избыточность семиричного сигнала r7 log27 2,81, существенно больше избыточности пятиричного сигнала r5 2,36, то на требуемой длине можно построить систематический семиричный корректирующий код, который будет компенсировать снижение помехоустойчивости без снижения плотности записи, которая остается такой же, как и в устройстве-прототипе.

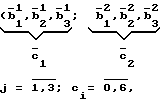

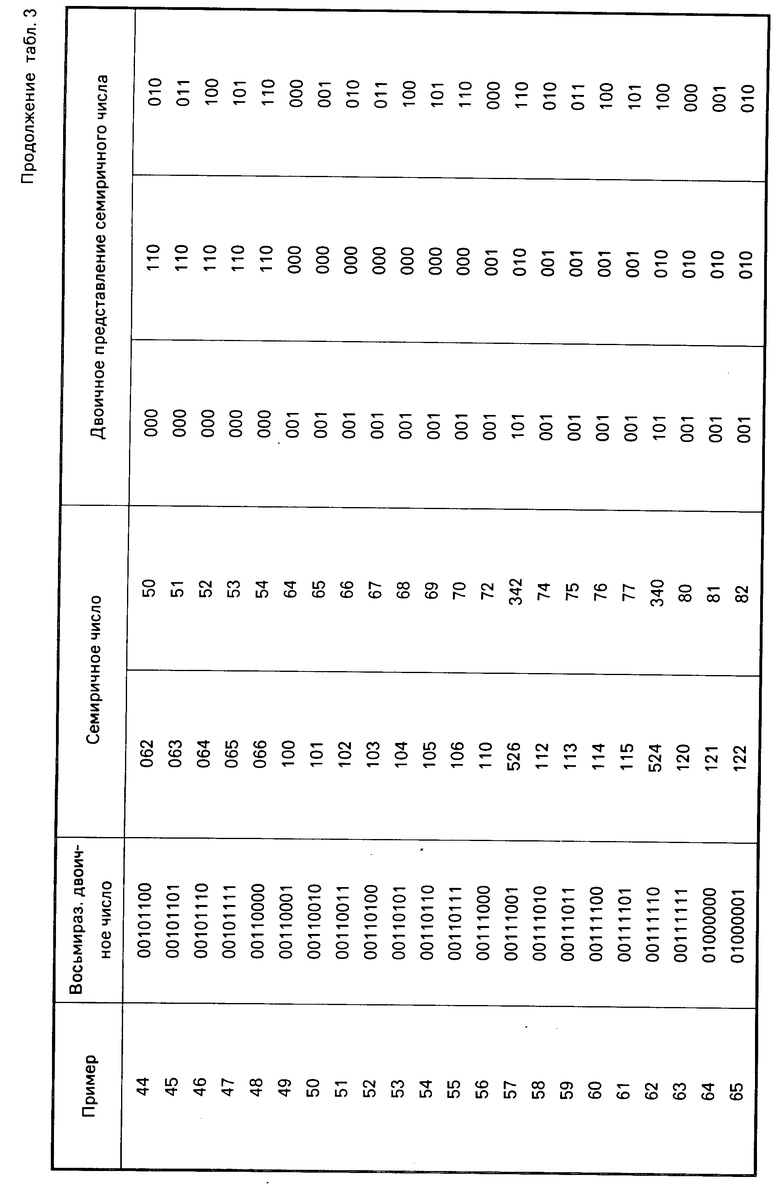

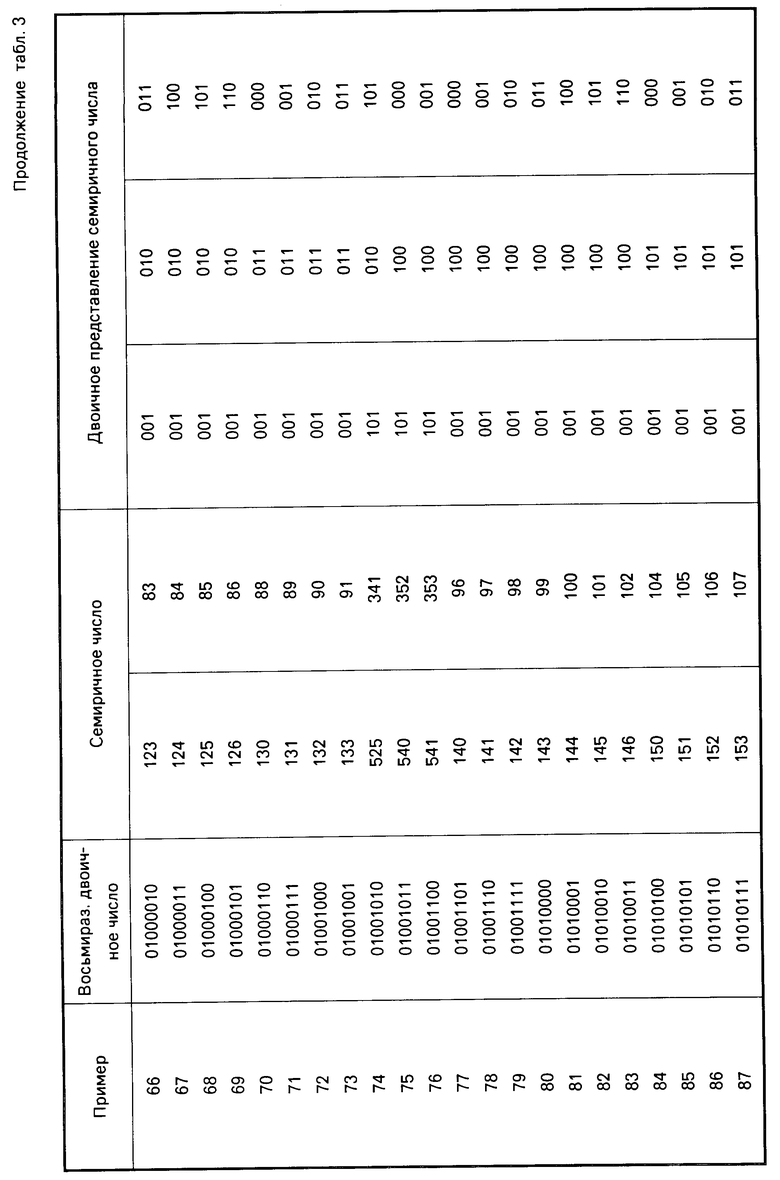

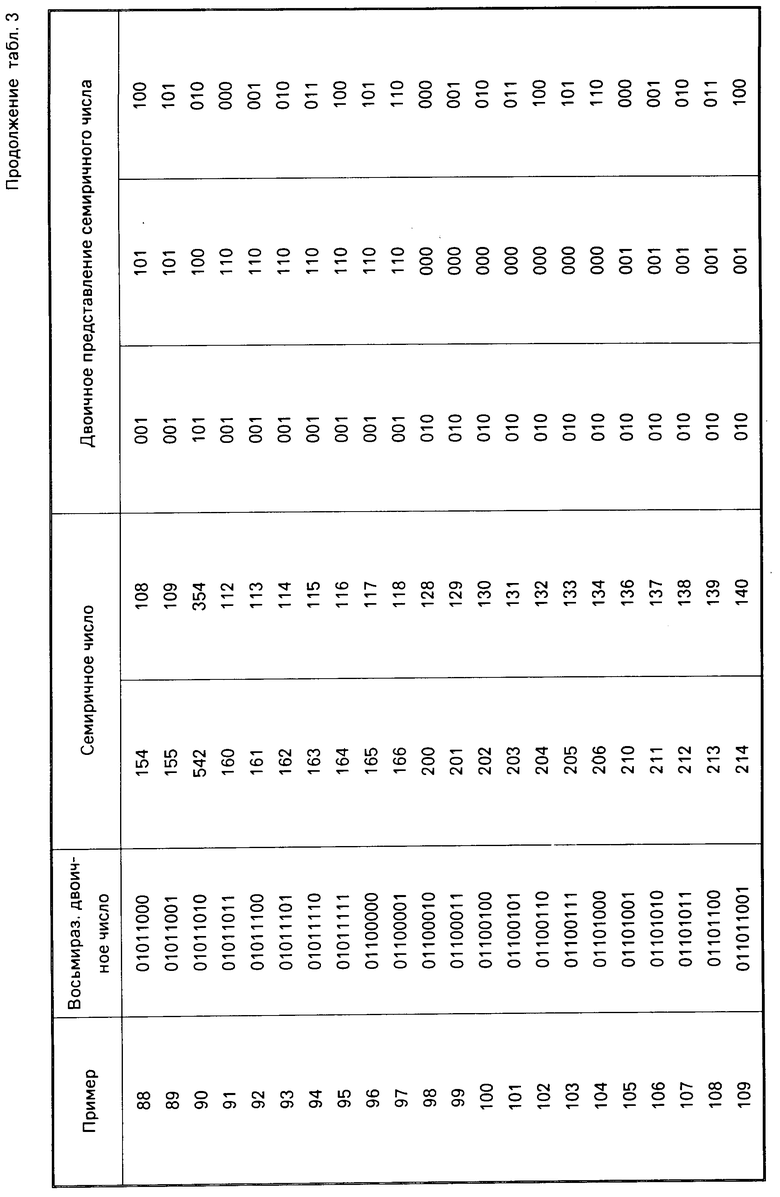

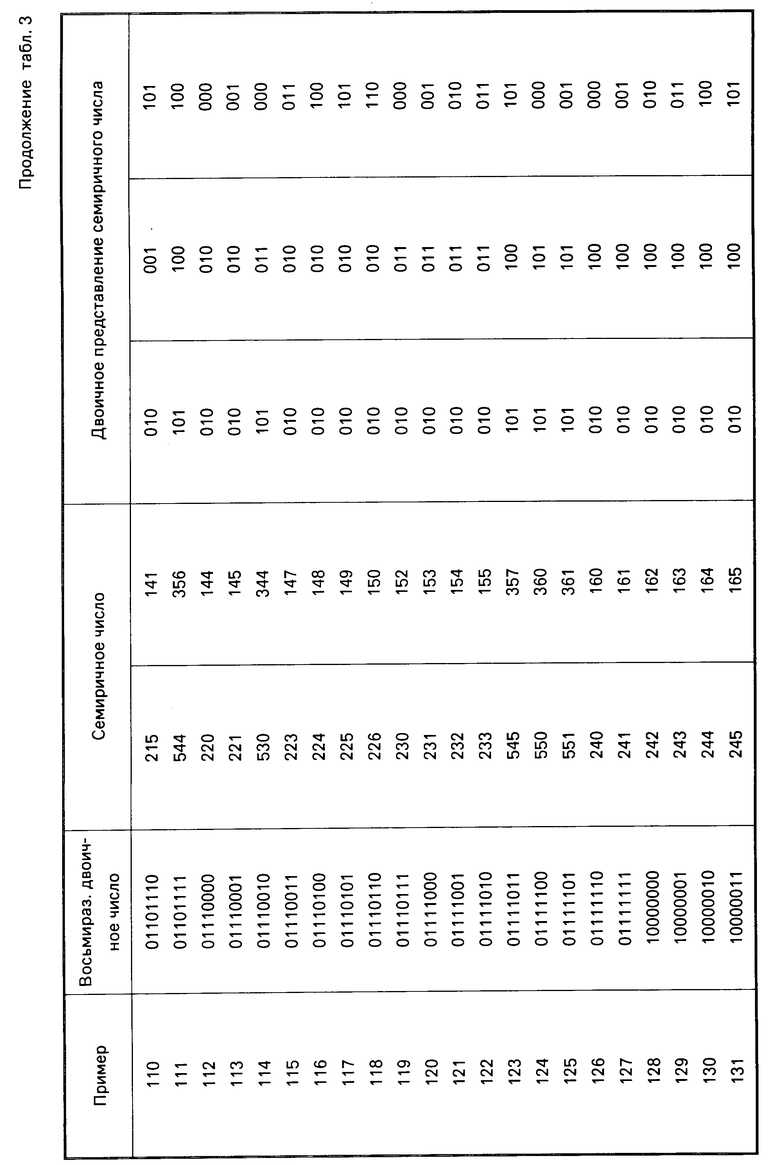

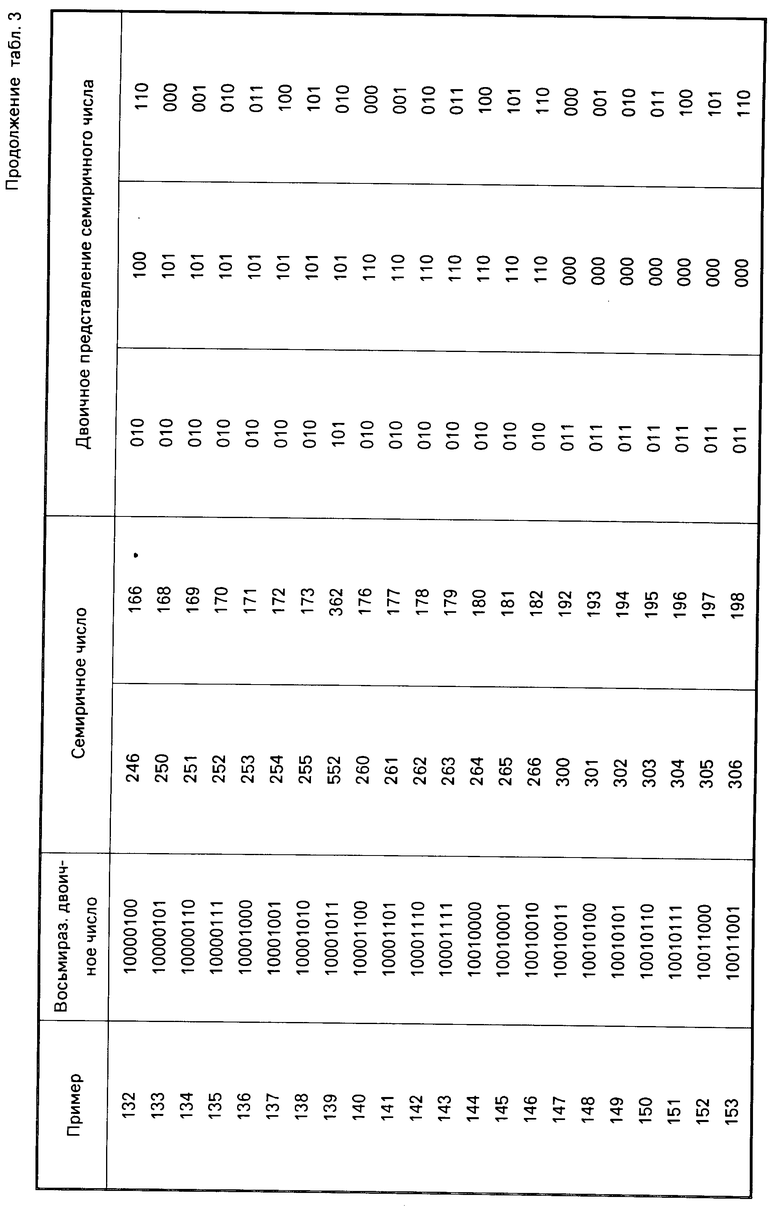

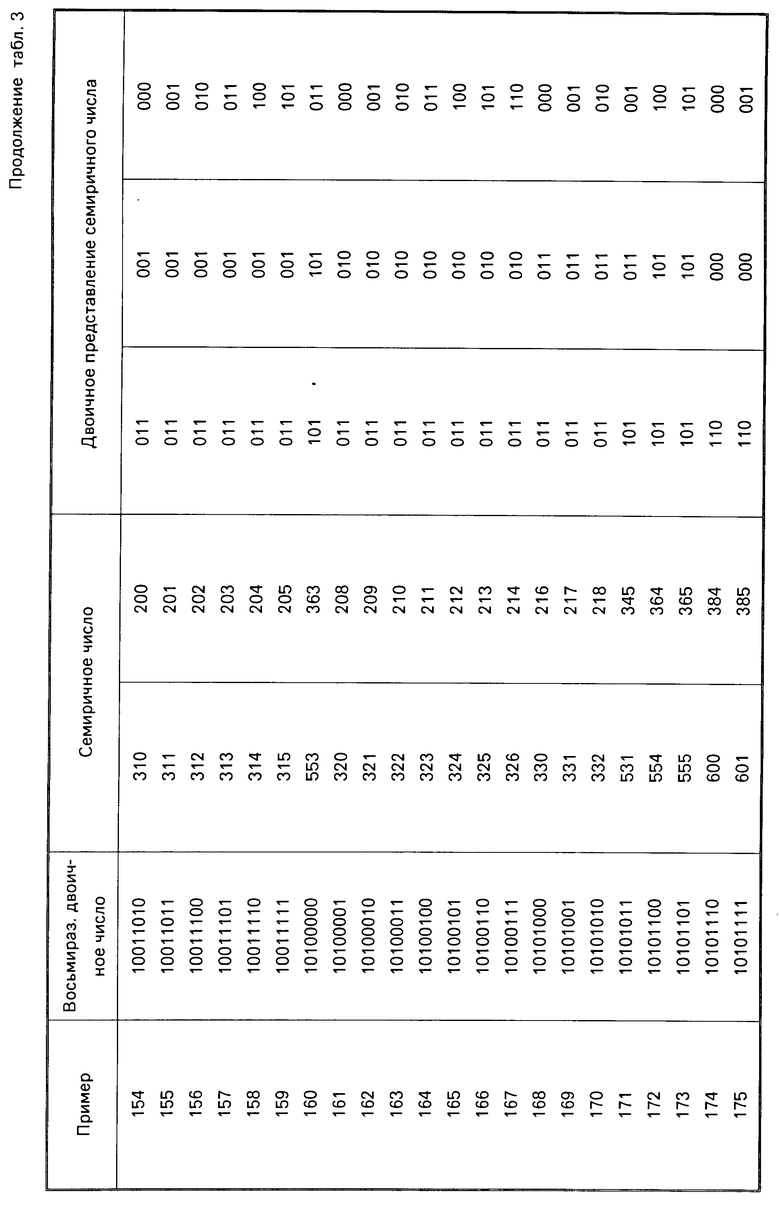

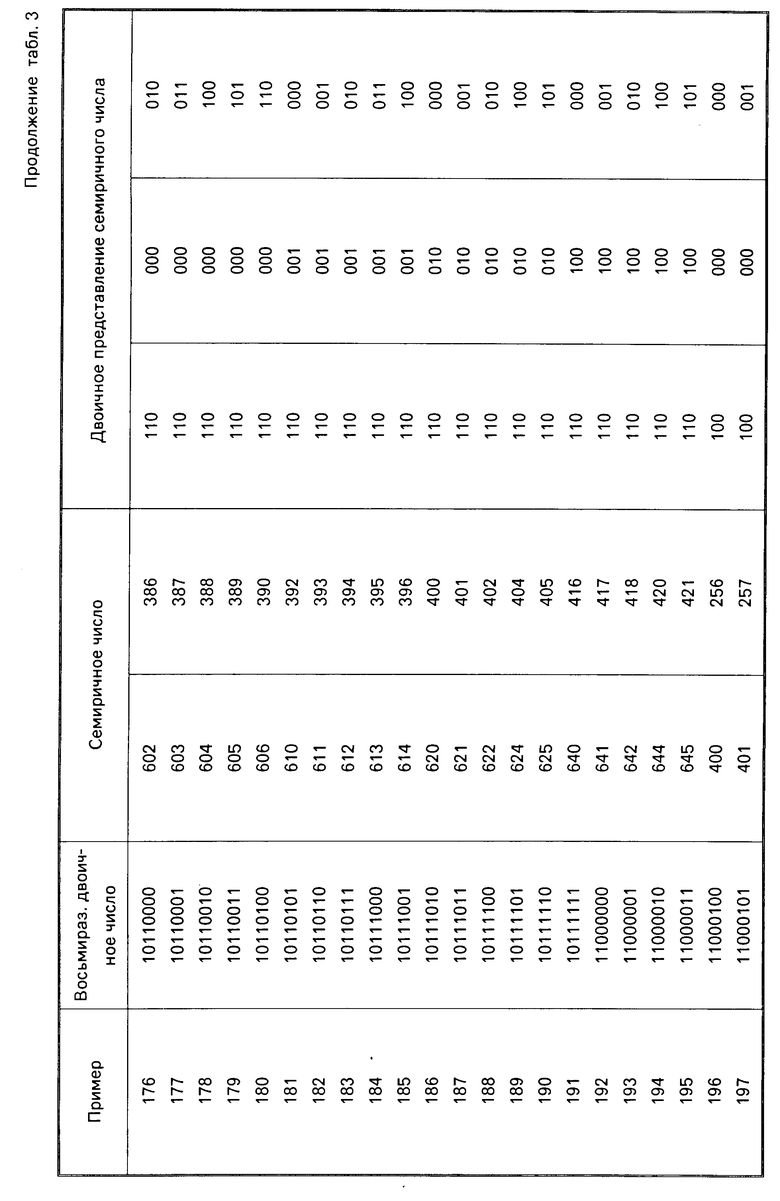

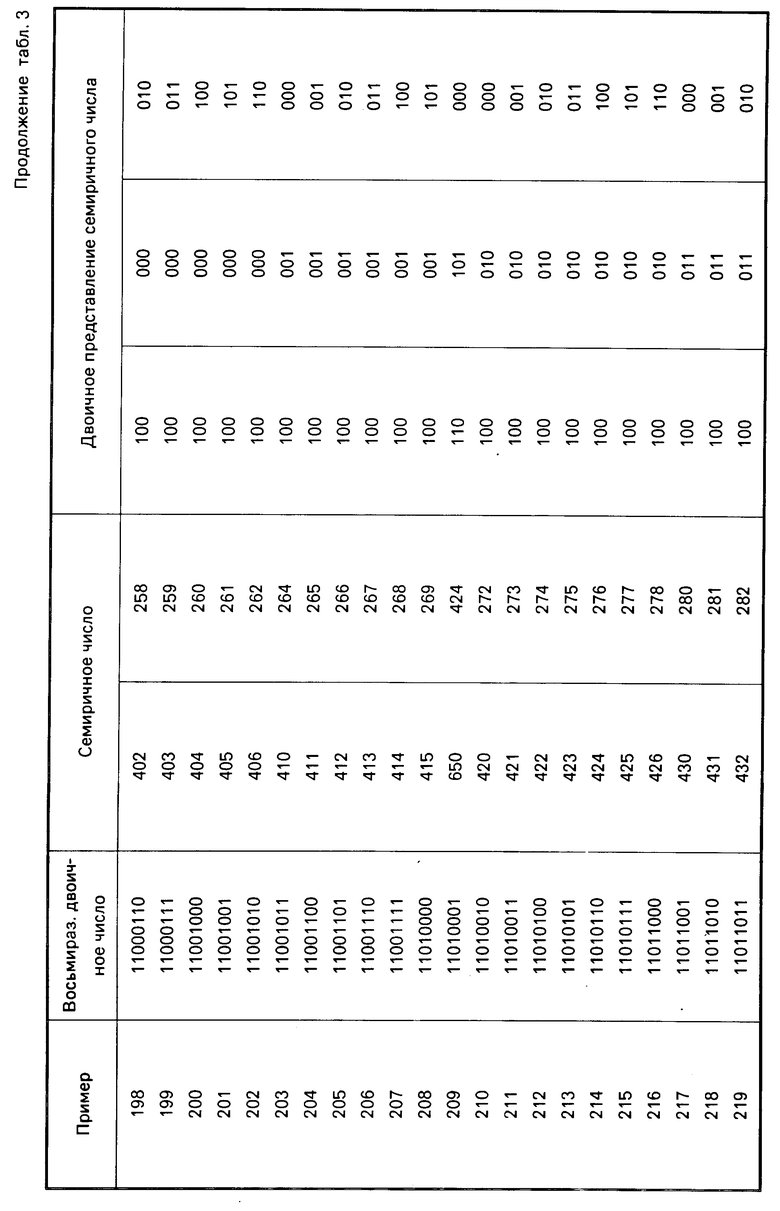

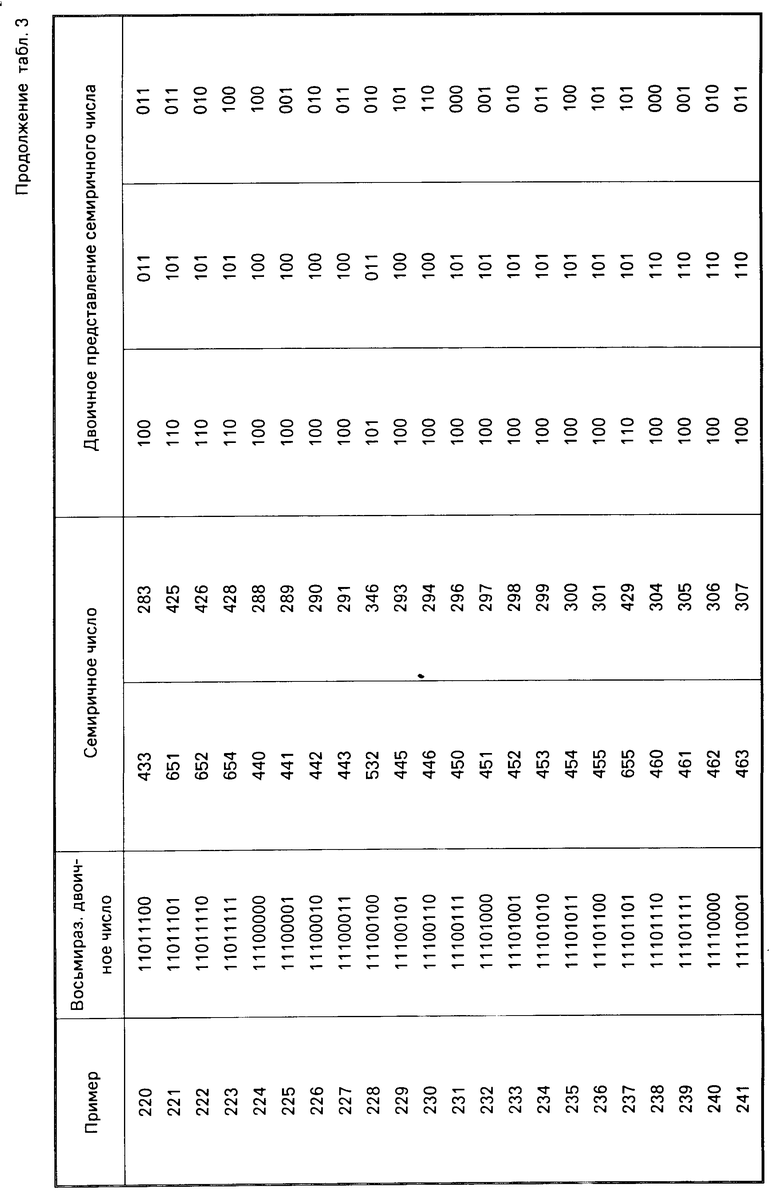

В предлагаемом устройстве исходное тридцатидвухразрядное информационное кодовое слово (а1,а2.а32) аi 0,1 преобразуется в двенадцатиразрядное семиричное кодовое слово (с1, с2.с12) ci . Это возможно, так как 232 < 712. Преобразование осуществляется по правилу перевода числа из двоичной системы счисления в семиричную. Для существенного упрощения всех последующих операций и для сокращения времени преобразования, каждый i-ый семиричный символ ci представляется трехразрядным двоичным кодовым словом (b1i, b2i, b3i), bji 0,1; i

. Это возможно, так как 232 < 712. Преобразование осуществляется по правилу перевода числа из двоичной системы счисления в семиричную. Для существенного упрощения всех последующих операций и для сокращения времени преобразования, каждый i-ый семиричный символ ci представляется трехразрядным двоичным кодовым словом (b1i, b2i, b3i), bji 0,1; i  ; j

; j  в соответствии с табл.3. В результате такого преобразования исходное 32-разрядное двоичное кодовое слово (а1,а2,а32) аi 0,1; представляется 36-разрядным двоичным кодовым словом (b11,b21,b31; b13,b22, b32.b1,b2,b3); bji 0,1; i

в соответствии с табл.3. В результате такого преобразования исходное 32-разрядное двоичное кодовое слово (а1,а2,а32) аi 0,1; представляется 36-разрядным двоичным кодовым словом (b11,b21,b31; b13,b22, b32.b1,b2,b3); bji 0,1; i  ; j

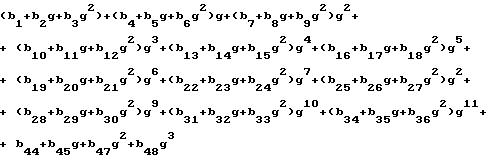

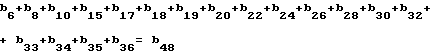

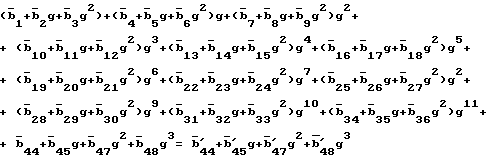

; j  ; ci 0,6. Для увеличения помехоустойчивости заявляемого устройства к сформированному 36-разрядному двоичному кодовому слову добавляется 12 проверочных двоичных символов (b37,b38.b48), которые выбираются таким образом, чтобы в 48-разрядном двоичном кодовом слове обеспечить исправление фазированного пакета ошибок из трех символов. Такое представление фактически соответствует исправлению одного семиричного символа в 16-разрядном семиричном кодовом слове. Остающаяся при этом незначительная избыточность будет использоваться для поддержания блочной синхронизации. Проверочные символы (b37,b38.b48) вычисляются по следующему алгоритму, где все операции суммирования осуществляются по модулю два:

; ci 0,6. Для увеличения помехоустойчивости заявляемого устройства к сформированному 36-разрядному двоичному кодовому слову добавляется 12 проверочных двоичных символов (b37,b38.b48), которые выбираются таким образом, чтобы в 48-разрядном двоичном кодовом слове обеспечить исправление фазированного пакета ошибок из трех символов. Такое представление фактически соответствует исправлению одного семиричного символа в 16-разрядном семиричном кодовом слове. Остающаяся при этом незначительная избыточность будет использоваться для поддержания блочной синхронизации. Проверочные символы (b37,b38.b48) вычисляются по следующему алгоритму, где все операции суммирования осуществляются по модулю два:

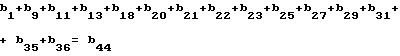

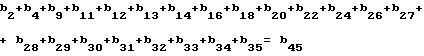

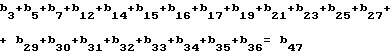

b1+b4+b7+b10+b13+b16+b19+b22+b25+b28+b31+b34= b38

b2+b5+b8+b11+b14+b17+b20+b23+b26+b29+b32+b35= b39

b3+b6+b9+b12+b15+b18+b21+b24+b27+b30+b33+b36= b41

(1)

(2)

Проверочные символы b37, b40, b42, b43, b46 приравниваем к нулю b37= b40 b42 b43 b46 0

Поскольку комбинация (111) избыточная, то для устранения неопределенности в каждую тройку кодовой комбинации проверочных символов, вводится нулевой символ. Из формулы (2), после некоторых преобразований, находим следующие проверочные символы:

(3)

Таким образом, на выходе устройства формируются 48-разрядные двоичные кодовые слова, в которых каждые фазированные три символа соответствуют одному семиричному символу. Тем самым, в предлагаемом устройстве осуществляется преобразование вида 32В-16S, т.е. 32 исходных двоичных символа преобразуются в 16 семиричных символов. Как следует из вышеизложенного, сформированный код обладает минимальным Хеминговым расстоянием dм ≥ 3, т.е. обеспечивает исправление одной любой семиричной ошибки.

Поскольку задержка вводится только в первоначальный момент времени сигналом разрешения, подаваемым на введенный буферный регистр, и то только для синхронизации, и как следует из вышеизложенного все операции выполняются в двоичной системе исчисления, то заявляемое устройство позволяет существенно упростить устройство и уменьшить время преобразования, а также увеличить помехоустойчивость преобразования без снижения плотности цифровой магнитной записи.

Таким образом, предлагаемое устройство позволяет достичь поставленной цели уменьшить время преобразования и повысить помехоустойчивость цифровой магнитной записи без снижения ее плотности.

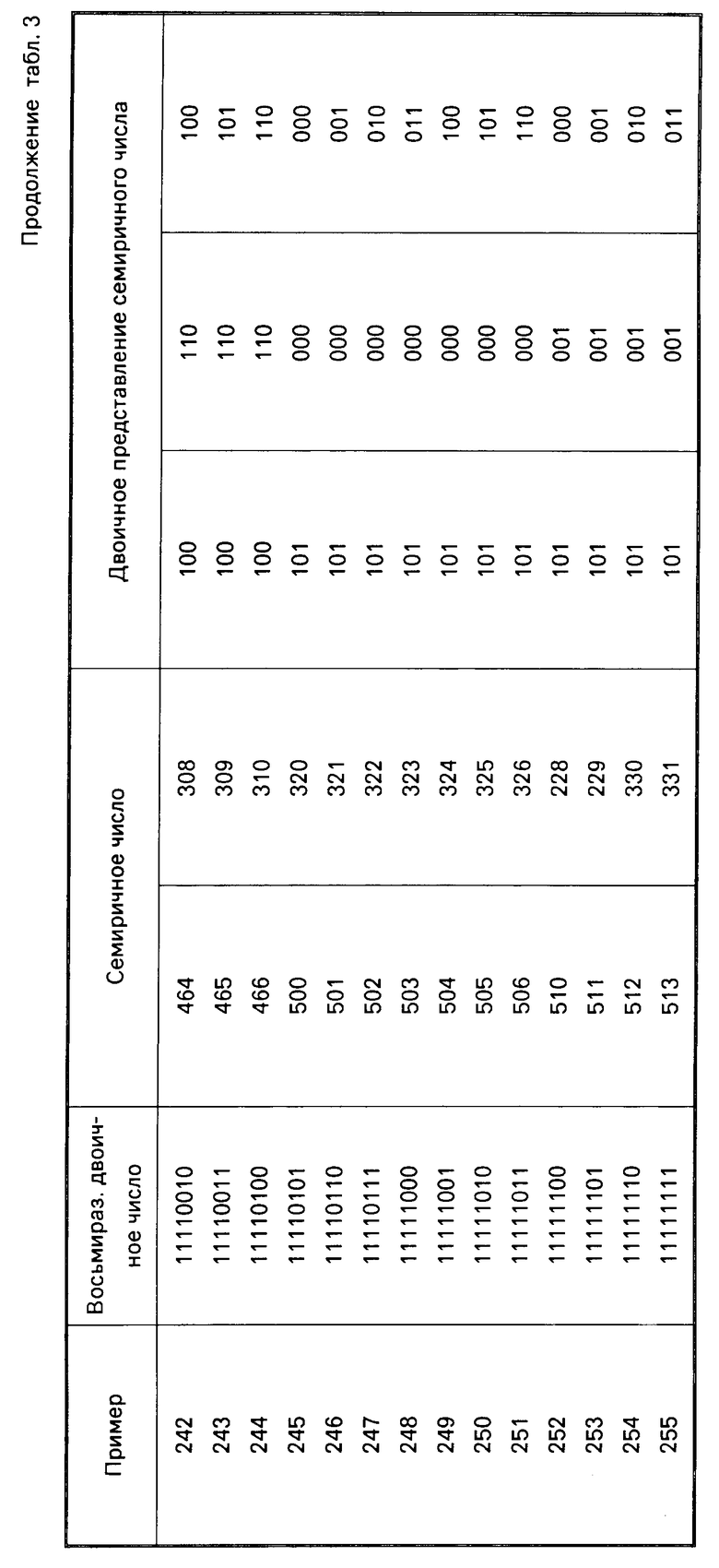

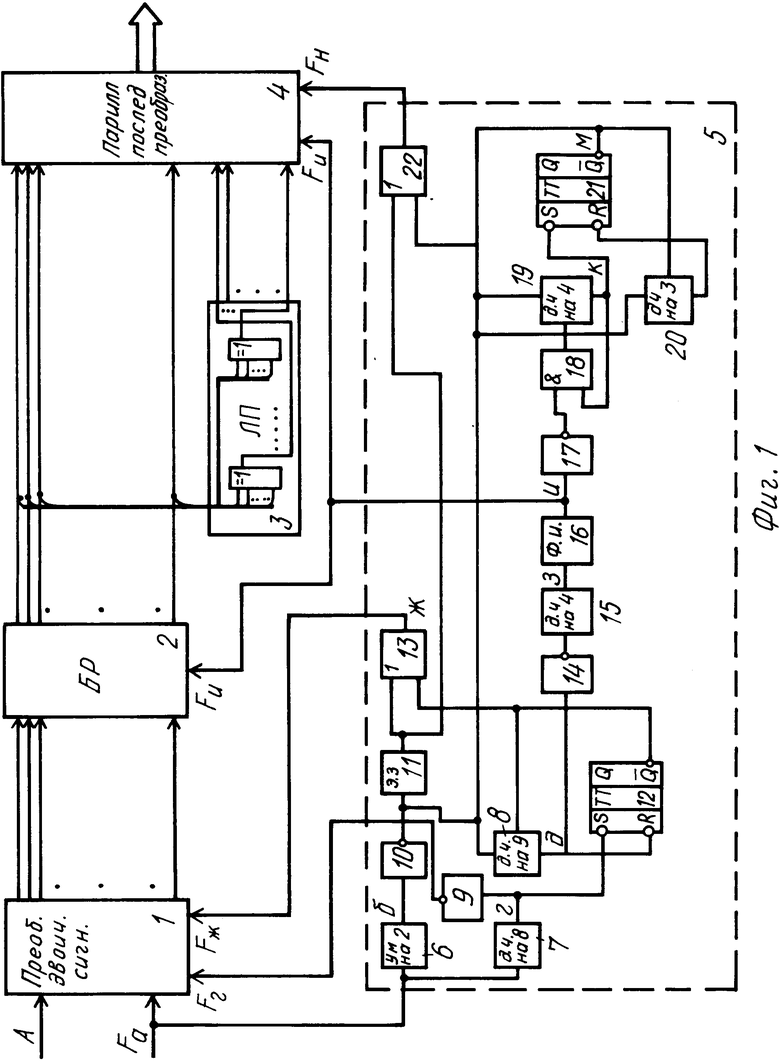

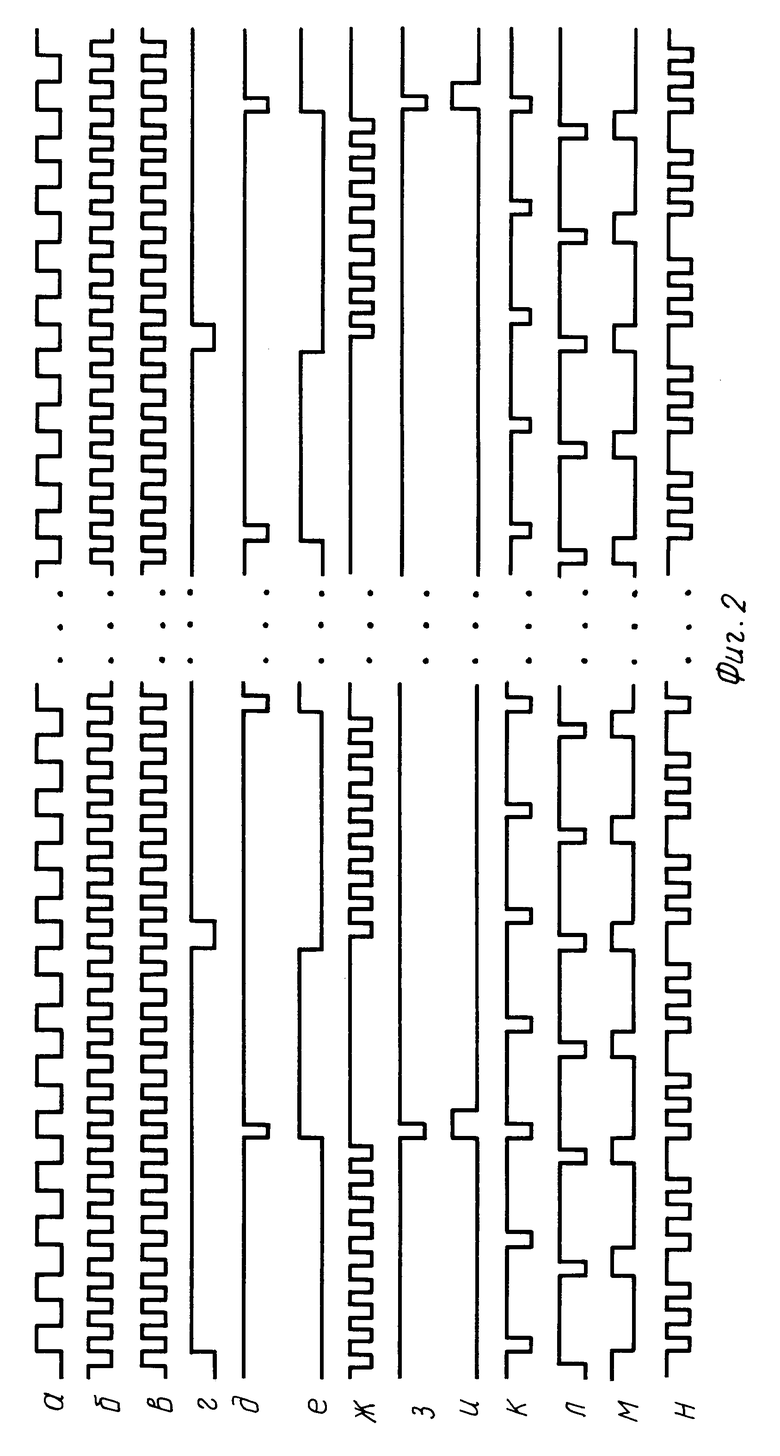

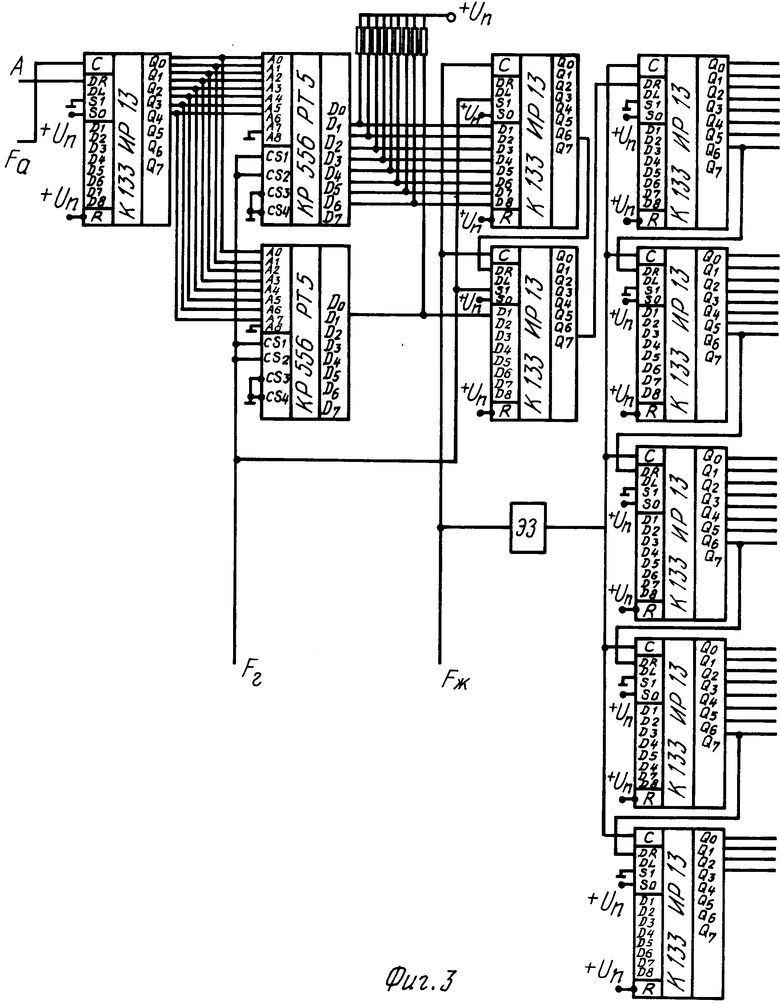

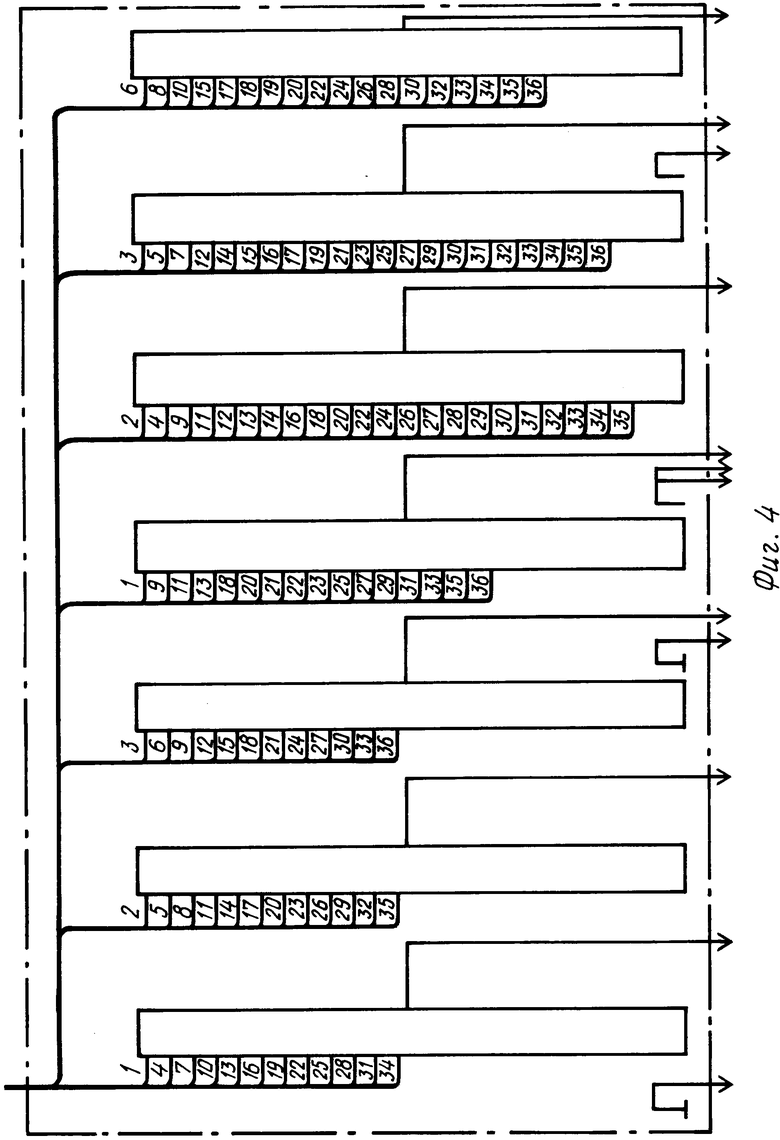

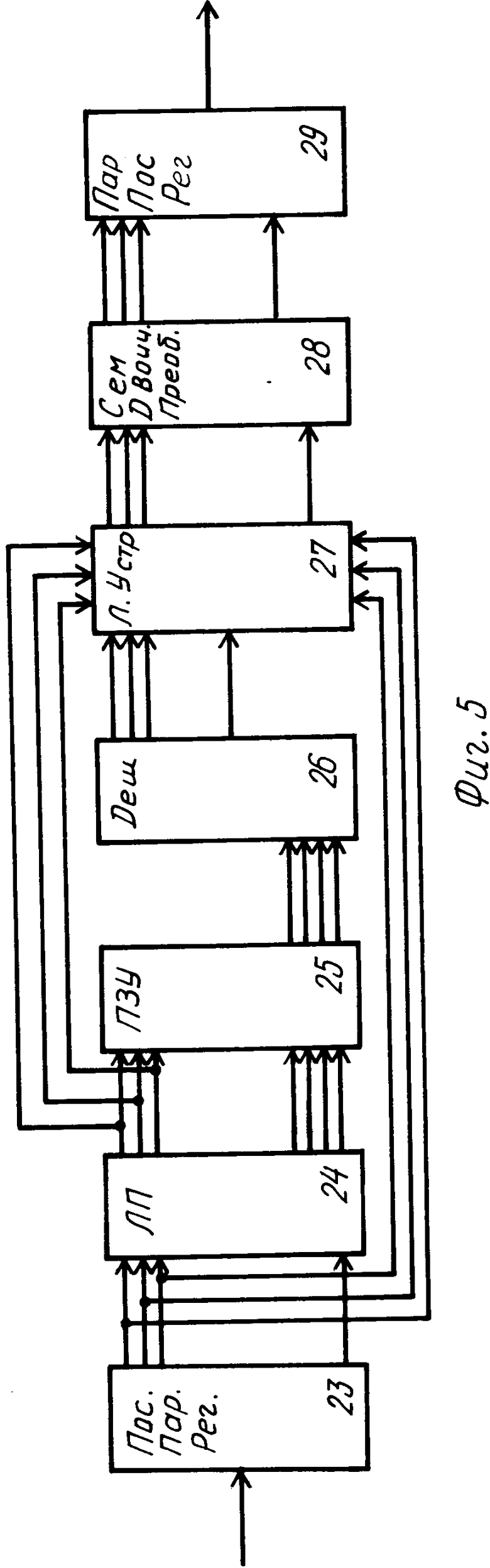

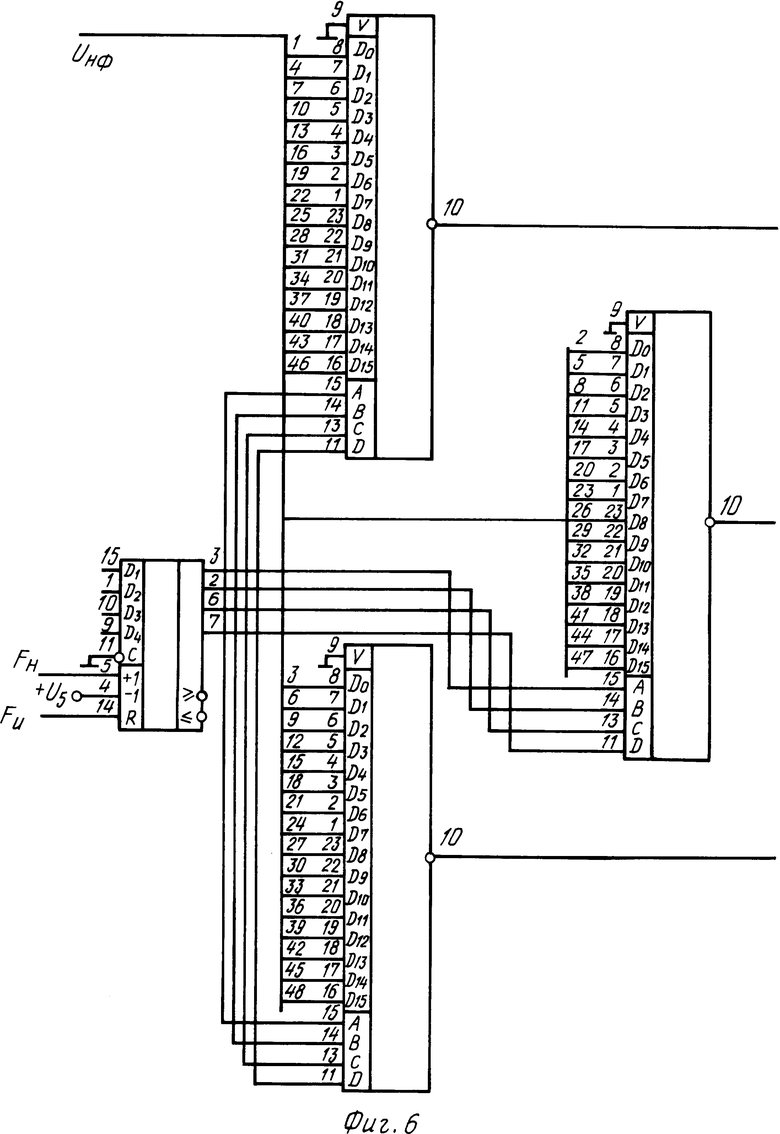

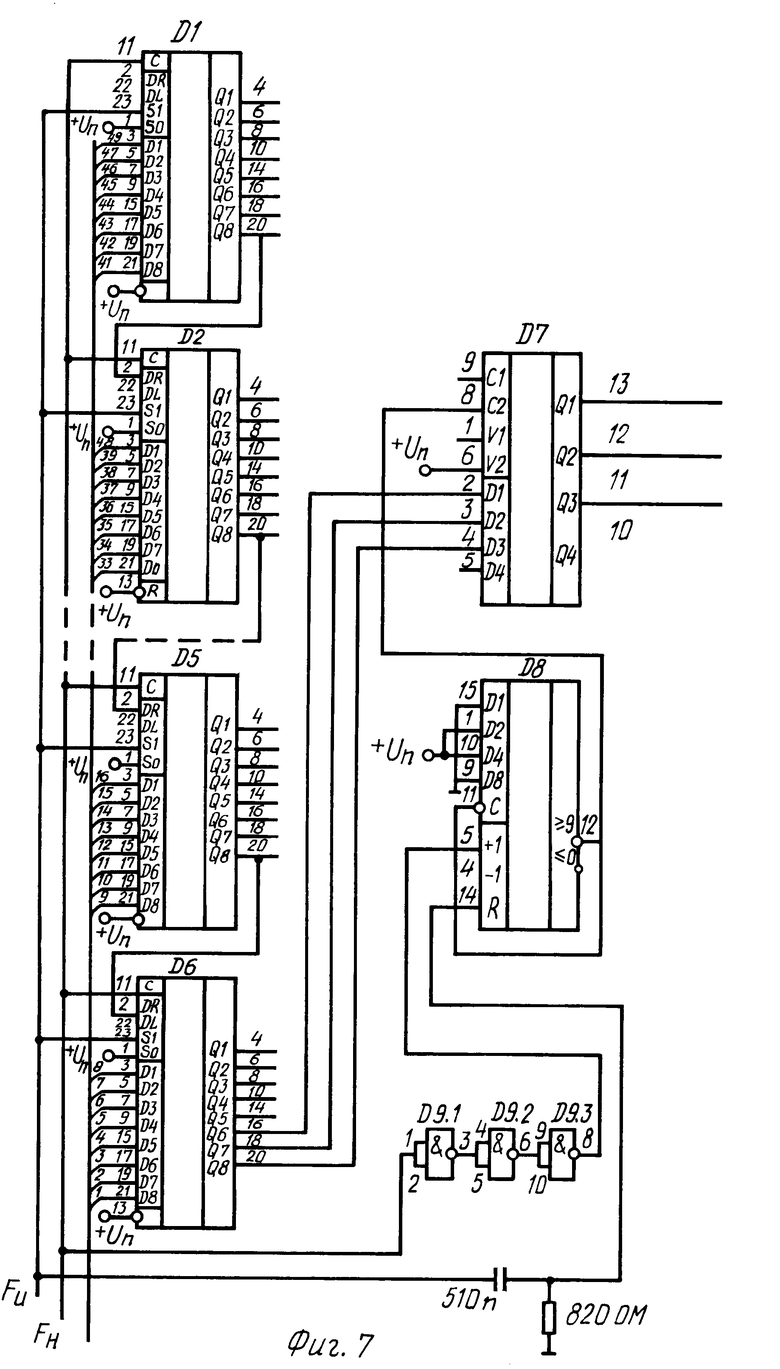

На фиг. 1 приведена структурная схема заявляемого устройства; на фиг.2 эпюры напряжений, иллюстрирующие работу заявляемого устройства; на фиг.3 реализация преобразователя двоичного сигнала; на фиг.4 структурная схема логического переключателя; на фиг.5 структурная схема декодера заявляемого устройства; на фиг. 6 одна из возможных реализаций параллельно последовательного преобразователя 4; на фиг.7 приведена одна из возможных реализаций параллельно-последовательного преобразователя 4.

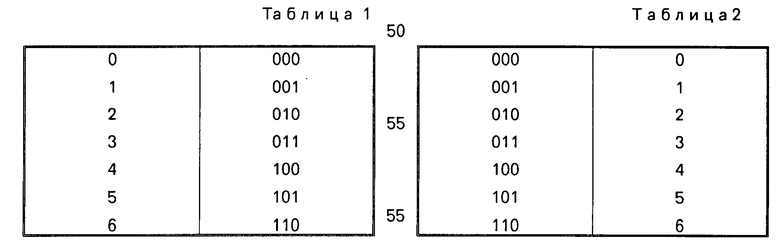

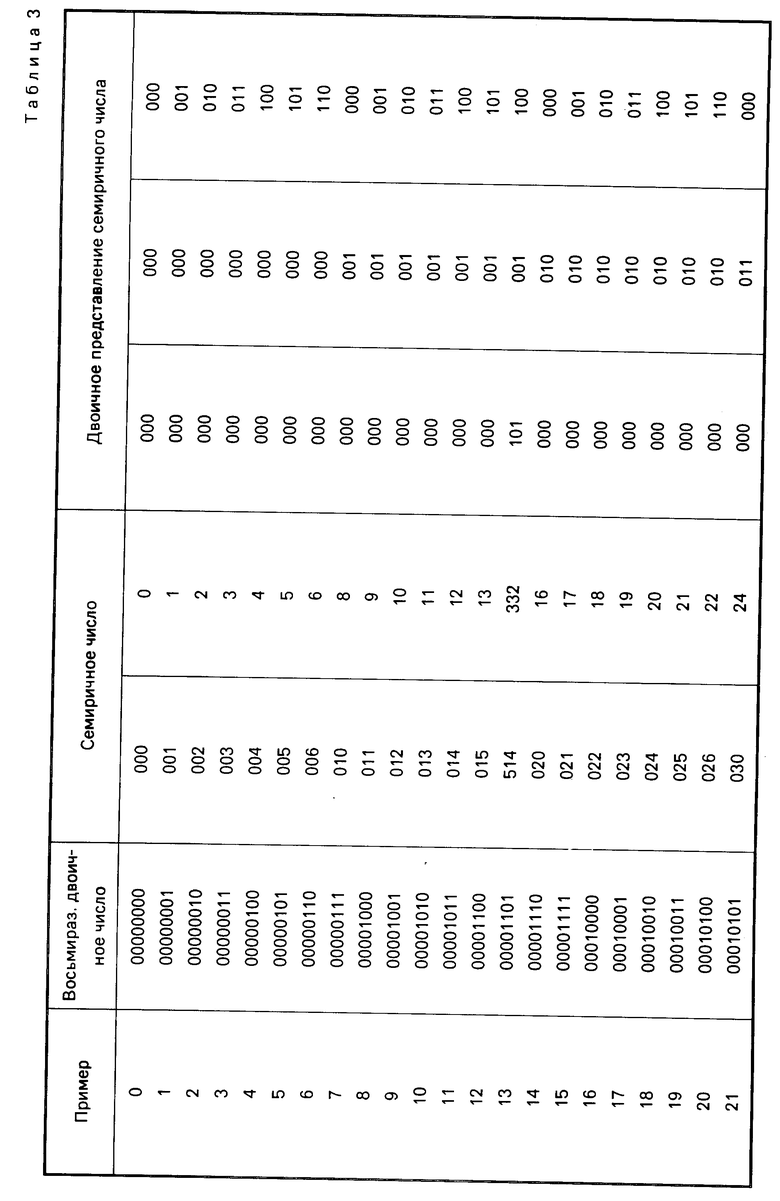

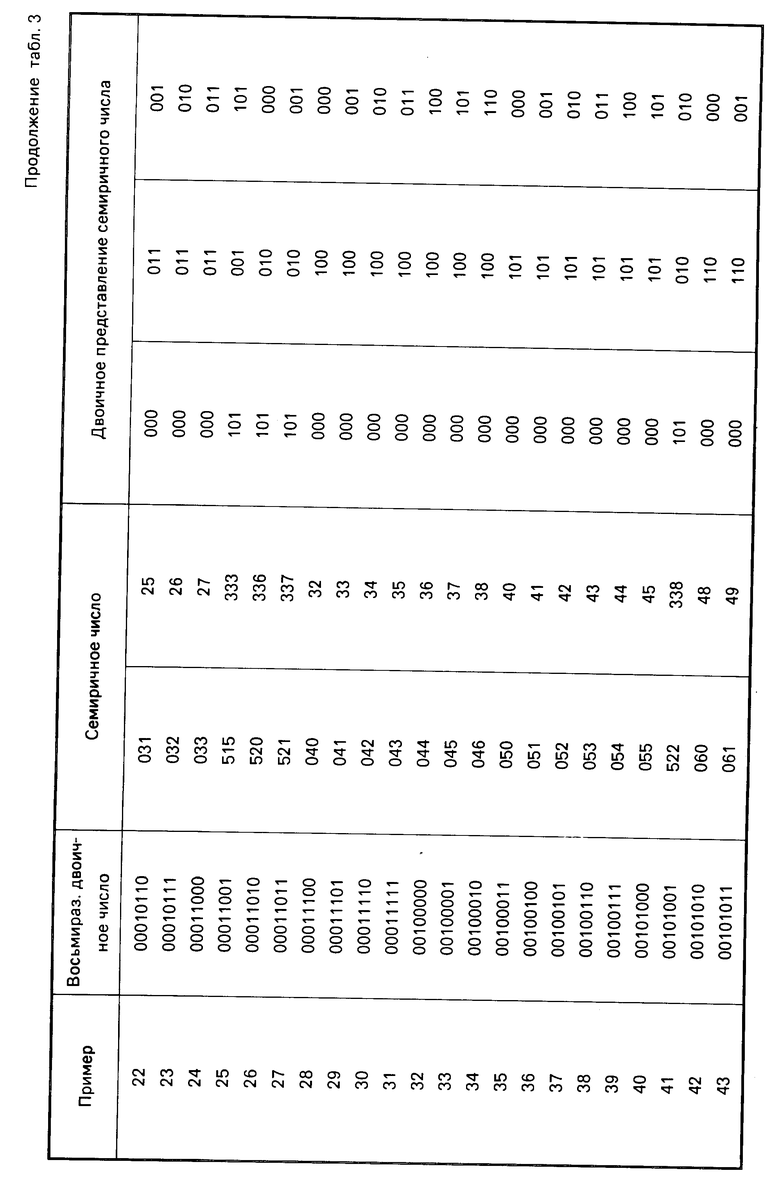

Табл.1 и 2 поясняют работу устройства (кодера) и декодера.

Табл.3 поясняет работу преобразователя 1.

Заявляемое устройство содержит преобразователь двоичного сигнала 1, информационный вход которого является информационным входом устройства, логический переключатель 3, выходы которого подключены к первым информационным входам параллельно-последовательного преобразователя 4, выходы которого являются выходами устройства, блока управления 5 и 36-разрядного буферного регистра, преобразователь двоичного сигнала 1 выполнен в виде двоично-семиричного преобразователя, логический переключатель 3 выполнен на семи сумматорах по модулю два, входы и выходы которых являются соответственно входами и выходами логического переключателя 3, при этом синхровход преобразователя 1 двоичного сигнала объединен с входом блока управления 5 и является входом синхронизации устройства, первый и второй выходы блока управления 5 подключены к первому и второму управляющим входам преобразователя 1 двоичного сигнала, выходы которого подключены к информационным входам 36-разрядного буферного регистра 2, выходы которого подключены к соответствующим входам логического переключателя 3 и вторым информационным входам параллельно-последовательного преобразователя 4, третий выход блока управления 5 подключен к управляющему входу параллельно-последовательного преобразователя 4, второй управляющий вход которого соединен с четвертым выходом блока управления 5, состоящего из умножителя частоты на два 6, делителя частоты на восемь 7, делителя частоты на девять 8, двух делителей частоты на четыре 15, 19 соответственно, делителя частоты на три 20, двух RS-триггеров 12, 21 соответственно, формирователя импульсов 16, элемента задержки 11, двух элементов ИЛИ 13, 22, соответственно, четырех инверторов 9, 10, 14, 17 и элемента И 18, вход умножителя частоты на два 6 объединен c входом умножителя частоты на восемь 7 и является входом блока управления 5, выход делителя частоты на восемь 7 подключен к S-входу первого триггера 12 и к входу первого инвертора 9, выход которого является первым выходом блока управления 5, выход умножителя частоты на два 6, подключен к входу второго инвертора 10, выход которого соединен с первыми входами делителя частоты на девять 8, делителя частоты на три 20, первого делителя частоты на четыре 19 и входом элемента задержки 11, выход которого подключен к первым входам первого и второго элемента ИЛИ 13, 22 соответственно, выходы которых являются соответственно вторым и четвертым выходами блока управления 5, выход делителя частоты на девять 8 подключен непосредственно к R-входу первого триггера 12 и через последовательно соединенные третий инвертор 14, второй делитель частоты на четыре 15 и формирователь импульсов 16 к третьему выходу блока управления 5 и к входу четвертого инвертора 17, выход которого подключен к первому входу элемента И 18, выход которого соединен со вторым входом первого делителя частоты на четыре 19, выход которого подключен ко второму входу элемента И 18 и к S-входу второго триггера 21, выход которого соединен с вторым входом второго элемента ИЛИ 22 и вторым входом делителя частоты на три 20, выход которого подключен к R-входу второго триггера 21, выход первого триггера 12 подключен ко вторым входам первого элемента ИЛИ 13 и делителя частоты на девять 8.

Устройство работает следующим образом. На первый вход преобразователя 1, поступает информационный сигнал с тактовой частотой Fa (фиг.2,а), который преобразуется в параллельный двенадцатиразрядный семиричный сигнал. Преобразование осуществляется по правилу перевода числа из двоичной системы счисления в семиричную. Такое преобразование возможно, так как 232 < 712. Каждый разряд семиричного кодовогоо слова в свою очередь представляется трехразрядной двоичной комбинацией в соответствии с табл.1, 2. Для существенного сокращения объема памяти, используемого в преобразователе 1, используется следующее соответствие между входными и выходными кодами.

Входная последовательность 32-х разрядных двоичных символов разбивается на блоки по 8 двоичных символов. Каждый такой блок (а всего их 4) преобразуется в 3 семиричных символа. Такое преобразование возможно, так как 28 < 73. Для упрощения реализации каждый семиричный символ предствляется блоками из 3-х двоичных символов, причем комбинация 111 является запрещенной. Таким образом, в ПЗУ фактически осуществляется преобразование 8 двоичных символов в 9 двоичных символов, причем за время одного из 32-х разрядного двоичного кодового слова, такое преобразование в ПЗУ осуществляется 4 раза. Соответствие между входными 8-и разрядными и выходными 9-ти разрядными кодами приведено в табл.3 (фиг.6). Такое преобразование соответствует переводу числа из двоичной системы счисления в семиричную. Поскольку комбинация 111 является запрещенной, то в табл.3 (фиг.6) приняты некоторые меры для устранения серии из трех единиц. Тем самым преобразователь двоичного сигнала 1 преобразует тридцатидвухразрядный двоичный сигнал в параллельный тридцатишестиразрядный двоичный сигнал с частотой Fи Fa/32 (фиг.2,и). Принцип работы преобразователя 1 является таким же, как и в устройстве-прототипе и заключается в переводе числа из одной системы счисления в другую. В отличие от прототипа, в предлагаемом устройстве в преобразователе 1 осуществляется представление каждого семиричного числа трехразрядным двоичным словом. Реализация преобразователя известна, возможна на восьми регистрах сдвига серий 133ИР13, двух ПЗУ серий КР556РТ5, элемента задержки и приведена на фиг.3. На вход А преобразователя 1 (фиг.3) в последовательном коде поступает 32-х разрядная двоичная последовательность символов с тактовой частотой Fa(фиг.2,а). Сигнал тактовой частоты поступает на синхровход 1-го восьмиразрядного регистра сдвига, который осуществляет последовательно-параллельное преобразование. С выходов первого регистра 8-ми разрядная двоичная комбинация в параллельном коде поступает на информационные входы первого и второго ПЗУ, которые в паре осуществляют преобразование кодов в соответствии с табл.3 (фиг.6). Сигнал разрешения преобразования кодов служит частота F2 (фиг.2,г). С выходов ПЗУ 9-ти разрядный двоичный сигнал (который соответствует 3-х разрядному семиричному сигналу) поступает на соответствующие входы второго и третьего регистров, на управляющий вход которых поступает частота F2(фиг.2,г), а на тактовый вход частота Fж (фиг.2,ж).

С выхода третьего регистра сдвига сигнал в последовательном коде поступает на информационный вход последовательного ввода информации DR четвертогоо регистра сдвига. В четвертом-седьмом регистре осуществляется последовательно-параллельное преобразование, т.е. преобразование четырех 9-и разрядных последовательных двоичных комбинаций в 36-и разрядную параллельную двоичную комбинацию, которая соответствует 12-ти разрядной семиричной комбинации. Таким образом, в преобразователе 1 осуществляется перевод 32-х разрядного двоичного числа в 12-ти разрядное семиричное, а далее в 36-ти разрядную параллельную двоичную комбинацию, причем благодаря предложенным техническим решениям, такое преобразование не требует огромной памяти (всего 28 бит, а не 232). Тем самым уменьшается время преобразования. С выходов преобразователя 1, преобразованные сигналы поступают на соответствующие входы буферного регистра 2, который служит для запоминания тридцатишестиразрядных символов в течение T' Ta' ˙32. С выходов буферного регистра 2 сигналы без изменения поступают на соответствующие первые 36 входов параллельно-последовательного преобразователя 4, а также на соответствующие входы логического переключателя 3. Принцип работы буферного регистра 2 заключается в осуществлении параллельно-последовательного преобразования, а его реализация известна из литературы.

В логическом переключателя 3 осуществляется операция суммирования по модулю два, в соответствии с алгоритмом кодирования. Реализация логического переключателя 3 известна (фиг.4) и возможна на семи многовходовых сумматорах по модулю два, выполненных на восемнадцати восьмивходовых микросхемах проверки на четность, серий 133ИП2. С выходов логического переключателя 3, сигналы, являющиеся проверочными символами в предлагаемом коды поступают на соответстввующие остальные 12 входов параллельно-последовательного преобразователя 4, выход которого предсталвяет собой трехразрядный код и является выходом устройства. Принцип работы параллельно-последовательного преобразователя 4 заключается в осуществлении преобразования сорокавосьми двоичных символов, представленных в параллельном коде, в группы по 3 двоичных символов, представленных в последовательном коде, причем каждая группа соответствует одному семиричному символу.

Параллельно-последовательный преобразователь 4 предлагаемого устройства выполнен в виде параллельно-последовательного регистра сдвига, три выходных последних разряда которых являются входами трехразрядного параллельно-последовательного регистра, информация которых считывается с частотой Fk (фиг. 2,к).

При этом параллельно-последовательный преобразователь содержит семь регистров сдвига, счетчик, три элемента И, дифференциальную цепочку, причем тактовый вход параллельно-последовательного преобразователя соединен с первыми входами первого, второго, третьего, четвертого, пятого, шестого регистров сдвига, через первый, второй, третий элемент И соединен с вторым входом счетчика, выход которого соединен с первым его входом и с первым входом седьмого регистра сдвига, при этом третий вход счетчика через дифференциальную цепочку соединен с управляющим входом преобразователя, который соединен с управляющим входом первого, второго, третьего, четвертого, пятого, шестого регистра сдвига, второй вход которого соединен с последним выходом пятого регистра сдвига, второй вход которого соединен с последним выходом четвертого регистра, сдвига, второй вход которого соединен с последним выходом третьего регистра сдвига, второй вход которого соединен с последним выходом второго регистра сдвига, второй вход которого соединен с последним выходом первого регистра сдвига, причем информационные входы параллельно-последовательного преобразователя соединены с соответствующими информационными входами первого, второго, третьего, четвертого, пятого, шестого регистра сдвига, три последних выхода которого соединены с тремя первыми информационными входами седьмого регистра сдвига, первые три выхода которого являются выходами параллельно-последовательного преобразователя. Выходом параллельно-последовательного преобразователя 4 является трехразрядное кодовое слово, которое соответствует первому семиричному сигналу следующему с тактовой частотой Fk. Реализация параллельно-последовательного преобразователя 4 известна из литературы.

Параллельно-последовательный преобразователь работает следующим образом. 48-ти разрядные параллельные двоичные символы поступают на соответствующие входы регистров D1-D6 для параллельного ввода, так как регистр сдвига К133ИР13 восьми разрядный, то используется шесть регистров сдвига. Для параллельного ввода с входов 48-ми разрядных двоичных символов на управляющие входы S1, D1-D6 подается сигнал записи Fи (фиг.2,и). Последние выходы D1-D6 соединены с соответствующими входами последовательного ввода информации DR. Информация с регистров сдвига D1-D6 считывается с тактовой частотой Fн (фиг. 2, н), которая поступает на тактовые входы с D1-D6. Тактовая частота через инвертор D9.1 и элемент задержки собранном на D9.2, D9.3 поступает на счетный +1 вход счетчика D6. На вход сброса, для установки нуля на всех выходах счетчика поступает сигнал Fн (фиг.2,и) через дифференциальную цепочку. На элементе D8 собран делитель на три частоты Fн (фиг.2,н), т.е. на выходе D8 получаем частоты Fк (фиг.2,к), которая поступает на тактовый вход С2 регистра сдвига D7, входы которого соединены соответственно с тремя последними выходами регистра сдвига D6. Выходы Q1, Q2, Q3 регистра сдвига D7 являются выходом параллельно-последовательного преобразователя 4 и выходом устройства. Элементы D1-D6 представляют собой регистры сдвига серии К133ИР13, D7 К133ИР1, Д8 133ИЕ6, D9 133ЛАЗ. Тем самым выходом параллельно-последовательного преобразователя является трехразрядное кодовое слово, которое соответствует одному семиричному сигналу следующему с тактовой частотой Fк (фиг.2,к).

Работой преобразователя двоичного сигнала 1, буферного регистра 2 параллельно-последовательного преобразователя 4 управляют сигналы, поступающие с блока управления 5. Тактовая частота Fa (фиг.2,а) поступает на второй вход преобразователя двоичного сигнала 1, а также на вход умножителя 6 частоты на два и на делитель 7 частоты на восемь, с выхода делителя 7 частоты на восемь через последовательно соединенный инвертор 9 частота Fг Fa/8 (фиг.2,г) поступает на третий управляющий вход преобразователя 1, а также на S вход первого RS-триггера 12, с инверсного выхода которого сигнал Fc (фиг.2,е) поступает на вход предварительной установки делителя частоты на девять, который является вторым входом делителя 8 частоты на девять, на первый вход которого, являющийся счетным входом, поступает инверсная удвоенная частота Fв(фиг. 2,в) с выхода второго инвертора 10. Реализация управляемого делителя 8 на девять известна из литературы и возможна на счетчике серии 133ИЕ6. С выхода управляемого делителя 8 частоты на девять сигнал Fд(фиг.2,д) поступает на R вход первого RS-триггера 12, с инверсного выхода которого сигнал Fe, изображенный на фиг.3,е, подается на второй вход первого элемента ИЛИ 13, на первый вход которого через последовательно соединенные второй инвертор и элемент задержки 11 подается инверсная удвоенная тактовая частота Fв (фиг. 2, в). С выхода первого элемента ИЛИ 3 управляющий сигнал Fж (фиг.2,ж) поступает на четвертый управляющий вход преобразователя 1 двоичного сигнала. Для управления буферного регистра с третьего выхода блока управления подается частота Fи Fa/32 (фиг.2,и), которая формируется следующим образом. Сигнал Fд (фиг.2,д) с выхода делителя 8 частоты на девять через последовательно-соединенный третий инвертор 14, первый делитель 15 частоты на четыре (фиг.2,з), формирователь 16 импульсов (фиг.2,и) подается на управляющий вход буферного регистра 2 и на первый управляющий вход параллельно-последовательного преобразователя 4. Сигнал Fи (фиг.2,и) с выхода формирователя импульсов 10 через четвертый инвертор 17 поступает на второй вход второго делителя 19 частоты на четыре, который является входом предварительной установки, с выхода которого сигнал Fк (фиг.2,к) поступает на S вход второго RS-триггера 21, на R вход которого поступает сигнал Fл (фиг.2,л) с выхода делителя частоты на три. Возможная реализация управляющих делителей частоты 19 на четыре и 20 на три, такая же, как и в описанном выше управляемом делителе 8 частоты на девять. Первый вход, являющийся счетным входом делителя 20 частоты на три, соединен с первым входом, являющимся счетным входом второго делителя 19 частоты на четыре, на который поступает инверсная удвоенная тактовая частота Fв (фиг.2,в) с выхода второго инвертора 10. При этом на второй вход делителя 20 частоты на три, который является входом предварительной установки, поступает сигнал Fм(фиг.2,м), с инверсного выхода второго триггера 21, который поступает также на второй вход второго элемента ИЛИ 22, на первый вход которого через элемент 11 задержки поступает инверсная удвоенная частота Fв(фиг.2,в), сигнал Fн (фиг.2,н) с выхода 22 элемента ИЛИ поступает на второй управляющий вход параллельно-последовательного преобразователя 4. Блок управления реализован на стандартных микросхемах серии К133.

Таким образом, заявляемое устройство обеспечивает исправление одной семиричной ошибки при длине семиричного кодового слова m 16. Это позволяет существенно повысить помехоустойчивость без снижения плотности цифровой магнитной записи при одновременном уменьшении времени преобразования.

Предлагаемое изобретение позволяет уменьшить время преобразования, во-первых, за счет того, что все операции выполняются в двоичной системе счисления и в параллель, во-вторых, за счет того, что отсутствет элемент задержки как указывалось, задержка вводится только в первоначальный момент времени сигналом разрешения и то только для синхронизации, а также позволяет в системе цифровой магнитной записи с удвоенной плотностью увеличить помехоустойчивость путем исправления ошибок. Повышение помехоустойчивости достигнутое без снижения плотности записи, что стало возможным благодаря введению элементов в совокупности с их связями. Это позволило осуществить запись семиричного сигнала, а появляющуюся избыточность использовать для исправления ошибок, при этом оставшаяся незначительная избыточность может использоваться для поддержания блочной синхронизации. Предлагаемое устройство обладает также рядом других достоинств: оно обеспечивает самосинхронизацию воспроизведенного сигнала, простоту реализации (кодера) декодера.

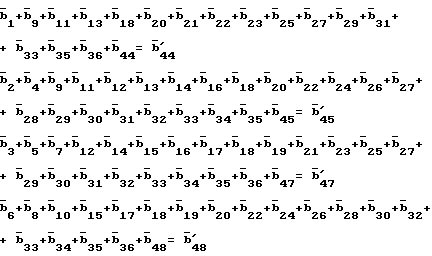

Проведенные экспериментальные исследования полностью подтвердили возможность достижения поставленной цели. Для подтверждения достижения поставленной цели, а также для доказательства однозначности декодирования, рассмотрим работу декодирующего устройства (устройства, выполняющего обратное преобразование), схема которого приведена на фиг.5. Алгоритм работы декодера поясняется следующими выражениями: +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ = e1

= e1 +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ = e2

= e2 +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ +

+ = e3,

= e3,

(4) где (е1, е2, е3) проверочный синдром, суммирование производится по модулю два

(15)

Из формулы (5) после преобразования находим следующие проверочные символы по формулам:

(6)

Из формулы (5) следует

(e1+e2g+e3g2)g6 +

+ g+

g+ g2+

g2+ g3 (7)

g3 (7)

откуда gi=

Пусть кодовое слово представляет собой семиричную последовательность ( ,

,  .

.  )

) =

=  , где каждый символ

, где каждый символ  этой последовательности представляется трехразрядным кодовым словом (

этой последовательности представляется трехразрядным кодовым словом ( ,

, ,

, ),

),  0,1; i

0,1; i  ; j

; j  . Таким образом, на информационный вход декодера поступает 48-разрядное последовательное кодовое слово (

. Таким образом, на информационный вход декодера поступает 48-разрядное последовательное кодовое слово ( ,

,  .

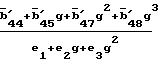

. ), где каждая тройка символов соответствует одному семиричному символу. Причем информационный вход декодера подключен к входу последовательно-параллельного регистра 23, в котором выполняется представление 48 последовательного кодового слова в 48 параллельное кодовое слово, которое поступает на соответствующие входы логического переключателя 24, в котором вычисляются суммы по модулю два по алгоритму (формулы 4, 5, 6). Если синдром е1 е2 е3 0, то входная 48 разрядная информация

), где каждая тройка символов соответствует одному семиричному символу. Причем информационный вход декодера подключен к входу последовательно-параллельного регистра 23, в котором выполняется представление 48 последовательного кодового слова в 48 параллельное кодовое слово, которое поступает на соответствующие входы логического переключателя 24, в котором вычисляются суммы по модулю два по алгоритму (формулы 4, 5, 6). Если синдром е1 е2 е3 0, то входная 48 разрядная информация

из которой берутся только (

из которой берутся только ( ,

,  ,

,

,

, ,

, ) с выхода последовательно-параллельного регистра 23, через последовательно соединенное логическое устройство 24, поступает на семирично-двоичный преобразователь 28, где происходит преобразование кодового слова (

) с выхода последовательно-параллельного регистра 23, через последовательно соединенное логическое устройство 24, поступает на семирично-двоичный преобразователь 28, где происходит преобразование кодового слова ( ,

, ,

,

,

, ,

, ) в кодовое слово (а1, а2, а3.а12), в соответствии с табл.2. С выхода семирично-двоичного преобразователя 28 кодовое слово поступает на параллельно-последовательный регистр 29, в котором происходит представление параллельного 32-разрядного кодового слова в последовательное 32-разрядное кодовое слово. Выход параллельно-последовательного регистра 29 является выходом декодера. Если же хотя бы один из проверочного синдрома символов (е1, е2, е3) не равен нулю, то накладывается запрет на логическое устройство 27 для прохождения 36-разрядного кодового слова. При этом проверочные вычисленные символы (е1, е2, е3) (

) в кодовое слово (а1, а2, а3.а12), в соответствии с табл.2. С выхода семирично-двоичного преобразователя 28 кодовое слово поступает на параллельно-последовательный регистр 29, в котором происходит представление параллельного 32-разрядного кодового слова в последовательное 32-разрядное кодовое слово. Выход параллельно-последовательного регистра 29 является выходом декодера. Если же хотя бы один из проверочного синдрома символов (е1, е2, е3) не равен нулю, то накладывается запрет на логическое устройство 27 для прохождения 36-разрядного кодового слова. При этом проверочные вычисленные символы (е1, е2, е3) ( ,

, ,

, ,

,  ), по алгоритму (формулы 4, 5, 6), с выхода логического переключателя 24 подаются на соответствующие входы программируемого запоминающего устройства (ПЗУ) 25, где в соответствии с алгоритмом (7) хранятся всевозможные решения алгоритма ф.6 в соответствии с арифметикой для GF(16), задаваемой неприводимым примитивным полиномом Х4+Х+1 формулами:

), по алгоритму (формулы 4, 5, 6), с выхода логического переключателя 24 подаются на соответствующие входы программируемого запоминающего устройства (ПЗУ) 25, где в соответствии с алгоритмом (7) хранятся всевозможные решения алгоритма ф.6 в соответствии с арифметикой для GF(16), задаваемой неприводимым примитивным полиномом Х4+Х+1 формулами:

g4 g+1

g5 g2+g

g6 g3+g2

g7 g3+g+1

g8 g2+1

g9 g3+g (8)

g10 g2+g+1

g11 g3+g2+g

g12 g3+g2+g

g13 g3+g2+1

g14 g3+1

g15 1

При этом на выходах ПЗУ 25 формируется 4-разрядное двоичное кодовое слово, указывающее на позицию  в (

в ( ,

, .

. ),

), =

=  где каждый символ

где каждый символ  этой последовательности представлен трехразрядным кодовым словом

этой последовательности представлен трехразрядным кодовым словом  ),

),

;

;  =

=  ; i

; i  ; j

; j  , пакета, где произошла ошибка. С выхода ПЗУ 25 4-разрядное кодовое слово поступает на соответствующие входы дешифратора 26, низкий уровень на выходе которого указывает именно в какой позиции произошла ошибка. С выхода дешифратора 26 12-разрядное кодовое слово поступает на соответствующие входы логического устройства 27, в котором исходя из 12-разрядного кодового слова дается разрешение на пакет, где произошла ошибка. При этом проверочный синдром (е1, е2, е3), который поступает на вход логического устройства 27 с соответствующих выходов логического переключателя 24, суммируется по модулю два именно с тем пакетом (представляющим собой (

, пакета, где произошла ошибка. С выхода ПЗУ 25 4-разрядное кодовое слово поступает на соответствующие входы дешифратора 26, низкий уровень на выходе которого указывает именно в какой позиции произошла ошибка. С выхода дешифратора 26 12-разрядное кодовое слово поступает на соответствующие входы логического устройства 27, в котором исходя из 12-разрядного кодового слова дается разрешение на пакет, где произошла ошибка. При этом проверочный синдром (е1, е2, е3), который поступает на вход логического устройства 27 с соответствующих выходов логического переключателя 24, суммируется по модулю два именно с тем пакетом (представляющим собой ( ,

, ,

, ;

; =0,1; i

=0,1; i  ;j

;j  ) где произошла ошибка.

) где произошла ошибка.

Далее 36-разрядное кодовое слово с выхода логического устройства 27 поступает на соответствующие входы семирично-двоичного преобразователя 28, с выхода которого 32-разрядное параллельное двоичное кодовое слово поступает на соответствующие входы параллельно-последовательного регистра 29, выход которого является выходом устройства. Макет предложенного устройства показал эффективность данного метода и сравнительно простую техническую реализацию.

Таким образом, предлагаемое техническое устройство позволило уменьшить время преобразования, что стало возможным благодаря введению новых элементов в совокупности с их связями. Это позволило все операции выполнить в двоичной системе счисления в параллель, осуществить запись семиричного сигнала, представленного в двоичном коде, а появляющуюся избыточность использовать для исправления ошибок. Это позволило также в системе цифровой магнитной записи с удвоенной плотностью увеличить помехоустойчивость путем исправления ошибок. Повышение помехоустойчивости достигнуто без снижения плотности записи.

Предлагаемое устройство обладает и другими достоинствами: оно обеспечивает самосинхронизацию воспроизведенного сигнала, простоту реализации (кодера) декодера. Проведенные экспериментальные исследования полностью подтвердили возможность достижения поставленной цели.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой магнитной записи-воспроизведения | 1988 |

|

SU1509991A1 |

| Кодек сигнально-кодовой конструкции | 1990 |

|

SU1830623A1 |

| Устройство для регенерации биимпульсных сигналов | 1989 |

|

SU1688413A1 |

| Устройство для исправления ошибок | 1986 |

|

SU1367028A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРОПРОВОДИМОСТИ | 1990 |

|

RU2024885C1 |

| Устройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации | 1989 |

|

SU1608730A1 |

| Преобразователь перемещения в код | 1989 |

|

SU1777240A1 |

| Устройство для исправления ошибок в волоконно-оптических системах передачи информации | 1990 |

|

SU1809534A1 |

| Устройство для оценки достоверности принимаемой информации | 1985 |

|

SU1251153A1 |

| Способ преобразования дискретных сигналов и устройство для его осуществления | 1980 |

|

SU940200A1 |

Изобретение относится к цифровой магнитной записи и может быть использовано для уменьшения времени преобразования, исправления ошибок во внешних запоминающих устройствах микро-ЭВМ и персональных компьютеров. Цель изобретения: уменьшение времени преобразования при одновременном повышении помехоустойчивости цифровой магнитной записи без снижения плотности цифровой магнитной записи. Устройство содержит преобразователь двоичного сигнала, буферный регистр, логический переключатель параллельно-последовательный преобразователь, блок управления, состоящий из умножителя частоты на девять, двух делителей частот на четыре, делителя частоты на три, двух RS-триггеров, формирователя импульсов, элемента задержки, двух элементов ИЛИ, четырех инвертов, элементы И. Снижение помехоустойчивости, вызванное переходом к семиричным сигналам, компенсируется за счет представления семиричного сигнала двоичным сигналом и использования кодирования, которое позволяет исправлять единичные семитричные ошибки любого порядка. 7 ил. 3 табл.

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ, содержащее преобразователь двоичного сигнала, информационный вход которого является информационным входом устройства, логический переключатель, выходы которого подключены к первым информационным входам параллельно-последовательного преобразователя, выходы которого являются выходами устройства, отличающееся тем, что, с целью уменьшения времени преобразования и повышения помехоустойчивости устройства без снижения плотности цифровой магнитной записи, в устройство введены блок управления и 36-разрядный буферный регистр, преобразователь двоичного сигнала выполнен в виде двоичного семиричного преобразователя, логический переключатель выполнен на семи сумматорах по модулю два, входы и выходы которых являются соответственно входами и выходами логического переключателя, синхровход преобразователя двоичного сигнала объединен с входом блока управления и является входом синхронизации устройства, первый и второй выходы блока управления подключены к первому и второму управляющим входам преобразователя двоичного сигнала, выходы которого подключены к информационным входам 36-разрядного буферного регистра, выходы которого подключены к соответствующим входам логического переключателя и вторым информационным входам параллельно-последовательного преобразователя, третий выход блока управления подключен к управляющему входу 36-разрядного буферного регистра и первому управляющему входу параллельно-последовательного преобразователя, второй управляющий вход которого соединен с четвертым выходом блока управления, состоящего из умножителя частоты на два, делителя частоты на восемь, делителя частоты на девять, двух делителей частоты на четыре, делителя частоты на три, двух RS-триггеров, формирователя импульсов, элемента задержки, двух элементов ИЛИ, четырех инверторов и элемента И, вход умножителя частоты на два объединен с входом умножителя частоты на восемь и является входом блока управления, выход детителя частоты на восемь подключен к S-входу первого RS-триггера и входу первого инвертора, выход которого является первым выходом блока управления, выход умножителя частоты на два подключен к входу второго инвертора, выход которого соединен с первыми входами делителя частоты на девять, делителя частоты на три, первого делителя частоты на четыре и входом элемента задержки, выход которого подключен к первым входам первого и второго элементов ИЛИ, выходы которых являются соответственно вторым и четвертым выходами блока управления, выход делителя частоты на девять подключен непосредственно к R-входу первого RS-триггера и через последовательно соединенные третий инвертор, второй делитель частоты на четыре и формирователь импульсов к третьему выходу блока управления и входу четвертого инвертора, выход которого подключен к первому входу элемента И, выход которого соединен с вторым входом первого делителя частоты на четыре, выход которого подключен к второму входу элемента И и S-входу второго RS-триггера, выход которого соединен с вторым входом второго элемента ИЛИ и вторым входом делителя частоты на три, выход которого подключен к R-входу второго RS-триггера, выход первого RS-триггера подключен к вторым входам первого элемента ИЛИ и делителя частоты на девять.

| Способ преобразования дискретных сигналов и устройство для его осуществления | 1980 |

|

SU940200A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1995-09-10—Публикация

1991-04-01—Подача