Изобретение относится к вычислительной технике и технике связи и может использоваться в системах обработки, хранения и передачи информации.

Цель изобретения - повышение быстродействия устройства при кодировании укороченными циклическими кодами с проверочными символами внутри кодового слова.

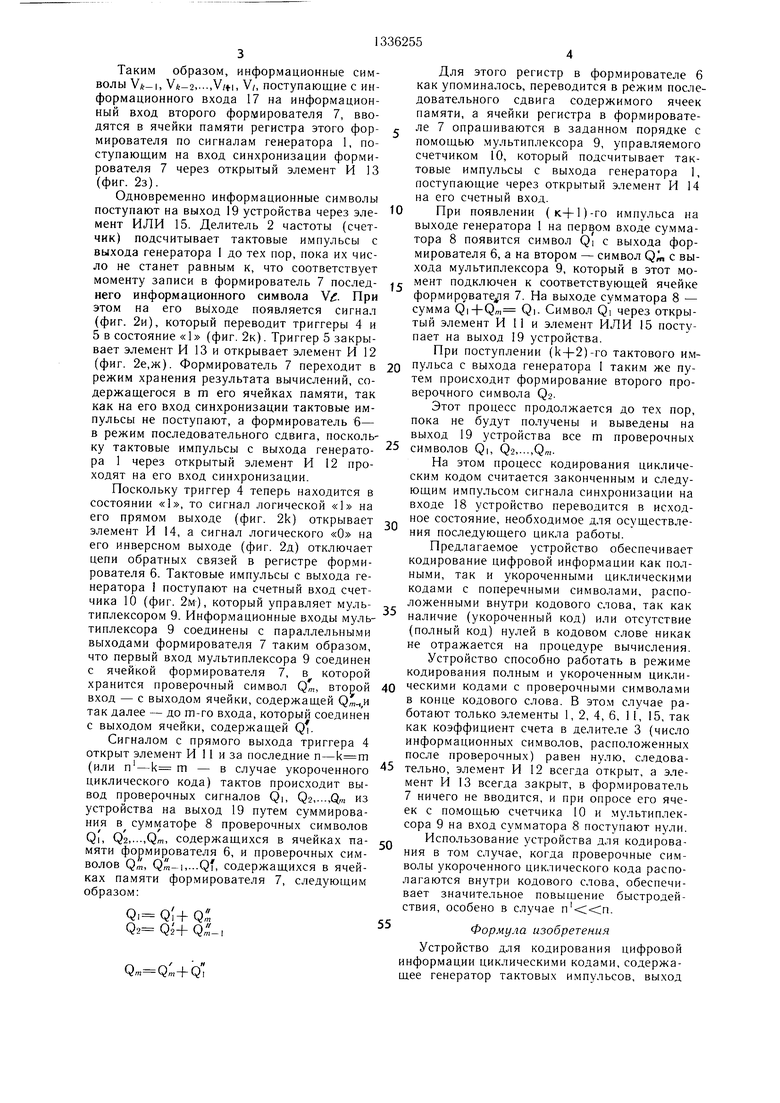

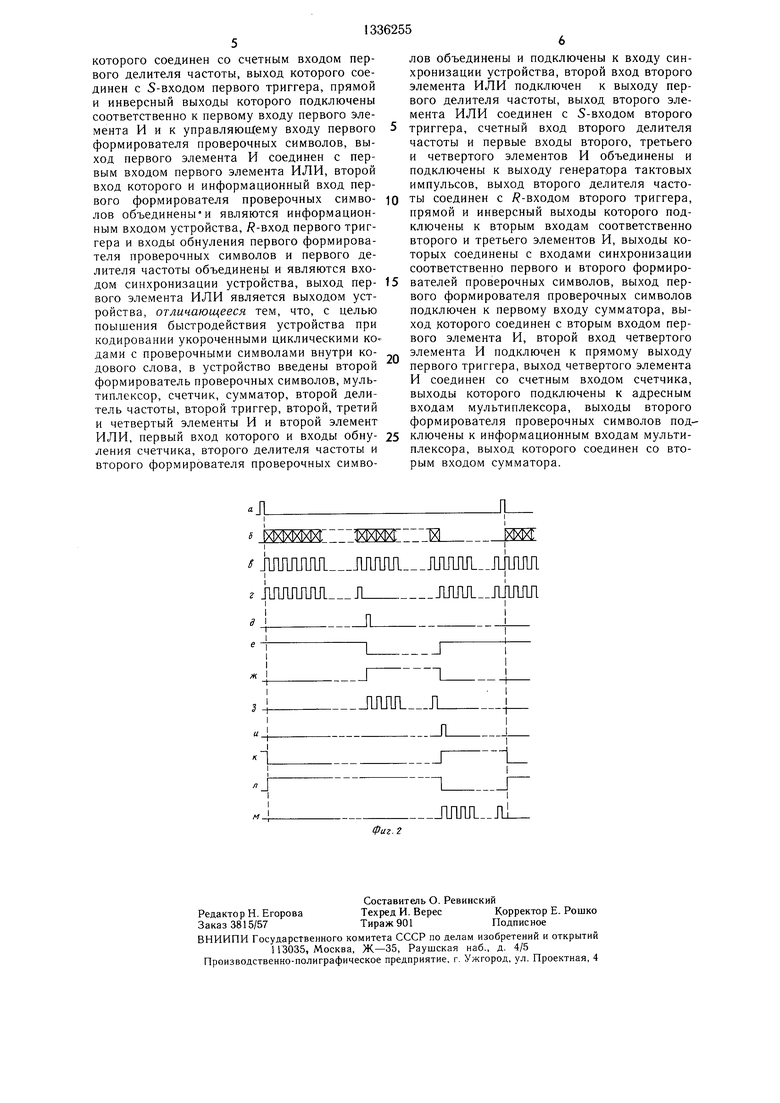

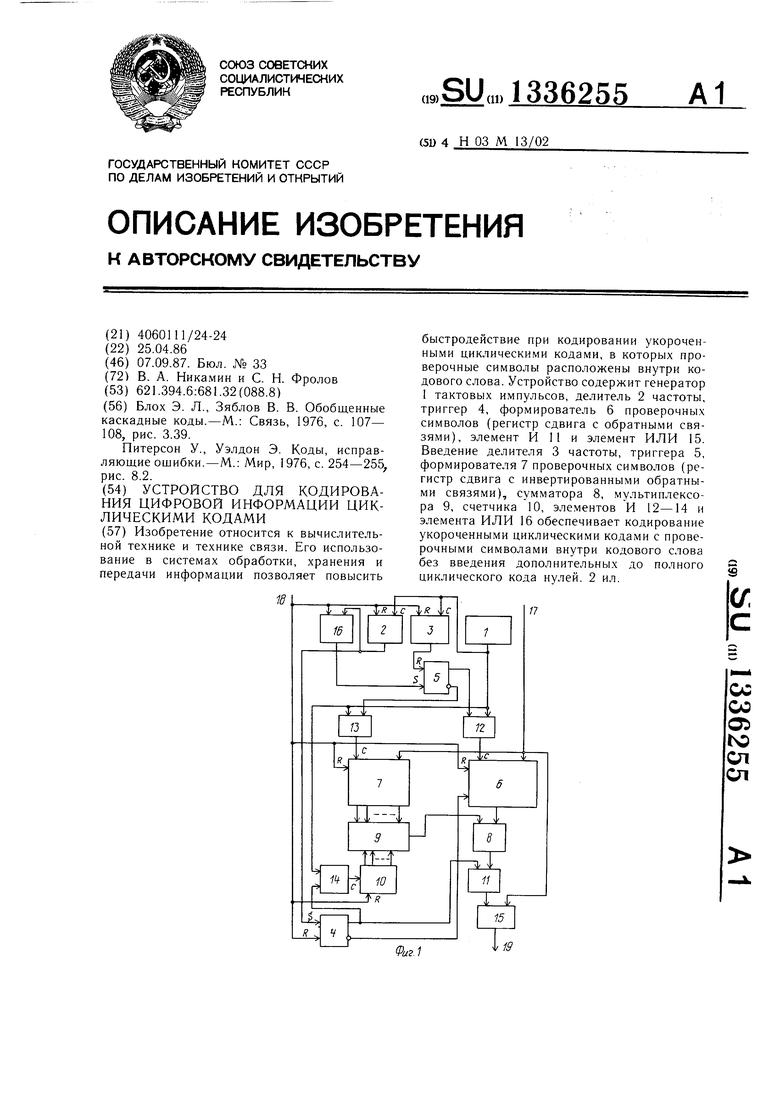

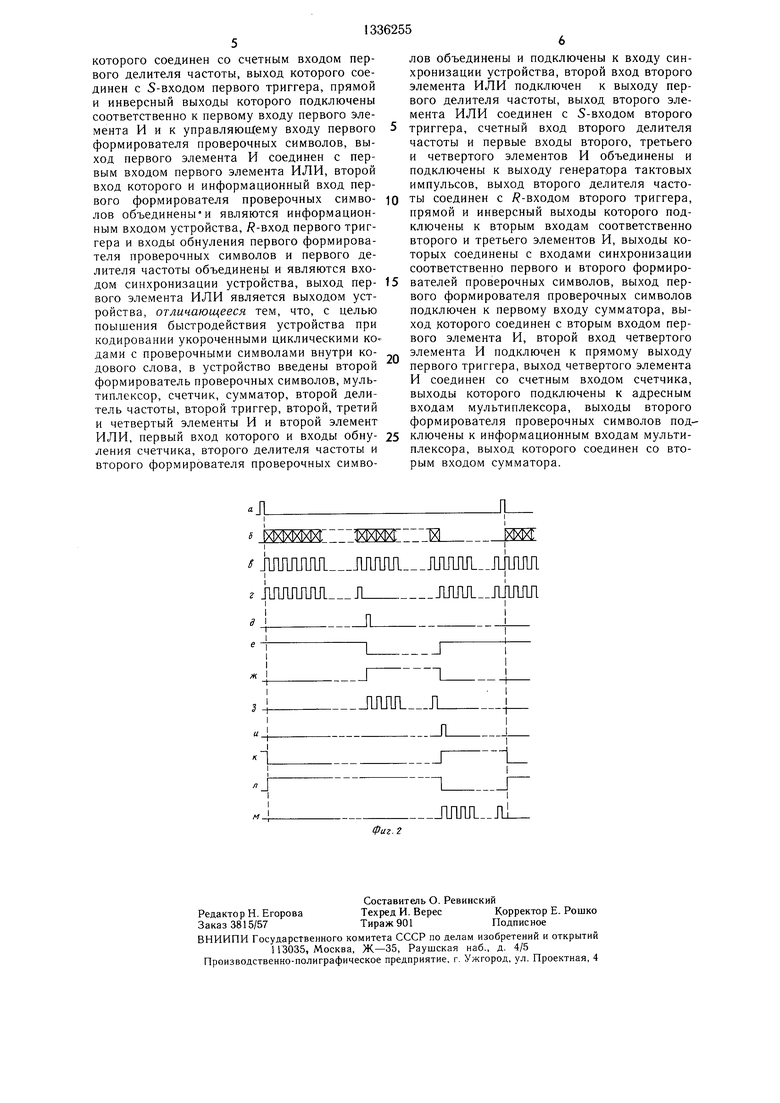

На фиг. 1 дана блок-схема устройства; на фиг. 2 - временные диаграммы его работы.

Устройство для кодирования цифровой информации циклическими кодами содержит генератор 1 тактовых импульсов, первый и второй делители 2 и 3 частоты, первый и второй триггеры 4 и 5, первый и второй формирователи 6 и 7 проверочных символов, сумматор 8, мультиплексор 9, счетчик 10, первый-четвертый элементы И II -14, первый и второй элементы ИЛИ 15 и 16, информационный вход 17, вход 18 синхронизации и выход 19.

Делители 2 и 3 частоты могут быть выполнены на счетчиках с заданным коэффициентом пересчета.

Первый формирователь 6 проверочных символов представляет собой регистр сдвига с обратными связями, выполненными в соответствии с неприводимым полиномом g(x) для первых I информационных символов используемого кода. Обратные связи замыкаются по сигналу на управляющем входе формирователя 6.

15

символов, включая эти нули, до тех пор, пока проверочные символы не переместятся на последние позиции, т.е. приведения кода к виду

V/, V/+,,...,V,,, Q, Q,...,Q, Vo, V,, V2..., Qi, Q2,..., Q«,

в предлагаемом устройстве кодирование производится без введения дополнительных нулей.

Устройство для кодирования цифровой 10 информации циклическими кодами работает следующим образом.

В исходном состоянии, которое возникает при появлении сигнала на входе 18 синхронизации (фиг. 2а), делители 2 и 3 частоты, счетчик 10, триггер 4 и формирователи 6 и 7 находятся в обнуленном состоянии, а триггер 5 - в состоянии «1. Элемент И 12 открыт, а элементы И 11, 13, 14 - закрыты. Обратные связи в формирователе 6 включены сигналом логической «1 с инверсного 20 выхода триггера 4. Обратные связи в формирователе 7 включены в течение всего времени работы устройства.

Информационные символы, поступающие на информационный вход 17 (фиг. 26) проходят на информационные входы формирователей 6 и 7 и одновременно - через элемент ИЛИ 15 - на выход 19 устройства. Тактовые импульсы с выхода генератора 1 тактовых импульсов (фиг. 2в) поступают в это время через открытый элемент И 12 на вход синхронизации первого формирова25

Второй формирователь 7 проверочных сим- теля 6 (фиг. 2г). Поэтому информационные символы Vo, Vi,..., продвигаются по ячейкам регистра сдвига в формирователе 6 до тех пор, пока информационный символ не будет записан во входную ячейку памяти этого регистра. Записи информационных символов в формирователь 7 в это время не производится, так как элемент И 13 закрыт и тактовые импульсы на вход синхронизации формирователя 7 не поступают.

волов выполнен на регистре сдвига такой же длины, как и в формирователе 6, но обратные связи его выполнены в соответствии с неприводимым полиномом g(x), где у х- .

Например, если обратные связи в регистре формирователя 6 выполнены в соответствии с полиномом g(x) х + х+ 1, то обратные связи в регистре формирователя 7 должны быть выполнены в соответствии с полиномом g(x) у + У +

Предлагаемое устройство предназначено для кодирования цифровой информации укороченными циклическими кодами вида (n j k), в которых общее число п символов меньще числа п в циклических кодах (n,k), а число k информационных символов не меняется. При этом укороченный циклический код задан таким образом, что проверочные символы располагаются в середине кодового слова, т.е.

Vo, V,,...,V,,, Qi, Q2,...,Q. V,, V,+ ,,...,V,,, где V;- информационные символы (i О,

I, 2,...,k-1);

Of- проверочные символы (j 1,2,...,гп); I - число информационных символов, расположенных перед проверочными символами.

В отличие от известного устройства, где кодирование такими кодами осуществляется путем записи перед информационными символами п-л нулей и циклического сдвига всех

5

символов, включая эти нули, до тех пор, пока проверочные символы не переместятся на последние позиции, т.е. приведения кода к виду

V/, V/+,,...,V,,, Q, Q,...,Q, Vo, V,, V2..., Qi, Q2,..., Q«,

в предлагаемом устройстве кодирование производится без введения дополнительных нулей.

Устройство для кодирования цифровой 0 информации циклическими кодами работает следующим образом.

В исходном состоянии, которое возникает при появлении сигнала на входе 18 синхронизации (фиг. 2а), делители 2 и 3 частоты, счетчик 10, триггер 4 и формирователи 6 и 7 находятся в обнуленном состоянии, а триггер 5 - в состоянии «1. Элемент И 12 открыт, а элементы И 11, 13, 14 - закрыты. Обратные связи в формирователе 6 включены сигналом логической «1 с инверсного 0 выхода триггера 4. Обратные связи в формирователе 7 включены в течение всего времени работы устройства.

Информационные символы, поступающие на информационный вход 17 (фиг. 26) проходят на информационные входы формирователей 6 и 7 и одновременно - через элемент ИЛИ 15 - на выход 19 устройства. Тактовые импульсы с выхода генератора 1 тактовых импульсов (фиг. 2в) поступают в это время через открытый элемент И 12 на вход синхронизации первого формирова5

теля 6 (фиг. 2г). Поэтому информацион теля 6 (фиг. 2г). Поэтому информацион5

0

5

0

5

ные символы Vo, Vi,..., продвигаются по ячейкам регистра сдвига в формирователе 6 до тех пор, пока информационный символ не будет записан во входную ячейку памяти этого регистра. Записи информационных символов в формирователь 7 в это время не производится, так как элемент И 13 закрыт и тактовые импульсы на вход синхронизации формирователя 7 не поступают.

Делитель 3 частоты (счетчик) при этом подсчитывает тактовые импульсы, вырабатываемые генератором 1. Как только количество этих импульсов станет равным I, что соответствует моменту записи символа в регистр формирователя 6, - на выходе делителя 3 появляется сигнал (фиг. 2д) обнуления триггера 5, который переводится в состояние «О и сигналом со своего прямого выхода закрыват элемент И 12 (фиг. 2е), а сигналом с инверсного выхода открывает элемент И 13 (фиг. 2ж).

Поскольку на вход синхронизации формирователя 6 тактовые импульсы с выхода генератора 1 не поступают (фиг. 2г), то он переходит в режим хранения результата вычислений, которым являются проверочные символы QI , Q2 ...,Qm, вычисленные по первым 1 информационным символам: Vo,V,,...,V,,,Q,, Q2 ,...,Q;.

Далее с помощью второго формирователя 7 вычисляются символы V/, V;+I,...,.

15

Таким образом, информационные символы , ,...,V/.|, V/, поступающие с информационного входа 17 на информационный вход второго формирователя 7, вводятся в ячейки памяти регистра этого фор- 5 мирователя по сигналам генератора 1, поступающим на вход синхронизации формирователя 7 через открытый элемент И 13 (фиг. 2з).

Одновременно информационные символы поступают на выход 19 устройства через эле- 0 мент ИЛИ 15. Делитель 2 частоты (счетчик) подсчитывает тактовые импульсы с выхода генератора 1 до тех пор, пока их число не станет равным к, что соответствует моменту записи в формирователь 7 последнего информационного символа V. При этом на его выходе появляется сигнал (фиг. 2и), который переводит триггеры 4 и 5 в состояние «1 (фиг. 2к). Триггер 5 закрывает элемент И 13 и открывает элемент И 12 (фиг. 2е,ж). Формирователь 7 переходит в 20 режим хранения результата вычислений, содержащегося в m его ячейках памяти, так как на его вход синхронизации тактовые импульсы не поступают, а формирователь 6- в режим последовательного сдвига, поскольку тактовые импульсы с выхода генератора 1 через открытый элемент И 12 проходят на его вход синхронизации.

Поскольку триггер 4 теперь находится в состоянии «1, то сигнал логической «1 на его прямом выходе (фиг. 2k) открывает элемент И 14, а сигнал логического «О на его инверсном выходе (фиг. 2д) отключает цепи обратных связей в регистре формирователя 6. Тактовые импульсы с выхода генератора 1 поступают на счетный вход счетДля этого регистр в формирователе 6 как упоминалось, переводится в режим последовательного сдвига содержимого ячеек памяти, а ячейки регистра в формирователе 7 опрашиваются в заданном порядке с помощью мультиплексора 9, управляемого счетчиком 10, который подсчитывает тактовые импульсы с выхода генератора 1, поступающие через открытый элемент И 14 на его счетный вход.

При появлении (к+1)-го импульса на выходе генератора I на первом входе сумматора 8 появится символ QI с выхода формирователя 6, а на втором - символ Q m с выхода мультиплексора 9, который в этот момент подключен к соответствующей ячейке формировате 1я 7. На выходе сумматора 8 - сумма Qi+Qm QI- Символ Qi через открытый элемент И 11 и элемент ИЛИ 15 поступает на выход 19 устройства.

При поступлении (k+2)-ro тактового импульса с выхода генератора 1 таким же путем происходит формирование второго проверочного символа Qa.

Этот процесс продолжается до тех пор, пока не будут получены и выведены на выход 19 устройства все m проверочных 25 символов QI, Q2,--.,Qm.

На этом процесс кодирования циклическим кодом считается законченным и следующим импульсом сигнала синхронизации на входе 18 устройство переводится в исходное состояние, необходимое для осуществления последующего цикла работы.

Предлагаемое устройство обеспечивает кодирование цифровой информации как полными, так и укороченными циклически.ми

30

кодами с поперечными символами, распо- чика 10 (фиг. 2м), который управляет муль- 5 о енными внутри кодового слова, так как

типлексором 9. Информационные входы мультиплексора 9 соединены с параллельными выходами формирователя 7 таким образом, что первый вход мультиплексора 9 соединен с ячейкой формирователя 7, в которой хранится проверочный символ Qm, второй вход - с выходом ячейки, содержащей Qm-,, так далее - до т-го входа, который соединен с выходом ячейки, содержащей Q|.

Сигналом с прямого выхода триггера 4 открыт элемент И 11 и за последние

наличие (укороченный код) или отсутствие (полный код) нулей в кодовом слове никак не отражается на процедуре вычисления. Устройство способно работать в режиме кодирования полным и укороченным цикли- 40 ческими кодами с проверочными символами в конце кодового слова. В этом случае работают только элементы 1, 2, 4, 6, 11, 15, так как коэффициент счета в делителе 3 (число информационных символов, расположенных после проверочных) равен нулю, следова(или - в случае укороченного тельно, элемент И 12 всегда открыт, а эле- циклического кода) тактов происходит вывод проверочных сигналов Qi, Q2,-.-,Qm из устройства на выход 19 путем суммирования в сумматоре 8 проверочных символов QI, Q2,..-,Qm, содержащихся в ячейках па- о мяти формирователя 6, и проверочных символов Qm, Qm-i,...Qi , содержащихся в ячейках памяти формирователя 7, следующим образом:

мент И 13 всегда закрыт, в формирователь 7 ничего не вводится, и при опросе его ячеек с помощью счетчика 10 и мультиплексора 9 на вход сумматора 8 поступают нули. Использование устройства для кодирования в том случае, когда проверочные символы укороченного циклического кода располагаются внутри кодового слова, обеспечивает значительное повышение быстродействия, особено в случае п «;п.

Q2 Q2-f Q;(,

,+ Ql

5

0 0

Для этого регистр в формирователе 6 как упоминалось, переводится в режим последовательного сдвига содержимого ячеек памяти, а ячейки регистра в формирователе 7 опрашиваются в заданном порядке с помощью мультиплексора 9, управляемого счетчиком 10, который подсчитывает тактовые импульсы с выхода генератора 1, поступающие через открытый элемент И 14 на его счетный вход.

При появлении (к+1)-го импульса на выходе генератора I на первом входе сумматора 8 появится символ QI с выхода формирователя 6, а на втором - символ Q m с выхода мультиплексора 9, который в этот момент подключен к соответствующей ячейке формировате 1я 7. На выходе сумматора 8 - сумма Qi+Qm QI- Символ Qi через открытый элемент И 11 и элемент ИЛИ 15 поступает на выход 19 устройства.

При поступлении (k+2)-ro тактового импульса с выхода генератора 1 таким же путем происходит формирование второго проверочного символа Qa.

Этот процесс продолжается до тех пор, пока не будут получены и выведены на выход 19 устройства все m проверочных 5 символов QI, Q2,--.,Qm.

На этом процесс кодирования циклическим кодом считается законченным и следующим импульсом сигнала синхронизации на входе 18 устройство переводится в исходное состояние, необходимое для осуществления последующего цикла работы.

Предлагаемое устройство обеспечивает кодирование цифровой информации как полными, так и укороченными циклически.ми

0

кодами с поперечными символами, распо- о енными внутри кодового слова, так как

наличие (укороченный код) или отсутствие (полный код) нулей в кодовом слове никак не отражается на процедуре вычисления. Устройство способно работать в режиме кодирования полным и укороченным цикли- ческими кодами с проверочными символами в конце кодового слова. В этом случае работают только элементы 1, 2, 4, 6, 11, 15, так как коэффициент счета в делителе 3 (число информационных символов, расположенных после проверочных) равен нулю, следовательно, элемент И 12 всегда открыт, а эле-

тельно, элемент И 12 всегда открыт, а эле-

мент И 13 всегда закрыт, в формирователь 7 ничего не вводится, и при опросе его ячеек с помощью счетчика 10 и мультиплексора 9 на вход сумматора 8 поступают нули. Использование устройства для кодирования в том случае, когда проверочные символы укороченного циклического кода располагаются внутри кодового слова, обеспечивает значительное повышение быстродействия, особено в случае п «;п.

Формула изобретения

Устройство для кодирования цифровой нформации циклическими кодами, содержаее генератор тактовых импульсов, выход

которого соединен со счетным входом первого делителя частоты, выход которого соединен с S-входом первого триггера, прямой и инверсный выходы которого подключены соответственно к первому входу первого элемента И и к управляющему входу первого формирователя проверочных символов, выход первого элемента И соединен с первым входом первого элемента ИЛИ, второй вход которого и информационный вход первого формирователя проверочных симво- лов объединены И являются информационным входом устройства, У -вход первого триггера и входы обнуления первого формирователя проверочных символов и первого делителя частоты объединены и являются вхолов объединены и подключены к входу синхронизации устройства, второй вход второго элемента ИЛИ подключен к выходу первого делителя частоты, выход второго элемента ИЛИ соединен с S-входом второго триггера, счетный вход второго делителя частоты и первые входы второго, третьего и четвертого элементов И объединены и подключены к выходу генератора тактовых импульсов, выход второго делителя частоты соединен с / -входом второго триггера, прямой и инверсный выходы которого подключены к вторым входам соответственно второго и третьего элементов И, выходы которых соединены с входами синхронизации соответственно первого и второго формиродом синхронизации устройства, выход пер-15 вателей проверочных символов, выход первого элемента ИЛИ является выходом уст-вого формирователя проверочных символов ройства, отличающееся тем, что, с цельюподключен к первому входу сумматора, вы- поышения быстродействия устройства приход которого соединен с вторым входом пер- кодировании укороченными циклическими ко-вого элемента И, второй вход четвертого дами с проверочными символами внутри ко- элемента И подключен к прямому выходу

дового слова, в устройство введены второй -

формирователь проверочных символов, мультиплексор, счетчик, сумматор, второй делитель частоты, второй триггер, второй, третий

и четвертый элементы И и второй элемент

первого триггера, выход четвертого элемента И соединен со счетным входом счетчика, выходы которого подключены к адресным входам мультиплексора, выходы второго формирователя проверочных символов подИЛИ, первый вход которого и входы обну- 25 ключены к информационным входам мульти- ления счетчика, второго делителя частоты и плексора, выход которого соединен со вто- второго формирователя проверочных симво- рым входом сумматора.

лов объединены и подключены к входу синхронизации устройства, второй вход второго элемента ИЛИ подключен к выходу первого делителя частоты, выход второго элемента ИЛИ соединен с S-входом второго триггера, счетный вход второго делителя частоты и первые входы второго, третьего и четвертого элементов И объединены и подключены к выходу генератора тактовых импульсов, выход второго делителя частоты соединен с / -входом второго триггера, прямой и инверсный выходы которого подключены к вторым входам соответственно второго и третьего элементов И, выходы которых соединены с входами синхронизации соответственно первого и второго формирователей проверочных символов, выход первого формирователя проверочных символов подключен к первому входу сумматора, вы- ход которого соединен с вторым входом пер- вого элемента И, второй вход четвертого элемента И подключен к прямому выходу

-

первого триггера, выход четвертого элемента И соединен со счетным входом счетчика, выходы которого подключены к адресным входам мультиплексора, выходы второго формирователя проверочных символов подключены к информационным входам мульти- плексора, выход которого соединен со вто- рым входом сумматора.

Л

Ж1Ш1М ЛМШ1

млшшл..

1

ЛШШ11 ШиШ

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Система для передачи и приема информации | 1988 |

|

SU1583953A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| АДАПТИВНАЯ СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1989 |

|

RU2019045C1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1541651A1 |

| Устройство для декодирования циклических кодов | 1985 |

|

SU1241480A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах обработки, хранения и передачи информации позволяет повысить 18 быстродействие при кодировании укороченными циклическими кодами, в которых проверочные символы расположены внутри кодового слова. Устройство содержит генератор 1 тактовых импульсов, делитель 2 частоты, триггер 4, формирователь 6 проверочных символов (регистр сдвига с обратными связями), элемент И 11 и элемент ИЛИ 15. Введение делителя 3 частоты, триггера 5, формирователя 7 проверочных символов (регистр сдвига с инвертированными обратными связями)., сумматора 8, мультиплексора 9, счетчика 10, элементов И 12-14 и элемента ИЛИ 16 обеспечивает кодирование укороченными циклическими кодами с проверочными символами внутри кодового слова без введения дополнительных до полного циклического кода нулей. 2 ил. S о: с ос СО 05 o СП СП

| Блох Э | |||

| Л., Зяблов В | |||

| В | |||

| Обобщенные каскадные коды.-М.: Связь, 1976, с | |||

| Счетный сектор | 1919 |

|

SU107A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Питерсон У., Уэлдон Э | |||

| Коды, исправляющие ощибки.-М.: Мир, 1976, с | |||

| Гонок для ткацкого станка | 1923 |

|

SU254A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-25—Подача