Изобретение относится к области радиотехники и может найти применение в радиосредствах специальной радиосвязи для высоконадежной передачи данных по радиоканалу в условиях воздействия комплекса помех, а также может быть использовано как элемент более сложного устройства - блока логической обработки, реализующий заданный мажоритарный алгоритм повышения достоверности по совокупности правил мажоритирования [МПК G06F 7/38, Н03K 19/23].

Из уровня техники известен МАЖОРИТАРНЫЙ ЭЛЕМЕНТ [авторское свидетельство СССР №1819100], содержащий управляемый генератор импульсов, 2 счетчика, дешифратор, коммутатор, цифровой компаратор, 3 элемента И и D - триггер.

Недостатком аналога является использование большой номенклатуры логических элементов, а также сложность реализации на электронных компонентах с изменяемой архитектурой.

Наиболее близким по технической сущности является МАЖОРИТАРНЫЙ МОДУЛЬ [патент РФ на изобретение №2533079], при этом вариант реализации им мажоритарной функции «5 и более из 9» содержит совокупность 10 мажоритарных элементов, которые реализуют мажоритарную функцию трех аргументов, 504 двухвходовых элементов И и 123 элемента ИЛИ.

Недостатком прототипа является схемотехническая сложность построения мажоритарного элемента, а также использование большого количества и номенклатуры логических элементов, а также сложность реализации на электронных компонентах с изменяемой архитектурой.

Техническим результатом изобретения является схемотехническое упрощение, сокращение номенклатуры и числа используемых логических элементов, а также обеспечение возможности реализации мажоритарного элемента на электронных компонентах с изменяемой архитектурой.

Технический результат изобретения достигается за счет того, что заявлен мажоритарный элемент «5 и более из 9», содержащий 22 двухвходовых элементов «И» и 21 элементов ИЛИ, отличающийся тем, что содержит девять иерархических уровней с логическими элементами ИЛИ и двухвходовыми элементами И, каждый из первых четырех уровней состоит из четырех пар элементов ИЛИ и И, при этом каждый из восьми первых входов устройства соединен с соответствующей парой элементов ИЛИ и И первого уровня, а девятый вход соединен с четвертой парой логических элементов ИЛИ и И второго уровня, выходы каждого их логических элементов первого уровня соединены с парой элементов ИЛИ и И второго уровня, при этом первый элемент ИЛИ первого уровня соединен с первой парой логических элементов ИЛИ и И третьего уровня, выходы каждого из логических элементов второго уровня соединены с парами логических элементов ИЛИ и И третьего уровня, при этом последний элемент И второго уровня соединен с четвертой парой элементов ИЛИ и И четвертого уровня, выходы каждого их логических элементов третьего уровня соединены с парой элементов ИЛИ и И четвертого уровня, при этом выход первого элемента ИЛИ третьего уровня соединен с первым элементом И пятого уровня к другому входу которого подключен выход первого элемента ИЛИ четвертого уровня, выходы следующей пары элементов И и ИЛИ четвертого уровня подключены ко второму элементу И пятого уровня, при этом выход указанного элемента ИЛИ четвертого уровня также подключен к входу первого элемента И шестого уровня на другой вход которого подключен выход первого элемента И пятого уровня, выходы следующей пары элементов И и ИЛИ четвертого уровня подключены к первому элементу И пятого уровня, при этом выход указанного элемента И четвертого уровня также подключен к элементу ИЛИ шестого уровня, к другому входу которого подключен выход второго элемента ИЛИ пятого уровня, к выходу следующего элемента И четвертого уровня подключен второй элемент ИЛИ пятого уровня к другому входу которого подключен выход последнего элемента И четвертого уровня, выход следующего элемента ИЛИ четвертого уровня подключен к элементу И восьмого уровня, к другому входу которого подключен выход элемента И седьмого уровня, выход первого элемента ИЛИ пятого уровня подключен к второму элементу И шестого уровня и элементу И седьмого уровня, при этом ко второму входу элемента И шестого уровня подключен выход второго элемента И пятого уровня, а ко второму входу элемента И седьмого уровня подключен выход элемента И шестого уровня, выход второго элемента И шестого уровня подключен к элементу ИЛИ седьмого уровня к другому входу которого подключен выход элемента ИЛИ шестого уровня, к входам элемента ИЛИ девятого уровня подключены выход элемента ИЛИ седьмого уровня и выход элемента И восьмого уровня, при этом выход элемента ИЛИ девятого уровня является выходом мажоритарного элемента.

Краткое описание чертежей.

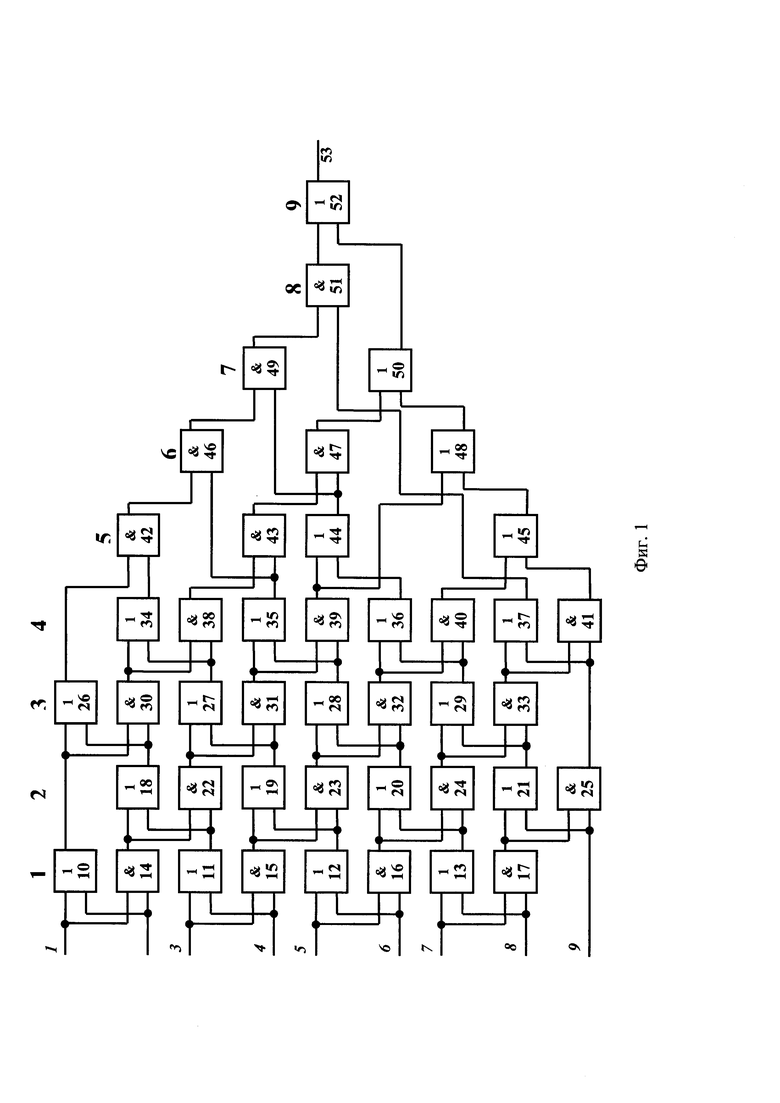

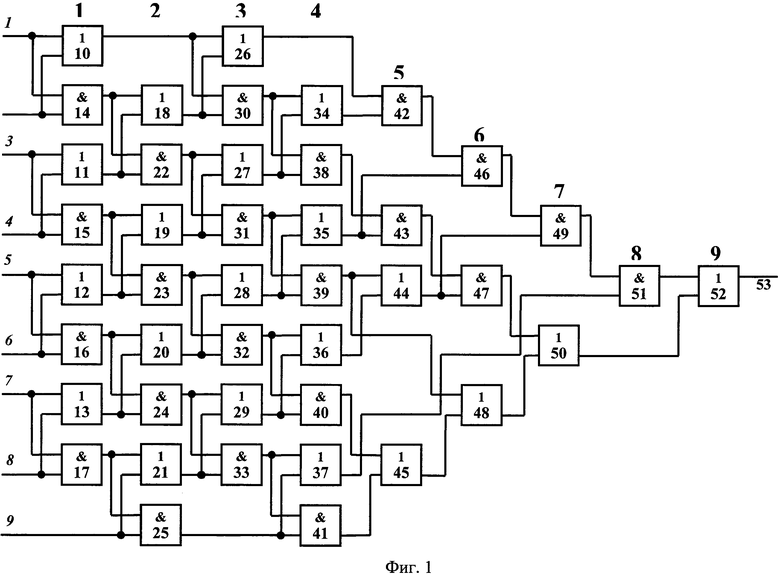

На фиг. 1 представлено схематичное изображение мажоритарного элемента «5 и более из 9».

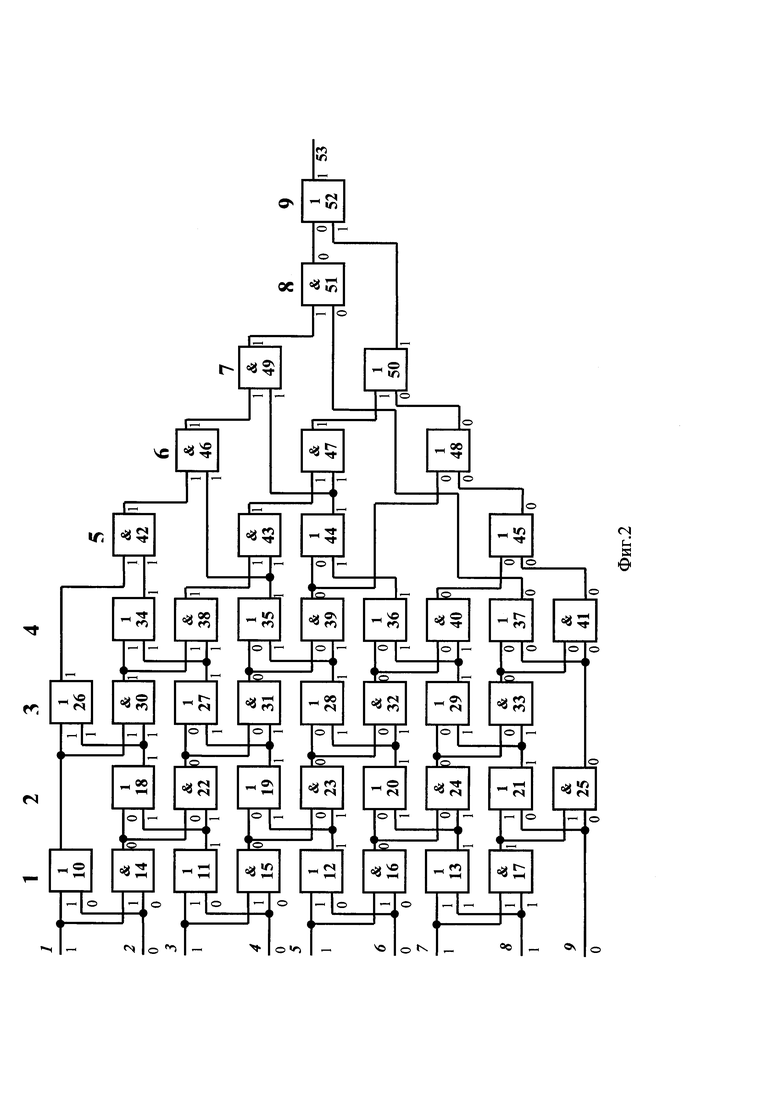

На фиг. 2 представлен пример работы мажоритарного элемента «5 и более из 9».

На чертежах обозначено: 1-9 - входы устройства, 10-13 - элементы ИЛИ первого уровня, 14-17 - элемента И первого уровня, 18-21 - элементы ИЛИ второго уровня, 22-25 - элементы И второго уровня, 26-29 - элементы ИЛИ третьего уровня, 30-33 - элементы И третьего уровня, 34-37 - элементы ИЛИ четвертого уровня, 38-41 - элементы И четвертого уровня, 42-43 - элементы И пятого уровня, 44-45 - элементы ИЛИ пятого уровня, 46-47 - элементы И шестого уровня, 48 - элемент ИЛИ шестого уровня, 49 - элементы И седьмого уровня, 50 - элемент ИЛИ седьмого уровня, 51 - элемент И восьмого уровня, 52 - элемент ИЛИ девятого уровня, 53 - выход устройства.

Осуществление изобретения.

Мажоритарный элемент «5 и более из 9» содержит девять иерархических уровней с логическими элементами ИЛИ и двухвходовыми элементами И, каждый из первых четырех уровней состоит из четырех пар элементов ИЛИ и И, при этом каждый из восьми первых входов 1-8 устройства соединен с соответствующей парой элементов ИЛИ 10-13 и И 14-17 первого уровня, а последний вход 9 соединен с четвертой парой логических элементов ИЛИ 21 и И 25 второго уровня, выходы каждого их логических элементов 11-17 первого уровня соединены с парой элементов ИЛИ 18-21 и И 22-25 второго уровня, при этом первый элемент ИЛИ 10 первого уровня соединен с первой парой логических элементов ИЛИ 26 и И 30 третьего уровня, выходы каждого из логических элементов 18-24 второго уровня соединены с парами логических элементов ИЛИ 26-29 и И 30-33 третьего уровня, при этом последний элемент И 25 второго уровня соединен с четвертой парой элементов ИЛИ 37 и И 41 четвертого уровня, выходы каждого их логических элементов 27-33 третьего уровня соединены с парой элементов ИЛИ 34-37 и И 38-41 четвертого уровня, при этом выход первого элемента ИЛИ 26 третьего уровня соединен с первым элементом И 42 пятого уровня к другому входу которого подключен выход первого элемента ИЛИ 34 четвертого уровня.

Выходы следующей пары элементов И 38 и ИЛИ 35 четвертого уровня подключены ко второму элементу И 43 пятого уровня, при этом выход элемента ИЛИ 35 четвертого уровня также подключен к входу первого элемента И 46 шестого уровня на другой вход которого подключен выход первого элемента И 42 пятого уровня.

выходы следующей пары элементов И 39 и ИЛИ 36 четвертого уровня подключены к Первому элементу И 44 пятого уровня, при этом выход элемента И 39 четвертого уровня также подключен к элементу ИЛИ 48 шестого уровня, к другому входу которого подключен выход второго элемента ИЛИ 45 пятого уровня, к выходу следующего элемента И 40 четвертого уровня подключен второй элемент ИЛИ 45 пятого уровня к другому входу которого подключен выход последнего элемента И 41 четвертого уровня.

Выход следующего элемента ИЛИ 37 четвертого уровня подключен к элементу И 51 восьмого уровня, к другому входу которого подключен выход элемента И 49 седьмого уровня.

Выход первого элемента ИЛИ 44 пятого уровня подключен к второму элемента И 47 шестого уровня и элементу И 49 седьмого уровня, при этом ко второму входу элемента И 47 шестого уровня подключены выход второго элемента И 43 пятого уровня, а ко второму входу элемента И 49 седьмого уровня подключен выход элемента И 46 шестого уровня.

Выход второго элемента И 47 шестого уровня подключен к элементу ИЛИ 50 седьмого уровня к другому входу которого подключен выход элемента ИЛИ 48 шестого уровня.

К входам элемента ИЛИ 52 девятого уровня подключены выход элемента ИЛИ 50 седьмого уровня и выход элемента И 51 восьмого уровня, при этом выход элемента ИЛИ 50 девятого является выходом 53 мажоритарного элемента.

Технический результат изобретения - схемотехническое упрощение мажоритарного элемента, сокращение числа используемых логических элементов и сокращение номенклатуры применяемых логических элементов достигается за счет использования 13 иерархических уровней с логическими элементами ИЛИ и двухвходовыми элементами И.

Прототип содержит 10 мажоритарных элементов, которые реализуют мажоритарную функцию трех аргументов, 504 двухвходовых элементов И и 123 элемента ИЛИ, при этом заявленное техническое решение содержит всего 88 логических элементов, из которых 21 элемента ИЛИ и 22 двухвходовых элементов И, что подтверждает вышеуказанный технический результат.

Технический результат изобретения - обеспечение возможности реализации мажоритарного элемента на электронных компонентах с изменяемой архитектурой достигается за счет использования логических элементов ИЛИ и двухвходовых элементов И, реализация иерархических построений которых технически наиболее простая и реализуется на большинстве электронных компонентов с изменяемой архитектурой, например, программируемых логических микросхемах или различных контроллерах.

Заявленное техническое решение работает следующим образом.

Принцип работы устройства заключается в том, что на входы 1-9 устройства поступает произвольная последовательность двоичных символов «1» и «0», а на выходе устройства 53, по принятому критерию большинства «5 из 9» формируется «ответ» - значение тех элементов входной последовательности, число которых превышает число противоположных. Таким образом, если число «1» среди входных значений превышает число «0», то на выходе устройства будет сформировано значение, равное логической «1», что будет справедливо и в обратном случае: при большем числе «0», выходное значение будет соответствовать логическому «0».

В качестве примера, поясняющего работу мажоритарного элемента «5 и более из 9», рассмотрим поступление на входы устройства 1-9 вектора [1 0 1 0 1 0 1 1 0].

После этого последовательно на выходах каждого из 9 уровней иерархического построения будут сформированы следующие вектора состояний (см. Фиг. 2):

на выходах элементов первого уровня 10, 14, 11, 15, 12, 16, 13, 17 сформируется вектор [1 0 1 0 1 0 1 1];

на выходах элементов второго уровня 18, 22,19, 23, 20, 24, 21, 25 сформируется вектор [1 0 1 0 1 0 1 0];

на выходах элементов третьего уровня 26, 30, 27, 31, 28, 32, 29, 33 сформируется вектор [1 1 1 0 1 0 1 0];

на выходах элементов четвертого уровня 34, 38, 35, 39, 36, 40, 37, 41 сформируется вектор [1 1 1 0 1 0 0 0];

на выходах элементов пятого уровня 42-45 сформируется вектор [1 1 1 0];

на выходах элементов шестого уровня 46-48 сформируется вектор [1 1 0];

на выходах элементов седьмого уровня 49-50 сформируется вектор [1 1].

Выход элемента 51 восьмого уровня примет логическое значение «0», на выходе элемента 52 девятого уровня иерархического построения являющегося выходом 53 устройства сформируется значение «1».

При других входных значениях устройство работает аналогичным образом.

| название | год | авторы | номер документа |

|---|---|---|---|

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "6 И БОЛЕЕ ИЗ 11" | 2016 |

|

RU2621340C1 |

| Адаптивный мажоритарный блок элементов "5 и более из 9" | 2019 |

|

RU2716061C1 |

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "8 И БОЛЕЕ ИЗ 15" | 2016 |

|

RU2617588C1 |

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "7 И БОЛЕЕ ИЗ 13" | 2016 |

|

RU2628222C2 |

| УПРАВЛЯЕМЫЙ МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "ТРИ ИЗ ПЯТИ" | 2017 |

|

RU2651189C1 |

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "4 И БОЛЕЕ ИЗ 7" | 2016 |

|

RU2619197C1 |

| СУММАТОР | 2011 |

|

RU2455680C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| СУММАТОР | 2010 |

|

RU2435196C1 |

| СУММАТОР | 2011 |

|

RU2469381C1 |

Изобретение относится к области радиотехники. Технический результат – схемотехническое упрощение, сокращение номенклатуры и числа используемых логических элементов, обеспечение возможности реализации мажоритарного элемента на электронных компонентах с изменяемой архитектурой. Мажоритарный элемент «5 и более из 9» содержит 22 двухвходовых элемента «И» и 21 элемент ИЛИ и включает девять иерархических уровней с логическими элементами ИЛИ и двухвходовыми элементами И. 2 ил.

Мажоритарный элемент «5 и более из 9», содержащий 22 двухвходовых элемента «И» и 21 элемент ИЛИ, отличающийся тем, что содержит девять иерархических уровней с логическими элементами ИЛИ и двухвходовыми элементами И, каждый из первых четырех уровней состоит из четырех пар элементов ИЛИ и И, при этом каждый из восьми первых входов устройства соединен с соответствующей парой элементов ИЛИ и И первого уровня, а девятый вход соединен с четвертой парой логических элементов ИЛИ и И второго уровня, выходы каждого их логических элементов первого уровня соединены с парой элементов ИЛИ и И второго уровня, при этом первый элемент ИЛИ первого уровня соединен с первой парой логических элементов ИЛИ и И третьего уровня, выходы каждого из логических элементов второго уровня соединены с парами логических элементов ИЛИ и И третьего уровня, при этом последний элемент И второго уровня соединен с четвертой парой элементов ИЛИ и И четвертого уровня, выходы каждого их логических элементов третьего уровня соединены с парой элементов ИЛИ и И четвертого уровня, при этом выход первого элемента ИЛИ третьего уровня соединен с первым элементом И пятого уровня, к другому входу которого подключен выход первого элемента ИЛИ четвертого уровня, выходы следующей пары элементов И и ИЛИ четвертого уровня подключены ко второму элементу И пятого уровня, при этом выход указанного элемента ИЛИ четвертого уровня также подключен к входу первого элемента И шестого уровня, на другой вход которого подключен выход первого элемента И пятого уровня, выходы следующей пары элементов И и ИЛИ четвертого уровня подключены к первому элементу И пятого уровня, при этом выход указанного элемента И четвертого уровня также подключен к элементу ИЛИ шестого уровня, к другому входу которого подключен выход второго элемента ИЛИ пятого уровня, к выходу следующего элемента И четвертого уровня подключен второй элемент ИЛИ пятого уровня, к другому входу которого подключен выход последнего элемента И четвертого уровня, выход следующего элемента ИЛИ четвертого уровня подключен к элементу И восьмого уровня, к другому входу которого подключен выход элемента И седьмого уровня, выход первого элемента ИЛИ пятого уровня подключен ко второму элементу И шестого уровня и элементу И седьмого уровня, при этом ко второму входу элемента И шестого уровня подключен выход второго элемента И пятого уровня, а ко второму входу элемента И седьмого уровня подключен выход элемента И шестого уровня, выход второго элемента И шестого уровня подключен к элементу ИЛИ седьмого уровня, к другому входу которого подключен выход элемента ИЛИ шестого уровня, к входам элемента ИЛИ девятого уровня подключены выход элемента ИЛИ седьмого уровня и выход элемента И восьмого уровня, при этом выход элемента ИЛИ девятого уровня является выходом мажоритарного элемента.

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2013 |

|

RU2533079C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2015 |

|

RU2580801C1 |

| СПОСОБ СПАИВАНИЯ СТЕКЛЯННЫХ ТРУБОК С РАЗЛИЧНЫМИ КОЭФИЦИЕНТАМИ РАСШИРЕНИЯ | 1936 |

|

SU52287A1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2012 |

|

RU2473954C1 |

| Устройство для автоматической зарядки уточными шпулями магазина ткацкого станка | 1949 |

|

SU81019A1 |

| US 5382950 A, 17.01.1995. | |||

Авторы

Даты

2018-08-28—Публикация

2016-01-21—Подача