Изобретение относится к автоматике и вычислительной техники и может быть использовано для непрерывного контроля работоспособности средств вычислительной техники, функционирующих в условиях непрерывной динамики и постоянных изменений параметров внешних условий и с учетом повышенных требований к их надежности.

Наиболее близким по технической сущности является мажоритарный блок элементов «5 и более из 9», при этом вариант реализации им мажоритарной функции «5 и более из 9» содержит 22 двухвходовых элемента «И» и 21 элемент ИЛИ, которые реализуют мажоритарную функцию девяти аргументов [1].

Недостатком данного устройства является невозможность переключения на режимы реализации им мажоритарной функции «4 и более из 7», «3 и более из 5» или «2 из 3», при функционировании адаптивных вычислительных систем.

Задача изобретения - создать устройство, обеспечивающее переключение на режимы реализации им мажоритарной функции «4 и более из 7», «3 и более из 5» или «2 из 3» при функционировании адаптивных вычислительных систем.

Это решение достигается тем, что в адаптивный мажоритарный блок элементов «5 и более из 9», содержащий 22 двухвходовых элемента «И» и 21 элемент ИЛИ, содержит девять иерархических уровней с логическими элементами ИЛИ и двухвходовыми элементами И, каждый из первых четырех уровней состоит из четырех пар элементов ИЛИ и элементов И, при этом каждый из трех первых, вторых, третьих, пятых и седьмых входов устройства соединены с соответствующей парой элементов ИЛИ и элементов И первого уровня, а девятый вход соединен с четвертой парой логических элементов ИЛИ и элементов И второго уровня, выходы каждого из логических элементов первого уровня соединены с парой элементов ИЛИ и элементов И второго уровня, при этом первый элемент ИЛИ первого уровня соединен с первой парой логических элементов ИЛИ и элементов И третьего уровня, выходы каждого из логических элементов второго уровня соединены с парами логических элементов ИЛИ и элементов И третьего уровня, при этом последний элемент И второго уровня соединен с четвертой парой элементов ИЛИ и элементов И четвертого уровня, выходы каждого из логических элементов третьего уровня соединены с парой элементов ИЛИ и элементов И четвертого уровня, при этом выход первого элемента ИЛИ третьего уровня соединен с первым элементом И пятого уровня, к другому входу которого подключен выход первого элемента ИЛИ четвертого уровня, выходы следующей пары элементов И и ИЛИ четвертого уровня подключены ко второму элементу И пятого уровня, при этом выход указанного элемента ИЛИ четвертого уровня также подключен к входу первого элемента И шестого уровня, на другой вход которого подключен выход первого элемента И пятого уровня, выходы следующей пары элементов И и ИЛИ четвертого уровня подключены к первому элементу И пятого уровня, при этом выход указанного элемента И четвертого уровня также подключен к элементу ИЛИ шестого уровня, к другому входу которого подключен выход второго элемента ИЛИ пятого уровня, к выходу следующего элемента И четвертого уровня подключен второй элемент ИЛИ пятого уровня, к другому входу которого подключен выход последнего элемента И четвертого уровня, выход следующего элемента ИЛИ четвертого уровня подключен к элементу И восьмого уровня, к другому входу которого подключен выход элемента И седьмого уровня, выход первого элемента ИЛИ пятого уровня подключен ко второму элементу И шестого уровня и элементу И седьмого уровня, при этом ко второму входу элемента И шестого уровня подключен выход второго элемента И пятого уровня, а ко второму входу элемента И седьмого уровня подключен выход элемента И шестого уровня, выход второго элемента И шестого уровня подключен к элементу ИЛИ седьмого уровня, к другому входу которого подключен выход элемента ИЛИ шестого уровня, к входам элемента ИЛИ девятого уровня подключены выход элемента ИЛИ седьмого уровня и выход элемента И восьмого уровня, при этом выход элемента ИЛИ девятого уровня является выходом мажоритарного элемента, включены четыре триггера 11 - 14, два десятых элементов И 21 и 22, три одиннадцатых элементов И 31, 32 и 33, три десятых элементов ИЛИ 41, 42 и 43, обратный выход второго триггера 12 подсоединен к первому входу первого элемента И 21 десятой группы элементов И, обратный выход третьего триггера 13 подсоединен к второму входу первого элемента И 21 десятой группы элементов И и к первому входу второго элемента И 22 десятой группы элементов И, обратный выход четвертого триггера 14 подсоединен к третьему входу первого элемента И 21 десятой группы элементов И, к второму входу второго элемента И 22 десятой группы элементов И и к второму входу третьего элемента И 33 одиннадцатой группы элементов И, выход первого триггера 11 подсоединен к первым входам элементов И 31 - 33 одиннадцатой группы элементов И, выход первого элемента И 21 десятой группы элементов И подсоединен к второму входу первого элемента И 31 одиннадцатой группы элементов И, выход которого подсоединен к первому входу первого элемента ИЛИ 41 группы десятых элементов ИЛИ, второй вход которого подсоединен в входу 29 устройства, а выход - к соответствующему входу второго элемента И 62 первой группы элементов И, выход второго элемента И 22 десятой группы элементов И подсоединен к второму входу второго элемента И 32 одиннадцатой группы элементов И, выход которого подсоединен к первому входу второго элемента ИЛИ 42 группы десятых элементов ИЛИ, второй вход которого подсоединен в входу 31 устройства, а выход - к соответствующему входу третьего элемента И 63 первой группы элементов И, выход третьего элемента И 33 одиннадцатой группы элементов И подсоединен к первому входу первого третьего элемента ИЛИ 43 группы десятых элементов ИЛИ, второй вход которого подсоединен в входу 33 устройства, а выход - к соответствующему входу четвертого элемента И 64 первой группы элементов И.

Проведенный поиск в известной научно-технической литературе не выявил наличие подобных технических решений.

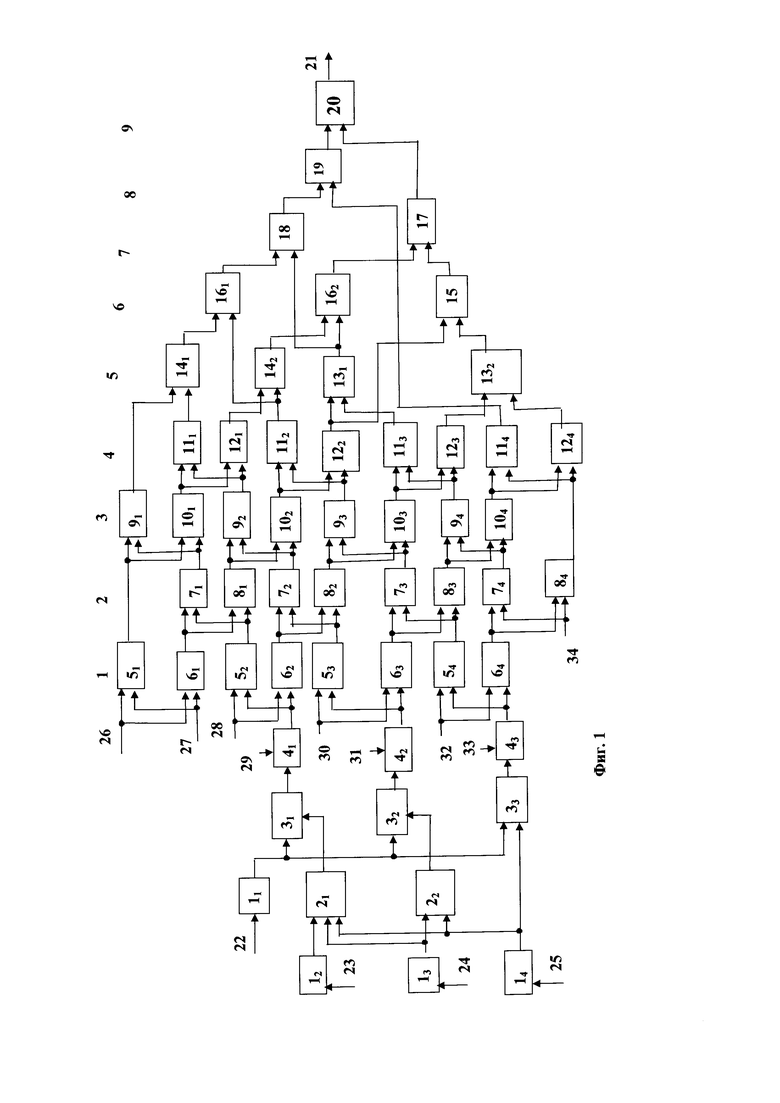

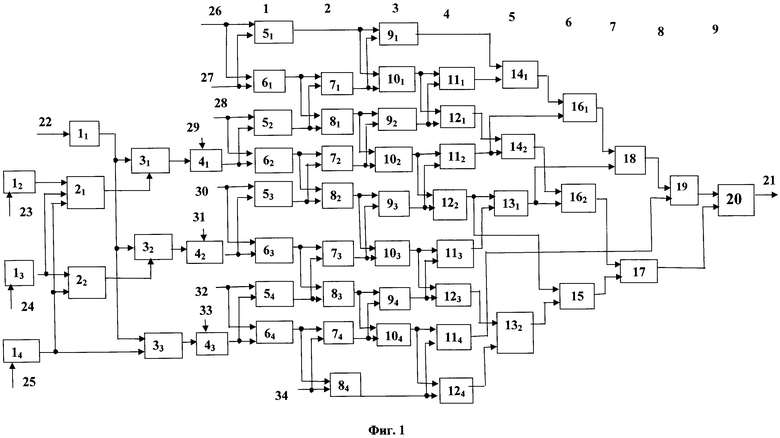

Сущность изобретения поясняется чертежом. На фиг. 1 представлено схематичное изображение адаптивного мажоритарного блока элементов «5 и более из 9».

Устройство содержит: триггеры 11, …, 14, элементы И 21 и 22, элементы И 31, 32 и 33, элементы ИЛИ 41, 42 и 43, элементы ИЛИ первого уровня 51, 52, 53 и 54, элементы И первого уровня 61, 62, 63 и 64, элементы ИЛИ второго уровня 71, 72, 73 и 74, элементы И второго уровня 81, 82, 83 и 84, элементы ИЛИ третьего уровня 91, 92, 93 и 94, элементы И третьего уровня 101, 102, 103 и 104, элементы ИЛИ четвертого уровня 111, 112, 113 и 114, элементы И четвертого уровня 121, 122, 123 и 124, элементы ИЛИ пятого уровня 131, 132, элементы И пятого уровня 141, и 142, элемент ИЛИ шестого уровня 15, элементы И шестого уровня 161 и 162, элемент ИЛИ седьмого уровня 17, элемент И седьмого уровня 18, элементы И восьмого уровня 19, элемент ИЛИ девятого уровня 20, выход 21, входы 22-34.

Мажоритарный блок элементов «5 и более из 9» содержит девять иерархических уровней с логическими элементами ИЛИ и двухвходовыми элементами И, каждый из первых четырех уровней состоит из четырех пар элементов ИЛИ и элементов И.

Принцип работы устройства заключается в том, что на входы 26-34 устройства поступает произвольная последовательность x1, … x9 двоичных символов «1» и «0», а на выходе устройства 21, по принятому критерию большинства «5 из 9», формируется «ответ» - значение тех элементов входной последовательности, число которых превышает число противоположных. Таким образом, если число «1» среди входных значений превышает число «0», то на выходе устройства будет сформировано значение, равное логической «1», что будет правильно, и в обратном случае: при большем числе «0», выходное значение будет соответствовать логическому «0».

В исходном состоянии на вход триггера 11 подается единичный сигнал, с прямого выхода которого единичный сигнал подается на первые входы элементов И31 - И33.

Устройство может работать в следующих режимах:

1). Режим «2 из 3», при этом триггеры 12 - 14 устанавливаются в нулевое состояние, с обратных выходов которых единичные сигналы подаются через открытые элементы И21 - И22 на первые входы элементов И31 - И33, после чего единичные сигналы поступят через элементы И31 - И33 на входы элементов ИЛИ 41 - ИЛИ 43, а на входах 30, 32 и 34 остаются нулевые сигналы. В этом случае выходной сигнал на выходе 21 устройства зависит только от комбинации входных сигналов на трех входах 26-28 устройства.

2). Режим «3 и более из 5», при этом триггер 12 устанавливается в единичное состояние, элемент И31 будет закрыт нулевым сигналом с выхода установленном в нулевое состояние триггера 11. При этом триггеры 13 и 14 устанавливаются в нулевое состояние, с обратных выходов которых единичные сигналы подаются через открытый элемент И 22 на первые входы элементов И 32 - И 33, после чего единичные сигналы поступят через элементы И 32 - И 33 на входы элементов ИЛИ 42 - ИЛИ 43, а на входах 32 и 34 остаются нулевые сигналы. В этом случае выходной сигнал на выходе 21 устройства зависит только от комбинации входных сигналов на трех входах 26-30 устройства.

3). Режим «4 и более из 7», при этом триггер 13 устанавливается в единичное состояние, триггеры 12 и 14 устанавливаются в нулевое состояние, после чего единичный сигнал поступает через элемент И 33 на вход элемента ИЛИ 43, а на входе 34 остается нулевой сигнал. В этом случае выходной сигнал на выходе 21 устройства зависит только от комбинации входных сигналов на входах 26-32 устройства.

4). Режим «5 и более из 9», при этом при этом триггер 14 устанавливается в единичное состояние, триггеры 12 и 13 устанавливаются в нулевое состояние, с обратных выходов которых единичные сигналы подаются на входы элементов И 21 - И 22 на первые входы элементов И 31 - И 32, после чего нулевой сигнал поступит на первый вход элементов ИЛИ 41 - ИЛИ 43. В этом случае выходной сигнал на выходе 21 устройства зависит от комбинации входных сигналов на входах 26-34 устройства.

В качестве примера, поясняющего работу мажоритарного блока «5 и более из 9», (элементы 5-20) рассмотрим поступление на входы устройства 26-34 устройства вектора [101010110], при этом на входах триггеров 11 и 14 присутствует единичный сигнал, а на входах триггеров 12 и 13 присутствует нулевой сигнал, то есть это режим «5 и более из 9».

После этого последовательно на выходах каждого из 9 уровней иерархического построения будут сформированы следующие вектора состояний:

далее на выходах элементов первого уровня 51 - 64 сформируется вектор [10101011];

далее на выходах элементов второго уровня 71 - 84 сформируется вектор [10101010];

далее на выходах элементов третьего уровня 91 - 104 сформируется вектор [11101010];

далее на выходах элементов четвертого уровня 111 - 124 сформируется вектор [1110100 0];

далее на выходах элементов пятого уровня 131 - 142 сформируется вектор [1110];

далее на выходах элементов шестого уровня 15 - 162 сформируется вектор [110];

далее на выходах элементов седьмого уровня 17 - 18 сформируется вектор [11].

Выход элемента 19 восьмого уровня примет логическое значение «0», на выходе элемента 20 девятого уровня - выходе 21 устройства сформируется значение «1».

При других входных значениях устройство работает аналогичным образом.

Литература

1. SU №2665226, 2018.

| название | год | авторы | номер документа |

|---|---|---|---|

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "6 И БОЛЕЕ ИЗ 11" | 2016 |

|

RU2621340C1 |

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ МОТОРОМ | 2019 |

|

RU2729322C1 |

| Система бесперебойного питания | 1990 |

|

SU1807546A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| Многоканальное устройство для синхронизации | 1980 |

|

SU883888A2 |

| Устройство для воспроизведения цифровых сигналов с носителя магнитной записи | 1986 |

|

SU1352527A1 |

| Резервированное устройство с перестра-иВАЕМОй СТРуКТуРОй | 1978 |

|

SU805503A2 |

| ДЕКОДЕР ФАЗОМОДУЛИРОВАННОГО СИГНАЛА | 2010 |

|

RU2453991C1 |

| Мажоритарный элемент | 1988 |

|

SU1538249A1 |

Изобретение относится к вычислительной техники. Технический результат заключается в обеспечении переключения на режимы реализации им мажоритарной функции «4 и более из 7», «3 и более из 5» или «2 из 3» при функционировании адаптивных вычислительных систем. Устройство содержит: триггеры 11, …, 14, элементы И 21 и 22, элементы И 31, 32 и 33, элементы ИЛИ 41, 42 и 43, элементы ИЛИ первого уровня 51, 52, 53 и 54, элементы И первого уровня 61, 62, 63 и 64, элементы ИЛИ второго уровня 71, 72, 73 и 74, элементы И второго уровня 81, 82, 83 и 84, элементы ИЛИ третьего уровня 91, 92, 93 и 94, элементы И третьего уровня 101, 102, 103 и 104, элементы ИЛИ четвертого уровня 111, 112, 113 и 114, элементы И четвертого уровня 121, 122, 123 и 124, элементы ИЛИ пятого уровня 131, 132, элементы И пятого уровня 141 и 142, элемент ИЛИ шестого уровня 15, элементы И шестого уровня 161 и 162, элемент ИЛИ седьмого уровня 17, элемент И седьмого уровня 18, элементы И восьмого уровня 19, элемент ИЛИ девятого уровня 20. 1 ил.

Адаптивный мажоритарный блок элементов «5 и более из 9», содержащий 22 двухвходовых элемента «И» и 21 элемент ИЛИ, содержит девять иерархических уровней с логическими элементами ИЛИ и двухвходовыми элементами И, каждый из первых четырех уровней состоит из четырех пар элементов ИЛИ и элементов И, при этом каждый из трех первых, вторых, третьих, пятых и седьмых входов устройства соединен с соответствующей парой элементов ИЛИ и элементов И первого уровня, а девятый вход соединен с четвертой парой логических элементов ИЛИ и элементов И второго уровня, выходы каждого из логических элементов первого уровня соединены с парой элементов ИЛИ и элементов И второго уровня, при этом первый элемент ИЛИ первого уровня соединен с первой парой логических элементов ИЛИ и элементов И третьего уровня, выходы каждого из логических элементов второго уровня соединены с парами логических элементов ИЛИ и элементов И третьего уровня, при этом последний элемент И второго уровня соединен с четвертой парой элементов ИЛИ и элементов И четвертого уровня, выходы каждого из логических элементов третьего уровня соединены с парой элементов ИЛИ и элементов И четвертого уровня, при этом выход первого элемента ИЛИ третьего уровня соединен с первым элементом И пятого уровня, к другому входу которого подключен выход первого элемента ИЛИ четвертого уровня, выходы следующей пары элементов И и ИЛИ четвертого уровня подключены ко второму элементу И пятого уровня, при этом выход указанного элемента ИЛИ четвертого уровня также подключен к входу первого элемента И шестого уровня, на другой вход которого подключен выход первого элемента И пятого уровня, выходы следующей пары элементов И и ИЛИ четвертого уровня подключены к первому элементу И пятого уровня, при этом выход указанного элемента И четвертого уровня также подключен к элементу ИЛИ шестого уровня, к другому входу которого подключен выход второго элемента ИЛИ пятого уровня, к выходу следующего элемента И четвертого уровня подключен второй элемент ИЛИ пятого уровня, к другому входу которого подключен выход последнего элемента И четвертого уровня, выход следующего элемента ИЛИ четвертого уровня подключен к элементу И восьмого уровня, к другому входу которого подключен выход элемента И седьмого уровня, выход первого элемента ИЛИ пятого уровня подключен ко второму элементу И шестого уровня и элементу И седьмого уровня, при этом ко второму входу элемента И шестого уровня подключен выход второго элемента И пятого уровня, а ко второму входу элемента И седьмого уровня подключен выход элемента И шестого уровня, выход второго элемента И шестого уровня подключен к элементу ИЛИ седьмого уровня, к другому входу которого подключен выход элемента ИЛИ шестого уровня, к входам элемента ИЛИ девятого уровня подключены выход элемента ИЛИ седьмого уровня и выход элемента И восьмого уровня, при этом выход элемента ИЛИ девятого уровня является выходом мажоритарного элемента, отличающийся тем, что в него дополнительно включены четыре триггера 11 - 14, два десятых элемента И 21 и 22, три одиннадцатых элемента И 31, 32 и 33, три десятых элемента ИЛИ 41 42 и 43, обратный выход второго триггера 12 подсоединен к первому входу первого элемента И 21 десятой группы элементов И, обратный выход третьего триггера 13 подсоединен к второму входу первого элемента И 21 десятой группы элементов И и к первому входу второго элемента И 22 десятой группы элементов И, обратный выход четвертого триггера 14 подсоединен к третьему входу первого элемента И 21 десятой группы элементов И, к второму входу второго элемента И 22 десятой группы элементов И и к второму входу третьего элемента И 33 одиннадцатой группы элементов И, выход первого триггера 11 подсоединен к первым входам элементов И 31 - 33 одиннадцатой группы элементов И, выход первого элемента И 21 десятой группы элементов И подсоединен к второму входу первого элемента И 31 одиннадцатой группы элементов И, выход которого подсоединен к первому входу первого элемента ИЛИ 41 группы десятых элементов ИЛИ, второй вход которого подсоединен в входу 29 устройства, а выход - к соответствующему входу второго элемента И 62 первой группы элементов И, выход второго элемента И 22 десятой группы элементов И подсоединен к второму входу второго элемента И 32 одиннадцатой группы элементов И, выход которого подсоединен к первому входу второго элемента ИЛИ 42 группы десятых элементов ИЛИ, второй вход которого подсоединен в входу 31 устройства, а выход - к соответствующему входу третьего элемента И 63 первой группы элементов И, выход третьего элемента И 33 одиннадцатой группы элементов И подсоединен к первому входу третьего элемента ИЛИ 43 группы десятых элементов ИЛИ, второй вход которого подсоединен в входу 33 устройства, а выход - к соответствующему входу четвертого элемента И 64 первой группы элементов И.

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "5 И БОЛЕЕ ИЗ 9" | 2016 |

|

RU2665226C2 |

| МАЖОРИТАРНЫЙ ЭЛЕМЕНТ "6 И БОЛЕЕ ИЗ 11" | 2016 |

|

RU2621340C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2015 |

|

RU2580801C1 |

| ПОДШИПНИК СКОЛЬЖЕНИЯ | 0 |

|

SU164173A1 |

| US 5382950 A, 17.01.1995. | |||

Авторы

Даты

2020-03-05—Публикация

2019-05-21—Подача