УРОВЕНЬ ТЕХНИКИ

Область техники

Изобретение относится к области технологии для жидкокристаллического дисплея, а более конкретно к схеме GOA и жидкокристаллическому дисплею.

Предшествующий уровень техники

Драйвер затвора на матрице, называемый GOA, является технологией, используемой текущим процессом производства жидкокристаллического дисплея на основе тонкопленочных транзисторов для изготовления схемы сканирующего управления сигналом затвора на матричной подложке для достижения управления затвором сканированием по шинам.

Текущая схема GOA состоит из повышающей схемы, схемы управления повышением, передаточной схемы, понижающей схемы, схемы удержания пониженного напряжения и вспомогательной схемы для повышения напряжения. Повышающая схема выводит введенный тактовый сигнал на клемму затвора как сигнал возбуждения для устройства отображения. Схема управления повышением управляет включением повышающей схемы. Управление включением обычно выполняется сигналом, передаваемым от схемы GPA верхнего уровня. Схема понижения понижает напряжение на затворе до уровня низкого напряжения после завершения вывода затвором, то есть окончания сигнала затвора. Схема удержания пониженного напряжения удерживает обычно выходной сигнал затвора и сигнал затвора (обычно называемый точкой Q) повышающей схемы в выключенном состоянии (то есть установлен отрицательный уровень напряжения). Как правило, две понижающие схемы функционируют альтернативно. Повышающая схема снова повышает уровень напряжения точки Q. Это обеспечивает нормальный вывод для G(N) повышающей схемы.

Тем не менее, каждый уровень в таком выполнении имеет схему удержания пониженного напряжения, и имеет две схемы функционирующие альтернативно. Потребляемая мощность высокая, что вредно сказывается на окружающей среде.

СУЩНОСТЬ

Техническая проблема, в основном решаемая настоящим изобретением, заключается в предоставлении схемы GOA и жидкокристаллического дисплея для снижения энергопотребления схемы GOA в жидкокристаллическом дисплее.

Для решения вышеуказанной технической проблемы одно техническое решение, принятое настоящим изобретением, состоит в том, чтобы обеспечить схему GOA, содержащую множество блоков GOA, каждый из которых последовательно заряжает горизонтальные шины сканирования N-ого уровня и горизонтальные шины сканирования (N+1)-ого уровня в области отображения, блок GOA, содержащий схемы управления повышением N-ого уровня, схемы управления повышением (N+1)-ого уровня, повышающие схемы N-ого уровня, повышающие схемы (N+1)-ого уровня, понижающие схемы N-ого уровня, понижающие схемы (N+1)-ого уровня и схему удержания пониженного напряжения; в котором повышающие схемы N-ого уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора N-ого уровня и горизонтальной шине сканирования N-ого уровня, а схемы управления повышением N-ого уровня и схемы понижения N-ого уровня подсоединены к точке сигнала затвора N-ого уровня повышающие схемы (N+1)-ого уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора (N+1)-ого уровня и горизонтальной шине сканирования (N+1)-ого уровня, а схемы управления повышением (N+1)-ого уровня и схемы понижения (N+1)-ого уровня подсоединены к точке сигнала затвора (N+1)-ого уровня; схема удержания пониженного напряжения удерживает уровень напряжения точки сигнала затвора N-ого уровня и горизонтальной шины сканирования N-ого уровня на низком уровне после зарядки горизонтальной шины сканирования N-ого уровня, и удерживает уровень напряжения точки сигнала затвора (N+1)-ого уровня и горизонтальной шины сканирования (N+1)-ого уровня на низком уровня после зарядки горизонтальной шины сканирования N-ого уровня; схема удержания пониженного напряжения содержит: первый транзистор, имеющий затвор и сток, подсоединенные к первому тактовому сигналу; второй транзистор, имеющий затвор, подсоединенный к истоку первого транзистора, сток, подсоединенный к первому тактовому сигналу, и исток, подсоединенный к первой общей точке; третий транзистор, имеющий затвор, подсоединенный ко второму тактовому сигналу, сток, подсоединенный к первому тактовому сигналу, и исток, подсоединенный к первой общей точке; четвертый транзистор, имеющий затвор и сток, подсоединенные к первой общей точке; пятый транзистор, имеющий затвор подсоединенный к точке сигнала затвора N-ого уровня, сток, подсоединенный к истоку первого транзистора и истоку четвертого транзистора, и исток подсоединенный к первому постоянному току низкого напряжения; шестой транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-ого уровня, сток, подсоединенный к истоку первого транзистора и исток, подсоединенный к первому постоянному току низкого напряжения; седьмой транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к точке сигнала затвора (N+1)-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; восьмой транзистор имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к горизонтальной шине сканирования (N+1)-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; девятый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к точке сигнала затвора (N+1)-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; десятый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к горизонтальной шине сканирования (N+1)-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; одиннадцатый транзистор, имеющий затвор и сток, подсоединенные ко второму тактовому сигналу; двенадцатый транзистор, имеющий затвор, подсоединенный к истоку одиннадцатого транзистора, сток, подсоединенный ко второму тактовому сигналу, и исток, подсоединенный ко второй общей точке; тринадцатый транзистор, имеющий затвор, подсоединенный к первому тактовому сигналу, сток, подсоединенный ко второму тактовому сигналу, и исток, подсоединенный ко второй общей точке; четырнадцатый транзистор, имеющий затвор и сток, подсоединенные ко второй общей точке; пятнадцатый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-ого уровня, сток, подсоединенный к истоку одиннадцатого транзистора и истоку четырнадцатого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения; шестнадцатый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-ого уровня, сток, подсоединенный к истоку одиннадцатого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения; семнадцатый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к точке сигнала затвора N-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; восемнадцатый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к горизонтальной шине сканирования N-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; девятнадцатый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к точке сигнала затвора N-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; и двадцатый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к горизонтальной шине сканирования N-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; блок GOA дополнительно содержит схему сброса, подсоединенную к точке сигнала затвора N-ого уровня, точке сигнала затвора (N+1)-ого уровня и первому постоянному току низкого напряжения, для снижения уровня напряжения точки сигнала затвора N-ого уровня и точки сигнала затвора (N+1)-ого уровня к низкому уровню напряжения после сброса полученного сигнала.

Чтобы решить вышеупомянутую техническую проблему, другое техническое решение, принятое в настоящем изобретении, заключается в схеме GOA, содержащей множество блоков GOA, каждый из которых последовательно заряжает горизонтальные шины сканирования N-ого уровня и горизонтальные шины сканирования (N+1)-ого уровня в области отображения, блок GOA, содержащий схемы управления повышением N-ого уровня, схемы управления повышением (N+1)-ого уровня, повышающие схемы N-ого уровня, повышающие схемы (N+1)-ого уровня, понижающие схемы N-ого уровня, понижающие схемы (N+1)-ого уровня и схему удержания пониженного напряжения; в котором повышающие схемы N-ого уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора N-ого уровня и горизонтальной шине сканирования N-ого уровня, а схемы управления повышением N-ого уровня и схемы понижения N-ого уровня подсоединены к точке сигнала затвора N-ого уровня, повышающие схемы (N+1)-ого уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора (N+1)-ого уровня и горизонтальной шине сканирования (N+1)-ого уровня, а схемы управления повышением (N+1)-ого уровня и схемы понижения (N+1)-ого уровня подсоединены к точке сигнала затвора (N+1)-ого уровня; схема удержания пониженного напряжения удерживает уровень напряжения точки сигнала затвора N-ого уровня и горизонтальной шины сканирования N-ого уровня на низком уровне после зарядки горизонтальной шины сканирования N-ого уровня, и удерживает уровень напряжения точки сигнала затвора (N+1)-ого уровня и горизонтальной шины сканирования (N+1)-ого уровня на низком уровня после зарядки горизонтальной шины сканирования N-ого уровня.

В одном варианте осуществления схема удержания пониженного напряжения содержит: первый транзистор, имеющий затвор и сток, подсоединенные к первому тактовому сигналу; второй транзистор, имеющий затвор, подсоединенный к истоку первого транзистора, сток, подсоединенный к первому тактовому сигналу, и исток, подсоединенный к первой общей точке; третий транзистор, имеющий затвор, подсоединенный ко второму тактовому сигналу, сток, подсоединенный к первому тактовому сигналу, и исток, подсоединенный к первой общей точке; четвертый транзистор, имеющий затвор и сток, подсоединенные к первой общей точке; пятый транзистор, имеющий затвор подсоединенный к точке сигнала затвора N-ого уровня, сток, подсоединенный к истоку первого транзистора и истоку четвертого транзистора, и исток подсоединенный к первому постоянному току низкого напряжения; шестой транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-ого уровня, сток, подсоединенный к истоку первого транзистора и исток, подсоединенный к первому постоянному току низкого напряжения; седьмой транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к точке сигнала затвора (N+1)-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; восьмой транзистор имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к горизонтальной шине сканирования (N+1)-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; девятый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к точке сигнала затвора (N+1)-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; десятый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к горизонтальной шине сканирования (N+1)-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; одиннадцатый транзистор, имеющий затвор и сток, подсоединенные ко второму тактовому сигналу; двенадцатый транзистор, имеющий затвор, подсоединенный к истоку одиннадцатого транзистора, сток, подсоединенный ко второму тактовому сигналу, и исток, подсоединенный ко второй общей точке; тринадцатый транзистор, имеющий затвор, подсоединенный к первому тактовому сигналу, сток, подсоединенный ко второму тактовому сигналу, и исток, подсоединенный ко второй общей точке; четырнадцатый транзистор, имеющий затвор и сток, подсоединенные ко второй общей точке; пятнадцатый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-ого уровня, сток, подсоединенный к истоку одиннадцатого транзистора и истоку четырнадцатого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения; шестнадцатый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-ого уровня, сток, подсоединенный к истоку одиннадцатого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения; семнадцатый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к точке сигнала затвора N-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; восемнадцатый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к горизонтальной шине сканирования N-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; девятнадцатый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к точке сигнала затвора N-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; и двадцатый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к горизонтальной шине сканирования N-ого уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; блок GOA дополнительно содержит схему сброса, подсоединенную к точке сигнала затвора N-ого уровня, точке сигнала затвора (N+1)-ого уровня и первому постоянному току низкого напряжения.

В одном варианте осуществления схема удержания пониженного напряжения дополнительно содержит: двадцать второй транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-ого уровня, и сток и исток, подсоединенные к первой общей точке и второй общей точке соответственно.

В одном варианте осуществления блок GOA дополнительно содержит передаточную схему N-ого уровня и передаточную схему (N+1)-ого уровня; передаточная схема N-ого уровня подсоединена к точке сигнала затвора N-ого уровня для обеспечения передаточных сигналов N-ого уровня к схеме управления передачей (N+1)-ого уровня; передаточная схема (N+1)-ого уровня подсоединена к точке сигнала затвора (N+1)-ого уровня для обеспечения передаточных сигналов (N+1)-ого уровня к схеме управления передачей (N+2)-ого уровня следующего уровня блока GOA.

В одном варианте осуществления схема удержания пониженного напряжения дополнительно содержит: двадцать третий транзистор, имеющий затвор, подсоединенный к горизонтальной шине сканирования (N+1)-ого уровня, сток, подсоединенный к первой общей точке, и исток, подсоединенный к первому постоянному току низкого напряжения; и двадцать четвертый транзистор, имеющий затвор, подсоединенный к горизонтальной шине сканирования N-ого уровня, сток, подсоединенный ко второй общей точке, и исток, подсоединенный к первому постоянному току низкого напряжения.

В одном варианте осуществления затвор двадцать третьего транзистора подсоединен к передаточным сигналам (N+1)-ого уровня; затвор двадцать четвертого транзистора подсоединен к передаточным сигналам N-ого уровня.

В одном варианте осуществления исток седьмого транзистора, исток девятого транзистора, исток семнадцатого транзистора и исток девятнадцатого транзистора подсоединены ко второму постоянному току низкого напряжения.

В одном варианте осуществления схема удержания пониженного напряжения дополнительно содержит:

двадцать пятый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к передаточным сигналам (N+1)-ого уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения;

двадцать шестой транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к передаточным сигналам (N+1)-ого уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения;

двадцать седьмой транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к передаточным сигналам N-ого уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения;

и двадцать восьмой транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к передаточным сигналам N-ого уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения.

В одном варианте осуществления блок GOA дополнительно содержит схему сброса, подсоединенную к точке сигнала затвора N-ого уровня, точке сигнала затвора (N+1)-ого уровня и первому постоянному току низкого напряжения, для снижения уровня напряжения точки сигнала затвора N-ого уровня и точке сигнала затвора (N+1)-ого уровня к уровню низкого напряжения после приема сигнала сброса.

Чтобы решить вышеупомянутую техническую проблему, другое техническое решение, принятое настоящим изобретением, представляет собой жидкокристаллический дисплей, содержащий схему GOA, содержащую множество блоков GOA, каждый из которых последовательно заряжает горизонтальные шины сканирования N-ого уровня и горизонтальные шины сканирования (N+1)-ого уровня в области отображения, блок GOA, содержащий схемы управления повышением N-ого уровня, схемы управления повышением (N+1)-ого уровня, повышающие схемы N-ого уровня, повышающие схемы (N+1)-ого уровня, понижающие схемы N-ого уровня, понижающие схемы (N+1)-ого уровня и схему удержания пониженного напряжения; причем повышающие схемы N-ого уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора N-ого уровня и горизонтальной шине сканирования N-ого уровня, а схемы управления повышением N-ого уровня и схемы понижения N-ого уровня подсоединены к точке сигнала затвора N-ого уровня; повышающие схемы (N+1)-ого уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора (N+1)-ого уровня и горизонтальной шине сканирования (N+1)-ого уровня, а схемы управления повышением (N+1)-ого уровня и схемы понижения (N+1)-ого уровня подсоединены к точке сигнала затвора (N+1)-ого уровня; схема удержания пониженного напряжения удерживает уровень напряжения точки сигнала затвора N-ого уровня и горизонтальной шины сканирования N-ого уровня на низком уровне после зарядки горизонтальной шины сканирования N-ого уровня, и удерживает уровень напряжения точки сигнала затвора (N+1)-ого уровня и горизонтальной шины сканирования (N+1)-ого уровня на низком уровня после зарядки горизонтальной шины сканирования N-ого уровня.

Отличие от нынешней технологии, положительный эффект настоящего изобретения заключается в том, что двухуровневые блоки GOA имеют одну и ту же схему удержания пониженного напряжения для соединения двухуровневых смежных блоков GOA. Схема удержания пониженного напряжения удерживает схему GOA первого уровня на уровне низкого напряжения после зарядки схемы GOA первого уровня, и удерживает схему GOA второго уровня на уровне низкого напряжения после зарядки схемы GOA второго уровня. Половина энергопотребления схемы удержания пониженного напряжения в жидкокристаллическом дисплее может быть уменьшена посредством такой конфигурации для дальнейшего снижения энергопотребления.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Вышеупомянутые и другие примерные аспекты, особенности и преимущества определенных иллюстративных вариантов осуществления настоящего изобретения будут более очевидны из последующего описания, взятого вместе с прилагаемыми чертежами, на которых:

Фиг. 1 является структурной схемой, иллюстрирующей соединение каждого блока GOA в первом варианте осуществления схемы GOA по настоящему изобретению;

Фиг. 2 является структурной схемой, иллюстрирующей схему соединения блока GOA в первом варианте осуществления схемы GOA по настоящему изобретению;

Фиг. 3 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA во втором варианте осуществления схемы по настоящему изобретению;

Фиг. 4 является временной диаграммой сигналов для каждого сигнала в определенной схеме блока GOA во втором варианте осуществления схемы по настоящему изобретению;

Фиг. 5 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA в третьем варианте осуществления схемы по настоящему изобретению;

Фиг. 6 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA в четвертом варианте осуществления схемы по настоящему изобретению;

Фиг. 7 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA в пятом варианте осуществления схемы по настоящему изобретению;

Фиг. 8 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA в шестом варианте осуществления схемы по настоящему изобретению;

Фиг. 9 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA в седьмом варианте осуществления схемы по настоящему изобретению;

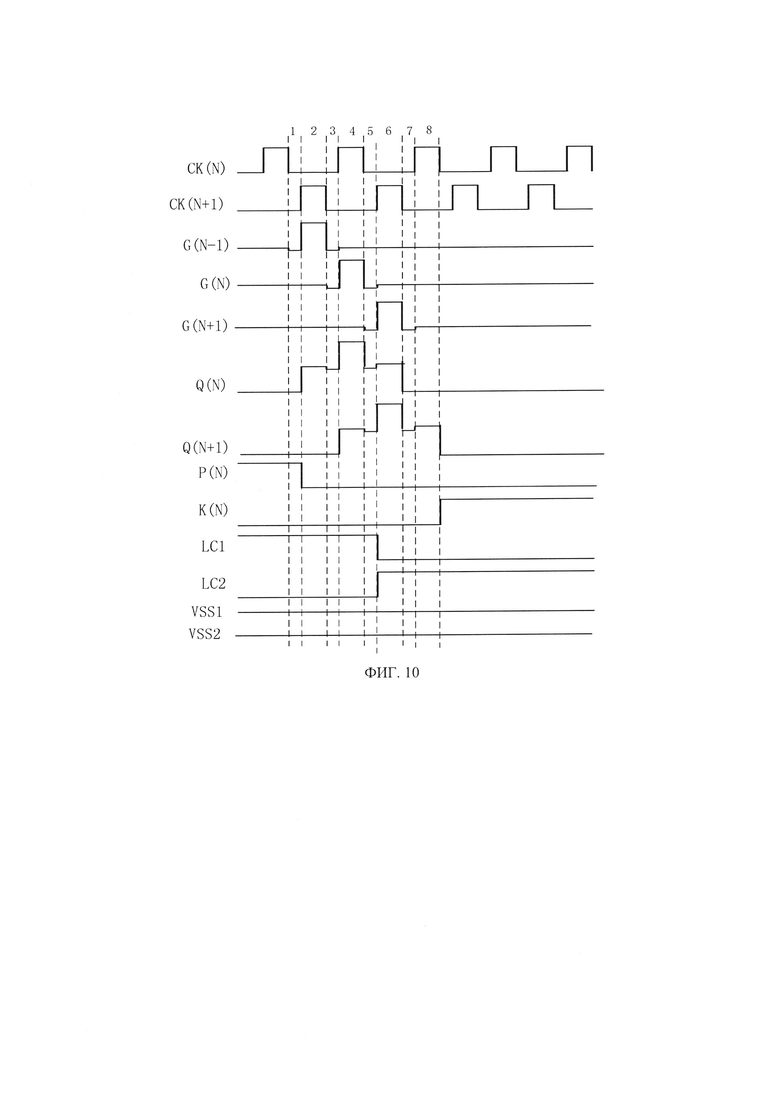

Фиг. 10 является временной диаграммой сигналов для каждого сигнала в определенной схеме блока GOA в седьмом варианте осуществления схемы по настоящему изобретению.

ПОДРОБНОЕ ОПИСАНИЕ

Фиг. 1 является структурной схемой, иллюстрирующей соединение каждого блока GOA в первом варианте осуществления схемы GOA по настоящему изобретению. Схема GOA содержит множество блоков GOA. Каждый блок GOA последовательно заряжает соседние горизонтальные шины сканирования двух уровней в области отображения.

Блок GOA, заряжающий горизонтальную шину сканирования G(N) N-ого уровня и горизонтальную линию сканирования G(N+1) (N+1)-ого уровня, взят в качестве примера ниже. Фиг. 2 является структурной схемой, иллюстрирующей схему соединения блока GOA в первом варианте осуществления схемы GOA по настоящему изобретению. Блок GOA содержит схемы управления повышением N-ого уровня 101, схемы управления повышением (N+1)-ого уровня 102, повышающие схемы N-ого уровня 201, повышающие схемы (N+1)-ого уровня 202, понижающие схемы N-ого уровня 301, понижающие схемы (N+1)-ого уровня 302 и схему удержания пониженного напряжения 400.

Повышающие схемы N-ого уровня 201 и схема удержания пониженного напряжения 400 подсоединены к точке сигнала затвора N-ого уровня Q(N) и горизонтальной шине сканирования N-ого уровня G(N). Схемы управления понижением N-ого уровня 101, и схемы управления повышением N-ого уровня 301 подсоединены к точке сигнала затвора N-ого уровня Q(N).

Повышающие схемы (N+1)-ого уровня 202 и схема удержания пониженного напряжения 400 соответственно подсоединены к точке сигнала затвора (N+1)-ого уровня Q(N+1) и горизонтальной шине сканирования (N+1)-ого уровня G(N+1). Схемы управления повышением (N+1)-ого уровня 102, и схемы управления понижением (N+1)-ого уровня 302 подсоединены к точке сигнала затвора (N+1)-ого уровня Q(N+1).

Схема удержания пониженного напряжения 400 удерживает уровень напряжения точки сигнала затвора N-ого уровня Q(N) и горизонтальной шины сканирования N-ого уровня G(N) на низком уровне после того, как горизонтальная шина сканирования N-ого уровня G(N) зарядится и удерживает уровень напряжения точки сигнала затвора (N+1)-ого уровня Q(N+1) и горизонтальной шины сканирования (N+1)-ого уровня G(N+1) на низком уровне после того, как горизонтальная шина сканирования (N+1)-ого уровня G(N+1) зарядится.

Конкретно, схема управления повышением N-ого уровня 101 повышает уровень напряжения точки сигнала затвора N-ого уровня Q(N) на высокий уровень и управляет повышающей схемой N-ого уровня 201 для включения после приема сигнала G(N-1) блока GOA предшествующего уровня. Схема управления повышением N-ого уровня 101 принимает тактовый сигнал N-ого уровня CK(N), чтобы зарядить горизонтальную шину сканирования N-ого уровня G(N). После завершения зарядки, понижающая схема N-ого уровня 301 понижает уровень напряжения точки сигнала затвора N-ого уровня Q(N) до низкого уровня и отключает повышающую схему N-ого уровня 201. Схема удержания пониженного напряжения 400 понижает уровень напряжения точки сигнала затвора N-ого уровня Q(N) и горизонтальной шины сканирования N-ого уровня G(N) к низкому уровню и удерживает низкий уровень.

Сигнал сканирования G(N), выводимый из горизонтальной шины сканирования N-ого уровня G(N) используется в качестве входного сигнала для схемы управления повышением (N+1)-ого уровня в схеме (N+1)-ого уровня. Принцип работы схемы (N+1)-ого уровня и схемы N-ого уровня аналогичны. Разница заключается лишь в сигнале управления для схемы управления повышением и понижающей схемы. Во время работы двухуровневой схемы, схема удержания пониженного напряжения 400 понижает уровень напряжения двухуровневой схемы до низкого уровня при этом под управлением первого тактового сигнала LC1 и второго тактового сигнала LC2 и удерживает низкий уровень.

Отличия от нынешней технологии, двухуровневые блоки GOA разделяют одну и ту же схему удержания пониженного напряжения соединяя смежные двухуровневые блоки GOA. Схема удержания пониженного напряжения удерживает схему GOA первого уровня на низком уровне напряжения после того, как схема GOA первого уровня зарядится, и удерживает схему GOA второго уровня на низком уровне напряжения после того, как схема GOA второго уровня зарядится. Половина потребляемая мощность схемы удержания пониженного напряжения в жидкокристаллическом дисплее может быть уменьшена посредством такой конфигурации для дальнейшего снижения потребляемой энергии.

Фиг. 3 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA во втором варианте осуществления схемы по настоящему изобретению. Блок GOA содержит схемы управления повышением N-ого уровня 101, схемы управления повышением (N+1)-ого уровня 102, повышающие схемы N-ого уровня 201, повышающие схемы (N+1)-ого уровня 202, понижающие схемы N-ого уровня 301, понижающие схемы (N+1)-ого уровня 302 и схему удержания пониженного напряжения 400. Схема удержания пониженного напряжения 400 содержит первый транзистор Т1, имеющий затвор и сток, подсоединенные к первому тактовому сигналу LC1; второй транзистор Т2, имеющий затвор, подсоединенный к истоку первого транзистора Т1, сток, подсоединенный к первому тактовому сигналу LC1, и исток, подсоединенный к первой общей точке K(N); третий транзистор Т3, имеющий затвор, подсоединенный ко второму тактовому сигналу LC2, сток, подсоединенный к первому тактовому сигналу LC1, и исток, подсоединенный к первой общей точке K(N); четвертый транзистор, имеющий затвор и сток, подсоединенные к первой общей точке K(N); пятый транзистор Т5, имеющий затвор подсоединенный к точке сигнала затвора N-ого уровня Q(N), сток, подсоединенный к истоку первого транзистора Т1 и истоку четвертого транзистора Т4, и исток подсоединенный к первому постоянному току низкого напряжения VSS1; шестой транзистор Т6, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-ого уровня Q(N+1), сток, подсоединенный к истоку первого транзистора Т1 и исток, подсоединенный к первому постоянному току низкого напряжения VSS1; седьмой транзистор Т7, имеющий затвор, подсоединенный к первой общей точке K(N), сток, подсоединенный к точке сигнала затвора (N+1)-ого уровня Q(N+1) и исток, подсоединенный к первому постоянному току низкого напряжения VSS1; восьмой транзистор Т8 имеющий затвор, подсоединенный к первой общей точке K(N), сток, подсоединенный к горизонтальной шине сканирования (N+1)-ого уровня G(N+1) и исток, подсоединенный к первому постоянному току низкого напряжения VSS1; девятый транзистор Т9, имеющий затвор, подсоединенный ко второй общей точке P(N), сток, подсоединенный к точке сигнала затвора (N+1)-ого уровня Q(N+1), и исток, подсоединенный к первому постоянному току низкого напряжения VSS1; одиннадцатый транзистор Т11, имеющий затвор и сток, подсоединенные ко второму тактовому сигналу LC2; двенадцатый транзистор Т12, имеющий затвор, подсоединенный к истоку одиннадцатого транзистора Т11, сток, подсоединенный ко второму тактовому сигналу LC2, и исток, под соединенный ко второй общей точке Р(N); тринадцатый транзистор Т13, имеющий затвор, подсоединенный к первому тактовому сигналу LC1, сток, подсоединенный ко второму тактовому сигналу LC2, и исток, подсоединенный ко второй общей точке Р(N); четырнадцатый транзистор Т14, имеющий затвор и сток, подсоединенные ко второй общей точке P(N); пятнадцатый транзистор Т15, имеющий затвор, подсоединенный к точке сигнала затвора N-ого уровня Q(N), сток, подсоединенный к истоку одиннадцатого транзистора Т11 и истоку четырнадцатого транзистора Т14, и исток, подсоединенный к первому постоянному току низкого напряжения VSS1; семнадцатый транзистор Т17, имеющий затвор, подсоединенный ко второй общей точке P(N), сток, подсоединенный к точке сигнала затвора N-ого уровня Q(N), и исток, подсоединенный к первому постоянному току низкого напряжения VSS1; восемнадцатый транзистор Т18, имеющий затвор, подсоединенный ко второй общей точке P(N), сток, подсоединенный к горизонтальной шине сканирования N-ого уровня G(N), и исток, подсоединенный к первому постоянному току низкого напряжения VSS1; девятнадцатый транзистор Т19, имеющий затвор, подсоединенный к первой общей точке K(N), сток, подсоединенный к точке сигнала затвора N-ого уровня Q(N), и исток, подсоединенный к первому постоянному току низкого напряжения VSS1; и двадцатый транзистор Т20, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к горизонтальной шине сканирования N-ого уровня G(N), и исток, подсоединенный к первому постоянному току низкого напряжения VSS1.

Фиг. 4 является временной диаграммой сигналов для каждого сигнала в определенной схеме блока GOA во втором варианте осуществления схемы по настоящему изобретению. Временная диаграмма сигналов разделена на семь секций пунктирными линиями на фиг.4.

В секции I, G(N-1) находится на уровне низкого напряжения, схема управления повышением N-ого уровня 101 отключена, точка Q(N) находится на уровне низкого напряжения, и схема повышения N-ого уровня 201 отключена. Благодаря функционированию LC1 и LC2, точка P(N) находится на уровне высокого напряжения, Т12 проводящий, и G(N) находится на уровне низкого напряжения. Схема управления повышением (N+1)-ого уровня 102 отключена. Точка Q(N+1) находится на уровне низкого напряжения. Схема повышения (N+1)-ого уровня 202 отключена. Благодаря функционированию LC1 и LC2, точка P(N) находится на высоком уровне напряжения, Т10 проводящий, и выход G(N+1) находится на уровне низкого напряжения.

В секции II, G(N-1) находится на уровне высокого напряжения, а схема управления повышением N-ого уровня 101 включена. Точка Q(N) находится на уровне высокого напряжения и схема повышения N-ого уровня 201 включена. Поскольку CK(N) все еще находится на уровне низкого напряжения, выход G(N) все еще находится на уровне низкого напряжения. Кроме того, поскольку Q(N) находится на уровне высокого напряжения так, что Т21, Т5 и Т15 включены, то есть P(N) и K(N) одновременно находятся на уровне низкого напряжения, G(N+1) продолжает находиться на уровне низкого напряжения.

В секции III, G(N-1) находится на уровне низкого напряжения, а схема управления повышением N-ого уровня 101 отключена. Уровень напряжения точки Q(N) немного уменьшается. Остальные ключевые точки практически не изменились.

В секции IV, функционирование первого конденсатора Сb1 в схеме повышения N-ого уровня 201 повышает напряжение точки Q(N) до более высокого уровня. Схема повышения N-ого уровня 201 все еще включена. В это время тактовый сигнал N-ого уровня CK(N) становится уровнем высокого напряжения, и G(N) заряжается.

Поскольку уровень G(N) становится высоким, схема управления повышением (N+1)-ого уровня 102 включена, и Q(N+1) становится уровнем высокого напряжения. Схема повышения (N+1)-ого уровня 202 включена. Но в это время, тактовый сигнал (N+1)-ого уровня становится низким, и G(N+1) все еще находится на низком уровне.

В секции V тактовый сигнал N-ого уровня CK(N) становится уровнем низкого напряжения, и зарядка G(N) завершена так, что схема управления повышением (N+1)-ого уровня 102 отключена. Остальные ключевые точки практически не изменились.

В секции VI, функционирование второго конденсатора Сb2 в в схеме повышения (NH-l)-ого уровня 202 повышает напряжение точки Q(N+1) до более высокого уровня. Схема повышения (N+1)-ого уровня 202 все еще включена. В это время тактовый сигнал (N+1)-ого уровня CK(N+1) становится уровнем высокого напряжения, и G(N+1) заряжается.

Поскольку уровень G(N+1) высокий, первая схема понижения 301 включена и понижает напряжение Q(N). Т21, Т5 и Т15 отключены. Поскольку функционирование Q(N+1), и изменение Lc1 и LC2, P(N) и K(N) все еще низки.

В секции VII тактовый сигнал (N+1)-ого уровня CK(N+1) становится уровнем низкого напряжения, и зарядка G(N+1) завершена. Другие ключевые точки по существу, остаются неизменными.

Фиг. 5 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA в третьем варианте осуществления схемы по настоящему изобретению. Разница между блоком GOA и вторым вариантом осуществления, упомянутым выше, описана ниже.

Схема удержания пониженного напряжения 400 дополнительно содержит: двадцать второй транзистор Т22, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-ого уровня Q(N+1), и сток и исток, подсоединенные к первой общей точке K(N) и второй общей точке P(N) соответственно.

Поскольку схема удержания пониженного напряжения 400 должна понижать и удерживать двухступенчатые схемы некоторое время, Т22 и Т21 принимаются для работы обычно для обеспечения нормального выхода двухуровневых схем. Схема более безопасна, и более стабильна.

Фиг. 6 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA в четвертом варианте осуществления схемы по настоящему изобретению. Разница между блоком GOA и третьим вариантом осуществления, упомянутым выше, описана ниже.

Блок GOA дополнительно содержит передаточная схема N-ого уровня 501 и передаточная схема (N+1)-ого уровня 502. Передаточная схема N-ого уровня 501 подсоединена к точке сигнала затвора N-ого уровня Q(N) для обеспечения передаточных сигналов N-ого уровня ST(N) к схеме управления передачей (N+1)-ого уровня. Передаточная схема (N+1)-ого уровня 502 подсоединяется к точке сигнала затвора (N+1)-ого уровня Q(N+1) для обеспечения передаточных сигналов (N+1)-ого уровня ST(N+1) к схеме управления передачей (N+2)-ого уровня следующего уровня блока GOA.

В варианте осуществления управляющие сигналы для схемы управления повышением N-ого уровня 101 и схемы управления повышением (N+1)-ого уровня 102 заменены как ST(N-l) и ST(N) соответственно, то есть затворы TFT транзисторов в схеме управления повышением N-ого уровня 101 и схеме управления повышением (N+1)-ого уровня 102 подсоединены к ST(N-1) и ST(N) соответственно.

Фиг. 7 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA в пятом варианте осуществления схемы по настоящему изобретению. Разница между блоком GOA и четвертым вариантом осуществления, упомянутым выше, описана ниже.

Схема удержания пониженного напряжения дополнительно содержит: двадцать третий транзистор Т23, имеющий затвор, подсоединенный к горизонтальной шине сканирования (N+1)-ого уровня G(N+1), сток, подсоединенный к первой общей точке K(N), и исток, подсоединенный к первому постоянному току низкого напряжения VSS1; и двадцать четвертый транзистор Т24, имеющий затвор, подсоединенный к горизонтальной шине сканирования N-ого уровня G(N), сток, подсоединенный ко второй общей точке P(N), и исток, подсоединенный к первому постоянному току низкого напряжения VSS1.

Поскольку понижение во время выходного периода, этот вариант осуществления принимает два дополнительных TFT-транзистора для усиления понижения для P(N) и K(N) во время период работы. Если эффект понижения не достаточный, дисплей будет отклоняющимся от нормы.

Кроме того, сигнал затвора понижающих схем N-ого уровня может быть изменен как ST(N+1), а сигнал затвора понижающих схем (N+1)-ого уровня может быть изменен как ST(N+2), сигнал затвора Т23 может быть изменен как ST(N+1), а сигнал затвора Т24 может быть изменен как ST (N) для предохранения транзисторов от утечки электричества.

Фиг. 8 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA в шестом варианте осуществления схемы по настоящему изобретению. Разница между блоком GOA и пятым вариантом осуществления, упомянутым выше, описана ниже.

Исток седьмого транзистора Т7, исток девятого транзистора Т9, исток семнадцатого транзистора Т17 и исток девятнадцатого транзистора Т19 подсоединены ко второму постоянному току низкого напряжения VSS2.

Фиг. 9 является структурной схемой, иллюстрирующей конкретную схему соединения блока GOA в седьмом варианте осуществления схемы по настоящему изобретению. Разница между блоком GOA и пятым вариантом осуществления, упомянутым выше, в том, что схема удержания понижения дополнительно содержит:

двадцать пятый транзистор Т25, имеющий затвор, подсоединенный к первой общей точке K(N), сток, подсоединенный к передаточным сигналам (N+1)-ого уровня ST(N+1), и исток, подсоединенный ко второму постоянному току низкого напряжения VSS2;

двадцать шестой транзистор Т26, имеющий затвор, подсоединенный ко второй общей точке P(N), сток, подсоединенный к передаточным сигналам (N+1)-ого уровня ST(N+1), и исток, подсоединенный ко второму постоянному току низкого напряжения VSS2;

двадцать седьмой транзистор Т27, имеющий затвор, подсоединенный ко второй общей точке P(N), сток, подсоединенный к передаточным сигналам N-ого уровня ST(N), и исток, подсоединенный ко второму постоянному току низкого напряжения VSS2; а также

двадцать восьмой транзистор. Т28, имеющий затвор, подсоединенный к первой общей точке K(N), сток, подсоединенный к передаточным сигналам N-ого уровня ST(N), и исток, подсоединенный ко второму постоянному току низкого напряжения VSS2.

Кроме того, сигнал затвора сигнала N-ого уровня может быть изменен как ST(N+2), а сигнал затвора схемы понижения (N+1)-ого уровня может быть изменен как ST(N+3) для содействия точке Q(N) в формировании лучшей  -образной формы.

-образной формы.

Фиг. 10 является временной диаграммой сигналов для каждого сигнала в определенной схеме блока GOA в седьмом варианте осуществления схемы по настоящему изобретению. Временная диаграмма сигналов аналогична фиг.4. Разница заключается в том, что  - образные формы Q(N) и Q(N+1) являются более полными.

- образные формы Q(N) и Q(N+1) являются более полными.

Вышеприведенные варианты осуществления принимают NTFT в качестве примеров. Они могут быть заменены как PTFT во время практической реализации. Высокий и низкий уровень напряжения для управления затвором переключаются. Время изменения уровня напряжения не изменяется.

Хотя настоящее изобретение проиллюстрировано и описано со ссылкой на конкретные варианты осуществления, специалист в данной области техники поймет, что многие варианты и модификации легко достижимы, без отступления от сущности и объема, определенных прилагаемой формулой изобретения и их юридическими эквивалентами.

Изобретение относится к области жидкокристаллических устройств отображения. Технический результат заключается в снижении энергопотребления жидкокристаллических устройств отображения. Технический результат достигается за счет повышающих схем N-го уровня и схемы удержания пониженного напряжения, соответственно подсоединенных к точке сигнала затвора N-го уровня и горизонтальной шине сканирования N-го уровня, при этом схемы управления повышением N-го уровня и схемы понижения N-го уровня подсоединены к точке сигнала затвора N-го уровня; повышающих схем (N+1)-го уровня и схемы удержания пониженного напряжения, соответственно подсоединенных к точке сигнала затвора (N+1)-го уровня и горизонтальной шине сканирования (N+1)-го уровня; схемы удержания пониженного напряжения, которая удерживает уровень напряжения точки сигнала затвора N-ого уровня и горизонтальной шины сканирования N-го уровня на низком уровне после зарядки горизонтальной шины сканирования N-го уровня, и удерживает уровень напряжения точки сигнала затвора (N+1)-го уровня и горизонтальной шины сканирования (N+1)-го уровня на низком уровне после зарядки горизонтальной шины сканирования N-го уровня. 3 н. и 15 з.п. ф-лы, 10 ил.

1. Схема GOA для жидкокристаллического дисплея, содержащая множество блоков GOA, каждый из которых последовательно заряжает горизонтальные шины сканирования N-го уровня и горизонтальные шины сканирования (N+1)-го уровня в области отображения, блок GOA, содержащий схемы управления повышением N-ого уровня, схемы управления повышением (N+1)-го уровня, повышающие схемы N-ого уровня, повышающие схемы (N+1)-го уровня, понижающие схемы N-го уровня, понижающие схемы (N+1)-го уровня и схему удержания пониженного напряжения;

повышающие схемы N-го уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора N-го уровня и горизонтальной шине сканирования N-го уровня, а схемы управления повышением N-го уровня и схемы понижения N-го уровня подсоединены к точке сигнала затвора N-го уровня;

повышающие схемы (N+1)-го уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора (N+1)-го уровня и горизонтальной шине сканирования (N+1)-го уровня, а схемы управления повышением (N+1)-го уровня и схемы понижения (N+1)-го уровня подсоединены к точке сигнала затвора (N+1)-го уровня;

схема удержания пониженного напряжения удерживает уровень напряжения точки сигнала затвора N-го уровня и горизонтальной шины сканирования N-го уровня на низком уровне после зарядки горизонтальной шины сканирования N-го уровня, и удерживает уровень напряжения точки сигнала затвора (N+1)-го уровня и горизонтальной шины сканирования (N+1)- го уровня на низком уровне после зарядки горизонтальной шины сканирования N-го уровня;

схема удержания пониженного напряжения содержит:

первый транзистор, имеющий затвор и сток, подсоединенные к первому тактовому сигналу;

второй транзистор, имеющий затвор, подсоединенный к истоку первого транзистора, сток, подсоединенный к первому тактовому сигналу, и исток, подсоединенный к первой общей точке;

третий транзистор, имеющий затвор, подсоединенный ко второму тактовому сигналу, сток, подсоединенный к первому тактовому сигналу, и исток, подсоединенный к первой общей точке;

четвертый транзистор, имеющий затвор и сток, подсоединенные к первой общей точке;

пятый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня, сток, подсоединенный к истоку первого транзистора и истоку четвертого транзистора, и исток подсоединенный к первому постоянному току низкого напряжения;

шестой транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-го уровня, сток, подсоединенный к истоку первого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения;

седьмой транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к точке сигнала затвора (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

восьмой транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к горизонтальной шине сканирования (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

девятый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к точке сигнала затвора (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

десятый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к горизонтальной шине сканирования (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

одиннадцатый транзистор, имеющий затвор и сток, подсоединенные ко второму тактовому сигналу;

двенадцатый транзистор, имеющий затвор, подсоединенный к истоку одиннадцатого транзистора, сток, подсоединенный ко второму тактовому сигналу, и исток, подсоединенный ко второй общей точке;

тринадцатый транзистор, имеющий затвор, подсоединенный к первому тактовому сигналу, сток, подсоединенный ко второму тактовому сигналу, и исток, подсоединенный ко второй общей точке;

четырнадцатый транзистор, имеющий затвор и сток, подсоединенные ко второй общей точке;

пятнадцатый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня, сток, подсоединенный к истоку одиннадцатого транзистора и истоку четырнадцатого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения;

шестнадцатый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-го уровня, сток, подсоединенный к истоку одиннадцатого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения;

семнадцатый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к точке сигнала затвора N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

восемнадцатый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к горизонтальной шине сканирования N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

девятнадцатый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к точке сигнала затвора N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; и

двадцатый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к горизонтальной шине сканирования N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

блок GOA дополнительно содержит схему сброса, подсоединенную к точке сигнала затвора N-го уровня, точке сигнала затвора (N+1)-го уровня и первому постоянному току низкого напряжения, для снижения уровня напряжения точки сигнала затвора N-го уровня и точки сигнала затвора (N+1)-го уровня к низкому уровню напряжения после сброса полученного сигнала.

2. Схема GOA по п. 1, в которой схема удержания пониженного напряжения дополнительно содержит:

двадцать второй транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-го уровня, и сток и исток, подсоединенные к первой общей точке и второй общей точке соответственно.

3. Схема GOA по п. 1, в которой блок GOA содержит передаточную схему N-го уровня и передаточную схему (N+1)-го уровня;

передаточная схема N-го уровня подсоединена к точке сигнала затвора N-го уровня для обеспечения передаточных сигналов N-го уровня к схеме управления передачей (N+1)-го уровня;

передаточная схема (N+1)-го уровня подсоединена к точке сигнала затвора (N+1)-го уровня для обеспечения передаточных сигналов (N+1)-го уровня к схеме управления передачей (N+2)-го уровня следующего уровня блока GOA.

4. Схема GOA по п. 1, в которой схема удержания пониженного напряжения дополнительно содержит:

двадцать третий транзистор, имеющий затвор, подсоединенный к горизонтальной шине сканирования (N+1)-го уровня, сток, подсоединенный к первой общей точке, и исток, подсоединенный к первому постоянному току низкого напряжения; и

двадцать четвертый транзистор, имеющий затвор, подсоединенный к горизонтальной шине сканирования N-го уровня, сток, подсоединенный ко второй общей точке, и исток, подсоединенный к первому постоянному току низкого напряжения.

5. Схема GOA по п. 4, в которой затвор двадцать третьего транзистора подсоединен к передаточным сигналам (N+1)-го уровня; затвор двадцать четвертого транзистора подсоединен к передаточным сигналам N-го уровня.

6. Схема GOA по п. 5, в которой исток седьмого транзистора, исток девятого транзистора, исток семнадцатого транзистора и исток девятнадцатого транзистора подсоединены ко второму постоянному току низкого напряжения.

7. Схема GOA по п. 6, в которой схема удержания пониженного напряжения дополнительно содержит:

двадцать пятый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к передаточным сигналам (N+1)-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения;

двадцать шестой транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к передаточным сигналам (N+1)-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения;

двадцать седьмой транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к передаточным сигналам N-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения; и

двадцать восьмой транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к передаточным сигналам N-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения.

8. Схема GOA для жидкокристаллического дисплея, содержащая множество блоков GOA, каждый из которых последовательно заряжает горизонтальные шины сканирования N-го уровня и горизонтальные шины сканирования (N+1)-го уровня в области отображения, блок GOA, содержащий схемы управления повышением N-го уровня, схемы управления повышением (N+1)-го уровня, повышающие схемы N-го уровня, повышающие схемы (N+1)-го уровня, понижающие схемы N-го уровня, понижающие схемы (N+1)-го уровня и схему удержания пониженного напряжения;

повышающие схемы N-го уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора N-го уровня и горизонтальной шине сканирования N-го уровня, а схемы управления повышением N-го уровня и схемы понижения N-го уровня подсоединены к точке сигнала затвора N-го уровня;

повышающие схемы (N+1)-го уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора (N+1)-го уровня и горизонтальной шине сканирования (N+1)-го уровня, а схемы управления повышением (N+1)-го уровня и схемы понижения (N+1)-го уровня подсоединены к точке сигнала затвора (N+1)-го уровня;

схема удержания пониженного напряжения удерживает уровень напряжения точки сигнала затвора N-го уровня и горизонтальной шины сканирования N-го уровня на низком уровне после зарядки горизонтальной шины сканирования N-го уровня и удерживает уровень напряжения точки сигнала затвора (N+1)-го уровня и горизонтальной шины сканирования (N+1)- го уровня на низком уровне после зарядки горизонтальной шины сканирования N-го уровня.

9. Схема GOA по п. 8, в которой схема удержания пониженного напряжения содержит:

первый транзистор, имеющий затвор и сток, подсоединенные к первому тактовому сигналу;

второй транзистор, имеющий затвор, подсоединенный к истоку первого транзистора, сток, подсоединенный к первому тактовому сигналу, и исток, подсоединенный к первой общей точке;

третий транзистор, имеющий затвор, подсоединенный ко второму тактовому сигналу, сток, подсоединенный к первому тактовому сигналу, и исток, подсоединенный к первой общей точке;

четвертый транзистор, имеющий затвор и сток, подсоединенные к первой общей точке;

пятый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня, сток, подсоединенный к истоку первого транзистора и истоку четвертого транзистора, и исток подсоединенный к первому постоянному току низкого напряжения;

шестой транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-го уровня, сток, подсоединенный к истоку первого транзистора и исток, подсоединенный к первому постоянному току низкого напряжения;

седьмой транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к точке сигнала затвора (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

восьмой транзистор имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к горизонтальной шине сканирования (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

девятый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к точке сигнала затвора (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

десятый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к горизонтальной шине сканирования (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

одиннадцатый транзистор, имеющий затвор и сток, подсоединенные ко второму тактовому сигналу;

двенадцатый транзистор, имеющий затвор, подсоединенный к истоку одиннадцатого транзистора, сток, подсоединенный ко второму тактовому сигналу, и исток, подсоединенный ко второй общей точке;

тринадцатый транзистор, имеющий затвор, подсоединенный к первому тактовому сигналу, сток, подсоединенный ко второму тактовому сигналу, и исток, подсоединенный ко второй общей точке;

четырнадцатый транзистор, имеющий затвор и сток, подсоединенные ко второй общей точке;

пятнадцатый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня, сток, подсоединенный к истоку одиннадцатого транзистора и истоку четырнадцатого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения;

шестнадцатый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-го уровня, сток, подсоединенный к истоку одиннадцатого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения;

семнадцатый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к точке сигнала затвора N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

восемнадцатый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к горизонтальной шине сканирования N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

девятнадцатый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к точке сигнала затвора N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; и

двадцатый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к горизонтальной шине сканирования N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения.

10. Схема GOA по п. 9, в которой схема удержания пониженного напряжения дополнительно содержит:

двадцать второй транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-го уровня, и сток и исток, подсоединенные к первой общей точке и второй общей точке соответственно.

11. Схема GOA по п. 10, в которой блок GOA дополнительно содержит передаточную схему N-го уровня и передаточную схему (N+1)-го уровня;

передаточная схема N-го уровня подсоединена к точке сигнала затвора N-го уровня для обеспечения передаточных сигналов N-го уровня к схеме управления передачей (N+1)-го уровня;

передаточная схема (N+1)-го уровня подсоединена к точке сигнала затвора (N+1)-го уровня для обеспечения передаточных сигналов (N+1)-го уровня к схеме управления передачей (N+2)-го уровня следующего уровня блока GOA.

12. Схема GOA по п. 11, в которой схема удержания пониженного напряжения дополнительно содержит:

двадцать третий транзистор, имеющий затвор, подсоединенный к горизонтальной шине сканирования (N+1)-го уровня, сток, подсоединенный к первой общей точке, и исток, подсоединенный к первому постоянному току низкого напряжения; и

двадцать четвертый транзистор, имеющий затвор, подсоединенный к горизонтальной шине сканирования N-го уровня, сток, подсоединенный ко второй общей точке, и исток, подсоединенный к первому постоянному току низкого напряжения.

13. Схема GOA по п. 12, в которой затвор двадцать третьего транзистора подсоединен к передаточным сигналам (N+1)-го уровня; затвор двадцать четвертого транзистора подсоединен к передаточным сигналам N-го уровня.

14. Схема GOA по п. 13, в которой исток седьмого транзистора, исток девятого транзистора, исток семнадцатого транзистора и исток девятнадцатого транзистора подсоединены ко второму постоянному току низкого напряжения.

15. Схема GOA по п. 14, в которой схема удержания пониженного напряжения дополнительно содержит:

двадцать пятый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к передаточным сигналам (N+1)-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения;

двадцать шестой транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к передаточным сигналам (N+1)-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения;

двадцать седьмой транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к передаточным сигналам N-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения; и

двадцать восьмой транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к передаточным сигналам N-го уровня, и исток, подсоединенный ко второму постоянному току низкого напряжения.

16. Схема GOA по п. 8, в которой блок GOA дополнительно содержит схему сброса, подсоединенную к точке сигнала затвора N-го уровня, точке сигнала затвора (N+1)-го уровня и первому постоянному току низкого напряжения, для снижения уровня напряжения точки сигнала затвора N-го уровня и точки сигнала затвора (N+1)-го уровня к низкому уровню напряжения после сброса полученного сигнала.

17. Жидкокристаллический дисплей, содержащий схему GOA, содержащую множество блоков GOA, каждый из которых последовательно заряжает горизонтальные шины сканирования N-го уровня и горизонтальные шины сканирования (N+1)-го уровня в области отображения, блок GOA, содержащий схемы управления повышением N-го уровня, схемы управления повышением (N+1)-го уровня, повышающие схемы N-го уровня, повышающие схемы (N+1)-го уровня, понижающие схемы N-го уровня, понижающие схемы (N+1)-го уровня и схему удержания пониженного напряжения;

повышающие схемы N-го уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора N-го уровня и горизонтальной шине сканирования N-го уровня, а схемы управления повышением N-го уровня и схемы понижения N-го уровня подсоединены к точке сигнала затвора N-го уровня;

повышающие схемы (N+1)-го уровня и схема удержания пониженного напряжения соответственно подсоединены к точке сигнала затвора (N+1)-го уровня и горизонтальной шине сканирования (N+1)-го уровня, а схемы управления повышением (N+1)-го уровня и схемы понижения (N+1)-го уровня подсоединены к точке сигнала затвора (N+1)-го уровня;

схема удержания пониженного напряжения удерживает уровень напряжения точки сигнала затвора N-го уровня и горизонтальной шины сканирования N-го уровня на низком уровне после зарядки горизонтальной шины сканирования N-го уровня и удерживает уровень напряжения точки сигнала затвора (N+1)-го уровня и горизонтальной шины сканирования (N+1)-го уровня на низком уровне после зарядки горизонтальной шины сканирования N-го уровня.

18. Жидкокристаллический дисплей по п. 17, в котором схема удержания пониженного напряжения содержит:

первый транзистор, имеющий затвор и сток, подсоединенные к первому тактовому сигналу;

второй транзистор, имеющий затвор, подсоединенный к истоку первого транзистора, сток, подсоединенный к первому тактовому сигналу, и исток, подсоединенный к первой общей точке;

третий транзистор, имеющий затвор, подсоединенный ко второму тактовому сигналу, сток, подсоединенный к первому тактовому сигналу, и исток, подсоединенный к первой общей точке;

четвертый транзистор, имеющий затвор и сток, подсоединенные к первой общей точке;

пятый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-го уровня, сток, подсоединенный к истоку первого транзистора и истоку четвертого транзистора, и исток подсоединенный к первому постоянному току низкого напряжения;

шестой транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-го уровня, сток, подсоединенный к истоку первого транзистора и исток, подсоединенный к первому постоянному току низкого напряжения;

седьмой транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к точке сигнала затвора (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

восьмой транзистор имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к горизонтальной шине сканирования (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

девятый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к точке сигнала затвора (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

десятый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к горизонтальной шине сканирования (N+1)-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

одиннадцатый транзистор, имеющий затвор и сток, подсоединенные ко второму тактовому сигналу;

двенадцатый транзистор, имеющий затвор, подсоединенный к истоку одиннадцатого транзистора, сток, подсоединенный ко второму тактовому сигналу, и исток, подсоединенный ко второй общей точке;

тринадцатый транзистор, имеющий затвор, подсоединенный к первому тактовому сигналу, сток, подсоединенный ко второму тактовому сигналу, и исток, подсоединенный ко второй общей точке;

четырнадцатый транзистор, имеющий затвор и сток, подсоединенные ко второй общей точке;

пятнадцатый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора N-ого уровня, сток, подсоединенный к истоку одиннадцатого транзистора и истоку четырнадцатого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения;

шестнадцатый транзистор, имеющий затвор, подсоединенный к точке сигнала затвора (N+1)-го уровня, сток, подсоединенный к истоку одиннадцатого транзистора, и исток, подсоединенный к первому постоянному току низкого напряжения;

семнадцатый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к точке сигнала затвора N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

восемнадцатый транзистор, имеющий затвор, подсоединенный ко второй общей точке, сток, подсоединенный к горизонтальной шине сканирования N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения;

девятнадцатый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к точке сигнала затвора N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения; и

двадцатый транзистор, имеющий затвор, подсоединенный к первой общей точке, сток, подсоединенный к горизонтальной шине сканирования N-го уровня, и исток, подсоединенный к первому постоянному току низкого напряжения.

| ПИКСЕЛЬНАЯ СХЕМА И УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2010 |

|

RU2510535C2 |

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

Авторы

Даты

2018-10-11—Публикация

2015-04-30—Подача