Область техники

[0001] Изобретение относится к области технологии жидкокристаллических дисплеев, и, в частности, к схеме возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора и к схеме логической операции И-НЕ такой схемы.

Описание предшествующего уровня техники

[0002] Для большой интегральной схемы основными тремя устройствами схемы логической операции являются логическая схема НЕ, логическая схема И-НЕ и логическая схема ИЛИ-НЕ и, как правило, три устройства формируются полевыми транзисторами CMOS (комплементарные металло-оксидные полупроводники), то есть схема имеет два типа устройств PMOS (p-канальные металло-оксидные полупроводники) и NMOS (n-канальные металло-оксидные полупроводники).

[0003] В оксидных полупроводниковых устройствах IGZO (оксид индия, галлия и цинка) стал центром внимания для устройства отображения следующего поколения, а оксидный полупроводник имеет хорошие характеристики NTFT благодаря своей особой структуре материала. Однако, тонкопленочные транзисторы (TFT) также содержат два типа устройств, то есть NTFT и PTFT, и, как правило, только LTPS-процесс может получить устройство PTFT с хорошими функциональными характеристиками. Поэтому, как использовать один тип устройства (PTFT или NTFT) для изготовления логической схемы НЕ, И-НЕ или ИЛИ-НЕ стало проблемой, которую необходимо срочно решить.

КРАТКОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

[0004] Технической проблемой, которая, в основном, должна быть решена изобретением, является создание схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора и схемы логической операции И-НЕ такой схемы, которая может использовать один тип устройства (PTFT или NTFT) для изготовления схемы И-НЕ.

[0005] Чтобы решить вышеупомянутую техническую проблему, техническим решением, предлагаемым изобретением, является создание схемы логической операции И-НЕ. Схема содержит: первый инвертор и второй инвертор, применяемые к схеме удержания пониженного напряжения схемы GOA; и девятый транзистор, причем затвор девятого транзистора электрически соединен с выходом первого инвертора, сток девятого транзистора электрически соединен с постоянным высоким потенциалом, а исток девятого транзистора электрически соединен с выходом схемы логической операции; десятый транзистор, причем затвор десятого транзистора электрически соединен с выходом второго инвертора, сток десятого транзистора электрически соединен с постоянным высоким потенциалом, а исток десятого транзистора электрически соединен с выходом схемы логической операции; одиннадцатый транзистор, причем затвор одиннадцатого транзистора электрически соединен с первым входом схемы логической операции, а сток одиннадцатого транзистора электрически соединен с выходом схемы логической операции; двенадцатый транзистор, причем затвор двенадцатого транзистора электрически соединен со вторым входом схемы логической операции, сток двенадцатого транзистора электрически соединен с истоком одиннадцатого транзистора, а исток двенадцатого транзистора электрически соединен с постоянным низким потенциалом. Первый инвертор и второй инвертор выполнены (то есть, структурированы и расположены) с возможностью приема сигналов управления схемой с помощью постоянного низкого потенциала и первого отрицательного потенциала.

[0006] Чтобы решить вышеупомянутую техническую проблему, другим техническим решением, предлагаемым изобретением, является создание схемы логической операции И-НЕ. Схема содержит: первый инвертор и второй инвертор, применяемые к схеме удержания пониженного напряжения схемы GOA; и девятый транзистор, причем затвор девятого транзистора электрически соединен с выходом первого инвертора, сток девятого транзистора электрически соединен с постоянным высоким потенциалом, а исток девятого транзистора электрически соединен с выходом схемы логической операции; десятый транзистор, причем затвор десятого транзистора электрически соединен с выходом второго инвертора, сток десятого транзистора электрически соединен с постоянным высоким потенциалом, а исток десятого транзистора электрически соединен с выходом схемы логической операции; одиннадцатый транзистор, причем затвор одиннадцатого транзистора электрически соединен с первым входом схемы логической операции, а сток одиннадцатого транзистора электрически соединен с выходом схемы логической операции; двенадцатый транзистор, причем затвор двенадцатого транзистора электрически соединен со вторым входом схемы логической операции, сток двенадцатого транзистора электрически соединен с истоком одиннадцатого транзистора, а исток двенадцатого транзистора электрически соединен с постоянным низким потенциалом.

[0007] В варианте осуществления первый инвертор и второй инвертор являются одинаковыми, и каждый содержит: первый транзистор, причем затвор и сток первого транзистора электрически соединены с постоянным высоким потенциалом, а исток первого транзистора электрически соединен с первым узлом; второй транзистор, причем затвор второго транзистора электрически соединен со входом первого инвертора, сток второго транзистора электрически соединен с первым узлом, а исток второго транзистора электрически соединен с первым отрицательным потенциалом; третий транзистор, причем затвор третьего транзистора электрически соединен с первым узлом, сток третьего транзистора электрически соединен с постоянным высоким потенциалом, а исток третьего транзистора электрически соединен с выходом инвертора; четвертый транзистор, причем затвор четвертого транзистора электрически соединен со входом инвертора, сток четвертого транзистора электрически соединен с выходом инвертора, а исток четвертого транзистора электрически соединен со вторым узлом; пятый транзистор, причем затвор и сток пятого транзистора электрически соединены с постоянным высоким потенциалом, а исток пятого транзистора электрически соединен с третьим узлом; шестой транзистор, причем затвор шестого транзистора электрически соединен со входом инвертора, сток шестого транзистора электрически соединен с третьим узлом, а исток шестого транзистора электрически соединен с постоянным низким потенциалом; седьмой транзистор, причем затвор седьмого транзистора электрически соединен с третьим узлом, сток седьмого транзистора электрически соединен с постоянным высоким потенциалом, а исток седьмого транзистора электрически соединен со вторым узлом; и восьмой транзистор, причем затвор восьмого транзистора электрически соединен со входом инвертора, сток восьмого транзистора электрически соединен со вторым узлом, а исток восьмого транзистора электрически соединен с постоянным низким потенциалом.

[0008] В варианте осуществления первый инвертор и второй инвертор выполнены с возможностью приема сигналов управления схемой с помощью постоянного низкого потенциала и первого отрицательного потенциала.

[0009] В варианте осуществления первый инвертор и второй инвертор являются одинаковыми, и каждый содержит: двадцать первый транзистор, причем затвор и сток двадцать первого транзистора электрически соединены с постоянным высоким потенциалом, а исток двадцать первого транзистора электрически соединен с первым узлом; двадцать второй транзистор, причем затвор двадцать второго транзистора электрически соединен со входом инвертора, сток двадцать второго транзистора электрически соединен с первым узлом, а исток двадцать второго транзистора электрически соединен с первым отрицательным потенциалом; двадцать третий транзистор, причем затвор двадцать третьего транзистора электрически соединен с первым узлом, сток двадцать третьего транзистора электрически соединен с постоянным высоким потенциалом, а исток двадцать третьего транзистора электрически соединен с выходом инвертора; двадцать четвертый транзистор, причем затвор двадцать четвертого транзистора электрически соединен со входом инвертора, сток двадцать четвертого транзистора электрически соединен с выходом инвертора, а исток двадцать четвертого транзистора электрически соединен со вторым узлом; двадцать пятый транзистор, причем затвор двадцать пятого транзистора электрически соединен с третьим узлом, сток двадцать пятого транзистора электрически соединен с постоянным высоким потенциалом, а исток двадцать пятого транзистора электрически соединен со вторым узлом; и двадцать шестой транзистор, причем затвор двадцать шестого транзистора электрически соединен со входом инвертора, сток двадцать шестого транзистора электрически соединен со вторым узлом, а исток двадцать шестого транзистора электрически соединен с постоянным низким потенциалом.

[0010] В варианте осуществления первый инвертор и второй инвертор выполнены с возможностью приема сигналов управления схемой с помощью постоянного высокого потенциала и постоянного низкого потенциала.

[0011] В варианте осуществления первый инвертор содержит: первый транзистор, причем затвор и сток первого транзистора электрически соединены с постоянным высоким потенциалом, а исток первого транзистора электрически соединен с первым узлом в первом инверторе; второй транзистор, причем затвор второго транзистора электрически соединен со входом первого инвертора, сток второго транзистора электрически соединен с первым узлом в первом инверторе, а исток второго транзистора электрически соединен с первым отрицательным потенциалом; третий транзистор, причем затвор третьего транзистора электрически соединен с первым узлом в первом инверторе, сток третьего транзистора электрически соединен с постоянным высоким потенциалом, а исток третьего транзистора электрически соединен с выходом первого инвертора; четвертый транзистор, причем затвор четвертого транзистора электрически соединен со входом первого инвертора, сток четвертого транзистора электрически соединен с выходом первого инвертора, а исток четвертого транзистора электрически соединен со вторым узлом в первом инверторе; пятый транзистор, причем затвор и сток пятого транзистора электрически соединены с постоянным высоким потенциалом, а исток пятого транзистора электрически соединен с третьим узлом в первом инверторе; шестой транзистор, причем затвор шестого транзистора электрически соединен со входом первого инвертора, сток шестого транзистора электрически соединен с третьим узлом в первом инверторе, а исток шестого транзистора электрически соединен с постоянным низким потенциалом; седьмой транзистор, причем затвор седьмого транзистора электрически соединен с третьим узлом в первом инверторе, сток седьмого транзистора электрически соединен с постоянным высоким потенциалом, а исток седьмого транзистора электрически соединен со вторым узлом в первом инверторе; и восьмой транзистор, причем затвор восьмого транзистора электрически соединен со входом первого инвертора, сток восьмого транзистора электрически соединен со вторым узлом в первом инверторе, а исток восьмого транзистора электрически соединен с постоянным низким потенциалом. Второй инвертор содержит: двадцать первый транзистор, причем затвор и сток двадцать первого транзистора электрически соединены с постоянным высоким потенциалом, а исток двадцать первого транзистора электрически соединен с первым узлом во втором инверторе; двадцать второй транзистор, причем затвор двадцать второго транзистора электрически соединен со входом второго инвертора, сток двадцать второго транзистора электрически соединен с первым узлом во втором инверторе, а исток двадцать второго транзистора электрически соединен с первым отрицательным потенциалом; двадцать третий транзистор, причем затвор двадцать третьего транзистора электрически соединен с первым узлом во втором инверторе, сток двадцать третьего транзистора электрически соединен с постоянным высоким потенциалом, а исток двадцать третьего транзистора электрически соединен с выходом второго инвертора; двадцать четвертый транзистор, затвор двадцать четвертого транзистора электрически соединен со входом второго инвертора, сток двадцать четвертого транзистора электрически соединен с выходом второго инвертора, а исток двадцать четвертого транзистора электрически соединен со вторым узлом во втором инверторе; двадцать пятый транзистор, причем затвор двадцать пятого транзистора электрически соединен с третьим узлом во втором инверторе, сток двадцать пятого транзистора электрически соединен с постоянным высоким потенциалом, а исток двадцать пятого транзистора электрически соединен со вторым узлом во втором инверторе; и двадцать шестой транзистор, причем затвор двадцать шестого транзистора электрически соединен со входом второго инвертора, сток двадцать шестого транзистора электрически соединен со вторым узлом во втором инверторе, а исток двадцать шестого транзистора электрически соединен с постоянным низким потенциалом.

[0012] В варианте осуществления первый инвертор выполнен с возможностью приема сигнала управления схемой с помощью постоянного низкого потенциала и первого отрицательного потенциала, второй инвертор выполнен с возможностью приема сигнала управления схемой с помощью постоянного высокого потенциала и постоянного низкого потенциала.

[0013] В варианте осуществления взаимная зависимость между первым отрицательным потенциалом, вторым отрицательным потенциалом и постоянным низким потенциалом заключается в том, что: постоянный низкий потенциал<второй отрицательный потенциал<первый отрицательный потенциал.

[0014] В варианте осуществления схема логической операции И-НЕ выполнена с возможностью приема сигналов управления схемой с помощью постоянного высокого потенциала и постоянного низкого потенциала.

[0015] Для решения технической проблемы еще одно техническое решение, предлагаемое изобретением, заключается в создании схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора. Схема возбуждения сканирования содержит схему логической операции И-НЕ, а схема логической операции И-НЕ содержит: первый инвертор и второй инвертор, применяемые к схеме удержания пониженного напряжения схемы GOA; и девятый транзистор, причем затвор девятого транзистора электрически соединен с выходом первого инвертора, сток девятого транзистора электрически соединен с постоянным высоким потенциалом, а исток девятого транзистора электрически соединен с выходом схемы логической операции; десятый транзистор, причем затвор десятого транзистора электрически соединен с выходом второго инвертора, сток десятого транзистора электрически соединен с постоянным высоким потенциалом, а исток десятого транзистора электрически соединен с выходом схемы логической операции; одиннадцатый транзистор, причем затвор одиннадцатого транзистора электрически соединен с первым входом схемы логической операции, а сток одиннадцатого транзистора электрически соединен с выходом схемы логической операции; двенадцатый транзистор, причем затвор двенадцатого транзистора электрически соединен со вторым входом схемы логической операции, сток двенадцатого транзистора электрически соединен с истоком одиннадцатого транзистора, а исток двенадцатого транзистора электрически соединен с постоянным низким потенциалом.

[0016] В варианте осуществления первый инвертор и второй инвертор одинаковые, и каждый содержит: первый транзистор, причем затвор и сток первого транзистора электрически соединены с постоянным высоким потенциалом, а исток первого транзистора электрически соединен с первым узлом; второй транзистор, причем затвор второго транзистора электрически соединен со входом первого инвертора, сток второго транзистора электрически соединен с первым узлом, а исток второго транзистора электрически соединен с первым отрицательным потенциалом; третий транзистор, причем затвор третьего транзистора электрически соединен с первым узлом, сток третьего транзистора электрически соединен с постоянным высоким потенциалом, а исток третьего транзистора электрически соединен с выходом инвертора; четвертый транзистор, причем затвор четвертого транзистора электрически соединен со входом инвертора, сток четвертого транзистора электрически соединен с выходом инвертора, а исток четвертого транзистора электрически соединен со вторым узлом; пятый транзистор, причем затвор и сток пятого транзистора электрически соединены с постоянным высоким потенциалом, а исток пятого транзистора электрически соединен с третьим узлом; шестой транзистор, причем затвор шестого транзистора электрически соединен со входом инвертора, сток шестого транзистора электрически соединен с третьим узлом, а исток шестого транзистора электрически соединен с постоянным низким потенциалом; седьмой транзистор, причем затвор седьмого транзистора электрически соединен с третьим узлом, сток седьмого транзистора электрически соединен с постоянным высоким потенциалом, а исток седьмого транзистора электрически соединен со вторым узлом; и восьмой транзистор, причем затвор восьмого транзистора электрически соединен со входом инвертора, сток восьмого транзистора электрически соединен со вторым узлом, а исток восьмого транзистора электрически соединен с постоянным низким потенциалом.

[0017] В варианте осуществления первый инвертор и второй инвертор выполнены с возможностью приема сигналов управления схемой с помощью постоянного низкого потенциала и первого отрицательного потенциала.

[0018] В варианте осуществления первый инвертор и второй инвертор являются одинаковыми, и каждый содержит: двадцать первый транзистор, причем затвор и сток двадцать первого транзистора электрически соединены с постоянным высоким потенциалом, а исток двадцать первого транзистора электрически соединен с первым узлом; двадцать второй транзистор, причем затвор двадцать второго транзистора электрически соединен со входом инвертора, сток двадцать второго транзистора электрически соединен с первым узлом, а исток двадцать второго транзистора электрически соединен с первым отрицательным потенциалом; двадцать третий транзистор, причем затвор двадцать третьего транзистора электрически соединен с первым узлом, сток двадцать третьего транзистора электрически соединен с постоянным высоким потенциалом, а исток двадцать третьего транзистора электрически соединен с выходом инвертора; двадцать четвертый транзистор, причем затвор двадцать четвертого транзистора электрически соединен со входом инвертора, сток двадцать четвертого транзистора электрически соединен с выходом инвертора, а исток двадцать четвертого транзистора электрически соединен со вторым узлом; двадцать пятый транзистор, причем затвор двадцать пятого транзистора электрически соединен с третьим узлом, сток двадцать пятого транзистора электрически соединен с постоянным высоким потенциалом, а исток двадцать пятого транзистора электрически соединен со вторым узлом; и двадцать шестой транзистор, причем затвор двадцать шестого транзистора электрически соединен со входом инвертора, сток двадцать шестого транзистора электрически соединен со вторым узлом, а исток двадцать шестого транзистора электрически соединен с постоянным низким потенциалом.

[0019] В варианте осуществления первая схема логической операции И-НЕ и вторая схема логической операции И-НЕ выполнены с возможностью приема сигналов управления схемой с помощью постоянного высокого потенциала и постоянного низкого потенциала.

[0020] В варианте осуществления первый инвертор содержит: первый транзистор, причем затвор и сток первого транзистора электрически соединены с постоянным высоким потенциалом, а исток первого транзистора электрически соединен с первым узлом в первом инверторе; второй транзистор, причем затвор второго транзистора электрически соединен со входом первого инвертора, сток второго транзистора электрически соединен с первым узлом в первом инверторе, а исток второго транзистора электрически соединен с первым отрицательным потенциалом; третий транзистор, причем затвор третьего транзистора электрически соединен с первым узлом в первом инверторе, сток третьего транзистора электрически соединен с постоянным высоким потенциалом, а исток третьего транзистора электрически соединен с выходом первого инвертора; четвертый транзистор, причем затвор четвертого транзистора электрически соединен со входом первого инвертора, сток четвертого транзистора электрически соединен с выходом первого инвертора, а исток четвертого транзистора электрически соединен со вторым узлом в первом инверторе; пятый транзистор, причем затвор и сток пятого транзистора электрически соединены с постоянным высоким потенциалом, а исток пятого транзистора электрически соединен с третьим узлом в первом инверторе; шестой транзистор, причем затвор шестого транзистора электрически соединен со входом первого инвертора, сток шестого транзистора электрически соединен с третьим узлом в первом инверторе, а исток шестого транзистора электрически соединен с постоянным низким потенциалом; седьмой транзистор, причем затвор седьмого транзистора электрически соединен с третьим узлом в первом инверторе, сток седьмого транзистора электрически соединен с постоянным высоким потенциалом, а исток седьмого транзистора электрически соединен со вторым узлом в первом инверторе; и восьмой транзистор, причем затвор восьмого транзистора электрически соединен со входом первого инвертора, сток восьмого транзистора электрически соединен со вторым узлом в первом инверторе, а исток восьмого транзистора электрически соединен с постоянным низким потенциалом. Второй инвертор содержит: двадцать первый транзистор, причем затвор и сток двадцать первого транзистора электрически соединены с постоянным высоким потенциалом, а исток двадцать первого транзистора электрически соединен с первым узлом во втором инверторе; двадцать второй транзистор, причем затвор двадцать второго транзистора электрически соединен со входом второго инвертора, сток двадцать второго транзистора электрически соединен с первым узлом во втором инверторе, а исток двадцать второго транзистора электрически соединен с первым отрицательным потенциалом; двадцать третий транзистор, причем затвор двадцать третьего транзистора электрически соединен с первым узлом во втором инверторе, сток двадцать третьего транзистора электрически соединен с постоянным высоким потенциалом, а исток двадцать третьего транзистора электрически соединен с выходом второго инвертора; двадцать четвертый транзистор, затвор двадцать четвертого транзистора электрически соединен со входом второго инвертора, сток двадцать четвертого транзистора электрически соединен с выходом второго инвертора, а исток двадцать четвертого транзистора электрически соединен со вторым узлом во втором инверторе; двадцать пятый транзистор, причем затвор двадцать пятого транзистора электрически соединен с третьим узлом во втором инверторе, сток двадцать пятого транзистора электрически соединен с постоянным высоким потенциалом, а исток двадцать пятого транзистора электрически соединен со вторым узлом во втором инверторе; и двадцать шестой транзистор, причем затвор двадцать шестого транзистора электрически соединен со входом второго инвертора, сток двадцать шестого транзистора электрически соединен со вторым узлом во втором инверторе, а исток двадцать шестого транзистора электрически соединен с постоянным низким потенциалом.

[0021] В варианте осуществления первый инвертор выполнен с возможностью приема сигнала управления схемой с помощью постоянного низкого потенциала и первого отрицательного потенциала, второй инвертор выполнен с возможностью приема сигнала управления схемой с помощью постоянного высокого потенциала и постоянного низкого потенциала.

[0022] В варианте осуществления взаимная зависимость между первым отрицательным потенциалом, вторым отрицательным потенциалом и постоянным низким потенциалом заключается в том, что: постоянный низкий потенциал < второй отрицательный потенциал < первый отрицательный потенциал.

[0023] В варианте осуществления схема логической операции И-НЕ выполнена с возможностью приема сигналов управления схемой с помощью постоянного высокого потенциала и постоянного низкого потенциала.

[0024] Эффективность, которая может быть достигнута с помощью изобретения, заключается в следующем: изобретение предусматривает схему возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора и схему логической операции И-НЕ такой схемы, содержащую первый инвертор и второй инвертор, применяемые к схеме удержания пониженного напряжения схемы GOА, и несколько (т.е. более одного) транзисторов, использует комбинацию NTFT и инвертора для замены функции исходных элементов PMMOS для достижения характеристик, аналогичных исходной схеме операции CMOS NAND (И-НЕ), и, следовательно, решает проблему проектирования IGZO TFT одного типа схемы логической операции устройства, и, таким образом, более подходит для интегрирования большой цифровой интегральной схемы на жидкокристаллическом устройстве отображения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0025] Чтобы более четко проиллюстрировать технические решения различных вариантов осуществления настоящего изобретения, следующие чертежи будут кратко описаны в вариантах осуществления. Очевидно, что чертежи являются только некоторыми вариантами осуществления настоящего изобретения, обычный специалист в данной области техники может получить другие чертежи в соответствии с этими чертежами без творческих усилий. На чертежах:

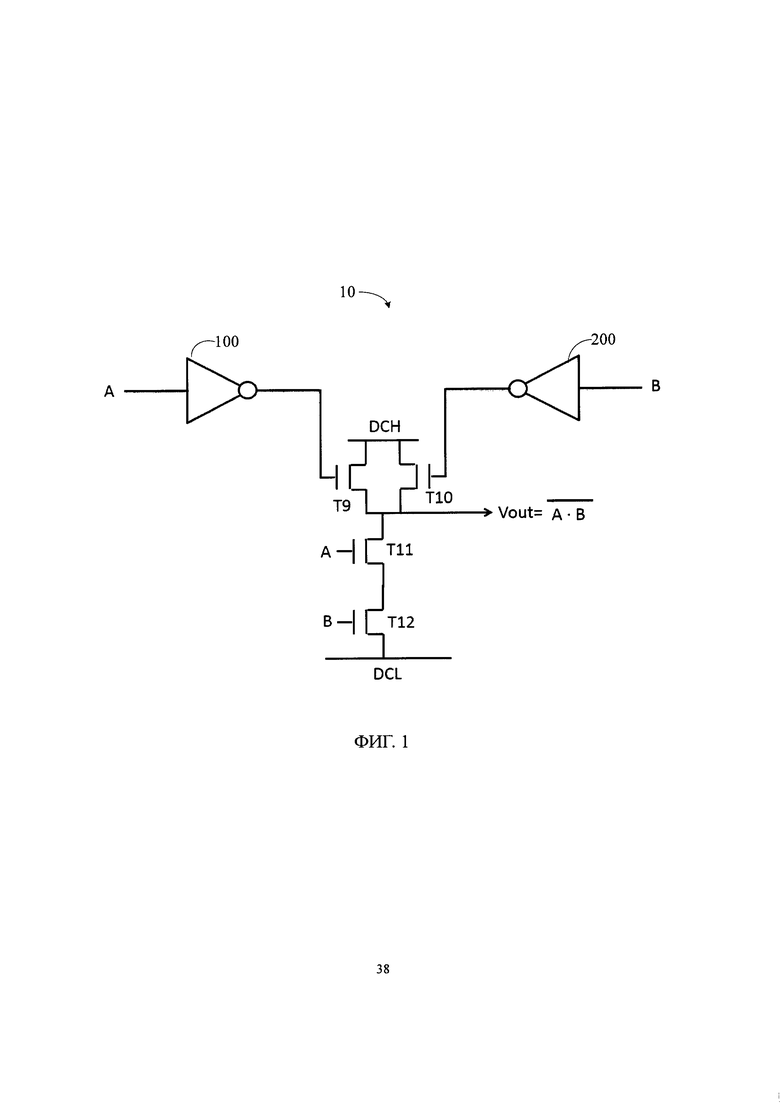

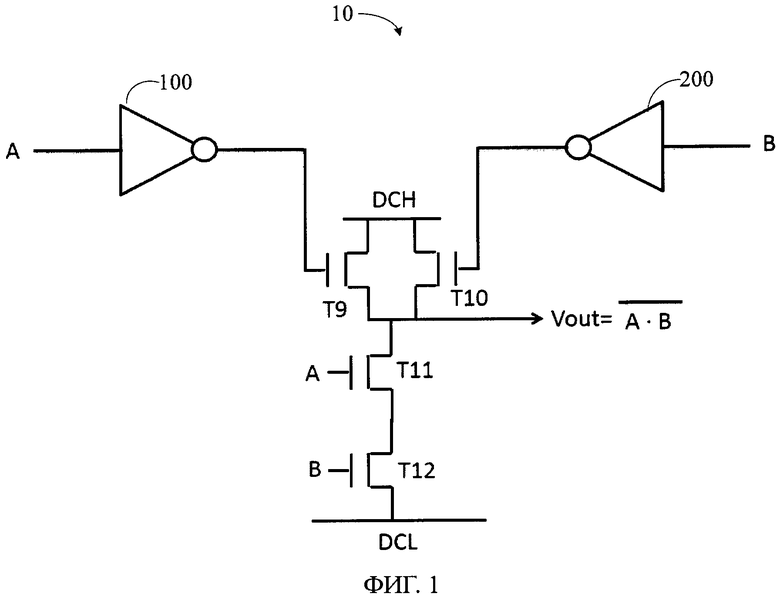

[0026] Фиг. 1 - принципиальная схема схемы логической операции И-НЕ варианта осуществления изобретения;

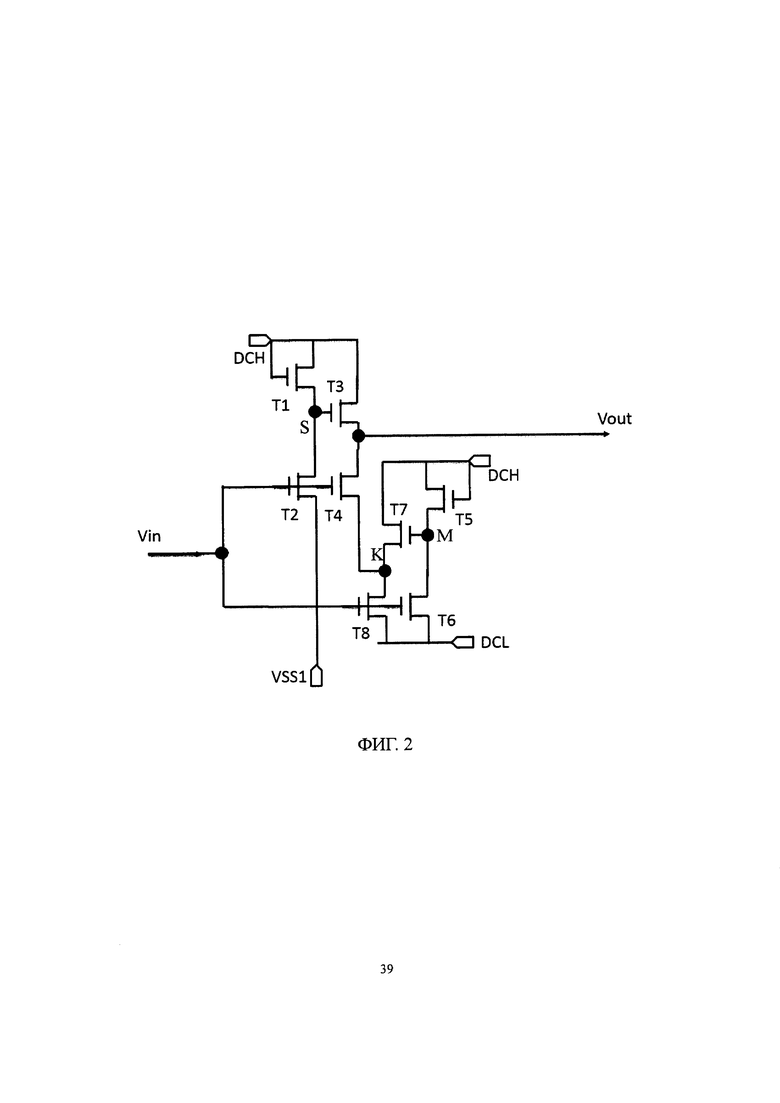

[0027] Фиг. 2 - принципиальная схема инвертора схемы логической операции И-НЕ варианта осуществления изобретения; и

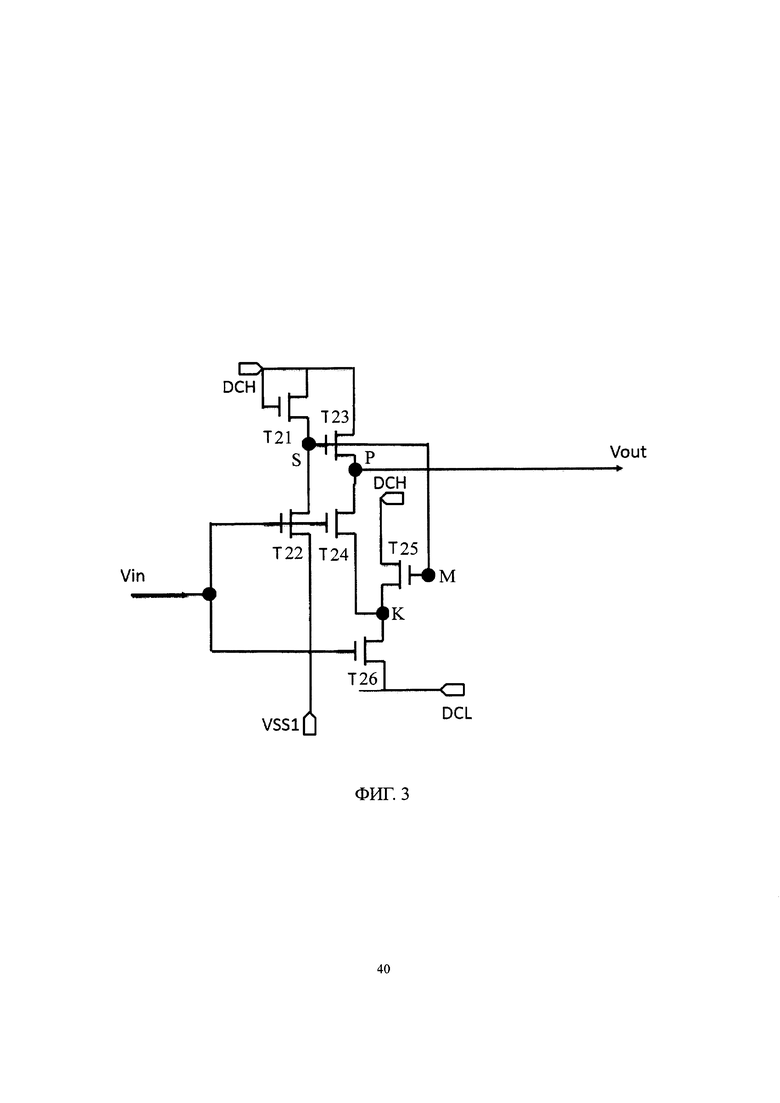

[0028] Фиг. 3 - принципиальная схема инвертора схемы логической операции И-НЕ другого варианта осуществления изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0029] Ниже со ссылкой на прилагаемые чертежи вариантов осуществления изобретения будут четко и полностью описаны технические решения в вариантах осуществления изобретения. Очевидно, что описанные варианты осуществления являются лишь частью вариантов осуществления настоящего изобретения, а не всеми вариантами осуществления. На основе вариантов осуществления настоящего изобретения все другие варианты осуществления, полученные обычным специалистом в данной области без творческих усилий, принадлежат к объему правовой охраны изобретения.

[0030] Со ссылкой на фиг. 1, показана принципиальная схема схемы логической операции И-НЕ варианта осуществления изобретения. Схема логической операции И-НЕ 10 представляет собой схему логической операции, применяемой к схеме возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора.

[0031] В частности, схема 10 содержит первый инвертор 100 и второй инвертор 200. Первый инвертор 100 и второй инвертор 200 оба являются инверторами, применяемыми к схеме удержания пониженного напряжения схемы GOА (драйвер затвора на матрице).

[0032] Кроме того, первый инвертор 100 и второй инвертор 200 оба являются основными частями инвертора, применяемого к схеме удержания пониженного напряжения схемы GOA.

[0033] Схема 10 дополнительно содержит:

[0034] девятый транзистор Т9, причем затвор девятого транзистора Т9 электрически соединен с выходом первого инвертора 100, сток девятого транзистора Т9 электрически соединен с постоянным высоким потенциалом DCH, а исток девятого транзистора Т9 электрически соединен с выходом Vout схемы логической операции 10;

[0035] десятый транзистор Т10, причем затвор десятого транзистора Т10 электрически соединен с выходом второго инвертора 200, сток десятого транзистора Т10 электрически соединен с постоянным высоким потенциалом DCH, а исток десятого транзистора Т10 электрически соединен с выходом Vout схемы логической операции 10;

[0036] одиннадцатый транзистор Т11, причем затвор одиннадцатого транзистора Т11 электрически соединен с первым входом А схемы логической операции 10, а сток одиннадцатого транзистора Т11 электрически соединен с выходом Vout схемы логической операции; и

[0037] двенадцатый транзистор Т12, причем затвор двенадцатого транзистора Т12 электрически соединен со вторым входом В схемы логической операции 10, сток двенадцатого транзистора Т12 электрически соединен с истоком одиннадцатого транзистора T11, а исток двенадцатого транзистора Т12 электрически соединен с постоянным низким потенциалом DCL.

[0038] Кроме того, схема логической операции И-НЕ принимает сигналы управления схемой с помощью постоянного высокого потенциала DCH и постоянного низкого потенциала DCL.

[0039] См. фиг. 2, показана принципиальная схема инвертора схемы логической операции И-НЕ варианта осуществления изобретения. Взаимная зависимость, касающаяся структуры и соединения инвертора, выглядит следующим образом:

[0040] первый транзистор Т1, причем затвор и сток первого транзистора Т1 электрически соединены с постоянным высоким потенциалом DCH, а исток первого транзистора Т1 электрически соединен с первым узлом S;

[0041] второй транзистор Т2, причем затвор второго транзистора Т2 электрически соединен со входом Vin инвертора, сток второго транзистора Т2 электрически соединен с первым узлом S, а исток второго транзистора Т2 электрически соединен с первым отрицательным потенциалом VSS1;

[0042] третий транзистор Т3, причем затвор третьего транзистора Т3 электрически соединен с первым узлом S, сток третьего транзистора Т3 электрически соединен с постоянным высоким потенциалом DCH, а исток третьего транзистора Т3 электрически соединен с выходом Vout инвертора;

[0043] четвертый транзистор Т4, причем затвор четвертого транзистора Т4 электрически соединен со входом Vin инвертора, сток четвертого транзистора Т4 электрически соединен с выходом Vout инвертора, а исток четвертого транзистора Т4 электрически соединен со вторым узлом K;

[0044] пятый транзистор Т5, причем затвор и сток пятого транзистора Т5 электрически соединены с постоянным высоким потенциалом DCH, а исток пятого транзистора Т5 электрически соединен с третьим узлом М;

[0045] шестой транзистор Т6, причем затвор шестого транзистора Т6 электрически соединен со входом Vin инвертора, сток шестого транзистора Т6 электрически соединен с третьим узлом М, а исток шестого транзистора Т6 электрически соединен с постоянным низким потенциалом DCL;

[0046] седьмой транзистор Т7, причем затвор седьмого транзистора Т7 электрически соединен с третьим узлом М, сток седьмого транзистора Т7 электрически соединен с постоянным высоким потенциалом DCH, а исток седьмого транзистора Т7 электрически соединен со вторым узлом K; и

[0047] восьмой транзистор Т8, причем затвор восьмого транзистора Т8 электрически соединен со входом Vin инвертора, сток восьмого транзистора Т8 электрически соединен со вторым узлом K, а исток восьмого транзистора Т8 электрически соединен с постоянным низким потенциалом DCL.

[0048] Кроме того, инвертор, показанный на фиг. 2, принимает сигнал управления схемой с помощью постоянного низкого потенциала DCL и первого отрицательного потенциала VSS1.

[0049] Взаимная зависимость между первым отрицательным потенциалом VSS1 и постоянным низким потенциалом DCL заключается в следующем: постоянный низкий потенциал DCL < первый отрицательный потенциал VSS1, то есть постоянный низкий потенциал DCL ниже, чем первый отрицательный потенциал VSS1.

[0050] См. фиг. 3, показана принципиальная схема инвертора схемы логической операции И-НЕ другого варианта осуществления изобретения. Взаимная зависимость, касающаяся структуры и соединения инвертора, выглядит следующим образом:

[0051] двадцать первый транзистор Т21, причем затвор и сток двадцать первого транзистора Т21 электрически соединены с постоянным высоким потенциалом DCH, а исток двадцать первого транзистора Т21 электрически соединен с первым узлом S;

[0052] двадцать второй транзистор Т22, причем затвор двадцать второго транзистора Т22 электрически соединен со входом Vin инвертора, сток двадцать второго транзистора Т22 электрически соединен с первым узлом S, а исток двадцать второго транзистора Т22 электрически соединен с первым отрицательным потенциалом VSS1;

[0053] двадцать третий транзистор Т23, причем затвор двадцать третьего транзистора Т23 электрически соединен с первым узлом S, сток двадцать третьего транзистора Т23 электрически соединен с постоянным высоким потенциалом DCH, а исток двадцать третьего транзистора Т23 электрически соединен с выходом Vout инвертора;

[0054] двадцать четвертый транзистор Т24, затвор двадцать четвертого транзистора Т24 электрически соединен со входом Vin инвертора, сток двадцать четвертого транзистора электрически соединен с выходом Vout инвертора, а исток двадцать четвертого транзистора Т24 электрически соединен со вторым узлом K;

[0055] двадцать пятый транзистор Т25, причем затвор двадцать пятого транзистора Т25 электрически соединен с третьим узлом М (также является первым узлом S, как показано на фиг. 3), сток двадцать пятого транзистора Т25 электрически соединен с постоянным высоким потенциалом DCH, а исток двадцать пятого транзистора Т25 электрически соединен со вторым узлом K; и

[0056] двадцать шестой транзистор Т26, причем затвор двадцать шестого транзистора Т26 электрически соединен со входом Vin инвертора, сток двадцать шестого транзистора Т26 электрически соединен со вторым узлом K, а исток двадцать шестого транзистора Т26 электрически соединен с постоянным низким потенциалом DCL.

[0057] Кроме того, инвертор, показанный на фиг. 3, принимает сигнал управления схемой с помощью постоянного высокого потенциала DCH и постоянного низкого потенциала DCL.

[0058] Взаимная зависимость между первым отрицательным потенциалом VSS1 и постоянным низким потенциалом DCL заключается в следующем: постоянный низкий потенциал DCL < первый отрицательный потенциал VSS1.

[0059] В варианте осуществления первый инвертор и второй инвертор в схеме 10 принимают инвертор, как показано на фиг. 2.

[0060] В другом варианте осуществления первый инвертор и второй инвертор в схеме 10 принимают инвертор, как показано на фиг. 3.

[0061] В еще одном варианте осуществления первый инвертор в схеме 10 принимает инвертор, как показано на фиг. 2, а второй инвертор в схеме 10 принимает инвертор, как показано на фиг. 3.

[0062] Кроме того, в вышеприведенных вариантах осуществления все транзисторы могут представлять собой IGZO (оксид индия, галлия и цинка) NTFT.

[0063] Таким образом, изобретение предусматривает схему возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора и схему логической операции И-НЕ такой схемы, содержащую первый инвертор и второй инвертор, применяемые к схеме удержания пониженного напряжения схемы GOА, и несколько (т.е. более одного) транзисторов, использует комбинацию NTFT и инвертора для замены функции исходных элементов PMMOS для достижения характеристик, аналогичных исходной схеме операции CMOS NAND (И-НЕ), и, следовательно, решает проблему проектирования IGZO TFT одного типа схемы логической операции устройства, и, таким образом, более подходит для интегрирования большой цифровой интегральной схемы на жидкокристаллическом устройстве отображения.

[0064] Хотя изобретение было описано с точки зрения того, что в настоящее время считается наиболее практичными и предпочтительными вариантами осуществления, следует понимать, что изобретение не должно ограничиваться раскрытыми вариантами осуществления. Напротив, оно предназначено для охвата различных модификаций и аналогичных устройств, включенных в объем и содержание прилагаемой формулы изобретения, которая должна предоставляться с самой широкой интерпретацией, чтобы охватить все такие модификации и аналогичные структуры.

Изобретение относится к области технологий для жидкокристаллических дисплеев. Технический результат заключается в обеспечении использования одного типа устройств тонкопленочных транзисторов за счет использования схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора. Технический результат достигается за счет схемы логической операции И-НЕ, содержащей первый инвертор и второй инвертор, применяемые к схеме удержания пониженного напряжения схемы GOA, девятый транзистор, затвор которого электрически соединен с выходом первого инвертора, сток электрически соединен с постоянным высоким потенциалом, а исток электрически соединен с выходом схемы логической операции, десятый транзистор, затвор которого электрически соединен с выходом второго инвертора, сток электрически соединен с постоянным высоким потенциалом, а исток электрически соединен с выходом схемы логической операции, одиннадцатый транзистор, затвор которого электрически соединен с первым входом схемы логической операции, а сток электрически соединен с выходом схемы логической операции, и двенадцатый транзистор, затвор которого электрически соединен со вторым входом схемы логической операции, сток электрически соединен с истоком одиннадцатого транзистора, а исток электрически соединен с постоянным низким потенциалом. 3 н. и 16 з.п. ф-лы, 3 ил.

1. Схема логической операции И-НЕ, содержащая:

первый инвертор и второй инвертор, применяемые к схеме удержания пониженного напряжения схемы GOA; и

девятый транзистор (Т9), затвор которого электрически соединен с выходом первого инвертора, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) схемы логической операции;

десятый транзистор (Т10), затвор которого электрически соединен с выходом второго инвертора, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) схемы логической операции;

одиннадцатый транзистор (Т11), затвор которого электрически соединен с первым входом (А) схемы логической операции, а сток электрически соединен с выходом (Vout) схемы логической операции; и

двенадцатый транзистор (Т12), затвор которого электрически соединен со вторым входом (В) схемы логической операции, сток электрически соединен с истоком одиннадцатого транзистора (T11), а исток электрически соединен с постоянным низким потенциалом (DCL);

причем первый инвертор и второй инвертор выполнены с возможностью приема сигналов управления схемой с помощью постоянного низкого потенциала (DCL) и первого отрицательного потенциала (VSS1).

2. Схема логической операции И-НЕ, содержащая:

первый инвертор и второй инвертор, применяемые к схеме удержания пониженного напряжения схемы GOA; и

девятый транзистор (Т9), затвор которого электрически соединен с выходом первого инвертора, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) схемы логической операции;

десятый транзистор (Т10), затвор которого электрически соединен с выходом второго инвертора, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) схемы логической операции;

одиннадцатый транзистор (Т11), затвор которого электрически соединен с первым входом (А) схемы логической операции, а сток электрически соединен с выходом (Vout) схемы логической операции; и

двенадцатый транзистор (Т12), затвор которого электрически соединен со вторым входом (В) схемы логической операции, сток электрически соединен с истоком одиннадцатого транзистора (T11), а исток электрически соединен с постоянным низким потенциалом (DCL).

3. Схема по п. 2, в которой первый инвертор и второй инвертор одинаковы и каждый содержит:

первый транзистор (Т1), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с первым узлом (S);

второй транзистор (Т2), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен с первым узлом (S), а исток электрически соединен с первым отрицательным потенциалом (VSS1);

третий транзистор (Т3), затвор которого электрически соединен с первым узлом (S), сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) инвертора;

четвертый транзистор (Т4), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен с выходом (Vout) инвертора, а исток электрически соединен со вторым узлом (K);

пятый транзистор (Т5), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с третьим узлом (М);

шестой транзистор (Т6), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен с третьим узлом (М), а исток электрически соединен с постоянным низким потенциалом (DCL);

седьмой транзистор (Т7), затвор которого электрически соединен с третьим узлом (М), сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен со вторым узлом (K); и

восьмой транзистор (Т8), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен со вторым узлом (K), а исток электрически соединен с постоянным низким потенциалом (DCL).

4. Схема по п. 3, в которой первый инвертор и второй инвертор выполнены с возможностью приема сигналов управления схемой с помощью постоянного низкого потенциала (DCL) и первого отрицательного потенциала (VSS1).

5. Схема по п. 2, в которой первый инвертор и второй инвертор одинаковы и каждый содержит:

двадцать первый транзистор (Т21), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с первым узлом (S);

двадцать второй транзистор (Т22), затвор которого электрически соединен с входом инвертора, сток электрически соединен с первым узлом (S), а исток электрически соединен с первым отрицательным потенциалом (VSS1);

двадцать третий транзистор (Т23), затвор которого электрически соединен с первым узлом (S), сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) инвертора;

двадцать четвертый транзистор (Т24), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен с выходом (Vout) инвертора, а исток электрически соединен со вторым узлом (K);

двадцать пятый транзистор (Т25), затвор которого электрически соединен с третьим узлом (М), сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен со вторым узлом (K); и

двадцать шестой транзистор (Т26), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен со вторым узлом (K), а исток электрически соединен с постоянным низким потенциалом (DCL).

6. Схема по п. 5, в которой первый инвертор и второй инвертор выполнены с возможностью приема сигналов управления схемой с помощью постоянного высокого потенциала (DCH) и постоянного низкого потенциала (DCL).

7. Схема по п. 2, в которой

первый инвертор содержит:

первый транзистор (Т1), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с первым узлом (S) в первом инверторе;

второй транзистор (Т2), затвор которого электрически соединен с входом (Vin) первого инвертора, сток электрически соединен с первым узлом (S) в первом инверторе, а исток электрически соединен с первым отрицательным потенциалом (VSS1);

третий транзистор (Т3), затвор которого электрически соединен с первым узлом (S) в первом инверторе, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) первого инвертора;

четвертый транзистор (Т4), затвор которого электрически соединен с входом (Vin) первого инвертора, сток электрически соединен с выходом (Vout) первого инвертора, а исток электрически соединен со вторым узлом (K) в первом инверторе;

пятый транзистор (Т5), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с третьим узлом (М) в первом инверторе;

шестой транзистор (Т6), затвор которого электрически соединен с входом (Vin) первого инвертора, сток электрически соединен с третьим узлом (М) в первом инверторе, а исток электрически соединен с постоянным низким потенциалом (DCL);

седьмой транзистор (Т7), затвор которого электрически соединен с третьим узлом (М) в первом инверторе, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен со вторым узлом (K) в первом инверторе; и

восьмой транзистор (Т8), затвор которого электрически соединен с входом (Vin) первого инвертора, сток электрически соединен со вторым узлом (K) в первом инверторе, а исток электрически соединен с постоянным низким потенциалом (DCL);

второй инвертор содержит:

двадцать первый транзистор (Т21), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с первым узлом (S) во втором инверторе;

двадцать второй транзистор (Т22), затвор которого электрически соединен с входом второго инвертора, сток электрически соединен с первым узлом (S) во втором инверторе, а исток электрически соединен с первым отрицательным потенциалом (VSS1);

двадцать третий транзистор (Т23), затвор которого электрически соединен с первым узлом (S) во втором инверторе, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) второго инвертора;

двадцать четвертый транзистор (Т24), затвор которого электрически соединен с входом (Vin) второго инвертора, сток электрически соединен с выходом (Vout) второго инвертора, а исток электрически соединен со вторым узлом (K) во втором инверторе;

двадцать пятый транзистор (Т25), затвор которого электрически соединен с третьим узлом (М) во втором инверторе, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен со вторым узлом (К) во втором инверторе; и

двадцать шестой транзистор (Т26), затвор которого электрически соединен с входом (Vin) второго инвертора, сток электрически соединен со вторым узлом (K) во втором инверторе, а исток электрически соединен с постоянным низким потенциалом (DCL).

8. Схема по п. 7, в которой первый инвертор выполнен с возможностью приема сигнала управления схемой с помощью постоянного низкого потенциала (DCL) и первого отрицательного потенциала (VSS1), второй инвертор выполнен с возможностью приема сигнала управления схемой с помощью постоянного высокого потенциала (DCH) и постоянного низкого потенциала (DCL).

9. Схема по п. 8, в которой взаимная зависимость между первым отрицательным потенциалом (VSS1), вторым отрицательным потенциалом (VSS2) и постоянным низким потенциалом (DCL) следующая: постоянный низкий потенциал (DCL) < второй отрицательный потенциал (VSS2) < первый отрицательный потенциал (VSS1).

10. Схема по п. 2, выполненная с возможностью приема сигналов управления схемой с помощью постоянного высокого потенциала (DCH) и постоянного низкого потенциала (DCL).

11. Схема возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора, содержащая схему логической операции И-НЕ, которая содержит:

первый инвертор и второй инвертор, применяемые к схеме удержания пониженного напряжения схемы GOA; и

девятый транзистор (Т9), затвор которого электрически соединен с выходом первого инвертора, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) схемы логической операции;

десятый транзистор (Т10), затвор которого электрически соединен с выходом второго инвертора, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) схемы логической операции;

одиннадцатый транзистор (Т11), затвор которого электрически соединен с первым входом (А) схемы логической операции, а сток электрически соединен с выходом (Vout) схемы логической операции; и

двенадцатый транзистор (Т12), затвор которого электрически соединен со вторым входом (В) схемы логической операции, сток электрически соединен с истоком одиннадцатого транзистора (T11), а исток электрически соединен с постоянным низким потенциалом (DCL).

12. Схема по п. 11, в которой первый инвертор и второй инвертор одинаковы и каждый содержит:

первый транзистор (Т1), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с первым узлом (S);

второй транзистор (Т2), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен с первым узлом (S), а исток электрически соединен с первым отрицательным потенциалом (VSS1);

третий транзистор (Т3), затвор которого электрически соединен с первым узлом (S), сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) инвертора;

четвертый транзистор (Т4), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен с выходом (Vout) инвертора, а исток электрически соединен со вторым узлом (K);

пятый транзистор (Т5), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с третьим узлом (М);

шестой транзистор (Т6), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен с третьим узлом (М), а исток электрически соединен с постоянным низким потенциалом (DCL);

седьмой транзистор (Т7), затвор которого электрически соединен с третьим узлом (М), сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен со вторым узлом (K); и

восьмой транзистор (Т8), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен со вторым узлом (K), а исток электрически соединен с постоянным низким потенциалом (DCL).

13. Схема по п. 12, в которой первый инвертор и второй инвертор выполнены с возможностью приема сигналов управления схемой с помощью постоянного низкого потенциала (DCL) и первого отрицательного потенциала (VSS1).

14. Схема по п. 11, в которой первый инвертор и второй инвертор одинаковы и каждый содержит:

двадцать первый транзистор (Т21), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с первым узлом (S);

двадцать второй транзистор (Т22), затвор которого электрически соединен с входом инвертора, сток электрически соединен с первым узлом (S), а исток электрически соединен с первым отрицательным потенциалом (VSS1);

двадцать третий транзистор (Т23), затвор которого электрически соединен с первым узлом (S), сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) инвертора;

двадцать четвертый транзистор (Т24), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен с выходом (Vout) инвертора, а исток электрически соединен со вторым узлом (K);

двадцать пятый транзистор (Т25), затвор которого электрически соединен с третьим узлом (М), сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен со вторым узлом (K); и

двадцать шестой транзистор (Т26), затвор которого электрически соединен с входом (Vin) инвертора, сток электрически соединен со вторым узлом (K), а исток электрически соединен с постоянным низким потенциалом (DCL).

15. Схема по п. 14, в которой первая схема логической операции И-НЕ и вторая схема логической операции И-НЕ выполнены с возможностью приема сигналов управления схемой с помощью постоянного высокого потенциала (DCH) и постоянного низкого потенциала (DCL).

16. Схема по п. 11, в которой

первый инвертор содержит:

первый транзистор (Т1), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с первым узлом (S) в первом инверторе;

второй транзистор (Т2), затвор которого электрически соединен с входом (Vin) первого инвертора, сток электрически соединен с первым узлом (S) в первом инверторе, а исток электрически соединен с первым отрицательным потенциалом (VSS1);

третий транзистор (Т3), затвор которого электрически соединен с первым узлом (S) в первом инверторе, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) первого инвертора;

четвертый транзистор (Т4), затвор которого электрически соединен с входом (Vin) первого инвертора, сток электрически соединен с выходом (Vout) первого инвертора, а исток электрически соединен со вторым узлом (K) в первом инверторе;

пятый транзистор (Т5), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с третьим узлом (М) в первом инверторе;

шестой транзистор (Т6), затвор которого электрически соединен с входом (Vin) первого инвертора, сток электрически соединен с третьим узлом (М) в первом инверторе, а исток электрически соединен с постоянным низким потенциалом (DCL);

седьмой транзистор (Т7), затвор которого электрически соединен с третьим узлом (М) в первом инверторе, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен со вторым узлом (K) в первом инверторе; и

восьмой транзистор (Т8), затвор которого электрически соединен с входом (Vin) первого инвертора, сток электрически соединен со вторым узлом (K) в первом инверторе, а исток электрически соединен с постоянным низким потенциалом (DCL);

второй инвертор содержит:

двадцать первый транзистор (Т21), затвор и сток которого электрически соединены с постоянным высоким потенциалом (DCH), а исток электрически соединен с первым узлом (S) во втором инверторе;

двадцать второй транзистор (Т22), затвор которого электрически соединен с входом второго инвертора, сток электрически соединен с первым узлом (S) во втором инверторе, а исток электрически соединен с первым отрицательным потенциалом (VSS1);

двадцать третий транзистор (Т23), затвор которого электрически соединен с первым узлом (S) во втором инверторе, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен с выходом (Vout) второго инвертора;

двадцать четвертый транзистор (Т24), затвор которого электрически соединен с входом (Vin) второго инвертора, сток электрически соединен с выходом (Vout) второго инвертора, а исток электрически соединен со вторым узлом (K) во втором инверторе;

двадцать пятый транзистор (Т25), затвор которого электрически соединен с третьим узлом (М) во втором инверторе, сток электрически соединен с постоянным высоким потенциалом (DCH), а исток электрически соединен со вторым узлом (K) во втором инверторе; и

двадцать шестой транзистор (Т26), затвор которого электрически соединен с входом (Vin) второго инвертора, сток электрически соединен со вторым узлом (K) во втором инверторе, а исток электрически соединен с постоянным низким потенциалом (DCL).

17. Схема по п. 16, в которой первый инвертор выполнен с возможностью приема сигнала управления схемой с помощью постоянного низкого потенциала (DCL) и первого отрицательного потенциала (VSS1), а второй инвертор выполнен с возможностью приема сигнала управления схемой с помощью постоянного высокого потенциала (DCH) и постоянного низкого потенциала (DCL).

18. Схема по п. 17, в которой взаимная зависимость между первым отрицательным потенциалом (VSS1), вторым отрицательным потенциалом (VSS2) и постоянным низким потенциалом (DCL) следующая: постоянный низкий потенциал (DCL) < второй отрицательный потенциал (VSS2) < первый отрицательный потенциал (VSS1).

19. Схема по п. 11, в которой схема логической операции И-НЕ выполнена с возможностью приема сигналов управления схемой с помощью постоянного высокого потенциала (DCH) и постоянного низкого потенциала (DCL).

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| СПОСОБ ПОЛУЧЕНИЯ ПОКРЫТИЯ С ВЫСОКОЙ ВОСПРОИЗВОДИМОСТЬЮ ОПТИЧЕСКИХ СВОЙСТВ | 2015 |

|

RU2608412C1 |

| КВАДРАТУРНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ДЕЛЕНИЕМ НА ТРИ | 2009 |

|

RU2479121C2 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

Авторы

Даты

2018-03-26—Публикация

2015-01-28—Подача