ОБЛАСТЬ ТЕХНИКИ

[0001] Изобретение относится к области технологии жидкокристаллических дисплеев, и, в частности, к жидкокристаллическому устройству отображения и схеме возбуждения затвора для него.

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

[0002] Технология схемы GOA (возбуждение затвора на матрице) использует процесс подложек с активной матрицей обычного жидкокристаллического устройства отображения для того, чтобы изготовить сканирующую схему возбуждения затвора на матричной подложке и тем самым достигнуть непрерывного сканирующего режима возбуждения. Схема GOA имеет преимущества в виде сниженной цены производства и конструкции с узкой рамкой, и поэтому используется для ряда устройств отображения. Схеме GOА требуется иметь две основные функции: первая заключается в том, чтобы вводить сигналы возбуждения затвора для управления затворными шинами в панели и тем самым включать множество TFT (тонкопленочных транзисторов) в области отображения, для того чтобы позволить информационным шинам заряжать пиксели; и вторая является функцией сдвига регистра, так что когда вывод n-ого сигнала возбуждения затвора завершается, она вслед за этим выполняет вывод (n+1)-го сигнала возбуждения затвора при помощи управления синхронизации; и т.д.

[0003] Схема GOA включает в себя повышающую схему, схему управления повышением, понижающую схему, схему управления понижением и схему усиления для поднятия потенциала. В частности, повышающая схема в основном отвечает за вывод сигнала синхронизации, введенного в затвор тонкопленочного транзистора, в качестве сигнала возбуждения жидкокристаллического устройства отображения. Схема управления повышением отвечает за управление повышающей схемой таким образом, чтобы она включалась, и, как правило, подчиняется управлению сигналом, переданным от предшествующей схемы GOA. Понижающая схема отвечает за быстрое понижение сканирующего сигнала до низкого уровня напряжения после вывода сканирующего сигнала, т.е. понижение потенциала затвора тонкопленочного транзистора до низкого уровня напряжения. Схема управления понижением отвечает за поддержание сканирующего сигнала и сигнала повышающей схемы (как правило, называемого сигналом узла Q) в выключенном состоянии (т.е., устанавливает отрицательный потенциал) и, как правило, имеет две схемы поддержания понижения, которые работают поочередно. Схема усиления отвечает за поднятие потенциала на узле Q в очередной раз, для того чтобы гарантировать нормальный вывод G(N) повышающей схемы.

[0004] Различные схемы GOA могут использовать различные процессы производства. Процесс LTPS (низкотемпературный поликристаллический кремний) имеет преимущества в виде высокой мобильности электронов и проверенной технологии и, вследствие этого, в настоящее время широко используется небольшими и среднего размера устройствами отображения. Процесс CMOS (комплементарная структура оксид металла - полупроводник) LTPS имеет преимущества в виде низких затрат энергии, высокой мобильности электронов и широкой устойчивости к помехам и т.д., и поэтому закономерно используется производителями панелей. Соответственно, имеется потребность разработки схемы GOA, соответствующей процессу CMOS LTPS.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0005] Соответственно, варианты осуществления изобретения обеспечивают жидкокристаллическое устройство отображения и схему возбуждения затвора, которые подходят для процесса CMOS и могут увеличить стабильность схемы.

[0006] В частности, изобретение обеспечивает схему возбуждения затвора, включающую в себя множество схем сдвиговых регистров. Множество схем сдвиговых регистров являются каскадно-включенными последовательно. Каждая из множества схем сдвиговых регистров включает в себя: первую повышающую схему, вторую повышающую схему, первую понижающую схему, вторую понижающую схему и схему управления понижением. Первая повышающая схема и вторая повышающая схема последовательно электрически подключены между предшествующим сигналом возбуждения затвора и выходным выводом сигнала возбуждения затвора. Первая понижающая схема, вторая понижающая схема и схема управления понижением электрически соединены с первой повышающей схемой и второй повышающей схемой параллельно. Схема управления понижением электрически соединена с предшествующим сигналом возбуждения затвора, первой понижающей схемой, второй понижающей схемой, первым уровнем напряжения и вторым уровнем напряжения. Помимо всего прочего, схема управления понижением выполнена с возможностью управления первой понижающей схемой и второй понижающей схемой в соответствии с предшествующим сигналом возбуждения затвора.

[0007] В варианте осуществления схема сдвиговых регистров дополнительно включает в себя первый конденсатор и второй конденсатор. Первая повышающая схема включает в себя первый транзистор; затвор и исток первого транзистора электрически подключены с возможностью приема предшествующего сигнала возбуждения затвора. Вторая повышающая схема включает в себя второй транзистор; затвор второго транзистора электрически подключен к стоку первого транзистора, исток второго транзистора подключается с возможностью приема первого сигнала синхронизации, и сток второго транзистора электрически подключен к выходному выводу сигнала возбуждения затвора. Первый конденсатор электрически подключен между стоком и затвором второго транзистора. Первая понижающая схема включает в себя третий транзистор; исток третьего транзистора электрически подключен к выходному выводу сигнала возбуждения затвора, и сток третьего транзистора электрически подключен к первому уровню напряжения. Вторая понижающая схема включает в себя четвертый транзистор; исток четвертого транзистора электрически подключен к стоку первого транзистора, и сток четвертого транзистора электрически подключен к первому уровню напряжения. Вывод второго конденсатора электрически подключен к первому уровню напряжения, и другой вывод второго конденсатора электрически подключен к затвору третьего транзистора и затвору четвертого транзистора.

[0008] В варианте осуществления схема управления понижением включает в себя: пятый транзистор, причем затвор пятого транзистора электрически подключен с возможностью приема предшествующего сигнала возбуждения затвора, исток пятого транзистора электрически подключен к первому уровню напряжения, и сток пятого транзистора электрически подключен к затвору третьего транзистора и затвору четвертого транзистора; шестой транзистор, причем затвор шестого транзистора электрически подключен с возможностью приема предшествующего сигнала возбуждения затвора, и исток шестого транзистора электрически подключен к первому уровню напряжения; седьмой транзистор, причем затвор седьмого транзистора электрически подключен к стоку шестого транзистора, исток седьмого транзистора электрически подключен ко второму уровню напряжения, и сток седьмого транзистора электрически подключен к стоку пятого транзистора; третий конденсатор электрически подключен между истоком и затвором седьмого транзистора; и восьмой транзистор, причем затвор и сток восьмого транзистора электрически подключены ко второму уровню напряжения, и исток восьмого транзистора электрически подключен к стоку шестого транзистора.

[0009] В варианте осуществления первый уровень напряжения является уровнем высокого напряжения, и второй уровень напряжения является уровнем низкого напряжения; т.е. первый уровень напряжения является более высоким, чем второй уровень напряжения.

[0010] В варианте осуществления первый транзистор, второй транзистор, третий транзистор, четвертый транзистор, пятый транзистор, шестой транзистор, седьмой транзистор и восьмой транзистор - все являются МОП транзисторами p-типа.

[0011] Изобретение дополнительно обеспечивает жидкокристаллическое устройство отображения, включающее в себя жидкокристаллическую панель отображения и схему возбуждения затвора. Схема возбуждения затвора электрически подключена к жидкокристаллической панели отображения и с возможностью подачи сканирующих сигналов возбуждения к жидкокристаллической панели отображения. Схема возбуждения затвора включает в себя множество схем сдвиговых регистров, каскадно-включенных последовательно. Каждая из множества схем сдвиговых регистров включает в себя: первую повышающую схему, вторую повышающую схему, первую понижающую схему, вторую понижающую схему и схему управления понижением. Первая повышающая схема и вторая повышающая схема последовательно электрически подключены между предшествующим сигналом возбуждения затвора и выходным выводом сигнала возбуждения затвора. Первая понижающая схема, вторая понижающая схема и схема управления понижением электрически соединены с первой повышающей схемой и второй повышающей схемой параллельно. Схема управления понижением электрически соединена с предшествующим сигналом возбуждения затвора, первой понижающей схемой, второй понижающей схемой, первым уровнем напряжения и вторым уровнем напряжения. Помимо всего прочего, схема управления понижением выполнена с возможностью управления первой понижающей схемой и второй понижающей схемой в соответствии с предшествующим сигналом возбуждения затвора.

[0012] В варианте осуществления схема сдвиговых регистров дополнительно включает в себя первый конденсатор и второй конденсатор. Первая повышающая схема включает в себя первый транзистор; затвор и исток первого транзистора электрически подключены с возможностью приема предшествующего сигнала возбуждения затвора. Вторая повышающая схема включает в себя второй транзистор; затвор второго транзистора электрически подключен к стоку первого транзистора, исток второго транзистора подключается с возможностью приема первого сигнала синхронизации, и сток второго транзистора электрически подключен к выходному выводу сигнала возбуждения затвора. Первый конденсатор электрически подключен между стоком и затвором второго транзистора. Первая понижающая схема включает в себя третий транзистор; исток третьего транзистора электрически подключен к выходному выводу сигнала возбуждения затвора, и сток третьего транзистора электрически подключен к первому уровню напряжения. Вторая понижающая схема включает в себя четвертый транзистор; исток четвертого транзистора электрически подключен к стоку первого транзистора, и сток четвертого транзистора электрически подключен к первому уровню напряжения. Вывод второго конденсатора электрически подключен к первому уровню напряжения, и другой вывод второго конденсатора электрически подключен к затвору третьего транзистора и затвору четвертого транзистора.

[0013] В варианте осуществления схема управления понижением включает в себя: пятый транзистор, причем затвор пятого транзистора электрически подключен с возможностью приема предшествующего сигнала возбуждения затвора, исток пятого транзистора электрически подключен к первому уровню напряжения, и сток пятого транзистора электрически подключен к затвору третьего транзистора и затвору четвертого транзистора; шестой транзистор, причем затвор шестого транзистора электрически подключен с возможностью приема предшествующего сигнала возбуждения затвора, и исток шестого транзистора электрически подключен к первому уровню напряжения; седьмой транзистор, причем затвор седьмого транзистора электрически подключен к стоку шестого транзистора, исток седьмого транзистора электрически подключен ко второму уровню напряжения, и сток седьмого транзистора электрически подключен к стоку пятого транзистора; третий конденсатор электрически подключен между истоком и затвором седьмого транзистора; и восьмой транзистор, причем затвор и сток восьмого транзистора электрически подключены ко второму уровню напряжения, и исток восьмого транзистора электрически подключен к стоку шестого транзистора.

[0014] В варианте осуществления первый уровень напряжения является уровнем высокого напряжения, и второй уровень напряжения является уровнем низкого напряжения.

[0015] В варианте осуществления первый транзистор, второй транзистор, третий транзистор, четвертый транзистор, пятый транзистор, шестой транзистор, седьмой транзистор и восьмой транзистор - все являются МОП транзисторами p-типа.

[0016] При помощи вышеуказанных решений эффект, который может достигаться при помощи изобретения, заключается в том, что: схема управления понижением изобретения электрически соединена с предшествующим сигналом возбуждения затвора, первой понижающей схемой, второй понижающей схемой, первым уровнем напряжения и вторым уровнем напряжения, и схема управления понижением дополнительно управляет первой понижающей схемой и второй понижающей схемой в соответствии с предшествующим сигналом возбуждения затвора. Соответственно, изобретение подходит для процесса CMOS и может увеличить стабильность схем.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0017] Для того чтобы более ясно проиллюстрировать технические решения различных вариантов осуществления настоящего изобретения, будут использоваться чертежи в описании вариантов осуществления, будет дано краткое описание ниже. Очевидным образом, чертежи в последующем описании представляют собой только некоторые варианты осуществления изобретения, средний специалист в данной области техники может получить другие чертежи, соответствующие этим проиллюстрированным чертежам, без творческих усилий. На чертежах:

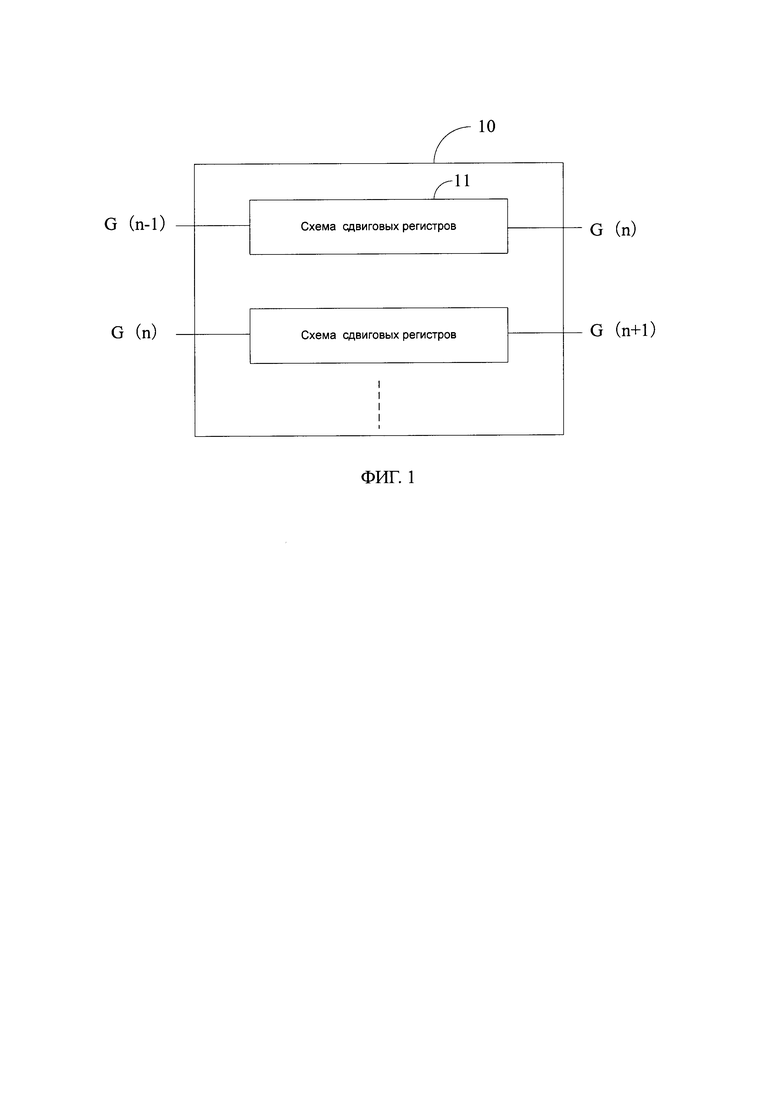

[0018] ФИГ. 1 представляет собой схематичный структурный вид схемы возбуждения затвора варианта осуществления изобретения;

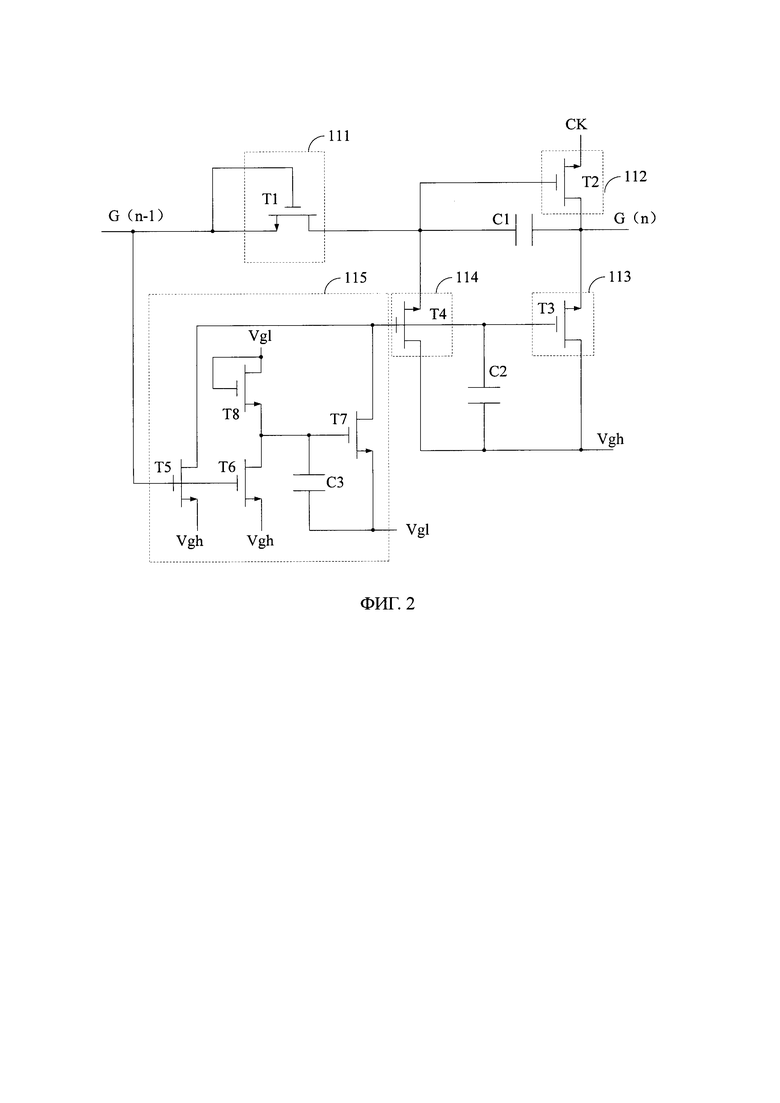

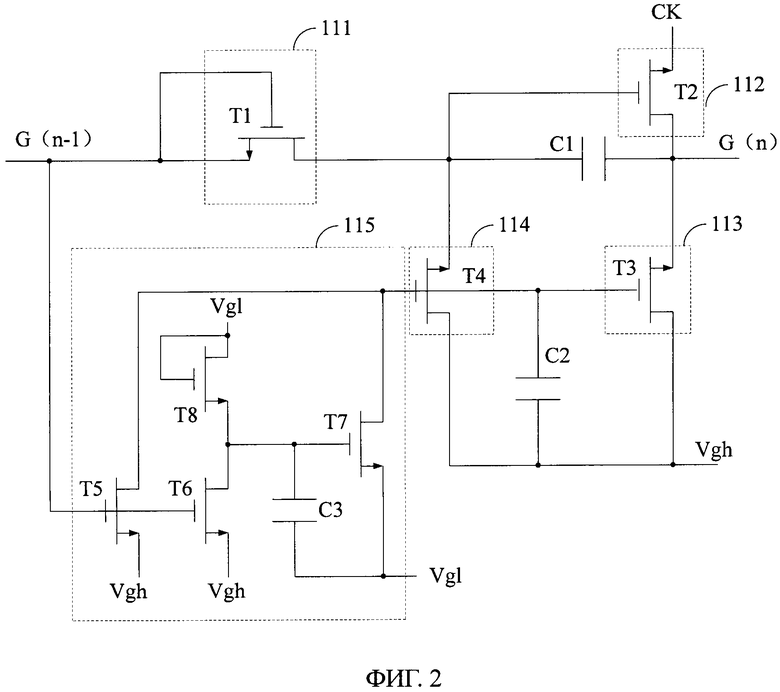

[0019] ФИГ. 2 представляет собой структурную схему схемы сдвиговых регистров, показанной на ФИГ. 1;

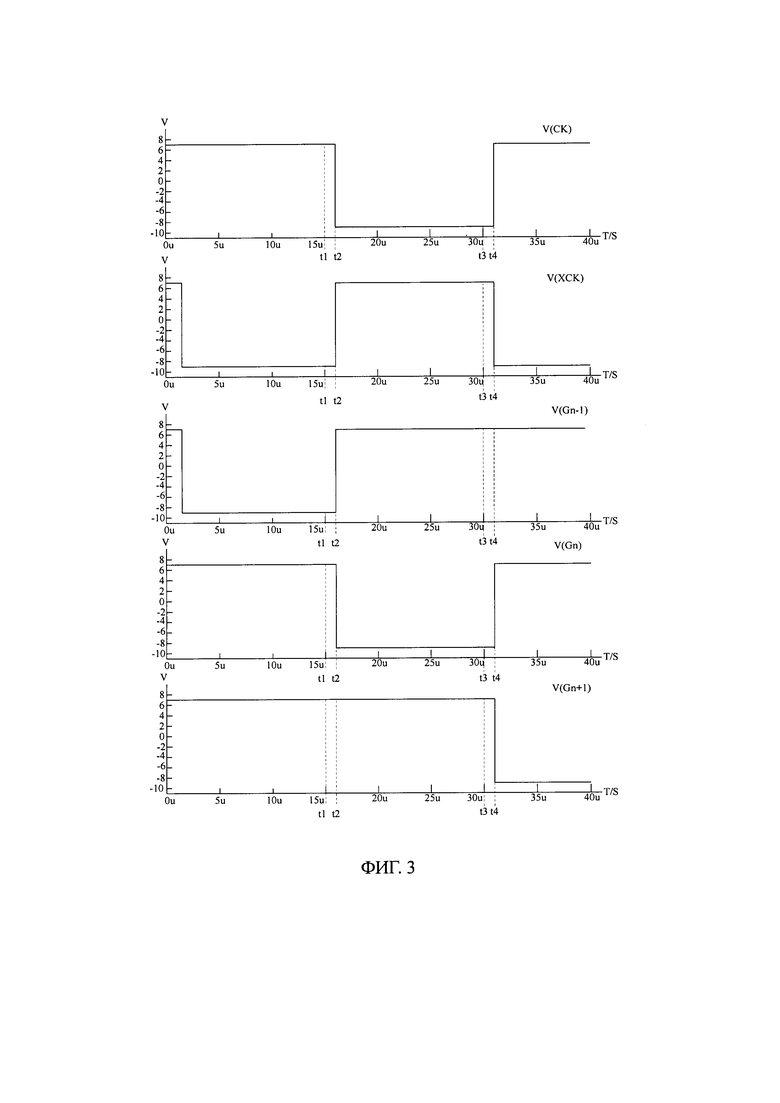

[0020] ФИГ. 3 представляет собой смоделированную временную диаграмму схемы возбуждения затвора, показанной на ФИГ. 1; и

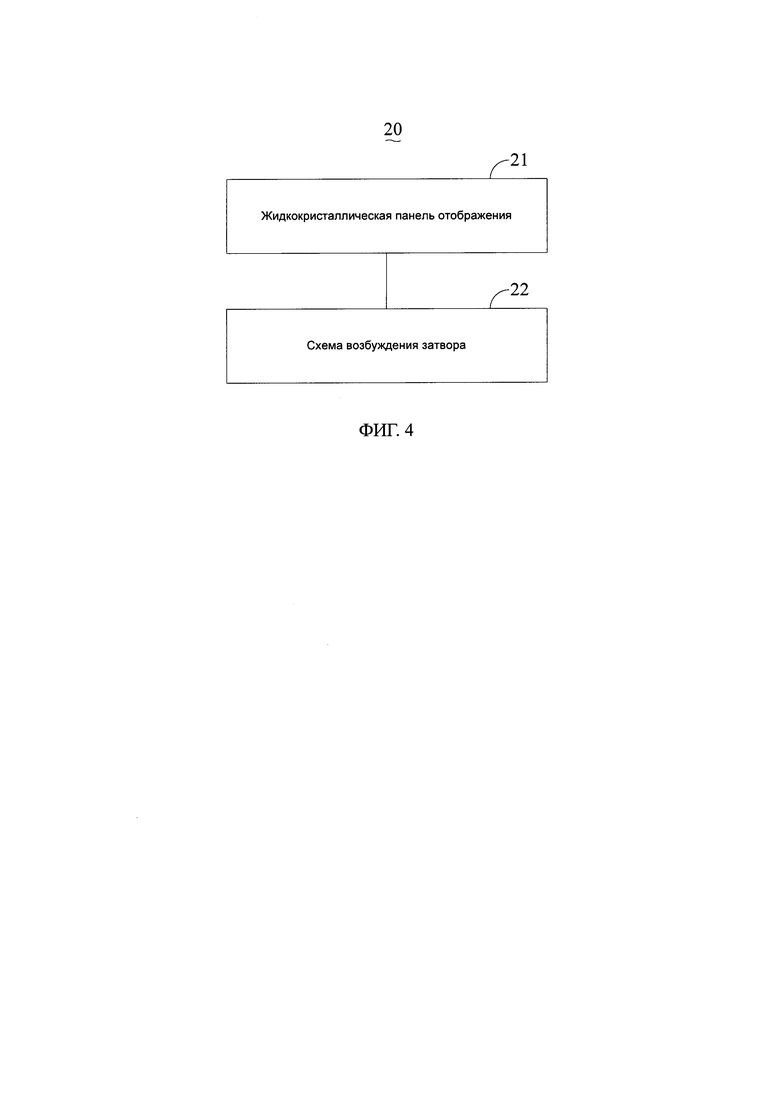

[0021] ФИГ. 4 представляет собой структурный схематичный вид жидкокристаллического устройства отображения варианта осуществления изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0022] В последующем, со ссылкой на сопровождающие чертежи вариантов осуществления изобретения, технические решения в вариантах осуществления изобретения будут описаны ясно и полностью. Очевидным образом, варианты осуществления изобретения, описанные ниже, представляют собой только часть вариантов осуществления изобретения, но не все варианты осуществления. На основе описанных вариантов осуществления изобретения все другие варианты осуществления, полученные средним специалистом в данной области техники без творческих усилий, принадлежат объему защиты изобретения.

[0023] Ссылаемся на ФИГ. 1, которая представляет собой схематичный структурный вид схемы возбуждения затвора варианта осуществления изобретения. Как показано на ФИГ. 1, схема 10 возбуждения затвора, обеспеченная в этом варианте осуществления, включает в себя множество схем 11 сдвиговых регистров. Множество схем 11 сдвиговых регистров являются каскадно-включенными последовательно.

[0024] Как показано на ФИГ. 2, схема 11 сдвиговых регистров включает в себя первую повышающую схему 111, вторую повышающую схему 112, первую понижающую схему 113, вторую понижающую схему 114, схему 115 управления понижением, первый конденсатор С1, второй конденсатор С2 и третий конденсатор С3. Первая повышающая схема 111 и вторая повышающая схема 112 последовательно электрически подключены между предшествующим сигналом G(n-1) возбуждения затвора и выходным выводом сигнала G(n) возбуждения затвора. Первая понижающая схема 113, вторая понижающая схема 114 и схема 115 управления понижением электрически соединены с первой повышающей схемой 111 и второй повышающей схемой 112 параллельно. Схема 115 управления понижением электрически соединена с предшествующим сигналом G(n-1) возбуждения затвора, первой понижающей схемой 113, второй понижающей схемой 114, первым уровнем Vgh напряжения и вторым уровнем Vgl напряжения. Схема 115 управления понижением выполнена с возможностью управления первой понижающей схемой 113 и второй понижающей схемой 114 в соответствии с предшествующим сигналом G(n-1) возбуждения затвора.

[0025] Первая повышающая схема 111 включает в себя первый транзистор Т1. Затвор и исток первого транзистора Т1 электрически подключены с возможностью приема предшествующего сигнала G(n-1) возбуждения затвора. Вторая повышающая схема 112 включает в себя второй транзистор Т2. Затвор второго транзистора Т2 электрически подключен к стоку первого транзистора Т1, исток второго транзистора Т2 электрически подключен с возможностью приема первого сигнала СK синхронизации, и сток второго транзистора Т2 электрически подключен к выходному выводу сигнала G(n) возбуждения затвора, и первый конденсатор С1 электрически подключен между затвором и стоком второго транзистора Т2. Первая понижающая схема 113 включает в себя третий транзистор Т3. Исток третьего транзистора T3 электрически подключен к выходному выводу сигнала G(n) возбуждения затвора, и сток третьего транзистора T3 электрически подключен к первому уровню Vgh напряжения. Вторая понижающая схема 114 включает в себя четвертый транзистор Т4. Исток четвертого транзистора Т4 электрически подключен к стоку первого транзистора Т1, и сток четвертого транзистора Т4 электрически подключен к первому уровню Vgh напряжения. Вывод второго конденсатора С2 электрически подключен к первому уровню Vgh напряжения, и другой вывод второго конденсатора С2 электрически подключен к затвору третьего транзистора Т3 и затвору четвертого транзистора Т4. Схема 115 управления понижением электрически соединена с предшествующим сигналом G(n-1) возбуждения затвора, затвором третьего транзистора Т3, затвором четвертого транзистора Т4, первым уровнем Vgh напряжения и вторым уровнем Vgl напряжения. Схема 115 управления понижением управляет действиями третьего транзистора Т3 и четвертого транзистора Т4 в соответствии с предшествующим сигналом G(n-1) возбуждения затвора, т.е. управляет третьим транзистором Т3 и четвертым транзистором Т4 таким образом, чтобы они включались или выключались.

[0026] Схема 115 управления понижением включает в себя пятый транзистор Т5, шестой транзистор Т6, седьмой транзистор Т7 и восьмой транзистор Т8. Затвор пятого транзистора Т5 электрически подключен с возможностью приема предшествующего сигнала G(n-1) возбуждения затвора, исток пятого транзистора Т5 электрически подключен к первому уровню Vgh напряжения, и сток пятого транзистора Т5 электрически подключен к затвору третьего транзистора T3 и затвору четвертого транзистора Т4. Затвор шестого транзистора Т6 электрически подключен с возможностью приема предшествующего сигнала G(n-1) возбуждения затвора, и исток шестого транзистора Т6 электрически подключен к первому уровню Vgh напряжения. Затвор седьмого транзистора Т7 электрически подключен к стоку шестого транзистора Т6, исток седьмого транзистора Т7 электрически подключен ко второму уровню Vgl напряжения, сток седьмого транзистора Т7 электрически подключен к стоку пятого транзистора Т5, и третий конденсатор С3 электрически подключен между истоком и затвором седьмого транзистора Т7. Затвор и сток восьмого транзистора Т8 электрически подключены ко второму уровню Vgl напряжения, и исток восьмого транзистора Т8 электрически подключен к стоку шестого транзистора Т6.

[0027] В этом варианте осуществления первый уровень Vgh напряжения преимущественно является уровнем высокого напряжения, и второй уровень Vgl напряжения преимущественно является уровнем низкого напряжения. Первый транзистор Т1, второй транзистор Т2, третий транзистор Т3, четвертый транзистор Т4, пятый транзистор Т5, шестой транзистор Т6, седьмой транзистор Т7 и восьмой транзистор Т8 - все являются МОП транзисторами p-типа, и в другом варианте осуществления средний специалист в данной области техники может использовать другие транзисторы с полевым эффектом, такие как МОП транзисторы n-типа, в качестве вышеуказанных транзисторов.

[0028] Теперь ниже будет описываться принцип работа схемы 10 возбуждения затвора более подробно со ссылкой на временную диаграмму, показанную на ФИГ. 3.

[0029] В первый момент t1, предшествующий сигнал G(n-1) возбуждения затвора имеет низкий уровень напряжения, первый транзистор Т1 включается, первый сигнал СK синхронизации имеет высокий уровень напряжения, затвор второго транзистора Т2 находится на низком уровне напряжения, второй транзистор Т2 включается; пятый транзистор Т5 и шестой транзистор Т6 оба включаются, затвор седьмого транзистора Т7 и исток восьмого транзистора Т8 оба находятся на высоких уровнях напряжения, седьмой транзистор Т7 выключается, восьмой транзистор Т8 включается; затвор третьего транзистора T3 и затвор четвертого транзистора Т4 оба находятся на высоких уровнях напряжения, третий транзистор T3 и четвертый транзистор Т4 оба выключаются; и вследствие этого, выходной сигнал выходного вывода сигнала G(n) возбуждения затвора является таким же, как и первый сигнал СK синхронизации, т.е. выходной сигнал выходного вывода сигнала G(n) возбуждения затвора имеет высокий уровень напряжения.

[0030] Во второй момент t2, предшествующий сигнал G(n-1) возбуждения затвора меняется с низкого уровня напряжения на высокий уровень напряжения, первый транзистор Т1 выключается, первый сигнал СK синхронизации меняется с высокого уровня напряжения на низкий уровень напряжения, второй транзистор Т2 включается; пятый транзистор Т5, шестой транзистор Т6, седьмой транзистор Т7 и восьмой транзистор Т8 все выключаются, третий транзистор T3 и четвертый транзистор Т4 оба выключаются; и вследствие этого, выходной сигнал выходного вывода сигнала G(n) возбуждения затвора является таким же, как и первый сигнал СK синхронизации, т.е. выходной сигнал выходного вывода сигнала возбуждения затвора G(n) меняется с высокого уровня напряжения на низкий уровень напряжения.

[0031] В третий момент t3, предшествующий сигнал G(n-1) возбуждения затвора имеет высокий уровень напряжения, первый транзистор Т1 выключается, первый сигнал СK синхронизации имеет низкий уровень напряжения, второй транзистор Т2 включается; пятый транзистор Т5, шестой транзистор Т6, седьмой транзистор Т7 и восьмой транзистор Т8 все выключаются; третий транзистор T3 и четвертый транзистор Т4 оба выключаются; и вследствие этого, выходной сигнал выходного вывода сигнала G(n) возбуждения затвора является таким же, как и первый сигнал СK синхронизации, т.е. выходной сигнал выходного вывода сигнала G(n) возбуждения затвора имеет низкий уровень напряжения.

[0032] В четвертый момент t4, предшествующий сигнал G(n-1) возбуждения затвора имеет высокий уровень напряжения, первый транзистор Т1 выключается, первый сигнал СK синхронизации меняется с низкого уровня напряжения на высокий уровень напряжения, второй транзистор Т2 включается; пятый транзистор Т5 и шестой транзистор Т6 оба выключаются, восьмой транзистор Т8 включается, седьмой транзистор Т7 включается, затвор третьего транзистора T3 и затвор четвертого транзистора Т4 оба находятся на низких уровнях напряжения, третий транзистор T3 и четвертый транзистор Т4 оба включаются, выходной сигнал выходного вывода сигнала G(n) возбуждения затвора непрерывно имеет высокий уровень напряжения.

[0033] Этот вариант осуществления использует схему 115 управления понижением для того, чтобы электрически соединиться с предшествующим сигналом G(n-1) возбуждения затвора, затвором третьего транзистора Т3, затвором четвертого транзистора Т4, первым уровнем Vgh напряжения и вторым уровнем Vgl напряжения, схема 115 управления понижением может управлять третьим транзистором T3 и четвертым транзистором Т4 в соответствии с предшествующим сигналом G(n-1) возбуждения затвора, и вследствие этого, этот вариант осуществления подходит для CMOS и может увеличить стабильность схем, также как и уменьшить количество сигналов синхронизации.

[0034] В дополнение к этому, изобретение дополнительно обеспечивает жидкокристаллическое устройство отображения. Как показано на ФИГ. 4, жидкокристаллическое устройство 20 отображения, обеспеченное при помощи этого варианта осуществления, включает в себя жидкокристаллическую панель 21 отображения и схему 22 возбуждения затвора. Схема 22 возбуждения затвора электрически соединена с жидкокристаллической панелью 21 отображения. Схема 22 возбуждения затвора выполнена с возможностью (т.е. сконструирована и приспособлена) обеспечения сканирующих сигналов возбуждения для жидкокристаллической панели 21 отображения. Схема 22 возбуждения затвора представляет собой схему 10 возбуждения затвора, описанную в вышеуказанном варианте осуществления, и поэтому не будет далее в данном документе повторяться.

[0035] Подводя итог вышесказанному, схема управления понижением изобретения электрически соединена с предшествующим сигналом возбуждения затвора, третьим транзистором, четвертым транзистором, первым уровнем напряжения и вторым уровнем напряжения, и схема управления понижением может управлять третьим транзистором и четвертым транзистором в соответствии с предшествующим сигналом возбуждения затвора, и вследствие этого, она подходит для процесса CMOS и может увеличить стабильность схем.

[0036] Принимая во внимание то, что изобретение описывалось применительно к тому, что в настоящее время считается наиболее практичными и предпочтительными вариантами осуществления, следует понимать, что изобретение не следует ограничивать раскрытыми вариантами осуществления. Напротив, предполагается, что оно охватывает различные модификации и аналогичные приспособления, входящие в состав сущности и объема прилагаемой формулы изобретения, которая должна отвечать требованиям широчайшей интерпретации, для того чтобы сосредоточить в себе все подобные модификации и аналогичные конструкции.

Изобретение относится к области жидкокристаллических дисплеев. Технический результат заключается в повышении стабильности работы схемы возбуждения затвора. Технический результат достигается за счет первой схемы повышения напряжения, которая содержит первый транзистор, затвор и исток первого транзистора, электрически подключенные с возможностью приема предшествующего сигнала возбуждения затвора, второй схемы повышения напряжения, которая содержит второй транзистор, затвор второго транзистора, электрически подключенный к стоку первого транзистора, при этом исток второго транзистора подключается с возможностью приема первого сигнала синхронизации, и сток второго транзистора электрически подключен к выходному выводу сигнала возбуждения затвора, первого конденсатора, электрически подключенного между стоком и затвором второго транзистора, первой схемы понижения напряжения, которая содержит третий транзистор, при этом исток третьего транзистора электрически подключен к выходному выводу сигнала возбуждения затвора, и сток третьего транзистора электрически подключен к первому уровню напряжения. 2 н. и 6 з.п. ф-лы, 4 ил.

1. Схема возбуждения затвора, содержащая множество схем сдвиговых регистров, причем множество схем сдвиговых регистров являются каскадно-включенными последовательно, каждая из множества схем сдвиговых регистров содержит:

первую схему повышения напряжения, вторую схему повышения напряжения, первую схему понижения напряжения, вторую схему понижения напряжения и схему управления понижением напряжения,

первая схема повышения напряжения и вторая схема повышения напряжения последовательно электрически подключены между предшествующим сигналом возбуждения затвора и выходным выводом сигнала возбуждения затвора; первая схема понижения напряжения, вторая схема понижения напряжения и схема управления понижением напряжения электрически соединены с первой схемой повышения напряжения и второй схемой повышения напряжения параллельно; схема управления понижением напряжения электрически соединена с предшествующим сигналом возбуждения затвора, первой схемой понижения напряжения, второй схемой понижения напряжения, первым уровнем напряжения и вторым уровнем напряжения; и схема управления понижением напряжения выполнена с возможностью управлять первой схемой понижения напряжения и второй схемой понижения напряжения в соответствии с предшествующим сигналом возбуждения затвора,

причем схема сдвиговых регистров дополнительно содержит первый конденсатор и второй конденсатор,

первая схема повышения напряжения содержит первый транзистор, затвор и исток первого транзистора, электрически подключенные с возможностью приема предшествующего сигнала возбуждения затвора,

вторая схема повышения напряжения содержит второй транзистор, затвор второго транзистора электрически подключен к стоку первого транзистора, исток второго транзистора подключается с возможностью приема первого сигнала синхронизации, и сток второго транзистора электрически подключен к выходному выводу сигнала возбуждения затвора,

первый конденсатор электрически подключен между стоком и затвором второго транзистора,

первая схема понижения напряжения содержит третий транзистор, исток третьего транзистора электрически подключен к выходному выводу сигнала возбуждения затвора, и сток третьего транзистора электрически подключен к первому уровню напряжения,

вторая схема понижения напряжения содержит четвертый транзистор, исток четвертого транзистора электрически подключен к стоку первого транзистора, и сток четвертого транзистора электрически подключен к первому уровню напряжения, и

вывод второго конденсатора электрически подключен к первому уровню напряжения, и другой вывод второго конденсатора электрически подключен к затвору третьего транзистора и затвору четвертого транзистора.

2. Схема возбуждения затвора по п. 1, в которой схема управления понижением напряжения содержит:

пятый транзистор, причем затвор пятого транзистора электрически подключен с возможностью приема предшествующего сигнала возбуждения затвора, исток пятого транзистора электрически подключен к первому уровню напряжения, и сток пятого транзистора электрически подключен к затвору третьего транзистора и затвору четвертого транзистора,

шестой транзистор, причем затвор шестого транзистора электрически подключен с возможностью приема предшествующего сигнала возбуждения затвора, и исток шестого транзистора электрически подключен к первому уровню напряжения,

седьмой транзистор, причем затвор седьмого транзистора электрически подключен к стоку шестого транзистора, исток седьмого транзистора электрически подключен ко второму уровню напряжения, и сток седьмого транзистора электрически подключен к стоку пятого транзистора,

третий конденсатор, электрически подключенный между истоком и затвором седьмого транзистора,

восьмой транзистор, причем затвор и сток восьмого транзистора электрически подключены ко второму уровню напряжения, и исток восьмого транзистора электрически подключен к стоку шестого транзистора.

3. Схема возбуждения затвора по п. 2, в которой первый уровень напряжения является уровнем высокого напряжения, и второй уровень напряжения является уровнем низкого напряжения.

4. Схема возбуждения затвора по п. 3, в которой первый транзистор, второй транзистор, третий транзистор, четвертый транзистор, пятый транзистор, шестой транзистор, седьмой транзистор и восьмой транзистор являются МОП транзисторами р-типа.

5. Жидкокристаллическое устройство отображения, содержащее жидкокристаллическую панель отображения и схему возбуждения затвора, причем схема возбуждения затвора электрически подключена к жидкокристаллической панели отображения и с возможностью подачи сканирующих сигналов возбуждения к жидкокристаллической панели отображения, схема возбуждения затвора содержит множество схем сдвиговых регистров, каскадно-включенных последовательно, причем каждая из множества схем сдвиговых регистров содержит:

первую схему повышения напряжения, вторую схему повышения напряжения, первую схему понижения напряжения, вторую схему понижения напряжения и схему управления понижением напряжения,

первая схема повышения напряжения и вторая схема повышения напряжения последовательно электрически подключены между предшествующим сигналом возбуждения затвора и выходным выводом сигнала возбуждения затвора; первая схема понижения напряжения, вторая схема понижения напряжения и схема управления понижением напряжения электрически соединены с первой схемой повышения напряжения и второй схемой повышения напряжения параллельно; схема управления понижением напряжения электрически соединена с предшествующим сигналом возбуждения затвора, первой схемой понижения напряжения, второй схемой понижения напряжения, первым уровнем напряжения и вторым уровнем напряжения; а схема управления понижением напряжения выполнена с возможностью управления первой схемой понижения напряжения и второй схемой понижения напряжения в соответствии с предшествующим сигналом возбуждения затвора,

причем схема сдвиговых регистров дополнительно содержит первый конденсатор и второй конденсатор,

первая схема повышения напряжения содержит первый транзистор, затвор и исток первого транзистора электрически соединены с возможностью приема предшествующего сигнала возбуждения затвора,

вторая схема повышения напряжения содержит второй транзистор, затвор второго транзистора электрически подключен к стоку первого транзистора, исток второго транзистора электрически подключен с возможностью приема первого сигнала синхронизации, а сток второго транзистора электрически подключен к выходному выводу сигнала возбуждения затвора,

первый конденсатор электрически подключен между стоком и затвором второго транзистора,

первая схема понижения напряжения содержит третий транзистор, исток третьего транзистора электрически подключен к выходному выводу сигнала возбуждения затвора, а сток третьего транзистора электрически подключен к первому уровню напряжения,

вторая схема понижения напряжения содержит четвертый транзистор, исток четвертого транзистора электрически подключен к стоку первого транзистора, а сток четвертого транзистора электрически подключен к первому уровню напряжения, и

вывод второго конденсатора электрически подключен к первому уровню напряжения, а другой вывод второго конденсатора электрически подключен к затвору третьего транзистора и затвору четвертого транзистора.

6. Жидкокристаллическое устройство отображения по п. 5, в котором схема управления понижением напряжения содержит:

пятый транзистор, причем затвор пятого транзистора электрически подключен с возможностью приема предшествующего сигнала возбуждения затвора, исток пятого транзистора электрически подключен к первому уровню напряжения, а сток пятого транзистора электрически подключен к затвору третьего транзистора и затвору четвертого транзистора,

шестой транзистор, причем затвор шестого транзистора электрически подключен с возможностью приема предшествующего сигнала возбуждения затвора, а исток шестого транзистора электрически подключен к первому уровню напряжения,

седьмой транзистор, причем затвор седьмого транзистора электрически подключен к стоку шестого транзистора, исток седьмого транзистора электрически подключен ко второму уровню напряжения, а сток седьмого транзистора электрически подключен к стоку пятого транзистора,

третий конденсатор, электрически подключенный между истоком и затвором седьмого транзистора,

восьмой транзистор, причем затвор и сток восьмого транзистора электрически подключены ко второму уровню напряжения, а исток восьмого транзистора электрически подключен к стоку шестого транзистора.

7. Жидкокристаллическое устройство отображения по п. 6, в котором первый уровень напряжения является уровнем высокого напряжения, а второй уровень напряжения является уровнем низкого напряжения.

8. Жидкокристаллическое устройство отображения по п. 7, в котором первый транзистор, второй транзистор, третий транзистор, четвертый транзистор, пятый транзистор, шестой транзистор, седьмой транзистор и восьмой транзистор являются МОП транзисторами р-типа.

| Колосоуборка | 1923 |

|

SU2009A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| US 7486269 B2, 03.02.2009 | |||

| US 7522145 B2, 21.04.2009 | |||

| УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2010 |

|

RU2494473C1 |

Авторы

Даты

2018-11-29—Публикация

2015-01-12—Подача