Область техники

[0001] Изобретение относится к области технологии жидкокристаллических дисплеев и, в частности, к схеме возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора.

Описание предшествующего уровня техники

[0002] Технология схемы GOA (возбуждение затвора на матрице) использует процесс подложек с активной матрицей для жидкокристаллического устройства отображения на основе тонкопленочных транзисторов (TFT) для того, чтобы изготовить схему возбуждения затвора на матричной подложке на основе тонкопленочных транзисторов и тем самым достигнуть непрерывного режима возбуждения сканирования.

[0003] Как правило, схема GOA в основном состоит из части повышающей напряжение, части управляющей повышением напряжения, передающей части, части понижающей напряжение, части удержания пониженного напряжения и части усиления, отвечающей за поднятие потенциала. Часть усиления, как правило, состоит из ускоряющего конденсатора.

[0004] Часть повышающая напряжение, в основном, отвечает за вывод входного сигнала синхронизации в затвор тонкопленочного транзистора в качестве возбуждающего сигнала устройства жидкокристаллического дисплея. Часть, управляющая повышением напряжения, в основном, отвечает за управление повышающей частью таким образом, чтобы она включалась, и, как правило, подчиняется управлению сигналом, переданному от схемы GOA предшествующего каскада. Часть, понижающая напряжение, в основном, отвечает за быстрое понижение сканирующего сигнала до низкого уровня напряжения после выхода сканирующего сигнала, т.е. понижение потенциала затвора тонкопленочного транзистора до низкого уровня напряжения. Часть удержания пониженного напряжения, в основном, отвечает за удержание сканирующего сигнала и сигнала части повышающей напряжение в выключенном состоянии (т.е. устанавливает отрицательный потенциал). Часть усиления, в основном, отвечает за поднятие потенциала части повышающей напряжение в очередной раз, для того чтобы гарантировать нормальный вывод сигналов части повышающей напряжение.

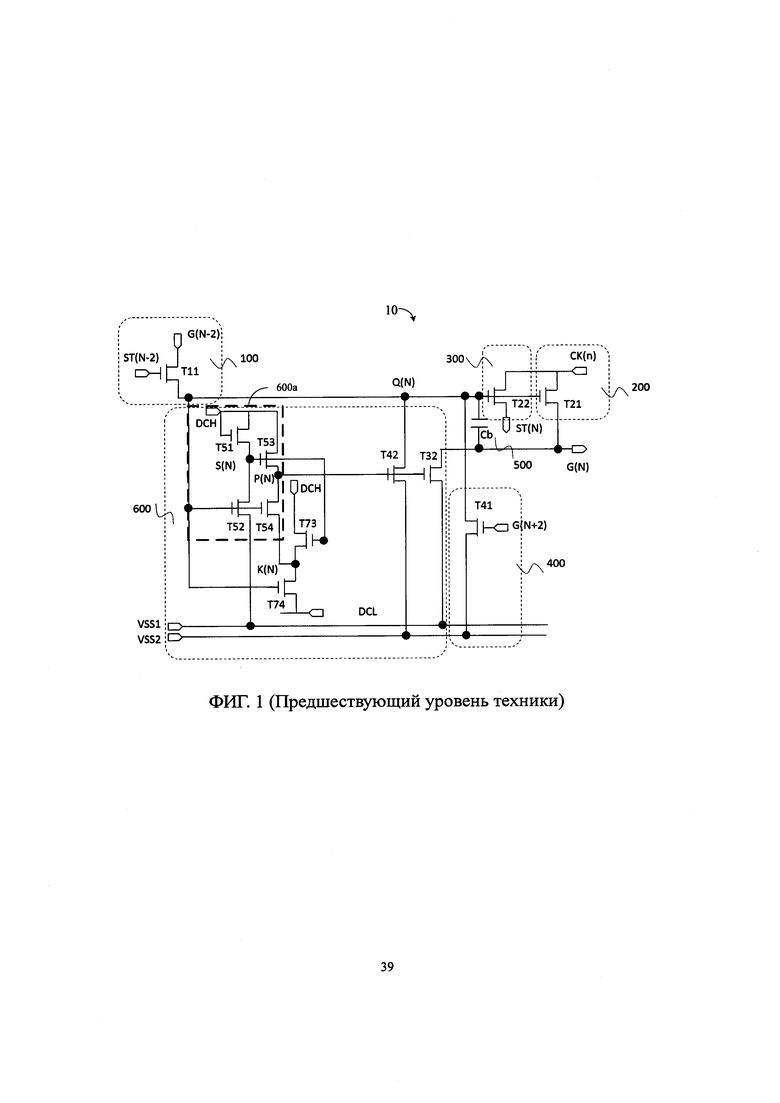

[0005] В предшествующем уровне техники (как показано на ФИГ. 1) схема возбуждения сканирования оксидного полупроводникового тонкопленочного транзистора представляет собой множество каскадов одинаковых схем GOA, соединенных каскадом, и части удержания пониженного напряжения схем GOA всех каскадов являются одинаковыми. Однако, поскольку каждая часть удержания пониженного напряжения включает в себя больше элементов TFT, это увеличит как пространство расположения GOA, так и энергопотребление схемы.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0006] Для того чтобы, по меньшей мере, частично решить вышеуказанные задачи, техническая задача, которая, в основном, должна решаться при помощи изобретения, состоит в том, чтобы обеспечить схему возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора, которая может достигнуть совместного использования схем удержания пониженного напряжения схем GOA множества каскадов и, вследствие этого, уменьшить количество элементов TFT для того, чтобы уменьшить как пространство расположения GOА, так и энергопотребление схемы.

[0007] Первое техническое решение, предложенное изобретением, заключается в том, чтобы обеспечить схему возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора. Схема возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора включает в себя P каскадно-соединенных блоков GOA. Каждый из блоков GOA включает в себя часть управляющую повышением напряжения, часть повышающую напряжение, передающую часть, первую часть понижающую напряжение, часть с ускоряющим конденсатором и часть с основным инвертором. Схема возбуждения сканирования дополнительно включает в себя общий вспомогательный инвертор, и часть с основным инвертором в каждом каскаде соединений электрически подключена к вспомогательному инвертору для формирования части удержания пониженного напряжения соответствующего одного из блоков GOA. P, N должны быть положительными целыми числами и N≤P. В N-м каскаде соединений часть с основным инвертором включает в себя: пятьдесят первый транзистор (Т51), причем затвор и сток пятьдесят первого транзистора оба электрически подключены к постоянному высокому потенциалу (DCH), и исток пятьдесят первого транзистора электрически подключен к четвертому узлу (S(N)); пятьдесят второй транзистор (Т52), причем затвор пятьдесят второго транзистора электрически подключен к первому узлу (Q(N)), сток пятьдесят второго транзистора электрически подключен к четвертому узлу (S(N)), и исток пятьдесят второго транзистора электрически подключен к первому отрицательному потенциалу (VSS1); пятьдесят третий транзистор (Т53), причем затвор пятьдесят третьего транзистора электрически подключен к четвертому узлу (S(N)), сток пятьдесят третьего транзистора электрически подключен к постоянному высокому потенциалу (DCH), и исток пятьдесят третьего транзистора электрически подключен ко второму узлу (P(N)); пятьдесят четвертый транзистор (Т54), причем затвор пятьдесят четвертого транзистора электрически подключен к первому узлу (Q(N)), сток пятьдесят четвертого транзистора электрически подключен ко второму узлу (P(N)), и исток пятьдесят четвертого транзистора электрически подключен к третьему узлу (K); вспомогательный инвертор включает в себя: семьдесят третий транзистор (Т73), причем затвор семьдесят третьего транзистора электрически подключен к четвертому узлу (S(1)) части с основным инвертором в первого каскаде соединений, и затвор семьдесят третьего транзистора электрически подключен к постоянному высокому потенциалу (DCH); семьдесят четвертый транзистор (Т74), причем затвор семьдесят четвертого транзистора электрически подключен к четвертому узлу (S(P)) части с основным инвертором в последнего каскаде соединений, затвор семьдесят четвертого транзистора электрически подключен к третьему узлу (K), и исток семьдесят четвертого транзистора электрически подключен к истоку семьдесят третьего транзистора (Т73); семьдесят пятый транзистор (Т75), причем затвор семьдесят пятого транзистора электрически подключен к первому узлу (Q(1)) части с основным инвертором в первом каскаде соединения, затвор семьдесят пятого транзистора электрически подключен к третьему узлу (K), и исток семьдесят пятого транзистора электрически подключен к постоянному низкому потенциалу (DCL); семьдесят шестой транзистор (Т76), причем затвор семьдесят шестого транзистора электрически подключен к первому узлу (Q(P)) части с основным инвертором в последнем каскаде соединения, затвор семьдесят шестого транзистора электрически подключен к постоянному низкому потенциалу (DCL), и исток семьдесят шестого транзистора электрически подключен к третьему узлу (K); часть повышающая напряжение включает в себя: двадцать первый транзистор (Т21), причем затвор двадцать первого транзистора электрически подключен к первому узлу (Q(N)), затвор двадцать первого транзистора электрически подключен к сигналу (CK(n)) синхронизации, и исток двадцать первого транзистора электрически подключен к выходу (G(N)); передающая часть включает в себя: двадцать второй транзистор (Т22), причем затвор двадцать второго транзистора электрически подключен к первому узлу (Q(N)), сток двадцать второго транзистора электрически подключен к сигналу (СK(М)) синхронизации, и исток двадцать второго транзистора электрически подключен к управляющему выходу (ST(N)). Первая кривая колебаний выходного сигнала первого узла (Q(1)) в первом каскаде соединения схемы возбуждения сканирования имеет форму  , вторая кривая колебаний выходного сигнала первого узла (Q(P)) в последнем каскаде соединения схемы возбуждения сканирования имеет форму

, вторая кривая колебаний выходного сигнала первого узла (Q(P)) в последнем каскаде соединения схемы возбуждения сканирования имеет форму  , и вспомогательный инвертор управляется в соответствии с сигналом, соответствующим перекрывающейся части первой кривой колебаний со второй кривой колебаний.

, и вспомогательный инвертор управляется в соответствии с сигналом, соответствующим перекрывающейся части первой кривой колебаний со второй кривой колебаний.

[0008] Второе техническое решение, предложенное изобретением, заключается в том, чтобы обеспечить схему возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора. Схема возбуждения сканирования содержит Р каскадно-соединенных блоков GOA, каждый из блоков GOA включает в себя часть управляющую повышением напряжения, часть повышающую напряжение, передающую часть, первую часть понижающую напряжение, часть с ускоряющим конденсатором и часть с основным инвертором. Схема возбуждения сканирования дополнительно включает в себя вспомогательный инвертор, и вспомогательный инвертор электрически подключен к части с основным инвертором в каждом каскаде соединения для формирования частей удержания повышенного напряжения для соответствующих блоков GOA. Р, N должны быть положительными целыми числами и N≤P. В N-м каскаде соединения часть с основным инвертором включает в себя: пятьдесят первый транзистор (Т51), причем затвор и сток пятьдесят первого транзистора оба электрически подключены к постоянному высокому потенциалу (DCH), и исток пятьдесят первого транзистора электрически подключен к четвертому узлу (S(N)); пятьдесят второй транзистор (Т52), причем затвор пятьдесят второго транзистора электрически подключен к первому узлу (Q(N)), сток пятьдесят второго транзистора электрически подключен к четвертому узлу (S(N)), и исток пятьдесят второго транзистора электрически подключен к первому отрицательному потенциалу (VSS1); пятьдесят третий транзистор (Т53), причем затвор пятьдесят третьего транзистора электрически подключен к четвертому узлу (S(N)), сток пятьдесят третьего транзистора электрически подключен к постоянному высокому потенциалу (DCH), и исток пятьдесят третьего транзистора электрически подключен ко второму узлу (P(N)); пятьдесят четвертый транзистор (Т54), причем затвор пятьдесят четвертого транзистора электрически подключен к первому узлу (Q(N)), сток пятьдесят четвертого транзистора электрически подключен ко второму узлу (P(N)); и исток пятьдесят четвертого транзистора электрически подключен к третьему узлу (K); вспомогательный инвертор включает в себя: семьдесят третий транзистор (Т73), причем затвор семьдесят третьего транзистора электрически подключен к четвертому узлу (S(1)) части с основным инвертором в первом каскаде соединения, и сток семьдесят третьего транзистора электрически подключен к постоянному высокому потенциалу (DCH); семьдесят четвертый транзистор (Т74), причем затвор семьдесят четвертого транзистора электрически подключен к четвертому узлу (S(P)) части с основным инвертором в последнем каскаде соединения, сток семьдесят четвертого транзистора электрически подключен к третьему узлу (K), и исток семьдесят четвертого транзистора электрически подключен к истоку семьдесят третьего транзистора; семьдесят пятый транзистор (Т75), причем затвор семьдесят пятого транзистора электрически подключен к первому узлу (Q(1)) части с основным инвертором в первом каскаде соединения, сток семьдесят пятого транзистора электрически подключен к третьему узлу (K), и исток семьдесят пятого транзистора электрически подключен к постоянному низкому потенциалу (DCL); семьдесят шестой транзистор (Т76), причем затвор семьдесят шестого транзистора электрически подключен к первому узлу (Q(P)) части с основным инвертором в последнем каскаде соединения, сток семьдесят шестого транзистора электрически подключен к постоянному низкому потенциалу (DCL), и исток семьдесят шестого транзистора электрически подключен к третьему узлу (K).

[0009] В варианте осуществления в N-м каскаде соединения часть повышающая напряжение включает в себя двадцать первый транзистор (Т21), причем затвор двадцать первого транзистора электрически подключен к первому узлу (Q(N)), сток двадцать первого транзистора электрически подключен к сигналу (CK(n)) синхронизации, и исток двадцать первого транзистора электрически подключен к выходу (G(N)); передающая часть включает в себя: двадцать второй транзистор (Т22), причем затвор двадцать второго транзистора электрически подключен к первому узлу (Q(N)), сток двадцать второго транзистора электрически подключен к сигналу (СK(М)) синхронизации, и исток двадцать второго транзистора электрически подключен к управляющему выходу (ST(N)); часть с ускоряющим конденсатором включает в себя конденсатор (Cb), причем вывод конденсатора электрически подключен к первому узлу (Q(N)), и другой вывод конденсатора электрически подключен к выходу (GOT).

[0010] В варианте осуществления, когда Р=3, сигнал (СK(М)) синхронизации содержит четыре сигнала синхронизации, включая в себя первый сигнал (СK(1)) синхронизации, второй сигнал (СK(2)) синхронизации, третий сигнал (СK(3)) синхронизации и четвертый сигнал (СK(4)) синхронизации.

[0011] В варианте осуществления, когда Р=5, сигнал (СK(М)) синхронизации содержит восемь сигналов синхронизации, включая в себя первый сигнал (СK(1)) синхронизации, второй сигнал (СK(2)) синхронизации, третий сигнал (СK(3)) синхронизации, четвертый сигнал (СK(4)) синхронизации, пятый сигнал (СK(5)) синхронизации, шестой сигнал (СK(6)) синхронизации, седьмой сигнал (СK(7)) синхронизации и восьмой сигнал (СK(8)) синхронизации.

[0012] В варианте осуществления коэффициент заполнения кривой колебания сигнала (СK(М)) синхронизации не больше, чем 25/75. Помимо всего прочего, когда Р=3, сигнал (СK(М)) синхронизации содержит четыре сигнала синхронизации, включая в себя первый сигнал (СK(1)) синхронизации, второй сигнал (СK(2)) синхронизации, третий сигнал (СK(3)) синхронизации и четвертый сигнал (СK(4)) синхронизации. Когда Р=5, сигнал синхронизации (СK(М)) содержит восемь сигналов синхронизации, включая в себя первый сигнал (СK(1)) синхронизации, второй сигнал (СK(2)) синхронизации, третий сигнал (СK(3)) синхронизации, четвертый сигнал (СK(4)) синхронизации, пятый сигнал (СK(5)) синхронизации, шестой сигнал (СK(6)) синхронизации, седьмой сигнал (СK(7)) синхронизации и восьмой сигнал (СK(8)) синхронизации.

[0013] В варианте осуществления коэффициент заполнения кривой колебания сигнала (СK(М)) синхронизации равен 25/75. Помимо всего прочего, когда Р=3, сигнал (СK(М)) синхронизации содержит четыре сигнала синхронизации, включая в себя первый сигнал (СK(1)) синхронизации, второй сигнал (СK(2)) синхронизации, третий сигнал (СK(3)) синхронизации и четвертый сигнал (СK(4)) синхронизации. Когда Р=5, сигнал (СK(М)) синхронизации содержит восемь сигналов синхронизации, включая в себя первый сигнал (СK(1)) синхронизации, второй сигнал (СK(2)) синхронизации, третий сигнал (СK(3)) синхронизации, четвертый сигнал (СK(4)) синхронизации, пятый сигнал (СK(5)) синхронизации, шестой сигнал (СK(6)) синхронизации, седьмой сигнал (СK(7)) синхронизации и восьмой сигнал (СK(8)) синхронизации.

[0014] В варианте осуществления первая кривая колебаний выходного сигнала первого узла (Q(1)) в первом каскаде соединения схемы возбуждения сканирования имеет форму  , вторая кривая колебаний выходного сигнала первого узла (Q(P)) в последнем каскаде соединения схемы возбуждения сканирования имеет форму

, вторая кривая колебаний выходного сигнала первого узла (Q(P)) в последнем каскаде соединения схемы возбуждения сканирования имеет форму  , и вспомогательный инвертор управляется в соответствии с сигналом, соответствующим перекрывающейся части первой кривой колебаний со второй кривой колебаний.

, и вспомогательный инвертор управляется в соответствии с сигналом, соответствующим перекрывающейся части первой кривой колебаний со второй кривой колебаний.

[0015] В варианте осуществления способ сдвига уровней, применяемый схемой возбуждения сканирования, заключается в том, что (N-2)-й каскад сдвигается на N-й каскад.

[0016] В варианте осуществления в первом каскаде соединения схемы возбуждения сканирования, затвор и сток одиннадцатого транзистора (Т11) электрически подключены к выводу сигнала стартового импульса (STV) схемы возбуждения сканирования.

[0017] В варианте осуществления в последнем каскаде соединения схемы возбуждения сканирования, затвор сорок первого транзистора (Т41) электрически подключен к выводу сигнала стартового импульса (STV) схемы возбуждения сканирования.

[0018] Эффект, который может достигаться изобретением, заключается в том, что: изобретение обеспечивает схему возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора, части удержания пониженного напряжения соответственно имеют основные инверторы и дополнительно имеют общий вспомогательный инвертор. Вспомогательный инвертор может соединяться с каждым из основных инверторов для формирования соответствующих частей удержания пониженного напряжения для схем GOA соответствующих каскадов для того, чтобы посредством этого достигнуть совместного использования частей удержания пониженного напряжения схем GOA множества каскадов, число/количество элементов TFT может уменьшаться и, вследствие этого, уменьшаются пространство расположения GOA и энергопотребление схемы.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0019] Для того чтобы более ясно проиллюстрировать технические решения различных вариантов осуществления настоящего изобретения, в описании вариантов осуществления будут использоваться чертежи и ниже будет дано их краткое описание. Очевидно, что чертежи в нижеследующем описании представляют собой только некоторые варианты осуществления изобретения, средний специалист в данной области техники может получить другие чертежи, соответствующие этим проиллюстрированным чертежам, без творческих усилий. На чертежах:

[0020] ФИГ. 1 представляет собой структурную схему блока GOA N-ого каскада схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора предшествующего уровня техники;

[0021] ФИГ. 2 представляет собой частичную структурную схему частей удержания пониженного напряжения схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора в первом варианте осуществления изобретения;

[0022] ФИГ. 3 представляет собой схематичное изображение установок для кривых колебаний и выходные кривые колебаний ключевых узлов схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора с частью удержания пониженного напряжения, показанной на ФИГ. 2;

[0023] ФИГ. 4 представляет собой частичную структурную схему частей удержания пониженного напряжения схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора во втором варианте осуществления изобретения; и

[0024] ФИГ. 5 представляет собой схематичное изображение установок для кривых колебаний и выходные кривые колебаний ключевых узлов схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора с частью удержания пониженного напряжения, показанной на ФИГ. 4.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0025] В последующем, со ссылкой на сопровождающие чертежи вариантов осуществления изобретения, технические решения в вариантах осуществления изобретения будут описаны ясно и полностью. Очевидно, что варианты осуществления изобретения, описанные ниже, представляют собой только часть вариантов осуществления изобретения, но не все варианты осуществления. На основе описанных вариантов осуществления изобретения, все другие варианты осуществления, полученные средним специалистом в данной области техники без творческого усилия, принадлежат объему защиты изобретения.

[0026] Со ссылкой на ФИГ. 1, показана структурная схема блока GOA N-го каскада схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора предшествующего уровня техники. Блок 10 GOA включает в себя часть 100 управляющую повышением напряжения, часть 200 повышающую напряжение, передающую часть 300, первую часть 400 понижающую напряжение, часть 500 с ускоряющим конденсатором и часть 600 удержания пониженного напряжения.

[0027] Конструкция и специальные соединения вышеуказанных частей представляют собой следующее:

[0028] Часть 100 управляющая повышением напряжения включает в себя одиннадцатый транзистор Т11. Затвор одиннадцатого транзистора Т11 электрически подключен к управляющему выходу ST(N-2) блока GOA второго предшествующего каскада (т.е. блоку GOA (N-2)-го каскада) блока GOA N-го каскада, сток одиннадцатого транзистора Т11 электрически подключен к выходу G(N-2) блока GOA (N-2)-го каскада, и исток одиннадцатого транзистора Т11 электрически подключен к первому узлу Q(N).

[0029] Часть 200 повышающая напряжение включает в себя двадцать первый транзистор Т21. Затвор двадцать первого транзистора Т21 электрически подключен к первому узлу Q(N), сток двадцать первого транзистора Т21 электрически подключен для приема сигнала СK(n) синхронизации, и исток двадцать первого транзистора Т21 электрически подключен к выходу G(N).

[0030] Передающая часть 300 включает в себя двадцать второй транзистор Т22. Затвор двадцать второго транзистора Т22 электрически подключен к первому узлу Q(N), сток двадцать второго транзистора Т22 электрически подключен для приема сигнала СK(n) синхронизации, и исток двадцать второго транзистора Т22 электрически подключен к управляющему выходу ST(N).

[0031] Первая часть 400 понижающая напряжение включает в себя сорок первый транзистор Т41. Затвор сорок первого транзистора Т41 электрически подключен к выходу G(N+2) блока GOA второго последующего каскада (т.е. блоку GOA (N+2)-го каскада) блока GOA N-го каскада, сток сорок первого транзистора Т41 электрически подключен к первому узлу Q(N), и исток сорок первого транзистора Т41 электрически подключен ко второму отрицательному потенциалу VSS2.

[0032] Часть 500 с ускоряющим конденсатором включает в себя конденсатор Cb. Вывод конденсатора Cb электрически подключен к первому узлу Q(N), и другой вывод конденсатора Cb электрически подключен к выходу G(N).

[0033] Часть 600 удержания пониженного напряжения включает в себя:

[0034] пятьдесят первый транзистор Т51, причем затвор и сток пятьдесят первого транзистора Т51 оба электрически подключены к постоянному высокому потенциалу DCH, и исток пятьдесят первого транзистора Т51 электрически подключен к четвертому узлу S(N);

[0035] пятьдесят второй транзистор Т52, причем затвор пятьдесят второго транзистора Т52 электрически подключен к первому узлу Q(N), сток пятьдесят второго транзистора Т52 электрически подключен к четвертому узлу S(N), и исток пятьдесят второго транзистора Т52 электрически подключен к первому отрицательному потенциалу VSS1;

[0036] пятьдесят третий транзистор Т53, причем затвор пятьдесят третьего транзистора Т53 электрически подключен к четвертому узлу S(N), сток пятьдесят третьего транзистора Т53 электрически подключен к постоянному высокому потенциалу DCH, и исток пятьдесят третьего транзистора Т53 электрически подключен ко второму узлу P(N);

[0037] пятьдесят четвертый транзистор Т54, причем затвор пятьдесят четвертого транзистора Т54 электрически подключен к первому узлу Q(N), сток пятьдесят четвертого транзистора Т54 электрически подключен ко второму узлу P(N), и исток пятьдесят четвертого транзистора Т54 электрически подключен к третьему узлу K(N);

[0038] семьдесят третий транзистор Т73, причем затвор семьдесят третьего транзистора Т73 электрически подключен к четвертому узлу S(N), сток семьдесят третьего транзистора Т73 электрически подключен к постоянному высокому потенциалу DCH, и исток семьдесят третьего транзистора Т73 электрически подключен к третьему узлу K(N);

[0039] семьдесят четвертый транзистор Т74, причем затвор семьдесят четвертого транзистора Т74 электрически подключен к первому узлу Q(N), сток семьдесят четвертого транзистора Т74 электрически подключен к третьему узлу K(N), и исток семьдесят четвертого транзистора Т74 электрически подключен к постоянному низкому потенциалу DCL;

[0040] сорок второй транзистор Т42, причем затвор сорок второго транзистора Т42 электрически подключен ко второму узлу P(N), сток сорок второго транзистора Т42 электрически подключен к первому узлу Q(N), и исток сорок второго транзистора Т42 электрически подключен ко второму отрицательному потенциалу VSS2; и

[0041] тридцать второй транзистор Т32, причем затвор тридцать второго транзистора Т32 электрически подключен ко второму узлу P(N), сток тридцать второго транзистора Т32 электрически подключен к выходу G(N), и исток тридцать второго транзистора Т32 электрически подключен к первому отрицательному потенциалу VSS1.

[0042] Со ссылкой на ФИГ. 2, показана частичная структурная схема частей удержания пониженного напряжения схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора в первом варианте осуществления изобретения. Схема возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора представляет собой схему возбуждения сканирования для тонкопленочного транзистора на основе оксидов индия-галлия-цинка (IGZO) и включает в себя Р каскадно-соединенных блоков GOA. Р, N являются положительными целыми числами, и N≤P. Со ссылкой совместно на ФИГ. 1 и ФИГ. 2, блок GOA N-го каскада включает в себя часть 100 управляющую повышением напряжения, часть 200 повышающую напряжение, передающую часть 300, первую часть 400 понижающую напряжение, часть 500 с ускоряющим конденсатором и часть 600 удержания пониженного напряжения.

[0043] Конструкция и специальные соединения вышеуказанных частей представляют собой следующее:

[0044] Часть 100 управляющая повышением напряжения включает в себя одиннадцатый транзистор Т11. Затвор одиннадцатого транзистора Т11 электрически подключен к управляющему выходу ST(N-2) блока GOA второго предшествующего каскада (т.е. блока GOA (N-2)-го каскада) блока GOA N-го каскада, сток одиннадцатого транзистора Т11 электрически подключен к выходу G(N-2) блока GOA второго предшествующего каскада (т.е. блок GOA (N-2)-го каскада) блока GOA N-го каскада, и исток одиннадцатого транзистора Т11 электрически подключен к первому узлу Q(N).

[0045] Часть 200 повышающая напряжение включает в себя двадцать первый транзистор Т21. Затвор двадцать первого транзистора Т21 электрически подключен к первому узлу Q(N), сток двадцать первого транзистора Т21 электрически подключен к сигналу СK(n) синхронизации, и исток двадцать первого транзистора Т21 электрически подключен к выходу G(N).

[0046] Передающая часть 300 включает в себя двадцать второй транзистор Т22. Затвор двадцать второго транзистора Т22 электрически подключен к первому узлу Q(N), сток двадцать второго транзистора Т22 электрически подключен к сигналу СK(М) синхронизации, и исток двадцать второго транзистора Т22 электрически подключен к управляющему выходу ST(N).

[0047] Первая часть 400 понижающая напряжение включает в себя сорок первый транзистор Т41. Затвор сорок первого транзистора Т41 электрически подключен к блоку GOA второго последующего каскада (т.е. блоку GOA (N+2)-го каскада) блока GOA N-го каскада, сток сорок первого транзистора Т41 электрически подключен к первому узлу Q(N), и исток сорок первого транзистора Т41 электрически подключен ко второму отрицательному потенциалу VSS2.

[0048] Часть 500 с ускоряющим конденсатором включает в себя конденсатор Сb. Вывод конденсатора Cb электрически подключен к первому узлу Q(N), и другой вывод конденсатора Cb электрически подключен к выходу G(N).

[0049] Часть 600 удержания пониженного напряжения включает в себя основной инвертор 600а, тридцать второй транзистор Т32 и сорок второй транзистор Т42. В частности, основной инвертор 600а включает в себя:

[0050] пятьдесят первый транзистор (Т51), причем затвор и сток пятьдесят первого транзистора (Т51) электрически подключены к постоянному высокому потенциалу (DCH), и исток пятьдесят первого транзистора (Т51) электрически подключен к четвертому узлу (S(N));

[0051] пятьдесят второй транзистор (Т52), причем затвор пятьдесят второго транзистора (Т52) электрически подключен к первому узлу (Q(N)), сток пятьдесят второго транзистора (Т52) электрически подключен к четвертому узлу (S(N)), и исток пятьдесят второго транзистора (Т52) электрически подключен к первому отрицательному потенциалу VSS1;

[0052] пятьдесят третий транзистор (Т53), причем затвор пятьдесят третьего транзистора электрически подключен к четвертому узлу (S(N)), сток пятьдесят третьего транзистора (Т53) электрически подключен к постоянному высокому потенциалу (DCH), и исток пятьдесят третьего транзистора (Т53) электрически подключен ко второму узлу (P(N));

[0053] пятьдесят четвертый транзистор (Т54), причем затвор пятьдесят четвертого транзистора электрически подключен к первому узлу (Q(N)), сток пятьдесят четвертого транзистора (Т54) электрически подключен ко второму узлу (P(N)), и исток пятьдесят четвертого транзистора (Т54) электрически подключен к третьему узлу (K);

[0054] Для сорок второго транзистора Т42, затвор сорок второго транзистора Т42 электрически подключен ко второму узлу P(N), сток сорок второго транзистора Т42 электрически подключен к первому узлу Q(N), и исток сорок второго транзистора Т42 электрически подключен ко второму отрицательному потенциалу VSS2.

[0055] Для тридцать второго транзистора Т32, затвор тридцать второго транзистора Т32 электрически подключен ко второму узлу P(N), сток тридцать второго транзистора Т32 электрически подключен к выходу G(N), и исток тридцать второго транзистора Т32 электрически подключен к первому отрицательному потенциалу VSS1.

[0056] Помимо всего прочего, блок GOA дополнительно включает в себя вспомогательный инвертор 700. Основной инвертор 600а в каждом каскаде соединения соединяется со вспомогательным инвертором 700, для того чтобы сформировать часть 600 удержания пониженного напряжения соответствующего блока GOA. Это означает, что части 600 удержания пониженного напряжения схем GOA множества каскадов совместно используют один и тот же вспомогательный инвертор 700.

[0057] В частности, вспомогательный инвертор 700 включает в себя:

[0058] семьдесят третий транзистор (Т73), причем затвор семьдесят третьего транзистора (Т73) электрически подключен к четвертому узлу (S(1)) основного инвертора в первом каскаде соединения, и сток семьдесят третьего транзистора (Т73) электрически подключен к постоянному высокому потенциалу (DCH);

[0059] семьдесят четвертый транзистор (Т74), причем затвор семьдесят четвертого транзистора (Т74) электрически подключен к четвертому узлу (S(P)) основного инвертора в последнем каскаде соединения, сток семьдесят четвертого транзистора (Т74) электрически подключен к третьему узлу (K), и исток семьдесят четвертого транзистора (Т74) электрически подключен к истоку семьдесят третьего транзистора (Т73);

[0060] семьдесят пятый транзистор (Т75), причем затвор семьдесят пятого транзистора (Т75) электрически подключен к первому узлу (Q(1)) основного инвертора в первом каскаде соединения, сток семьдесят пятого транзистора (Т75) электрически подключен к третьему узлу (K), и исток семьдесят пятого транзистора (Т75) электрически подключен к постоянному низкому потенциалу (DCL);

[0061] семьдесят шестой транзистор (Т76), причем его затвор электрически подключен к первому узлу (Q(P)) основного инвертора в последнем каскаде соединения, его сток электрически подключен к постоянному низкому потенциалу (DCL), и его исток электрически подключен к третьему узлу (K).

[0062] Соотношения между первым отрицательным потенциалом VSS1, вторым отрицательным потенциалом VSS2 и постоянным низким потенциалом следующие: постоянный низкий потенциал DCL <второго отрицательного потенциала VSS2 <первого отрицательного потенциала VSS1.

[0063] Способ сдвига уровней, применяемый схемой возбуждения сканирования, заключается в том, что (N-2)-й каскад сдвигается на N-й каскад.

[0064] В первом каскаде соединения схемы возбуждения сканирования затвор и сток одиннадцатого транзистора Т11 оба электрически подключены к выводу сигнала стартового импульса STV схемы.

[0065] Во втором каскаде соединения схемы возбуждения сканирования затвор и сток одиннадцатого транзистора Т11 оба электрически подключены к выводу сигнала стартового импульса STV схемы.

[0066] Во втором последнем каскаде соединения схемы возбуждения сканирования, затвор сорок первого транзистора Т41 электрически подключен к выводу сигнала стартового импульса STV схемы.

[0067] В первом последнем каскаде соединения схемы возбуждения сканирования, затвор сорок первого транзистора Т41 электрически подключен к выводу сигнала стартового импульса STV схемы.

[0068] В проиллюстрированном варианте осуществления Р=3, т.е. подключены блоки GOA трех каскадов. В каждом каскаде соединения основной инвертор 600а блока GOA каскада и вспомогательный инвертор 700 соединены для того, чтобы совместно сформировать соответствующую часть 600 удержания пониженного напряжения для блока GOA каскада; и в трех каскадах соединения требуемое количество транзисторов для формирования частей удержания пониженного напряжения для трех каскадов равняется 22. Однако в схеме возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора предшествующего уровня техники, как показано на ФИГ. 1, часть 600 удержания пониженного напряжения в каждом каскаде соединения является одинаковой и требует 8 штук транзисторов, вследствие чего требуемое количество транзисторов для формирования частей удержания пониженного напряжения для трех каскадов равняется 24. Соответственно, при помощи варианта осуществления изобретения, когда формируются три каскада соединения, количество транзисторов соответственно уменьшается на 2.

[0069] Помимо всего прочего, в этом варианте осуществления, первая часть 400 понижающая напряжение имеет только сорок первый транзистор Т41, который должен отвечать за понижение напряжения первого узла Q(N), и затвор сорок первого транзистора Т41 электрически подключен к выходу G(N+2) блока GOA (N+2)-го каскада, исток Т41 электрически подключен ко второму отрицательному потенциалу VSS2. Сигнал СK(n) синхронизации содержит четыре сигнала синхронизации: первый сигнал СK(1) синхронизации, второй сигнал СK(2) синхронизации, третий сигнал СK(3) синхронизации и четвертый сигнал СK(4) синхронизации, коэффициент заполнения сигнала СK(М) синхронизации установлен таким образом, чтобы не превышать 25/75, поскольку желательно гарантировать то, что кривая колебаний на первом узле Q(N) имеет форму  . Предпочтительно, коэффициент заполнения кривой колебаний сигнала СK(М) синхронизации равняется 25/75.

. Предпочтительно, коэффициент заполнения кривой колебаний сигнала СK(М) синхронизации равняется 25/75.

[0070] Принцип работы схемы возбуждения сканирования заключается в следующем:

[0071] В части 600 удержания пониженного напряжения пятьдесят первый транзистор Т51, пятьдесят второй транзистор Т52, пятьдесят третий транзистор Т53 и пятьдесят четвертый транзистор Т54 составляют основной инвертор 600а; функцией основного инвертора является управление двумя транзисторами, т.е. тридцать вторым транзистором Т32 и сорок вторым транзистором Т42. Функцией вспомогательного инвертора 700 является обеспечение основного инвертора 600а низким потенциалом в эффективный период и обеспечение основного транзистора 600а надлежащим высоким потенциалом в неэффективный период для снижения утечки электричества пятьдесят четвертого транзистора Т54, для того чтобы гарантировать то, что основной инвертор 600а может генерировать относительно высокий потенциал в неэффективный период.

[0072] В частности, в эффективный период вспомогательного инвертора 700, после того как вспомогательный инвертор 700 приводится в действие при помощи высокого/низкого напряжений, т.е. постоянного высокого потенциала DCH и постоянного низкого потенциала DCL, пятьдесят второй транзистор Т52 понижается до первого отрицательного потенциала VSS1, пятьдесят четвертый транзистор Т54 и семьдесят пятый транзистор Т75 включаются, когда первый узел Q(N) находится на высоком потенциале и понижает постоянный высокий потенциал DCH, вследствие чего третий узел K(N) находится на более низком потенциале, и второй P(N) также понижается на более низкий потенциал. Говоря другими словами, вспомогательный инвертор 700 обеспечивает основной инвертор 600а низким потенциалом в эффективный период, что может предотвратить появление утечки электричества тридцать второго Т32 и сорок второго транзистора Т42, вызванной физической характеристикой их пороговых напряжений, являющихся низкими или близкими к 0 В, и тем самым может гарантировать то, что часть 600 удержания пониженного напряжения в эффективный период может нормально осуществлять понижение напряжения.

[0073] В неэффективный период вспомогательного инвертора 700 пятьдесят второй транзистор Т52, пятьдесят четвертый транзистор Т54, семьдесят пятый транзистор Т75 и семьдесят шестой транзистор Т76 -все выключаются. Поскольку затвор пятьдесят четвертого транзистора Т54 электрически подключен к первому узлу Q(N), исток Т54 электрически подключен к третьему узлу K(N), затвор пятьдесят четвертого транзистора Т54 находится на отрицательном потенциал, и его исток находится на положительном потенциале, его Vgs представляет собой относительно сильно отрицательный потенциал, пятьдесят четвертый транзистор Т54 вполне может выключаться для снижения его утечки электричества, т.е. вспомогательный инвертор в неэффективный период обеспечивает почти высокий потенциал основному инвертору для снижения утечки электричества пятьдесят четвертого транзистора Т54, что может гарантировать то, что часть 600 удержания пониженного напряжения находится на относительно высоком потенциале в неэффективный период, и тем самым эффективно удерживает первый узел Q(N) и выходной вывод G(N) на низких потенциалах. В дополнение к этому, когда третий узел K(N) находится на высоком потенциале, существует функция резисторного делителя, потенциал на втором узле P(N) может усиливаться, чтобы стать выше, и тем самым может стабилизировать потенциал на втором узле P(N).

[0074] Пожалуйста, также сделайте ссылку на ФИГ. 3, где показано схематичное изображение установок для кривых колебаний и выходные кривые колебаний ключевых узлов схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора в первом варианте осуществления изобретения. STV является сигналом стартового импульса схемы, СK(1)-СK(4) являются сигналами синхронизации схемы. Как можно видеть на ФИГ. 3, каждый из коэффициентов заполнения проиллюстрированных кривых колебаний сигнала синхронизации в настоящем описании равняется 25/75, может гарантироваться то, что выходная кривая колебаний сигнала первого узла Q(N) имеет форму  . Другие кривые являются кривыми колебаний выходных сигналов, сгенерированными ключевыми узлами схемы. Из чертежа можно выяснить, что первая кривая колебаний выходного сигнала первого узла (Q(N)) в первом каскаде соединения схемы возбуждения сканирования имеет форму

. Другие кривые являются кривыми колебаний выходных сигналов, сгенерированными ключевыми узлами схемы. Из чертежа можно выяснить, что первая кривая колебаний выходного сигнала первого узла (Q(N)) в первом каскаде соединения схемы возбуждения сканирования имеет форму  , вторая кривая колебаний выходного сигнала первого узла (Q(N+2)) в последнем каскаде соединения имеет форму

, вторая кривая колебаний выходного сигнала первого узла (Q(N+2)) в последнем каскаде соединения имеет форму  , и соответствующий выход G(N) перекрывающейся части первой кривой колебаний со второй кривой колебаний нормально осуществляет выход сигналов. В неэффективный период первая кривая колебаний выходного сигнала первого узла (Q(N)) в первом каскаде соединения находится на низком потенциале, вторая кривая колебаний выходного сигнала первого узла (Q(N+2)) в последнем каскаде соединения также находится на низком потенциале, и в это время выход G(N) находится на низком потенциале.

, и соответствующий выход G(N) перекрывающейся части первой кривой колебаний со второй кривой колебаний нормально осуществляет выход сигналов. В неэффективный период первая кривая колебаний выходного сигнала первого узла (Q(N)) в первом каскаде соединения находится на низком потенциале, вторая кривая колебаний выходного сигнала первого узла (Q(N+2)) в последнем каскаде соединения также находится на низком потенциале, и в это время выход G(N) находится на низком потенциале.

[0075] Со ссылкой на ФИГ. 4, показана частичная структурная схема частей удержания пониженного напряжения схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора во втором варианте осуществления изобретения. В этом варианте осуществления Р=5, т.е. подключены блоки GOA пяти каскадов. В каждом каскаде соединения основной инвертор 600а каскада и вспомогательный инвертор 700 соединены для того, чтобы совместно сформировать соответствующую часть 600 удержания пониженного напряжения для каскада; и в пяти каскадах соединения требуемое количество транзисторов для формирования частей удержания пониженного напряжения пяти каскадов равняется 34. Однако в схеме возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора предшествующего уровня техники, как показано на ФИГ. 1, часть 600 удержания пониженного напряжения в каждом каскаде соединения является одинаковой и требует 8 штук транзисторов, вследствие чего требуемое количество транзисторов для формирования частей удержания пониженного напряжения для пяти каскадов равняется 40. Соответственно, при помощи этого варианта осуществления изобретения, когда формируются пять каскадов соединения, количество транзисторов соответственно уменьшается/сохраняется на 6.

[0076] Помимо всего прочего, Сигнал СK(М) синхронизации содержит восемь сигналов синхронизации: первый сигнал (СK(1)) синхронизации, второй сигнал (СK(2)) синхронизации, третий сигнал (СK(3)) синхронизации, четвертый сигнал (СK(4)) синхронизации, пятый сигнал (СK(5)) синхронизации, шестой сигнал (СK(6)) синхронизации, седьмой сигнал (СK(7)) синхронизации и восьмой сигнал (СK(8)) синхронизации. Аналогичным образом, коэффициент заполнения сигнала СK(М) синхронизации установлен таким образом, чтобы не превышать 25/75, для того чтобы гарантировать то, что кривая колебаний на первом узле Q(N) имеет форму  ; и предпочтительно, коэффициент заполнения кривой колебаний сигнала СK(М) синхронизации равняется 25/75. Помимо этих, на ФИГ. 4 одни и те же ссылочные номера, как и на ФИГ. 2, обозначают одни и те же конструкцию, каскады соединения, функции и принципы работы, и поэтому не будут повторяться в настоящем описании.

; и предпочтительно, коэффициент заполнения кривой колебаний сигнала СK(М) синхронизации равняется 25/75. Помимо этих, на ФИГ. 4 одни и те же ссылочные номера, как и на ФИГ. 2, обозначают одни и те же конструкцию, каскады соединения, функции и принципы работы, и поэтому не будут повторяться в настоящем описании.

[0077] Пожалуйста, также сделайте ссылку на ФИГ. 5, где показано схематичное изображение установок для кривых колебаний и выходные кривые колебаний ключевых узлов схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора во втором варианте осуществления изобретения. STV является сигналом стартового импульса схемы, СK(1)-СK(8) являются сигналами синхронизации схемы, и как видно на ФИГ. 5, каждый коэффициент заполнения проиллюстрированных кривых колебаний сигналов синхронизации равен 25/75, и таким образом, может гарантировать то, что выходная кривая колебаний сигнала на первом узле Q(N) имеет форму  . Другие кривые являются кривыми колебаний выходных сигналов, сгенерированных ключевыми узлами схемы. Из чертежа можно обнаружить, что: первая кривая колебаний выходного сигнала первого узла (Q(N)) в первом каскаде соединения схемы возбуждения сканирования имеет форму

. Другие кривые являются кривыми колебаний выходных сигналов, сгенерированных ключевыми узлами схемы. Из чертежа можно обнаружить, что: первая кривая колебаний выходного сигнала первого узла (Q(N)) в первом каскаде соединения схемы возбуждения сканирования имеет форму  , вторая кривая колебаний выходного сигнала первого узла (Q(N+4)) в последнем каскаде соединения имеет форму

, вторая кривая колебаний выходного сигнала первого узла (Q(N+4)) в последнем каскаде соединения имеет форму  , соответствующий выход G(N) перекрывающейся части первой кривой колебаний со второй кривой колебаний нормально осуществляет выход сигналов. В неэффективный период первая кривая колебаний выходного сигнала первого узла (Q(N)) в первом каскаде соединения находится на низком потенциале, вторая кривая колебаний выходного сигнала первого узла (Q(N+4)) в последнем каскаде соединения также находится на низком потенциале, и в это время выход G(N) находится на низком потенциале.

, соответствующий выход G(N) перекрывающейся части первой кривой колебаний со второй кривой колебаний нормально осуществляет выход сигналов. В неэффективный период первая кривая колебаний выходного сигнала первого узла (Q(N)) в первом каскаде соединения находится на низком потенциале, вторая кривая колебаний выходного сигнала первого узла (Q(N+4)) в последнем каскаде соединения также находится на низком потенциале, и в это время выход G(N) находится на низком потенциале.

[0078] Суммируя вышесказанное, изобретение обеспечивает схему возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора, части удержания повышенного напряжения схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора соответственно имеют основные инверторы и дополнительно имеют общий/совместно-используемый вспомогательный инвертор, вспомогательный инвертор может формировать соответствующую часть удержания пониженного напряжения с каждым основным инвертором, т.е. может достигнуть совместного использования частей удержания пониженного напряжения схем GOA множества каскадов, число/количество TFT может уменьшаться, и вследствие этого, могут уменьшаться как пространство расположения GOA, так и энергопотребление схемы.

[0079] Принимая во внимание то, что изобретение описывалось применительно к тому, что в настоящее время считается наиболее практичными и предпочтительными вариантами осуществления, следует понимать, что изобретение не следует ограничивать раскрытыми вариантами осуществления. Напротив, предполагается, что оно охватывает различные модификации и аналогичные приспособления, входящие в состав сущности и объема прилагаемой формулы изобретения, которая должна отвечать требованиям широчайшей интерпретации, для того чтобы сосредоточить в себе все подобные модификации и аналогичные конструкции.

Изобретение относится к области жидкокристаллических дисплеев. Технический результат заключается в снижении энергопотребления схемы возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора. Технический результат достигается за счет множества каскадно-соединенных блоков GOA и совместно-используемого вспомогательного инвертора. Каждый из блоков GOA включает в себя основной инвертор. Вспомогательный инвертор электрически подключен к каждому основному инвертеру для формирования соответствующих частей удержания пониженного напряжения для соответствующих блоков GOA. 2 н. и 13 з.п. ф-лы, 5 ил.

1. Схема возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора, содержащая множество Р каскадно-соединенных блоков GOA, каждый из которых содержит часть, управляющую повышением напряжения, часть, повышающую напряжение, передающую часть, первую часть, понижающую напряжение, часть с ускоряющим конденсатором и часть с основным инвертором, причем схема возбуждения сканирования дополнительно содержит общий вспомогательный инвертор, часть с основным инвертором в каждом каскаде соединения электрически подключена к вспомогательному инвертору для формирования части удержания пониженного напряжения соответствующего одного из блоков GOA; Р, N должны быть положительными целыми числами и N≤Р; в N-м каскаде соединения,

часть с основным инвертором содержит:

пятьдесят первый транзистор (Т51), затвор и сток которого электрически подключены к постоянному высокому потенциалу (DCH), а исток электрически подключен к четвертому узлу (S(N));

пятьдесят второй транзистор (Т52), затвор которого электрически подключен к первому узлу (Q(N)), сток электрически подключен к четвертому узлу (S(N)), а исток подключен к первому отрицательному потенциалу (VSS1);

пятьдесят третий транзистор (Т53), затвор которого электрически подключен к четвертому узлу (S(N)), сток электрически подключен к постоянному высокому потенциалу (DCH), а исток электрически подключен ко второму узлу (P(N));

пятьдесят четвертый транзистор (Т54), затвор которого электрически подключен к первому узлу (Q(N)), сток электрически подключен ко второму узлу (P(N)), а исток электрически подключен к третьему узлу (K);

вспомогательный инвертор содержит:

семьдесят третий транзистор (Т73), затвор которого электрически подключен к четвертому узлу (S(1)) части с основным инвертором в соединительной взаимосвязи первого уровня, а сток электрически подключен к постоянному высокому потенциалу (DCH);

семьдесят четвертый транзистор (Т74), затвор которого электрически подключен к четвертому узлу (S(P)) части с основным инвертором в последнем каскаде соединения, сток электрически подключен к третьему узлу (K), а исток электрически подключен к истоку семьдесят третьего транзистора (Т73);

семьдесят пятый транзистор (Т75), затвор которого электрически подключен к первому узлу (Q(1)) части с основным инвертором в первом каскаде соединения, сток электрически подключен к третьему узлу (K), а исток электрически подключен к постоянному низкому потенциалу (DCL);

семьдесят шестой транзистор (Т76), затвор которого электрически подключен к первому узлу (Q(P)) части с основным инвертором в последнем каскаде соединения, сток электрически подключен к постоянному низкому потенциалу (DCL), а исток электрически подключен к третьему узлу (K);

часть, повышающая напряжение, содержит:

двадцать первый транзистор (Т21), затвор которого электрически подключен к первому узлу (Q(N)), сток электрически подключен к сигналу синхронизации (CK(n)), а исток электрически подключен к выходу (G(N));

передающая часть содержит:

двадцать второй транзистор (Т22), затвор которого электрически подключен к первому узлу (Q(N)), сток электрически подключен к сигналу синхронизации (CK(М)), а исток электрически подключен к управляющему выходу (ST(N));

причем первая кривая колебаний выходного сигнала первого узла (Q(1)) в первом каскаде соединения схемы возбуждения сканирования имеет форму " ", вторая кривая колебаний выходного сигнала первого узла (Q(P)) в последнем каскаде соединения схемы возбуждения сканирования имеет форму "

", вторая кривая колебаний выходного сигнала первого узла (Q(P)) в последнем каскаде соединения схемы возбуждения сканирования имеет форму " ", а вспомогательный инвертор управляется в соответствии с сигналом, соответствующим перекрывающейся части первой кривой колебаний со второй кривой колебаний.

", а вспомогательный инвертор управляется в соответствии с сигналом, соответствующим перекрывающейся части первой кривой колебаний со второй кривой колебаний.

2. Схема возбуждения сканирования для оксидного полупроводникового тонкопленочного транзистора, содержащая множество Р каскадно-соединенных блоков GOA, каждый из блоков GOA содержит часть, управляющую повышением напряжения, часть, повышающую напряжение, передающую часть, первую часть, понижающую напряжение, часть с ускоряющим конденсатором и часть с основным инвертором, причем схема возбуждения сканирования дополнительно содержит вспомогательный инвертор, который электрически подключен к части каждого каскада соединения для формирования частей удержания повышенного напряжения для соответствующих блоков GOA; Р, N должны быть положительными целыми числами и N≤P; в N-м каскаде соединения,

часть с основным инвертором содержит:

пятьдесят первый транзистор (Т51), затвор и сток которого электрически подключены к постоянному высокому потенциалу (DCH), а исток электрически подключен к четвертому узлу (S(N));

пятьдесят второй транзистор (Т52), затвор которого электрически подключен к первому узлу (Q(N)), сток электрически подключен к четвертому узлу (S(N)), а исток электрически подключен к первому отрицательному потенциалу (VSS1);

пятьдесят третий транзистор (Т53), затвор которого электрически подключен к четвертому узлу (S(N)), сток электрически подключен к постоянному высокому потенциалу (DCH), а исток электрически подключен ко второму узлу (P(N));

пятьдесят четвертый транзистор (Т54), затвор которого электрически подключен к первому узлу (Q(N)), сток электрически подключен ко второму узлу (P(N)), а исток электрически подключен к третьему узлу (K);

вспомогательный инвертор содержит:

семьдесят третий транзистор (Т73), затвор которого электрически подключен к четвертому узлу (S(1)) части с основным инвертором первого каскада соединения, а сток электрически подключен к постоянному высокому потенциалу (DCH);

семьдесят четвертый транзистор (Т74), затвор которого электрически подключен к четвертому узлу (S(P)) части с основным инвертором последнего каскада соединения, сток электрически подключен к третьему узлу (K), а исток электрически подключен к истоку семьдесят третьего транзистора (Т73);

семьдесят пятый транзистор (Т75), затвор которого электрически подключен к первому узлу (Q(1)) части с основным инвертором первого каскада соединения, сток электрически подключен к третьему узлу (K), а исток электрически подключен к постоянному низкому потенциалу (DCL);

семьдесят шестой транзистор (Т76), затвор которого электрически подключен к первому узлу (Q(P)) части с основным инвертором последнего каскада соединения, сток электрически подключен к постоянному низкому потенциалу (DCL), а исток электрически подключен к третьему узлу (K).

3. Схема по п. 2, в которой в N-м каскаде соединения,

часть, повышающая напряжение, содержит двадцать первый транзистор (Т21), затвор которого электрически подключен к первому узлу (Q(N)), сток электрически подключен к сигналу синхронизации (CK(n)), а исток электрически подключен к выходу (G(N));

передающая часть содержит двадцать второй транзистор (Т22), затвор которого электрически подключен к первому узлу (Q(N)), сток электрически подключен к сигналу синхронизации (CK(М)), а исток электрически подключен к управляющему выходу (ST(N));

часть с ускоряющим конденсатором содержит конденсатор (Cb), вывод которого электрически подключен к первому узлу (Q(N)), а другой вывод электрически подключен к выходу (G(N)).

4. Схема по п. 3, в которой когда Р=3, сигнал синхронизации (CK(М)) содержит четыре сигнала синхронизации, включающие в себя первый сигнал синхронизации (CK(1)), второй сигнал синхронизации (CK(2)), третий сигнал синхронизации (CK(3)) и четвертый сигнал синхронизации (CK(4)).

5. Схема по п. 3, в которой, когда Р=5, сигнал синхронизации (CK(М)) содержит восемь сигналов синхронизации, включающих в себя первый сигнал синхронизации (CK(1)), второй сигнал синхронизации (CK(2)), третий сигнал синхронизации (CK(3)), четвертый сигнал синхронизации (CK(4)), пятый сигнал синхронизации (CK(5)), шестой сигнал синхронизации (CK(6)), седьмой сигнал синхронизации (CK(7)) и восьмой сигнал синхронизации (CK(8)).

6. Схема по п. 3, в которой коэффициент заполнения кривой колебания сигнала синхронизации (CK(М)) не больше чем 25/75.

7. Схема по п. 6, в которой, когда Р=3, сигнал синхронизации (CK(М)) содержит четыре сигнала синхронизации, включающих в себя первый сигнал синхронизации (CK(1)), второй сигнал синхронизации (CK(2)), третий сигнал синхронизации (CK(3)) и четвертый сигнал синхронизации (CK(4)).

8. Схема по п. 6, в которой когда Р=5, сигнал синхронизации (CK(М)) содержит восемь сигналов синхронизации, включающих в себя первый сигнал синхронизации (CK(1)), второй сигнал синхронизации (CK(2)), третий сигнал синхронизации (CK(3)), четвертый сигнал синхронизации (CK(4)), пятый сигнал синхронизации (CK(5)), шестой сигнал синхронизации (CK(6)), седьмой сигнал синхронизации (CK(7)) и восьмой сигнал синхронизации (CK(8)).

9. Схема по п. 3, в которой коэффициент заполнения кривой колебания сигнала синхронизации (CK(М)) равен 25/75.

10. Схема по п. 9, в которой, когда Р=3, сигнал синхронизации (CK(М)) содержит четыре сигнала синхронизации, включающих в себя первый сигнал синхронизации (CK(1)), второй сигнал синхронизации (CK(2)), третий сигнал синхронизации (CK(3)) и четвертый сигнал синхронизации (CK(4)).

11. Схема по п. 9, в которой когда Р=5, сигнал синхронизации (CK(М)) содержит восемь сигналов синхронизации, включающих в себя первый сигнал синхронизации (CK(1)), второй сигнал синхронизации (CK(2)), третий сигнал синхронизации (CK(3)), четвертый сигнал синхронизации (CK(4)), пятый сигнал синхронизации (CK(5)), шестой сигнал синхронизации (CK(6)), седьмой сигнал синхронизации (CK(7)) и восьмой сигнал синхронизации (CK(8)).

12. Схема по п. 2, в которой первая кривая колебаний выходного сигнала первого узла (Q(1)) первого каскада соединения схемы возбуждения сканирования имеет форму " ", вторая кривая колебаний выходного сигнала первого узла (Q(P)) последнего каскада соединения схемы возбуждения сканирования имеет форму "

", вторая кривая колебаний выходного сигнала первого узла (Q(P)) последнего каскада соединения схемы возбуждения сканирования имеет форму " ", а вспомогательный инвертор управляется в соответствии с сигналом, соответствующим перекрывающейся части первой кривой колебаний со второй кривой колебаний.

", а вспомогательный инвертор управляется в соответствии с сигналом, соответствующим перекрывающейся части первой кривой колебаний со второй кривой колебаний.

13. Схема по п. 2, в которой способ сдвига уровней, применяемый схемой возбуждения сканирования, заключается в том, что (N-2)-й каскад сдвигается на N-й каскад.

14. Схема по п. 2, в которой в первом каскаде соединения схемы возбуждения сканирования, затвор и сток одиннадцатого транзистора (Т11) электрически подключены к выводу сигнала стартового импульса (STV) схемы возбуждения сканирования.

15. Схема по п. 2, в которой в последнем каскаде соединения схемы возбуждения сканирования затвор сорок первого транзистора (Т41) электрически подключен к выводу сигнала стартового импульса (STV) схемы возбуждения сканирования.

| УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2009 |

|

RU2464647C1 |

| СХЕМА ВОЗБУЖДЕНИЯ ЛИНИЙ СИГНАЛА СКАНИРОВАНИЯ И УСТРОЙСТВО ОТОБРАЖЕНИЯ, ВКЛЮЧАЮЩЕЕ В СЕБЯ ДАННУЮ СХЕМУ | 2010 |

|

RU2514903C2 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Станок-качалка модернизированный | 2020 |

|

RU2747068C1 |

Авторы

Даты

2018-09-19—Публикация

2015-01-12—Подача