Изобретение относится к области микроэлектроники, а именно к радиационно-стойким КМОП элементам памяти многопортовых (один, два и более портов) ОЗУ, и может быть использовано при проектировании радиационно-стойких СБИС по субмикронным КМОП технологиям на объемном кремнии, в частности, СБИС типа «система-на-кристалле» для авионики, аэрокосмических и других применений.

Известны [патент США №6469328 В2, патент США №6909135 В2] конструктивно-топологические решения КМОП элементов памяти ОЗУ, занимающих минимальную площадь на кристалле, в которых отсутствуют контакты к подложке и «карману». В матрице элементов памяти данные контакты, подключенные к шинам нулевого потенциала и питания, расположены вне элементов памяти с шагом в несколько ячеек.

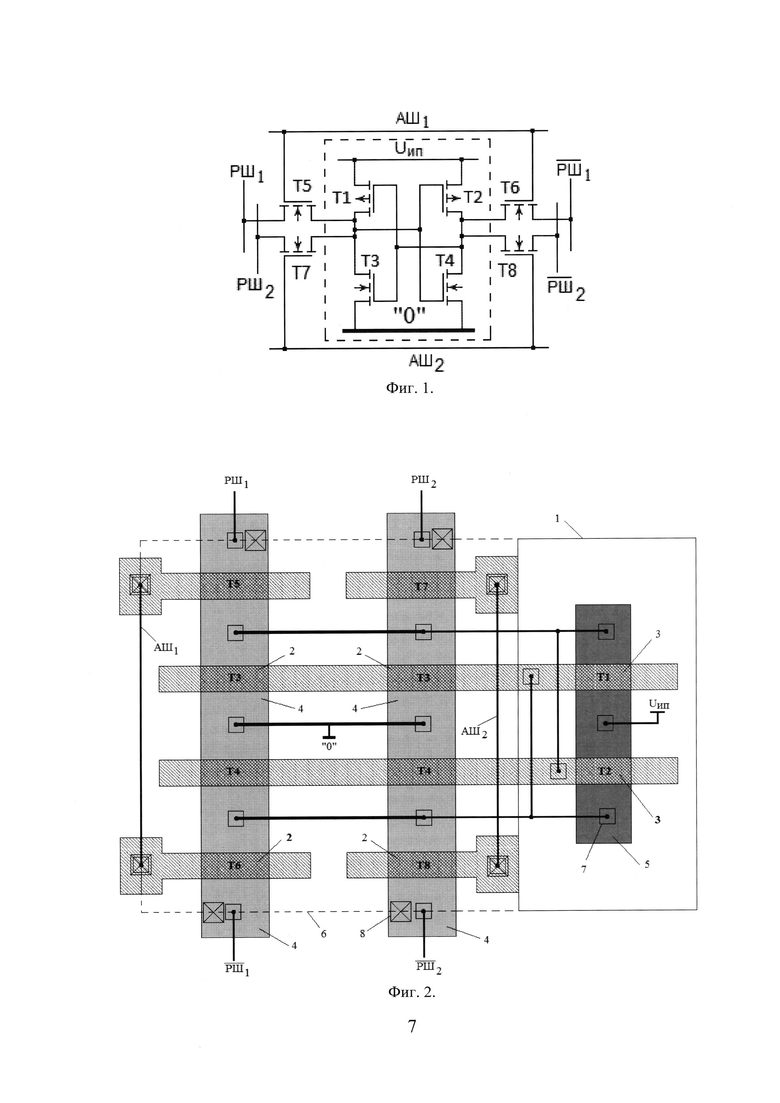

Конструктивно-топологические решения, выполненные согласно прототипу и изобретению, соответствуют стандартному 8-транзисторному (8Т) элементу памяти двухпортового (Фиг. 1) статического ОЗУ, в котором транзисторы T1, Т2, Т3, Т4 образуют триггер элемента памяти, а пары транзисторов Т5-Т6 и Т7-Т8 предназначены для записи и считывания информации в элемент памяти по первому и второму портам соответственно.

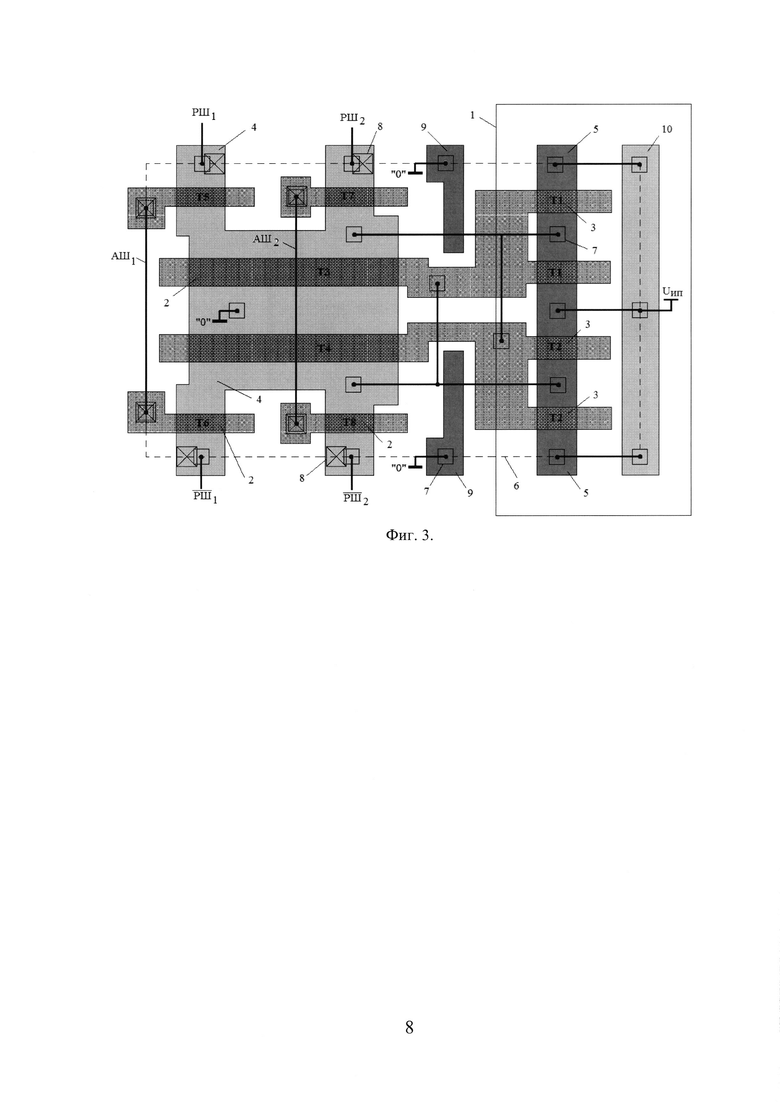

Наиболее близким к заявленному изобретению является элемент памяти, выполненный в соответствии с патентом США №6909135 В2. Конструкция двухпортового элемента памяти, разработанная в соответствии с этим патентом приведена на Фиг. 2, где показаны область 1 n-кармана, области 2 и 3 затворов n-канальных и p-канальных транзисторов соответственно, области 4 и 5 стоков/истоков n-канальных и p-канальных транзисторов соответственно, топологическая граница 6 элемента памяти, по которой стыкуются соседние элементы памяти, контакты 7 диффузии и поликремния к первому уровню металлизации, контакты 8 диффузии и поликремния ко второму и третьему уровням металлизации. Данный элемент памяти выбран в качестве прототипа заявленного изобретения.

Недостатком конструктивного решения элемента памяти прототипа является его низкая радиационная стойкость к ионизирующему излучению. Это связано со значительными утечками в области n-канальных транзисторов: между n+ областями стоков/истоков соседних транзисторов с разным потенциалом и между n-карманом и n+ областями стоков/истоков с нулевым потенциалом. Кроме того, такая конструкция элементов памяти обладает низкой стойкостью к эффекту «защелкивания» и к одиночным и многократным сбоям при воздействии тяжелых частиц.

Техническим результатом заявленного изобретения является создание радиационно-стойкого элемента памяти для статических оперативных запоминающих устройств на комплементарных металл-окисел-полупроводник транзисторах, выполненных по технологии объемного кремния, с повышенной стойкостью к внешним радиационным факторам, за счет наличия контактов p+ и n+ к подложке и «карману», подключенных к шинам нулевого потенциала и питания соответственно и располагающимся в каждом элементе матрицы памяти рядом с границей подложка-«карман», за счет увеличения длины и ширины канала n- и p-канальных транзисторов триггера элемента памяти, а также за счет выполнения p-канальных транзисторов триггера элемента памяти в виде двух параллельно соединенных транзисторов с общей p+ областью стоков.

Заявленный элемент памяти может быть использован для создания ОЗУ с одним, двумя и более числом портов. Высокая радиационная стойкость элемента памяти достигается за счет существенного снижения межприборной утечки между n-карманом и n+ областями стоков/истоков транзисторов n-типа триггера элемента памяти при воздействии ионизирующего излучения, а также исключения эффекта «защелкивания» в элементе памяти при воздействии тяжелых частиц.

Поставленный технический результат достигнут путем создания радиационно-стойкого элемента памяти для статических оперативных запоминающих устройств на комплементарных металл-окисел-полупроводник транзисторах, содержащий подложку p-типа и «карман» n-типа, активные области триггерных транзисторов n-типа и p-типа и управляющих транзисторов n-типов, отличающегося тем, что дополнительно содержит контакты p+ и n+ к подложке и к «карману», подключенные к шинам нулевого потенциала и питания соответственно и располагающиеся в каждом элементе матрицы памяти рядом с границей между подложкой и «карманом», при этом длина и ширина канала n-канальных и p-канальных транзисторов триггера элемента памяти увеличены, а p-канальные транзисторы триггера выполнены в виде двух параллельно соединенных транзисторов с общей p+ областью стоков.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

Фиг. 1. Схема восьмитранзисторного элемента памяти ОЗУ, выполненная согласно изобретению и прототипу.

Фиг. 2. Конструктивно-топологическая схема элемента памяти, выполненная согласно прототипу.

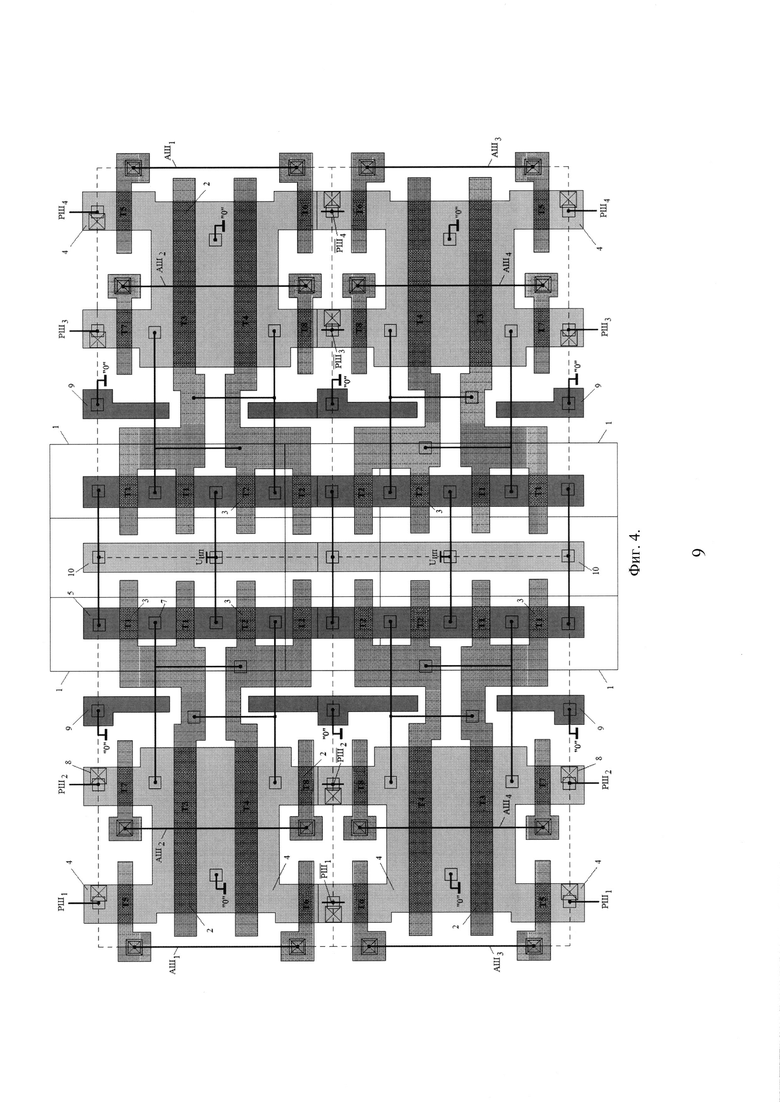

Фиг.3. Конструктивно-топологическая схема элемента памяти, выполненная согласно заявленному изобретению.

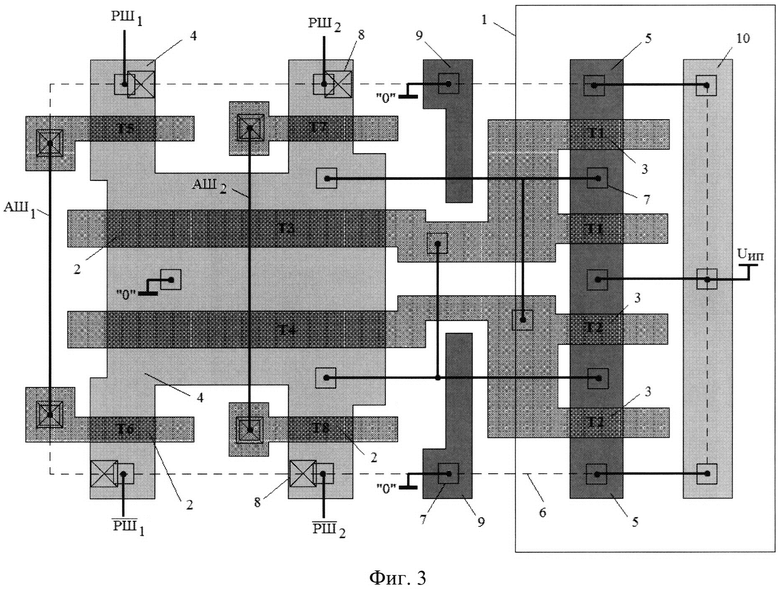

Фиг.4. Конструктивно-топологическая схема массива, состоящего из четырех элементов памяти, выполненная согласно изобретению.

Элементы:

T1-Т8 - транзисторы;

1 - область n-кармана;

2 - область затвора n-канального транзистора;

3 - область затвора p-канального транзистора;

4 - область стоков/истоков n-канального транзистора;

5 - область стоков/истоков p-канального транзистора;

6 - топологическая граница элемента памяти, по которой стыкуются соседние элементы памяти;

7 - контакты диффузии и поликремния к первому уровню металлизации;

8 - контакты диффузии и поликремния ко второму и третьему уровням металлизации;

9 - область p+ охраны;

10 - область n+ охраны.

Рассмотрим вариант выполнения заявленного радиационно-стойкого элемента памяти для статических оперативных запоминающих устройств на комплементарных металл-окисел-полупроводник транзисторах (Фиг. 3-4). В конструктивно-топологическом решении элемента памяти (Фиг. 3) p+ контакты подложки к шине нулевого потенциала располагаются вдоль границы «карман»-подложка без разрыва поликремниевых затворов транзисторов, что позволяет одновременно уменьшить ток утечки между областями стоков/истоков транзисторов Т3, Т4, Т7, Т8 и n-карманом после облучения и обеспечить высокую стойкость к «тиристорному» эффекту. Расположение сплошного n+ контакта к n-карману позволяет блокировать распространение избыточного заряда от попадания тяжелой заряженной частицы в соседние ячейки памяти и уменьшить кратность сбоев. Увеличенные геометрические размеры транзисторов T1, Т2, Т3, Т4 позволяют повысить ток хранения и внутренние узловые емкости, что способствует увеличению критического заряда, необходимого для возникновения сбоя. Транзисторы p-типа Т1 и Т2 при этом выполнены в виде двух параллельно соединенных транзисторов с общим стоком, что позволяет не увеличивать площадь чувствительной области и ячейки памяти. Увеличенная длина канала транзисторов T1, Т2, Т3, Т4 способствует уменьшению внутритранзисторных токов утечки, в том числе и после облучения.

На Фиг. 3 показаны область n-кармана 1, области 2 и 3 затворов n- и p-канальных транзисторов соответственно, области стоков/истоков 4 и 5n- и p-канальных транзисторов соответственно, топологическая граница 6 элемента памяти, по которой стыкуются соседние элементы памяти, контакты 7 диффузии и поликремния к первому уровню металлизации, контакты 8 диффузии и поликремния ко второму и третьему уровням металлизации. Все области 9 р+ охраны подключаются к шине нулевого потенциала, а области 10 n+ охраны - к шине питания, благодаря чему обеспечивается привязка подложки и области 1 n-кармана.

Испытания микросхем, разработанных с использованием сложно-функциональных блоков двухпортовых ОЗУ с предложенной ячейкой памяти, показали высокую дозовую стойкость и отсутствие тиристорного эффекта при воздействии тяжелых частиц во всем диапазоне линейных потерь энергии. Пороговое ЛПЭ одиночных сбоев при этом увеличилось в два раза, а многократные сбои в различных информационных битах не выявлены.

На Фиг. 4 показаны область n-кармана 1, области 2 и 3 затворов n- и p-канальных транзисторов соответственно, области 4 и 5 стоков/истоков n-канальных и p-канальных транзисторов соответственно, топологическая граница 6 элемента памяти, по которой стыкуются соседние элементы памяти, контакты 7 диффузии и поликремния к первому уровню металлизации, контакты 8 диффузии и поликремния ко второму и третьему уровням металлизации, контакты области 9 p+ охраны и области 10 n-кармана. Соседние элементы памяти соединены между собой для наращивания массивов по вертикали областями стоков транзисторов Т5, Т6, Т7 и Т8 и по горизонтали затворами транзисторов Т5 и Т6. Адресные шины (АШ) проведены горизонтально, при этом они соединяют элементы памяти в строках накопителя по соответствующим портам. Прямые и инверсные разрядные шины (РШ,  ) проведены вертикально, при этом они соединяют элементы памяти в столбцах накопителя по соответствующим портам.

) проведены вертикально, при этом они соединяют элементы памяти в столбцах накопителя по соответствующим портам.

Хотя описанный выше вариант выполнения изобретения был изложен с целью иллюстрации заявленного изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла заявленного изобретения, раскрытого в прилагаемой формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИАЦИОННО-СТОЙКИЙ ЭЛЕМЕНТ ПАМЯТИ ДЛЯ СТАТИЧЕСКИХ ОПЕРАТИВНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК ТРАНЗИСТОРАХ | 2018 |

|

RU2692307C1 |

| РАДИАЦИОННО-СТОЙКАЯ БИБЛИОТЕКА ЭЛЕМЕНТОВ НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК ТРАНЗИСТОРАХ | 2018 |

|

RU2674415C1 |

| РАДИАЦИОННО-СТОЙКАЯ БИБЛИОТЕКА ЭЛЕМЕНТОВ НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК ТРАНЗИСТОРАХ | 2013 |

|

RU2539869C1 |

| СИММЕТРИЧНЫЙ МУЛЬТИПЛЕКСОР НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК (КМОП) ТРАНЗИСТОРАХ | 2018 |

|

RU2689820C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ РАДИАЦИОННО-СТОЙКОЙ БИС | 2010 |

|

RU2434312C1 |

| БИКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1996 |

|

RU2106719C1 |

| Способ повышения радиационной стойкости микросхем статических ОЗУ на структурах "кремний на сапфире" | 2019 |

|

RU2727332C1 |

| СПОСОБ ФОРМИРОВАНИЯ КМОП-СТРУКТУР С ПОЛИКРЕМНИЕВЫМ ЗАТВОРОМ | 1992 |

|

RU2056673C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИКМОП ПРИБОРА | 1998 |

|

RU2141148C1 |

| СПОСОБ ФОРМИРОВАНИЯ КМОП-СТРУКТУР С ПОЛИКРЕМНИЕВЫМ ЗАТВОРОМ | 1992 |

|

RU2038647C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в создании радиационно-стойкого элемента памяти для статических оперативных запоминающих устройств на комплементарных металл-окисел-полупроводник транзисторах, выполненных по технологии объемного кремния, с повышенной стойкостью к внешним радиационным факторам. Радиационно-стойкий элемент памяти для статических оперативных запоминающих устройств на комплементарных металл-окисел-полупроводник транзисторах содержит подложку p-типа и «карман» n-типа, активные области триггерных транзисторов n-типа и p-типа и управляющих транзисторов n-типов, а также дополнительно содержит контакты p+ и n+ к подложке и к «карману», подключенные к шинам нулевого потенциала и питания соответственно и располагающиеся в каждом элементе матрицы памяти рядом с границей между подложкой и «карманом», при этом длина и ширина канала n-канальных и p-канальных транзисторов триггера элемента памяти увеличены, а p-канальные транзисторы триггера выполнены в виде двух параллельно соединенных транзисторов с общей p+ областью стоков. 4 ил.

Радиационно-стойкий элемент памяти для статических оперативных запоминающих устройств на комплементарных металл-окисел-полупроводник транзисторах, содержащий подложку p-типа и «карман» n-типа, активные области триггерных транзисторов n-типа и p-типа и управляющих транзисторов n-типов, отличающийся тем, что дополнительно содержит контакты p+ и n+ к подложке и к «карману», подключенные к шинам нулевого потенциала и питания соответственно и располагающиеся в каждом элементе матрицы памяти рядом с границей между подложкой и «карманом», при этом длина и ширина канала n-канальных и p-канальных транзисторов триггера элемента памяти увеличены, а p-канальные транзисторы триггера выполнены в виде двух параллельно соединенных транзисторов с общей p+ областью стоков.

| РАДИАЦИОННО-СТОЙКАЯ БИБЛИОТЕКА ЭЛЕМЕНТОВ НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК ТРАНЗИСТОРАХ | 2013 |

|

RU2539869C1 |

| US 6909135 B2, 21.06.2005 | |||

| РАДИАЦИОННО-СТОЙКАЯ ЭНЕРГОНЕЗАВИСИМАЯ ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 2014 |

|

RU2563548C2 |

| US 6656803 B2, 02.12.2003 | |||

| US 8497195 B2, 30.07.2013. | |||

Авторы

Даты

2018-12-13—Публикация

2018-02-27—Подача