Изобретение относится к области микроэлектроники, к асинхронным схемам, функционирование которых зависит от симметричности прохождения сигнала через цифровые элементы, а именно к мультиплексорам на комплементарных металл-окисел-полупроводник (КМОП) транзисторах, и может быть использовано в системах автоматизированного проектирования цифровых сверхбольших интегральных схем (СБИС), изготовленных по КМОП технологиям объемного кремния и содержащих схемы, функционирование которых зависит от симметричности прохождения сигнала через цифровые элементы.

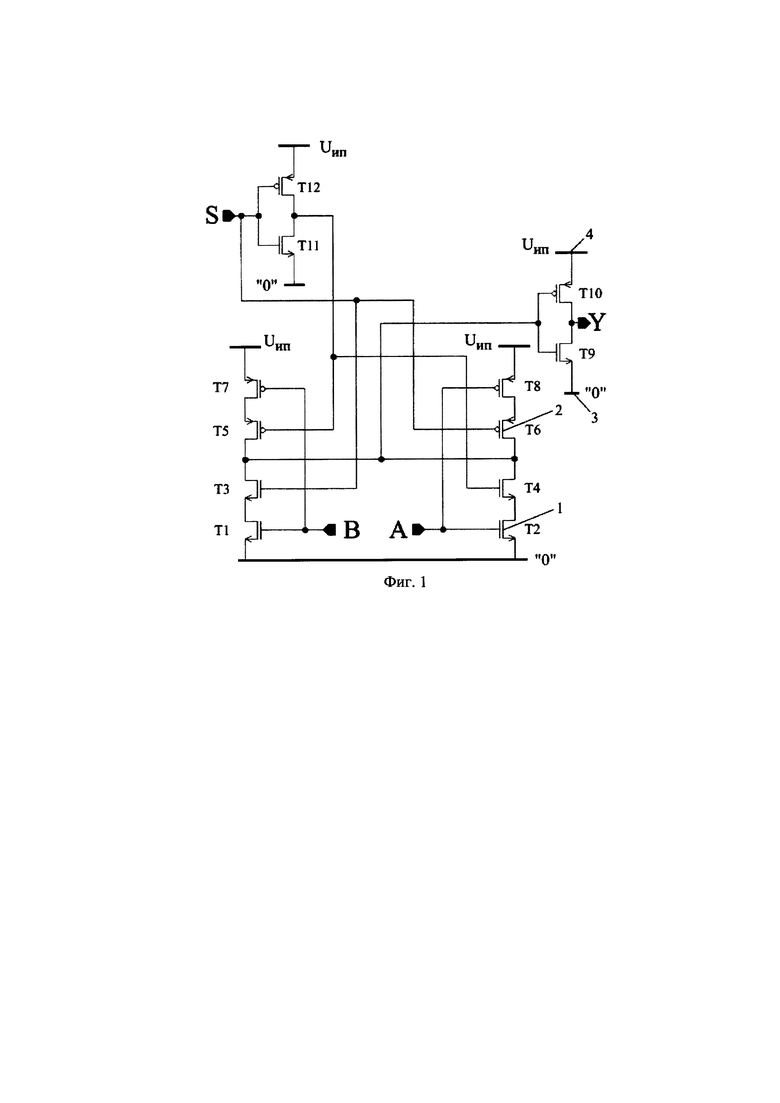

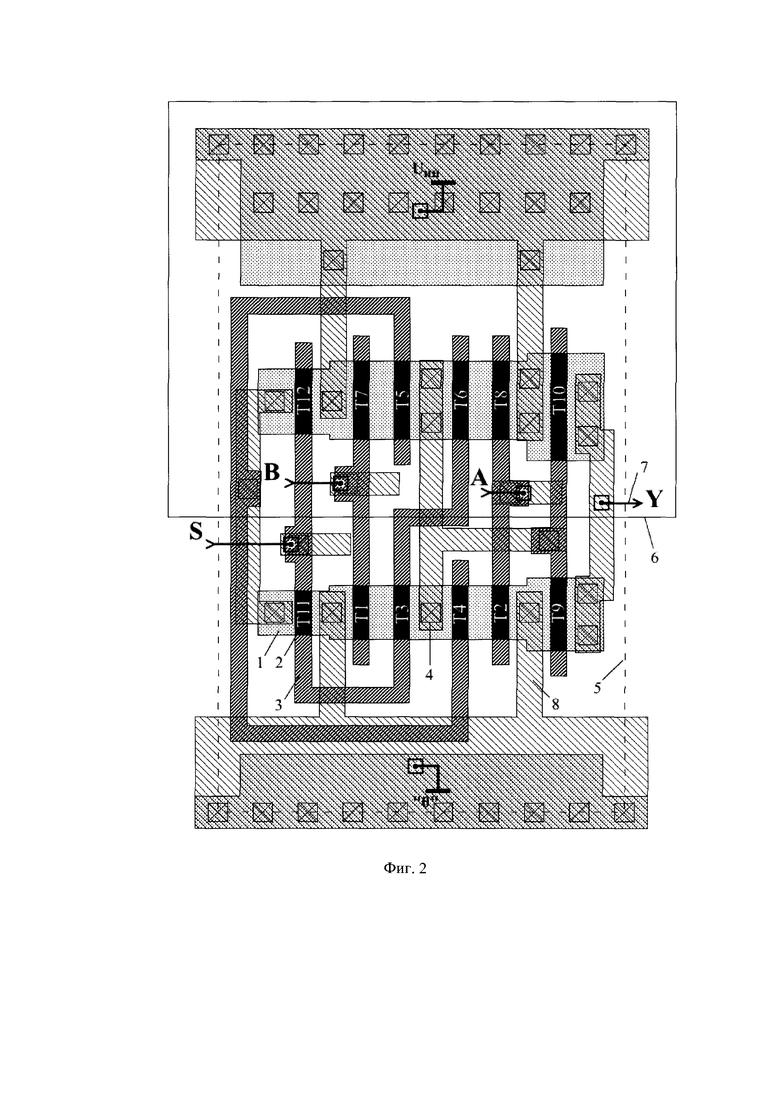

Наиболее близким к заявленному изобретению является мультиплексор на комплементарных металл-окисел-полупроводник (КМОП) транзисторах (Zimmermann R., Fichtner W. Low-Power Logic Styles: CMOS Versus Pass-Transistor Logic // IEEE journal of solid-state circuits. 1997. V. 32. N. 7. P. 1079-1090), имеющий два сигнальных входа, один вход управления и один выход. Такой мультиплексор имеет высокое быстродействие, занимает маленькую площадь на кристалле, однако имеет неидентичные задержки распространения сигналов от сигнальных входов до выхода. На Фиг. 1 и Фиг. 2 приведены соответственно электрическая схема и топология такого мультиплексора. На Фиг. 1 показаны n-канальные и р-канальные металл-окисел-полупроводник транзисторы 1 и 2, шина 3 нулевого потенциала (земля), шина 4 питающего напряжения. На Фиг. 2 показаны активные области 1, области 2 канала и области 3 затворов транзисторов, контакты 4 активной области 1 к первому уровню металлизации 8, топологическая граница 5 элемента (мультиплексора), по которой стыкуются соседние цифровые элементы, область 6 кармана, условное обозначение электрической связи 7. Данный мультиплексор выбран в качестве прототипа заявленного изобретения.

Недостатком мультиплексора-прототипа является низкое качество коммутации сигналов, вследствие низкой степень идентичности задержек распространения сигналов от сигнальных входов А и В до выхода Y.

Техническим результатом заявленного изобретения является создание симметричного мультиплексора на комплементарных металл-окисел-полупроводник (КМОП) транзисторах, имеющего два сигнальных входа, один вход управления, один выход и выполненного в виде элемента библиотеки стандартных цифровых элементов (СЦЭ), с более высоким качеством коммутации сигналов, за счет более высокой степени идентичности задержек распространения сигналов от сигнальных входов до выхода, вследствие симметрии топологических слоев, которая обеспечивает идентичность паразитных емкостей и сопротивлений и их нахождение в одинаковых электрических режимах; вследствие установки на управляющем входе мультиплексора дополнительных буферных каскадов, с целью обеспечения независимости задержек распространения сигналов от параметров драйвера управляющего входа; а также вследствие увеличения размеров транзисторов, с целью уменьшения влияния локальных внутрикристалльных вариаций на идентичность задержек распространения сигналов.

Поставленный технический результат достигнут путем создания симметричного мультиплексора на комплементарных металл-окисел-полупроводник (КМОП) транзисторах, содержащего девять р-канальных транзисторов и девять n-канальных транзисторов, причем затворы первого р-канального и первого n-канального транзисторов Т7 и Т1 подключены к информационному (сигнальному) входу В; затворы второго р-канального и второго n-канального транзисторов Т8 и Т2 подключены к информационному (сигнальному) входу А; затворы третьего р-канального, третьего n-канального, четвертого р-канального и четвертого n-канального транзисторов Т12, Т11, Т18 и Т17 подключены к управляющему входу S; стоки третьего р-канального и третьего n-канального транзисторов Т12 и Т11 объединены с затворами пятого р-канального, пятого n-канального и седьмого р-канального транзисторов Т14, Т13 и Т5; стоки четвертого р-канального и четвертого n-канального транзисторов Т18 и Т17 объединены с затворами шестого р-канального, шестого n-канального и восьмого n-канального транзисторов Т16, Т15 и Т4; стоки пятого р-канального и пятого n-канального транзисторов Т14 и Т13 подключены к затвору седьмого n-канального транзистора Т3; стоки шестого р-канального и шестого n-канального транзисторов Т16 и Т15 подключены к затвору восьмого р-канального транзистора Т6; стоки первого р-канального и первого n-канального транзисторов Т7 и Т1 подключены соответственно к истокам седьмого р-канального и седьмого n-канального транзисторов Т5 и Т3; стоки второго р-канального и второго n-канального транзисторов Т8 и Т2 подключены соответственно к истокам восьмого р-канального и восьмого n-канального транзисторов Т6 и Т4; стоки седьмого р-канального, седьмого n-канального, восьмого р-канального и восьмого n-канального транзисторов Т5, Т3, Т6 и Т4 объединены с затворами девятого р-канального и девятого n-канального транзисторов Т10 и Т9; стоки девятого р-канального и девятого n-канального транзисторов Т10 и Т9 подключены к выходу Y; истоки первого, второго, третьего, четвертого, пятого, шестого и девятого р-канальных транзисторов Т7, Т8, Т12, Т18, Т14, Т16 и Т10 подключены к шине питающего напряжения; истоки первого, второго, третьего, четвертого, пятого, шестого и девятого n-канальных транзисторов T1, Т2, T11, Т17, Т13, Т15 и Т9 подключены к шине нулевого потенциала (земле).

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

Фиг. 1. Электрическая схема мультиплексора на комплементарных металл-окисел-полупроводник (КМОП) транзисторах, выполненная согласно прототипу.

Фиг. 2. Конструктивно-топологическая схема мультиплексора на комплементарных металл-окисел-полупроводник (КМОП) транзисторах, выполненная согласно прототипу.

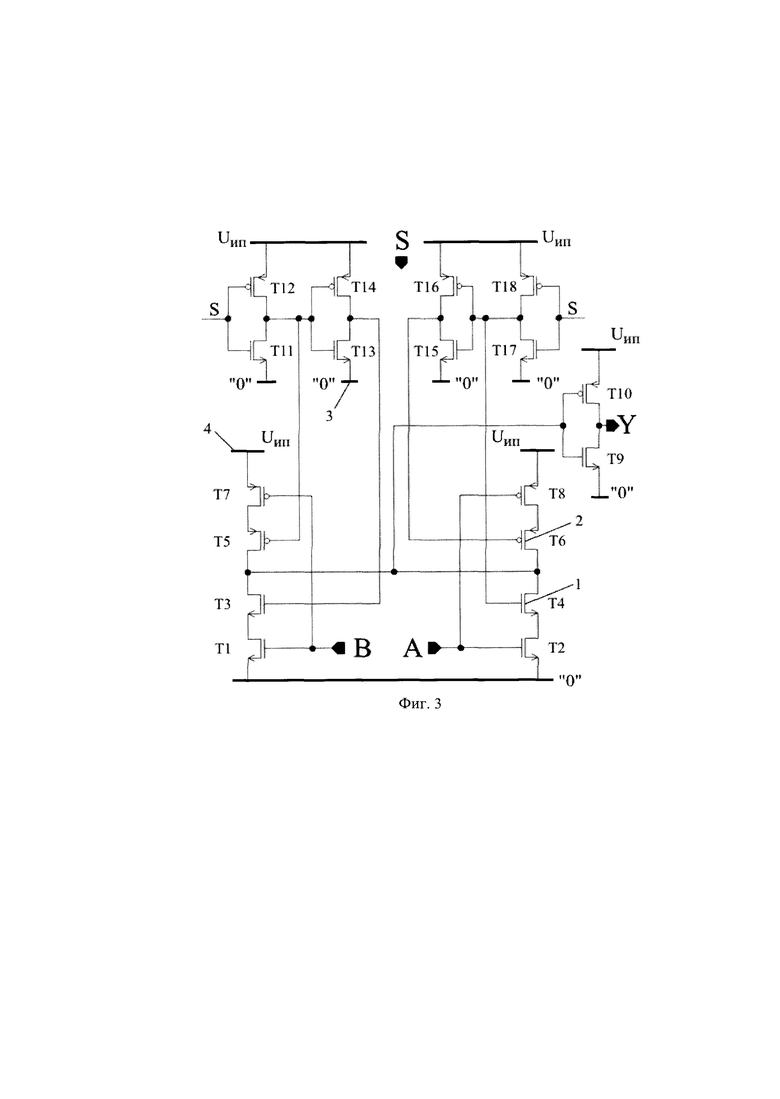

Фиг. 3. Общая электрическая схема мультиплексора на комплементарных металл-окисел-полупроводник (КМОП) транзисторах, выполненная согласно изобретению.

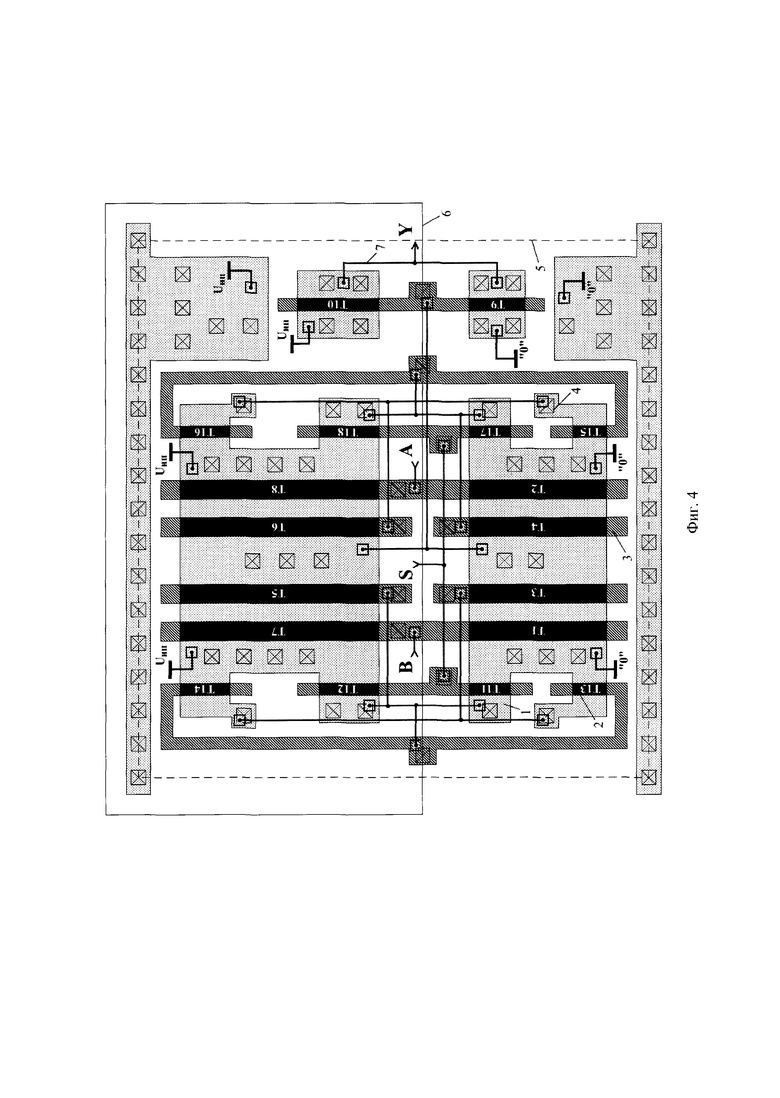

Фиг. 4. Общая конструктивно-топологическая схема мультиплексора на комплементарных металл-окисел-полупроводник (КМОП) транзисторах, выполненная согласно изобретению.

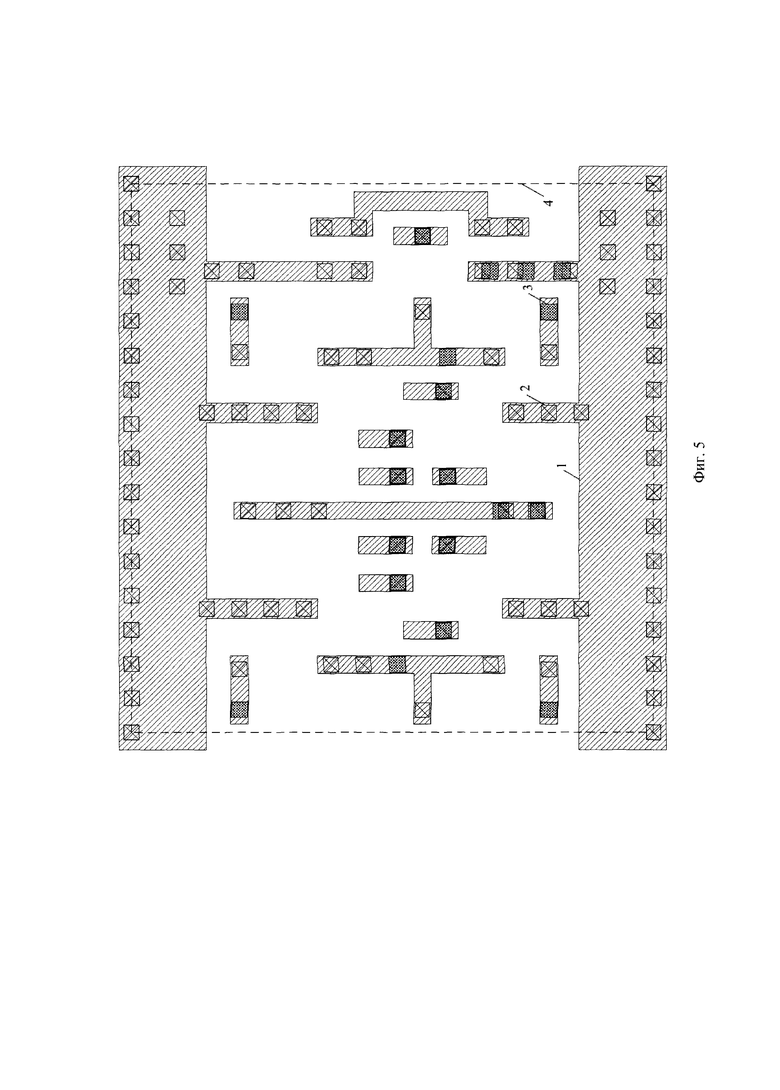

Фиг. 5. Конструктивно-топологическая схема мультиплексора на комплементарных металл-окисел-полупроводник (КМОП) транзисторах, выполненная согласно изобретению, на которой показаны первый уровень металлизации и его контакты к активной области и к второму уровню металлизации, а также топологическая граница элемента (мультиплексора).

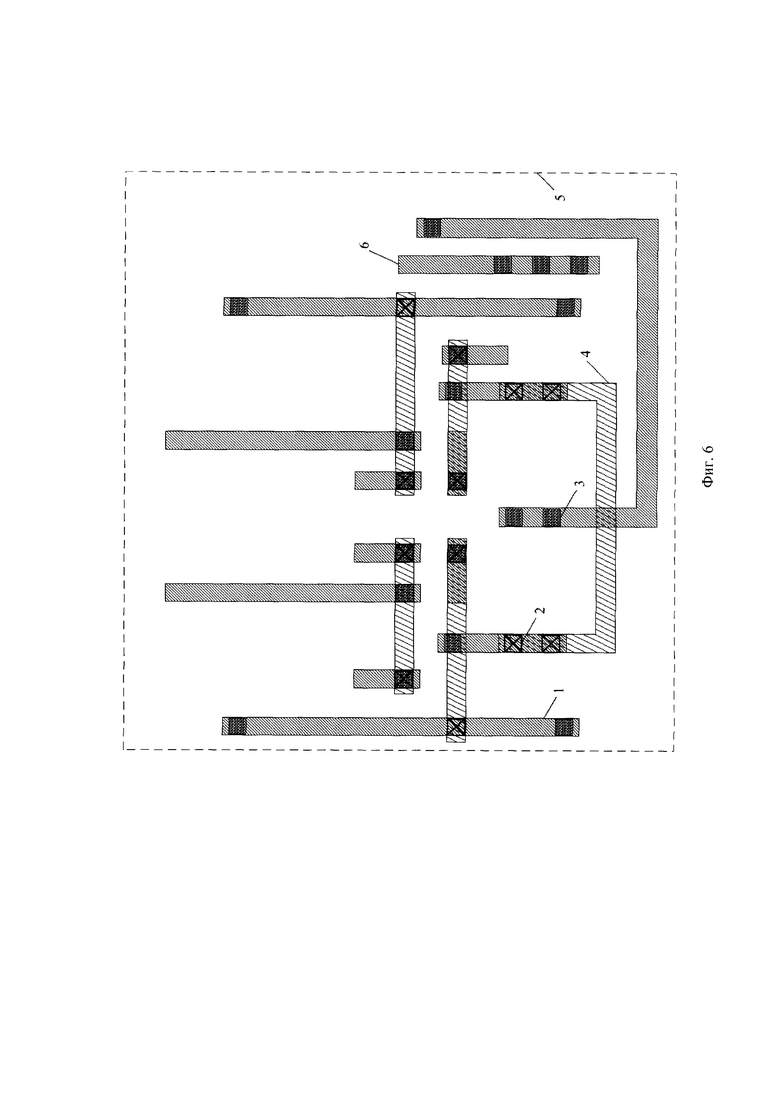

Фиг. 6. Конструктивно-топологическая схема мультиплексора на комплементарных металл-окисел-полупроводник (КМОП) транзисторах, выполненная согласно изобретению, на которой показаны второй уровень металлизации и его контакты к первому и третьему уровню металлизации, а также третий уровень металлизации и топологическая граница элемента (мультиплексора).

Рассмотрим более подробно вариант выполнения заявленного симметричного мультиплексора на комплементарных металл-окисел-полупроводник (КМОП) транзисторах (Фиг. 3-6).

На Фиг. 3 показаны n- 1 и р-канальный 2 металл-окисел-полупроводник транзисторы, шина 3 нулевого потенциала (земля), шина питающего напряжения 4. Данная схема мультиплексора содержит девять р-канальных и девять n-канальных транзисторов, причем затворы транзисторов Т7 и Т1 подключены к информационному (сигнальному) входу В; затворы транзисторов Т8 и Т2 подключены к информационному (сигнальному) входу А; затворы транзисторов Т12, T11, Т18 и Т17 подключены ко входу управления S; стоки транзисторов Т12 и Т11 объединены с затворами транзисторов Т14, Т13 и Т5; стоки транзисторов Т18 и Т17 объединены с затворами транзисторов Т16, Т15 и Т4; стоки транзисторов Т14 и Т13 подключены к затвору транзистора Т3; стоки транзисторов Т16 и Т15 подключены к затвору транзистора Т6; стоки транзисторов Т7 и Т1 подключены соответственно к истокам транзисторов Т5 и Т3; стоки транзисторов Т8 и Т2 подключены соответственно к истокам транзисторов Т6 и Т4; стоки транзисторов Т5, Т3, Т6 и Т4 объединены с затворами транзисторов Т10 и Т9; стоки транзисторов Т10 и Т9 подключены к выходу Y; истоки транзисторов Т7, Т8, Т12, Т18, Т14, Т16 и Т10 подключены к шине питающего напряжения; истоки транзисторов T1, Т2, T11, Т17, Т13, Т15 и Т9 подключены к шине нулевого потенциала (земле).

В предложенном варианте мультиплексора сигнал с управляющего входа S поступает на два параллельно расположенных инвертора T11, Т12 и Т17, Т18, после чего инверсный управляющий сигнал поступает на соответствующие управляющие транзисторы Т5 и Т4 и инверторы Т13, Т14 и Т15, Т16, подключенные к соответствующим управляющим транзисторам Т3 и Т6. Транзисторы Т3, Т5 и Т4, Т6 блокируют, либо пропускают сигналы, поступающие соответственно со входов данных В и А через транзисторы T1, Т7 и Т2, Т8 в зависимости от логического уровня на управляющем входе S. Далее сигнал со стоков Т3, Т5, Т4, Т6 поступает на выход Y через инвертирующий каскад Т9, Т10.

В отличие от прототипа, сигнал с управляющего входа S подают на управляющие транзисторы не напрямую, а через буферизующие инверторы, которые изолируют транзисторы Т5 и Т6 от драйвера управляющего входа S, тем самым устраняя один из источников разности задержек. Кроме того, в данном изобретении входной каскад инверторов на управляющем входе S дублирован для обеспечения возможности симметричной трассировки сигналов к управляющим транзисторам.

На Фиг. 4 показаны активная область (ионная имплантация) 1, область канала 2 и затвора 3 транзистора, контакт 4 активной области к первому уровню металлизации, топологическая граница 5, область 6 кармана, условное обозначение электрической связи 7, области р+ и n+ не показаны. В конструктивно-топологическом решении заявленного мультиплексора транзисторы и их затворы расположены симметрично, обеспечивая возможность симметричной трассировки линий металлизации (Фиг. 5 и 6). Такое расположение топологических структур обеспечивает идентичность паразитных параметров топологии и их электрических режимов при распространении сигнала со входов А (при низком уровне на входе S) и В (при высоком уровне на входе S) на выход Y. Также, в отличие от имеющегося прототипа, площадь каналов транзисторов T1 - Т8 увеличена для снижения влияния локальных технологических вариаций на кристалле на параметры этих транзисторов, а, следовательно, и на дисперсию разности задержек.

На Фиг. 5 показаны первый уровень металлизации 1, его контакты к активной области и второму уровню металлизации соответственно 2 и 3, Граница 4.

На Фиг. 6. показаны второй уровень металлизации 1, его контакты к третьему и первому уровню металлизации соответственно 2 и 3, третий уровень металлизации 4 и топологическая граница 5. Цифрой 6 обозначена линия металлизации, подключенная к нулевому потенциалу. Наличие этой линии обеспечивает независимость электрического режима паразитных параметров линии, объединяющей стоки транзисторов Т3-Т6 и затворы транзисторов Т9, Т10, от сигнала на входе S.

Результаты SPICE моделирования заявленного мультиплексора с учетом паразитных параметров топологии и возможных технологических вариаций показали, что максимальная разность задержек уменьшается примерно в 10 раз по сравнению с прототипом.

Заявленное изобретение может быть использовано для создания мультиплексоров с большим количеством входов. Конструктив заявленного мультиплексора с двумя сигнальными входами, одним входом управления и одним выходом позволяет использовать его в качестве элемента библиотеки стандартных цифровых элементов (СЦЭ). Идентичность задержек распространения сигналов от входов до выхода заявленного мультиплексора достигается за счет следующих особенностей. Симметрия топологических слоев обеспечивает идентичность паразитных емкостей и сопротивлений и их нахождение в одинаковых электрических режимах. На вход управления мультиплексора установлены дополнительные буферные каскады для обеспечения независимости задержек от параметров драйвера этого входа. При этом размеры транзисторов увеличены для уменьшения влияния локальных внутрикристалльных вариаций на идентичность задержек.

Хотя описанный выше вариант выполнения изобретения был изложен с целью иллюстрации заявленного изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла заявленного изобретения, раскрытого в прилагаемой формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

| РЕГИСТР СДВИГА, СХЕМА УПРАВЛЕНИЯ ЗАТВОРОМ ПОЭТАПНОГО СДВИГА И ПАНЕЛЬ ОТОБРАЖЕНИЯ | 2014 |

|

RU2658887C1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ПАТОЛОГИИ ПОЗВОНОЧНИКА | 2009 |

|

RU2405417C1 |

| РАДИАЦИОННО-СТОЙКИЙ ЭЛЕМЕНТ ПАМЯТИ ДЛЯ СТАТИЧЕСКИХ ОПЕРАТИВНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК ТРАНЗИСТОРАХ | 2018 |

|

RU2674935C1 |

| РЕГУЛИРУЕМЫЙ ПРЕЦИЗИОННЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ДВУПОЛЯРНЫМ ВЫХОДОМ | 1991 |

|

RU2037871C1 |

| АВТОМАТИЧЕСКИЙ КОНТРОЛЬНО-ПРОПУСКНОЙ ПУНКТ | 1973 |

|

SU399890A1 |

| Устройство управления регулятором переменного напряжения со звеном повышенной частоты | 1976 |

|

SU624347A1 |

| РАДИАЦИОННО-СТОЙКИЙ ЭЛЕМЕНТ ПАМЯТИ ДЛЯ СТАТИЧЕСКИХ ОПЕРАТИВНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК ТРАНЗИСТОРАХ | 2018 |

|

RU2692307C1 |

| D-триггер на КМДП-транзисторах | 1990 |

|

SU1728963A1 |

Изобретение относится к области микроэлектроники. Техническим результатом изобретения является создание симметричного мультиплексора на комплементарных металл-окисел-полупроводник (КМОП) транзисторах, имеющего два сигнальных входа, один вход управления, один выход и выполненного в виде элемента библиотеки стандартных цифровых элементов (СЦЭ), с более высоким качеством коммутации сигналов, за счет более высокой степени идентичности задержек распространения сигналов от сигнальных входов до выхода, вследствие симметрии топологических слоев, которая обеспечивает идентичность паразитных емкостей и сопротивлений и их нахождение в одинаковых электрических режимах; вследствие установки на управляющем входе мультиплексора дополнительных буферных каскадов, с целью обеспечения независимости задержек распространения сигналов от параметров драйвера управляющего входа; а также вследствие увеличения размеров транзисторов, с целью уменьшения влияния локальных внутрикристальных вариаций на идентичность задержек распространения сигналов. 6 ил.

Симметричный мультиплексор на комплементарных металл-окисел-полупроводник (КМОП) транзисторах, содержащий девять р-канальных транзисторов и девять n-канальных транзисторов, причем затворы первого р-канального и первого n-канального транзисторов Т7 и Т1 подключены к информационному (сигнальному) входу В; затворы второго р-канального и второго n-канального транзисторов Т8 и Т2 подключены к информационному (сигнальному) входу А; затворы третьего р-канального, третьего n-канального, четвертого р-канального и четвертого n-канального транзисторов Т12, Т11, Т18 и Т17 подключены к управляющему входу S; стоки третьего р-канального и третьего n-канального транзисторов Т12 и Т11 объединены с затворами пятого р-канального, пятого n-канального и седьмого р-канального транзисторов Т14, Т13 и Т5; стоки четвертого р-канального и четвертого n-канального транзисторов Т18 и Т17 объединены с затворами шестого р-канального, шестого n-канального и восьмого n-канального транзисторов Т16, Т15 и Т4; стоки пятого р-канального и пятого n-канального транзисторов Т14 и Т13 подключены к затвору седьмого n-канального транзистора Т3; стоки шестого р-канального и шестого n-канального транзисторов Т16 и Т15 подключены к затвору восьмого р-канального транзистора Т6; стоки первого р-канального и первого n-канального транзисторов Т7 и Т1 подключены соответственно к истокам седьмого р-канального и седьмого n-канального транзисторов Т5 и Т3; стоки второго р-канального и второго n-канального транзисторов Т8 и Т2 подключены соответственно к истокам восьмого р-канального и восьмого n-канального транзисторов Т6 и Т4; стоки седьмого р-канального, седьмого n-канального, восьмого р-канального и восьмого n-канального транзисторов Т5, Т3, Т6 и Т4 объединены с затворами девятого р-канального и девятого n-канального транзисторов Т10 и Т9; стоки девятого р-канального и девятого n-канального транзисторов Т10 и Т9 подключены к выходу Y; истоки первого, второго, третьего, четвертого, пятого, шестого и девятого р-канальных транзисторов Т7, Т8, Т12, Т18, Т14, Т16 и Т10 подключены к шине питающего напряжения; истоки первого, второго, третьего, четвертого, пятого, шестого и девятого n-канальных транзисторов T1, Т2, T11, Т17, Т13, Т15 и Т9 подключены к шине нулевого потенциала (земле).

| Колосоуборка | 1923 |

|

SU2009A1 |

| US 5773995 A, 30.06.1998 | |||

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| US 6531910 B1, 11.03.2003 | |||

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

Авторы

Даты

2019-05-29—Публикация

2018-09-04—Подача