ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения функциональных узлов для анализа свойств генераторов псевдослучайных последовательностей двоичных чисел, для мониторинга, контроля и управления технологическими процессами.

Известно устройство для детектирования групп бит в бинарной последовательности количества (RU №2728957 С1, МПК G06F 7/74, H03K 21/00, заявл. 15.01.2020, опубл. 03.08.2020, Бюл. №6), содержащее внешний вход данных D1, группу внешних выходов данных QO, группу внешних выходов количества групп QG, группу внешних выходов количества нулей QZ, группу внешних выходов количества единиц QU, группу внешних выходов «разность единиц и нулей» QZU, группы внешних выходов количества единиц в максимальной группе MU, количества нулей в максимальной группе MZ, номера группы максимальной группы единиц NGMU, номера группы максимальной группы нулей NGMZ, номера начала максимальной группы единичных бит NMU и номера начала максимальной группы нулевых бит NMZ, первый RS-триггер пуска-останова TSS 1, блок детектора единиц и нулей 2, третий D-триггер разрешения счета групп ТСЕ 7, третий элемент И 8, первый сумматор SMG 9, второй счетчик бит СВ 10, выходной буфер ОВ 11, четвертый 12, пятый 13 и шестой 14 элементы И, третий счетчик нулей CZ 15, четвертый счетчик единиц CU 16, пятый реверсивный счетчик нулей-единиц CZU 17 и блок преобразователя кода разности 18, первый счетчик CNB 22, первый регистр RNM 23, второй сумматор SNM 24, второй 25, третий 26, четвертый 27, пятый 28, шестой 29, седьмой 32 и восьмой 35 регистры, первый компаратор 30 сравнения количества единичных бит, седьмой элемент И 31, второй компаратор 33 сравнения количества нулевых бит, восьмой элемент И с одним инверсным входом 34, а также введены внешние флаги готовности результата FE, «Буфер заполнен» FF, «Буфер пуст» FZ и флаг «нулей больше единиц» F01.

Данное устройство осуществляет выявление максимальных групп единичных и нулевых бит и определение количества бит в максимальных группах, номеров групп и начала групп в бинарной последовательности. Недостатком данного устройства является отсутствие средств для вычисления кумулятивных сумм частичных подпоследовательностей.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятое за прототип устройство последовательного типа для детектирования групп нулевых и единичных бит и определение их количества (RU №2680759 С1, МПК G06F 7/74, заявл. 16.02.2018, опубл. 26.02.2019, Бюл. №6), в котором для входных последовательностей данных размерностью N, поступающих на внешний вход данных DI, на соответствующих внешних выходах групп устройства формируются двоичные коды, соответствующие количеству групп QG, количеству нулевых бит QZ, количеству единичных бит QU, разности между количеством единичных и нулевых бит QZU, количество бит по группам QO с выходного буфера ОВ, при этом в четных адресах, начиная с нулевого адреса, указывается количество нулевых бит в группах, а в нечетных адресах, начиная с первого адреса, указывается количество единичных бит в группах, а также формируются флаг готовности FE, флаг «нулей больше единиц» F01, флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

Данное устройство выявляет группы единичных и нулевых бит, определяет общее количество и по группам единичных и нулевых бит, вычисляет разность между количеством единичных и нулевых бит во входной последовательности данных размерностью N. Недостатком данного устройства является вычисление общих сумм единичных и нулевых бит, и разности между ними, и отсутствие средств для вычисления кумулятивных сумм частичных подпоследовательностей.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является разработка аппаратных средств для исследования свойств генераторов псевдослучайных последовательностей двоичных чисел, а также для систем принятия решений.

При анализе генераторов псевдослучайных последовательностей двоичных чисел устройство предназначено для вычисления кумулятивных сумм частичных подпоследовательностей, определения циклов отклонений от нуля и подсчет количества отклонений по состояниям.

В задачах принятия решений кумулятивные суммы используются для мониторинга, контроля, управления и ретроспективного анализа. При оценке технологических операций, параметров процессов и характеристик продукции входные данные представляются как последовательные количественные данные, измеряемые непрерывной шкалой или неколичественные данные вида «да»/«нет», «хорошо »/«плохо», «успех»/«отказ» или статистику.

Техническим результатом изобретения является обеспечение возможности вычисления кумулятивных сумм, детектирование и подсчет циклов отклонения сумм от нуля, а также подсчет количества отклонений по состояниям и количества циклов по состояниям, и определение соотношения между количеством единичных и нулевых бит во входной двоичной последовательности.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

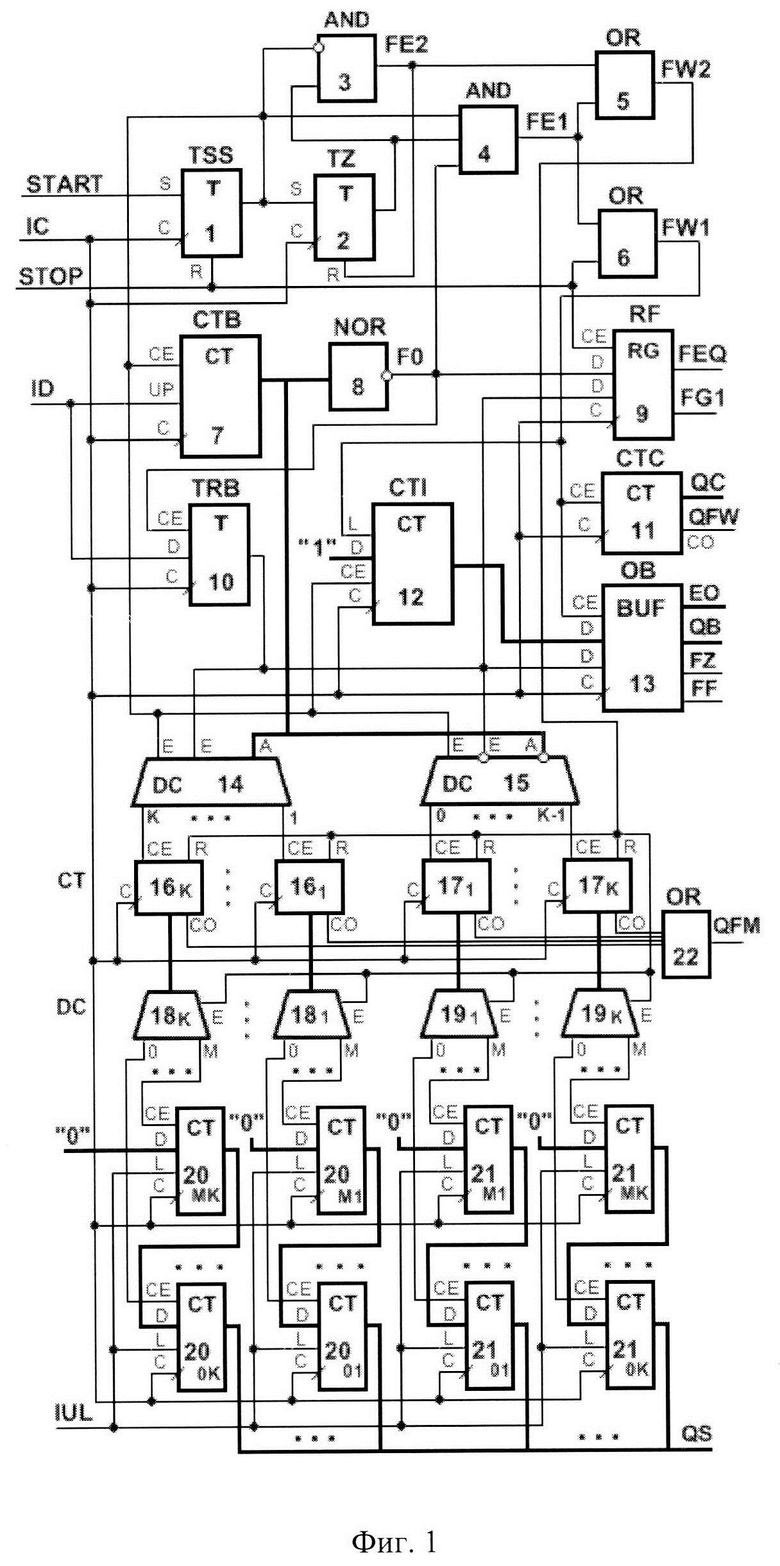

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для вычисления отклонений кумулятивных сумм в двоичной последовательности и определение количества циклов по состояниям содержит внешние входы данных ID и выдачи количества циклов по состояниям IUL, группы внешних выходов параметров цикла QB, количества циклов ОС и количества циклов по состояниям QS, первый RS-триггер пуска-останова TSS 1, второй триггер задержки TZ 2, первый элемент И с инверсным входом 3, второй элемент И 4, первый 5 и второй 6 элементы ИЛИ, первый реверсивный счетчик бит СТВ 7, элемент ИЛИ-НЕ 8, регистр флагов RF 9, третий триггер первого бита цикла TRB 10, второй счетчик количества циклов СТС 11, третий счетчик интервала CTI 12, выходной буфер ОВ 13, первый 14 и второй 15 дешифраторы DC, первую 161, …, 16К и вторую 171, …, 17К группы счетчиков (где К - количество положительных и отрицательных отклонений (состояний) кумулятивных сумм), первую 181, …, 18К и вторую 191, …, 19К группы дешифраторов DC, первую 20[0:М, 1:К] и вторую 21[0:М, 1:К] матрицы счетчиков, содержащие по (М+1) строк и К столбцов (где М - максимальное количество одинаковых состояний в цикле) и элемент ИЛИ 22,

а также введены внешние входы тактового сигнала 1С, пуска устройства START и остановки устройства STOP, внутренние флаг F0 нулевого состояния счетчика бит СТВ 7, флаг FE1 конца цикла, флаг FE2 конца последовательности, флаг FW1 записи цикла и флаг FW2 записи отклонений, внешняя шина управления обменом ЕО, внешние флаги FF «Буфер заполнен», FZ «Буфер пуст», FEQ «равенства нулевых и единичных бит», FG1 «единиц больше нулей», QFM превышения состояний и QFW превышения количества циклов,

причем внешний тактовый вход устройства 1С соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, второго триггера задержки TZ 2, первого реверсивного счетчика бит СТВ 7, регистра флагов RF 9, третьего триггера первого бита цикла TRB 10, второго счетчика количества циклов СТС 11, третьего счетчика интервала CTI12, выходного буфера ОВ 13, счетчиков первой 161, …, 16К и второй 171, …, 17К групп, счетчиков первой 20[0:М, 1:К] и второй 21 [0:М, 1:К] матриц,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1, а также соединен со вторым входом второго элемента ИЛИ бис входом СЕ разрешения работы регистра флагов RF 9,

причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен с входами СЕ разрешения работы первого реверсивного счетчика бит СТВ 7 и третьего счетчика CTI 12, а также соединен с первым инверсным входом первого элемента И 3, с первым входом второго элемента И 4, с первыми прямыми входами Е разрешения работы первого 14 и второго 15 дешифраторов DC и с входом S синхронной установки в единичное состояние второго триггера задержки TZ 2, выход которого соединен со вторым прямым входом первого элемента И 3 и со вторым входом второго элемента И 4, выход которого является внутренним флагом FE1 конца цикла и соединен со вторым входом первого элемента ИЛИ 5 и с первым входом второго элемента ИЛИ 6, выход которого является внутренним флагом FW1 записи цикла и соединен с входами СЕ разрешения работы второго счетчика количества циклов СТС 11 и выходного буфера ОВ 13, а также соединен с входом L разрешения записи третьего счетчика интервала CTI 12, а выход первого элемента И 3 является внутренним флагом FE2 конца последовательности и соединен с входом R синхронной установки в нулевое состояние второго триггера задержки TZ 2 и с первым входом первого элемента ИЛИ 5, выход которого является внутренним флагом FW2 записи отклонений и соединен с входами R синхронной установки в нулевое состояние счетчиков первой 161, …, 16К и второй 171, …, 17К групп и соединен с входами Е разрешения работы дешифраторов первой 181, …, 18К и второй 191, …, 19К групп,

внешний вход данных ID соединен с входом UP направления счета первого реверсивного счетчика бит СТВ 7 и с D-входом третьего триггера первого бита цикла TRB 10, выход которого соединен со вторым D-входом регистра флагов RF 9, со вторым D-входом выходного буфера ОВ 13, со вторым прямым входом Е разрешения работы первого дешифратора DC 14 и со вторым инверсным входом Е разрешения работы второго дешифратора DC 15,

кроме того, группа выходов первого реверсивного счетчика бит СТВ 7 соединена с прямыми адресными входами первого 14 и инверсными адресными входами второго 15 дешифраторов DC и с соответствующими входами элемента ИЛИ-НЕ 8, инверсный выход которого является внутренним флагом F0 нулевого состояния счетчика бит СТВ и соединен с третьим входом второго элемента И 4, с первым D-входом регистра флагов RF 9 и с входом СЕ разрешения работы третьего триггера первого бита цикла TRB 10,

причем набор двоичного кода «1» задан на группу D-входов третьего счетчика интервала CTI 12, группа выходов которого соединена с первой группой D-входов выходного буфера ОВ 13, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 13 являются группой внешних выходов параметров цикла QB и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ,

кроме того, выходы регистра флагов RF 9 являются внешними флагами соответственно «равенства нулевых и единичных бит» FEQ и «единиц больше нулей» FG1, группа выходов второго счетчика СТС И является группой внешних выходов количества циклов QC, а выход переполнения СО второго счетчика СТС 11 является внешним флагом превышения количества циклов QFW,

причем выходы первого дешифратора DC 14, начиная с первого выхода до К-го выхода, соединены с входами С£ разрешения работы одноименных счетчиков первой группы 161, …, 16К, а выходы второго дешифратора DC 14, начиная с нулевого выхода до (К-1)-го выхода, соединены с входами СЕ разрешения работы соответствующих счетчиков второй группы 171, …, 17К, начиная с первого счетчика до К-го счетчика,

кроме того, выходы счетчиков первой 161, …, 16К и второй 171, …, 17К групп соединены с адресными входами одноименных дешифраторов соответственно первой 181, …, 18К и второй 191, …, 19К групп, а выходы переполнения СО счетчиков первой 161, …, 16К и второй 171, …, 17К групп соединены с соответствующими входами третьего элемента ИЛИ 22, выход которого является внешним флагом превышения состояний QFM,

причем (М+1) выходов дешифраторов первой 181, …, 18К и второй 191, …, 19К групп, начиная с нулевого выхода до М-го выхода, соединены с входами СЕ разрешения работы счетчиков соответствующих строк, начиная с нулевой строки до М-ой строки, одноименных столбцов соответственно первой 20 и второй 21 матриц счетчиков, у которых входы L разрешения записи счетчиков соединены с внешним входом выдачи количества циклов по состояниям IUL, а также в К-х строках первой 20 и второй 21 матриц счетчиков на группы D-входов счетчиков заданы нулевые коды «0», а группы D-входов счетчиков первой 20 и второй 21 матриц, начиная с (К-1)-ой строки до нулевой строки, подключены к выходам счетчиков следующих строк соответственно первой 20 и второй 21 матриц, начиная с К-ой строки до первой строки, а выходы счетчиков нулевых строк первой 20 и второй 21 матриц являются соответствующими группами внешних выходов количества циклов по состояниям QS.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

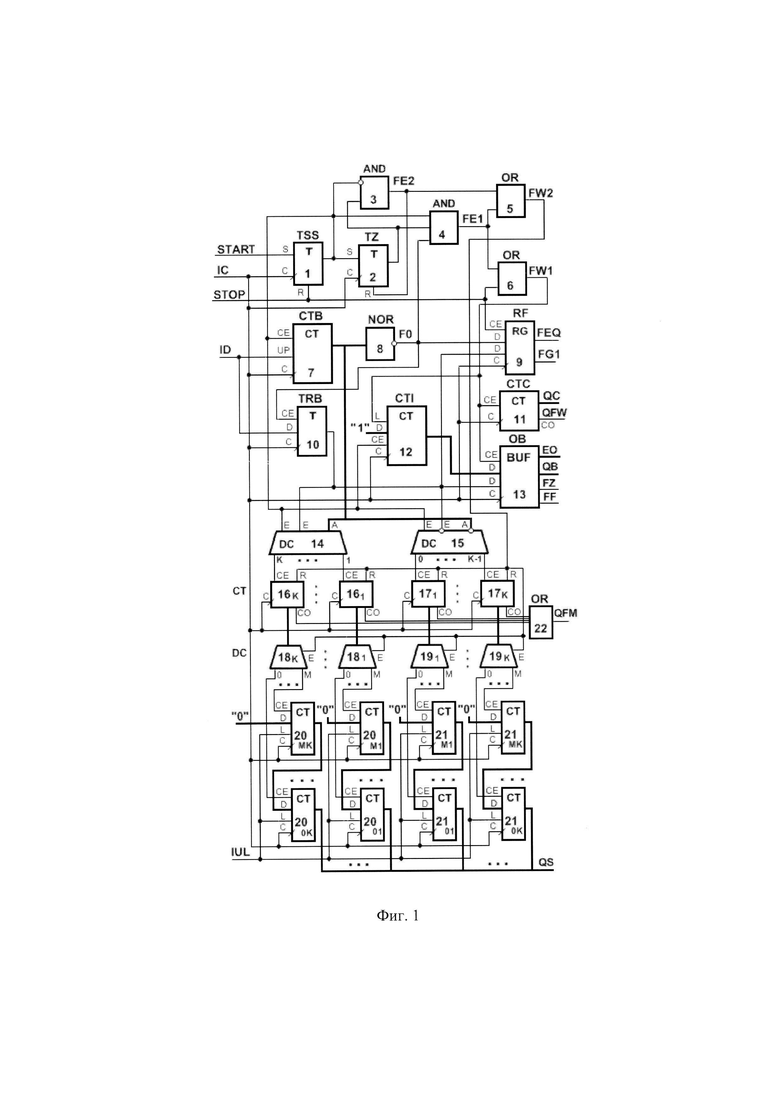

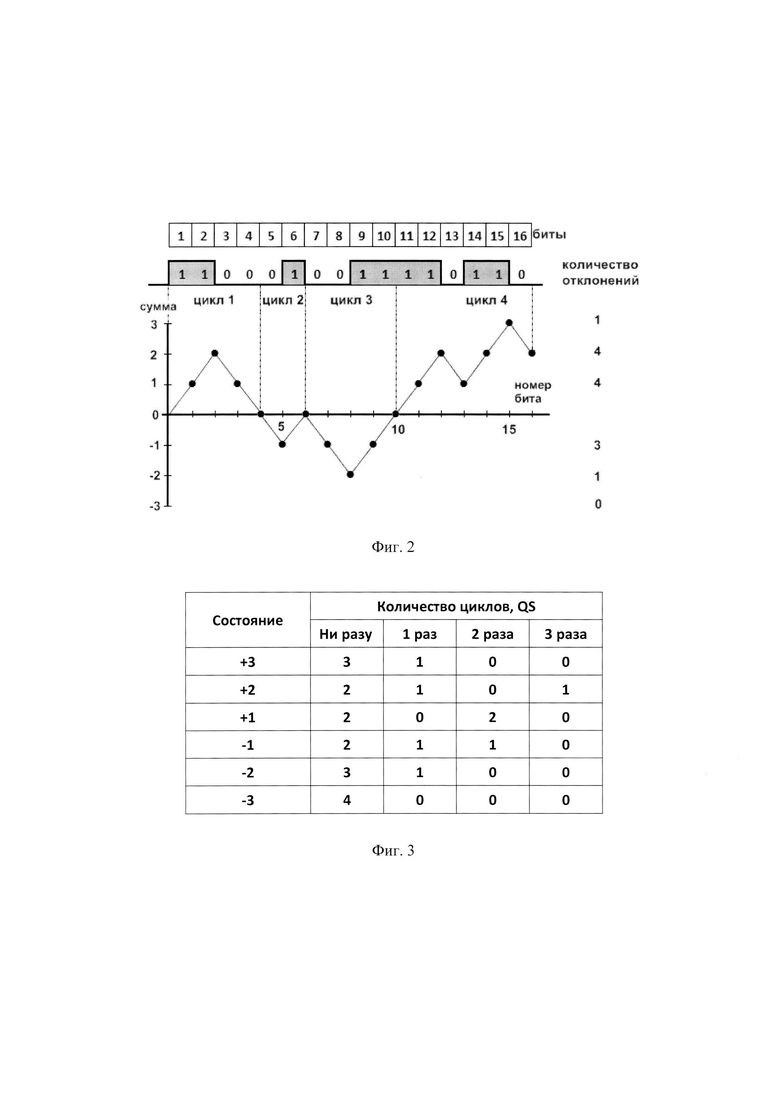

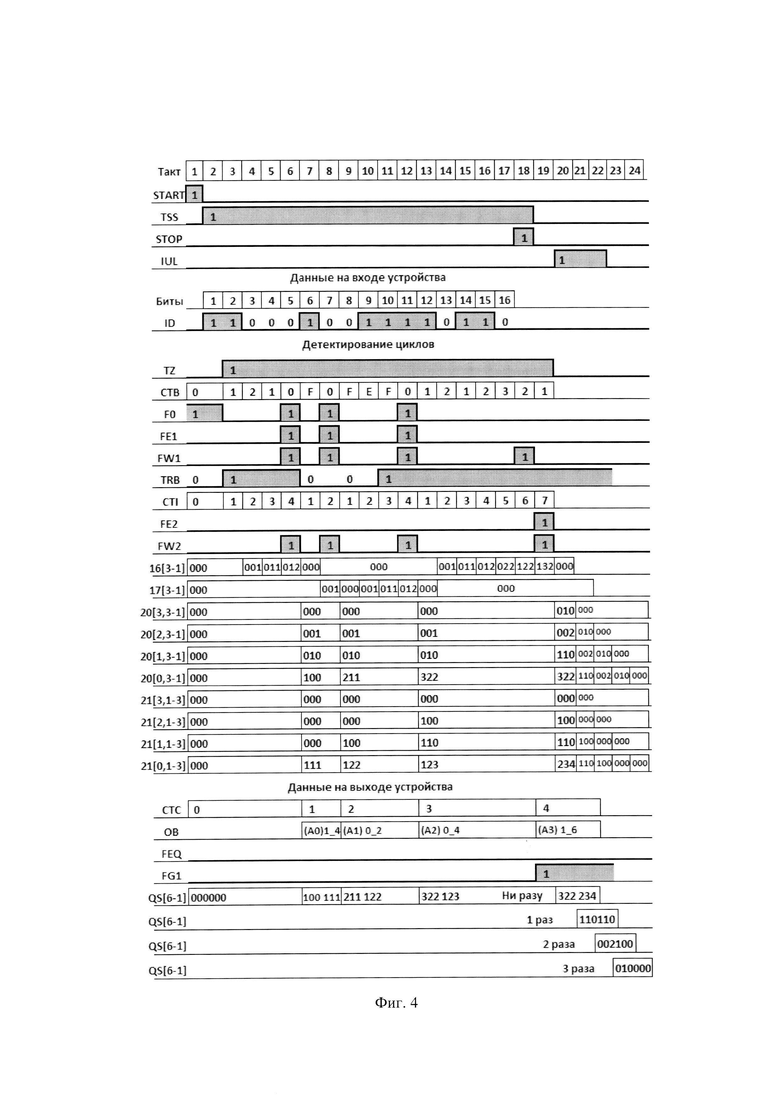

На фиг.1 приведена схема предлагаемого устройства. На фиг.2 приведен график отклонений кумулятивных сумм. На фиг.3 приведена таблица количества циклов по состояниям. На фиг.4 приведена временная диаграмма работы устройства.

На фиг.1-4 и в тексте приняты следующие обозначения:

А - адресные входы,

AND - элемент И,

BUF - буфер с дисциплиной обслуживания FIFO,

С - тактовый вход,

СЕ - вход разрешения работы,

СО - выход переполнения счетчика,

СТ - счетчик,

СТВ - реверсивный счетчик бит,

СТС - счетчик количества циклов,

CTI - счетчик интервала,

D - информационные входы,

DC - дешифратор,

ЕО - внешняя шина управления обменом,

Е - вход разрешения работы дешифраторов,

F0 - внутренний флаг нулевого состояния счетчика бит СТВ,

FE1 - внутренний флаг конца цикла,

FE2 - внутренний флаг конца последовательности,

FW1 - внутренний флаг записи цикла,

FW2 - внутренний флаг записи отклонений,

FEQ - внешний флаг «равенства нулевых и единичных бит»,

FG1 - внешний флаг «единиц больше нулей»,

FF - внешний флаг «Буфер заполнен»,

FZ - внешний флаг «Буфер пуст»,

ID - внешний вход данных,

1С - внешний тактовый вход,

IUL - внешний вход выдачи количества циклов по состояниям,

К - количество состояний (отклонений) кумулятивных сумм,

L - вход разрешения записи,

М - максимальное количество одинаковых состояний в цикле,

N - размерность (длина) входной последовательности данных,

NOR - элемент ИЛИ-НЕ,

ОВ - выходной буфер циклов,

QB - группа внешних выходов параметров цикла,

QC - группа внешних выходов количества циклов,

QFM - внешний флаг превышения состояний М,

QFW - внешний флаг превышения количества циклов W,

QS - группы внешних выходов количества циклов по состояниям,

OR - элемент ИЛИ,

RG - регистр,

RF - регистр флагов,

R - вход синхронной установки в нулевое состояние,

S - вход синхронной установки в единичное состояние,

START - внешний вход пуска,

STOP - внешний вход останова,

Т - триггер,

TRB - триггер первого бита цикла,

TSS - триггер пуска-останова,

TZ - триггер задержки старта,

UP - вход направления счета,

W - максимальное количество циклов,

1 - первый RS-триггер пуска-останова TSS,

2 - второй триггер задержки TZ,

3 - первый элемент И с инверсным входом (AND),

4 - второй элемент И (AND),

5 - первый элемент ИЛИ (OR),

6 - второй элемент ИЛИ (OR),

7 - первый реверсивный счетчик бит СТВ,

8 - элемент ИЛИ-НЕ (NOR),

9 - регистр флагов RF,

10 - третий триггер первого бита цикла TRB,

11 - второй счетчик количества циклов СТС,

12 - третий счетчик интервала CTI,

13 - выходной буфер ОВ,

14 - первый дешифратор DC,

15 - второй дешифратор DC,

161, …, 16К - первая группа счетчиков,

171, …, 17К - вторая группа счетчиков,

181, …, 18К - первая группа дешифраторов DC,

191, …, 19К - вторая группа дешифраторов DC,

20[0:М, 1:К] - первая матрица счетчиков, содержащая (М+1) строк и К столбцов,

21[0:М, 1:К] - вторая матрица счетчиков содержащая (М+1) строк и К столбцов,

22 - третий элемент ИЛИ (OR).

Предлагаемое устройство содержит внешние входы данных ID и выдачи количества циклов по состояниям 1UL, группы внешних выходов параметров цикла QB, количества циклов QC и количества циклов по состояниям QS, первый RS-триггер пуска-останова TSS 1, второй триггер задержки TZ 2, первый элемент И с инверсным входом 3, второй элемент И 4, первый 5 и второй 6 элементы ИЛИ, первый реверсивный счетчик бит СТВ 7, элемент ИЛИ-НЕ 8, регистр флагов RF 9, третий триггер первого бита цикла TRB 10, второй счетчик количества циклов СТС 11, третий счетчик интервала CTI 12, выходной буфер ОВ 13, первый 14 и второй 15 дешифраторы DC, первую 161, …, 16К и вторую 171, …, 17К группы счетчиков (где К - количество положительных и отрицательных отклонений (состояний) кумулятивных сумм), первую 181, …, 18К и вторую 191, …, 19К группы дешифраторов DC, первую 20[0:М, 1:К] и вторую 21[0:М, 1:К] матрицы счетчиков, содержащие по (М+1) строк и К столбцов (где М - максимальное количество одинаковых состояний в цикле) и элемент ИЛИ 22.

В предлагаемое устройство также введены внешние входы тактового сигнала 1С, пуска устройства START и остановки устройства STOP, внутренние флаг F0 нулевого состояния счетчика бит СТВ 7, флаг FE1 конца цикла, флаг FE2 конца последовательности, флаг FW1 записи цикла и флаг FW2 записи отклонений, внешняя шина управления обменом ЕО, внешние флаги FF «Буфер заполнен», FZ «Буфер пуст», FEQ «равенства нулевых и единичных бит», FG1 «единиц больше нулей», QFM превышения состояний и QFW превышения количества циклов.

Первый реверсивный счетчик бит СТВ 7 предназначен для вычислений текущих кумулятивных сумм (состояний, отклонений) входной последовательности. Второй счетчик количества циклов СТС 11 осуществляет счет общего количества циклов. Третий счетчик интервала CTI 12 осуществляет счет количества бит в цикле - определяет размерность цикла. Третий триггер TRB 10 предназначен для фиксации значения первого бита цикла, а регистр флагов RF 9 для фиксации флагов FEQ «равенства нулевых и единичных бит» и FG1 «единиц больше нулей» - соотношения между количеством единичных и нулевых бит во входной последовательности. Счет количества нахождений в каждом из К состояний (отклонений) в каждом цикле осуществляется для положительной области в первой группе счетчиков 161, …, 16К и для отрицательной области во второй группе счетчиков 171, …, 17К. Счет количества циклов по одинаковым состояниям во входной последовательности осуществляется для положительной области в первой матрице счетчиков 20 и для отрицательной области во второй матрице счетчиков 21.

Внешний тактовый вход устройства 1С соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, второго триггера задержки TZ 2, первого реверсивного счетчика бит СТВ 7, регистра флагов RF 9, третьего триггера первого бита цикла TRB 10, второго счетчика количества циклов СТС 11, третьего счетчика интервала CTI12, выходного буфера ОВ 13, счетчиков первой 161, …, 16К и второй 171, …, 17К групп, счетчиков первой 20[0:М, 1:К] и второй 21[0:М, 1:К] матриц.

Внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1.

Внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1, а также соединен со вторым входом второго элемента ИЛИ бис входом СЕ разрешения работы регистра флагов RF 9.

Первый RS-триггер пуска-останова TSS 1 предназначен для выделения цикла работы предлагаемого устройства, между сигналами START и STOP, для входной последовательности данных ID размерности N. Причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен с входами СЕ разрешения работы первого реверсивного счетчика бит СТВ 7 и третьего счетчика CTI 12, а также соединен с первым инверсным входом первого элемента И 3, с первым входом второго элемента И 4, с первыми прямыми входами Е разрешения работы первого 14 и второго 15 дешифраторов DC и с входом S синхронной установки в единичное состояние второго триггера задержки TZ2.

Выход второго триггера задержки TZ 2 соединен со вторым прямым входом первого элемента И 3 и со вторым входом второго элемента И 4, выход которого является внутренним флагом FE1 конца цикла и соединен со вторым входом первого элемента ИЛИ 5 и с первым входом второго элемента ИЛИ 6, выход которого является внутренним флагом FW1 записи цикла и соединен с входами СЕ разрешения работы второго счетчика количества циклов СТС 11 и выходного буфера ОВ 13, а также соединен с входом L разрешения записи третьего счетчика интервала CTI 12.

Выход первого элемента И 3 является внутренним флагом FE2 конца последовательности и соединен с входом R синхронной установки в нулевое состояние второго триггера задержки TZ 2 и с первым входом первого элемента ИЛИ 5, выход которого является внутренним флагом FW2 записи отклонений и соединен с входами R синхронной установки в нулевое состояние счетчиков первой 161, …, 16К и второй 171, …, 17К групп и соединен с входами Е разрешения работы дешифраторов первой 181, …, 18К и второй 191, …, 19К групп.

Внешний вход данных ID соединен с входом UP направления счета первого реверсивного счетчика бит СТВ 7 и с D-входом третьего триггера первого бита цикла TRB 10, выход которого соединен со вторым D-входом регистра флагов RF 9, со вторым D-входом выходного буфера ОВ 13, со вторым прямым входом Е разрешения работы первого дешифратора DC 14 и со вторым инверсным входом Е разрешения работы второго дешифратора DC 15.

Группа выходов первого реверсивного счетчика бит СТВ 7 соединена с прямыми адресными входами первого 14 и инверсными адресными входами второго 15 дешифраторов DC и с соответствующими входами элемента ИЛИ-НЕ 8, инверсный выход которого является внутренним флагом F0 нулевого состояния счетчика бит СТВ и соединен с третьим входом второго элемента И 4, с первым D-входом регистра флагов RF 9 и с входом СЕ разрешения работы третьего триггера первого бита цикла TRB 10.

Набор двоичного кода «1» задан на группу D-входов третьего счетчика интервала CTI 12, группа выходов которого соединена с первой группой D-входов выходного буфера ОВ 13, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 13 являются группой внешних выходов параметров цикла QB и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

Выходы регистра флагов RF 9 являются внешними флагами соответственно «равенства нулевых и единичных бит» FEQ и «единиц больше нулей» FG1, группа выходов второго счетчика СТС 11 является группой внешних выходов количества циклов QC, а выход переполнения СО второго счетчика СТС 11 является внешним флагом превышения количества циклов QFW.

Выходы первого дешифратора DC 14, начиная с первого выхода до К-го выхода, соединены с входами СЕ разрешения работы одноименных счетчиков первой группы 161, …, 16К, а выходы второго дешифратора DC 14, начиная с нулевого выхода до (К-1)-го выхода, соединены с входами СЕ разрешения работы соответствующих счетчиков второй группы 171, …, 17К, начиная с первого счетчика до К-го счетчика.

Выходы счетчиков первой 161, …, 16К и второй 171, …, 17К групп соединены с адресными входами одноименных дешифраторов соответственно первой 181, …, 18К и второй 191, …, 19К групп, а выходы переполнения СО счетчиков первой 161, …, 16К и второй 171, …, 17К групп соединены с соответствующими входами третьего элемента ИЛИ 22, выход которого является внешним флагом превышения состояний QFM.

Причем (М+1) выходов дешифраторов первой 181, …, 18К и второй 191, …, 19К групп, начиная с нулевого выхода до М-го выхода, соединены с входами СЕ разрешения работы счетчиков соответствующих строк, начиная с нулевой строки до М-ой строки, одноименных столбцов соответственно первой 20 и второй 21 матриц счетчиков, у которых входы L разрешения записи счетчиков соединены с внешним входом выдачи количества циклов по состояниям IUL. Кроме того, в К-х строках первой 20 и второй 21 матриц счетчиков на группы D-входов счетчиков заданы нулевые коды «0». Группы D-входов счетчиков первой 20 и второй 21 матриц, начиная с (К-1)-ой строки до нулевой строки, подключены к выходам счетчиков следующих строк соответственно первой 20 и второй 21 матриц, начиная с К-ой строки до первой строки. Выходы счетчиков нулевых строк первой 20 и второй 21 матриц являются соответствующими группами внешних выходов количества циклов по состояниям QS.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем.

Предлагаемое устройство позволяет определять кумулятивные суммы подпоследовательностей (циклов) во входной N-разрядной двоичной последовательности. Кумулятивные суммы считаются для нормализованной последовательности, в которой нулевой бит исходной последовательности принимается за «-1», а каждый единичный бит - за «+1». На каждом такте вычисляется сумма всех предыдущих бит и определяется отклонение текущей суммы от нуля. При этом текущее числовое значение кумулятивной суммы (отклонение) называется состоянием (на фиг.2 состояния отмечены точками на графике частичных кумулятивных сумм). Биты между нулевыми значениями сумм (нулевыми состояниями) делят входную N-разрядную последовательность на подпоследовательности (циклы). При этом в каждом цикле количество единичных бит равно количеству нулевых бит, кроме последнего цикла, на основании которого определяется общее соотношение между количеством единичных и нулевых бит во входной последовательности.

В предлагаемом устройстве детектируются циклы кумулятивных сумм, осуществляется вычисление размерности (длительности) циклов и проводится подсчет количества циклов, а также осуществляется подсчет нахождения кумулятивных сумм в каждом из К положительных и К отрицательных состояний (отклонений) в каждом цикле и подсчет количества циклов по состояниям. На группу внешних выходов QS выдается количество циклов по состояниям в зависимости от количества раз (от 0 до М раз) нахождения в одинаковых состояниях для всей входной последовательности.

На фиг.2 приведен пример вычисления кумулятивных сумм для входной N=16 разрядной последовательности и отмечены К=3 отрицательных и К=3 положительных отклонений (состояний): -3, -2, -1, +1, +2, +3. При этом в каждом из К состояний кумулятивная сумма находится не более М=3 раз. Точки (биты) пересечения горизонтальной оси (когда текущая сумма равна нулю) делят последовательность на циклы. На графике на фиг.2 входная N=16 разрядная последовательность делится на четыре цикла. В предлагаемом устройстве проводится выявление циклов и определяется их размерность - количество бит в цикле. Кроме того, на третьем триггере TRB 10 фиксируется значение первого бита в цикле, который заказывает на направление (наклон) пересечения горизонтальной оси (нулевая сумма) - при единичном бите TRB=1 цикл размещается в положительной области графика, а при нулевом TRB=0 - в отрицательной области.

На внешний вход данных ID последовательно разряд за разрядом поступают биты входной последовательности данных размерностью N, которые далее передаются на D-вход триггера первого бита в цикле TRB 10 и на вход UP направления счета первого счетчика бит СТВ 7. При единичном значении бита ID=1 осуществляется увеличение (UP=1 - инкремент, суммирование) значения счетчика СТВ 7, а при нулевом значении бита ID=0 - уменьшение (UP=0 - декремент, вычитание).

В предлагаемом устройстве вычисление кумулятивной суммы осуществляется на первом реверсивном счетчике бит СТВ 7, счет числа бит в цикле осуществляется на третьем счетчике интервала СП 12, а счет числа циклов осуществляется на втором счетчике СТС 11. Флаг F0 нулевого состояния первого реверсивного счетчика бит СТВ 7 (когда значение кумулятивной суммы равно нулю) формируется на выходе элемента ИЛИ-НЕ (NOR) 8. Значения числа бит в цикле с выхода счетчика интервала CTI 12 и значение с триггера первого бита в цикле TRB 10 последовательно записываются в выходной буфер ОВ 13 при единичном значении флага записи цикла FW1=1.

Текущее значение кумулятивных сумм (состояние, отклонение) с выхода первого реверсивного счетчика бит СТВ 7 преобразуется в унитарный код «1 из К» на первом дешифраторе DC 14 для положительных состояний и на втором дешифраторе DC 15 для отрицательных состояний (текущая кумулятивная сумма для нормализованной последовательности отрицательная - меньше нуля). Счет количества нахождений в каждом из К состояний (отклонений) в каждом цикле осуществляется для положительной области в первой группе счетчиков 161, …, 16К и для отрицательной области во второй группе счетчиков 171, …, 17К. При этом нулевой выход первого 14 дешифратора DC не используется - не осуществляется счет нахождений в нулевых состояниях, так как их суммарное количество соответствует количеству циклов во входной последовательности.

Значения количества нахождений в каждом из К состояний положительной и отрицательной областей в каждом цикле с выходов первой 161, …, 16К и второй 171, …, 17К групп счетчиков передаются на адресные входы соответственно первой 181, …, 18К и второй 191, …, 19К групп дешифраторов DC, на которых преобразуются в унитарные коды «1 из М», где М - максимальное количество одинаковых состояний в цикле, а нулевое значение соответствует отсутствию нахождения сумм в соответствующем состоянии. Далее в соответствии с единичными значениями на выходах первой 181, …, 18К и второй 191, …, 19К групп дешифраторов DC, при единичном значении флага записи отклонений FW2=1, осуществляется подсчет циклов в соответствующих счетчиках первой 20[0:М, 1:К] и второй 21[0:М, 1:К] матриц. Например, в М-х строках первой 20[М, 1:К] и второй 21 [М, 1:К] матриц осуществляется счет циклов соответственно в 1, К состояниях в которых суммы находятся М-раз, а в нулевых строках первой 20[0, 1:К] и второй 21 [0, 1:К] матриц - в которых суммы не находятся ни разу (отсутствие нахождения в состоянии).

После передачи N бит входной последовательности, при единичном значении на внешнем входе выдачи количества циклов по состояниям IUL-T на группу внешних выходов QS выдаются количество циклов для К положительных и К отрицательных состояний последовательно в течении М тактов в зависимости от количества раз нахождения в них, начиная с отсутствия нахождения в состояниях (0 раз или ни разу) до М раз. На фиг.3 приведена таблица выходных данных QS (по столбцам) для количества циклов по состояниям +3, +2, +1, -1, -3, -2 (при К=3 и М=3) для входной N=16 разрядной последовательности приведенной на фиг.2.

Перед началом работы в начальное нулевое состояние устанавливаются триггеры и счетчики, а также устанавливается начальный нулевой адрес в выходном буфере ОВ 13.

Устройство начинает работать после подачи единичного сигнала пуска START=1, по которому в единичное состояние устанавливается первый RS-триггер 1 пуска-останова TSS=1 и далее на втором такте устанавливается в единичное состояние второй триггер 2 TZ=1, на котором осуществляется задержка сигнала START=1 на один такт, для запрета на втором такте формирования единичных значений внутренних флагов записи FW1 и FW2.

На внешний вход данных ID биты начинают поступать на втором такте, после сигнала START=1, и далее поступают в каждом такте 1С.Данные с входа ID поступают на вход направления счета UP счетчика бит СТВ 7 и на D-вход триггера первого бита в цикле TRB 10. На следующих тактах осуществляется реверсивный счет на первом счетчике бит СТВ 7, в зависимости от значения входного бита ID, и счет бит на счетчике интервала CTI 12. При этом значение кода с выхода счетчика бит СТВ 7 преобразуется в унитарные коды «1 из К» на первом DC 14 и втором DC 15 дешифраторах, которые соответствуют соответствующему отклонению (состоянию) суммы. Поэтому на каждом такте осуществляется счет в соответствующем счетчике из первой 161, …, 16К или второй 171, …, 17К групп. При этом если значение хотя бы в одном из счетчиков превысит значение М, то формируется единичное значение переполнения на выходе СО соответствующего счетчика, по которому формируется единичное значение внешнего флага QFM=1 превышения состояний М. После ввода последнего N-го разряда входного двоичного числа на следующем такте задается единичный сигнал остановки STOP=l.

При формировании единичного значения флага F0=1 кулевого состояния первого реверсивного счетчике бит СТВ 7 и единичных состояниях первого TSS=1 и второго TZ=1 триггеров формируется единичные значения флага записи цикла FW1=T на выходе второго элемента ИЛИ 6 и флага записи отклонений FW2=1 на выходе первого элемента ИЛИ 5. При этом в счетчике интервала СП 12 будет установлено значение количества бит в текущем цикле (интервале).

По единичному флагу записи цикла FW1=1 проводится увеличение (счет) циклов на втором счетчике СТС 11 и запись в выходной буфер ОВ 13 - значений с выхода счетчика интервала CTI 12 и триггера первого бита в цикле TRB 10. Одновременно по единичному значению флага записи цикла FW1=1 осуществляется загрузка кода «1» в третий счетчик интервала CTI 12. Кроме того, если значение счетчика СТС 11 превысит заданное максимальное количество циклов W, то на его выходе СО формируется единичное значение, по которому формируется единичное значение внешнего флага превышения количества циклов QFW=1.

По единичному флагу записи отклонений FW2=T осуществляется счет в соответствующих счетчиках первой 20[0:М, 1:К] и второй 21[0:М, 1:К] матриц - подсчет количества циклов по состояниям. Кроме того, по флагу записи отклонений FW2=1 устанавливаются в нулевое состояние счетчики первой 161, …, 16К и второй 171, …, 17К групп.

На следующих тактах 1С осуществляется детектирование следующих циклов во входной последовательности и при их выявлении выполняется запись размерности циклов со счетчика интервала CTI12 и первого бита в цикле с триггера TRB 10 в выходной буфер ОВ 13. Если в последнем цикле кумулятивная сумма не равна нулю (количество единиц не равно количеству нулей), при этом установлено нулевое значение флага F0=0, то формирование единичного значения флага записи цикла FW1=T на выходе первого элемента ИЛИ 6 осуществляется по единичному сигналу остановки STOP=l, по которому осуществляется запись в выходной буфер ОВ 13 значений для последнего цикла.

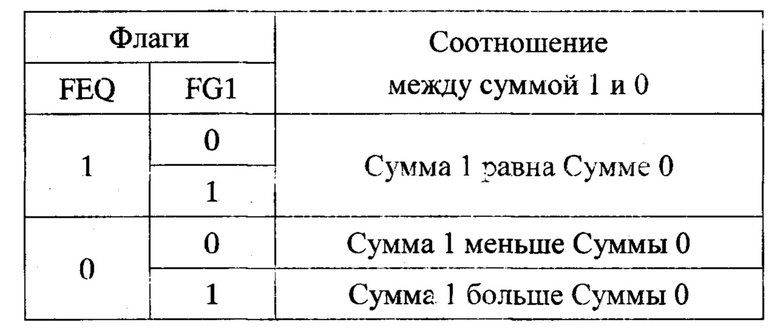

Кроме того, в устройстве осуществляется оценка соотношения между количеством единичных бит и количеством нулевых бит. Для этого в последнем цикле входной последовательности анализируются значения флага F0 нулевого состояния первого реверсивного счетчике бит СТВ 7 и третьего триггера первого бита в цикле TRB 10, которые по единичному сигналу остановки STOP=l записываются в регистр флага RF 9 и формируются соответствующие внешние флаги устройства - флаг FEQ «равенства нулевых и единичных бит» и флаг FG1 «единиц больше нулей». Соотношения между количеством единичных и нулевых бит, в зависимости от установленных флагов, следующие:

Кроме того, осуществляется задержка сигнала остановки STOP=1 на один такт - импульс формируется на выходе первого элемента И 3 (флаг конца последовательности FE2), по которому осуществляется счет в соответствующих счетчиках первой 20[0:М, 1:К] и второй 21[0:М, 1:К] матриц для последнего цикла.

Кроме того, после сигнала остановки STOP=1 при задании единичного значения на внешнем входе выдачи количества циклов по состояниям IUL=1 осуществляется в течении М тактов последовательная выдача на группу внешних выходов QS количества циклов для К положительных и К отрицательных состояний в зависимости от количества раз нахождения в них, начиная с отсутствия нахождения в состоянии (0 раз или ни разу) до М раз.

Предлагаемое устройство работает следующим образом.

На фиг.2 приведен график отклонений от нуля вычисляемых кумулятивных сумм для входной N=16 разрядной последовательности для К=3 отрицательных и К=3 положительных состояний: -3, -2, -1, +1, +2, +3. На фиг.4 приведена временная диаграмма устройства.

Перед началом работы в начальное нулевое состояние устанавливаются - триггеры TSS 1, TZ 2 и TRB 10, счетчики СТВ 7, СТС 11 и СП 12, регистр RF 9, группы счетчиков 161, …, 16К и 171, …, 17К, и счетчики в матрицах 20[0:М, 1:К] и 21[0:М, 1:К], а также устанавливается начальный нулевой адрес в выходном буфере ОВ 13. При этом формируется единичное значение флага F0=1 нулевого состояния счетчика бит СТВ 7 на выходе элемента ИЛИ-НЕ 8.

Работа устройства для каждой входной последовательности начинается после подачи единичного сигнала START=1. При этом но фронту тактового сигнала 1С (такт 2 на фиг.4) в единичное состояние устанавливается первый RS-триггер 1 пуска-останова TSS=1, по которому на следующих тактах 1С разрешается работа реверсивного счетчика бит СТВ 7 и счетчика интервала CTI 12. В такте 3 в единичное состояние переключается второй 2 триггер задержки TZ=1, но которому на следующих тактах IC разрешается формирование внутренних флага конца цикла FE1 на выходе второго элемента И 4 и флага конца последовательности FE2 на выходе первого элемента И 3 с инверсным входом.

В такте 3 при единичном значении ID=1 (фиг.4) на входе данных, первого бита входной последовательности заданное в такте 2, осуществляется увеличение на единицу счетчиков бит СТВ=1 и интервала CTI=1. Одновременно в такте 3, так как было установлено единичное значение флага F0=1 нулевого состояния счетчика бит СТВ 7, при значении F0=1, также в единичное состояние устанавливается третий триггер 10 первого бита цикла TRB=1. Далее в такте 4 по значению кода со счетчика бит СТВ=1 единичное значение формируется на первом выходе первого дешифратора DC 14, по которому осуществляется увеличение (счет) в первом счетчике 161 первой группы.

Кроме того, в такте 4 при единичном значении ID=1, для второго входного бита, также осуществляется счет в счетчиках и устанавливаются коды: СТВ=2 и CTI=2. При этом запрещен прием в третий триггер TRB 10, так как в такте 3 при значении счетчика СТВ=1 установился нулевой флаг F0=0 (такт 3). На графике фиг.2 для второго бита отмечено отклонение кумулятивной суммы в состояние «+2». Кроме того, по значению кода со счетчика бит СТВ-2 единичное значение формируется на втором выходе первого дешифратора DC 14, по которому осуществляется увеличение (счет) во втором счетчике I62 первой группы и устанавливается значение в первой группе 16 [3-1]=011.

В такте 4 также поступает нулевое значение ID=0 третьего бита входной последовательности, по которому в такте 5 осуществляется вычитание (декремент) в счетчике бит СТВ=1 и увеличение счетчика интервала CTI=3. При этом по значению кода со счетчика бит СТВ=1 единичное значение формируется на первом выходе первого дешифратора DC 14, по которому осуществляется увеличение (счет) в первом счетчике 16i первой группы и устанавливаются значение в первой группе 16[3-1]=012.

Аналогично для четвертого бита задается нулевое значение ID=0, по которому в такте 6 устанавливаются коды: СТВ=0 и CTI=4. Одновременно при нулевом состоянии счетчика бит СТВ=0 на выходе элемента ИЛИ-НЕ 8 формируется единичное значение внутреннего флага F0=T, которое соответствует нулевой текущей кумулятивной сумме - выявлен первый цикл размерностью четыре бита, значение которого установлено на счетчике 12 интервала CTI=4. При нулевом коде счетчика бит СТВ=0 единичный код устанавливается на нулевом выходе первого дешифратора DC 14, который не используется, поэтому нет счета в группах счетчиков.

Далее также в такте 6 формируется единичный флаг конца цикла FE1=1, по которому далее формируется единичный флаг записи цикла FW1=1, по которому разрешается работа выходного буфера ОВ 13, в который в такте 7 по нулевому адресу записывается код ОВ (А0)=1_4 - единичное значение первого бита цикла с триггера TRB=1 и значение кода с выхода счетчика интервала CTI=4. Одновременно по флагу FW1=1 осуществляется увеличение (счет) кода в счетчике количества циклов СТС=1. Кроме того, единичное значение флага FW1=1 также поступает на вход L разрешения записи в счетчик интервала CTI, по которому в такте 7 осуществляется загрузка кода «1» в счетчик интервалов CTI=1.

Одновременно в такте 6 формируется единичный флаг записи отклонений FW2=T на выходе первого элемента ИЛИ 5, по которому разрешается работа первой 181, …, 18К и второй 191, …, 19К групп дешифраторов, на соответствующих выходах которых формируются единичные значения, по которым в такте 7 осуществляется счет в первой матрице 20 - в нулевой строке в третьем столбце 20[0, 3-1]=100 - отсутствие нахождения в состоянии «+3», в первой строке во втором столбце 20[1, 3-1]=010 - нахождение один раз в состоянии «+2», во второй строке в первом столбце 20[2, 3-1]=001 - нахождение два раза в состоянии «+1» и отсутствие счета в третьей строке 20[3, 3-1]=000 - отсутствие нахождений 3 раза во всех положительных состояниях, а также осуществляется счет во второй матрице 21 - в нулевой строке по трем столбцам 21[0, 1-3]=111 - отсутствие нахождения в состояниях «-1», «-2», «-3» и отсутствие счета в первой, второй и третьей строках счетчиков, гак как не было отклонений в отрицательной области. При этом на внешнюю шину количества циклов QS передаются значения счетчиков нулевых строк первой и второй матриц и устанавливается значение QS[6-1]=100 111 - количество циклов отсутствия нахождения в соответствующих состояниях. Кроме того, по единичному флагу записи отклонений FW2=1 в такте 7 в нулевое состояние устанавливаются счетчики первой группы 161, …, 16К.

Одновременно в такте 6 поступает нулевое значение ID=0 пятого бита входной последовательности, по которому в такте 7 осуществляется вычитание (декремент) в счетчике бит CTB=F (код 1111 для четырехразрядного счетчика или состояние «-1») и в нулевое состояние устанавливается третий триггер 10 первого бита цикла TRB=0, так как в такте 6 было установлено единичное значение флага F0=1. При значении TRB=0 запрещается работа первого дешифратора DC 14 и разрешается работа второго дешифратора DC 15. Поэтому в такте 7 по значению кода со счетчика бит CTB=F, которое передается на инверсные входы второго дешифратора DC 15, единичное значение формируется на нулевом выходе DC 15, по которому осуществляется увеличение (счет) в первом счетчике 171 второй группы и устанавливается значение во второй группе 17[3-1]=001.

В такте 8 по входному единичному значению ID=T для шестого бита входной последовательности осуществляется счет в счетчике интервала СТ1=2 и инкремент (увеличение) в счетчике бит СТВ 7 и устанавливается нулевое состояние СТВ=0 - нулевая кумулятивная сумма, т.е. выявлен второй цикл размерностью два бита и первый бит цикла нулевой TRB=0. Данные значения в такте 9 записываются в выходной буфер ОВ 13 по первому адресу ОВ (А1)=0_2, а также увеличивается счетчик количества циклов СТС=2.

Одновременно по единичному флагу записи отклонений FW2=1 в такте 8 разрешается работа первой 181, …, 18К и второй 191, …, 19К групп дешифраторов, на соответствующих выходах которых формируются единичные значения, по которым в такте 9 осуществляется счет в первой матрице 20 только в нулевой строке в первом, втором и третьем столбцах - отсутствие нахождения в состояниях «+3», «+2» и «+1» и устанавливается код 20[0, 3-1]=211, а также осуществляется счет во второй матрице 21 в нулевой строке во втором и третьем столбцах 21 [0, 1-3]=122 - отсутствие нахождения в состояниях «-2» и «-3», в первой строке в первом столбце 21 [1, 1-3]=100 -нахождение один раз в состоянии «-1», и отсутствие счета во второй и третьей строках счетчиков. При этом на внешнюю шину количества циклов QS передаются значения счетчиков нулевых строк первой и второй матриц и устанавливается значение QS[6-1]=211 122 - количество циклов отсутствия нахождения в соответствующих состояниях. Кроме того, по единичному флагу записи отклонений FW2=1 в такте 9 в нулевое состояние устанавливаются счетчики второй группы 171, …, 17К.

Следующий третий цикл выявлен на такте 12 для входных данных ID=0011 (седьмого - десятого входных бит) для которых в такте 13 в выходной буфер ОВ 13 по второму адресу записываются коды ОВ (А2)=0_4 и увеличивается счетчик количества циклов СТС=3. При этом для третьего цикла также осуществлялся счет отрицательных состояний во второй 171, …, 17К группе счетчиков, в которой устанавливается код 17[3-1]=012.

Одновременно по единичному флагу записи отклонений FW2=1 в такте 12 разрешается работа первой 181, …, 18К и второй 191, …, 19К групп дешифраторов, на соответствующих выходах которых формируются единичные значения, по которым в такте 13 осуществляется счет в первой матрице 20 только в нулевой строке в первом, втором и третьем столбцах - отсутствие нахождения в состояниях «+3», «+2» и «+1» и устанавливается код 20[0, 3-1]=322, а также осуществляется счет во второй матрице 21 в нулевой строке только третьем столбце 21 [0, 1-3]=123 - отсутствие нахождения в состоянии «-3», в первой строке во втором столбце 21 [1, 1-3]=110 - нахождение один раз в состоянии «-2», во второй строке в первом столбце 21 [2, 1-3]=100 - нахождение два раза в состоянии «-1» и отсутствие счета в третьей строке счетчиков 21[3, 1-3]=000 - отсутствие нахождений 3 раза во всех отрицательных состояниях. При этом на внешнюю шину количества циклов QS передаются значения счетчиков нулевых строк первой и второй матриц и устанавливается значение OS[6-1]=322-123 - количество циклов отсутствия нахождения в соответствующих состояниях. Кроме того, по единичному флагу записи отклонений FW2=1 в такте 13 в нулевое состояние устанавливаются счетчики второй группы 171, …, 17К.

Далее для следующих шести входных бит, с одиннадцатого до шестнадцатого бита, на внешний вход данных ГО в тактах 12-17 последовательно поступает код ID=110110. Отклонения кумулятивной суммы от нуля приведены в положительной области графика на фиг.2. Аналогично приведенному выше алгоритму осуществляется работа триггера первого бита цикла TRB 10 и счетчиков СТВ 7 и CTI 12. Поэтому в такте 18 устанавливаются коды - TRB=1, СТВ=2 и СТ1=6.

Одновременно в такте 18 поступает единичный сигнал останова STOP=1, по которому в нулевое состояние переключается RS-триггер 1 пуска-останова TSS=0. Кроме того, по единичному сигналу STOP=1 формируется единичный флаг записи цикла FW1=1, по которому разрешается работа выходного буфера ОВ 13, в который в такте 19 по третьему адресу записывается код ОВ (А3)=1_6 - единичное значение для первого бита четвертого цикла с триггера TRB=1 и значение кода с выхода счетчика интервала СТ1=6. При этом четвертый цикл кумулятивных сумм не пересекает нулевое значение - общая кумулятивная сумма для N=16 разрядной входной последовательности равна значению СТВ=2. Одновременно по флагу FW1=1 осуществляется увеличение кода в счетчике циклов СТС=4. Кроме того, по единичному сигналу STOP=l разрешается запись в регистр флагов RF 9 соответствующих значений флага нулевого состояния F0=0 и с выхода триггера первого бита цикла TRB=1. Поэтому формируются внешние флаги: нулевое значение флага равенства нулевых и единичных бит FEQ-0 и единичное значение флага «единиц больше нулей» FG1=1.

Кроме того, в такте 19 в первой группе счетчиков устанавливается код 16[3-1]=132. Также в такте 19 на выходе первого элемента И 3 формируется единичное значение внутреннего флага конца последовательности FE2=1, по которому на выходе первого элемента ИЛИ 5 формируется единичное значение флага записи отклонений FW2=1, по которому разрешается работа первой 181, …, 18К и второй 191, …, 19К групп дешифраторов и далее в такте 20 осуществляется счет и устанавливаются следующие коды: в первой матрице 20 - в первой строке 20[1, 3-1]=110, во второй строке 20[2, 3-1]=002, в третьей строке 20[3, 3-1]=010, а во второй матрице 21 только в нулевой строке 21[0,1-3]=234.

При этом после сигнала остановки STOP=1 в такте 20 на внешнюю шину количества циклов QS передаются значения счетчиков нулевых строк первой 20 и второй 21 матриц и устанавливается код QS[6-1]=322 234 - количество циклов отсутствия нахождения в соответствующих состояниях. Далее в тактах 20-22 задается единичное значение на внешнем входе выдачи количества циклов по состояниям IUL=1. При этом осуществляется последовательная передача между строками первой 20 и второй 21 матриц счетчиков в направлении 0-ой строки и осуществляется последовательная выдача на группу внешних выходов количества циклов по состояниям QS: в такте 21 устанавливается код QS[6-1]=110 110 - количество циклов нахождения 1 раз в состояниях «+3», «+2», «-1» и «-2», в такте 22 устанавливается код QS[6-1]=002 100 - количество циклов нахождения 2 раза в состояниях «+1» и «-1», в такте 23 устанавливается код QS[6-1]=010 000 - количество циклов нахождения 3 раза в состояниях «+2» (столбцы QS в таблице на фиг.3 для графика отклонений приведенного на фиг.2).

Таким образом, для входной N=16 разрядной входной последовательности данных, содержащей девять единичных бит и семь нулевых бит, приведенной на фиг.2-4, выявлено четыре цикла QC=4, для которых соответствующие значения первых бит цикла и размерности циклов записаны в выходной буфер ОВ 13 по четырем адресам ОВ(А0), …, ОВ(А3), определено соотношение - количество единиц (9) больше количества нулей (7), поэтому сформированы значения внешних флагов FEQ=0 и FG1=1, а также в счетчиках первой 20 и второй 21 матриц получены значения количества циклов по состояниям в зависимости от количества раз нахождения в одинаковых состояниях для всей входной последовательности.

Считывание результатов на группу внешних выходов параметров цикла QB из выходного буфера ОВ 13 выполняется под управлением по внешней шине управления обменом ЕО. При реализации выходного буфера ОВ в виде двухпортовой памяти FIFO, обмен можно выполнять в процессе вычисления кумулятивных сумм с учетом значений соответствующих флагов «Буфер пуст» FZ и «Буфер заполнен» FF.

Предлагаемое устройство может быть применено для аппаратной реализации статистических тестов, разработанных лабораторией информационных технологий Национального института стандартов и технологий (NIST, США), целью которых является определение меры случайности двоичных последовательностей, порожденных генераторами случайных чисел. В частности, предлагаемое устройство реализует тесты кумулятивных сумм и произвольных отклонений, в которых определяется сумма нормализованной последовательности и осуществляется подсчет циклов и отклонений в состояниях циклов, а также реализуется частотный побитовый тест, который заключается в определении соотношения между нулями и единицами во всей двоичной последовательности.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу и соответствует заявляемому техническому результату - реализация возможности вычисления кумулятивных сумм, детектирование и подсчет циклов отклонения сумм от нуля, а также подсчет количества отклонений по состояниям и количества циклов по состояниям, а также определение соотношения между количеством единичных и нулевых бит во входной последовательности.

Изобретение относится к области вычислительной техники. Технический результат заключается в возможности вычисления кумулятивных сумм, детектирования и подсчета циклов отклонения сумм от нуля, а также подсчета количества отклонений по состояниям и количества циклов по состояниям, и определения соотношения между количеством единичных и нулевых бит во входной двоичной последовательности. Устройство содержит внешние входы данных ID и выдачи количества циклов по состояниям IUL, группы внешних выходов параметров цикла QB, количества циклов QC и количества циклов по состояниям QS, первый RS-триггер пуска-останова TSS 1, второй триггер задержки TZ 2, первый элемент И с инверсным входом 3, второй элемент И 4, первый 5 и второй 6 элементы ИЛИ, первый реверсивный счетчик бит СТВ 7, элемент ИЛИ-НЕ 8, регистр флагов RF 9, третий триггер первого бита цикла TRB 10, второй счетчик количества циклов СТС 11, третий счетчик интервала CTI 12, выходной буфер ОВ 13, первый 14 и второй 15 дешифраторы DC, первую 161, …, 16К и вторую 171, …, 17К группы счетчиков (где К - количество положительных и отрицательных отклонений (состояний) кумулятивных сумм), первую 181, …, 18К и вторую 191, …, 19К группы дешифраторов DC, первую 20[0:М, 1:К] и вторую 21[0:М, 1:К] матрицы счетчиков, содержащие по (М+1) строк и К столбцов (где М - максимальное количество одинаковых состояний в цикле) и элемент ИЛИ 22, а также введены внешние входы тактового сигнала 1С, пуска устройства START и остановки устройства STOP, внутренние флаги F0 нулевого состояния счетчика бит СТВ 7, FE1 конца цикла, FE2 конца последовательности, FW1 записи цикла и FW2 записи отклонений, внешняя шина управления обменом ЕО, внешние флаги FF «Буфер заполнен», FZ «Буфер пуст», FEQ «равенства нулевых и единичных бит», FG1 «единиц больше нулей», QFM превышения состояний и QFW превышения количества циклов. 4 ил.

Устройство для вычисления отклонений кумулятивных сумм в двоичной последовательности и определение количества циклов по состояниям, содержащее внешние входы данных ID и выдачи количества циклов по состояниям IUL, группы внешних выходов параметров цикла QB, количества циклов QC и количества циклов по состояниям QS, первый RS-триггер пуска-останова TSS 1, второй триггер задержки TZ 2, первый элемент И с инверсным входом 3, второй элемент И 4, первый 5 и второй 6 элементы ИЛИ, первый реверсивный счетчик бит СТВ 7, элемент ИЛИ-НЕ 8, регистр флагов RF 9, третий триггер первого бита цикла TRB 10, второй счетчик количества циклов СТС 11, третий счетчик интервала CTI 12, выходной буфер ОВ 13, первый 14 и второй 15 дешифраторы DC, первую 161, …, 16К и вторую 171, …, 17К группы счетчиков (где К - количество положительных и отрицательных отклонений (состояний) кумулятивных сумм), первую 181, …, 18К и вторую 191, …, 19К группы дешифраторов DC, первую 20[0:М, 1:К] и вторую 21[0:М, 1:К] матрицы счетчиков, содержащие по (М+1) строк и К столбцов (где М - максимальное количество одинаковых состояний в цикле) и элемент ИЛИ 22, а также введены внешние входы тактового сигнала 1С, пуска устройства START и остановки устройства STOP, внутренние флаг F0 нулевого состояния счетчика бит СТВ 7, флаг FE1 конца цикла, флаг FE2 конца последовательности, флаг FW1 записи цикла и флаг FW2 записи отклонений, внешняя шина управления обменом ЕО, внешние флаги FF «Буфер заполнен», FZ «Буфер пуст», FEQ «равенства нулевых и единичных бит», FG1 «единиц больше нулей», QFM превышения состояний и QFW превышения количества циклов,

причем внешний тактовый вход устройства 1С соединен с входами синхронизации С первого RS-триггера пуска-останова TSS 1, второго триггера задержки TZ 2, первого реверсивного счетчика бит СТВ 7, регистра флагов RF 9, третьего триггера первого бита цикла TRB 10, второго счетчика количества циклов СТС 11, третьего счетчика интервала CTI12, выходного буфера ОВ 13, счетчиков первой 161, …, 16К и второй 171, …, 17К групп, счетчиков первой 20[0:М, 1:К] и второй 21[0:М, 1:К] матриц,

внешний вход пуска устройства START соединен с входом S синхронной установки в единичное состояние первого RS-триггера пуска-останова TSS 1,

внешний вход остановки устройства STOP соединен с входом R синхронной установки в нулевое состояние первого RS-триггера пуска-останова TSS 1, а также соединен со вторым входом второго элемента ИЛИ 6 и с входом СЕ разрешения работы регистра флагов RF 9,

причем прямой выход первого RS-триггера пуска-останова TSS 1 соединен с входами СЕ разрешения работы первого реверсивного счетчика бит СТВ 7 и третьего счетчика CTI 12, а также соединен с первым инверсным входом первого элемента И 3, с первым входом второго элемента И 4, с первыми прямыми входами Е разрешения работы первого 14 и второго 15 дешифраторов DC и с входом S синхронной установки в единичное состояние второго триггера задержки TZ 2, выход которого соединен со вторым прямым входом первого элемента И 3 и со вторым входом второго элемента И 4, выход которого является внутренним флагом FE1 конца цикла и соединен со вторым входом первого элемента ИЛИ 5 и с первым входом второго элемента ИЛИ 6, выход которого является внутренним флагом FW1 записи цикла и соединен с входами СЕ разрешения работы второго счетчика количества циклов СТС 11 и выходного буфера ОВ 13, а также соединен с входом L разрешения записи третьего счетчика интервала CTI 12, а выход первого элемента И 3 является внутренним флагом FE2 конца последовательности и соединен с входом R синхронной установки в нулевое состояние второго триггера задержки TZ 2 и с первым входом первого элемента ИЛИ 5, выход которого является внутренним флагом FW2 записи отклонений и соединен с входами R синхронной установки в нулевое состояние счетчиков первой 161, …, 16К и второй 171, …, 17К групп и соединен с входами Е разрешения работы дешифраторов первой 181, …, 18К и второй 191, …, 19К групп,

внешний вход данных ID соединен с входом UP направления счета первого реверсивного счетчика бит СТВ 7 и с D-входом третьего триггера первого бита цикла TRB 10, выход которого соединен со вторым D-входом регистра флагов RF 9, со вторым D-входом выходного буфера ОВ 13, со вторым прямым входом Е разрешения работы первого дешифратора DC 14 и со вторым инверсным входом Е разрешения работы второго дешифратора DC 15,

кроме того, группа выходов первого реверсивного счетчика бит СТВ 7 соединена с прямыми адресными входами первого 14 и инверсными адресными входами второго 15 дешифраторов DC и с соответствующими входами элемента ИЛИ-НЕ 8, инверсный выход которого является внутренним флагом F0 нулевого состояния счетчика бит СТВ и соединен с третьим входом второго элемента И 4, с первым D-входом регистра флагов RF 9 и с входом СЕ разрешения работы третьего триггера первого бита цикла TRB 10,

причем набор двоичного кода «1» задан на группу D-входов третьего счетчика интервала CTI 12, группа выходов которого соединена с первой группой D-входов выходного буфера ОВ 13, который также подключен к внешней шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 13 являются группой внешних выходов параметров цикла QB и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ,

кроме того, выходы регистра флагов RF 9 являются внешними флагами соответственно «равенства нулевых и единичных бит» FEQ и «единиц больше нулей» FG1, группа выходов второго счетчика СТС 11 является группой внешних выходов количества циклов QC, а выход переполнения СО второго счетчика СТС 11 является внешним флагом превышения количества циклов QFW,

причем выходы первого дешифратора DC 14, начиная с первого выхода до К-го выхода, соединены с входами СЕ разрешения работы одноименных счетчиков первой группы 161, …, 16к, а выходы второго дешифратора DC 14, начиная с нулевого выхода до (К-1)-го выхода, соединены с входами СЕ разрешения работы соответствующих счетчиков второй группы 171, …, 17К, начиная с первого счетчика до К-го счетчика,

кроме того, выходы счетчиков первой 161, …, 16К и второй 171, …, 17К групп соединены с адресными входами одноименных дешифраторов соответственно первой 181, …, 18К и второй 191, …, 19К групп, а выходы переполнения СО счетчиков первой 161, …, 16К и второй 171, …, 17К групп соединены с соответствующими входами третьего элемента ИЛИ 22, выход которого является внешним флагом превышения состояний QFM,

причем (М+1) выходов дешифраторов первой 181, …, 18К и второй 191, …, 19К групп, начиная с нулевого выхода до М-го выхода, соединены с входами СЕ разрешения работы счетчиков соответствующих строк, начиная с нулевой строки до М-ой строки, одноименных столбцов соответственно первой 20 и второй 21 матриц счетчиков, у которых входы L разрешения записи счетчиков соединены с внешним входом выдачи количества циклов по состояниям IUL, а также в К-х строках первой 20 и второй 21 матриц счетчиков на группы D-входов счетчиков заданы нулевые коды «0», а группы D-входов счетчиков первой 20 и второй 21 матриц, начиная с (К-1)-ой строки до нулевой строки, подключены к выходам счетчиков следующих строк соответственно первой 20 и второй 21 матриц, начиная с К-ой строки до первой строки, а выходы счетчиков нулевых строк первой 20 и второй 21 матриц являются соответствующими группами внешних выходов количества циклов по состояниям QS.

| УСТРОЙСТВО ПОСЛЕДОВАТЕЛЬНОГО ТИПА ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2018 |

|

RU2680759C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ДИАПАЗОНА ЕДИНИЧНЫХ БИТ | 2019 |

|

RU2717631C1 |

| US 6029187 A1, 22.02.2000 | |||

| СПОСОБ ПОЛУЧЕНИЯ И ВОСПРОИЗВЕДЕНИЯ ЦВЕТНЫХ ИЗОБРАЖЕНИЙ | 1930 |

|

SU39578A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 2018 |

|

RU2696223C1 |

Авторы

Даты

2025-03-14—Публикация

2024-07-17—Подача